104S-C中文资料

DB104中文资料

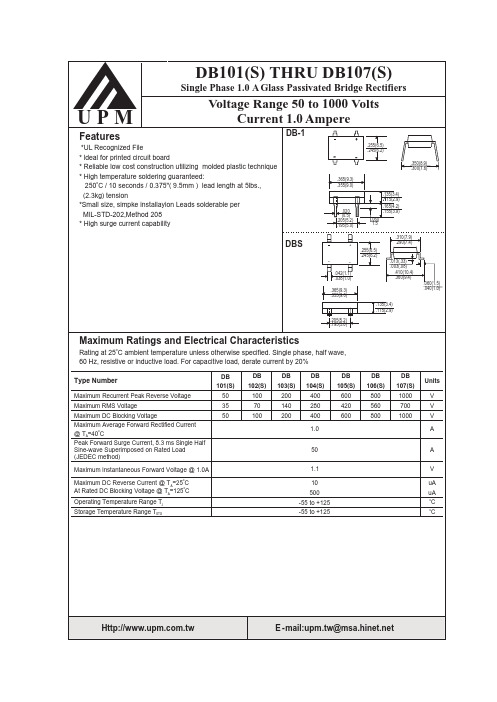

Maximum Ratings and Electrical Characteristics

DB 101(S) 50 35 50 DB 102(S) 100 70 100 DB 103(S) 200 140 200

DB 104(S) 400 280 400 1.0 50 1.1 10 500 -55 to +125 -55 to VERSE CURRENT . ( A )

10

INSTANTANEOUS FORWARD CURRENT . ( A )

10

FIG . 4 - TYPICAL FORWARD CHARACTERISTICS PER BRIDGE ELEMENT

1

1.0

0.1

Tj = 25 OC PULSE WIDTH-300 S 2% DUTY CYCLE

Maximum Recurrent Peak Reverse Voltage Maximum RMS Voltage Maximum DC Blocking Voltage Maximum Average Forward Rectified Current @ TA=40oC Peak Forward Surge Current, 8.3 ms Single Half Sine-wave Superimposed on Rated Load (JEDEC method) Maximum lnstantaneous Forward Voltage @ 1.0A Maximum DC Reverse Current @ TA=25 C At Rated DC Blocking Voltage @ TA=125oC Operating Temperature Range TJ Storage Temperature Range TSTG

100S-D中文资料

230 — — KF

240 T A KA

277 — T —

380… 400 N — —

415 B — —

440 G N —

480 — B —

500 M — —

550 C — —

600 — C —

Electronic Coil w/PLC Interface ➋ 100S-D95… 100S-D250 100S-D300… 100S-D420 100S-D630… 100S-D860

元器件交易网

Contactors & Control Relays

Safety Contactors

100S-D Specifications Conformity to Standards

IEC 60947-4 IEC 60947-4 Annex F IEC 60947 Type “2” Coordination CSA 22.2 No. 14 UL 508

V DC DC DC

24 EZJ — —

48…72 EZY EZY —

110…130 EZD EZD ED

ቤተ መጻሕፍቲ ባይዱ

200…255 EZA EZA EA

➊ The N.C. contacts meet IEC 60947-4 Annex F requirements to mirror contact performance. The N.C. mirror contacts are wired in series or parallel and must

V 50/60 Hz 50/60 Hz 50/60 Hz

24 EJ — —

42… 64 EY EY —

100 EP EP EP

DVHV2812SFR-XXX资料

DVHV2800S SeriesHIGH RELIABILITY HYBRIDDC-DC CONVERTERSDESCRIPTIONThe DVHV series of high reliability DC-DCconverters is operable over the full military (-55 °C to +125 °C) temperature range with no power derating. Unique to the DVHV series is a magnetic feedback circuit that is radiation immune. Operating at a nominal fixed frequency of 475 kHz, these regulated, isolated units utilize well controlled undervoltage lockout circuitry to eliminate slow start-up problems. The output voltage is trimmable up to +10% or down –20%.These converters are designed and manufactured ina facility qualified to ISO9001 and certified to MIL-PRF-38534 and MIL-STD-883.This product may incorporate one or more of thefollowing U.S. patents:5,784,2665,790,3895,963,4385,999,4336,005,7806,084,7926,118,673 FEATURES• High Reliability • Very Low Output Noise • Output Voltage Trim Up +10% or Down –20% • Wide Input Voltage Range: 15 to 50 Volts per MIL-STD-704 • Up to 15 Watts Output Power • Radiation Immune Magnetic Feedback Circuit • NO Use of Optoisolators • Undervoltage Lockout • Indefinite Short Circuit Protection• Current Limit Protection• Industry Standard Pinout• High Input Transient Voltage: 80 Volts for 1 sec per MIL-STD-704A • Radiation Hardened Version Available • Precision Seam Seal or Solder Seal Hermetic Package • Custom Versions Available • Additional Environmental Screening Available • Meets MIL-STD-461C and MIL-STD-461D EMC Requirements When Used With a DVMC28 EMI Filter • Flanged and Non-flanged Versions Available. •MIL-PRF-38534 Element Evaluated ComponentsFigure 1 – DVHV2800S / DVHV2800SF DC-DC Converter(Not To Scale )DVHV2800S SeriesSPECIFICATIONS (T CASE = -55°C to +125°C, V IN = +28V ± 5%, Full Load, Unless Otherwise Specified)ABSOLUTE MAXIMUM RATINGSInput Voltage (Continuous)50 V DC Junction Temperature Rise to Case +15°CInput Voltage (Transient, 1 second) 80 Volts Storage Temperature-65°C to +150°C Output Power 115 Watts Lead Solder Temperature (10 seconds) 270°CPower Dissipation (Full Load, T CASE = +125°C)11 WattsWeight (Maximum) (Un-Flanged / Flanged)(49 / 52) GramsDVHV283R3S DVHV2805SParameter Conditions Min Typ Max Min Typ Max UnitsSTATICContinuous 15 28 50 15 28 50 V INPUTVoltage4Transient, 1 sec - - 80 - - 80 VInhibited - - 6 - - 6 mA CurrentNo Load - - 90 - - 90 mARipple Current Full Load, 20Hz to 10MHz--50--50mA p-pInhibit Pin Input40 - 1.5 0 - 1.5 V Inhibit Pin Open Circuit Voltage 49.0 11.0 13.0 9.0 11.0 13.0 V UVLO Turn On 12.0-14.812.0-14.8VUVLO Turn Off 411.0 - 14.5 11.0 - 14.5 V V OUT T CASE =25°C 3.26 3.30 3.34 4.95 5.00 5.05 VOUTPUTVoltageV OUT T CASE =-55°C to +125°C 3.25 3.30 3.35 4.925 5.00 5.075 VPower3 0 - 10 0 - 15 W Current 3V OUT0 - 3.03 0 - 3.0 ARipple Voltage V OUT Full Load, 20Hz to 10MHz - - 30 - - 30 mV p-p Line Regulation V OUT V IN = 15V to 50V - - 20 - - 20 mV Load Regulation V OUTNo Load to Full Load --50--50mVEFFICIENCY68 - - 73 - - % Overload 4- - 11 - - 11 W LOAD FAULT POWER DISSIPATION Short Circuit- - 11 - - 11 W CAPACITIVE LOAD4- - 1000 - - 1000 µF SWITCHING FREQUENCY400 475 550 400 475 550 kHzSYNC FREQUENCY RANGEV H – V L = 5VDuty Cycle = 20% - 80% 500 - 600 500 - 600 kHzISOLATION 500 V DC 100 - - 100 - - M Ω MTBF (MIL-HDBK-217F)AIF @ T C =55°C- 413 - - 413 - kHrsDYNAMICLoad Step Output Transient V OUT - - 200 - - 300 mV PK Load Step Recovery 2Half Load to Full Load - - 550 - - 500 µSec Line Step Output Transient 4V OUT - 300 600 - 300 600 mV PK Line Step Recovery 2, 4V IN = 16V to 40V - 300 500 - 300 500 µSec Turn On Delay V OUT- - 20 - - 20 mSecTurn On OvershootV IN = 0V to 28V- - 15 - - 25 mV PKNotes: 1. Dependant on output voltage.2. Time for output voltage to settle within 1% of its nominal value.3. Derate linearly to 0 at 135°C.4. Verified by qualification testing.DVHV2800S SeriesSPECIFICATIONS (T CASE = -55°C to +125°C, V IN = +28V ± 5%, Full Load, Unless Otherwise Specified)ABSOLUTE MAXIMUM RATINGSInput Voltage (Continuous)50 V DC Junction Temperature Rise to Case +15°CInput Voltage (Transient, 1 second) 80 Volts Storage Temperature-65°C to +150°C Output Power 115 Watts Lead Solder Temperature (10 seconds) 270°CPower Dissipation (Full Load, T CASE = +125°C)11 WattsWeight (Maximum) (Un-Flanged / Flanged)(49 / 52) GramsDVHV2812S DVHV2815SParameter Conditions Min Typ Max Min Typ MaxUnitsSTATICContinuous 15 28 50 15 28 50 V INPUTVoltage4Transient, 1 sec - - 80 - - 80 VInhibited - - 6 - - 6 mA CurrentNo Load - - 90 - - 90 mARipple Current Full Load, 20Hz to 10MHz--50--50mA p-pInhibit Pin Input40 - 1.5 0 - 1.5 V Inhibit Pin Open Circuit Voltage 49.0 11.0 13.0 9.0 11.0 13.0 V UVLO Turn On 12.0-14.812.0-14.8VUVLO Turn Off 411.0 - 14.5 11.0 - 14.5 V V OUT T CASE =25°C 11.88 12.0 12.12 14.85 15.0 15.15 V OUTPUTVoltageV OUT T CASE = -55°C to +125°C 11.8212.012.1814.77515.015.225VPower3 0 - 15 0 - 15 W Current 3V OUT0 - 1.25 0 - 1.0 ARipple Voltage V OUT Full Load, 20Hz to 10MHz - - 40 - - 40 mV p-p Line Regulation V OUT V IN = 15V to 50V - - 20 - - 20 mV Load Regulation V OUTNo Load to Full Load --50--50mVEFFICIENCY77 - - 77 - - % Overload4- - 11 - - 11 W LOAD FAULT POWER DISSIPATION Short Circuit - - 11 - - 11 W CAPACITIVE LOAD4- - 500 - - 500 µF SWITCHING FREQUENCY400 475 550 400 475 550 kHzSYNC FREQUENCY RANGEV H – V L = 5VDuty Cycle = 20% - 80% 500 - 600 500 - 600 KHzISOLATION 500 V DC 100 - - 100 - - M Ω MTBF (MIL-HDBK-217F)AIF @ T C =55°C- 413 - - 413 - kHrsDYNAMICLoad Step Output Transient V OUT - - 300 - - 350 mV PK Load Step Recovery 2Half Load to Full Load - - 550 - - 450 µSec Line Step Output Transient 4V OUT - 500 900 - 500 900 mV PK Line Step Recovery 2, 4V IN = 16V to 40V - 300 500 - 300 500 µSec Turn On Delay V OUT- - 20 - - 20 mSecTurn On OvershootV IN = 0V to 28V- - 50 - - 50 mV PKNotes: 1. Dependant on output voltage.2. Time for output voltage to settle within 1% of its nominal value.3. Derate linearly to 0 at 135°C.4. Verified by qualification testing.DVHV2800S SeriesSPECIFICATIONS (T CASE = -55°C to +125°C, V IN = +28V ± 5%, Full Load, Unless Otherwise Specified)ABSOLUTE MAXIMUM RATINGSInput Voltage (Continuous)50 V DC Junction Temperature Rise to Case +15°CInput Voltage (Transient, 1 second) 80 Volts Storage Temperature-65°C to +150°C Output Power 115 Watts Lead Solder Temperature (10 seconds) 270°CPower Dissipation (Full Load, T CASE = +125°C)11 WattsWeight (Maximum) (Un-Flanged / Flanged)(49 / 52) GramsDVHV285R2SParameter Conditions Min Typ MaxUnitsSTATICContinuous 15 28 50 V INPUTVoltage4Transient, 1 sec - - 80 V Inhibited - - 6 mACurrentNo Load- - 90 mA Ripple Current Full Load, 20Hz to 10MHz--50mA p-pInhibit Pin Input40 - 1.5 V Inhibit Pin Open Circuit Voltage 49.0 11.0 13.0 V UVLO Turn On12.0 - 14.8 V UVLO Turn Off 411.0 - 14.5 VV OUT T CASE = 25°C5.148 5.20 5.252 V OUTPUTVoltageV OUT T CASE = -55°C to +125°C5.1225.205.278VPower3 0 - 15 W Current3V OUT 0 - 3.0 A Ripple Voltage V OUT Full Load, 20Hz to 10MHz - - 30 mV p-p Line Regulation V OUT V IN = 15V to 50V - - 20 mV Load RegulationV OUTNo Load to Full Load --50mVEFFICIENCY 73 - - % Overload4- - 11 W LOAD FAULT POWER DISSIPATION Short Circuit --11WCAPACITIVE LOAD4- - 1000 µFSWITCHING FREQUENCY400 475 550 kHz SYNC FREQUENCY RANGEV H – V L = 5VDuty Cycle = 20% - 80% 500 - 600 kHzISOLATION 500 V DC 100 - - M Ω MTBF (MIL-HDBK-217F)AIF @ T C = 55°C-413-kHrsDYNAMICLoad Step Output Transient V OUT - - 300 mV PK Load Step Recovery 2Half Load to Full Load - - 500 µSec Line Step Output Transient 4V OUT - 300 600 mV PK Line Step Recovery 2, 4V IN = 16V to 40V - 300 500 µSecTurn On Delay V OUT- - 20 mSec Turn On OvershootV IN = 0V to 28V- - 25 mV PKNotes: 1. Dependant on output voltage.2. Time for output voltage to settle within 1% of its nominal value.3. Derate linearly to 0 at 135°C.4. Verified by qualification testing.DVHV2800S SeriesBLOCK DIAGRAMUNDER VOLTAGE SHUTDOWNPRIMARY HOUSEKEEPINGSUPPLYPWM CONTROLVOLTAGE AND CURRENT AMPLIFIERSSECONDARY HOUSEKEEPINGSUPPLYPIN 128V INPIN 10IN COML1C1Q1Rs1T1D1C2Rs2+V OUTPIN 5PIN 4OUT COM INHPIN 2FEEDBACKMAGNETIC SYNCPIN 9TRIM PIN 3Figure 2CONNECTION DIAGRAM10IN COM 2INH128V IN5+V OUT4OUT COMLOAD+-28 VdcSYNC9Figure 3DVHV2800S SeriesINHIBIT DRIVE CONNECTION DIAGRAMSFigure 4 – Internal Inhibit Circuit and Recommended DriveFigure 5 – Isolated Inhibit Drive(Shown with optional capacitor for turn-on delay)(Shown with optional capacitor for turn-on delay)EMI FILTER HOOKUP DIAGRAM10IN COM 2INH128V IN5+V OUT4OUT COMLOAD+-28 Vdc228V OUT4OUT COM 128V IN5IN COMCASE6, 7, 8SYNC93DVMC28 EMI FILTERDVHV2800S DC-DC CONVERTERFigure 6 – Converter with EMI FilterDVHV2800S SeriesPARALLEL CONNECTION DIAGRAM10IN COM 2INH128V IN5+V OUT4OUT COMLOAD+-28 Vdc228V OUT4OUT COM128V IN5IN COMCASESYNC936, 7, 86, 7, 8DVMC28 EMI FILTERDVHV2800S DC-DC CONVERTERCASE10IN COM 2INH128V IN 5+V OUT4OUT COMSYNC9DVHV2800S DC-DC CONVERTERCASEFigure 7DVHV2800S Series OUTPUT VOLTAGE TRIMThe output voltage can be trimmed down byconnecting a resistor between the TRIM pin(PIN 3) and the +V OUT pin (PIN 5), or canbe trimmed up by connecting a resistorbetween the TRIM pin (PIN 3) and the OUTCOM pin (PIN 4). The maximum trim rangeis +10% up and –20% down. Theappropriate resistor values versus theoutput voltage are given in the trim tablebelow.Figure 8 – Output Voltage TrimDVHV283R3S DVHV2805S DVHV285R2S DVHV2812S DVHV2815S+V OUT (V) R TRIM (Ω) +V OUT (V) R TRIM (Ω) +V OUT (V) R TRIM (Ω) +V OUT (V) R TRIM (Ω) +V OUT (V) R TRIM (Ω)3.75 25.4k 5.5 19k 5.7 23k 13.2 5.93k 16.75 03.70 32.5k 5.4 31.5k 5.6 36.5k 13.0 10.1k 16.50 1.67k3.65 41.8k 5.3 52.3k 5.5 59k 12.8 16.5k 16.25 5k3.60 54.2k5.2 94k 5.4 104k 12.6 27.1k 16.00 10k3.55 71.6k 5.1 219k 5.3 239k 12.4 48.4k 15.75 18.3k3.50 98.2k 5.0 - 5.2 - 12.2113.7k15.5035k3.45 143.2k4.9 209k5.1 249.8k 12.0 - 15.25 85k3.40 236k4.8 84k5.0 104k 11.8 437k 15.00 -3.35 543k4.7 42.3k 4.9 55.4k 11.6 209k 14.75 475k3.30 -4.6 21.5k 4.8 31.1k 11.4 132k 14.50 225k3.25 102k4.5 9k 4.7 16.5k 11.2 93k 14.25 142k3.20 34.8k 4.4 0 4.6 6.8k 11.0 69.5k 14.00 100k3.1510.5k 10.8 53.8k 13.75 75k3.100 10.642.6k 13.50 58.3k10.434.2k13.2546.4k10.227.6k13.0037.5k10.022.4k12.7530.6k9.818.1k12.5025k9.614.5k12.2520.5k9.411.5k12.0016.7k9.28.88k9.06.63kDVHV2800S SeriesEFFICIENCY PERFORMANCE CURVES (T CASE = 25°C, Full Load, Unless Otherwise Specified)V IN = 16VV IN = 28VV IN = 40V45505560657075345678910Output Power (W)E f f i c i e n c y (%)505560657075803691215Output P ow er (W)E f f i c i e n c y (%)Figure 9 – DVHV283R3S Figure 10 – DVHV2805S / DVHV285R2S Efficiency (%) vs. Output Power (W)Efficiency (%) vs. Output Power (W)6065707580853691215Output P ow er (W)E f f i c i e n c y (%)6065707580853691215Output Power (W)E f f i c i e n c y (%)Figure 11 – DVHV2812S Figure 12 – DVHV2815S Efficiency (%) vs. Output Power (W)Efficiency (%) vs. Output Power (W)DVHV2800S Series EMI PERFORMANCE CURVES(T CASE = 25°C, V IN = +28V ± 5%, Full Load, Unless Otherwise Specified)Figure 13 – DVHV2800S without EMI FilterFigure 14 – DVHV2800S with EMI FilterDVHV2800S Series PACKAGE SPECIFICATIONS (NON-FLANGED, SOLDER SEAL)TOP VIEW SIDE VIEWPIN FUNCTIONIN1 28V2 INHIBIT3 TRIMCOM4 OUTOUT5 +V6 CASE7 CASE8 CASE9 SYNCCOM10 INBOTTOM VIEWFigure 15 – Non-Flanged, Solder Seal Tin Plated Package and Pinout (Not Used for /HB or Higher Screened Products)(Dimensional Limits are ±0.005” Unless Otherwise Stated)DVHV2800S Series PACKAGE SPECIFICATIONS (NON-FLANGED, SEAM SEAL)TOP VIEW SIDE VIEWPIN FUNCTIONIN1 28V2 INHIBIT3 TRIMCOM4 OUTOUT5 +V6 CASE7 CASE8 CASE9 SYNCCOM10 INBOTTOM VIEWFigure 16 – Non-Flanged, Seam Seal Package and Pinout(Dimensional Limits are ±0.005” Unless Otherwise Stated)DVHV2800S Series PACKAGE SPECIFICATIONS (FLANGED, SOLDER SEAL)TOP VIEW SIDE VIEWPIN FUNCTIONIN1 28V2 INHIBIT3 TRIMCOM4 OUTOUT5 +V6 CASE7 CASE8 CASE9 SYNCCOM10 INBOTTOM VIEWFigure 17 – Flanged, Solder Seal Tin Plated Package and Pinout (Not Used for /HB or Higher Screened Products)(Dimensional Limits are ±0.005” Unless Otherwise Stated)DVHV2800S Series PACKAGE SPECIFICATIONS (FLANGED, SEAM SEAL)TOP VIEW SIDE VIEWPIN FUNCTIONIN1 28V2 INHIBIT3 TRIMCOM4 OUTOUT5 +V6 CASE7 CASE8 CASE9 SYNCCOM10 INBOTTOM VIEWFigure 18 – Flanged, Seam Seal Package and Pinout(Dimensional Limits are ±0.005” Unless Otherwise Stated)DVHV2800S Series PACKAGE PIN DESCRIPTIONPin Function Description1 28V IN Positive Input Voltage Connection2 INHIBIT Logic Low = Disabled Output. Connecting the inhibit pin to input common causes converter shutdown.Logic High = Enabled Output. Unconnected or open collector TTL.3 TRIM Trim Output Voltage to +10%, -20% of Nominal Value4 OUTCOM Output Common Connection5 +V OUT Positive Output Voltage Connection6 CASE CaseConnection7 CASE CaseConnection8 CASE CaseConnection9 SYNC SynchronizationSignal10 IN COM Input Common ConnectionDVHV2800S SeriesENVIRONMENTAL SCREENING (Per MIL-STD-883 as referenced to MIL-PRF-38534, Class H)Notes: 1. 100% R&R testing at –55°C, +25°C, and +125°C with all test data included in product shipment. 2. PIND test Certificate of Compliance included in product shipment.3. Radiographic test Certificate of Compliance and film(s) included in product shipment.Screening MIL-STD-883Standard(No Suffix)Extended /ES HB /HBClass H/HClass K /KNon-Destructive Bond Pull Method 2023 • • • • • Internal Visual Method 2017, 2032 Internal Procedure• • • • • Temperature Cycling Method 1010, Condition C Method 1010, -55°C to 125°C • • • • Constant Acceleration Method 2001, 3000g, Y1 Direction Method 2001, 500g, Y1 Direction • • • • PIND Method 2020, Condition A 2•Pre Burn-In Electrical100% at 25°C • Burn-InMethod 1015, 320 hours at +125°C Method 1015, 160 hours at +125°C 96 hours at +125°C 24 hours at +125°C • • • • • Final ElectricalMIL-PRF-38534, Group A 1 100% at 25°C• • • • • HermeticityMethod 1014, Fine Leak, Condition A Method 1014, Gross Leak, Condition CDip (1 x 10-3)• • • • • • • • • Radiography Method 20123 • External VisualMethod 2009•••••DVHV2800S Series ORDERING INFORMATIONDVHV 28 05 S F R /HB - XXX1 2 3 4 5 6 7 8(1) (2) (3) (4)Product Series Nominal InputVoltageOutput Voltage Number of OutputsDVHV 28 28 Volts 3R3055R21215 3.3 Volts5 Volts5.2 Volts12 Volts15 VoltsS Single(5) (6) (7) (8)Package Option Rad-Hard Option2 Screening Code1,3 Additional ScreeningCodeNone F Non-FlangedFlangedNoneRStandard100 kRadNone/ES/HB/H/KStandardExtendedHBClass HClass KContact SalesNotes: 1. Contact the VPT Inc. Sales Department for availability of Class H (/H) or Class K (/K) qualified products.2. VPT Inc. is not currently qualified to a DSCC certified radiation hardness assurance program.3. VPT Inc. reserves the right to ship higher screened or SMD products to meet lower screened orders at oursole discretion unless specifically forbidden by customer contract.Please contact your sales representative or the VPT Inc. Sales Department for more information concerning additional environmental screening and testing, different input voltage, output voltage, power requirement, source inspection, and/or special element evaluation for space or other higher quality applications.DVHV2800S Series SMD (STANDARD MICROCIRCUIT DRAWING) NUMBERSStandard Microcircuit Drawing (SMD)DVHV2800S Series Similar Part Number*T.B.D.DVHV283R3S/H DVHV283R3SF/H*T.B.D.DVHV2805S/H DVHV2805SF/H*T.B.D.DVHV285R2S/H DVHV285R2SF/H*T.B.D.DVHV2812S/H DVHV2812SF/H*T.B.D.DVHV2815S/H DVHV2815SF/HDo not use the DVHV2800S Series similar part number for SMD product acquisition. It is listed forreference only. For exact specifications for the SMD product, refer to the SMD drawing. SMD’s can be downloaded from the DSCC website at /programs/smcr/. The SMD numberlisted above is for MIL-PRF-38534 Class H screening, standard gold plated lead finish, and no RHA(Radiation Hardness Assurance) level. Please reference the SMD for other screening levels, leadfinishes, and radiation levels.CONTACT INFORMATIONTo request a quotation or place orders please contact your sales representative or the VPT Inc. Sales Department at:Phone: (425)353-3010Fax: (425) 353-4030E-mail: vptsales@All information contained in this datasheet is believed to be accurate, however, no responsibility is assumed for possible errors or omissions. The products or specifications contained herein are subject to change without notice.。

DRV104中文资料

DRV104

"

NOTE: (1) For the most current specifications and package information, refer to our web site at .

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

Copyright © 2003, Texas Instruments Incorporated

ADC081S021中文资料

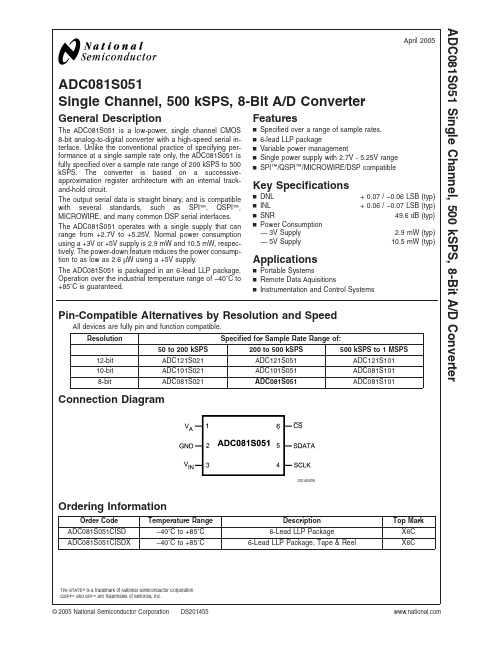

ADC081S051Single Channel,500kSPS,8-Bit A/D ConverterGeneral DescriptionThe ADC081S051is a low-power,single channel CMOS 8-bit analog-to-digital converter with a high-speed serial in-terface.Unlike the conventional practice of specifying per-formance at a single sample rate only,the ADC081S051is fully specified over a sample rate range of 200kSPS to 500kSPS.The converter is based on a successive-approximation register architecture with an internal track-and-hold circuit.The output serial data is straight binary,and is compatible with several standards,such as SPI ™,QSPI ™,MICROWIRE,and many common DSP serial interfaces.The ADC081S051operates with a single supply that can range from +2.7V to +5.25V.Normal power consumption using a +3V or +5V supply is 2.9mW and 10.5mW,respec-tively.The power-down feature reduces the power consump-tion to as low as 2.6µW using a +5V supply.The ADC081S051is packaged in an 6-lead LLP package.Operation over the industrial temperature range of −40˚C to +85˚C is guaranteed.Featuresn Specified over a range of sample rates.n 6-lead LLP packagen Variable power managementn Single power supply with 2.7V -5.25V range nSPI ™/QSPI ™/MICROWIRE/DSP compatibleKey Specificationsn DNL +0.07/−0.06LSB (typ)n INL +0.06/−0.07LSB (typ)n SNR49.6dB (typ)nPower Consumption —3V Supply 2.9mW (typ)—5V Supply10.5mW (typ)Applicationsn Portable Systemsn Remote Data Aquisitionsn Instrumentation and Control SystemsPin-Compatible Alternatives by Resolution and SpeedAll devices are fully pin and function compatible.ResolutionSpecified for Sample Rate Range of:50to 200kSPS200to 500kSPS 500kSPS to 1MSPS12-bit ADC121S021ADC121S051ADC121S10110-bit ADC101S021ADC101S051ADC081S1018-bitADC081S021ADC081S051ADC081S101Connection Diagram20145505Ordering InformationOrder Code Temperature Range Description Top Mark ADC081S051CISD −40˚C to +85˚C 6-Lead LLP PackageX6C ADC081S051CISDX−40˚C to +85˚C6-Lead LLP Package,Tape &ReelX6CTRI-STATE ®is a trademark of National Semiconductor Corporation QSPI ™and SPI ™are trademarks of Motorola,Inc.April 2005ADC081S051Single Channel,500kSPS,8-Bit A/D Converter©2005National Semiconductor Corporation Block Diagram20145507Pin Descriptions and Equivalent CircuitsPin No.SymbolDescriptionANALOG I/O3V INAnalog inputs.This signal can range from 0V to V A .DIGITAL I/O4SCLK Digital clock input.This clock directly controls the conversion and readout processes.5SDATA Digital data output.The output samples are clocked out of this pin on falling edges of the SCLK pin.6CSChip select.On the falling edge of CS,a conversion process begins.POWER SUPPLY1V A Positive supply pin.This pin should be connected to a quiet +2.7V to +5.25V source and bypassed to GND with a 1µF capacitor and a 0.1µF monolithic capacitor located within 1cm of the power pin.2GNDThe ground return for the supply and signals.A D C 081S 051 2Absolute Maximum Ratings(Notes1,2) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Analog Supply Voltage V A−0.3V to6.5V Voltage on Any Pin to GND−0.3V to V A+0.3V Input Current at Any Pin(Note3)±10mA Package Input Current(Note3)±20mA Power Consumption at T A=25˚C See(Note4) ESD Susceptibility(Note5)Human Body Model Machine Model 3500V 300VJunction Temperature+150˚C Storage Temperature−65˚C to+150˚C Operating Ratings(Notes1,2)Operating Temperature Range−40˚C≤T A≤+85˚C V A Supply Voltage+2.7V to+5.25V Digital Input Pins Voltage Range−0.3V to V A Clock Frequency4MHz to10MHz Sample Rate up to500kSPS Analog Input Voltage0V to V APackage Thermal ResistancePackageθJA6-lead LLP78˚C/WSoldering process must comply with National Semiconduc-tor’s Reflow Temperature Profile specifications.Refer to /packaging.(Note6)ADC081S051Converter Electrical Characteristics(Note9)The following specifications apply for V A=+2.7V to5.25V,GND=0V,f SCLK=4MHz to10MHz,f SAMPLE=200kSPS to500kSPS,unless otherwise noted.Boldface limits apply for T A=T MIN to T MAX:all other limits T A= 25˚C.Symbol Parameter Conditions TypicalLimits(Note9)UnitsSTATIC CONVERTER CHARACTERISTICSResolution with No Missing Codes8BitsINL Integral Non-Linearity +0.06+0.3LSB(max)−0.07−0.3LSB(min)DNL Differential Non-Linearity +0.07+0.2LSB(max)−0.06−0.2LSB(min)V OFF Offset Error+0.03±0.2LSB(max) GE Gain Error±0.08±0.4LSB(max)TUE Total Unadjusted Error+0.8+0.2LSB(max)−0.07−0.3LSB(min)DYNAMIC CONVERTER CHARACTERISTICSSINAD Signal-to-Noise Plus Distortion Ratio V A=+2.7to5.25Vf IN=100kHz,−0.02dBFS49.649dB(min)SNR Signal-to-Noise Ratio V A=+2.7to5.25Vf IN=100kHz,−0.02dBFS49.649dB(min)THD Total Harmonic Distortion V A=+2.7to5.25Vf IN=100kHz,−0.02dBFS−70−65dB(max)SFDR Spurious-Free Dynamic Range V A=+2.7to5.25Vf IN=100kHz,−0.02dBFS6765dB(min)ENOB Effective Number of Bits V A=+2.7to5.25Vf IN=100kHz,−0.02dBFS7.97.8Bits(min)IMD Intermodulation Distortion,SecondOrder TermsV A=+5.25Vf a=103.5kHz,f b=113.5kHz−68dB Intermodulation Distortion,ThirdOrder TermsV A=+5.25Vf a=103.5kHz,f b=113.5kHz−68dBFPBW-3dB Full Power Bandwidth V A=+5V11MHzV A=+3V8MHzADC081S051 3ADC081S051Converter Electrical Characteristics(Note 9)(Continued)The following specifications apply for V A =+2.7V to 5.25V,GND =0V,f SCLK =4MHz to 10MHz,f SAMPLE =200kSPS to 500kSPS,unless otherwise noted.Boldface limits apply for T A =T MIN to T MAX :all other limits T A =25˚C.SymbolParameterConditionsTypicalLimits (Note 9)UnitsANALOG INPUT CHARACTERISTICS V IN Input Range 0to V AVI DCL DC Leakage Current ±1µA (max)C INAInput CapacitanceTrack Mode 30pF Hold Mode 4pF DIGITAL INPUT CHARACTERISTICS V IH Input High Voltage V A =+5.25V 2.4V (min)V IL Input Low Voltage V A =+5.25V 0.8V (max)V A =+3.6V 0.4V (max)I IN Input CurrentV IN =0V or V A±0.1±1µA (max)C INDDigital Input Capacitance24pF (max)DIGITAL OUTPUT CHARACTERISTICS V OH Output High Voltage I SOURCE =200µA V A −0.03V A −0.2V (min)I SOURCE =1mA V A −0.1V V OL Output Low VoltageI SINK =200µA 0.030.4V (max)I SINK =1mA0.1VI OZH ,I OZL TRI-STATE ®Leakage Current ±0.1±10µA (max)C OUTTRI-STATE ®Output Capacitance 24pF (max)Output CodingStraight (Natural)BinaryPOWER SUPPLY CHARACTERISTICS (C L =10pF)V ASupply Voltage2.7V (min)5.25V (max)I ASupply Current,Normal Mode (Operational,CS low)V A =+5.25V,f SAMPLE =200kSPS 2.0 2.4mA (max)V A =+3.6V,f SAMPLE =200kSPS 0.8 1.0mA (max)Supply Current,Shutdown (CS high)f SCLK =0MHz,V A =+5.25V f SAMPLE =0kSPS0.5µA V A =+5.25V,f SCLK =10MHz,f SAMPLE =0kSPS 22µA P DPower Consumption,Normal Mode (Operational,CS low)V A =+5.25V 10.512.6mW (max)V A =+3.6V2.93.6mW (max)Power Consumption,Shutdown (CS high)f SCLK =0MHz,V A =+5.25V f SAMPLE =0kSPS2.6µW V A =+5.25V,f SCLK =10MHz,f SAMPLE =0kSPS0.12mWAC ELECTRICAL CHARACTERISTICS f SCLK Clock Frequency (Note 8)4MHz (min)10MHz (max)f S Sample Rate (Note 8)50200kSPS (min)500kSPS (max)t CONV Conversion Time 16SCLK cycles DC SCLK Duty Cyclef SCLK =10MHz5040%(min)60%(max)t ACQTrack/Hold Acquisition Time 400ns (max)Throughput TimeAcquisition Time +Conversion Time20SCLK cyclesA D C 081S 0514ADC081S051Converter Electrical Characteristics(Note9)(Continued)The following specifications apply for V A=+2.7V to5.25V,GND=0V,f SCLK=4MHz to10MHz,f SAMPLE=200kSPS to500kSPS,unless otherwise noted.Boldface limits apply for T A=T MIN to T MAX:all other limits T A= 25˚C.Symbol Parameter Conditions TypicalLimits(Note9)UnitsAC ELECTRICAL CHARACTERISTICSt QUIET(Note10)50ns(min) t AD Aperture Delay3nst AJ Aperture Jitter30ps ADC081S051Timing SpecificationsThe following specifications apply for V A=+2.7V to5.25V,GND=0V,f SCLK=4MHz to10MHz,f SAMPLE=200kSPS to500kSPS,Boldface limits apply for T A=T MIN to T MAX:all other limits T A=25˚C.Symbol Parameter Conditions Typical Limits Units t CS Minimum CS Pulse Width10ns(min) t SU CS to SCLK Setup Time10ns(min)t EN Delay from CS Until SDATA TRI-STATE®Disabled(Note11)20ns(max)t ACC Data Access Time after SCLK Falling Edge(Note12)V A=+2.7to+3.640ns(max)V A=+4.75to+5.2520ns(max)t CL SCLK Low Pulse Width 0.4xt SCLKns(min)t CH SCLK High Pulse Width 0.4xt SCLKns(min)t H SCLK to Data Valid Hold Time V A=+2.7to+3.67ns(min) V A=+4.75to+5.255ns(min)t DIS SCLK Falling Edge to SDATA HighImpedance(Note13)V A=+2.7to+3.625ns(max)6ns(min)V A=+4.75to+5.2525ns(max)5ns(min)t POWER-UP Power-Up Time from Full Power-Down1µsNote1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.For guaranteed specifications and test conditions,see the Electrical Characteristics.The guaranteed specifications apply only for the test conditions listed.Some performance characteristics may degrade when the device is not operated under the listed test conditions.Note2:All voltages are measured with respect to GND=0V,unless otherwise specified.Note3:When the input voltage at any pin exceeds the power supply(that is,V IN<GND or V IN>V A),the current at that pin should be limited to10mA.The20mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of10mA to two.The Absolute Maximum Rating specification does not apply to the V A pin.The current into the V A pin is limited by the Analog Supply Voltage specification.Note4:The absolute maximum junction temperature(T J max)for this device is150˚C.The maximum allowable power dissipation is dictated by T J max,thejunction-to-ambient thermal resistance(θJA),and the ambient temperature(T A),and can be calculated using the formula P D MAX=(T J max−T A)/θJA.The valuesfor maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition(e.g.when input or output pins are drivenbeyond the power supply voltages,or the power supply polarity is reversed).Obviously,such conditions should always be avoided.Note5:Human body model is100pF capacitor discharged through a1.5kΩresistor.Machine model is220pF discharged through zero ohmsNote6:Reflow temperature profiles are different for lead-free and non-lead-free packages.Note7:Tested limits are guaranteed to National’s AOQL(Average Outgoing Quality Level).Note8:This is the frequency range over which the electrical performance is guaranteed.The device is functional over a wider range which is specified under Operating Ratings.Note9:Data sheet min/max specification limits are guaranteed by design,test,or statistical analysis.Note10:Minimum Quiet Time required by Bus relinquish and start of the next conversion.Note11:Measured with the timing test circuit shown in Figure1and defined as the time taken by the output signal to cross1.0V.Note12:Measured with the timing test circuit shown in Figure1and defined as the time taken by the output signal to cross1.0V or2.0V.Note13:t DIS is derived from the time taken by the output to change by0.5V with the timing test circuit shown in Figure1.The measured number is then adjustedto remove the effects of charging or discharging the25pF capacitor.This means that t DIS is the true bus relinquish time,independent of the bus loading.ADC081S0515Timing Diagrams20145508FIGURE 1.Timing Test Circuit20145506FIGURE 2.ADC081S051Serial Timing DiagramA D C 081S 051 6Specification DefinitionsACQUISITION TIME is the time required to acquire the input voltage.That is,it is time required for the hold capacitor to charge up to the input voltage.APERTURE DELAY is the time between the fourth falling SCLK edge of a conversion and the time when the input signal is acquired or held for conversion.APERTURE JITTER (APERTURE UNCERTAINTY)is the variation in aperture delay from sample to sample.Aperture jitter manifests itself as noise in the output.CONVERSION TIME is the time required,after the input voltage is acquired,for the ADC to convert the input voltage to a digital word.DIFFERENTIAL NON-LINEARITY (DNL)is the measure of the maximum deviation from the ideal step size of 1LSB.DUTY CYCLE is the ratio of the time that a repetitive digital waveform is high to the total time of one period.The speci-fication here refers to the SCLK.EFFECTIVE NUMBER OF BITS (ENOB,or EFFECTIVE BITS)is another method of specifying Signal-to-Noise and Distortion or SINAD.ENOB is defined as (SINAD −1.76)/6.02and says that the converter is equiva-lent to a perfect ADC of this (ENOB)number of bits.FULL POWER BANDWIDTH is a measure of the frequency at which the reconstructed output fundamental drops 3dB below its low frequency value for a full scale input.GAIN ERROR is the deviation of the last code transition (111...110)to (111...111)from the ideal (V REF −1.5LSB),after adjusting for offset error.INTEGRAL NON-LINEARITY (INL)is a measure of the deviation of each individual code from a line drawn from negative full scale (1⁄2LSB below the first code transition)through positive full scale (1⁄2LSB above the last code transition).The deviation of any given code from this straight line is measured from the center of that code value.INTERMODULATION DISTORTION (IMD)is the creation of additional spectral components as a result of two sinusoidal frequencies being applied to the ADC input at the same time.It is defined as the ratio of the power in the second and third order intermodulation products to the sum of the power in both of the original frequencies.IMD is usually expressed in dB.MISSING CODES are those output codes that will never appear at the ADC outputs.The ADC081S051is guaranteed not to have any missing codes.OFFSET ERROR is the deviation of the first code transition (000...000)to (000...001)from the ideal (i.e.GND +0.5LSB).SIGNAL TO NOISE RATIO (SNR)is the ratio,expressed in dB,of the rms value of the input signal to the rms value of the sum of all other spectral components below one-half the sampling frequency,not including harmonics or d.c.SIGNAL TO NOISE PLUS DISTORTION (S/N+D or SINAD)Is the ratio,expressed in dB,of the rms value of the input signal to the rms value of all of the other spectral compo-nents below half the clock frequency,including harmonics but excluding d.c.SPURIOUS FREE DYNAMIC RANGE (SFDR)is the differ-ence,expressed in dB,between the rms values of the input signal and the peak spurious signal where a spurious signal is any signal present in the output spectrum that is not present at the input,excluding d.c.TOTAL HARMONIC DISTORTION (THD)is the ratio,ex-pressed in dB or dBc,of the rms total of the first five harmonic components at the output to the rms level of the input signal frequency as seen at the output.THD is calcu-lated aswhere Af 1is the RMS power of the input frequency at the output and Af 2through Af 6are the RMS power in the first 5harmonic frequencies.THROUGHPUT TIME is the minimum time required between the start of two successive conversion.It is the acquisition time plus the conversion time.TOTAL UNADJUSTED ERROR is the worst deviation found from the ideal transfer function.As such,it is a comprehen-sive specification which includes full scale error,linearity error,and offset error.ADC081S0517Typical Performance CharacteristicsT A =+25˚C,f SAMPLE =200kSPS to 500kSPS,f SCLK =4MHz to 10MHz,f IN=100kHz unless otherwise stated.DNL vs Clock FrequencyINL vs Clock Frequency2014556520145566Total Adjusted Error vs Clock Frequency SNR vs Clock Frequency2014556720145563SINAD vs.Clock FrequencyPower Consumption vs.Throughput,f SCLK =10MHz2014556420145555A D C 081S 051 8Applications Information1.0ADC081S051OPERATIONThe ADC081S051are successive-approximation analog-to-digital converters designed around a charge-redistribution digital-to-analog converter.Simplified schematics of the ADC081S051in both track and hold operation are shown in Figures 3and 4,respectively.In Figure 3,the device is in track mode:switch SW1connects the sampling capacitor to the input,and SW2balances the comparator inputs.The device is in this state until CS is brought low,at which point the device moves to hold mode.Figure 4shows the device in hold mode:switch SW1con-nects the sampling capacitor to ground,maintaining the sampled voltage,and switch SW2unbalances the compara-tor.The control logic then instructs the charge-redistribution DAC to add or subtract fixed amounts of charge from the sampling capacitor until the comparator is balanced.When the comparator is balanced,the digital word supplied to the DAC is the digital representation of the analog input voltage.The device moves from hold mode to track mode on the 13th rising edge of SCLK.2.0USING THE ADC081S051The serial interface timing diagram for the ADC081S051is shown in Figure 2.CS is chip select,which initiates conver-sions on the ADC081S051and frames the serial data trans-fers.SCLK (serial clock)controls both the conversion pro-cess and the timing of serial data.SDATA is the serial data out pin,where a conversion result is found as a serial data stream.Basic operation of the ADC081S051begins with CS going low,which initiates a conversion process and data transfer.Subsequent rising and falling edges of SCLK will be labelled with reference to the falling edge of CS;for example,"the third falling edge of SCLK"shall refer to the third falling edge of SCLK after CS goes low.At the fall of CS,the SDATA pin comes out of TRI-STATE,and the converter moves from track mode to hold mode.The input signal is sampled and held for conversion on the falling edge of CS.The converter moves from hold mode to trackmode on the 13th rising edge of SCLK (see Figure 2).The SDATA pin will be placed back into TRI-STATE after the 16th falling edge of SCLK,or at the rising edge of CS,whichever occurs first.After a conversion is completed,the quiet time t QUIET must be satisfied before bringing CS low again to begin another conversion.Sixteen SCLK cycles are required to read a complete sample from the ADC081S051.The sample bits (including any leading or trailing zeroes)are clocked out on falling edges of SCLK,and are intended to be clocked in by a receiver on subsequent falling edges of SCLK.The ADC081S051will produce three leading zero bits on SDATA,followed by eight data bits,most significant first.After the data bits,the ADC081S051will clock out four trailing zeros.If CS goes low before the rising edge of SCLK,an additional (fourth)zero bit may be captured by the next falling edge of SCLK.20145509FIGURE 3.ADC081S051in Track Mode20145510FIGURE 4.ADC081S051in Hold ModeADC081S0519Applications Information(Continued)3.0ADC081S051TRANSFER FUNCTIONThe output format of the ADC081S051is straight binary.Code transitions occur midway between successive integer LSB values.The LSB width for the ADC081S051is V A /256.The ideal transfer characteristic is shown in Figure 5.The transition from an output code of 00000000to a code of 00000001is at 1/2LSB,or a voltage of V A /512.Other code transitions occur at steps of one LSB.4.0TYPICAL APPLICATION CIRCUITA typical application of the ADC081S051is shown in Figure 6.Power is provided in this example by the National Semi-conductor LP2950low-dropout voltage regulator,available in a variety of fixed and adjustable output voltages.The power supply pin is bypassed with a capacitor network located close to the ADC081S051.Because the reference for the ADC081S051is the supply voltage,any noise on the supplywill degrade device noise performance.To keep noise off the supply,use a dedicated linear regulator for this device,or provide sufficient decoupling from other circuitry to keep noise off the ADC081S051supply pin.Because of the ADC081S051’s low power requirements,it is also possible to use a precision reference as a power supply to maximize performance.The four-wire interface is also shown con-nected to a microprocessor or DSP .20145511FIGURE 5.Ideal Transfer Characteristic20145513FIGURE 6.Typical Application CircuitA D C 081S 051 10Applications Information(Continued)5.0ANALOG INPUTSAn equivalent circuit for one of the ADC081S051’s input channels is shown in Figure 7.Diodes D1and D2provide ESD protection for the analog inputs.At no time should any input go beyond (V A +300mV)or (GND −300mV),as these ESD diodes will begin conducting,which could result in erratic operation.The capacitor C1in Figure 7has a typical value of 4pF,and is mainly the package pin capacitance.Resistor R1is the on resistance of the multiplexer and track /hold switch,and is typically 500ohms.Capacitor C2is the ADC081S051sam-pling capacitor and is typically 26pF.The ADC081S051will deliver best performance when driven by a low-impedance source to eliminate distortion caused by the charging of the sampling capacitance.This is especially important when using the ADC081S051to sample AC signals.Also important when sampling dynamic signals is a band-pass or low-pass filter to reduce harmonics and noise,improving dynamic performance.6.0DIGITAL INPUTS AND OUTPUTSThe ADC081S051digital inputs (SCLK and CS)are not limited by the same absolute maximum ratings as the analog inputs.The digital input pins are instead limited to +6.5V with respect to GND,regardless of V A ,the supply voltage.This allows the ADC081S051to be interfaced with a wide range of logic levels,independent of the supply voltage.7.0MODES OF OPERATIONThe ADC081S051has two possible modes of operation:normal mode,and shutdown mode.The ADC081S051en-ters normal mode (and a conversion process is begun)whenCS is pulled low.The device will enter shutdown mode if CS is pulled high before the tenth falling edge of SCLK after CS is pulled low,or will stay in normal mode if CS remains low.Once in shutdown mode,the device will stay there until CS is brought low again.By varying the ratio of time spent in the normal and shutdown modes,a system may trade-off throughput for power consumption.7.1Normal ModeThe fastest possible throughput is obtained by leaving the ADC081S051in normal mode at all times,so there are no power-up delays.To keep the device in normal mode con-tinuously,CS must be kept low until after the 10th falling edge of SCLK after the start of a conversion (remember that a conversion is initiated by bringing CS low).If CS is brought high after the 10th falling edge,but before the 16th falling edge,the device will remain in normal mode,but the current conversion will be aborted,and SDATA will return to TRI-STATE (truncating the output word).Sixteen SCLK cycles are required to read all of a conversion word from the device.After sixteen SCLK cycles have elapsed,CS may be idled either high or low until the next conversion.If CS is idled low,it must be brought high again before the start of the next conversion,which begins when CS is again brought low.After sixteen SCLK cycles,SDATA returns to TRI-STATE.Another conversion may be started,after t QUIET has elapsed,by bringing CS low again.7.2Shutdown ModeShutdown mode is appropriate for applications that either do not sample continuously,or it is acceptable to trade through-put for power consumption.When the ADC081S051is in shutdown mode,all of the analog circuitry is turned off.To enter shutdown mode,a conversion must be interrupted by bringing CS back high anytime between the second and tenth falling edges of SCLK,as shown in Figure 8.Once CS has been brought high in this manner,the device will enter shutdown mode;the current conversion will be aborted and SDATA will enter TRI-STATE.If CS is brought high before the second falling edge of SCLK,the device will not change mode;this is to avoid accidentally changing mode as a result of noise on the CS line.20145514FIGURE 7.Equivalent Input Circuit20145516FIGURE 8.Entering Shutdown ModeADC081S05111Applications Information(Continued)To exit shutdown mode,bring CS back low.Upon bringing CS low,the ADC081S051will begin powering up (power-up time is specified in the Timing Specifications table).This microsecond of power-up delay results in the first conversion result being unusable.The second conversion performed after power-up,however,is valid,as shown in Figure 9.If CS is brought back high before the 10th falling edge of SCLK,the device will return to shutdown mode.This is done to avoid accidentally entering normal mode as a result of noise on the CS line.To exit shutdown mode and remain in normal mode,CS must be kept low until after the 10th falling edge of SCLK.The ADC081S051will be fully powered-up after 16SCLK cycles.8.0POWER MANAGEMENTThe ADC081S051takes time to power-up,either after first applying V A ,or after returning to normal mode from shut-down mode.This corresponds to one "dummy"conversion for any SCLK frequency within the specifications in this document.After this first dummy conversion,the ADC081S051will perform conversions properly.Note that the t QUIET time must still be included between the first dummy conversion and the second valid conversion.When the V A supply is first applied,the ADC081S051may power up in either of the two modes:normal or shutdown.As such,one dummy conversion should be performed after start-up,exactly as described in the previous paragraph.The part may then be placed into either normal mode or the shutdown mode,as described in Sections 7.1and 7.2.When the ADC081S051is operated continuously in normal mode,the maximum throughput is f SCLK /20.Throughput may be traded for power consumption by running f SCLK at its maximum 10.0MHz and performing fewer conversions per unit time,putting the ADC081S051into shutdown modebetween conversions.A plot of typical power consumption versus throughput is shown in the Typical Performance Curves section.To calculate the power consumption for a given throughput,multiply the fraction of time spent in the normal mode by the normal mode power consumption and add the fraction of time spent in shutdown mode multiplied by the shutdown mode power consumption.Generally,the user will put the part into normal mode and then put the part back into shutdown mode.Note that the curve of power consumption vs.throughput is nearly linear.This is because the power consumption in the shutdown mode is so small that it can be ignored for all practical purposes.9.0POWER SUPPLY NOISE CONSIDERATIONSThe charging of any output load capacitance requires cur-rent from the power supply,V A .The current pulses required from the supply to charge the output capacitance will cause voltage variations on the supply.If these variations are large enough,they could degrade SNR and SINAD performance of the ADC.Furthermore,discharging the output capaci-tance when the digital output goes from a logic high to a logic low will dump current into the die substrate,which is resis-tive.Load discharge currents will cause "ground bounce"noise in the substrate that will degrade noise performance if that current is large enough.The larger the output capaci-tance,the more current flows through the die substrate and the greater is the noise coupled into the analog channel,degrading noise performance.To keep noise out of the power supply,keep the output load capacitance as small as practical.If the load capacitance is greater than 25pF,use a 100Ωseries resistor at the ADC output,located as close to the ADC output pin as practical.This will limit the charge and discharge current of the output capacitance and improve noise performance.20145517FIGURE 9.Entering Normal ModeA D C 081S 051 12。

3590S-2-502L;3590S-2-102L;3590S-2-103L;3590S-2-203L;3590S-1-502L;中文规格书,Datasheet资料

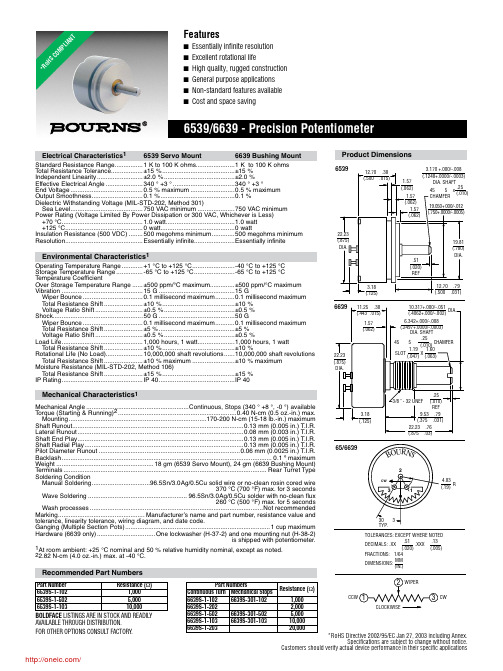

Specifi cations are subject to change without notice.Customers should verify actual device performance in their specifi c applications.*RoHS Directive 2002/95/EC Jan. 27, 2003 including annex and RoHS Recast 2011/65/EU June 8, 2011.Stop Strength..............................................................................................................................................................................45 N-cm (64 oz.-in.) minimum Mechanical Angle ...........................................................................................................................................................................................3600 ° +10 °, -0 °Torque (Starting & Running) ................................................................................................................................0.35 N-cm (0.5 oz.-in.) maximum (unsealed) 1.1 N-cm (1.5 oz.-in.) maximum (sealed) Mounting ..............................................................................................................................................................................55-80 N-cm (5-7 lb.-in.) (plastic) 90-113 N-cm (8-10 in.-lb.) (metal)Shaft Runout......................................................................................................................................................................................0.13 mm (0.005 in.) teral Runout ...................................................................................................................................................................................0.20 mm (0.008 in.) T.I.R.Shaft End Play ...................................................................................................................................................................................0.25 mm (0.010 in.) T.I.R.Shaft Radial Play ...............................................................................................................................................................................0.13 mm (0.005 in.) T.I.R.Pilot Diameter Runout .......................................................................................................................................................................0.08 mm (0.003 in.) T.I.R.Backlash ............................................................................................................................................................................................................1.0 ° maximum Weight ........................................................................................................................................................................................................Approximately 19 G Terminals ................................................................................................................................................................................................Solder lugs or PC pins Soldering ConditionManual Soldering...........................................................96.5Sn/3.0Ag/0.5Cu solid wire or no-clean rosin cored wire; 370 °C (700 °F) max. for 3 seconds Wave Soldering ...................................................................................96.5Sn/3.0Ag/0.5Cu solder with no-clean fl ux; 260 °C (500 °F) max. for 5 seconds Wash processes .......................................................................................................................................................................................Not recommended Marking .....................................Manufacturer’s name and part number, resistance value and tolerance, linearity tolerance, wiring diagram, and date code.Ganging (Multiple Section Potentiometers) ......................................................................................................................................................1 cup maximum Hardware ............................................................................................................One lockwasher and one mounting nut is shipped with each potentiometer.NOTE: For Anti-rotation pin add 91 after confi guration dash number. Example: -2 becomes -291 to add AR pin.1At room ambient: +25 °C nominal and 50 % relative humidity nominal, except as noted. 2Consult manufacturer for complete specifi cation details for resistances below 1k ohms.BOLDFACE LISTINGS ARE IN STOCK AND READILY AVAILABLETHROUGH DISTRIBUTION. FOR OTHER OPTIONS CONSULT FACTORY.ROHS IDENTIFIER: L = COMPLIANTRecommended Part Numbers(Printed Circuit)(Solder Lug)(Solder Lug)Resistance (Ω)Resolution (%)3590P-2-102L 3590S-2-102L 3590S-1-102L 1,000.0293590P-2-202L 3590S-2-202L 3590S-1-202L 2,000.0233590P-2-502L 3590S-2-502L 3590S-1-502L 5,000.0253590P-2-103L 3590S-2-103L 3590S-1-103L 10,000.0203590P-2-203L 3590S-2-203L 3590S-1-203L 20,000.0193590P-2-503L 3590S-2-503L 3590S-1-503L 50,000.0133590P-2-104L3590S-2-104L3590S-1-104L100,000.009*Ro H S C O MP L I A N T/Panel Thickness Dimensions(For Bushing Mount Only)1.60 +.08/-.03(.063 +.003/-.001)DIA.ANTI-ROTATION PINAnti-rotation pin hole is shown at six o'clockposition for reference only. The actual location isdetermined by the customer's application. Referto the front view of the potentiometer to see thelocation of the optional A/R pin.Panel thickness and hole diameters arerecommended for best fit. However, customersmay adjust the dimensions to suit their specificapplication.Product DimensionsSpecifi cations are subject to change without notice.Customers should verify actual device performance in their specifi c applications.REV. 06/12 MOUNTING SURFACE-2, -4, -6, -8 Confi gurations-1, -3, -5, -7 Confi gurationsRecommended PCB LayoutHOLE DIAMETER5.08(.200)5.08(.200)6.99(.275)SchematicTOLERANCES: EXCEPT WHERE NOTED.508 .127DECIMALS: .XX ±(.02),.XXX ±(.005)FRACTIONS: ±1/64MMDIMENSIONS:(IN.)Shaft & Bushing Confi gurations(Bushing - DxL, Shaft - D):(-1) Plastic Bushing (3/8 ” x 5/16 ”)and Shaft (.2480 + .001, - .002)(-2) Metal Bushing (3/8 ” x 5/16 ”)and Shaft (.2497 + .0000, - .0009)(-3) Sealed, Plastic Bushing (3/8 ” x 5/16 ”)and Shaft (.2480 + .001, - .002)(-4) Sealed, Metal Bushing (3/8 ” x 5/16 ”)and Shaft (.2497 + .0000, - .0009)(-5) Metric, Plastic Bushing (9 mm x 7.94 mm)and Shaft (6 mm + 0, - .076 mm)(-6) Metric, Metal Bushing (9 mm x 7.94 mm)and Shaft (6 mm + 0, - .023 mm)(-7) Metric, Sealed, Plastic Bushing (9 mm x7.94 mm) and Shaft (6 mm + 0, - .076 mm)(-8) Metric, Sealed, Metal Bushing (9 mm x7.94 mm) and Shaft (6 mm + 0, - .023 mm)Terminal Styles“P” Terminal Style“S” Terminal Style/分销商库存信息:BOURNS3590S-2-502L3590S-2-102L3590S-2-103L 3590S-2-203L3590S-1-502L3590S-2-104L 3590S-1-203L3590S-2-501L3590S-2-202L 3590S-1-503L3590S-2-503L3590S-1-104L 3590S-291-102L3590S-291-203L3590S-291-502L 3590S-1-201L3590S-1-501L3590S-2-101L 3590S-2-201L3590P-1-102L3590P-1-103L 3590P-1-201L3590P-1-502L3590S-1-102L 3590S-1-103L3590S-2-252L3590P-291-501L 3590P-2-102L3590P-2-201L3590P-2-203L 3590P-2-502L3590S-1-202L3590S-6-102L 3590S-6-201L3590S-6-202L3590S-6-203L 3590S-6-501L3590P-1-104L3590S-6-502L 3590S-4-102L3590S-4-103L3590S-4-202L 3590S-4-203L3590S-4-502L3590S-8-102L 3590S-8-103L3590S-8-202L3590P-2-104L 3590P-4-103L3590P-4-202L3590S-6-503L 3590S-6-104L3590S-4-104L3590P-4-503L 3590P-4-104L3590S-2-5023590S-1-102 3590S-1-1033590S-1-1043590S-1-203 3590S-1-5023590S-1-5033590S-2-102 3590S-2-1033590S-2-1043590S-2-203 3590S-2-5033590S-1-2023590S-2-202 3590S-2-501。

ER104中文资料

ER100 THRU ER106SUPERFAST RECOVERY RECTIFIERSVOLTAGE - 50 to 600 Volts CURRENT - 1.0 AmpereFEATURESl Superfast recovery times-epitaxial construction l Low forward voltage, high current capabilityl Exceeds environmental standards of MIL-S-19500/228l Hermetically sealed l Low leakagel High surge capabilityl Plastic package has Underwriters Laboratories Flammability Classification 94V-O utilizing Flame Retardant Epoxy Molding Compound MECHANICAL DA TACase: Molded plastic, DO-41Terminals: Axial leads, solderable to MIL-STD-202, Method 208Polarity: Color Band denotes cathode end Mounting Position: Any Weight: 0.012 ounce, 0.3 gramMAXIMUM RA TINGS AND ELECTRICAL CHARACTERISTICSRatings at 25¢J ambient temperature unless otherwise specified.Resistive or inductive load, 60Hz.ER100ER101ER101AER102ER103ER104ER106UNITS Maximum Recurrent Peak Reverse Voltage 50100150200300400600V Maximum RMS Voltage3570105140210320420V Maximum DC Blocking Voltage 50100150200300400600V Maximum Average ForwardCurrent .375"(9.5mm) lead length at T A =55¢J1.0APeak Forward Surge Current, I FM (surge):8.3ms single half sine-wave superimposed on rated load(JEDEC method)30.0AMaximum Forward Voltage at 1.0A DC.951.251.7V Maximum DC Reverse Current at Rated DC Blocking Voltage 5.0£g A Maximum DC Reverse Current atRated DC Blocking Voltage T A =125¢J 150£g A Maximum Reverse Recovery Time(Note 1)35.0nsTypical Junction capacitance (Note 2)17P FTypical Junction Resistance(Note 3) R £K JA 50¢J /W Operating and Storage T emperature Range T J-55 to +150¢JNOTES:1. Reverse Recovery T est Conditions: I F =.5A, I R =1A, Irr=.25A2. Measured at 1 MHz and applied reverse voltage of 4.0 VDC3. Thermal resistance from junction to ambient and from junction to lead length 0.375”(9.5mm) P .C.B. mountedDO-41RATING AND CHARACTERISTIC CURVES ER100 THRU ER106NOTE:1.Rise Time = 7ns max.Input Impedance = 1 megohm. 22pF 2.Rise Time = 10ns max. Source Impedance = 50 Ohms50 ns/cmFig. 1-REVERSE RECOVERY TIME CHARACTERISTIC ANDTEST CIRCUIT DIAGRAMFig. 2-MAXIMUM NON-REPEITIVESURGE CURRENTAMBIENT TEMPERATURE, ¢JFig. 3-MAXIMUM AVERAGE FORWARD CURRENT RATINGINSTANTANEOUS FORWARD VOLTAGE VOLTSFig. 4-FORWARD CURRENTDERATING CURVE% OF PIV, VOLTSREVERSE VOLTAGE, VOLTSFig. 5-TYPICAL REVERSE CHARACTERISTICSFig. 6-TYPICAL JUNCTIONCAPACITANCE。

TOP104YAI中文资料

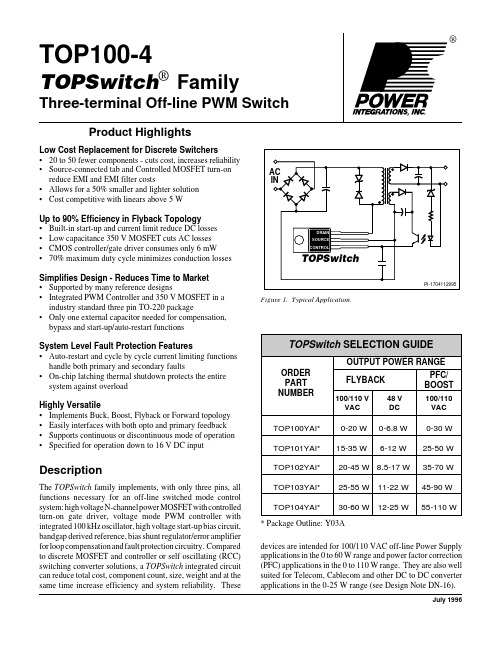

Highly Versatile • Implements Buck, Boost, Flyback or Forward topology • Easily interfaces with both opto and primary feedback • Supports continuous or discontinuous mode of operation • Specified for operation down to 16 V DC input

IFB

THERMAL

SHUTDOWN

INTERNAL SUPPLY

÷8

R

Q

S

Q

OSCILLATOR DMAX

CLOCK SAW

-

+

PWM COMPARATOR

S

Q

R

Q

RE

Figure 2. Functional Block Diagram.

DRAIN

VILIMIT

CONTROLLED TURN-ON GATE DRIVER

Control Voltage Supply CONTROL pin voltage V is the supply

C

or bias voltage for the controller and driver circuitry. An external bypass capacitor closely connected between the CONTROL and SOURCE pins is required to supply the gate drive current. The total amount of capacitance connected to this pin (C ) also sets the

PESD5V0S1BA中文资料

V(CL)R

clamping voltage

V(BR) rdif Cd

breakdown voltage differential resistance diode capacitance

Conditions

VRWM = 5 V; see Figure 6 IPP = 1 A IPP = 12 A IR = 1 mA IR = 1 mA VR = 0 V; f = 1 MHz; see Figure 5

Min

Typ

Max

-

-

5

-

5

100

[1] [2] -

-

10

[1] [2] -

-

14

5.5

-

9.5

-

-

50

-

35

45

[1] Non-repetitive current pulse 8/20 µs exponentially decaying waveform according to IEC61000-4-5; see Figure 1. [2] Measures from pin 1 to pin 2.

PESD5V0S1BA/BB/BL

Low capacitance bidirectional ESD protection diodes

103

Ppp (W)

102

001aaa202

1.2 Ppp Ppp(25˚C)

0.8

0.4

001aaa193

10 1

10

102

103

104

tp (µs)

Tamb = 25 °C

Pin

Description

SOD323, SOD523

C1410中文资料

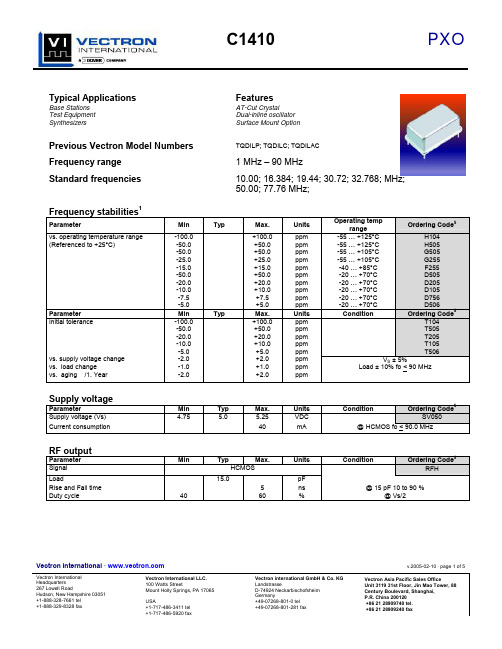

Vectron International · v.2005-02-10 · page 1 of 5Vectron International Headquarters Vectron International LLC. 100 Watts StreetVectron international GmbH & Co. KG LandstrasseVectron Asia Pacific Sales OfficeUnit 3119 31st Floor, Jin Mao Tower, 88Typical ApplicationsFeaturesBase Stations AT-Cut CrystalTest Equipment Dual-inline oscillator Synthesizers Surface Mount OptionPrevious Vectron Model NumbersTQDILP; TQDILC; TQDILACFrequency range1 MHz – 90 MHzStandard frequencies10.00; 16.384; 19.44; 30.72; 32.768; MHz; 50.00; 77.76 MHz;Frequency stabilities 1ParameterMin Typ Max. Units Operating temprange Ordering Code 5vs. operating temperature range (Referenced to +25°C)-100.0 -50.0 -50.0 -25.0 -15.0 -50.0 -20.0 -10.0 -7.5 -5.0+100.0 +50.0 +50.0 +25.0 +15.0 +50.0 +20.0 +10.0 +7.5 +5.0 ppm ppm ppm ppm ppm ppm ppm ppm ppm ppm -55 … +125°C -55 … +125°C -55 … +105°C -55 … +105°C -40 … +85°C -20 … +70°C -20 … +70°C -20 … +70°C -20 … +70°C -20 … +70°C H104 H505 G505 G255 F255 D505 D205 D105 D756 D506Parameter Min Typ Max. Units ConditionOrdering Code 5T104 T505 T205 T105 T506Initial tolerancevs. supply voltage change vs. load change vs. aging /1. Year-100.0 -50.0 -20.0 -10.0 -5.0 -2.0 -1.0 -2.0+100.0 +50.0 +20.0 +10.0 +5.0 +2.0 +1.0 +2.0ppm ppm ppm ppm ppm ppm ppm ppmV S ± 5%Load ± 10% fo < 90 MHzSupply voltageParameterMin Typ Max. Units ConditionOrdering Code 5Supply voltage (Vs)4.755.0 5.25 VDCSV050Current consumption40mA@ HCMOS fo < 90.0 MHzRF outputParameter Min Typ Max.Units ConditionOrdering Code 5SignalHCMOSRFHLoad15.0 pFRise and Fall time 5 ns @ 15 pF 10 to 90 %Duty cycle4060%@ Vs/2Vectron International · v.2005-02-10 · page 2 of 5Vectron International Headquarters Vectron International LLC.100 Watts StreetVectron international GmbH & Co. KGLandstrasseVectron Asia Pacific Sales OfficeUnit 3119 31st Floor, Jin Mao Tower, 88Additional parametersParameter Min Typ Max. Units ConditionPhase Noise -80 dBc/Hz 10 Hz @10.000-110 dBc/Hz 100 Hz MHz-135 dBc/Hz 1 kHz HCMOS-145 dBc/Hz 10 kHz 5.0 V-150 dBc/Hz 100 kHzWeight 6 gProcessing & Packing handling&processing noteVectron International · v.2005-02-10 · page 3 of 5Vectron International Headquarters Vectron International LLC.100 Watts StreetVectron international GmbH & Co. KGLandstrasseVectron Asia Pacific Sales OfficeUnit 3119 31st Floor, Jin Mao Tower, 88EnclosuresAbsolute Maximum RatingsParameter Min Typ Max. Units Condition Supply voltage (Vs) 7 VOperable temperature range -40 +80 °C For temperature Code F, D Storage temperature range -40 +90 °C For temperature Code F, DVectron International · v.2005-02-10 · page 4 of 5Vectron International Headquarters Vectron International LLC. 100 Watts StreetVectron international GmbH & Co. KG LandstrasseVectron Asia Pacific Sales OfficeUnit 3119 31st Floor, Jin Mao Tower, 88Recommended Reflow ProfileSMD oscillators must be on the top side of the PCB during the reflow process.Vectron International · v.2005-02-10 · page 5 of 5Vectron International Headquarters Vectron International LLC.100 Watts StreetVectron international GmbH & Co. KGLandstrasseVectron Asia Pacific Sales OfficeUnit 3119 31st Floor, Jin Mao Tower, 88How to Order this Product:Step 1 Use this worksheet to forward the following information to your factory representative:Model Stability Code Initial tolerance Supply Voltage Code RF Output Code Package Code C1410Example: C1410 D205 T104 SV050 RFH A1Step 2 The factory representative will then respond with a Vectron Model Number in the following Configuration: Model Package Code Dash Dash NumberC1410 [Customer Specified Package Code]- [Factory Generated 4 digit number] Typical P/N = C1410A1-0001Notes:1 Contact factory for improved stabilities or additional product options. Not all options and codes are available at all frequencies.2 Unless otherwise stated all values are valid after warm-up time and refer to typical conditions for supply voltage, frequency controlvoltage, load, temperature (25°C)3 Phase noise degrades with increasing output frequency.4 Subject to technical modification.5 Contact factory for availability.。

6639S-1-103;6639S-1-102;6639S-1-104;6639S-1-202;6639S-1-203;中文规格书,Datasheet资料

22.23 (.875) DIA.

3.18 (.125)

6639

11.25 .38 (.443 .015)

1.57 (.062)

Байду номын сангаас

22.23 (.875) DIA.

.51 (.020) REF

19.81 (.780) DIA.

12.70 .79 (.500 .031)

10.317+.000/-.051 (.4062+.000/-.002)

DIA.

6.342+.000/-.008

(.2497+.0000/-.0003) DIA. SHAFT .25

45 5 (.010) CHAMFER 1.19 1.60

SLOT (.047) X (.063)

Mechanical Characteristics1

Mechanical Angle ..........................................................Continuous, Stops (340 ° +8 °, -0 °) available Torque (Starting & Running)2 ...................................................................0.40 N-cm (0.5 oz.-in.) max.

Sea Level......................................... 750 VAC minimum .....................750 VAC minimum Power Rating (Voltage Limited By Power Dissipation or 300 VAC, Whichever is Less)

零部件英文缩写及零部件中英文对照

22

AIR-FLOW-SENSOR-FOR-AG63-AT

空气流量传感器-4G63AT

23

AIR-FLOW-SENSOR-FOR-AG64-AT

空气流量传感器-4G64AT

24

AIR-SUCTION-HOSE-ASS

空调吸气软管总成

25

AIR-TEMPERATURE-SENSOR

进气温度传感器

26

ALLOY-WHEEL

铝车轮

27

ANT-ASH-TRAY-LID

减振块-地毯

28

ANTENNA-ELE-ASS

自动天线总成

29

ANTENNA-IMMOBILIZER

发动机防盗系统-天线

30

ANTENNA-OUT-BC-OUTLINE

外置天线放大器总成

31

ANT-FOAM-TRUNK

减振垫-行李箱保护架

表1汽车产品零部件名称英文单词缩写

缩写

英文单词

中文名称

A、ASS

ASSEMBLY/ASSEMBLE

总成/集合、装配

ABS

ANTI-LOCK BRAKE SYSTEM

防抱死制动系统

AC

AIR-CONDITION

空调

ACCEL

ACCELERATOR

加速

ANT

ANTIVBIRATION

阻尼、减震器

ANTID

ARM-WIPER-LH-ASS

左刮臂总成

53

ARM-WIPER-RH-ASS

右刮臂总成

54

ASHTRAY-A-RR-DR-LH-PNL

左后门板烟灰盒总成

55

ASHTRAY-A-RR-DR-RHPANEL-RH

HER107S中文资料

PEAK FORWARD SURGE CURRENT. (A)

30 25 20 15 10 0 1 2 5 10

JUNCTION CAPACITANCE.(pF)

35 8.3ms Single Half Sine Wave JEDEC Method

60 50 40 30 20 10

HER 101 S~H ER1 HE 05S R10 6S~ HE R10 8S

A Cathode Mark B

D

C

DIMENSIONS INCHES MIN .166 .080 .021 1.000 MM MIN 4.10 2.00 .53 25.40

DIM A B C D

MAX .205 .107 .025 ---

MAX 5.20 2.70 .64 ---

NOTE

% !"#

HER101S THRU HER108S

1.0 Amp High Efficient Rectifiers 50 to 1000 Volts

A-405

• • •

Maximum Ratings

Operating Temperature: -55°C to +125°C Storage Temperature: -55°C to +150°C For capcitive load, derate current by 20% MCC Device Maximum Maximum Catalog Marking Recurrent RMS Number Peak Reverse Voltage Voltage HER101S --50V 35V HER102S --100V 70V HER103S --200V 140V HER104S --300V 210V HER105S --400V 280V HER106S --600V 420V HER107S --800V 560V HER108S --1000V 700V

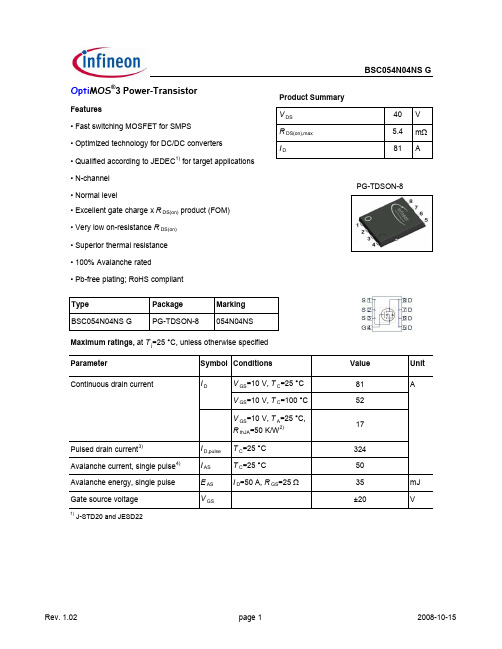

BSC054N04NS G中文资料

ValueUnit 81ABSC054N04NS GMaximum ratings, at T j =25 °C, unless otherwise specified Parameter Symbol Conditions Unit Power dissipationP totT C =25 °C 57WT A =25 °C, R thJA =50 K/W 2)2.5Operating and storage temperature T j , T stg-55 ... 150°C IEC climatic category; DIN IEC 68-155/150/56Parameter Symbol ConditionsUnitmin.typ.max.Thermal characteristicsThermal resistance, junction - caseR thJCbottom -- 2.2K/Wtop--20Device on PCBR thJA6 cm 2 cooling area 2)--50Electrical characteristics, at T j =25 °C, unless otherwise specified Static characteristicsDrain-source breakdown voltage V (BR)DSS V GS =0 V, I D =1 mA 40--VGate threshold voltage V GS(th)V DS =V GS , I D =27 µA 2-4Zero gate voltage drain currentI DSSV DS =40 V, V GS =0 V, T j =25 °C-0.11µAV DS =40 V, V GS =0 V, T j =125 °C-10100Gate-source leakage current I GSS V GS =20 V, V DS =0 V -10100nA Drain-source on-state resistance R DS(on)V GS =10 V, I D =50 A- 4.5 5.4m ΩGate resistance R G -1.5-ΩTransconductanceg fs|V DS |>2|I D |R DS(on)max , I D =50 A3467-S4)See figure 13 for more detailed information3) See figure 3 for more detailed information Value Values 2)Device on 40 mm x 40 mm x 1.5 mm epoxy PCB FR4 with 6 cm 2(one layer, 70 µm thick) copper area for drain connection. PCB is vertical in still air.BSC054N04NS GParameter Symbol Conditions Unitmin.typ.max. Dynamic characteristicsInput capacitance C iss-21002800pF Output capacitance C oss-620820 Reverse transfer capacitance C rss-22-Turn-on delay time t d(on)-11-ns Rise time t r- 2.6-Turn-off delay time t d(off)-16-Fall time t f- 3.6-Gate Charge Characteristics5)Gate to source charge Q gs-11-nC Gate charge at threshold Q g(th)- 6.3-Gate to drain charge Q gd- 3.3-Switching charge Q sw-8.2-Gate charge total Q g-2634Gate plateau voltage V plateau- 5.3-VGate charge total, sync. FET Q g(sync)V DS=0.1 V,V GS=0 to 10 V-24-nCOutput charge Q oss V DD=20 V, V GS=0 V-23-Reverse DiodeDiode continuous forward current I S--47A Diode pulse current I S,pulse--324Diode forward voltage V SD V GS=0 V, I F=50 A,T j=25 °C-0.91 1.2VReverse recovery charge Q rr V R=20 V, I F=I S,d i F/d t=400 A/µs-27-nC5) See figure 16 for gate charge parameter definition T C=25 °CValuesV GS=0 V, V DS=20 V,f=1 MHzV DD=20 V, V GS=10 V,I D=30 A, R G=1.6 ΩV DD=20 V, I D=30 A,V GS=0 to 10 VBSC054N04NS G Package Outline PG-TDSON-8PG-TDSON-8: OutlineFootprintBSC054N04NS G Package OutlinePG-TDSON-8: TapeBSC054N04NS GPublished byInfineon Technologies AG81726 Munich, Germany© 2008 Infineon Technologies AGAll Rights Reserved.Legal DisclaimerThe information given in this document shall in no event be regarded as a guarantee ofconditions or characteristics. With respect to any examples or hints given herein, any typicalvalues stated herein and/or any information regarding the application of the device,Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind,including without limitation, warranties of non-infringement of intellectual property rightsof any third party.InformationFor further information on technology, delivery terms and conditions and prices, pleasecontact the nearest Infineon Technologies Office().WarningsDue to technical requirements, components may contain dangerous substances. For informationon the types in question, please contact the nearest Infineon Technologies Office.Infineon Technologies components may be used in life-support devices or systems only withthe express written approval of Infineon Technologies, if a failure of such components canreasonably be expected to cause the failure of that life-support device or system or to affectthe safety or effectiveness of that device or system. Life support devices or systems areintended to be implanted in the human body or to support and/or maintain and sustainand/or protect human life. If they fail, it is reasonable to assume that the health of the useror other persons may be endangered.。

EPCS4SI8N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

串行配置器件

EPCS4 — — — — — — — — — —

EPCS16 v (2) v (2)

— — — — — — — —

EPCS64 EPCS128

v

v

v

v

v

v

v

v

v (2)

v

—

v

v

v

v

v

v

v

v (2)

v

表4-4 列出每个Stratix II GX FPGA和所使用串行配置器件 配置文件大小. Stratix II GX器件可以使用EPCS16,EPCS64,或 EPCS128.

处理器通过内存访问未使用闪存重新可编程内存超过10万次擦除编程写存储扇区防护护支持使用状态寄存器位在系统编程支持srunner软件驱动程序在系统编程支持usb冲击波byteblaster

芯片中文手册,看全文,戳

C51014-3.2

4.串行配置器件(EPCS1, EPCS4,EPCS16,EPCS64和EPCS128)

4–4

功能说明

表4-5 列出每个Stratix II FPGA和所使用串行配置设备 配置文件大小. Stratix II器件可与EPCS4,EPCS16,EPCS64,或使用 EPCS128.

表 4-5. 对于Stratix II器件串行配置设备支持

Stratix II器件

原始二进制文件大小

( 位 )(1)

表 4-4. 为Stratix II GX器件串行配置设备支持

Stratix II GX器件

原始二进制文件

大 小 ( 位 )(1)

EP2SGX30C

9,640,672

EP2SGX30D

EP2SGX60C

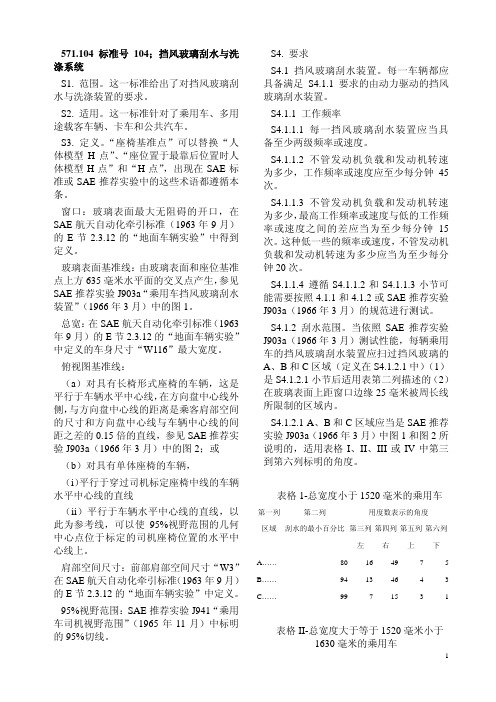

FMVSS104中文版

表格 1-总宽度小于 1520 毫米的乘用车

第一列

第二列

用度数表示的角度

区域 刮水的最小百分比 第三列 第四列 第五列 第六列

表格 II-总宽度大于等于 1630 毫米小于 1730 毫米的乘用车

第一列

第二列

用度数表示的角度

区域

刮水的最小 第三 第四 第五 第六

百分比

列列列列

左右上下

A……………

80 17 53

9

5

B……………

94 14 519

7 15

4

1

表格 II-总宽度大于等于 1730 毫米的乘用 车

S4.1.1.2 不管发动机负载和发动机转速 为多少,工作频率或速度应至少每分钟 45 次。

S4.1.1.3 不管发动机负载和发动机转速 为多少,最高工作频率或速度与低的工作频 率或速度之间的差应当为至少每分钟 15 次。这种低一些的频率或速度,不管发动机 负载和发动机转速为多少应当为至少每分 钟 20 次。

(b)对具有单体座椅的车辆,

(i)平行于穿过司机标定座椅中线的车辆 水平中心线的直线

(ii)平行于车辆水平中心线的直线,以 此为参考线,可以使 95%视野范围的几何 中心点位于标定的司机座椅位置的水平中 心线上。

肩部空间尺寸:前部肩部空间尺寸“W3” 在 SAE 航天自动化牵引标准(1963 年 9 月) 的 E 节 2.3.12 的“地面车辆实验”中定义。

第一列

第二列

用度数表示的角度

EP1C12Q240I7N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

400-Pin FineLine

BGA

1.0 441 21 × 21

1–3

初稿

芯片中文手册,看全文,戳

第一节气旋FPGA

系列数据表

修订记录

本节为设计师提供数据表规格

Cyclone器件.该章节包含内部功能定义 架构,配置和JTAG边界扫描测试信息, DC操作条件下,AC时序参数,一提到功耗和订购信息Cyclone器件.

本节包含以下章节:

■ 简介 ■ 旋风架构

配置与测试直流和开

表4-19.

对于EP1C3定稿定时信息和

EP1C12器件.更新时间信息

inTables 4–25 通过 4–26 and 表4-30

通过 4–51.

更新PLL规范

表4-52.

更新时间信息.时间最终确定 EP1C6和EP1C20器件.更新 性能信息.添加 部分.

"PLL时序"

添加文件到Cyclone器件手册.

运行条件 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1 能量消耗 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8 时序模型. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

× 36位) (1)

注意 表 1-1: (1) 该参数包括全局时钟引脚.

EP1C3 2,910

13 59,904

1 104

EP1C4 4,000

西门子 全自动型洗碗机 SJS4HKB00C [中文] 使用说明书

![西门子 全自动型洗碗机 SJS4HKB00C [中文] 使用说明书](https://img.taocdn.com/s3/m/6bacf22d7f21af45b307e87101f69e314232fa60.png)

立即在M y B o s c h上为您的电器注册,免费获得以下福利:b o sc h-h o m e.c n/m y b o s c h全自动型洗碗机SJS4HKB00C[zh]使用说明书zh2目录1安全性............................................ 41.1一般注意事项............................... 41.2使用范围...................................... 41.3用户群的限制............................... 41.4安装的安全性............................... 41.5使用安全性................................... 51.6洗碗机的损坏............................... 61.7对儿童有危险!............................ 72避免财物损失................................. 92.1安装的安全性............................... 92.2使用安全性................................... 93环境保护和节约.............................. 93.1处理包装材料............................... 93.2节约能源...................................... 93.3智能传感器................................. 104安装和接通................................... 104.1供货清单.................................... 104.2安装和接通洗碗机...................... 104.3排水连接.................................... 104.4自来水连接................................. 104.5电源连接.................................... 105了解机器...................................... 125.1机器........................................... 125.2操作面板.................................... 136程序............................................. 156.1自定义 ................................... 157增值功能...................................... 168配置............................................. 168.1上层碗篮.................................... 178.2下层碗篮.................................... 178.3多功能餐具篮............................. 178.4餐具最大直径............................. 179首次使用前................................... 189.1进行首次启动.. (18)10软水系统 (18)10.1水硬度设置概览........................ 1810.2软化盐...................................... 1810.3设置水软化系统........................ 1910.4关闭水软化系统........................ 1911漂洗剂装置................................. 1911.1漂洗剂...................................... 1911.2设置漂洗剂用量........................ 2011.3关闭漂洗剂装置........................ 2012洗涤剂........................................ 2012.1合适的洗涤剂........................... 2012.2不合适的洗涤剂........................ 2112.3洗涤剂注意事项........................ 2112.4填充洗涤剂............................... 2213餐具........................................... 2213.1玻璃杯和餐具的损坏................. 2213.2摆放餐具.................................. 2313.3取出餐具.................................. 2414操作基本知识............................. 2414.1开机......................................... 2414.2设置洗涤程序........................... 2414.3设置增值功能........................... 2414.4设置预约功能........................... 2414.5启动洗涤程序........................... 2514.6启用按键锁............................... 2514.7停用按键锁............................... 2514.8中断洗涤程序........................... 2514.9取消洗涤程序........................... 2514.10关机....................................... 2515基本设置.................................... 2615.1基本设置概览........................... 2615.2更改基本设置........................... 2716Home Connect 晶御智能 ........ 2716.1Home Connect 晶御智能 快速启动......................................2816.2Home Connect 晶御智能 设置.............................................28zh316.3远程启动 ............................... 2816.4远程诊断 ................................. 2916.5软件更新.................................. 2916.6数据保护 (29)17清洁和保养................................. 2917.1清洁洗碗机腔体........................ 2917.2清洁剂...................................... 2917.3洗碗机保养提示........................ 2917.4三重净滤系统........................... 3017.5清洁冲刷臂............................... 3118处理故障.................................... 3218.1清洁排水泵............................... 4219运输、储存和废弃处理............... 4219.1拆卸洗碗机............................... 4219.2防冻保护.................................. 4219.3搬运洗碗机............................... 4319.4处理旧机器............................... 4320客户服务.................................... 4320.1产品编号(E-Nr.)、制造编号(FD)及货号(Z-Nr.)........ 4321技术数据 (44)21.1给测试机构的说明.................... 4421.2有关自由开源软件的信息.......... 4522执行标准 (45)zh 安全性41 安全性请注意以下安全注意事项。

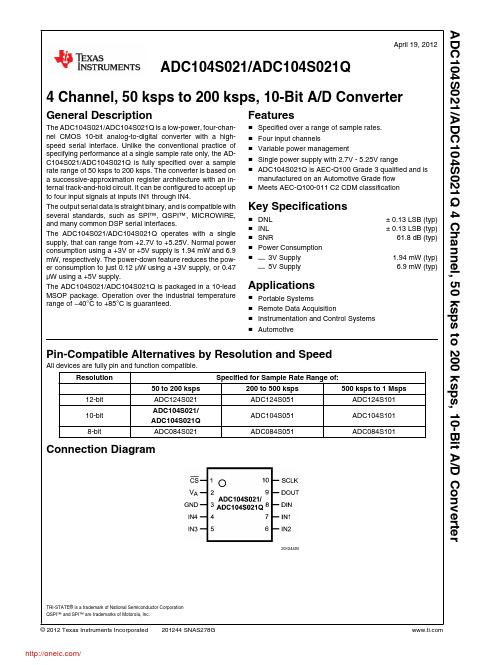

ADC104S021CIMMNOPB;ADC104S021CIMMXNOPB;中文规格书,Datasheet资料