ddc BU61580芯片手册

WT588D语音芯片及模块应用电路V1.9

WT588D 语音芯片/模块应用电路目录1、WT588D模块内部电路 ........................................................................................................................................... (3)1.1、WTW-16P模块内部电路 . ......................................................................................................................................... .................................... 3 1.2、WTW-28P模块内部电路 . ......................................................................................................................................... .................................... 4 2、WT588D-18P应用电路 ........................................................................................................................................... .. (5)2.1、WT588D-18P按键控制PWM 输出应用电路 . .........................................................................................................................................5 2.2、WT588D-18P按键控制DAC 输出(接三极管)应用电路 ................................................................................................................... 6 2.3、WT588D-18P按键控制DAC 输出(接功放)应用电路 ....................................................................................................................... 7 2.4、WT588D-18P一线串口控制PWM 输出应用电路 . (8)2.5、WT588D-18P三线串口PWM 输出应用电路 . .........................................................................................................................................9 3、WT588D-20SS应用电路 . ......................................................................................................................................... . (10)3.1、WT588D-20SS按键控制PWM 输出应用电路 . (10)3.2、WT588D-20SS按键控制DAC 输出(接三极管)应用电路 . ............................................................................................................. 11 3.3、WT588D-20SS按键控制DAC 输出(接功放)应用电路 .................................................................................................................. 12 3.4、WT588D-20SS一线串口PWM 输出应用电路 . (13)3.5、WT588D-20SS三线串口PWM 输出应用电路 . (14)4、WT588D-32L应用电路 . ......................................................................................................................................... . (15)4.1、WT588D-32L按键控制PWM 输出应用电路 .......................................................................................................................................15 4.2、WT588D-32L按键控制DAC 输出(接三极管)应用电路 . ................................................................................................................ 16 4.3、WT588D-32L按键控制DAC 输出(接功放)应用电路 . .................................................................................................................... 17 4.4、WT588D-32L MP3控制PWM 输出应用电路 (18)4.5、WT588D-32L 3×8矩阵按键控制PWM 输出应用电路 . .................................................................................................................. 19 4.6、WT588D-32L并口控制PWM 输出应用电路 .......................................................................................................................................20 4.7、WT588D-32L一线串口控制PWM 输出应用电路 (21)4.8、WT588D-32L三线串口控制PWM 输出应用电路 (22)4.9、WT588D-32L三线串口控制I/O口扩展输出应用电路 ....................................................................................................................... 23 5、WTW-16P应用电路 ........................................................................................................................................... .. (24)5.1、WTW-16P按键控制PWM 输出应用电路 ........................................................................................................................................... .. 24 5.2、WTW-16P按键控制DAC 输出(接三极管)应用电路 ...................................................................................................................... 24 5.3、WTW-16P按键控制DAC 输出(接功放)应用电路 .......................................................................................................................... 25 5.4、WTW-16P一线串口控制PWM 输出应用电路 . (26)5.5、WTW-16P三线串口PWM 输出应用电路 ........................................................................................................................................... .. 26 6、WTW-28P应用电路 ........................................................................................................................................... .. (27)6.1、WTW-28P按键控制PWM 输出应用电路 ........................................................................................................................................... .. 27 6.2、WTW-28P按键控制DAC 输出(接三极管)应用电路 ...................................................................................................................... 28 6.3、WTW-28P按键控制DAC 输出(接功放)应用电路 .......................................................................................................................... 29 6.4、WTW-28P MP3控制PWM 输出应用电路 ...........................................................................................................................................30 6.5、WTW-28P 3×8矩阵按键控制PWM 输出应用电路 . (30)6.6、WTW-28P并口控制PWM 输出应用电路 ........................................................................................................................................... .. 316.7、WTW-28P一线串口控制PWM 输出应用电路 . (31)6.8、WTW-28P三线串口控制PWM 输出应用电路 . (32)6.9、WTW-28P三线串口控制I/O口扩展输出应用电路 . ............................................................................................................................ 33 7、DAC(外接功放)输出外围电路 . ......................................................................................................................................... .................................. 33 8、按键触发电路 ........................................................................................................................................... (34)8.1、单键实现单曲循环播放/停止功能 ........................................................................................................................................... .................. 34 8.2、先复位后电平触发电路 ........................................................................................................................................... (34)6.6、WTW-28P 并口控制 PWM 输出应用电路 VDD1 A3 A4 A5 A6 A7 RESET A2 A1 A0 SBT MCU SPEAKER 1 2 3 4 5 6 7 8 9 10 11 12 13 14 P05 P06 P07 P10 P11 P12 RESET DAC PWM+ PWMP14 P13 P16 GND NC NC NC NC NC P04 VDD BU SY VCC P00 P01 P02 P03 P15 28 27 26 25 24 23 22 21 20 19 18 17 16 15 VDD R1 470 D1 LED VCC WTW-28P 软件设置:并口控制模式。

基于BU-61580的航空1553B总线RT模式设计

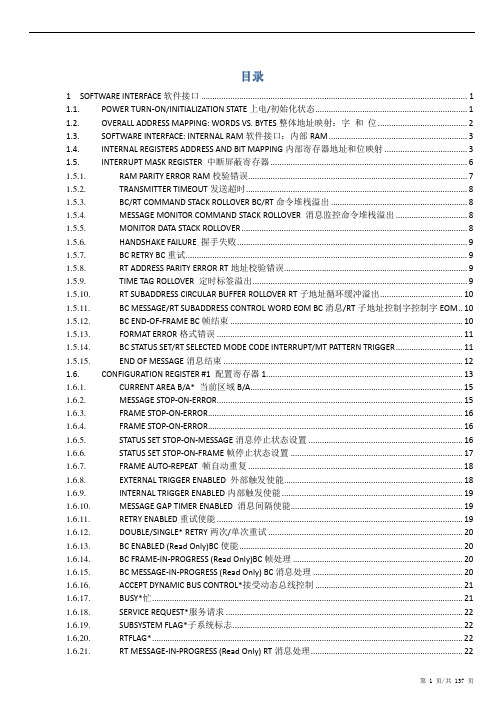

BU_61580寄存器说明中文版

61580说明

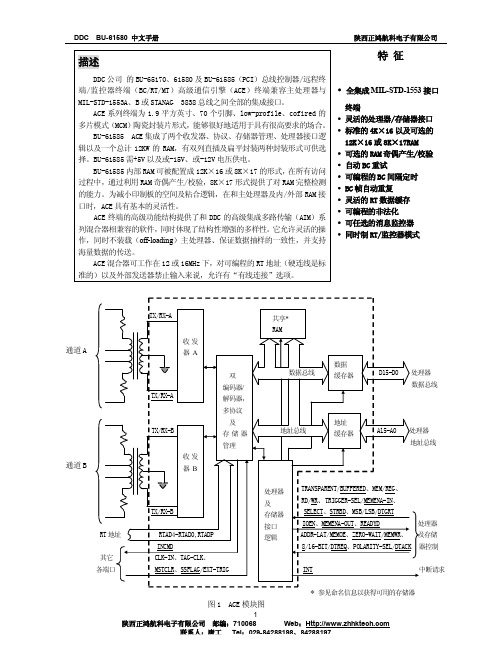

61580说明B61580处理器产品使⽤说明航天时代电⼦公司第772研究所2007年3⽉1、主要特点●双路1553总线收发模块●完整的MIL-STD-1553B双余度总线控制器(BC)、远程终端(RT)和监测终端(MT);●与主机和外部存储器灵活的接⼝模式;●16M / 12M可选择的时钟⼯作频率;●BC和RT⽅式的多消息处理能⼒;●BC⽅式消息⾃动重试、信息帧的⾃动重发和可编程的消息间延时;●强⼤的内部⾃测试功能;●RT模式灵活的数据缓冲⽅式;●可选择消息的监测模式;●同步RT/监测模式;●DIP70封装;2、简单介绍B61580为MIL-STD-1553B总线上先进的通讯控制器,其内部的BC、RT和MT功能,为MIL-STD-1553B系统设计提供了⼀个智能的解决⽅法。

该器件多电路模块的陶瓷封装(MCM),电路内部集成有:数字协议控制电路,双路总线收发器等模块。

因此,该电路更适合⾼强度的应⽤环境。

电路内部主要的逻辑模块为:双路收发器、完整的BC/RT/MT多功能协议逻辑、存储器管理逻辑和中断逻辑,4K×16位的静态存储器和与处理器总线的接⼝逻辑,其整体框图如图1所⽰。

B61580包括内部地址锁存器和双向的数据缓冲电路以便于其与处理器总线的数据交换。

B61580还可以很⽅便的与8位或16位的处理器进⾏接⼝通信,另外,在共⽤RAM和DMA配置模式下,B61580能最⼤外扩64KRAM。

B61580电路是⽀持多协议数据总线的器件,它⽀持多种通信协议,如:MIL-STD-1553A、MIL-STD-1553B、MIL-STD-1773、STANAG3838和MCAIR A3818,A5232和A5690等协议。

B61580的MT模式⽀持三种监视模式:字测试、可选择消息测试和与RT组合的可选择测试⽅式。

BC模式具有总线消息⾃动重试和可编程消息间间隔以及帧⾃动重发功能。

RT模式具有总线消息记录时标和内部命令⾮法化功能。

基于BU—61580与USB的MIL—STD—1553B总线控制卡的设计

基于BU—61580与USB的MIL—STD—1553B总线控制卡的设计王冬伟;孙越强;杜起飞;白伟华;王先毅;吴迪;余庆龙【摘要】MIL-STD-1553B bus is a military serial bus, with high reliability. This bus has a wide range of applications in aviation, aerospace, automotive and other fields. USB is a popular universal serial bus. The USB communication protocol allows the bus transferring data whit high rate, with versatility interface and other advantages. In order to testing the 1553B communication in the aircraft or other applications normal or not, a special 1553B Bus control card is need. An design named 1553B Bus Control Card is described which is based on the 1553B Bus and USB protocols. This control card can achieve the basic functions including reading and sending data, mode and broadcast messages. This control card can also inherit the advantages of USB, including supporting plug and play, high rate and programmable message structure. Then the implementation of this design, including the BU-61580 and USB connection and software methods are introducd. Finally, it describes the results of the control card.%MIL—STD—1553B总线是一种军用串行总线,具有完整的总线通信协议,具有很高的可靠性,在航空、航天、汽车电子等领域有广泛的应用.USB总线是一种常用的通用串行总线.USB完整的通信协议使得USB传输具有很高的传输速率,接口通用性强等优点.为了在地面测得飞机或者卫星等应用上的1553B总线通信是否正常,需要专门的总线控制卡来进行通信测试.介绍了一种基于BU—61580和USB芯片设计的1553总线控制卡,该控制卡实现1553B总线控制的基本功能,包括读取和发送数据,发送方式控制字,向总线广播数据等基本的总线消息.同时继承了USB的各种优点,即支持即插即用功能,传输速度高,支持可编程的消息控制模式.并且介绍了这种总线控制卡的实现方法,包括BU—61580与USB芯片的硬件连接和软件实现,最后介绍了控制卡的测试结果.【期刊名称】《科学技术与工程》【年(卷),期】2012(012)011【总页数】6页(P2580-2585)【关键词】MIL—STD—1553B总线;BU—61580;USB;总线控制卡【作者】王冬伟;孙越强;杜起飞;白伟华;王先毅;吴迪;余庆龙【作者单位】中国科学院国家空间科学中心,北京100190;中国科学院国家空间科学中心,北京100190;中国科学院国家空间科学中心,北京100190;中国科学院国家空间科学中心,北京100190;中国科学院国家空间科学中心,北京100190;中国科学院国家空间科学中心,北京100190;中国科学院国家空间科学中心,北京100190【正文语种】中文【中图分类】TP336MIL—STD—1553B总线是美国定义的军方串行总线标准,它是数字式时分制指令/响应式多路传输数据总线,传输速率可达到1 Mbps,该通信协议的完整性使通信的控制更具安全性和可靠性。

BU61580芯片RT模式操作笔记

BU61580芯片RT模式操作笔记RT状态机:RT状态机当node_mode==10时,节点被配置为RT模式.RT的工作流程如图2的右分支,RT响应是从接收到一个完整的命令字开始的,而接收命令字由解码器的同步头检测开始.当检测出同步头111000时,则说明检测到了一个命令字,位流控制模块将从解码器得到的信息字进行命令字解析,得到节点标识符RT_ID=dw_data[15:11]、接收发送标识符T/R=dw_data[10]、子地址(方式代码)SUB_ADDR=dw_data[9:5]和数据字个数(方式代码数据)DW_NUM=dw_data[4:0].首先由RT地址识别子模块验证RT_ID,如果是11111,则进入广播处理状态;如果与节点id相同,则判断子地址,若子地址是00000或11111,则是方式代码,进入方式代码处理状态;若子地址在00000与11111之间,则是数据传递,进入数据处理状态。

进入数据处理状态后,如果要求远程终端接收数据字,则先从配置寄存器1的bit13得到使用RAM区域A还是区域B,假设使用区域A,则(1)从RAM中地址为0x0100的位置读取本条消息的描述符堆栈地址;(2)从相应查找表地址中读取子地址控制字,判断相应RT子地址的RAM管理和中断机制;(3)从相应查找表地址中读取数据块地址;(4)描述符堆栈的4个字由下向上一次写入当前命令字、数据块地址、时间标记字和块状态字;(5)在堆栈指针位置写入本条消息堆栈描述符的地址;(6)向数据块中写入接收到的数据字;(7)数据字全部接收完毕后,返回相应状态字;(8)产生中断,通知微处理器数据接收完毕.如果命令字要求远程终端发送数据,则执行(3)后,在相应位置写入状态字,从数据块地址中读取数据字,置发送使能,通过编码器发送要求个数的数据字.不同状态对RAM区域的访问如图4所示.广播处理状态与数据收发类似,不做状态字回复.方式代码处理状态,根据1553B总线标准对不同的方式代码进行相关的位操作。

61580中文手册

际.权 杂.扁 附0 附0

彼A 彼A 承F 承F

B此-际附所70/际所附片0/际所附片附应所 · 为附步 · 为附步 · -所附步 · 为附步 · 为附步 · -所扁步 · 为附步 · 为附步 A B A A B B A A B B

权.附 权.附 -所附.7附 权.附 权.附 -所扁.际 权.附 权.7附

际7 际0 扁.附 版.附

所附附杂

C也此 BC BC/R正/M正

R正 正

所所

所7.附 扁所.附 权版.附 所扁7 权

所片.附 扁扁.附 附0.附 所扁版.附 际片片

D浸年 θJC B此-际附所70/际所附片0应所 B此-际附所70/际所附片0应扁 B此-际附所70/际所附片0应杂 B此-际附所70/际所附片0应际

所-7) 所-7) 所-7) 所-7)

所所 扁.附 所0 附 0.片际0 所0

K操 K操 承F 承F 步承-承 步承年⑷顺

0.扁00

杂附操 70操 B此-际附所70/际所附片0/际所附片附应所 B此-际附所70/际所附片0/际所附片附应扁 应杂 应际

际

7 扁0 所片

/ 步存字 步存L 存存字(步CC=附.附步 步存N=步CC) 存存字(步CC=附.附步 步存N=扁.7步) 止止FLAG/EX正-正R存G 存存L(步CC=附.附步 步存N=0.权步) 止止FLAG/EX正-正R存G 步O字(步CC=权.附步 步存字=扁.7步 步存L=0.扁步 存O字= 步OL(步CC=权.附步 步存字=扁.7步 步存L=0.扁步 存OL= 存OL DB所附-DB0 A所附-A0 MEMOE/ADDR-LA正 MEMWR/ZERO-WA存正 D正RE习/所际/片 D正ACK/也OLAR存正Y-止EL 存NCMD 存N正 MEMENA-O此正 READYD 存OEN 正XA 正XA 正XB 正XB 正X-存N字-O此正-A 正X-存N字-O此正-B ) )

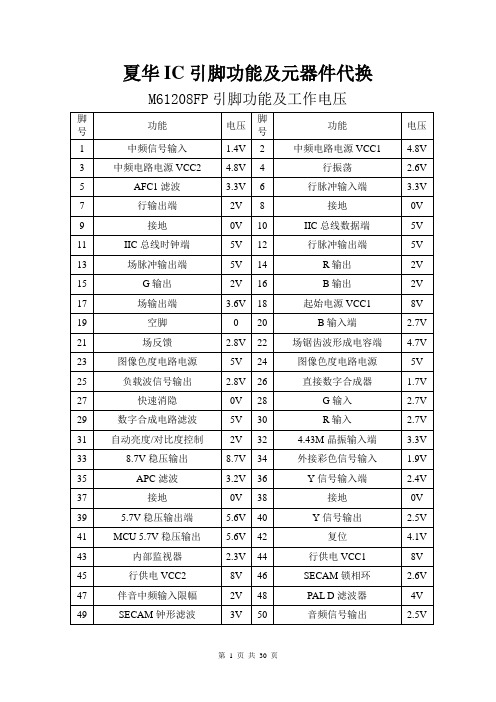

IC引脚功能及元器件代换

夏华IC引脚功能及元器件代换M61208FP引脚功能及工作电压

J系列CPU(SDA555X)各脚功能及电压

TDA16846功能脚简介

STR-G5653引脚功能及电压

ST6378引脚功能

TDA6210Q引脚功能

AN7583引脚功能

TA8720AN AV开关

SDA9380引脚功能

TDA8362引脚功能

厦华彩电各型号中周内置电容值

厦华彩电显像管、高压包及电路主要参数对照表(一)

第10 页共30 页

第11 页共30 页

第12 页共30 页

第13 页共30 页

第14 页共30 页

第15 页共30 页

第16 页共30 页

第17 页共30 页

第18 页共30 页

第19 页共30 页

厦华彩电行包代换表

第20 页共30 页

第21 页共30 页

第22 页共30 页

第23 页共30 页

第24 页共30 页

第25 页共30 页

开关变压器代用表

1/2W稳压管型号稳压值

场效应管K3116可用K2645代用。

D400可用C2344代用。

C2344可用C5248代用厦华彩电机型与CPU型号对应表。

61580datasheet

®Fully Integrated MIL-STD-1553DESCRIPTIONCOMMUNICATION ENGINE (ACE)Card you purchase has...2Data Device Corporation BU-65170/61580/61585L-03/06-0F IG U R E 1.A C E B L O C K D I A G R A MC H . AC H . BR T A O C E S S O R A T A B U SO C E S S O R D R E S S B U SM I S C R O C E S S O R A N D M E M O R Y C O N T R O L N T E R R U P T R E Q U E S TE M O R YData Device Corporation BU-65170/61580/61585L-03/06-03Data Device Corporation BU-65170/61580/61585L-03/06-04Data Device Corporation BU-65170/61580/61585L-03/06-0INTRODUCTIONDDC's ACE series of Integrated BC/RT/MT hybrids provide a complete, flexible interface between a microprocessor and a MIL-STD-1553A, B Notice 2, McAir, or STANAG 3838 bus, implementing Bus Controller, Remote T erminal (RT) and Monitor T erminal (MT) modes.Packaged in a single 1.9-square-inch, 70-pin DIP or surface mountable flatpack or J-lead package, the ACE series contains dual low-power transceivers and encoder/decoders, complete BC/RT/MT multi-protocol logic, memory management and interrupt logic, 4K x 16 of shared stat-ic RAM and a direct, buffered interface to a host processor bus.The BU-65170/61580 contains internal address latches and bidi-rectional data buffers to provide a direct interface to a host processor bus.The BU-65170/61580 may be interfaced directly to both 16-bit and 8-bit microprocessors in a buffered shared RAM configuration.In addition, the ACE may connect to a 16-bit processor bus via a Direct Memory Access (DMA) interface.The BU-65170/61580 includes 4K words of buffered RAM. Alternatively, the ACE may be interfaced to as much as 64K words of external RAM in either the shared RAM or DMA config-urations.The ACE RT mode is multiprotocol, supporting MIL-STD-1553A, MIL-STD-1553B Notice 2, STANAG 3838 (including E FAbus), and the McAir A3818, A5232, and A5690 protocols.Full compli-ance to the McAir specs, however, requires the use of a sinu-soidal transceiver (transceiver option 5).Refer to the BU-61590 data sheet for additional information on McAir terminals.The memory management scheme for RT mode provides an option for separation of broadcast data, in compliance with 1553B Notice 2.Both double buffer and circular buffer options are programmable by subaddress.These features serve to ensure data consistency and to off-load the host processor for bulk data transfer applications.The ACE series implements three monitor modes:a word moni-tor, a selective message monitor, and a combined RT/selective monitor.Other features include options for automatic retries and programmable intermessage gap for BC mode, an internal Time Tag Register, an Interrupt Status Register and internal command illegalization for RT mode.FUNCTIONAL OVERVIEWTRANSCEIVERSThe transceivers in the BU-65170/61580X3(X6) are fully mono-lithic, requiring only a +5 volt power input.Besides eliminating the need for an additional power supply, the use of a 5 volt (only) transceiver requires the use of step-up, rather than step-down, isolation transformers.This provides the advantage of a higher terminal input impedance than is possible for a 15 volt or 12 volt transmitter.As a result, there is greater margin for the input impedance test, mandated for 1553 validation testing.This allows for longer cable lengths between an LRU's system con-nector and the isolation transformers of an embedded 1553 ter-minal.For the +5 V and -15 V/-12 V front end, the BU-65170/ 61580X1(X2) uses low-power bipolar analog monolithic and thick-film hybrid technology.The transceiver requires +5 V and -15 V (-12 V) only (requiring no +15 V/+12 V) and includes volt-age source transmitters.The voltage source transmitters provide superior line driving capability for long cables and heavy amounts of bus loading.In addition, the monolithic transceivers in the BU-65170/61580X1 provide a minimum stub voltage level of 20 volts peak-to-peak transformer coupled, making them suit-able for MIL-STD-1760 applications.The receiver sections of the BU-65170/61580 are fully compliant with MIL-STD-1553B in terms of front end overvoltage protec-tion, threshold, common mode rejection, and word error rate.In addition, the receiver filters have been designed for optimal oper-ation with the J´ chip's Manchester II decoders.J´ DIGITAL MONOLITHICThe J´ digital monolithic represents the cornerstone element of the ACE family of terminals.The development of the J´ chip rep-resents the fifth generation of 1553 protocol and interface design for DDC.Over the years, DDC's 1553 protocol and interface design has evolved from:(1) discrete component sets, consisting of multiple hybrids (with large numbers of chips inside the indi-vidual hybrids) and programmable logic devices, to (2) multiple custom ASICs to perform the functions of encoder/decoder andNotes for Table 1:Notes 1 through 6 are applicable to the Receiver Differential Resistance and Differential Capacitance specifications: (1) Specifications include both transmitter and receiver (tied togetherinternally).(2) Measurement of impedance is directly between pins TX/RX A(B)and TX/RX A(B) of the BU-65170/61580XX hybrid.(3) Assuming the connection of all power and ground inputs to thehybrid.(4) The specifications are applicable for both unpowered and poweredconditions.(5) The specifications assume a 2 volt rms balanced, differential, sinu-soidal input.The applicable frequency range is 75 kHz to 1 MHz.(6) Minimum resistance and maximum capacitance parameters areguaranteed,but not tested, over the operating range.(7) Assumes a common mode voltage within the frequency range of dcto 2MHz, applied to pins of the isolation transformer on the stubside (either direct or transformer coupled), referenced to hybride a DDC recommended transformer or other transformerthat provides an equivalent minimum CMRR.(8) Typical value for minimum intermessage gap time.Under softwarecontrol, may be lengthened to (65,535µs minus message time), inincrements of 1µs.(9) Software programmable (4 options).Includes RT-to-RT Timeout(Mid-Parity of Transmit Command to Mid-Sync of Transmitting RTStatus).(10) For both +5V logic and transceiver.+5V for channels A and B.(11) Measured from mid-parity crossing of Command Word to mid-synccrossing of RT's Status Word.(12) Specifications for BU-65171, BU-61581, and BU-61586 are identi-cal to the specifications for the BU-65170, BU-61580, and BU-61585 respectively.5Data Device Corporation BU-65170/61580/61585L-03/06-0Interrupt Status Register when the Time T ag Register rolls over from 0000 to FFFF.Assuming the Time T ag Register is not loaded or reset, this will occur at approximately 4-second time intervals, for 64 µs/LSB resolution, down to 131 ms intervals, for2 µs/LSB resolution.Another programmable option for RT mode is the automatic clearing of the Service Request Status Word bit following the ACE's response to a T ransmit Vector Word mode command.INTERRUPTSThe ACE series components provide many programmable options for interrupt generation and handling.The interrupt out-put pin (INT) has three software programmable modes of opera-tion:a pulse, a level output cleared under software control, or a level output automatically cleared following a read of the Interrupt Status Register.Individual interrupts are enabled by the Interrupt Mask Register.The host processor may easily determine the cause of the inter-rupt by using the Interrupt Status Register.The Interrupt Status Register provides the current state of the interrupt conditions.The Interrupt Status Register may be updated in two ways.In the standard interrupt handling mode, a particular bit in the Interrupt Status Register will be updated only if the condition exists and the corresponding bit in the Interrupt Mask Register is enabled.In the enhanced interrupt handling mode, a particular bit in the Interrupt Status Register will be updated if the condition exists regardless of the contents of the corresponding Interrupt Mask Register bit.In any case, the respective Interrupt Mask Register bit enables an interrupt for a particular condition.ADDRESSING,INTERNAL REGISTERS,ANDMEMORY MANAGEMENTThe software interface of the BU-65170/61580 to the host processor consists of 17 internal operational registers for normal operation, an additional 8 test registers, plus 64K x 16 of shared memory address space.The BU-65170/61580's 4K x 16 of inter-nal RAM resides in this address space.Reference T ABLE 2 and24.Definition of the address mapping and accessibility for the ACE's17 non-test registers, and the test registers, is as follows:Interrupt Mask Register is used to enable and disable interrupt requests for various conditions.Configuration Registers #1 and #2are used to select the BU-61580's mode of operation, and for software control of RT Status Word bits, Active Memory Area, BC Stop-on-Error, RT Memory Management mode selection, and control of the Time T ag oper-ation.Start/Reset Register is used for “command”type functions, such as software reset, BC/MT Start, Interrupt Reset, Time T ag Reset, and Time T ag Register T est.The Start/Reset Register includes provisions for stopping the BC in its auto-repeat mode, either at the end of the current message or at the end of the cur-rent BC frame.6Data Device Corporation BU-65170/61580/61585L-03/06-0BC/RT Command Stack Pointer Register allows the host CPU to determine the pointer location for the current or most recent message when the BU-61580 is in BC or RT modes.BC Control Word/RT Subaddress Control Word Register:In BC mode, it allows host access to the current, or most recent BC Control Word.The BC Control Word contains bits that select the active bus and message format, enable off-line self-test, mask-ing of Status Word bits, enable retries and interrupts, and speci-fy MIL-STD-1553A or -1553B error handling.In RT mode, this register allows host access to the current or most recent Subaddress Control Word.The Subaddress Control Word is used to select the memory management scheme and enable interrupts for the current message.The read/write accessibility can be used as an aid for testing the ACE.Time T ag Register maintains the value of a real-time clock.The resolu-tion of this register is programmable from among 2, 4, 8, 16, 32, and 64µs/LSB.The T AG_CLK input signal also may cause an external oscillator to clock the Time T ag Register.Start-of-Message (SOM) and E nd-of-Message (EOM) sequences in BC, RT, and Message Monitor modes cause a write of the current value of the Time T ag Register to the stack area of RAM.Interrupt Status Register mirrors the Interrupt Mask Register and con-tains a Master Interrupt bit.It allows the host processor to determine the cause of an interrupt request by means of a single READ operation. Configuration Registers #3,#4,and #5are used to enable many of the BU-61580's advanced features.These include all the enhanced mode features;that is, all the functionality beyond that of the previous generation product, the BUS-61559 Advanced Integrated Mux Hybrid with Enhanced RT Features (AIM-HY'er).For all three modes, use of the Enhanced Mode enables the various read-only bits in Configuration Register #1.For BC mode, the enhanced mode features include the expanded BC Control Word and BC Block Status Word, additional Stop-On-Error and Stop-On-Status Set functions, frame auto-repeat, programmable intermessage gap times, automatic retries, expanded Status Word Masking, and the capability to generate interrupts following the completion of any selected message.For RT mode, the enhanced mode features include the expanded RT Block Status Word, the combined RT/Selective Message Monitor mode, internal wrapping of the RTF AIL output signal (from the J´chip) to the RTFLAG RT Status Word bit, the double buffering scheme for individual receive (broadcast) subaddresses, and the alternate (fully soft-ware programmable) RT Status Word.For MT mode, use of the enhanced mode enables use of the Selective Message Monitor, the com-bined RT/Selective Monitor modes, and the monitor triggering capability. Data Stack Address Register is used to point to the current address location in shared RAM used for storing message words (second Command Words, Data Words, RT Status Words) in the Selective Word Monitor mode.Frame Time Remaining Register provides a read only indication of the time remaining in the current BC frame.The resolution of this register is 100 µs/LSB.Message Time Remaining Register provides a read only indication of the time remaining before the start of the next message in a BC frame. The resolution of this register is 1 µs/LSB.BC Frame/RT Last Command/MT T rigger Word Register:In BC mode, it programs the BC frame time, for use in the frame auto-repeat mode.The resolution of this register is 100 µs/LSB, with a range of 6.55 seconds;in RT mode, this register stores the current (or most previous) 1553 Command Word processed by the ACE RT;in the Word Monitor mode, this register specifies a 16-bit T rigger (Command) Word.The T rigger Word may be used to start or stop the monitor, or to generate inter-rupts.Status Word Register and BIT Word Registers provide read-only indi-cations of the BU-65170/61580's RT Status and BIT Words.Test Mode Registers 0-7:These registers may be used to facilitate pro-duction or maintenance testing of the BU-65170/61580 and systems incorporating the BU-65170/61580.*Not applicable to BU-65170/615717Data Device Corporation BU-65170/61580/61585L-03/06-08Data Device Corporation BU-65170/61580/61585L-03/06-09Data Device Corporation BU-65170/61580/61585L-03/06-0Notes for TABLE 14:Read only, logic “0”for 65170/61580, logic “1”for 65171/61581/61586.Note:resolution = 1 µs per LSB10NOTE:TABLES 21 TO 24 ARE NOT REGISTERS,BUTTHEY ARE WORDS STORED IN RAM.Data Device Corporation BU-65170/61580/61585BUS CONTROLLER (BC) ARCHITECTUREThe BC protocol of the BU-61580 implements all MIL-STD-1553B message formats.Message format is programmable on a message-by-message basis by means of bits in the BC Control Word and the T/R bit of the Command Word for the respective message.The BC Control Word allows 1553 message format, 1553A/B type RT, bus channel, self-test, and Status Word mask-ing to be specified on an individual message basis.In addition, automatic retries and/or interrupt requests may be enabled or disabled for individual messages.The BC performs all error checking required by MIL-STD-1553B.This includes validation of response time, sync type and sync encoding, Manchester II encoding, parity, bit count, word count, Status Word RT Address field, and various RT-to-RT transfer errors.The BU-61580's BC response timeout value is programmable with choices of 18, 22, 50, and 130 µs.The longer response timeout values enable oper-ation over long buses and/or the use of repeaters.FIGURE 2 illustrates BC intermessage gap and frame timing. The BU-61580 may be programmed to process BC frames of up to 512 messages with no processor intervention.It is possible to program for either single frame or frame auto-repeat operation. In the auto-repeat mode, the frame repetition rate may be con-trolled either internally, using a programmable BC frame timer, or from an external trigger input.The internal BC frame time is pro-grammable up to 6.55 seconds in increments of 100 µs.In addi-tion to BC frame time, intermessage gap time, measured from the start of the current message to the start of the subsequent message, is programmable on an individual message basis.The time between individual successive messages is programmable up to 65.5 ms, in increments of 1 µs.BC MEMORY ORGANIZATIONTABLE 25 illustrates a typical memory map for BC mode.It is important to note that the only fixed locations for the BU-61580 in the Standard BC mode are for the two Stack Pointers (address locations 0100 (hex) and 0104) and for the two Message Count locations (0101 and 0105).E nabling the Frame Auto-Repeat mode will reserve four more memory locations for use in the Enhanced BC mode;these locations are for the two Initial Stack Pointers (address locations 102 (hex) and 106) and for the Initial Message Count locations (103 and 107).The user is free to locate the Stack and BC Message Blocks anywhere else within the 64K (4K internal) shared RAM address space.For simplicity of illustration, assume the allocation of the maxi-mum length of a BC message for each message block in the typ-Data Device Corporation BU-65170/61580/61585ical BC memory map of T ABLE 25.The maximum size of a BC message block is 38 words, for an RT -to-RT transfer of 32 Data Words (Control + 2 Commands + Loopback + 2 Status Words +32 Data Words).Note, however, that this example assumes the disabling of the 256-word boundaries.BC MEMORY MANAGEMENTFIGURE 3 illustrates the BU-61580's BC memory management scheme.One of the BC memory management features is the global double buffering mechanism.This provides for two sets of the various BC mode data structures:Stack Pointer and Message Counter locations, Descriptor Stack areas, and BC message blocks.Bit 13 of Configuration Register #1 selects the current active area.At any point in time, the BU-61580's internal 1553 memory management logic may access only the various data structures within the “active”area.FIGURE 3 delineates the “active”and “inactive”areas by the nonshaded and shaded areas, respectively;however, at any point in time, both the “active”and “nonactive”areas are accessible by the host processor .In most applications, the host processor will access the “nonactive”area, while the 1553 bus processes the “active”area messages.The BC may be programmed to transmit multimessage frames of up to 512 messages.The number of messages to be processed is programmable by the Active Area Message Count location in the shared RAM, initialized by the host processor.In addition, the host processor must initialize another location, the Active Area Stack Pointer.The Stack Pointer references the four-word mes-sage block descriptor in the Stack area of shared RAM for each message to be processed.The BC Stack size is programmable with choices of 256, 512, 1024, and 2048 words.In the BC Frame Auto-Repeat mode, the Initial Stack Pointer and Initial Message Counter locations must be loaded by the host prior to the processing of the first frame.The single frame mode does not use these two locations.The third and fourth words of the BC block descriptor are the Intermessage Gap Time and the Message Block Address for the respective message.These two memory locations must be writ-ten by the host processor prior to the start of message e of the Intermessage Gap Time is optional.The Block Address pointer specifies the starting location for each message block.The first word of each BC message block is the BC Control Word.At the start and end of each message, the Block Status and Time T ag Words write to the message block descriptor in the stack.FIGURE 2.BC MESSAGE GAP AND FRAME TIMINGThe Block Status Word includes indications of message in process or message completion, bus channel, status set,response timeout, retry count, status address mismatch, loop test (on-line self-test) failure, and other error conditions.T ABLE 21 illustrates the bit mapping of the BC Block Status word.The 16-bit Time T ag Word will reflect the current contents of the inter-nal Time T ag Register.This read/writable register, which oper-ates for all three modes, has programmable resolution of from 2to 64 µs/LSB.In addition, the Time T ag register may be clocked from an external source.BC MESSAGE BLOCK FORMATS AND BC CONTROL WORDIn BC mode, the BU-61580 supports all MIL-STD-1553 message formats.For each 1553 message format, the BU-61580 man-dates a specific sequence of words within the BC Message Block.This includes locations for the Control, Command and (transmitted) Data Words that are to be read from RAM by the BC protocol logic.In addition, subsequent contiguous locations must be allocated for storage of received Loopback, RT Status and Data Words.FIGURE 4 illustrates the organization of the BC message blocks for the various MIL-STD-1553 message for-mats.Note that for all of the message formats, the BC Control Word is located in the first location of the message block.For each of the BC Message Block formats, the first word in the block is the BC Control Word.The BC Control Word is not trans-mitted on the 1553 bus.Instead, it contains bits that select the active bus and message format;enable off-line self-test;mask-ing of Status Word bits;enable retries and interrupts;and speci-fies MIL-STD-1553A or -1553B error handling.The bit mapping and definitions of the BC Control Word are illustrated in TABLE 8.The BC Control Word is followed by the Command Word to be transmitted, and subsequently by a second Command Word (for an RT -to-RT transfer), followed by Data Words to be transmitted (for Receive commands).The location after the last word to be transmitted is reserved for the Loopback Word.The Loopback Word is an on-line self-test feature.The subsequent locations after the Loopback Word are reserved for received Status Words and Data Words (for T ransmit commands).AUTOMATIC RETRIESThe BU-61580 BC implements automatic message retries.When enabled, retries will occur, following response timeout or format error conditions.As additional options, retries may be enabled when the Message Error Status Word bit is set by a 1553A RT or following a ”Status Set”condition.For a failed message, either one or two message retries will occur, the bus channel (same or alternate) is independently programmable for the first and sec-ond retry attempts.Retries may be enabled or disabled on an individual message basis.BC INTERRUPTSBC interrupts may be enabled by the Interrupt Mask Register for Stack Rollover, Retry, E nd-of-Message (global), E nd-of-Message (in conjunction with the BC Control Word for individual messages), response timeout, message error, end of BC frame,and Status Set conditions.The definition of “Status Set”is pro-grammable on an individual message basis, by means of the BC Control Word.This allows for masking (“care/don't care”) of the individual RT Status Word bits.REMOTE TERMINAL (RT) ARCHITECTUREThe RT protocol design of the BU-65170/61580 represents DDC's fifth generation implementation of a 1553 RT .One of the salient features of the ACE's RT architecture is its true multipro-tocol functionality.This includes programmable options for sup-port of MIL-STD-1553A, the various McAir protocols, and MIL-STD-1553B Notice 2.The BU-65170/61580 RT response time is 2 to 5 µs dead time (4 to 7 µs per 1553B), providing compliance to all the 1553 protocols.Additional multiprotocol features of the BU-65170/61580 include options for full software control of RT Status and Built-in-Test (BIT) words.Alternatively, for 1553B applications, these words may be formulated in real time by the BU-65170/61580 protocol logic.The BU-65170/61580 RT protocol design implements all the MIL-STD-1553B message formats and dual redundant modeFIGURE 3.BC MODE MEMORY MANAGEMENTcodes.This design is based largely on previous generation prod-ucts that have passed SEAFAC testing for MIL-STD-1553B com-pliance.The ACE RT performs comprehensive error checking,word and format validation, and checks for various RT -to-RT transfer errors.Other key features of the BU-65170/61580 RT include a set of interrupt conditions, internal command illegaliza-tion, and programmable busy by subaddress.RT MEMORY ORGANIZATIONTABLE 26 illustrates a typical memory map for the BU-61580 in RT mode.As in BC mode, the two Stack Pointers reside in fixed locations in the shared RAM address space:address 0100 (hex)for the Area A Stack Pointer and address 0104 for the Area B Stack Pointer.Besides the Stack Pointer, for RT mode there are several other areas of the ACE address space designated as fixed locations.All RT modes of operation require the Area A and Area B Lookup T ables.Also allocated are several fixed locations for optional features:Command Illegalization Lookup T able,Mode Code Selective Interrupt Table, Mode Code Data T able,and Busy Bit Lookup T able.It should be noted that any unen-abled optional fixed locations may be used for general purpose storage (data blocks).The RT Lookup tables, which provide a mechanism for mapping data blocks for individual Tx/Rx/Bcst-subaddresses to areas in the RAM, occupy address range locations are 0140 to 01BF for Area A and 01C0 to 023F for Area B.The RT lookup tables include Subaddress Control Words and the individual Data Block Pointers.If used, address range 0300-03FF will be dedicated as the illegalizing section of RAM.The actual Stack RAM area and the individual data blocks may be located in any of the nonfixed areas in the shared RAM address space.Data Device Corporation BU-65170/61580/61585BC-to-RT Transfer Control Word Receive Command WordData Word #1Data Word #2...Last Data WordLast Data Word Looped BackStatus Received Last Data Word...Data Word #2Data Word #1Status Received Transmit Command Looped BackTransmit Command Word Control Word RT-to-BC Transfer Transmit Command Looped Back Rx RT Status Word Last Data...Data #2Data #1Tx RT Status WordTransmit Command Receive Command Control Word RT-to-RT Transfer Mode Command Looped Back Status ReceivedMode Command Control Word Mode Code;No Data Mode Command Looped Back Data WordStatus Received Tx Mode Command Control Word Tx Mode Code;With Data Tx Command Looped Back Last Data...Data #2Data #1Tx RT Status WordTx Command Rx Broadcast CommandControl Word RT-to-RTs (Broadcast)TransferLast Data StatusWordLast Data ...Data #2Data #1Broadcast CommandControl Word Broadcast Data Word Data Word LoopedBackStatus ReceivedRx Mode CommandControl Word Rx Mode Code;With Data Broadcast Mode CommandLooped BackBroadcast Mode Command Control Word Broadcast Mode Code;No Data Data Word Looped BackData WordBroadcast Mode CommandControl Word Broadcast Mode Code;With Data FIGURE 4.BC MESSAGE BLOCK FORMATSRT MEMORY MANAGEMENTOne of the salient features of the ACE series products is the flex-ibility of its RT memory management architecture.The RT archi-tecture allows the memory management scheme for each trans-mit, receive, or broadcast subaddress to be programmable on a subaddress basis.Also, in compliance with MIL-STD-1553B Notice 2, the BU-65170/61580 provides an option to separate data received from broadcast messages from nonbroadcast received data.Besides supporting a global double buffering scheme (as in BC mode), the ACE RT provides a pair of 128-word Lookup T ables for memory management control.They are programmable on a subaddress basis (refer to T ABLE 27).These 128-word tables include 32-word tables for transmit message pointers and receive message pointers.There is also a third, optional Lookup Table for broadcast message pointers, providing Notice 2 com-pliance, if necessary.The fourth section of each of the RT Lookup T ables stores the 32Subaddress Control Words (refer to T ABLE 9 and 28).The indi-vidual Subaddress Control Words may be used to select the RT memory management option and interrupt scheme for each transmit, receive, and (optionally) broadcast subaddress.For each transmit subaddress, there are two possible memory management schemes:(1) single message;and (2) circular buffer.For each receive (and optionally broadcast) subaddress,there are three possible memory management schemes:(1) sin-gle message;(2) double buffered;and (3) circular buffer.For each transmit, receive and broadcast subaddress, there are two interrupt conditions that are programmable by the respective Subaddress Control Word:(1) after every message to the sub-address;(2) after a circular buffer rollover.An additional table in RAM may be used to enable interrupts following selected mode code messages.When using the circular buffer scheme for a given subaddress,the size of the circular buffer is programmable by three bits of the Subaddress Control Word (see T ABLE 28).The options for circu-lar buffer size are 128, 256, 512, 1024, 2048, 4096, and 8192Data Words.SINGLE MESSAGE MODEFIGURE 5 illustrates the RT Single Message memory manage-ment scheme.When operating the BU-65170/61580 in its “AIM-HY”(default) mode, the Single Message scheme is implemented for all transmit, receive, and broadcast subaddresses.In the Single Message mode (also in the Double Buffer and Circular Buffer modes), there is a global double buffering scheme, con-trolled by bit 13 of Configuration Register #1.This selects from between the two sets of the various data structures shown in the figure:the Stack Pointers (fixed addresses), Descriptor Stacks (user defined addresses), RT Lookup T ables (fixed addresses),and RT Data Word blocks (user defined addresses).FIGURES 5,6, and 7 delineate the “active”and “nonactive”areas by the non-shaded and shaded areas, respectively.As shown, the ACE stores the Command Word from each mes-sage received, in the fourth location within the message descrip-tor (in the stack) for the respective message.The T/R bit, subad-dress field, and (optionally) broadcast/own address, index into the active area Lookup T able, to locate the data block pointer for the current message.The BU-65170/61580 RT memory man-agement logic then accesses the data block pointer to locate the starting address for the Data Word block for the current mes-sage.The maximum size for an RT Data Word block is 32 words.。

61580中文手册_DDC_BU-61585

终端

ACE 系列终端为 1.9 平方英寸、70 个引脚、low-profile、cofired 的 • 灵活的处理器/存储器接口

多片模式(MCM)陶瓷封装片形式,能够很好地适用于具有很高要求的场合。 • 标准的 4K×16 以及可选的

BU-61585 ACE 集成了两个收发器、协议、存储器管理、处理器接口逻

陕西正鸿航科电子有限公司

表 1 “ACE”系列详细说明(续 3)

参数

最小

功耗(续)

全部混合器

■ BU-61585×2

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

· 100%发送器工作周期

■ BU-61585×3、BU-61585×6

· 空闲

· 25%发送器工作周期

· 50%发送器工作周期

■ (BU-65170/61580/61585×3、BU-65170/61580/61585×6)(注 1-7)

门限电压(变压器耦合、短截线上测得)

0.200

共模电压(注 7)

发送器

差分输出电压

■ 跨接 35Ω直接耦合、在总线上测得

6

■ 跨接 70Ω变压器耦合、在总线上测得

■ (BU-65170/61580/61585×1、BU-65170/61580/61585×2、×3、×6)

联系人:唐工 Tel:029-84288198、84288197

DDC BU-61580 中文手册

陕西正鸿航科电子有限公司

表 1 “ACE”系列详细说明(续 1)

参数

最小

逻辑(续)

IOH

■ DB15-DB0、A15-A0、MEMOE/ADDR-LAT、MEMWR/ZERO-WAIT、

基于FPGA和BU-65170的1553B远程终端设计与实现

基于FPGA和BU-65170的1553B远程终端设计与实现佚名【摘要】为了满足载荷与卫星进行可靠通信的目的,设计并实现了基于FPGA和BU⁃65170协议芯片的1553B远程终端。

自行设计了用于控制BU⁃65170的主控制状态机,采用16位零等待缓冲接口模式,使用单消息和双缓冲模式进行消息传输。

创新性地引入RS 422总线与1553B总线进行通信,方便测试过程,结果直观可见。

采用专用测试板卡Alta ECD54⁃1553对系统进行测试,获得预期的可靠结果。

FPGA取代传统CPU来控制1553B通信并集成数据传输功能,采用Verilog HDL硬件描述语言有利于软件移植,缩短研发周期,提高系统可靠性。

%In order to realize reliable communication between payload and satellite platform, a 1553B remote terminal was designed based on FPGA and BU⁃65170. A FSM was designed to control BU⁃65170. The 16⁃bit zero latency buffering interface mode and single message/double buffering mode are adopted to transmite messages. RS⁃422 is used to communicate with 1553B for the convenient testing. In the test, an exclusive testing card Alta ECD54⁃1553 was employed, and a correct result was ob⁃tained. All of the control and data processing functions are centralized in FPGA instead of CPU. Verilog HDL is used for soft⁃ware transportation, R&D cycle reduction and reliability improvement.【期刊名称】《现代电子技术》【年(卷),期】2013(000)014【总页数】5页(P65-69)【关键词】1553B;FPGA;BU-65170;RS 422【正文语种】中文【中图分类】TN911-34MIL-STD-1553B是美国于20世纪70年提出的一种用于战机的时分控制/命令响应式总线[1]。

YD4558 D类 2.1声道+3D环绕立体声数字音频功放

XZ-V1.0

Page 3

CRT ELECTRONIC TECHNOLOGY LIMITED

图目录

YD4558

ห้องสมุดไป่ตู้

图 1 YD4558 典型应用电路(上图标号对应TQFN4×4-28 封装) .................................................................... 6 图 2 TQFN4×4-28 封装管脚分配图(top view) ................................................................................................ 8 图 3 SOP-28 封装管脚分配图(top view) ......................................................................................................... 9 图 5 带通滤波器外围 ..................................................................................................................................... 15 图 6 二阶巴特沃斯有源低通滤波器 ............................................................................................................. 15 图 7 二阶巴特沃斯有源高通滤波器 ............................................................................................................. 16 图 8 一线脉冲时序图 ..................................................................................................................................... 16 图 9 输出端加磁珠应用图 ............................................................................................................................. 17 图 10 TQFN4×4-28 封装尺寸....................................................................................................................... 18 图11 SOP-28 封装尺寸 ................................................................................................................................ 19

超精确SLB615D POWERCELL 产品说明书

SLB615D POWERCELL ®Know What‘s AheadThe SLB615D POWERCELL ® is approved for use in various applications in Europe, Asia, America and almost everywhere else in the world. If an approval is required, the SLB615D POWERCELL ® already complies.Every SLB615D beam load cell features: • μP controlled accuracy • Robust output signal • 10V/m EMC protection• No junction box connections • OIML C3, C6, C10 accuracy • NTEP II M 5K, 10K accuracy • ATEX Zone 2/22 approvalsS L B 615D P O W E R C E L L®SLB615D POWERCELL ® Specifications2METTLER TOLEDO Data Sheet SLB615D POWERCELL ®©05/2020Parameter unit of measure SpecificationModel No.POWERCELL ® SLB615D (5)Rated Capacity (R.C.)kg (klb) nominal220 (500)550 (1250)1100 (2500)2200 (5000)4400 (10000)External resolution 220,000550,0001,100,0002,200,000440,000Min. Increment Size, typical4.4 (0.01)11 (0.025)22 (0.05)44 (0.1)88 (0.2)Zero load Output %R.C.<0.1Combined Error 1) 2)%R.C.C3/IIIM n:5: ≤0.018 ; C6/IIIM n:10: ≤ 0.012 ; C10: ≤0.007Repeatability Error %A.L.3)C3/IIIM n:5: ≤0.01 ; C6/IIIM n:10: ≤ 0.005 ; C10: ≤0.003Creep, 30 minute%A.L.C3/IIIM n:5: ≤0.017 ; C6/IIIM n:10: ≤ 0.008 ; C10: ≤0.005Min. Dead Load Output Retrun (DR), 30 min%A.L.C3/IIIM n:5: ≤0.017 ; C6/IIIM n:10: ≤ 0.008 ; C10: ≤0.005Temperature Effect onMin. Dead load%R.C./°C (../°F)0.0014 (0.0008)C3/IIIM n:5: ≤ 0.0011 (0.0006) / C6/IIIM n:10: ≤ 0.0007 (0.0004) / C10: ≤ 0.0007 (0.0004)Sensitivity 2)%A.L./°C (../°F)C3/IIIM n:5: ≤0.001(0.0006) ; C6/IIIM n:10: ≤ 0.0005(0.0003) ; C10: ≤0.0003(0.0002)Effective System Update Rate (4 load cells)Hz 40Temperature Range Compensated°C (°F)-10 to +40 (+14 to +104)Operating-20 to +65 (-4 to +150)Safe Storage-40 to +80 (-40 to +176)OIML / EuropeanApproval 4)European Cert. No.R60/2000-CN1-13.01 / NMi TC8489Class C3C6C10C3C6C10C3C6C10C3C6C10C3C6nmax 300060001000030006000100003000600010000300060001000030006000vming201037257050150100290250PLC0.8Humidity Symbol CH Min. dead load kgZ30006001000030006000100003000600010000300060001000030006000Barometric Pressure Effect None NTEP Approval 4)Number13-118Classlll M n:5lll M n:10-lll M n:5lll M n:10-lll M n:5lll M n:10-lll M n:5lll M n:10-lll M n:5lll M n:10nmax 5’00010000-5’00010’000-5’00010’000-5’00010’000-5’00010’000vminlb 0.050.0250.0950.0650.190.130.380.260.760.65Min. dead load lbATEX Approval 4)Number. cat. 2FM17ATEX0023RatingII 2 G Ex ib IIB T4 Gb / II 2 D Ex ib IIIC T130C Db / -40°C ≤ Ta ≤ +55°CEntity Parameters Ui = 8.4V, Ii = 100 mA, Pi = 0.84W, Ci = 5.3 uF, Li = 0 uH (7)Number. cat. 3DEKRA 14ATEX0030RatingII 3 G Ex nA IIC T6 Gc / II 3 D Ex tc IIIC T85°C Dc Entity Parameters Umax = 28V, Imax = 50mA, Pmax = 0.5W (7)IECEx Approval 4)Ex ib IIB T4 Gb / Ex ib IIIC T130°C Db / Ex nA IIC T6 Gc / Ex ec IIC T6 Gc / Ex tc IIIC T85°C DcFactory Manual Approval 4)Number, USA / Canada Division 1 FM17US0025 / FM17CA0013Rating, USA IS / I, II, III / 1 / CDEFG / T4 Ta = -40°C to 55°C ; I / 1 / AEx ib / IIB / T4 Ta = -40°C to 55°C / Gb ; 21 / AEx ib / IIIC / T130°C Ta =-40°C to 55°C / DbRating, CanadaIS / I, II, III / 1 / CDEFG / T4 Ta = -40°C to 55°C ; I / 1 / AEx ib / IIB / T4 Ta = -40°C to 55°C / Gb ; 21 / AEx ib / IIIC / T130°C Ta =-40°C to 55°C / DbEntity ParametersUi (Vmax) = 8.4V, Ii (Imax) = 100 mA, Pi = 0.84W, Ci = 5.3 uF, Li = 0 uHSystem Drawing no. USA30343371System Drawing no. Canada 30343371Number, USA / Canada Division 2FM17US0281 / FM17CA0143Rating, USA NI / I, II, III / 2 / ABCDFG / T6 -40°C ≤ Ta ≤ 55°C Rating, Canada NI / I, II, III / 2 / ABCDFG / T6 -40°C ≤ Ta ≤ 55°C Entity ParametersVmax = 13.5V, Imax = 1500mA, Ci = 4.8µF, Li = 4.05µHSystem Drawing no. USA 30095703System Drawing no. Canada30095703Insulation Resistance @50VDC MΩ≥ 2000Breakdown Voltage V AC ≥ 500Supply Voltage Non-regulatedRange (nominal)V DC 10 ~ 26Typical 12 / 24Supply Current MaxmA 130Typical20Overvoltage Protection Max. Tested A2000 (no outdoor lightning conditions)Warm-up Time from Cold Start 15CommunicationsController Area Network (CAN), EncryptedCan Open Effective System Update Rate (4 load cells)100ESD rating8Span Stability, typical (peak to peak in 1 min)15Immunity OIML R60V/m10MaterialSpring Element stainless steelEnclosure304 stainless steel, ElectropolishedConnectors stainless steel Cable Polyurethane (PU)ProtectionType welded IP Rating IP68, IP69K NEMA Rating NEMA 6/6POverload Protection yes NoLoad LimitSafe %R.C.150Ultimate300Safe Dynamic Load %R.C.100Fatigue Life**********.70Direction of Loading> 1,000,000**************.,nominalmm (in)0.16(0.006)0.25(0.01)0.32(0.013)0.43(0.017)0.72(0.028)SLB615D POWERCELL ® Dimensional Drawings mm [inch]3METTLER TOLEDO Data Sheet SLB615D POWERCELL ®©05/2020Notes:1. Dimensions are in mm [inches]CapacityDimensionsD D1D2`H H1H2H3H4H5L L1L2L3L4L5W 220/550/1100 kg [500/1250/2500 lb]13.0[0.51]22.2[0.87]15.9[0.63]30.2[1.19]0.38/0.38/0.51[0.015]/[0.015]/ 0.02]17.0[0.67]16.0[0.63] 4.7[0.19]7.7[0.30]134,4[5.29]57.7[2.27]1016[4.00]25,4[1.00]16,4[0.65] 6.4[0.25]32.7[129]2200 kg [5000 lb]13.0[0.51]22.2[0.87]15,9[0.63]36.6[1.44]4[0.158]22.9[0.90]20.3[0.80]9.5[0.37]12.7[0.50]136.7[5.38]57.9[2.28]1016[4.00]25.4[1.00]18,4[0.72]36.8[1.4514400 kg [10000 lb]19.3[0.76]34.9[137]22.2[0.87]42.9[1.69]2.3[0.091]29.3[1.15]22.6[0.90]11[0.43]17.4[0.69]171.5[6.75]73.8[2.91]133,3[5.25]38.1[150]21.5[0.85]42.9[169]1) Error due to the combined effect of non-linearity and hysteresis2)Typical values only. The sum of errors due to Combined Error and Temperature Effect on Sensitivity comply with the requirements of OIML R60 and NIST HB44.3)A.L. = Applied Load 4)See certificate for complete information.5)Max. 14 load cells / terminal 6)Max. total cable length 90-300m depending on no. of LC and Terminal.7)/ Load Cell 8)Calculate the scale’s minimum increment size by multiplying this value by the square root of the number of load cells. For non Legal-For-Trade ApplicationsParameter unit of measure SpecificationWeightkg (lb)1 (2.2) 1.3 (2.9) 2.2 (4.8)Cable Load Cell Cable 6)Polyurethane, 11mm Connector, 21mm Branch Housing (200mm Distance to LC), Req. Conduit ≥12mm (0.5''), Bend Radius ≥40mm (1.6'')Home-Run Cable 6)Polyurethane, 6mm Jacket, 21mm Branch Housing (200mm Distance to LC), 4 Conductors, Internal Shield with Drain Wires, Req.Conduit ≥12mm(0.5''), Bend Radius ≥ 40mm (1.6'')ConnectorsQuick-Connect Mounting ScrewGrade10.9 (Grade 8)Size/thread mm (in) M12 (1/2-13 UNC)M18x1,5 (3/4-10UNC)Torque, nominalNm (ft-lb)120 (100)275 (220)4METTLER TOLEDO Data Sheet SLB615D POWERCELL ®©05/2020SLB615D POWERCELL ® Foot Kit FTK mm [inch]SLB615D POWERCELL ® Expansion Kit EK mm [inch]Materials: Stainless steel, Polyethylene foamCapacity Dimensions and Locations L L1 L2 L3 H H1 H2 H3 Smax*220kg–1.1t ø50 34 M8 ø15 59.6 47.1 24 14 ±3mm [ø1.97] [1.34] [ø0.59] [2.35] [1.85] [0.94] [0.55] [±0.12]2.2t ø50 34 M8 ø15 63.5 52.3 24 14 ±3mm [ø1.97] [1.34] [ø0.59] [2.50] [2.06] [0.94] [0.55] [±0.12]4.4t ø60 45 M10 ø21.5 73.6 62.4 28 17 ±3mm [ø2.36] [1.77] [ø0.85] [2.90] [2.46] [1.10] [0.67] [±0.12]* Max lateral displacement5METTLER TOLEDO Data Sheet SLB615D POWERCELL ®©05/2020SLB615D POWERCELL ® Expansion + Vibration Kit EVK mm [inch]SLB615D POWERCELL ®Base Plate Kit BPK mm [inch]Capacity Dimensions and Locations L1 L2 L3 L4 L5 L6 L7 W1 W2 W3 W4220kg–1.1t 177.8 152.4 12.7 16.0 117.6 25.4 41.4 114.3 88.9 57.2 41.4 [7] [6] [0.5] [0.63] [4.63] [1] [1.63] [4.5] [3.5] [2.25] [1.63]2.2t 177.8 152.4 12.7 16.0 117.6 25.4 41.4 114.3 88.9 57.2 41.4 [7] [6] [0.5] [0.63] [4.63] [1] [1.63] [4.5] [3.5] [2.25] [1.63]4.4t 235.0 184.2 25.4 22.4 149.4 38.1 54.1 152.4 101.6 76.2 54.1 [9.25] [7.25] [1] [0.88] [5.88] [1.5] [2.13] [6] [4] [3] [2.13]Capacity Dimensions and Locations H1 H2 H3 H4 D1 D2 D3 MA cs MA ss 220kg–1.1t 70.2 62.0 19.1 12.7 M12 M16 11.2 136Nm 100Nm [2.76] [2.44] [0.75] [0.5] [0.44] [100 l b–ft] [75 l b–ft]2.2t 76.5 68.4 19.1 12.7 M12 M16 11.2 136Nm 100Nm [3.01] [2.96] [0.75] [0.5] [0.44] [100 l b–ft] [75 l b–ft]4.4t 99.6 87.4 25.4 19.1 M18 M18 17.5 340Nm 270Nm [3.92] [3.44] [1] [0.75] [0.69] [250 l b–ft] [200 l b–ft]1) Torque carbon steel version2) Torque steinless steel versionMaterials: Stainless steel or painted steelCapacity Dimensions and Locations D L L1 L2 L3 H H1 H2 H3 SHmax* SVmax**220kg–1.1t ø9 ø80 ø58 ø15 58 56.6 44.1 21.5 5 ±2.8mm 1 mm [ø0.35] [ø3.15] [ø2.28] [ø0.59] [2.28] [2.23] [1.74] [0.85] [0.20] [±0.11] [0.04]2.2t ø9 ø80 ø58 ø15 58 60.5 49.3 21.5 5 ±3mm 1.6mm [ø0.35] [ø3.15] [ø2.28] [ø0.59] [2.28] [2.38] [1.94] [0.85] [0.20] [±0.12] [0.07]4.4t ø11 ø100 ø72 ø21.5 76 75.6 64.4 30 10 ±3mm 2.2mm [ø0.43] [ø3.94] [ø2.83] [ø0.85] [2.99] [2.98] [2.54] [1.18] [0.39] [±0.12] [0.09]* Max lateral displacement ** Max vertical displacement incl. load cellMaterials: Stainless steel, NBR 70, Polyethylene foamMettler Toledo GmbH CH-8606 Greifensee SwitzerlandTel. +41 44 944 22 11Fax +41 44 944 30 60Subject to technical changes © 05/2020 Mettler-Toledo GmbH MarCom Switzerland MTSI 30242889For more informationWeighing ElectronicsMETTLER TOLEDO offers a complete family of electronics from simple weighing to application solutions for filling, stock control, batching, formulation, counting, checkweighing.Our extensive service network is among the best in the world and ensures maximum availability and service life of your product.SLB615D POWERCELL ® Order InformationRated CapacityItem No., Load CellItem No. , Options ClassBase Plate Kit BPK, CSBase Plate Kit BPK, 304Expansion Kit EKExpansion+Vibr Kit EVKFoot Kit FTKAdapter, ConduitC3/III M n:5C6/III M n:10C10220kg / 500lb 304503083045031130450314302653693026537072208662722086707220867430095581550kg/1.25klb 3045031730450320304503231100kg / 2500lb 3045032630450329304503322200kg / 5000lb 30450335304503383053963630265371302653724400kg / 10000lb3045034430450347-3026537330265374722086637220867172208675Bold entries are stockedSLB615D POWERCELL ® Order Information, CablesGlobal ApprovalsThe SLB615D is provided with all listed approvals. No need to think about options and additional charges. Simplifies the conduct of global business, order processing and service-part stocking.Colour Function Yellow Shield Blue CAN_L White CAN_H Red V+BlackV -SLB615D POWERCELL® Home Run CableOrder Information, Cables Item No.DescriptionCable, Material / LengthPU / 2.5m (8.2ft)PU / 5m (16.4ft)PU / 10m (32.8ft)PU / 15m (49.2ft)PU / 20m (65.6ft)PU / 30m (98.4ft)PU / 50m (164ft)PU / 100m (328ft)PU / 200m (656ft)Cable Kit, 3 Load Cells 303829943038299030382991------Cable Kit, 4 Load Cells 303829953038299230382993------Load Cell Y-Cable 303829753038297630382977------Home Run Cable -3038298030382981303829823038298330382984303829853038298630423113Extension Cable -3038298730382988-----CAN Termination 30382989Blind plug30417485Cable Gland forHome Run Cable with IND780PDX30095639Bold entries are stocked。

Tektronix P6158 20X Low Capacitance Probe说明书

20X Low Capacitance ProbeP6158 DatasheetP6158Notice to EU customersThis product is not updated to comply with the RoHS 2 Directive 2011/65/EU and will not be shipped to the EU. Customers may be able to purchase products from inventory that were placed on the EU market prior toJuly 22, 2017 until supplies are depleted. Tektronix is committed to helping you with your solution needs. Please contact your local salesrepresentative for further assistance or to determine if alternative product(s)are available. Tektronix will continue service to the end of worldwide support life.Features and benefits3 GHz Bandwidth1.5 pF Input Capacitance1 kΩ Input Resistance 22 V RMSMax. Input VoltageActivates 20X Readout in TEKPROBE ™Interface Instruments Compact Probe Tip Compatible with a Wide Range of Tektronix Accessories and AdaptersApplicationsHigh-speed device characterizationPropagation delays for ECL, CMOS and other logic circuitry anddevicesCircuit board impedance testing (TDR)High-speed sampling systemsP6158 DC to 3 GHzThe P6158 is a 3 GHz, 20X, low-capacitance probe. The P6158 is ideal for high-speed applications because of its ability to extend high-frequency response to 3 GHz. The BNC connector incorporates encoding to correct scale factors for 20X attenuation in oscilloscopes with TEKPROBE ® power supply interface. To facilitate SMD probing, the P6158 comes standard with SureFoot ® adapters. Additionally, the probe comes standard with an array of short ground leads that insert minimal inductance into the signal path of the measured waveform. The compact probe head/tip assembly iscompatible with the full line of 3.5 mm probe accessories. Designed for the TDS500/600/700/5000/6000/7000 Series oscilloscopes, the P6158 probe may also be used with 50 Ω 11000 Series plug-ins and the 11800 SeriesSD2X Sampling/TDR plug-ins with BNC to SMA Adapters.Recommended instrumentsTDS500/600/700/7000 Series11000 Series11800 SD2X Sampling/TDR plug-insTDS820/TDS8000/CSA8000/11801C/CSA803CFigure 1. P6158 Attenuation vs. frequency.Figure 2. P6158 Input impedance and phase.Figure 3. SF200A Series SureFoot ®adapters.Figure 4. Compact probe tip circuit board test points.Datasheet20X Low Capacitance Probe P6158SpecificationsAll specifications are guaranteed unless noted otherwise. All specifications apply to all models unless noted otherwise.Electrical CharacteristicsBandwidth (Probe only)DC to 3 GHz, -3 dBRise time>100 psAttenuation x20 (-26 dB)Attenuation accuracy±3%Input capacitance 1.5 pFInput resistance 1 kΩOutput termination Terminate into 50 ΩSignal delay 5 nsPhysical charactersiticsProb tip/head style 3.5 mm/CompactOutput cable length 1.2 m.Environmental charactersiticsOperating temperature-15 °C to +55 °C (+5 °F to +131 °F)High operating:55 °C @ 95 to 97% RHLow operating:30 °C @ 95 to 97% RHOrdering InformationModelsP6158 3 GHz Low Capacitance ProbeStandard accessories020-2232-00P6158 probe tip accessory kit204-1049-00 Attenuator tip cover; 2 ea. 50 mil, 25 mil (0.65 mm), and 0.5 mm SureFoot adapters 195-4240-00 2 in. ground lead343-1003-01ground collar016-1077-00 2 ea. ground tip contact, 5 lengths w/cover shell016-0633-00 2 ea. compact probe tip circuit board test points; 2 ea. marker set, various colors 071-0123-00Instruction manualRecommended replacement accessoriesSF201A SureFoot Adapter, Orange, 50 mil (12 ea.)SF202A SureFoot Adapter, Blue, 0.65 mm/25 mil (12 ea.)SF203SureFoot Adapter, Red, 0.50 mm/20 mil (12 ea.)131-5031-00Compact Probe Tip Circuit Board Test Points (25 ea.)Tektronix is registered to ISO 9001 and ISO 14001 by SRI Quality System Registrar. Datasheet20X Low Capacitance Probe P6158DatasheetASEAN / Australasia (65) 6356 3900 Austria 00800 2255 4835*Balkans, Israel, South Africa and other ISE Countries +41 52 675 3777 Belgium 00800 2255 4835*Brazil +55 (11) 3759 7627 Canada180****9200Central East Europe and the Baltics +41 52 675 3777 Central Europe & Greece +41 52 675 3777 Denmark +45 80 88 1401Finland +41 52 675 3777 France 00800 2255 4835*Germany 00800 2255 4835*Hong Kong 400 820 5835 India 000 800 650 1835 Italy 00800 2255 4835*Japan 81 (3) 6714 3086 Luxembourg +41 52 675 3777 Mexico, Central/South America & Caribbean 52 (55) 56 04 50 90Middle East, Asia, and North Africa +41 52 675 3777 The Netherlands 00800 2255 4835*Norway 800 16098People's Republic of China 400 820 5835 Poland +41 52 675 3777 Portugal 80 08 12370Republic of Korea +822 6917 5084, 822 6917 5080 Russia & CIS +7 (495) 6647564 South Africa +41 52 675 3777Spain 00800 2255 4835*Sweden 00800 2255 4835*Switzerland 00800 2255 4835*Taiwan 886 (2) 2656 6688 United Kingdom & Ireland 00800 2255 4835*USA180****9200* European toll-free number. If not accessible, call: +41 52 675 3777For Further Information. Tektronix maintains a comprehensive, constantly expanding collection of application notes, technical briefs and other resources to help engineers working on the cutting edge of technology. Please visit . Copyright © Tektronix, Inc. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specification andprice change privileges reserved. TEKTRONIX and TEK are registered trademarks of Tektronix, Inc. All other trade names referenced are the service marks, trademarks, or registered trademarks of their respective companies.24 Mar 2017 60W-12026-3 。

基于1553B总线的BU-61580芯片测试系统的设计与实现

基于1553B总线的BU-61580芯片测试系统的设计与实现张世兵;苗克坚【摘要】BU-61580芯片测试系统用于检测DDC公司的BU-61580系列芯片的总线协议功能和电气特性,筛选失效芯片,并具备芯片接口时序调整功能,可检验芯片在不同的接口环境和工作方式下的特殊表现.以Windows XP为开发平台,标准VC++为开发工具,针对该芯片设计一套测试系统.PCI总线接口的专用芯片测试卡能够方便的插入待测试的芯片,与之相应的测试系统能够设置芯片的访问时序,测试芯片工作于不同模式下的状态.实际应用表明,该测试系统具有测试界面灵活、简单、准确的特点,满足了用户的要求.%The aim of test system for the chip BU-61580 is to test the chips' protocol function and electrical specification, to select failed chips, to adjustment the chips' time sequence, to test the performance of chip on different interface element and work mode. In aid of Windows XP system and standard C++ language, a test system is designed and implement. The especial testing card, based on the interface of PCI, is convenient to put a chip on it And the test system can set time sequence of the chip, and test the status of chip on different working mode. The practice application shows that the test system has the features of flexible testing interfaces, simple, accurate to meet requires of users.【期刊名称】《电子设计工程》【年(卷),期】2013(021)003【总页数】5页(P85-89)【关键词】1553B;61580;BC;RT;BM;测试系统【作者】张世兵;苗克坚【作者单位】西北工业大学计算机学院,陕西西安710075;西北工业大学计算机学院,陕西西安710075【正文语种】中文【中图分类】TP277随着航空电子系统的发展,多路数据传输数据总线在航空电子系统中起着越来越重要的作用,其主要特点是集中控制、实时性要求高、分布处理[1]。

美国DDC公司1553协议芯片

美国DDC 公司1553协议芯片BU-65170/71 BU-61580/81/85/86BU-65178/79 BU-61588/BU-61688/89ACE 系列产品 典型封装: DIP4K,12K 或8K x17字的片内双口RAM 自动的BC 重试可编程的BC 间隔时间 BC 帧自动重试灵活的RT 数据缓存 可编程的非法化 可选的消息监控 RT/MT 同时操作方式Mini-ACE 和Mini-ACE+系列 典型封装: 扁平F 或G 功能兼容ACE 系列产品 自动的BC 重试可编程的BC 间隔时间 可编程的非法化4K 或64K 字的片内双口RAM 支持10/12/16/20 MHz 时钟 自动启动为RT 功能 单5V 电源供电BU-61864/65 BU-61845 BU-61843BU-62743 BU-62843 BU-62864PCI Enhanced Mini-ACE典型封装: 扁平F 或G 兼容ACE, Mini-ACE (+), Enhanced Mini-ACE 3.3V 逻辑RT 功能: 中断状态队列1/2环型缓冲区中断33 MHz 32-bit PCI 目标接口 4K 或64K 字片内双口RAM 10,12,16,20 MHZ 时钟Enhanced Mini-ACE 典型封装: 扁平F 或G 兼容ACE, Mini-ACE(+) 可选的5V 或3.3V 逻辑 综合的BIT 功能RT 功能: 中断状态队列 1/2环型缓冲区中断 4K 或64K 字片内双口RAM 10,12,16,20 MHZ 时钟常用的变压器器件: 1型: B2203 BUS25679 TST-9002 2型: B2385 BUS29854 TST-90013型: B3067B3226TST-9007。

DCU 6155-OP配置手册1

DCU 6155-OP配置手册前言用户指南本手册主要讲述如何通过命令行界面管理DCU 设备。

本手册尽量将系统的每一个功能的配置命令放在同一章,这样当您需要配置某种功能的时候,只需查看对应的章节即可。

对一些相互交错的功能的配置命令,如果不能放在一起,本手册会特别指明。

希望本手册能对您的工作有所帮助!读者对象●网络工程师●技术推广人员●网络管理人员●……适用范围适用于配置DCU6155-MPU204C-1GE1FE主控的DCU 6155-OP设备。

本书约定命令行关键字用加粗表示;命令行参数用斜体表示。

大括号“{ }”表示括号中的选项是必选的;中括号“[ ]”表示括号中的选项是可选的;尖括号“<>”表示括号中的信息不被显示出来;方括号“【】”表示括号中的内容需要用户注意;竖线“|”用于分隔若干选项,表示二选一或多选一;正斜线“/”用于分隔若干选项,表示被分隔的各选项是可以被同时选中的;“ 注意”表示需要读者注意的事项,是配置系统的关键之处,希望用户能认真阅读。

“ 注”表示对前面内容的注解;“ 图解”表示对图例的文字解释。

声明由于产品版本升级或其它原因,本手册内容会不定期进行更新。

除非另有约定,本手册仅作为使用指导,本手册中的所有陈述、信息和建议不构成任何明示或暗示的担保。

目录第1章系统基础--------------------------------------------------------------------------------------------------1 1.1 DCU设备配置方式 -------------------------------------------------------------------------------------------- 1 1.2 命令运行模式 -------------------------------------------------------------------------------------------------- 1 1.3 搭建配置环境 -------------------------------------------------------------------------------------------------- 31.3.1 通过配置口(Console)配置DCU设备---------------------------------------------------------------- 31.3.2 通过Telnet配置DCU设备 -------------------------------------------------------------------------------- 5 1.4 命令行接口 ----------------------------------------------------------------------------------------------------- 81.4.1 命令行在线帮助 ------------------------------------------------------------------------------------------ 81.4.2 命令行错误信息 ---------------------------------------------------------------------------------------- 121.4.3 历史命令 ------------------------------------------------------------------------------------------------ 121.4.4 编辑特性 ------------------------------------------------------------------------------------------------ 131.4.5 显示特性 ------------------------------------------------------------------------------------------------ 13第2章系统配置及管理------------------------------------------------ 12.1 系统配置------------------------------------------------------------------------------------------------ 12.1.1 配置系统名称------------------------------------------------------------------------------------ 12.1.2 配置系统日历------------------------------------------------------------------------------------ 22.1.3 配置系统用户------------------------------------------------------------------------------------ 22.1.4 enable密码和超时时间 -------------------------------------------------------------------------- 32.2 系统管理------------------------------------------------------------------------------------------------ 32.2.1 简介----------------------------------------------------------------------------------------------- 42.2.2 文件系统管理------------------------------------------------------------------------------------ 42.2.2.1 文件系统介绍 ---------------------------------------------------------------------------- 42.2.2.2 文件系统命令简介 ---------------------------------------------------------------------- 42.2.2.3 命令使用实例 ---------------------------------------------------------------------------- 52.2.2.4 目录管理-------------------------------------------------------------------------------- 172.2.3 DCU设备配置文件的管理 -------------------------------------------------------------------- 192.2.3.1 配置文件内容及格式------------------------------------------------------------------ 192.2.3.2 配置文件的加载 ----------------------------------------------------------------------- 242.2.3.3 保存系统当前配置 -------------------------------------------------------------------- 242.2.3.4 查看DCU设备当前运行的配置 ------------------------------------------------------ 25 2.3 系统认证和命令分级授权管理 -------------------------------------------------------------------- 252.3.1 简介--------------------------------------------------------------------------------------------- 252.3.2 基本指令描述---------------------------------------------------------------------------------- 262.3.3 修改用户的级别------------------------------------------------------------------------------- 262.3.4 修改命令的级别------------------------------------------------------------------------------- 282.3.5 设置enable密码-------------------------------------------------------------------------------- 292.3.6 配置用户及其相关属性 ---------------------------------------------------------------------- 292.3.7 设置line属性 ----------------------------------------------------------------------------------- 302.3.8 查看当前用户级别 ---------------------------------------------------------------------------- 32 2.4 系统工具---------------------------------------------------------------------------------------------- 322.4.1 show命令---------------------------------------------------------------------------------------- 322.4.2 网络排错工具---------------------------------------------------------------------------------- 432.4.3 系统日志功能---------------------------------------------------------------------------------- 432.4.4 查看cpu利用率 -------------------------------------------------------------------------------- 45 2.5 系统远程登录服务 ---------------------------------------------------------------------------------- 462.5.1 telnet --------------------------------------------------------------------------------------------- 462.5.2 SSH ---------------------------------------------------------------------------------------------- 46 2.6 系统软件的升级 ------------------------------------------------------------------------------------- 47 2.7系统SNMP管理 ---------------------------------------------------------------------------------------- 472.7.1 SNMP简介 -------------------------------------------------------------------------------------- 472.7.2 SNMP基本指令描述--------------------------------------------------------------------------- 472.7.3 SNMP代理服务器配置详解 ------------------------------------------------------------------ 47第3章 DCU配置------------------------------------------------------ 13.1 DCU简介 ----------------------------------------------------------------------------------------------- 13.2 DCU配置命令描述 ------------------------------------------------------------------------------------ 13.2.1 配置CE1 ------------------------------------------------------------------------------------------ 13.2.2 配置CPOS ---------------------------------------------------------------------------------------- 23.2.3 配置虚拟以太接口 ------------------------------------------------------------------------------ 63.2.4 配置环网 ----------------------------------------------------------------------------------------- 83.2.5 查看与保存配置--------------------------------------------------------------------------------- 83.3 DCU配置示例------------------------------------------------------------------------------------------ 8 3.3.1.1环网配置 --------------------------------------------------------------------------------------------------------------------------93.4 DCU的监测 ------------------------------------------------------------------------------------------ 10 第4章软件升级----------------------------------------------------- 14.1 ROOT程序的升级 ------------------------------------------------------------------------------------- 14.1.1 通过Console接口升级Monitor程序的hex文件 ----------------------------------------------- 14.2 应用程序(IOS)的升级 ----------------------------------------------------------------------------- 24.2.1 通过TFTP/FTP方式升级应用程序的bin文件 ------------------------------------------------ 24.2.2 通过Console接口升级应用程序的bin文件 --------------------------------------------------- 44.2.3 通过Console接口升级应用程序的hex文件--------------------------------------------------- 54.3 文件系统擦除 ------------------------------------------------------------------------------------------ 5第5章网络测试和故障诊断-------------------------------------------- 15.1 网络测试工具 ------------------------------------------------------------------------------------------ 15.1.1 ping命令和groupping命令——测试网络连通性及目标的可达性-------------------------- 15.1.2 traceroute命令--测试数据包的路由信息------------------------------------------------------- 45.1.3 netstat命令——查看各个网络接口的状态及详细的统计信息 ----------------------------- 75.1.4 show命令——查看系统统计信息、系统状态------------------------------------------------ 75.2 如何诊断网络故障 ------------------------------------------------------------------------------------ 85.2.1 诊断局域网口的故障 --------------------------------------------------------------------------- 8 5.2.2 诊断广域网口的故障 ------------------------------------------------------------------------- 10。