FPGA starter开发板原理图

FPGA 开发板原理图 EP1C3T144C8

2

U1

1 2 3

A1 A2 A3

VCC

7 4

SCL WP SDA GND

AT24C16

8 +3.3V

6 AT24_SCL 5 AT24_SDA

A

+3.3V R2 4.7K

+3.3V R3 4.7K

AT 24 _SCL AT 24 _SD A

3

4

5

6

7

8

D1 LED1

D2

R5

LED

LED2

D3 LED

GND GND

22 23

MSEL 0 MSEL 1

nCE

21 20

nCE n CE O

U3D EP1C3T144C8

16 17

16 17

CLK0, LVDS CLK1p CLK1, LVDS CLK1n

CLK2, LVDS CLK2p CLK3, LVDS CLK2n

93 CLKIN 92 92

VDDA_1.2V +1.2V

EP1C3T144C8 U3B

+3.3V

DATA 13

TDI 95 TDO 90 TCK 88 TMS 89

DATA0

TDI TDO TCK TMS

DCLK CONF_DONE

nCONFIG nSTATUS

24 86 14 87

DCL K nCONF_DOWN nCONFIG nSTATUS

R11 4.7K

6 8

9 C3

12 C4

72 UART_RXD0 72

71

71

70 UART_TXD0 70

69

69

68

EP1C3T144 FPGA develop board manual(开发板原理图)

FPGA develop board manual ALTERA Cyclone EP1C3T144ALTERA Cyclone 系列的fpga是altera 公司针对底端用户推出的一个系列的fpga。

具有成本低,使用的方便的优点,规模从3000到20000LE。

这一块实验板用的EP1C3T144的芯片,有3000LE逻辑资源,另外还有13条M4K RAM (共6.5Kbyte),另外还有还有一个数字锁相环。

这些资源能够足够应付电子设计竞赛和日常教学的需要,也可以作为初学者入门学习fpga的工具。

1. 开发板介绍1.1. 总体介绍开发板的电路图,如附录所示,电路图一共可分为9个部分:电源部分、按键和LED、下载配置部分、复位部分、外部时钟、滤波电容、用户扩展接口、5 1单片机接口、FPGA 芯片。

1.2. 具体介绍1.2.1. 电源部分板子由外部提供5V电源,使用的圆头插座的封装,可以直接用5V的电源适配器插上使用,不需要直流稳压电源,FPGA的IO的电源是3.3V,内核的电压是1.5V,所以用上两个LEO,一个将5V转到3.3V,另一个将3.3V转到1.5V,加上一些滤波电容,板上的其他外设的电源均是3.3V,另外有3.3V的电源指示灯,表示电源是否正常,还有防反插二极管,防止电源反插,对器件造成损坏。

1.2.2. 按键和LED板上提供4个拨码按键和4个led,分别接到fpga的8个IO引脚上,具体的引脚可以参看电路图或者丝印。

对于初学者,按键和led可以用外当成最简单的外设,用和来控制这些外设。

对于用该板作开发的用户来说,可以把按键当成键盘控制,而把led当成提示来用。

1.2.3. 下载配置部分大家都知道fpga是sram型的可编程逻辑器件,不像rom型可编程器件cpld那样,通过jtag就可以直接把代码固化片子里面。

Fpga随便也可以通过jtag下载代码到片子里面运行。

Fpga下载到片子里面代码是存放在ram里,所以断电后这些代码马上就没有了。

FPGA的基本原理ppt课件

4、 按可重复编程性分:

l 一次性编程的FPGA: 这种FPGA只能编程一次, 如逆熔丝型FPGA就是一次性编程的FPGA。

l

可重复编程的FPGA:这种FPGA可以反复编程,

如基于RAM的FPGA和FLASH型FPGA都可反复编程。

最新版整理ppt

5

(四)、FPGA的优点

和其它类型的ASIC相比,FPGA具有以下优点: l 不需要初始投资 l 不要提前制造 l 无库存风险 l 模拟工作费时较少 l 适合样品试制和小批量生产

14

五、 FPGA内部布线资源

分段连接线,分段连线的两端为编程单元, 通过对编程单元的编程来决定两个分段 连线是否连接。

最新版整理ppt

15

六、 FPGA内部编程单元

1、 逆熔丝开关

逆熔丝开关的功能和熔丝开关正好相反,当加上编程电压后两 端相连(电阻很小〈1kΩ〉,且为永久性连接;不编程时两端电阻 很 大 ( >100MΩ ) 。 市 场 上 有 两 种 类 型 的 逆 熔 丝 开 关 , 分 别 是 ACTEL公司的多晶硅- 扩散逆熔丝和QuickLogic公司的金属-金属逆 熔丝(ViaLinkTM)。

2) CPLD延时可预测(Predictable),FPGA的延时与布局布线情况 有关。

3) CPLD 组合逻辑多而触发器较少,而FPGA触发器多。

最新版整理ppt

3

(三)、 FPGA的分类

1、 按可编程逻辑模块大小分:

l 细粒度型(fine-grain):内部可编程模块较小的FPGA, 如Actel公司的FPGA。

最新版整理ppt

23

十三、FPGA的利用率

l 模块利用率

模块利用率=所用模块数/FPGA总的模块数

EP1C3T144FPGAdevelopboardmanual(开发板原理图)

EP1C3T144FPGAdevelopboardmanual(开发板原理图)FPGA develop board manual ALTERA Cyclone EP1C3T144ALTERA Cyclone 系列的fpga是altera 公司针对底端用户推出的一个系列的fpga。

具有成本低,使用的方便的优点,规模从3000到20000LE。

这一块实验板用的EP1C3T144的芯片,有3000LE逻辑资源,另外还有13条M4K RAM (共6.5Kbyte),另外还有还有一个数字锁相环。

这些资源能够足够应付电子设计竞赛和日常教学的需要,也可以作为初学者入门学习fpga的工具。

1. 开发板介绍1.1. 总体介绍开发板的电路图,如附录所示,电路图一共可分为9个部分:电源部分、按键和LED、下载配置部分、复位部分、外部时钟、滤波电容、用户扩展接口、5 1单片机接口、FPGA 芯片。

1.2. 具体介绍1.2.1. 电源部分板子由外部提供5V电源,使用的圆头插座的封装,可以直接用5V的电源适配器插上使用,不需要直流稳压电源,FPGA的IO的电源是3.3V,内核的电压是1.5V,所以用上两个LEO,一个将5V转到3.3V,另一个将3.3V转到1.5V,加上一些滤波电容,板上的其他外设的电源均是3.3V,另外有3.3V的电源指示灯,表示电源是否正常,还有防反插二极管,防止电源反插,对器件造成损坏。

1.2.2. 按键和LED板上提供4个拨码按键和4个led,分别接到fpga的8个IO引脚上,具体的引脚可以参看电路图或者丝印。

对于初学者,按键和led 可以用外当成最简单的外设,用和来控制这些外设。

对于用该板作开发的用户来说,可以把按键当成键盘控制,而把led当成提示来用。

1.2.3. 下载配置部分大家都知道fpga是sram型的可编程逻辑器件,不像rom型可编程器件cpld那样,通过jtag就可以直接把代码固化片子里面。

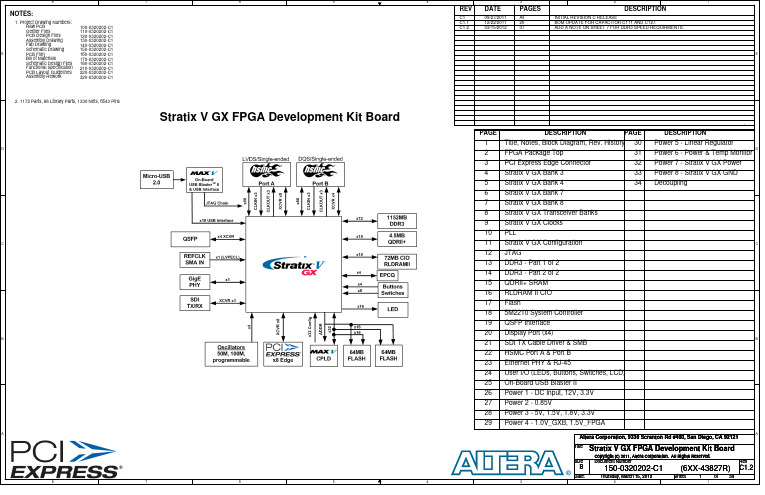

Stratix V GX FPGA开发板电路图

8 8 8 8

C

8 8

8 8 8 8 8 8 8 8

PCIE_TX_CP4 PCIE_TX_CN4 PCIE_TX_CP5 PCIE_TX_CN5 PCIE_TX_CP6 PCIE_TX_CN6 PCIE_TX_CP7 PCIE_TX_CN7

0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

REV

C1 C1.1 C1.2

DATE

09/27/2011 12/22/2011 03/15/2012

PAGES

All 26 07

DESCRIPTION

INITIAL REVISION C RELEASE BOM UPDATE FOR CAPACITOR C111 AND C127. ADD A NOTE ON SHEET 7 FOR DDR3 SPEED REQUIRMENTS.

HSMC Port B x2 (of 4 XCVRS) DisplayPort (x4)

XCVR BANK QR3

QSFP SDI

C

C

XCVR BANKS QR0, QR1

HSMC Port A x8 HSMC Port B x2 (of 4 XCVRS)

XCVR BANKS QR0, QR2

PCI Express x8

3.3V_PCIE

A

C74 0.1uF PCI BRACKET

C75 0.1uF

C76 0.1uF

C584 0.1uF

C585 0.1uF

C582 0.1uF

C583 0.1uF

C77 0.1uF

Altera Corporation, 9330 Scranton Rd #400, San Diego, CA 92121

FPGA实验教程_原理图设计部分

实验注意事项1.做实验前,先连接好下载线,然后才能接上电源。

2.做完实验后,先拨掉实验箱上的电源,然后才能拨下载线。

实验一:简单逻辑门实验目的:掌握Quartus使用及基于原理框图进行FPGA开发的基本流程实验要求:掌握Quartus使用及基于原理框图进行FPGA开发的基本流程,注意设备及人身安全,严禁带电插拔JTAG下载线,防止损坏设备所需器材:FPGA教学实验系统,带并口的普通计算机实验介绍:本实验是在FPGA教学实验系统上实现简单的逻辑门,例如2输入的与门、与非门、或门、异或门等,对应部分的电路原理图如图1所示。

当K0(K1)按键断开时,FPGA引脚175(173)的输入为低电平,对应发光二极管D2(D3)熄灭,当K0(K1)按键按下时,FPGA引脚175(173)的输入为高电平,对应发光二极管D2(D3)发光。

FPGA引脚175、173在本实验中可用作输入引脚。

FPGA引脚64、65、66、73分别接有发光二极管(LED)DR0~DR3,在实验中可用作输出引脚,当引脚输出高电平时,对应的LED被驱动发光。

这些输出引脚可用于实现2个输入的不同逻辑功能。

图1 部分按键与LED的原理图实验步骤:1. 为工程建立工作目录为了方便工程涉及到的文件的管理,以后的每一个工程,都需要为其建立专门的工作目录,目录路径中不要包含有非英文或数字的字符(例如不要包含空格或中文字符等)。

请利用系统自带的“我的电脑”或“资源管理器”建立目录。

在此假设在E:\work目录下建立名为mylogic_sch的工程工作目录,其目录路径为E:\work\mylogic_sch,本实验所涉及的文件都需要放置在该目录当中。

2. 运行Quartus II程序方法1(通过开始菜单):开始->程序(P)->Altera->Quartus II 7.2->Quartus II 7.2 (32-Bit)方法2(桌面快捷方式):双击桌面的快捷方式图标打开Quartus II后,其界面如图2所示。

FPGA原理图方式设计流程图

2 Quartus II软件的使用、开发板的使用本章将通过3个完整的例子,一步一步的手把手的方式完成设计。

完成这3个设计,并得到正确的结果,将会快速、有效的掌握在Altera QuartusII软件环境下进行FPGA设计与开发的方法、流程,并熟悉开发板的使用。

2.1 原理图方式设计3-8译码器一、设计目的1、通过设计一个3-8译码器,掌握祝组合逻辑电路设计的方法。

2、初步了解QuartusII采用原理图方式进行设计的流程。

3、初步掌握FPGA开发的流程以及基本的设计方法、基本的仿真分析方法。

二、设计原理三、设计容四、设计步骤1、建立工程文件1)双击桌面上的Quartus II的图标运行此软件。

开始界面2)选择File下拉菜单中的New Project Wizard,新建一个工程。

如图所示。

新建工程向导3)点击图中的next进入工作目录。

新建工程对话框4)第一个输入框为工程目录输入框,用来指定工程存放路径,建议可根据自己需要更改路径,若直接使用默认路径,可能造成默认目录下存放多个工程文件影响自己的设计,本步骤结束后系统会有提示(当然你可不必理会,不会出现错误的)。

第二个输入框为工程名称输入框。

第三个输入框为顶层实体名称输入框,一般情况下保证工程名称与顶层实体名称相同。

设定完成后点击next。

指定工程路径、名称5)设计中需要包含的其它设计文件,在此对话框中不做任何修改,直接点击next。

工程所需其它文件对话框6)在弹出的对话框中进行器件的选择。

在Device Family框中选用Cyclone II,然后在Available device框中选择EP2C35F484C8,点击next进入下一步。

器件选择界面7)下面的对话框提示可以勾选其它的第三方EDA设计、仿真的工具,暂时不作任何选择,在对话框中按默认选项,点击next。

第三方EDA工具选择8)出现新建工程以前所有的设定信息后,点击finish完成新建工程的建立。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

I2C主主EEPROM接接电电

C45 104 C46 104 U5 1 2 3 4 GND A0 A1 A2 GND AT24C01 VCC WP SCL SDA 8 7 6 5 VCCIO R22 2.2K R23 2.2K I2C_SCL I2C_SDA FPGA PIN 20 FPGA PIN 21

VCCIO R9 10k R8 10k R7 10k JTAG TCKI TDO TMS TDI 1 3 5 7 9 JTAG 2 4 6 8 10 GND VCCIO GND

AS(主主主主主主)接接电电

nSTATUS U1 nCS DATA VCCIO GND 1 2 3 4 nCS Vcc DATA Vcc Vcc DCLK GND ASDI EPCS1 8 7 6 5 VCCIO VCCIO DCLK ASDI VCCIO R6 R5 10k DCLK nCONFIG_DONE nCONFIG 10k DATA ASDI

RA6 1 2 3 4

RESPACK3 8 7 6 5 RESPACK3

KEY3 KEY2 SW0 SW1 GND VCCIO GND VCCINT SW2 SW3 KEY1 SW4 SW5 SW6 SW7 KEY0 RESET GND VCCINT GND VCCIO BEEP GPIO11 GPIO12 GPIO9

FPGA主主主电电

SEG_SEL7 SEG_SEL6 SEG_SEL5 SEG_SEL4 GND VCCIO GND VCCINT SEG_C SEG_DP SEG_D SEG_E LED7 LED6 LED5 LED4 GND VCCINT GND VCCIO LED3 LED2 LED1 LED0

R11 10k AS 1 3 5 7 9 2 4 6 8 10

SPI主主EEPROM接接电电

VCCIO U6 GND VCCIO nCE nCS GND R10 10k FPGA PIN 22 FPGA PIN 23 FPGA PIN 24 FPGA PIN 25 SPI_CS SPI_CLK SPI_DI SPI_DO 1 2 3 4 CS CLK DI DO R20 10K 93C06 VCC NC NC GND 8 7 6 5 GND VCCIO VCCIO

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76

U8 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 SEG_SEL0 SEG_SEL1 SEG_SEL2 SEG_SEL3 SEG_A SEG_F SEG_G SEG_B TDI GPIO1 GPIO2 TDO TMS TCK nSTATUS nCONF_DONE VCCIO GND GPIO4 GPIO3 GPIO6 GPIO5 GPIO8 GPIO7 GPIO10

FPGA PIN 85

LED4

R4 680

FPGA PIN 86

LED5

R5 680

FPGA PIN 87

LED6

R6 680

FPGA PIN 88

LED7

R7 680

拨拨拨拨电电

VCCIO GND RA6 1 2 3 4 8 7 6 5 SW0 SW1 SW2 SW3 R31 51 S2 FPGA PIN 28 FPGA PIN 29 FPGA PIN 34 FPGA PIN 35 FPGA PIN 37 FPGA PIN 38 FPGA PIN 39 FPGA PIN 40 SW0 SW1 SW2 SW3 SW4 SW5 SW6 SW7 1 2 3 4 5 6 7 8 SW-DIP8 16 15 14 13 12 11 10 9 GND

IO IO IO IO IO IO/nCSO DATA0 nCONFIG VCCA_PLL1 CLK0 GNDA_PLL1 nCEO nCE MSEL0 MSEL1 DCLK IO/ASDO VCCIO1 GND IO IO IO IO IO IO

IO IO IO IO/DPCLK4 IO IO IO IO TDI CLK2 IO TDO TMS TCK nSTATUS CONF_DONE VCCIO3 GND IO IO IO IO IO IO IO

a g d b f c dp e

a g d b c dp

IO IO IO IO GND VCCIO4 GND VCCINT IO/DPCLK7 IO IO IO IO IO IO IO IO/DPCLK6 GND VCCINT GND VCCIO4 IO IO IO IO

FPGA_CTS 1 FPGA_RTS 2 FPGA_TXD 3 FPGA_RXD 4 5 nCS 6 DATA 7 nCONFIG 8 VCCINT 9 FPGA_CLK 10 GND 11 12 nCEO 13 nCE GND 14 GND 15 DCLK 16 ASDI 17 VCCIO 18 GND 19 I2C_SCL 20 I2C_SDA 21 SPI_CS 22 SPI_CLK 23 SPI_DI 24 SPI_DO 25

FPGA PIN 36

KEY1

KEY1

RESPACK3 C GND RA6 1 2 3 4 8 7 6 5 SW4 SW5 SW6 SW7

RESPACK3 FPGA PIN 27 KEY2 KEY2 R26 10K 104CRESPACK3

FPGA PIN 26

KEY3

KEY3

GND

10K

GND

JTAG接接电电

IO IO IO IO GND VCCIO GND VCCINT IO/DPCLK2 IO IO IO IO IO IO IO IO/DPCLK3 GND VCCINT GND VCCIO2 IO IO IO IO

SEG_SEL4 RA6 1 SEG_SEL5 2 SEG_SEL6 3 SEG_SEL7 4

B

B

Q1 8550

Q2 8550

Q3 8550

Q4 8550

Q5 8550

Q6 8550

Q7 8550

Q8 8550

DS2

DS1

a f e g d b f c dp e

a g d b f c dp e

a g d b f c e dp

a g d b c dp f e

a g d b f c dp e

a g d b f c dp e

KEY按按电电

RESET按按电电

脉脉脉脉脉电电

BEEP

扩扩IO电电

RA6 1 2 3 4

FPGA PIN 41 8 7 6 5 KEY0 KEY1 KEY2 KEY3

KEY0

KEY0

VCCIO RESET VCCIO

VCC50 GPIO1可可可 可可可可 可 FPGA PIN 42 RESET R25 4.7K C45 FPGA PIN 47 BEEP R19 2.2K R106 Q1 8050 GPIO FPGA PIN 66 FPGA PIN 56 FPGA PIN 54 FPGA PIN 52 FPGA PIN 50 FPGA PIN 48 GPIO1 GPIO3 GPIO5 GPIO7 GPIO9 GPIO11 VCCIO GND 1 3 5 7 9 11 13 15 2 4 6 8 10 12 14 16 GPIO2 GPIO4 GPIO6 GPIO8 GPIO10 GPIO12 VCCIO GND FPGA PIN 65 FPGA PIN 57 FPGA PIN 55 FPGA PIN 53 FPGA PIN 51 FPGA PIN 49

6 8 9 12

s1 s2 s3 s4

a b c d e f g dp

a b c d e f g dp

s1 s2 s3 s4

6 8 9 12

11 7 4 2 1 10 5 3

A

FPGA PIN 89 FPGA PIN 70 FPGA PIN 69 FPGA PIN 91

SEG_E SEG_F SEG_G SEG_DP

FPGA PIN 71 FPGA PIN 68 FPGA PIN 92 FPGA PIN 90

SEG_A SEG_B SEG_C SEG_D

RA6 1 2 3 4

11 7 4 2 1 10 5 3

EP1C3T100 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 A

有电有有电电

L1 47uH U9 1 2 GND VCC GND 50MHZ VCC F_OUT 4 3 104 R16 100 FPGA_CLK FPGA PIN 10 VCCIO C41 C43 104 GND

主动7段段拨段段段电电

FPGA PIN 75 FPGA PIN 72 FPGA PIN 73 FPGA PIN 74 FPGA PIN 97 FPGA PIN 98 FPGA PIN 99 FPGA PIN 100 SEG_SEL0 SEG_SEL1 SEG_SEL2 SEG_SEL3 RA6 1 2 3 4 8 7 6 5 RESPACK3 8 7 6 5 RESPACK3 VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO VCCIO

FPGA PIN 76

LED0

R0 680

RS232接接电电

FPGA PIN 77 LED1 FPGA PIN 78 J1 1 6 2 7 3 8 4 9 5 FPGA PIN 79 LED3 LED2

R1 680 R2 680 R3 680

LM1117-1.5v 1