Exception Handling in Embedded Systems--Cortex-M0 & 68000

嵌入式系统简介和组成部分说明书

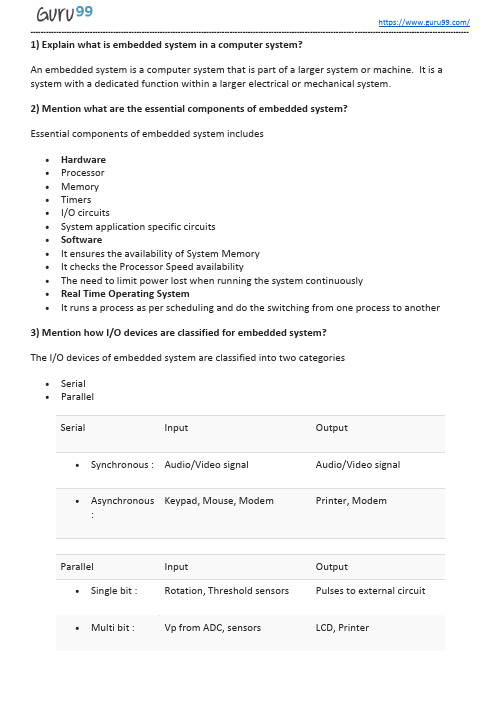

1) Explain what is embedded system in a computer system?An embedded system is a computer system that is part of a larger system or machine. It is a system with a dedicated function within a larger electrical or mechanical system.2) Mention what are the essential components of embedded system?Essential components of embedded system includes•Hardware•Processor•Memory•Timers•I/O circuits•System application specific circuits•Software•It ensures the availability of System Memory•It checks the Processor Speed availability•The need to limit power lost when running the system continuously•Real Time Operating System•It runs a process as per scheduling and do the switching from one process to another 3) Mention how I/O devices are classified for embedded system?The I/O devices of embedded system are classified into two categories•Serial•Parallel•Synchronous : Audio/Video signal Audio/Video signal•Single bit : Rotation, Threshold sensors Pulses to external circuit•Multi bit : Vp from ADC, sensors LCD, Printer4) Why embedded system is useful?With embedded system, it is possible to replace dozens or even more of hardware logic gates, input buffers, timing circuits, output drivers, etc. with a relatively cheap microprocessor.5) Explain what are real-time embedded systems?Real-time embedded systems are computer systems that monitor, respond or control an external environment. This environment is connected to the computer system through actuators, sensors, and other input-output interfaces.6) Explain what is microcontroller?The microcontroller is a self-contained system with peripherals, memory and a processor that can be used as embedded system.7) Mention what is the difference between microprocessor and microcontroller? Microprocessor is managers of the resources (I/O, memory) which lie outside of its architecture Microcontroller have I/O, memory, etc. built into it and specifically designed for control8) What does DMA address will deal with?DMA address deals with physical addresses. It is a device which directly drives the data and address bus during data transfer. So, it is purely physical address.9) Explain what is interrupt latency? How can you reduce it?Interrupt latency is a time taken to return from the interrupt service routine post handling a specific interrupt. By writing minor ISR routines, interrupt latency can be reduced.10) Mention what are buses used for communication in embedded system?For embedded system, the buses used for communication includes•I2C: It is used for communication between multiple ICs•CAN: It is used in automobiles with centrally controlled network•USB: It is used for communication between CPU and devices like mouse, etc.While ISA, EISA, PCI are standard buses for parallel communication used in PCs, computer network devices, etc.11) List out various uses of timers in embedded system?Timers in embedded system are used in multiple ways•Real Time Clock (RTC) for the system•Initiating an event after a preset time delay•Initiating an even after a comparison of preset times•Capturing the count value in timer on an event•Between two events finding the time interval•Time slicing for various tasks•Time division multiplexing•Scheduling of various tasks in RTOS12) Explain what is a Watchdog Timer?A watchdog timer is an electronic device or electronic card that execute specific operation after certain time period if something goes wrong with an electronic system.13) Explain what is the need for an infinite loop in embedded systems?Embedded systems require infinite loops for repeatedly processing or monitoring the state of the program. For instance, the case of a program state continuously being verified for any exceptional errors that might just happen during run-time such as memory outage or divide by zero, etc.14) List out some of the commonly found errors in Embedded Systems?Some of the commonly found errors in embedded systems are•Damage of memory devices static discharges and transient current•Address line malfunctioning due to a short in circuit•Data lines malfunctioning•Due to garbage or errors some memory locations being inaccessible in storage•Inappropriate insertion of memory devices into the memory slots•Wrong control signals15) Explain what is semaphore?A semaphore is an abstract datatype or variable that is used for controlling access, by multiple processes to a common resource in a concurrent system such as multiprogramming operating system. Semaphores are commonly used for two purposes•To share a common memory space•To share access to files16) Explain what is the difference between mutexes and semaphores?• A mutex object enables one thread into a controlled section, forcing other threads which tries to gain access to that section to wait until the first thread has movedout from that section •Semaphore allowsmultiple access to sharedresources•Mutex will always have a known owner •While for semaphore youwon’t know which threadwe are blocking on•Mutex is also a tool that is used to provide deadlock-free mutual exclusion (eitherconsumer or producer can have the keyand proceed with their work) •Semaphore is asynchronization tool toovercome the criticalsection problem•Mutexes by definition are binary semaphores, so there are two states locked or unlocked •Semaphores are usually referred to counted locks17) When one must use recursion function? Mention what happens when recursion functions are declared inline?Recursion function can be used when you are aware of the number of recursive calls is not excessive. Inline functions property says whenever it will called, it will copy the complete definition of that function. Recursive function declared as inline creates the burden on the compilers execution.18) Explain whether we can use semaphore or mutex or spinlock in interrupt context in Linux Kernel?Semaphore or Mutex cannot be used for interrupt context in Linux Kernel. While spinlocks can be used for locking in interrupt context.Guru99 Provides FREE ONLINE TUTORIAL on Various courses likeSelenium CCNA AngularJS NodeJS PLSQL。

BIEE_常见问题解答

Oracle Business Intelligence Enterprise Edition 10g项目实施问题解答汇总2008年4月10日目录:仪表板: (4)仪表板分组下拉显示: (4)设置默认的仪表板: (7)撤销页面“刷新“按钮(不建议) (8)如何跳过注销页面,直接跳转到登陆界面 (9)交叉表行数限制 (9)报表显示上的列级别控制 (10)报表中现实自己有权限访问的第一个列 (10)登录界面“版权所有“信息客户化 (10)仪表盘顺序定制 (10)时间细度不一样 (11)Prompt值显示的顺序定制: (11)表格下的“125-”是1到25条记录的显示方式,需要改成“1-25”(附图) (11)查询大数量时,出现等待提示,可以在下面修改 (12)Dashboard中钻取返回提示修改: (12)友好打印PDF中的空格 (12)Answer中的主题文件夹层次现实: (13)Excel下载如果不自动变成科学计数法: (13)如何强制Answer中列的宽度 (13)个性化汇总查询: (14)在仪表板上加入当前client日期显示: (15)在Answer的Titel中加入变量显示: (15)客户化仪表盘右上角的产品清单,如去除等多产品中的Marketing (16)在仪表板制定位置显示Deliver的内容 (16)OBI EE and oracle stored procedures WITH parameter passing (16)如何将Go URL中的“页选项”按钮去除 (18)Configuration for the Dashboard Prompt Types Feature (19)图形: (21)中文显示方块问题 (21)BIEE中雷达图中文显示问题: (21)图形鼠标点到的地方的值的背景希望是透明的: (21)BIPublisher Chart Description (21)图形出现“Evaluation Time Limit“ (22)指定BIEE中图形的类型(flash,SVG,PNG) (22)图形中“上”字,“名”字和“作”字的链接错误 (22)配置和服务 (24)几处配置文件的作用优先级别 (24)禁止OC4J自动启动 (24)如何在Office 2003中启用BIEE Excel Add-in (24)BIP (25)BI Publisher 和Oracle BI Server 的安全集成 (25)报表复制 (27)RDF to RTF Template Generator (27)RDF to Data Template Generator (27)其他 (27)修改BIEE中的用户密码 (27)BIEE和其他应用集成,如果出现频繁登录提示: (32)Metadata report (32)Oracle BIEE性能提高 (33)使用BIP和iBot中的外部认证 (33)BIEE 10.1.3.2中ibot的配置: (34)其他Web程序调用BIEE的报表方式: (34)其他Web程序调用BIEE的仪表板方式: (35)Customizing OBI EE – GO URL Parameters (36)从BIEE的报表链接到其他系统: (39)Writeback for dashboard commentary in OBI EE (40)Siebel Analytics Web Catalog 升级到Oracle BIEE Presentation Catalog (46)How To Log An Oracle Support Service Request Via SupportWeb for Oracle BusinessIntelligence Enterprise Edition (OBIEE) (49)Applies to: (49)Goal (49)Create SR for BIEE from metalink: (51)仪表板:仪表板分组下拉显示:1.配置instanceconfig.xml,加入<DahboardMaxBeforeMenu>的配置,然后重启BI presentation server.数字3表示,当一个组的仪表板数量大于等于3时,会将仪表板分组下拉显示。

ADS异常处理

0x1C 0x18 0x14 0x10 0x0C 0x08 0x04 0x00

FIQ IRQ (Reserved) Data Abort Prefetch Abort

Software Interrupt Undefined Instruction

这将导致: 这将导致:

函数所有用到的寄存器被保护 如果可能, 任何远程调用所使用的其他寄存器也被保护 函数退出使用正确的返回指令(修正 pc = lr-4 并从 spsr恢复cpsr)

__irq 仅仅可在 armcc中使用 中使用. 中使用

可是被__irq 函数调用的子程序可以用 tcc编译.

test

从数据异常( 从数据异常 Data Abort)返回 返回

在特权模式不仅仅更新PC, 在特权模式不仅仅更新 ,而且 拷贝SPSR 到 CPSR 拷贝

test

SUBS pc,lr,#8

之前被压栈的话使用LDM " 如果 LR之前被压栈的话使用 之前被压栈的话使用 ^" "

LDMFD sp!,{pc}^

Output without __irq

STMFD sp!,{r4,lr} MOV r4,#0x80000000 LDR r0,[r4,#0] CMP r0,#1 LEQ int_handler_1 MOV r0,#0 STR r0,[r4,#4] LDMFD sp!,{r4,pc}

Output with __irq test

异常处理

T

H

E

A

R

C

H

I

T

E

单片机英语词汇

单片机英语词汇Microcontroller English VocabularyIntroductionIn the field of electronics and embedded systems, microcontrollers play a vital role. Whether it's in consumer electronics, industrial automation, or Internet of Things (IoT) devices, microcontrollers are extensively used for controlling and monitoring various applications. This article aims to provide an overview of commonly used English vocabulary related to microcontrollers.1. MicrocontrollerA microcontroller is a miniature computer system on a single integrated circuit (IC). It consists of a central processing unit (CPU), memory, and input/output peripherals. Microcontrollers are designed for specific tasks and typically used in embedded systems where they control and interact with other electronic components.2. Embedded SystemAn embedded system is a combination of hardware and software designed for a specific function. It is integrated into a larger system and performs dedicated tasks. Microcontrollers are often at the heart of embedded systems, providing the intelligence and control required for the system to function.3. PeripheralA peripheral refers to an external device connected to a microcontroller. It allows the microcontroller to interact with the outside world, such as sensors, actuators, displays, and communication interfaces. Examples of peripherals include analog-to-digital converters (ADC), digital-to-analog converters (DAC), UART (Universal Asynchronous Receiver/Transmitter), and GPIO (General Purpose Input/Output) pins.4. InterruptAn interrupt is a signal generated by a peripheral or internal event that momentarily suspends the normal execution of the program. Interrupts allow critical tasks to be handled immediately, ensuring real-time responsiveness. Common types of interrupts include timer interrupts, external interrupts, and communication interrupts.5. FirmwareFirmware refers to software that is permanently stored on a microcontroller's memory and provides low-level control over its hardware peripherals. It is responsible for initializing the microcontroller, managing peripherals, and implementing specific functionalities. Firmware is typically written in assembly language or a high-level programming language like C.6. BitA bit, short for binary digit, is the smallest unit of digital information. It can represent either a 0 or a 1. Microcontrollers internally process data in terms of individual bits, allowing for precise control over binary operations. Bits are combined to form bytes, which are commonly used for data storage and manipulation.7. OscillatorAn oscillator generates a stable and accurate clock signal that provides timing for various operations within a microcontroller. The clock signal determines the speed at which the microcontroller executes instructions and controls the timing of data transfer. Common types of oscillators include crystal oscillators and ceramic resonators.8. Interrupt Service Routine (ISR)An Interrupt Service Routine (ISR) is a specific section of code that is executed when an interrupt occurs. It is responsible for handling the interrupt event and performing necessary actions. ISRs are typically written to respond to specific interrupt sources and can be customized based on the application's requirements.9. Serial CommunicationSerial communication is the process of transmitting data one bit at a time over a single data line. It is commonly used for communication between microcontrollers, sensors, and other peripherals. Serial communication protocols such as UART, SPI (Serial Peripheral Interface), and I2C (Inter-Integrated Circuit) are widely used in microcontroller-based systems.10. Real-Time Operating System (RTOS)A Real-Time Operating System (RTOS) is a specialized operating system designed for applications that require precise timing and responsiveness. RTOS provides task scheduling, resource management, and communication mechanisms tailored for real-time systems. It allows forconcurrent execution of multiple tasks and ensures critical tasks meet their timing deadlines.ConclusionIn conclusion, a thorough understanding of microcontroller-related English vocabulary is essential for professionals and enthusiasts working in the field of electronics and embedded systems. This article has provided a concise overview of key terms related to microcontrollers. By familiarizing yourself with these terms, you will be better equipped to communicate and comprehend technical documentation, participate in discussions, and deepen your knowledge in this exciting domain.。

软考高级架构师系统设计40题

软考高级架构师系统设计40题1. In a system design, which of the following is the most important consideration for scalability?A. Hardware performanceB. Software architectureC. Network bandwidthD. User interface design答案:B。

解析:软件架构对于系统的可扩展性至关重要。

硬件性能在一定程度上影响,但不是最关键的。

网络带宽主要影响数据传输,对可扩展性的直接影响较小。

用户界面设计与系统的可扩展性关系不大。

2. When designing a system, which principle should be followed to ensure high availability?A. RedundancyB. Minimization of componentsC. Simple architectureD. Low cost答案:A。

解析:冗余是确保高可用性的重要原则。

减少组件可能会降低复杂性,但不一定能保证高可用性。

简单架构有助于理解和维护,但不是保证高可用性的关键。

低成本通常不是高可用性设计的首要考虑因素。

3. Which of the following is a key factor in determining theperformance of a system?A. The number of usersB. The algorithm usedC. The color scheme of the interfaceD. The brand of the hardware答案:B。

解析:算法的优劣直接决定了系统的性能。

用户数量会影响系统负载,但不是决定性能的根本因素。

界面的颜色方案与性能无关。

硬件品牌对性能有一定影响,但算法的影响更为关键。

计算机操作系统英文论文

Introduction to the operating system of the new technology Abstract:the Operating System (Operating System, referred to as OS) is an important part of a computer System is an important part of the System software, it is responsible for managing the hardware and software resources of the computer System and the working process of the entire computer coordination between System components, systems and between users and the relationship between the user and the user. With the appearance of new technology of the operating system functions on the rise. Operating system as a standard suite must satisfy the needs of users as much as possible, so the system is expanding, function of increasing, and gradually formed from the development tools to system tools and applications of a platform environment. To meet the needs of users. In this paper, in view of the operating system in the core position in the development of computer and technological change has made an analysis of the function of computer operating system, development and classification of simple analysis and elaborationKey words: computer operating system, development,new technology Operating system is to manage all the computer system hardware resources include software and data resources; Control program is running; Improve the man-machine interface; Provide support for other application software, etc., all the computer system resourcesto maximize the role, to provide users with convenient, efficient, friendly service interface.The operating system is a management computer hardware and software resources program, is also the kernel of the computer system and the cornerstone. Operating system have such as management and configuration memory, decided to system resources supply and demand of priorities, control input and output devices, file system and other basic network operation and management affairs. Operating system is to manage all the computer system hardware resources include software and data resources; Control program is running; Improve the man-machine interface; Provide support for other application software, etc., all the computer system resources to maximize the role, to provide users with convenient, efficient, friendly service interface. Operating system is a huge management control procedures, including roughly five aspects of management functions, processes and processor management, operation management, storage management, equipment management, file management. At present the common operating system on microcomputer DOS, OS / 2, UNIX, XENIX, LINUX, Windows, Netware, etc. But all of the operating system with concurrency, sharing, four basic characteristics of virtual property and uncertainty. At present there are many different kinds of operating system, it is difficultto use a single standard unified classification. Divided according to the application field, can be divided into the desktop operating system, server operating system, the host operating system, embedded operating system.1.The basic introduction of the operating system(1)The features of the operating systemManagement of computer system hardware, software, data and other resources, as far as possible to reduce the work of the artificial allocation of resources and people to the machine's intervention, the computer automatically work efficiency into full play.Coordinate the relationship between and in the process of using various resources, make the computer's resources use reasonable scheduling, both low and high speed devices running with each other.To provide users with use of a computer system environment, easy to use parts of a computer system or function. Operating system, through its own procedures to by all the resources of the computer system provides the function of the abstract, the function of the formation and the equivalent of the operating system, and image, provide users with convenient to use the computer.(2)The development of the operating systemOperating system originally intended to provide a simple sorting ability to work, after updating for auxiliary more complex hardwarefacilities and gradual evolution.Starting from the first batch mode, also come time sharing mechanism, in the era of multiprocessor comes, the operating system also will add a multiprocessor coordination function, even the coordination function of distributed systems. The evolution of the other aspects also like this.On the other hand, on a personal computer, personal computer operating system of the road, following the growth of the big computer is becoming more and more complex in hardware, powerful, and practice in the past only large computer functions that it step by step.Manual operation stage. At this stage of the computer, the main components is tube, speed slow, no software, no operating system. User directly using a machine language program, hands-on completely manual operation, the first will be prepared machine program tape into the input, and then start the machine input the program and data into a computer, and then through the switch to start the program running and computing, after the completion of the printer output. The user must be very professional and technical personnel to achieve control of the computer.Batch processing stage. Due to the mid - 1950 - s, the main components replaced by the transistor computer, running speed hadthe very big enhancement, the software also began to develop rapidly, appeared in the early of the operating system, it is the early users to submit the application software for management and monitoring program of the batch.Multiprogramming system phase. As the medium and small-scale integrated circuit widely application in computer systems, the CPU speed is greatly increased, in order to improve the utilization rate of CPU and multiprogramming technology is introduced, and the special support multiprogramming hardware organization, during this period, in order to further improve the efficiency of CPU utilization, a multichannel batch system, time-sharing system, etc., to produce more powerful regulatory process, and quickly developed into an important branch of computer science, is the operating system. Collectively known as the traditional operating system.Modern operating systems. Large-scale, the rapid development of vlsi rapidly, a microprocessor, optimization of computer architecture, computer speed further improved, and the volume is greatly reduced, for personal computers and portable computer appeared and spread. Its the biggest advantage is clear structure, comprehensive functions, and can meet the needs of the many USES and operation aspects.2. New technology of the operating systemFrom the standpoint of the operating system of the new technology, it mainly includes the operating system structure design of the micro kernel technology and operating system software design of the object-oriented technology.(1) The microkernel operating system technologyA prominent thought in the design of modern operating systems is the operating system of the composition and function of more on a higher level to run (i.e., user mode), and leave a small kernel as far as possible, use it to complete the core of the operating system is the most basic function, according to the technology for micro kernel (Microkernel) technology.The microkernel structure(1) Those most basic, the most essential function of the operatingsystem reserved in the kernel(2)Move most of the functionality of the operating system intothe kernel, and each operating system functions exist in theform of a separate server process, and provide services.(3)In user space outside of the kernel including all operatingsystem, service process also includes the user's applicationprocess. Between these processes is the client/server mode.Micro kernel contains the main ingredient(1) Interrupt and the exception handling mechanism(2)Interprocess communication mechanisms(3)The processor scheduling mechanism(4)The basic mechanism of the service functionThe realization of the microkernelMicro kernel implementation "micro" is a major problem and performance requirements of comprehensive consideration. To do "micro" is the key to implementation mechanism and strategy, the concept of separation. Due to the micro kernel is the most important of news communication between processes and the interrupt processing mechanism, the following briefly describes the realization of both.Interprocess communication mechanismsCommunication service for the client and the server is one of the main functions of the micro kernel, is also the foundation of the kernel implement other services. Whether to send the request and the server reply messages are going through the kernel. Process of news communication is generally through the port (port). A process can have one or more ports, each port is actually a message queue or message buffer, they all have a unique port ID (port) and port authority table, the table is pointed out that this process can be interactive communications and which process. Ports ID and kernel power table maintenance.Interrupt processing mechanismMicro-kernel structure separation mechanism will interrupt and the interrupt processing, namely the interrupt mechanism on micro kernel, and put the interrupt handling in user space corresponding service process. Micro kernel interruption mechanism, is mainly responsible for the following work:(1) When an interrupt occurs to identify interrupt;(2) Put the interrupt signal interrupt data structure mapping tothe relevant process;(3) The interrupt is transformed into a message;(4) Send a message to the user space in the process of port, butthe kernel has nothing to do with any interrupt handling.(5) Interrupt handling is to use threads in a system.The advantages of the microkernel structure(1) Safe and reliableThe microkernel to reduce the complexity of the kernel, reduce the probability of failure, and increases the security of the system.(2) The consistency of the interfaceWhen required by the user process services, all based on message communication mode through the kernel to the server process. Therefore, process faces is a unified consistent processescommunication interface.(3) Scalability of the systemSystem scalability is strong, with the emergence of new hardware and software technology, only a few change to the kernel.(4) FlexibilityOperating system has a good modular structure, can independently modify module and can also be free to add and delete function, so the operating system can be tailored according to user's need.(5) CompatibilityMany systems all hope to be able to run on a variety of different processor platform, the micro kernel structure is relatively easy to implement.(6) Provides support for distributed systemsOperating under the microkernel structure system must adopt client/server mode. This model is suitable for distributed systems, can provide support for distributed systems.The main drawback of microkernelUnder the micro-kernel structure, a system service process need more patterns (between user mode and kernel mode conversion) and process address space of the switch, this increases costs, affected the speed of execution.3 .Object-oriented operating system technologyObject-oriented operating system refers to the operating system based on object model. At present, there have been many operating system used the object-oriented technology, such as Windows NT, etc. Object-oriented has become a new generation of an important symbol of the operating system.The core of object-oriented conceptsIs the basic idea of object-oriented to construct the system as a series of collections of objects. The object refers to a set of data and the data of some basic operation encapsulated together formed by an entity. The core of object-oriented concept includes the following aspects:(1) EncapsulationIn object-oriented encapsulation is the meaning of a data set and the data about the operation of the packaging together, form a dynamic entity, namely object. Encapsulated within the request object code and data to be protected.(2) InheritanceInheritance refers to some object can be inherited some features and characteristics of the object.(3) PolymorphismPolymorphism refers to a name a variety of semantics, or the same interface multiple implementations. Polymorphism inobject-oriented languages is implemented by overloading and virtual functions.(4) The messageNews is the way of mutual requests and mutual cooperation between objects. An object through the message to activate another object. The message typically contains a request object identification and information necessary to complete the work.Object-oriented operating systemIn object-oriented operating system, the object as a concurrent units, all system resources, including documents, process and memory blocks are considered to be an object, such as the operating system resources are all accomplished through the use of object services.The advantages of object-oriented operating system:(1)Can reduce operating system throughout its life period whena change is done to the influence of the system itself.For example, if the hardware has changed, will force the operating system also changes, in this case, as long as change the object representing the hardware resources and the operation of the object of service, and those who use only do not need to change the object code.(2)Operating system access to its resources and manipulation are consistent .Operating system to produce an event object, delete, and reference, and it produces reference, delete, and a process object using the same method, which is implemented by using a handle to the object. Handle to the object, refers to the process to a particular object table in the table.(3)Security measures to simplify the operating system.Because all the objects are the same way, so when someone tries to access an object, security operating system will step in and approved, regardless of what the object is.(4)Sharing resources between object for the process provides a convenient and consistent approach.Object handle is used to handle all types of objects. The operating system can by tracking an object, how many handle is opened to determine whether the object is still in use. When it is no longer used, the operating system can delete the object.ConclusionIn the past few decades of revolutionary changes have taken place in the operating system: technological innovation, the expansionof the user experience on the upgrade, application field and the improvement of function. As in the past few decades, over the next 20 years there will be huge changes in operating system. See we now use the operating system is very perfect. Believe that after the technology of the operating system will still continue to improve, will let you use the more convenient. Believe that the operating system in the future will make our life and work more colorful.。

(MIPS体系结构剖析,编程与实践)第4章 MIPS 异常和中断处理文库

(MIPS体系结构剖析,编程与实践)第4章 MIPS 异常和中断处理文库.txt小时候觉得父亲不简单,后来觉得自己不简单,再后来觉得自己孩子不简单。

越是想知道自己是不是忘记的时候,反而记得越清楚。

第四章 MIPS 异常和中断处理MIPS 异常和中断处理(Exception and Interrupt handling)任何一个CPU都要提供一个详细的异常和中断处理机制。

一个软件系统,如操作系统,就是一个时序逻辑系统,通过时钟,外部事件来驱动整个预先定义好的逻辑行为。

这也是为什么当写一个操作系统时如何定义时间的计算是非常重要的原因。

大家都非常清楚UNIX提供了一整套系统调用(System Call)。

系统调用其实就是一段EXCEPTION处理程序。

我们可能要问:为什么CPU要提供Excpetion 和 Interrupt Handling呢?*处理illegal behavior, 例如,TLB Fault, or, we say, the Page fault; Cache Error;* Provide an approach for accessing priviledged resources, for example, CP0 registers. As we know, for user level tasks/processes, they are runningwith the User Mode priviledge and are prohibilited to directly control CPO. CPU need provide a mechanism for them to trap to kernel mode and then safely manipulate resources that are only availablewhen CPU runs in kernel mode.* Provide handling for external/internal interrupts. For instance, the timer interrupts and watch dog exceptions. Those two interrupt/exceptions are very important for an embedded system applicances.Now let's get back to how MIPS supports its exception and interrupt handling.For simplicty, all information below will be based on R7K CPU, which is derived from the R4k family.* The first thing for understanding MIPS exception handling is: MIPS adopts **Precise Exceptions** mechanisms. What that means? Here is the explaination from the book of "See MIPS Run": "In a precise-exception CPU, on any exception we get pointed at one instruction(the exception victim). All instructions preceding the exception victim in executionsequence are complete; any work done on the victim and on any subsequent instructions (BNN NOTE: pipeline effects) has no side effects that the software need worry about. The software that handles exceptions can ignore all the timing effects of the CPU's implementations"上面的意思其实很简单:在发生EXCEPTION之前的一切计算行为会**FINISH**。

解决EmbeddedWB弹出页面错误框的问题

使用EmbeddedWB控件的时候,发现有一些错误完全无法用try..except去接,这些错误的提示并非是通过Raize抛出的,而是通过Windows消息传递而来,因此要解决此问题,必须从消息下手。

在EmbeddedWB.pas中,找到重写消息的方法,即TEmbeddedWB.FormWndProc(),其中的代码即是消息的接收,而看其他码,它正是处理了WM_ACTIVATE消息,即有对话框弹出时触发的消息。

在EmbeddedWB控件里,有一个属性的设置,将DisableErrors.ScriptError改成False就好了

即然出错信息也是对话框,那么从此消息跟入就不会有错,继续往下读代码,发现有一句

SetWindowText(Wnd, PChar(S));

直觉告诉我应该在此处下个断点,下了之后调试,果然发现了,这里的变量S就是出错对话框的标题!

那么参数中的Wnd也就是对话框的句柄了。没想到这么简单就直接找到了关键之处

SendMessage(hButton, BM_Click, 0,0);

except on E: Exception do

end;

这样就直接发送了No这个Button被点击的消息,对话框就自己关掉了

如果是中文版的Windows,只需要把 "&No" 改成 "否(&N)" 即可

如果觉得这么做不放心,要启动出错报告怎么办呢?办法也很简单

随后要做的,就是把这个对话框关掉了,在对话框显示后,立刻关闭之,这时的一闪而过是用户肉眼无法捕捉的,也不会造成界面闪烁。

于是在 if FDisableErrors.FScriptE FindWindowEx(wnd, 0, 'Button', '&No');

后缀表达式原理

后缀表达式原理In computing, postfix notation, also known as reverse Polish notation (RPN), is a mathematical notation in which every operator follows all of its operands. This differs from infix notation, where operators are placed between operands. Postfix notation can be more efficient when evaluating mathematical expressions since it eliminates the need for parentheses and operator precedence rules. It is commonly used in stack-based computing systems, including some programming languages like Forth and PostScript.在计算领域,后缀表达式(也称为逆波兰表达式)是一种数学表示法,其中每个运算符都在所有操作数之后。

这与中缀表示法不同,中缀表示法中运算符位于操作数之间。

后缀表达式在计算数学表达式时可以更有效率,因为它消除了括号和运算符优先级规则的需求。

在基于堆栈的计算系统中常常使用后缀表达式,包括一些编程语言,如Forth和PostScript。

One advantage of postfix notation is its simplicity and ease of implementation in computer programs. Since operators immediately follow their operands, there is no ambiguity in the order of operations. This makes it easier for computers to evaluateexpressions using a simple algorithm that processes each token sequentially. Additionally, postfix notation is easily converted to and from infix notation using a stack-based algorithm, allowing for flexibility in handling mathematical expressions.后缀表达式的一个优点是其简单性和在计算机程序中实现的便捷性。

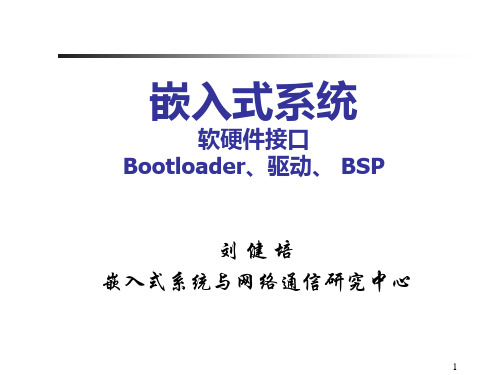

嵌入式系统软硬件接口 ppt课件

SD/MMC/CF卡

RAM、SDRAM

怎么放?

JTAG仿真器/BDM等

外部烧写器

Hale Waihona Puke 固化的loader,与主机通过串口/USB/网口等通信获取bootloader

怎么被执行?

固定的复位向量地址

调试时仿真器指定地址

执行完后怎么办?

不走回头路

发生异常跳回bootloader

13

Bootloader常设计成支持2种模式

ARM 的C 库ABI —— CLIBABI(The C Library ABI for the ARM Architecture )

10

系统初始化过程

指令执行前硬件初始化

系统上电,执行内部初始固码微程序( 如果有),设置处理器上电默认工作状 态,最后从复位向量处开始执行

硬件初始化

片级初始化(设置微处理器执行状态)

硬件 开发板实物

提炼 地址

软件 C语言头文件

3

TQ2440硬件开发板

4

2440addr.h

5

从软件开发角度看存储器

存储器地址空间分布图 存储芯片信息

类型、基址、大小、片选、配置参数 存储器控制寄存器 MMU

6

从软件开发角度看外设

指令能访问到什么

IO管脚配置寄存器

设备寄存器组

数据、控制、状态

EABI: Embedded Application Binary Interface,嵌入式应用程序二进制接口

APP

LIBs

API

OS

Source code

compile

Compiler

toolchain Linker Loader Debugger

Xsens MTi 1-series 开发套件用户手册说明书

Revision Date By ChangesA 8 July 2015 MHA Initial release…………E25 June 2018WBO Added information on PCB versions withI2C pull-up resistorsF22 August 2018SGI Refer to new embedded examples (MTSSv4.9.1)G16 Jan 2019SGI Update Chapter 3 to match GUI of MTSS2019.0H SGI Added chapter 4.3: Power Supplies2019.A Dec 2019AKO Xsens brand update© 2005-2020, Xsens Technologies B.V. All rights reserved. Information in this document is subject to change without notice. Xsens, Xsens DOT, MVN, MotionGrid, MTi, MTi-G, MTx, MTw, Awinda and KiC are registered trademarks or trademarks of Xsens Technologies B.V. and/or its parent, subsidiaries and/or affiliates in The Netherlands, the USA and/or other countries. All other trademarks are the property of their respective owners.Table of Contents1General information (5)1.1Package information (5)1.2Ordering information (6)2Introduction (7)2.1Kit contents and features (7)2.2Software and documentation (8)2.2.1Embedded examples (8)3Getting started (9)3.1Installing MT Software Suite (9)3.2Displaying data in MT Manager (10)3.3Configuring the MTi 1-series (11)4Shield board (13)4.1Connections and peripheral switch (13)4.2Pin descriptions (17)4.3Power supplies (17)4.4Electrical specifications (18)4.5Absolute maximum ratings (18)4.6Package drawing (20)List of TablesTable 1: Package contents for 1-series Development Kits (5)Table 2: Ordering information for 1-series Development Kits (6)Table 3: Connections on external power header (J100 in Figure 7) (14)Table 4: Connections on Arduino-compatible header (P100, P101, P102 and P103 in Figure 7) (14)Table 5: Connections on UART communication extension sockets (P202 and P203 in Figure 7) (15)Table 6: Switch positions to enable interfaces on Shield Board (SW200 in Figure 7) (15)Table 7: Connections on auxiliary sensor extension sockets (P200 and P201 in Figure 7) (16)Table 8: Pin descriptions Shield Board (17)Table 9: System specification Shield Board (18)Table 10: Absolute maximum ratings Shield Board (18)List of FiguresFigure 1: Exploded view of the MTi 1-series Shield board (7)Figure 2: Start up screen for MT Software Suite installer (9)Figure 3: Software components installation (9)Figure 4: Successful installation screen (10)Figure 5: MT Manager overview (11)Figure 6: Output configuration dialog in MT Manager using an MTi-7-DK (11)Figure 7: MTi 1-series Shield Board with connector designators (13)Figure 8: Top view (left) and the bottom view (right) of the GNSS daughter card (16)Figure 9: MTi 1-series Shield Board package drawing (Top and Side view) (20)1 General informationThis document provides information on the contents and usage of the MTi 1-series Development Kits. The MTi 1-series module (MTi 1-s) is a fully functional, self-contained module that is easy to design-in. The MTi 1-s can be connected to a host through I2C, SPI or UART interfaces. The MTi-3 Development Kit (MTi-3-DK) enables users to evaluate features for the MTi-3 (AHRS), MTi-2 (VRU) and MTi-1 (IMU) modules. The MTi-7 Development Kit (MTi-7-DK) enables users to evaluate features of the MTi-7 (external-GNSS/INS). In addition to the MTi 1-s interfaces, both Development Kits include a USB interface.The MTi 1-series module consists of components that are sensitive tostress. As a result, sensor characteristics may change when forces areapplied to the module. As each module is calibrated individually, Xsenscannot guarantee performance after improper handling. It is thereforerecommended not to remove the module from the socket, and to usethe Development Kit for prototyping and evaluation purposes only. Formore information on proper handling, refer to the MTi 1-seriesHardware Integration manual (see Section 2.2).1.1Package informationTable 1: Package contents for 1-series Development KitsComponentNameShield boardMTi 1-series module (MTi 1-s) GNSS daughter card11 Only with MTi-7-DKGNSS antenna1USB cable1.2Ordering informationTable 2: Ordering information for 1-series Development KitsKit Description Package contents Packing Method MTi-7-DK Development kit for MTi-7(external-GNSS-aided-AHRS)- Shield board- MTi-7 module (in the socket)- GNSS daughter card- GNSS antenna- USB cableSingle unitMTi-3-DK Development kit for MTi-1 (IMU),MTi-2 (VRU) and MTi-3 (AHRS)- Shield board- MTi-3 module (in the socket)- USB cableSingle unit2Introduction2.1Kit contents and featuresThe MTi 1-series Development Kit contains- Shield board- MTi-3 or MTi-7 mounted in the socket- GNSS daughter card (only with MTi-7-DK)- GNSS antenna (only with MTi-7-DK)- USB cableFigure 1: Exploded view of the MTi 1-series Shield boardThe Shield Board, the MTi 1-s (orange module) and the GNSS daughter card (with the SMA connector) are shown in Figure 1. The features of the Shield Board include: - 3.3 V compatible I/O-Power indicator LEDs-Arduino-compatible headers-External power pin header-Manual peripheral selection switch for MTi 1-series-Switching between UART and I2C on Arduino-compatible headers based on PSEL switch setting-USB to UART converter-Auxiliary extension socket-Optional socket connections for mikroBUS™ RS232/RS485 click boards™See Section 4 for more details.2.2Software and documentationThe MTi 1-series Development Kit is supported by the MT Software Suite, which includes the following software components:- MT Manager- Magnetic Field Mapper- MT SDK with documentationAdditionally, the latest firmware for the MTi-3 or the MTi-7 module can be downloaded and updated using the Firmware Updater that is also available on our website.The Software components can be downloaded from the Xsens website –. Along with the SDK documentation that is part of the MT Software Suite installer package, the MTi 1-series Development Kit is supported by the following additional documents2- Hardware Integration Manual: MTi 1-series (MT1503)- Datasheet: MTi 1-series (MT0512P)- MT Low Level Communication Protocol (MT0101P)- MT Manager User Manual (MT0216P)- MT Magnetic Field Mapper Documentation (MT0202P)- Product Change Notificationo MTi 1-series: Components placement change2.2.1Embedded examplesThe MTi 1-series is designed for easy integration in embedded systems. As of MT Software Suite version 4.9.1, there are embedded examples available for the MTi 1-series Development Kit that make use of the SPI and I2C interface. The examples and corresponding documentation can be found in the MT Software Suite installation folder at:C:\Program Files\Xsens\MT Software Suite x.x.x\MTSDK\Examples\embedded_examplesThe examples target the STM32F401 Nucleo board. They allow for a quick start in receiving measurement data from the MTi, and evaluating the low-level communication protocol.It is easy to extend the program with commands from the Xsens Low Level Communication Protocol (LLCP). This protocol is documented in detail in the Low Level Communication Protocol Documentation.2 The latest available documentation can be found in your MT Software Suite installation folder or via the following link: https:///xsens-mti-documentation3Getting started3.1Installing MT Software SuiteThe MT Software Suite is available from the Xsens website (/mt-software-suite).The installation procedure consists of a set of several installers and starts with the GUI as shown in Figure 2.Figure 2: Start up screen for MT Software Suite installerIt is possible to choose the components that you need to install (Figure 3).Figure 3: Software components installationWhen you cancel the installation of a particular component, the installer will continue with the next component. Make sure to accept the End-User License agreement and Software License Agreements, and then wait for the successful installation screen to appear as shown in Figure 4.Figure 4: Successful installation screen3.2Displaying data in MT ManagerWhen the MTi 1-series Shield Board is connected in MT Manager, the device description is shown in the “Device List” (Figure 5). To see a real time 3D orientation of the MTi click the 3D View icon . The inertial data , orientation data in Euler angles and the status data can be visualized by clicking their respective icons in Figure 5.Figure 5: MT Manager overview3.3Configuring the MTi 1-seriesThe MTi-1s can be directly configured by means of MT Manager. Click the Device Settings button to open the Output Configuration dialog (Figure 6).Figure 6: Output configuration dialog in MT Manager using an MTi-7-DKBy default, the output of the MTi-3 and MTi-7 is set to the ‘Onboard Processing’ preset, whereas the MTi-1 module is set to ‘XDA processing’ preset. Click “Inertial Data” (∆q/∆v or Rate of Turn/Acceleration) and “Magnetic Field” to be able to show this data in MT Manager.With MT Manager, it is possible to record data and export that data for use in other programs, set alignment matrices, configure synchronization options and to review the test and calibration report. More information on the functions and features can be found in the MT Manager User Manual. The MT Manager User Manual can be found via Help –> Documentation.4 Shield boardThe MTi 1-s modules are available with a development kit. An MTi-3 AHRS or an MTi-7 external-GNSS/INS is mounted in a PLCC-28 socket and connected to USB, UART, I 2C and SPI. The Shield Board exposes the pins of the MTi 1-s module making it easier for the user to test all the features and the peripherals offered by the MTi 1-s. This chapter discusses in more detail the connections and peripherals available on the MTi 1-s Shield Board.4.1 Connections and peripheral switchThe MTi 1-series Shield Board has the following connections as shown in Figure 7:- External power pin header (J100)- Arduino-compatible headers (P100, P101, P102 and P103)- UART communication extension socket, not placed by default (P202 and P203) - Micro USB (J102)- Peripheral selection switch (SW200)- Auxiliary sensor extension socket (P200 and P201) used for GNSS daughter card - MTi 1-series module placed in J101Figure 7: MTi 1-series Shield Board with connector designatorsShield boards from version 2.4 (PCB number: SD180624) and higher have 2.7 kΩ pull -up resistors on the I 2C pins on the Arduino-compatible header (P100-9 and P100-10). These resistors pull the I 2C lines toVDDIO. Figure 7shows the position of the resistors. The versionnumber of the board can be derived from the last two digits of the PCBnumber, located at the bottom side of the board (in the solder mask).For shield boards of version 2.3 or lower the pull-up resistors need tobe added externally, if the I2C protocol is used.The External power pin header J100 can be used to directly supply the VDDIO and/or VDDA supplies for the MTi 1-s module (Table 3). The IOREF pin on this connector can be used to override the default 3.3 V VDDIO by placing a jumper from this pin to the adjacent VDDIO pin.Table 3: Connections on external power header (J100 in Figure 7)Pin Description1 VDDA2 GND3 GND4 VDDIO5 IOREFThe connections for Arduino-compatible headers with a pitch of 2.54 mm (0.1 inch) are shown in Table 4. The MTi 1-series Shield Board does not support Arduino-compatible boards with an IOREF of 5V as the maximum VDDIO is 3.6V for the MTi 1-s module. Therefore, the VDDIO is by default set to 3.3V. This default VDDIO voltage can be overruled by placing a jumper on the external power header, but only for voltages within the operational VDDIO range of the MTi 1-s module. For information on the connections, refer to the pin description in Section 4.2. Refer to Table 6 on how to enable the various interfaces on the Shield Board.Table 4: Connections on Arduino-compatible header (P100, P101, P102 and P103 in Figure 7) Pin Arduino Shield Board Pin Arduino Shield BoardP100-10 SCL/D15 SCLP100-9 SDA/D14 SDAP100-8 AVDD NCP101-1 NC NC P100-7 GND GNDP101-2 IOREF IOREF P100-6 SCK/D13 SCK/ADD0P101-3 NRST NC P100-5 MISO/D12 MISO/ADD1P101-4 3V3 3V3 P100-4 MOSI/D11 MOSI/ADD2P101-5 5V 5V P100-3 CS/D10 nCSP101-6 GND GND P100-2 D9 PSEL0P101-7 GND GND P100-1 D8 PSEL1P101-8 VIN NC P102-8 D7 SYNC_INP102-7 D6 SYNC_OUT P103-1 A0 NC P102-6 D5 SYNC_PPSP103-2 A1 NC P102-5 D4 RESETP103-3 A2 NC P102-4 D3 DRDY/CTS/nREP103-4 A3 NC P102-3 D2 RTS/DEP103-5 A4 NC P102-2 TX/D1 RxDP103-6 A5 NC P102-1 RX/D0 TxDThe UART communication extension socket is not placed by default. When the socket is placed, it can be used to directly plug an UART transceiver module of MikroElektronika like the ‘RS232 click’ or ‘RS485 click 3.3V’. This UART communication extension socket uses (only) the 3.3V supply pin, which is connected to VDDIO. We recommend to place low profile sockets (like the CES-108-01-T-S) to make sure that the MTi 1-s module is still easily accessible. The pin description of these headers is shown in Table 5.Table 5: Connections on UART communication extension sockets (P202 and P203 in Figure 7) Pin Mikro BUS MTi 1-s Pin Mikro BUS MTi 1-sP202-1 AN NC P203-1 PWM DRDY/CTS/nREP202-2 RST Pull-down P203-2 INT DRDY/CTS/nREP202-3 CS RTS/DE P203-3 TX RxDP202-4 SCK NC P203-4 RX TxDP202-5 MISO NC P203-5 SCL NCP202-6 MOSI NC P203-6 SDA NCP202-7 3.3V VDDIO P203-7 5V NCP202-8 GND GND P203-8 GND GNDThe MTi 1-series Shield Board has a Micro USB connection that can be connected directly to a USB port on a PC or laptop. Note: Make sure to disconnect any other power supply, as this will overrule the USB connection.The Peripheral selection switch sets the interface configuration of the MTi 1-s module in the socket. The switch connects the PSEL lines (Table 6) to GND with a 5 kΩ pull-down when set to ON. Otherwise, the PSEL lines are pulled-up with a 100 kΩ resistor. The PSEL pins on the Arduino-compatible headers can be used to overrule these lines.Table 6: Switch positions to enable interfaces on Shield Board (SW200 in Figure 7)PSEL1 PSEL0 Interface Comments0 0 UART full-duplex This interface uses the flow control lines RTS and CTS. The UART full-duplex communications mode can be used without hardware flow control. In this case the CTS line needs to be tied low (GND) to make the MTi device transmit.0 1 UART half-duplex The UART itself is still full duplex but the DE and nRE lines are used to control a half-duplex transceiver1 0 SPI1 1 I2C When I2C interface is selected, it is required toset the address on the Arduino-compatibleheaders (see MTi 1-series Data Sheet for the I2C-addresses table)Figure 8: Top view (left) and the bottom view (right) of the GNSS daughter cardThe MTi-7-DK comes with the GNSS daughter card installed in the auxiliary sensor extension sockets (P200 and P201). As shown in Figure 8, the GNSS daughter cardconsists of a GNSS and a barometer sensor component. The LEDs (Power and PPS) give indication of proper functioning of the GNSS daughter card. The supplied GNSS antenna can be connected to the SMA connector.The auxiliary sensor extension socket has mikroBUS™ compatible pinning. This enables the user to connect alternate GNSS daughter card modules with mikroBUS™ pinning to the MTi 1-series Shield board. The pinning connections for the auxiliary sensor extension socket are listed in Table 7. This extension only uses the 3.3V supply pin, which isconnected to VDDIO. Therefore, make sure that the VDDIO is within the required voltage range of the GNSS module.Table 7: Connections on auxiliary sensor extension sockets (P200 and P201 in Figure 7) PinMikro BUS MTi 1-s PinMikro BUS MTi 1-s P200-1 AN NC P201-1 PWM NCP200-2 RST nRSTP201-2 INT SYNC_PPS P200-3 CS AUX_nCS P201-3 TX AUX_RxD P200-4 SCK AUX_SCK P201-4 RX AUX_TxD P200-5 MISO AUX_MISO P201-5 SCL NC P200-6 MOSI AUX_MOSI P201-6 SDA NC P200-7 3.3V VDDIO P201-7 5V NC P200-8GNDGNDP201-8GNDGND4.2Pin descriptionsTable 8: Pin descriptions Shield BoardName Type DescriptionPower InterfaceVDDA Power Power supply voltage for sensing elementsVDDIO Power Digital I/O supply voltageControlsPSEL0 Selection pins These pins determine the signal interface. Note that when thePSEL0/PSEL1 is not connected, its logic value is 1. WhenPSEL0/PSEL1 is connected to GND, its logic value is 0PSEL1RESET Active high reset pin, connect to GND if not usedPeripheral InterfaceSDA I2C interface I2C serial dataSCL I2C serial clockADD[0..2] I2C address selection pinsnCS SPI interface SPI chip selectMOSI SPI serial data input (slave)MISO SPI serial data output (slave)SCK SPI serial clockRTS UART interface Hardware flow control in UART full-duplex mode (Ready-to-Send) CTS Hardware flow control in UART full-duplex mode (Clear-to-Send) nRE Receiver control signal in UART half-duplex modeDE Transmitter control signal in UART half-duplex modeRxD Receiver data inputTxD Transmitter data outputDRDY Data ready Data ready pin indicates that data is available (SPI / I2C)SYNC_IN Sync interface Accepts a trigger input to request the latest available datamessageSYNC_OUT N/ASYNC_PPS Pulse Per Second output of GNSS moduleAUX_RxD Auxiliary UARTinterface Auxiliary UART data inputAUX_TxD Auxiliary UART data outputAUX_nCS Auxiliary SPIinterface Auxiliary SPI chip selectAUX_MOSI Auxiliary SPI serial data output (master)AUX_MISO Auxiliary SPI serial data input (master)AUX_SCK Auxiliary SPI serial clock4.3Power suppliesThe MTi 1-series module requires two different power supplies: VDDIO (used for the MCU and all IO) and VDDA (used as analog supply for the sensing elements).The Shield Board has five supply inputs:B: supplies both VDDIO and VDDA at 3.3V. Forces USB mode(SPI/I2C/UART interfaces not available).2.5V (P101): supplies both VDDIO and VDDA at3.3V. Forces USB mode(SPI/I2C/UART interfaces not available).3.3V3 (P101): supplies VDDIO directly and overrides USB mode (SPI/I2C/UARTinterfaces available).4.VDDIO (J100): supplies VDDIO directly, overrides all other VDDIO suppliesand overrides USB mode (SPI/I2C/UART interfaces available).5.VDDA (J100): supplies VDDA directly.Note: Only supplying VDDIO (through 3V3 (P101) or VDDIO (J100)) without supplying VDDA is not recommended. The only single supply options are USB and 5V (P101), but in both cases the Shield Board will be forced into USB mode.4.4Electrical specificationsThe Shield Board has the same communication protocol as the MTi 1-s module. Table 9 shows the electrical specifications for the Shield Board.Table 9: System specification Shield BoardMin Typ Max UnitVDDA 2.16 3.3 3.6 VVDDIO 1.8 3.3 3.6 VVV IO V IH0.75 *VDDIOV IL0.25 *VVDDIO4.5Absolute maximum ratingsTable 10: Absolute maximum ratings Shield BoardParameter Min Max Unit CommentsStorage temperature -50 +125 ºCOperating temperature -40 +85 ºCVDD -0.3 4.0 V Specification for the externalpower header J100.5V on P101 and J102 -0.3 6.0 V Specification for the Arduinoand USB.VDDIO -0.3 4.0 V Specification for the externalpower header J100.VV UART,PSEL,I2C-0.3 VDDIO +0.3VV RESET,SYNC,SPI -0.3 VDDIO +4.0Acceleration 310,000 g Any axis, unpowered, for 0.2msESD protection4±2000 V Human body modelStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at3 This is a mechanical shock (g) sensitive device. Proper handling is required to prevent damage to the part.4 This is an ESD-sensitive device. Proper handling is required to prevent damage to the part.these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Make sure not to apply force on the components of the MTi 1-s module, especially when placing the MTi 1-s module in a PLCC socket.4.6Package drawingFigure 9: MTi 1-series Shield Board package drawing (Top and Side view)。

gpioset gpioget用法

GPIO(General Purpose Input/Output)是一种通用输入输出接口,可以用于连接不同外部设备,如传感器、执行器、LED等。

在嵌入式系统中,我们经常需要使用GPIO来控制外部设备的状态,这就需要使用一些工具来对GPIO进行设置和获取。

在Linux系统中,我们可以使用gpioset和gpioget这两个命令来实现对GPIO的设置和获取。

本文将介绍gpioset和gpioget的用法及相关注意事项。

一、gpioset的用法gpioset命令用于设置GPIO的状态,可以将GPIO设置为高电平、低电平或者反转电平。

其基本用法如下:1. 设置GPIO为高电平:gpioset <chip设备编号> <引脚编号>=12. 设置GPIO为低电平:gpioset <chip设备编号> <引脚编号>=03. 反转GPIO电平:gpioset <chip设备编号> <引脚编号>=2其中,<chip设备编号>为GPIO设备在系统中的编号,<引脚编号>为具体引脚的编号。

通过这些简单的命令,我们可以轻松地控制GPIO 的状态。

需要注意的是,使用gpioset命令设置GPIO状态时,需要保证所选的GPIO引脚是可编程的,并且拥有足够的权限。

否则,可能会出现权限不足的错误,导致操作失败。

二、gpioget的用法gpioget命令用于获取GPIO的状态,可以用来查看某个特定GPIO引脚当前的状态(高电平或低电平)。

其基本用法如下:1. 获取GPIO状态:gpioget <chip设备编号> <引脚编号>通过这个命令,我们可以查看指定GPIO引脚的当前状态,并据此进行相应的处理。

同样地,使用gpioget命令时也需要注意设备编号和引脚编号的选择,以及对GPIO的访问权限。

三、常见问题及解决方法在使用gpioset和gpioget命令时,可能会遇到一些常见的问题,下面进行逐一介绍及解决方法。

嵌入式linux应用开发完全手册 v5

嵌入式linux应用开发完全手册 v51.嵌入式linux应用开发需要深入了解linux系统的特性和架构。

Embedded Linux application development requires a deep understanding of the features and architecture of the Linux system.2.开发人员应该掌握linux内核和驱动程序的基本知识。

Developers should have a good understanding of the basics of Linux kernel and drivers.3.需要熟悉linux的命令行工具和脚本语言。

Familiarity with Linux command-line tools and scripting languages is essential.4.理解嵌入式系统中的资源管理和优化是至关重要的。

Understanding resource management and optimization in embedded systems is crucial.5.了解嵌入式系统中的实时性能和响应是必不可少的。

Understanding real-time performance and responsiveness in embedded systems is essential.6.理解Linux系统的安全机制和措施对于开发安全的嵌入式应用至关重要。

Understanding the security mechanisms and measures in the Linux system is crucial for developing secure embedded applications.7.开发人员需要熟悉linux开发工具链和调试技术。

Developers need to be familiar with the Linux development toolchain and debugging techniques.8.对linux应用的交叉编译和交叉调试有一定的了解是必要的。

精确异常处理方法的实现与嵌入式管道处理器说明书

Efficient Implementation of Precise Exception for Processor Based on Pre-detectionQingyu ChenXi‟an Microelectronics Technology InstituteXi‟an, Chinae-mail:**********************Longsheng WuXi‟an Microelectronics Technology InstituteXi‟an, Chinae-mail:**********************Erjuan ZhuShaanxi Changling Photovoltaic Electric Co. LtdBao ji, Chinae-mail:******************Abstract—Embedded systems have higher requirements on real-time performance of processor. However exception, which can interrupt normal execution of program, will decrease the processor performance. For improving the exception handling efficiency of processor, a precise exception handling method for embedded pipeline processor based on pre-detection is proposed in this paper. When the precise exception occurs in any pipeline stage, the precise exception flag is set valid immediately and advanced to the next pipeline stage. Based on pre-detection on the exception flag, a single-cycle NOP instruction is provided for the processor by a dedicated hardware module. That separates the processor from spending large number of clock cycles requesting main instruction memory for instructions which will be flushed in the process of exception handling. This method has been implemented in a SPARC V8 processor which has successfully taped out. Test results of chip show that the precise exception detection and response efficiency is increased by 35.47% without increasing the processor critical path. The proposed method can be used to improve response efficiency of the precise exception at low hardware overheads.Keywords-exception flag; pre-detection; dedicated module; NOP instruction; processorI.I NTRODUCTIONMost modern embedded processors develop the instruction-level parallelism and improve the real-time performance of processor by the means of deep pipeline and multiple issue[1]. These techniques make the control of the processor, especially the accurate control of exception more difficult. The implementation of the precise exception is the important to the processor to satisfy the sequential architecture [2].In order to implement the precise exception, the controller in the processor will flush all instructions in pipeline to ensure that the results of instruction execution will be committed in-order when it responses to precise exception. References [3-5] introduce some techniques, which are commonly used in out-of-order processor to implement the precise exception, and the authors had studied the implementation method of the hardware and the overhead, but did not consider the response efficiency of exception. And the implementation principles and schemes of precise exception in single issue processor are concluded in [6-9]. Those schemes can accelerate the speed of recovery processor context by increasing the backup buffer or future buffer, but they didn‟t take the time of fetching instruction into account as those instructions will be flushed finally in the response of exception.Aiming at the defects of the existing method for handling precise exception, this paper presents an optimization method to implement precise exception for single issue processor, and conducts an experimental verification with a SPARC V8 processor developed by Xi'an micro-electronics technology institute. The method focuses on reduce the time of fetching invalid instruction which is in the pipeline and have not arrived at write-back stage when processor is handling the precise exception. Firstly, the paper introduces the definition of precise exception and its implementation in SPARC V8 architecture, and then based on the analysis of the existing methods, the precise exception implementation method based on pre-detection are illustrated. Finally, we analyze and conclude the testing process and results of this method.II.P RECISE E XCEPTIONThe exception is like an unexpected procedure call and may be caused by an instruction-induced exception or an external interrupt request not directly related to a particular instruction. There are 256 distinct types of exception by 8-bit TT (trap type) field identification in SPARC V8 architecture —half for hardware exceptions and half for software exceptions and the transfer addresses of all traps are decided by the exceptional type. All exceptions can be divided into three categories of exception: precise exception, deferred exception or interrupting exception.A precise exception is induced by a particular instruction and occurs before any program-visible state has been changed by the trap-inducing instruction. Several conditions must hold: (1) The instructions before the one which induced the exception have completed execution.(2)The instructions after the one which induced the exception remain unexecuted. (3)The PC saved in local register1 points to the instruction which induced theInternational Conference on Mechatronics, Electronic, Industrial and Control Engineering (MEIC 2015)exception, and the NPC saved in local register2 points at the instruction which was to be executed next [10].III.I MPLEMENTATION OF P RECISE E XCEPTIONThe precise exception handling method based on pre-detection has been proved to be effective in a SPARC V8 processor which has been successfully taped out. The processor achieves 159 kinds of exceptions, of which 144 types of precise exceptions and 15 types of external interrupt which will induce deferred exceptions. This section mainly introduces the process of exception handle, the traditional method for implementing precise exception, and the method based on pre-detection which is proposed in this paper.A.Traditional ImplementationThe implementation of precise exception typically is divided into four processes. The first is the exception detection and response, namely detecting the exception in instructions, and beginning to handle. Secondly the context preservation, mainly refers to save instruction PC, processor state PSR, generate subroutine entry address of exception handler. And then the controller begins to execute exception handler programs. Finally recovering state/control fields, such as PSR, from exception handler subroutine, at the same time resuming the main program. The main process of exception handling and time consumption is shown in Fig .1. Different from the public methods which aim at decreasing t2 or t4, this paper focuses on optimizing t1 since the t1 time overhead is more serious than t2 and t4 in the deep pipeline processor.Figure 1.Process of exception handing & time consumptionThe V8 processor mentioned in this paper has a typical 5-stage pipeline, which are IF (instruction fetch), ID(instruction decode), EX(execute), MEM(memory access) and WB(write back). The traditional method to implement precise exception is shown in Fig .2, includingtwo steps: (1) distributional detection. In order to balance the payload of each pipeline stage, the detection andpriority arrangement of precise exception is distributed to the all pipeline stage. Ten kinds of exception related to instruction execution, such as illegal instruction, windows overflow, privileged instruction and floating exception, can be detected in ID stage and the highest priority exception is advanced to the EX stage after priority arrangement. Some precise exceptions which has relationship with memory accessing will be detected in MEM stage. (2) centralized control. All exceptions change the state of the processor in WB stage, which can simplify and reduce the degree of difficulty in achieving precise exception to put exception controller logic on WB stage. When finding the instruction exception in any pipeline stage except for WB stage, the pipeline controller executes it continually as a normal instruction instead of handling immediately and sets the exceptional flag and reason (TT) into pipeline registers to transfer it to the WB at the same time. As soon as the exception controller in WB detects the exceptional flags, it will generate exceptional service address according to exceptional reason (TT) and preserve the context of program execution. In addition, the exception controller will flush all instructions which are in pipeline at the same time. These flushed instruction execution will not change processor state, so these instructions are executed uselessly. We call these flushed instructions as invalid instruction. As is shown in Fig.2, there are four pipeline stages before WB stage. So, in the worst case, four invalid instructions would be in the pipeline. The operation on flushing these instructions will lead the time consumption in fetching invalid instructions useless. When instruction SUB induces an exception, which is shown in Fig .3, its subsequent instruction …AND‟, …XOR‟, …SMUL‟and …SDIV‟has been fetched and executed normally before the SUB reaching the WB. Exception controller will flush all instructions in the pipeline, …AND‟, …XOR‟, …SMUL‟and …SDIV‟in Fig.3, when the SUB arrives at the WB. Although the mechanism of central controller can simplify and reduce the implementation difficulty of precise exceptions, it cannot reduce the time consumption in instruction fetching and execution of invalid instruction.Figure 2.Traditional method to achieve precise exceptionclk_h addsub and xor smul sdive_trap⎪⎪⎪⎩⎪⎪⎪⎨⎧Figure 3. Instructions flush in the precise exceptionB. Implementation based on Pre-detectionIn order to reduce the time consumption of invalid instruction fetching, the method which is based on the mechanism of exception distributional detection, by pre-detecting the precise exception flags, immediately provides a single-cycle NOP instruction for the ID stage through a dedicated hardware module and stops IF stage to request instructions to slower main memory as soon as the EFD (exception flag detection) module finds the exceptional flags valid in any pipeline stage. The method can effectively reduce the time consumption of fetch instruction operation of the invalid instructions.The concrete implementation of this method is shown in Fig .4. When detecting the instruction exception in any pipeline stage, the exception flag is set valid in that pipeline stage. Two modules, namely EFD (exception flag detect) and ROR (read only register), are added in the IF stage of the processor. Considering the exception flagsthe output of the OR connects to EFD module. If the output of the OR is effective, EFD would ban processor to request instructions to the main memory through inull signal connected to the Icache (instruction cache) and select a NOP instruction saved in the ROR module for ID stage by a multi-channel selector. The exceptional flags will be valid until the instruction inducing exception is completely out of the pipeline where the EFD inull signal becoming invalid, IF resumes to request instructions to main memory and the processor is transferred to exception handler program to execute. Because invalid instructions replaced by NOP instruction which does not cause the change of processor state, The method can simplify the refresh logic for the whole pipeline with only refresh logic in EX and MEM stages retained. On the others hand, such a mechanism avoids the processor from spending plenty of clock cycles requesting instructions to slower main memory and reduces the time consumption of invalid instruction fetching.Figure 4. Implementation based on pre-detectionIV. V ERIFICATION AND R ESULTSThe exception response time of the processor is one of the important standards for the real-time performance. This scheme verifies the same two silicon circuits except for the method to implement precise exception on ASIC development board by the TIMER integrated into the processor[11]. The process and environment of testing are shown in Fig .5 and 6. In the process of testing, through the DSU we upload test case to SRAM with 5-waiting clock cycles in the GRMON environment and started running the processor[12]. When executing instruction ta1(soft trap), the processor enters debug mode. Then checking the TIMER count value, we can calculate the exception detection and response time t1 in specific test case according to the clock frequency. Test results are listed in the table 1 and 2 between different cases, of which case1 is suitable for illegal instruction exception, case2 for register file check error, case3 for unaligned address exception. case1, case2 and case3 are respectively detected in ID, EX and MEM stage. The verification results are catalogued in Table 1 and 2.Testing results show that: (1) when cache hit, this method has no effect on the precise exception responseefficiency. (2)When cache un-hit, the approach cansignificantly reduce the exception detection and response time t1. The earlier the exception flag is detected, the moreobvious this method optimizes the performance. The design implements 144 types of precise exception, of which 138 kinds are detected in ID stage, one kind is detected in EX stage, 5 types of precise exception are detected in MEM stage. With comprehensive consideration of various exception cases, the exception detection andFigure 5.Exception detect and response time testing processFigure 6.Silicon circuit verification environmentTABLE I.T ESTING R ESULT WITH C ACHE-UNHITTABLE II.T ESTING R ESULT WITH C ACHE-HITV.S UMMARYBased on the analysis on definition of SPARC V8 precision exception, this paper proposes a method to implement precise exception for single issue pipeline processor aiming at the deficiency of existing preciseexception implementation. When an exception occurs, the method, by pre-detecting the precise exception flags,immediately provides a single-cycle NOP instruction for the processor through a dedicated hardware module. Such a mechanism can effectively reduce the time consumption of fetch instruction operation of the invalid instructions and simplify the flush operation of the whole instruction pipeline. This method has been implemented in a SPARC V8 processors developed by Xi'an microelectronics technology institute. The exception detection and response time of the silicon circuit is verified through 6 cases. The results show that this method makes the precise exception detection and response time t1 reduced by 35.47%. The proposed method can be used to improve response efficiency of the precise exception at low hardware overheads.A CKNOWLEDGMENTThe research work is supported by National High-Tech Research and Development Program of China(No. 2010ZX01021, No. 2009ZX01023). And I appreciate that the help from Xi‟an Microelectronics Technology Institute.R EFERENCES[1] D. A. Patterson and J. L. Hennessy, Computer organization anddesign: the hardware/software interface, 2nd ed., Newnes, 2013, pp.483-495.[2]J. L. Hennessy and D. A. Patterson, Computer architecture: aquantitative approach, 3rd ed., Elsevier, 2012, pp.68-75.[3]J. E. Smith and A.R. Pleszkun, "Implementing precise interrupts inpipelined processors," Computers, IEEE Transactions, vol.37, no.5, 1988, pp.562-573.[4]M. Pericas, A. Cristal, R. González, D. A. Jiménez and M. Valero,"A decoupled kilo-instruction processor," Proc. The Twelfth International Symposium on High-Performance Computer Architecture, IEEE Press, 2006, pp.53-64.[5]Z. Y. Liu and J. Y. Qi, "Implementation of precise exception in a5-stage pipeline embedded processor," Proc. The 5th International Conference on ASIC, IEEE press, 2003, pp.447-451.[6]W. J. Li, "A 5-stage pipelined embedded processor with optimizedhandling exception," Proc. 2011 International Conference on Computer Science and Network Technology (ICCSNT), IEEE press, 2011, pp.2773-2777.[7]X.Chen, S.B. Zhang and X.B. Shen, "Optimized Realization ofPrecise Interrupt on Microprocessor Longtium R2," Application Research of Computers, vol. 7, 2007, pp. 60-65.[8]Z.Y. Liu and J.Y. Qi, ”High Performance RISC MicroprocessorHardware Simulator Design,”Journal of Computer Research and Development, vol. 41, 2004, pp. 1436-1440.[9] B. Edouard, "Binary translator with precise exceptionsynchronization mechanism," U.S. Patent No. 8,296,551. 23 Oct.2012.[10]Internationa S, The SPARC architecture manual Version 8,SPARC International Inc, 1998.[11]X.F. Yin, S. H. Yuan and J. B. Hu, “Experimental Research onInterrupt Latency Time of ARM Microprocessor,”Computer Engineering, vol. 37, 2011, pp.252-563.[12]Q. Y. Chen, T. Y. Sheng and Q. Y. Duan , “The design of reusableinterface for AHB bus slave,”Microelectronics & Computer, vol.23, no.7, 2008, pp.129-133.。

关于嵌入式实时操作系统freertos的书籍

关于嵌入式实时操作系统freertos的书籍I would recommend the book "Mastering the FreeRTOS Real Time Kernel - A Hands-On Tutorial Guide" by Richard Barry as a comprehensive guide to understanding and implementing FreeRTOS in embedded systems. 该书以富有实践性的方式详细介绍了如何理解和实现FreeRTOS在嵌入式系统中的应用。

The book covers essential concepts of real-time operating systems, such as task scheduling, synchronization, inter-task communication, memory management, and interrupt handling, providing a solid foundation for beginners. 该书涵盖了实时操作系统的基本概念,包括任务调度、同步、任务间通信、内存管理和中断处理,为初学者打下了坚实的基础。

One of the key strengths of the book is its hands-on approach, offering practical examples and exercises that allow readers to apply the concepts learned in real-world scenarios. 该书的一大优势在于其实践性,提供了实际示例和练习,使读者能够将所学概念应用于实际场景中。

The author, Richard Barry, is the founder of FreeRTOS and possesses a wealth of knowledge and experience in real-time embedded systems, making him a trusted source for learning about FreeRTOS. 作者Richard Barry是FreeRTOS的创始人,具有丰富的实时嵌入式系统知识和经验,因此是学习FreeRTOS的可信源。

exception handing document异常处理文档模板 -回复

exception handing document异常处理文档模板-回复异常处理是编程中非常重要的一部分,它涉及到在程序运行过程中出现错误时如何进行处理。

在编写代码时,我们无法预料所有可能出现的错误情况,但我们可以通过合理的异常处理来保证程序的健壮性和可靠性。

本文将介绍关于异常处理的概念、原则以及常用的异常处理方式。

一、异常处理的概念1. 什么是异常异常是指在程序运行过程中出现的错误或意外情况,它可能会导致程序的中断、崩溃或产生不可预料的结果。

2. 异常处理的目的异常处理的目的是为了解决程序运行过程中出现的错误,保证程序的正常运行或优雅地退出,同时给予用户友好的提示信息。

二、异常处理的原则1. 适当屏蔽异常在异常的层次结构中,有些异常我们是可以预料并处理的,但也有些异常是没有必要或无法处理的。

对于后者,我们应该适当屏蔽,保证程序不会因为无关的异常而中断。

2. 捕获异常时要精确在捕获异常时,应该尽量精确地捕获特定类型的异常,避免将所有异常都捕获在一个大的try-catch块中,这样会导致代码可读性下降,并且可能会屏蔽掉一些需要处理的异常。

3. 异常处理不应该改变程序逻辑在处理异常时,应该尽量避免改变原有的程序逻辑。

异常处理应该是对正常程序流程的补充,而不是重定义程序行为。

三、常用的异常处理方式1. try-catch块try-catch块是最常见的异常处理方式。

在try块中编写可能会抛出异常的代码,然后在catch块中捕获并处理异常。

使用try-catch块可以防止异常导致程序中断,同时可以在异常发生时进行相应的处理和记录。

2. finally块finally块是可选的,用于在无论异常是否发生都执行一段代码,比如资源的释放。

无论是否发生异常,finally块中的代码都会被执行,因此可以在这里进行一些清理工作。

3. throws关键字如果在方法声明中出现了throws关键字,表示该方法可能会抛出某种类型的异常,而不是在方法内部处理异常。

燃放烟花和爆竹英文作文

燃放烟花和爆竹英文作文英文回答:Fireworks and firecrackers, a ubiquitous part of many cultures' celebrations, are a source of both joy and concern. Their vibrant displays illuminate the night sky, casting a magical glow upon festivities. However, their use also raises questions about safety, environmental impact, and noise pollution.From a safety perspective, fireworks and firecrackers pose inherent risks of burns, eye injuries, and even death. In the United States alone, an estimated 15,600 fireworks-related injuries were treated in emergency departments in 2020. These injuries can result from improper handling, malfunctioning devices, or stray embers.Environmental concerns also surround the use of fireworks. The chemicals they release into the atmosphere can contribute to air pollution, particularly when used inlarge quantities. Additionally, the remnants of fireworks, such as paper, plastic, and metal, can litter the environment and pose hazards to wildlife.Noise pollution is another significant issue associated with fireworks and firecrackers. The loud explosions they produce can be disturbing to both humans and animals. Studies have shown that exposure to excessive noise levels can lead to hearing loss, sleep disturbances, and cardiovascular problems.Despite these concerns, fireworks and firecrackers remain popular in many cultures. They are often seen as symbols of celebration and joy, and their use is deeply embedded in traditions. However, it is crucial to weigh the risks and benefits carefully before using these devices.Proper safety precautions, such as wearing protective eyewear, using fireworks only in designated areas, and keeping children and pets a safe distance away, are essential. Additionally, choosing environmentally friendly fireworks, limiting the use of large displays, anddisposing of fireworks responsibly can help mitigate their impact on the environment.Ultimately, the decision of whether or not to use fireworks and firecrackers is a personal one. By understanding the risks and taking necessary precautions, individuals can minimize the potential hazards and enjoy these dazzling displays responsibly.中文回答:烟花和爆竹。

hal定时器中断函数 -回复