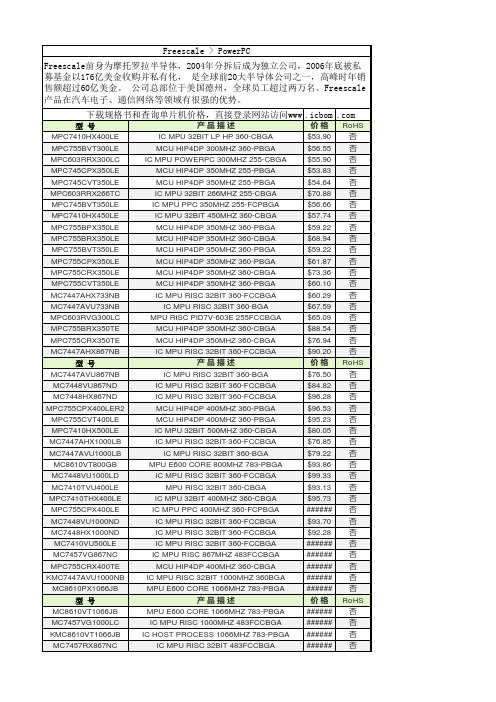

PPC440SPE-RGB533C中文资料

PowerPC单片机资料 、应用、价格、参数

MC9S12KG256VPVE

MC9S12KT256CPVE

MC9S12KT256VPVE

MC9S12T64CPKE16

MC9S12T64MPKE16

MC9S12XA256VAG

MC9S12XA512VAG

MC9S12XD256VAG

MC9S12XDT512VAA

MC9S12XDT512VAG

MC9S12DJ256VPVE

MC8610TPX800GB MC8610TVT800GB MC7457RX1000LC MC8640HX1067NE MC8640VU1067NE MC8640VU1000HE MC7447AVS1267LB MC7447AVU1267LB MPC7410THX450NE MC7447AVS1167NB MC7447AHX1167NB MC7457RX1000NC MC8610TPX1066JB MC8610TVT1066JB MC7448THX1000ND MC7448TVU1000ND 型 号 MC7457VG1000NC MC8640DHX1000HE MC8640DVU1000HE KMC7447AHX1167NB KMC7447AVS1167NB MC8640DHX1067NE MC8640DVU1067NE MC8640DHX1250HE MPC7410THX500LE MC7448VS1250ND MC7448VU1250ND MC7448HX1250ND MC8640DTHX1000HC MC8640DTHX1000HE MC8610PX1333JB MC8610VT1333JB MC8641DHX1000GE MC7448HX1420LD KMC7457RX1000NC KMC8610VT1333JB

MC9S12E128VFUE

440SP中文资料

Part Number 440SPRevision 1.23 - Sept 26, 2006 PowerPC 440SP Embedded ProcessorData Sheet Features•PowerPC‚ 440 processor core operating at up to 667MHz with 32-KB I- and D-caches (with parity checking)•On-chip 256-KB SRAM configurable as L2 Cache or Ethernet Packet/Code store memory•Selectable Processor:Bus clock ratios (Refer to the Clocking chapter in the PPC440SP Embedded Processor User’s Manual for details)•Supports up to 4 GB (2 Chip Selects) of 64-bit/32-bit SDRAM with ECC–DDR1 266-333-400–DDR2 400-533-667•Three DDR PCI-X interfaces (32-bit or 64-bit) up to 133 MHz (DDR 266) with support forconventional PCI•XOR Accelerator with DMA controller•Optional: High throughput RAID 6 hardware acceleration, performs XOR and Galois Field P & Q parity computations, supports up to 255 drives •I2O Messaging Unit with two DMA controllers •External Peripheral Bus (24-bit Address, 8-bit Data) for up to three devices•One Ethernet 10/100/1000 Mbps half- or full-duplex interface. Operational modes supported are MII and GMII.•Programmable Interrupt Controller supports interrupts from a variety of sources.•Programmable General Purpose Timers (GPT)•Three serial ports (16750 compatible UART)•Two IIC interfaces•General Purpose I/O (GPIO) interface available •JTAG interface for board level testing •Processor can boot from PCI memoryDescriptionDesigned specifically to address high-end embedded applications for storage, the PowerPC 440SP Embedded Processor (PPC440SP) provides a high-performance, low power solution that interfaces to a wide range of peripherals by incorporating on-chip power management features and lower power dissipation.This chip contains a high-performance RISC processor core, a DDR2 SDRAM controller, configurable 256KB SRAM to be used as L2 cache or software-controlled on-chip memory, three DDR PCI-X bus interfaces, an Ethernet interface, an I2O/DMA controller, control for external ROM and peripherals, optional RAID 6 acceleration, an XOR DMA unit, serial ports, IIC interfaces, and general purpose I/O.Technology: CMOS Cu-11, 0.13mm Package: 29mm, 783-ball, 1mm pitch, Flip Chip-Plastic Ball Grid Array (FC-PBGA)Power (estimated): Less than 6W @533MHz Supply voltages required: 3.3V, 2.5V, 1.8V, 1.5VPowerPC 440SP Embedded Processor Revision 1.23 - Sept 26, 2006Data SheetContentsOrdering and PVR Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 PPC440SP Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Address Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 PowerPC 440 Processor Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Internal Buses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 On-Chip SRAM/L2 Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 DDR PCI-X Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 DDR1/DDR2 SDRAM Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 External Peripheral Bus Controller (EBC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Ethernet Controller Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 I2O/DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Optional RAID 5 and RAID 6 Acceleration Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 XOR/DMA2 Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Serial Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 IIC Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 General Purpose Timers (GPT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 General Purpose IO (GPIO) Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Universal Interrupt Controller (UIC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 29mm, 783-Ball FC-PBGA Core Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Signal Lists . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 Device Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63 Clock Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67 Clock Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68 Spread Spectrum Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69 I/O Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70 Input/Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 DDR SDRAM I/O Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 DDR SDRAM Write Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78 DDR SDRAM Read Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83 Strapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83 Serial Bootstrap ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83 Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84PowerPC 440SP Embedded ProcessorRevision 1.23 - Sept 26, 2006Data SheetFiguresFigure 1. Order Part Number Key . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4Figure 2. PPC440SP Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5Figure 3. 29mm, 783-Ball FC-PBGA Core Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16Figure 4. Clock Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68Figure 5. Input Setup and Hold Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71Figure 6. Output Delay and Hold Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71Figure 7. DDR SDRAM Simulation Signal Termination Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76Figure 8. DDR SDRAM Write Cycle Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78Figure 9. DDR SDRAM Read Data Path. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80Figure 10. DDR SDRAM Memory Data and DQS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81Figure 11. DDR SDRAM Read Cycle Timing Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82TablesTable 1. System Memory Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6Table 2. DCR Address Map (4KB of Device Configuration Registers) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8Table 3. Signals Listed Alphabetically . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17Table 4. Signals Listed by Ball Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47Table 5. Pin Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54Table 6. Signal Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56Table 7. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63Table 8. Package Thermal Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64Table 9. Recommended DC Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64Table 10. Input Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66Table 11. DC Power Supply Loads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67Table 12. Clocking Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68Table 13. Peripheral Interface Clock Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70Table 14. I/O Specifications—All Speeds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72Table 15. I/O Specifications—533MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75Table 16. DDR SDRAM Output Driver Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77Table 17. DDR SDRAM Read and Write I/O Timing—TSA and THA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78Table 18. DDR SDRAM Clock to Write DQS Timing—TDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79Table 19. DDR SDRAM Write Data to DQS Timing—TSD and THD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79Table 20. DDR SDRAM I/O Read Timing—T SD and T HD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81Table 21. Strapping Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83PowerPC 440SP Embedded Processor Revision 1.23 - Sept 26, 2006Data SheetOrdering and PVR InformationFor information about the availability of the following parts, contact your local AMCC sales office.Each part number contains a revision code. This is the die mask revision number and is included in the part number for identification purposes only.The PVR (Processor Version Register) and the JTAG ID register are software accessible (read-only) and contain information that uniquely identifies the part. See the PPC440SP Embedded Processor User’s Manual for details about accessing these registers.Note: Raid-enabled versions (Product Feature = R) require a RAID key license.Figure 1. Order Part Number KeyProduct Name Order Part Number(see Notes:)Package Rev Level PVR Value JTAG ID PPC440SP PPC440SP-xpCfffC29mm, 783 FC-PBGAC0x532218910x12056049Notes:1.x = Product FeatureA = RAID6 not enabled R = RAID6 enabled2.p = Module Package TypeF = leaded FC-PBGAN = lead free FC-PGBA (RoHS compliant)3. C = Chip Revision Level C 4.fff = Processor Frequency533 = 533MHz 667 = 667MHz5. C = Case Temperature Range of -40°C to +100°CAMCC Part NumberPPC440SP-RNC667CPackageProcessor Speed Product FeatureRevision LevelCase Temperature Range Note: The example part number above is a RAID6-enabled, lead-free package, at Chip Revision Level C, capable of running at 667 MHz, and is shipped in tray packaging.PowerPC 440SP Embedded ProcessorRevision 1.23 - Sept 26, 2006Data SheetPPC440SP Functional Block DiagramFigure 2. PPC440SP Functional Block DiagramThe PPC440SP is a System on a chip, which uses IBM ® CoreConnect Bus™ Architecture.Implemented with the Crossbar option, the IBM CoreConnect buses provide:•128-bit Data, 64-bit Address PLB interfaces up to 166.66MHz, 2.6GB/s on both the Read and Write data paths (10.6GB/sec total)•32-bit OPB interfaces up to 83.33MHz, 333MB/sAddress MapsThe PPC440SP incorporates two address maps. The first is a fixed processor system memory address map. This address map defines the possible contents of various processor accessible address regions. The second address map identifies the system Device Configuration Registers (DCRs). DCRs are accessed by software running on the PPC440SP processor through the use of mtdcr and mfdcr instructions.UART2UART1IIC1Processor Core DCR Bus32KB On-chip Peripheral Bus (OPB)GPIO AcceleratorBridgeDDR2 SDRAM External Bus ControllerControllerClock,Control,ResetPower MgmtJTAG Timers MMUUnit OPB Interrupt ControllerUniversal I-Cache32KB D-CacheXOR/DMA PPC440DDR PCI-XMALEthernet DCRsGPT L2 Cache/SRAM10/100/Low Latency (LL) SegmentHigh Bandwidth (HB) SegmentController Processor Local Bus (PLB)Trace ArbiterPLBI2O/DMA Host Local 64 bits 64 bits Local 32 bitsMemory PCI0PCI1PCI21000MII,GMII(EBC)(DMA0 and DMA1)(DMA2)Queue IIC0UART0(EMAC)PowerPC 440SP Embedded Processor Revision 1.23 - Sept 26, 2006Data SheetTable 1. System Memory Address Map (Sheet 1 of 2)Function Sub Function Start Address End Address SizeLocal Memory (LL)1DDR SDRAM0000 0000 0000 00000000 0000 FFFF FFFF4GB SRAM0000 0001 0000 00000000 0001 0003 FFFF256KB Reserved0000 0001 0004 00000000 0001 000F FFFFInternal PLB Interfaces (LL)I2O Registers0000 0001 0010 00000000 0001 0010 00FF256B DMA 0 Registers0000 0001 0010 01000000 0001 0010 01FF256B DMA 1 Registers0000 0001 0010 02000000 0001 0010 02FF256B I20/DMA Buffers0000 0001 0010 03000000 0001 0010 0FFF 3.25KB Reserved0000 0001 0010 10000000 0001 001F FFFFXOR/DMA20000 0001 0020 00000000 0001 0020 3FFF16KB Reserved0000 0001 0020 40000000 0001 EFFF FFFFInternal OPB Peripherals (LL)Reserved0000 0001 F000 00000000 0001 F000 01FFUART00000 0001 F000 02000000 0001 F000 02078B Reserved0000 0001 F000 02080000 0001 F000 02FFUART10000 0001 F000 03000000 0001 F000 03078B Reserved0000 0001 F000 03080000 0001 F000 03FFIIC00000 0001 F000 04000000 0001 F000 041F32B Reserved0000 0001 F000 04200000 0001 F000 04FFIIC10000 0001 F000 05000000 0001 F000 051F32B Reserved0000 0001 F000 05200000 0001 F000 05FFUART20000 0001 F000 06000000 0001 F000 06078B Reserved0000 0001 F000 06080000 0001 F000 06FF248B GPIO Controller Registers0000 0001 F000 07000000 0001 F000 077F128B Reserved0000 0001 F000 07800000 0001 F000 07FFEthernet Controller Registers0000 0001 F000 08000000 0001 F000 08FF256B Reserved0000 0001 F000 09000000 0001 F000 09FFGeneral Purpose Timers0000 0001 F000 0A000000 0001 F000 0B3F320B Reserved0000 0001 F000 0B400000 0001 F7FF FFFFEBC Memory0000 0001 F800 00000000 0001 FFBF FFFF124MB Additional Boot ROM60000 0001 FFC0 00000000 0001 FFDF FFFF2MBBoot ROM2, 30000 0001 FFE0 00000000 0001 FFFF FFFF2MB Reserved0000 0002 0000 00000000 0007 FFFF FFFFLocal Memory Alias (HB)Aliased DDR SDRAM0000 0008 0000 00000000 0008 FFFF FFFF4GBPowerPC 440SP Embedded ProcessorRevision 1.23 - Sept 26, 2006Data SheetDDR PCI-X Space (HB)Reserved 0000 0009 0000 00000000 0009 07FF FFFF PCIX0 I/O 0000 0009 0800 00000000 0009 0800 FFFF 64KB PCIX1 I/O 0000 0009 1800 00000000 0009 1800 FFFF 64KB PCIX2 I/O0000 0009 2800 00000000 0009 2800 FFFF64KBPCIX0 Addressing Config. Regs 0000 0009 0EC0 00000000 0009 0EC0 00078B PCIX1 Addressing Config. Regs 0000 0009 1EC0 00000000 0009 1EC0 00078B PCIX2 Addressing Config. Regs 0000 0009 2EC0 00000000 0009 2EC0 00078BPCIX0 Core Config. Regs 0000 0009 0EC8 00000000 0009 0EC8 0FFF 4KB PCIX1 Core Config. Regs 0000 0009 1EC8 00000000 0009 1EC8 0FFF 4KB PCIX2 Core Config. Regs0000 0009 2EC8 00000000 0009 2EC8 0FFF4KBPCIX0 Simple Message Passing 0000 0009 0EC8 11000000 0009 0EC8 11FF 256B PCIX1 Simple Message Passing 0000 0009 1EC8 11000000 0009 1EC8 11FF 256B PCIX2 Simple Message Passing0000 0009 2EC8 11000000 0009 2EC8 11FF256BPCIX0 Special Cycle 0000 0009 0ED0 00000000 0009 0EDF FFFF 1MB PCIX1 Special Cycle 0000 0009 1ED0 00000000 0009 1EDF FFFF 1MB PCIX2 Special Cycle 0000 0009 2ED0 00000000 0009 2EDF FFFF 1MBReserved 0000 0009 2EE0 00000000 0009 2EFF FFFF PCI Memory 0000 0009 2F00 00000000 0009 FFBF FFFF 3.3GBReserved0000 0009 FFC0 00000000 0009 FFDF FFFF PCI Boot ROM (PCI Memory)0000 0009 FFE0 00000000 0009 FFFF FFFF 2MB PCI Memory0000 000A 0000 00000000 000F FFFF FFFF 24GBReserved 40000 0010 0000 000003FF FFFF FFFF FFFF Reserved 50400 0010 0000 000007FF FFFF FFFF FFFF DDR PCI-X Space (HB)PCI Memory0800 0000 0000 0000FFFF FFFF FFFF FFFF15.7EBNotes:1.DDR SDRAM and on-chip SRAM can be located anywhere in the Local Memory area of the memory map.2.The Boot ROM and Expansion ROM areas of the memory map are intended for use by ROM or Flash-type devices. While locating volatile DDR SDRAM and SRAM in this region is supported, use of these regions for this purpose is not recommended.3.When the optional boot from PCI-X memory is selected, the PCI-X Boot ROM address space begins at 9 FFE0 0000 (128 KB).4.Never decoded.5.Unpredictable results on Read and Write operations.6.Accessed by means of EBC Peripheral Bank Configuration RegistersTable 1. System Memory Address Map (Sheet 2 of 2)FunctionSub FunctionStart Address End Address SizePowerPC 440SP Embedded Processor Revision 1.23 - Sept 26, 2006Data SheetTable 2. DCR Address Map (4KB of Device Configuration Registers)Function Start Address End Address SizeTotal DCR Address Space10003FF1KW (4KB)1By function:Reserved00000B12W Clocking Power On Reset00C00D2W System DCRs 00E00F2W Memory Controller 0100112W External Bus Controller0120132W Reserved01401F12W SRAM02002F16WL2 Controller03003F16W Memory Queue04004F16W Reserved05005F16WI2O/DMA06007F32WPLB08008F16WPLB to OPB Bridge Out09009F16W Reserved0A00AF16W Reserved0B00B12W Reserved0B20BF14W Interrupt Controller 00C00CF16W Interrupt Controller 10D00DF16W Power Management0E00E78W Reserved0E817F152W Ethernet MAL1801FF128W Reserved2003FF512WNotes:1.DCR address space is addressable with up to 10 bits (1024 or 1K unique addresses). Each unique address represents a sin-gle 32-bit (word) register. One KW (1024W) equals 4KB (4096 bytes).PowerPC 440SP Embedded ProcessorRevision 1.23 - Sept 26, 2006Data SheetPowerPC 440 Processor CoreThe PowerPC 440 processor core is designed for high-end applications such as RAID controllers, SAN, iSCSI, routers, switches, printers, set-top boxes, and so on. It is the first processor core to implement the Book E PowerPC embedded architecture and the first to use the 128-bit version of IBM’s on-chip CoreConnect Bus Architecture.Features include:•Up to 667MHz operation•PowerPC Book E architecture •32KB I-cache, 32KB D-cache–Parity on Data and Tag address - checking of parity with error injection •Three logical regions in D-cache: Locked, Transient, and Normal •D-cache full-line flush capability•41-bit virtual address, 36-bit (64GB) physical address •Superscalar, out-of-order execution •Seven-stage pipeline•Three execution pipelines •Dynamic branch prediction •Memory management unit–64-entry, full associative, unified TLB with parity –Separate instruction and data micro-TLBs–Storage attributes for write-through, cache-inhibited, guarded, and big or little endian •Debug facilities–Multiple instruction and data range breakpoints –Data value compare–Single step, branch, and trap events –Non-invasive real-time trace interface •24 DSP instructions–Single cycle multiply and multiply-accumulate –32 x 32 integer multiplyInternal BusesThe PowerPC 440SP Embedded Processor features three standard on-chip buses: the Processor Local Bus (PLB), the On-Chip Peripheral Bus (OPB), and the Device Control Register Bus (DCR). The high performance, high bandwidth cores such as the PowerPC 440 processor core, the DDR SDRAM memory controller, and the DDR PCI-X bridge connect to the PLB. The OPB hosts lower data rate peripherals. The daisy-chained DCR provides a lower bandwidth path for passing status and control information between the processor core and the other on-chip cores.The PLB has a Crossbar arbiter that supports data transfer between the PLB master and two slave segments identified as the Low Latency (LL) and High Bandwidth (HB) segments. The LL segment allows PLB masters CPU and I2O, that are adversely affected by latency, to communicate with slave devices with minimal latency. The HB segment allows PLB masters DMA, XOR, and PCI to exchange large blocks of data with SDRAM and PCI without interfering with the low latency PLB masters.Bus features include:•PLB–128-bit Data implementation of the PLB architecture –Separate and simultaneous read and write data paths –64-bit address–Simultaneous control, address, and data phases –Four levels of pipelining–Byte enable capability supporting unaligned transfersPowerPC 440SP Embedded Processor Revision 1.23 - Sept 26, 2006Data Sheet–32- and 64-byte burst transfers–166MHz, maximum 5.2GB/s (simultaneous read and write)–Processor:Bus clock ratios of N:1 and N:2•OPB–Dynamic bus sizing: 32-, 16-, and 8-bit data path–32-bit address–83.33MHz, maximum 333MB/s•DCR–32-bit data path–10-bit addressOn-Chip SRAM/L2 CacheFeatures include:•Four banks of 64KB each for a total of 256KB•Configurable as either L2 cache or SRAM•Memory cycles supported:–Single beat read and write, 1 to 16 bytes–Quadword Read and Write burst for 12-bit master–Guarded memory accesses on 4KB boundaries•Sustainable 2.6GB/s peak bandwidth at 166MHz•Use as an L2 cache improves processor performance and reduces the PLB load–Cache coherency maintained by a hardware snoop mechanism on the Low Latency (LL) PLB or by software–Data Array and Tag Array parity–Unified data and instruction cache–Four-way set associative–36-bit addressing–Full LRU replacement algorithm–Write through, look aside•Use as Ethernet packet store allows Ethernet packets to be held for processing by the Ethernet coreDDR PCI-X InterfaceThe DDR PCI-X interface allows connection of PCI and PCI-X devices to the PowerPC processor and local memory. There are three separate interfaces supporting 32- and 64-bit PCI-X buses in DDR mode. All three interfaces can be configured for either host or adapter mode. PCI 32/64-bit legacy mode, compatible with PCI Version 2.3, is also supported.Features include:•PCI-X2.0–Split transactions–Frequency to 266MHz–32- and 64-bit address/data bus–ECC supported for 266MHz Mode 2 only•PCI 2.3 backward compatibility–Frequency to 66MHz–32- and 64-bit bus•Can be the PCI Host Bus Bridge or an Adapter Device PCI interface•Optional PCI arbitration function with PCI and PCI-X mode 1, supporting up to four external devices, that can be disabled for use with an external arbiter•Support for Message Signaled Interrupts (MSI) on both in- and out-bound interrupts•Simple message passing capability•Asynchronous to the PLBPowerPC 440SP Embedded ProcessorRevision 1.23 - Sept 26, 2006Data Sheet•PCI Power Management Version 1.1•PCI arbitration function with PCI-X Mode 2 support (optional)•PCI register set addressable both from on-chip processor and PCI device sides •Ability to boot from PCI-X bus memory •Error tracking/status•Supports initiation of transfer to the following address spaces:–Single beat I/O reads and writes–Single beat and burst memory reads and writes–Single beat configuration reads and writes (Type 0 and Type 1)–Single beat special cycles•PCI-X initialization sequence support (frequency & mode determination)•Support for unexpected split completions •Outbound transaction split discard timers •Vital Product Data (VPD) support •PCI-to-PCI opaque bridgeDDR1/DDR2 SDRAM Memory ControllerThe DDR2 SDRAM memory controller supports industry standard 184-pin DIMMs, SO-DIMMs, and other discrete devices. Global memory timings, address and bank sizes, and memory addressing modes are programmable. The DDR2 SDRAM controller interfaces to the PLB through a Memory Queue (MQ) function that includes six high-speed 1KB FIFO buffers.Features include:•Registered and non-registered industry standard DIMMs •DDR1 266-333-400•DDR2 400-533-667•64-and 32-bit memory interfaces with optional 8-bit ECC (SEC/DED)• 5.32GB/s peak bandwidth for the 64-bit interface • 2.66GB/s peak bandwidth for the 32-bit interface•Two chip (bank) select signals supporting two external banks •CAS latencies of 2, 3, 4, 5, 6, and 7 supported•Page mode accesses (up to 32 open pages) with configurable paging policy •Look-ahead request queue with programmable depth of four commands.•Optional optimized command scheduling (activate/precharge non-conflicting banks while accessing the current bank)•Up to 4GB in two external banks•Programmable address mapping and timing •Hardware and software initiated self-refresh•Sync DRAM configuration by means of mode register and extended mode register set commands •Power management (self-refresh, suspend, sleep)•Low Latency & High Bandwidth PLB ports•Selectable PLB read response (immediate or deferred)•Programmable Low Latency & High Bandwidth arbitration schemes•High Bandwidth port has four 1KB read buffers and two1KB write buffers •Low Latency port has four 128B read buffers and two 128B write buffersExternal Peripheral Bus Controller (EBC)Features include:•Support 2MB Boot ROM•Up to three ROM, EPROM, SRAM, Flash memory, and slave peripherals supported •Burst and non-burst devices •8-bit data bus。

芝麻坊 4 系列电脑电源说明书

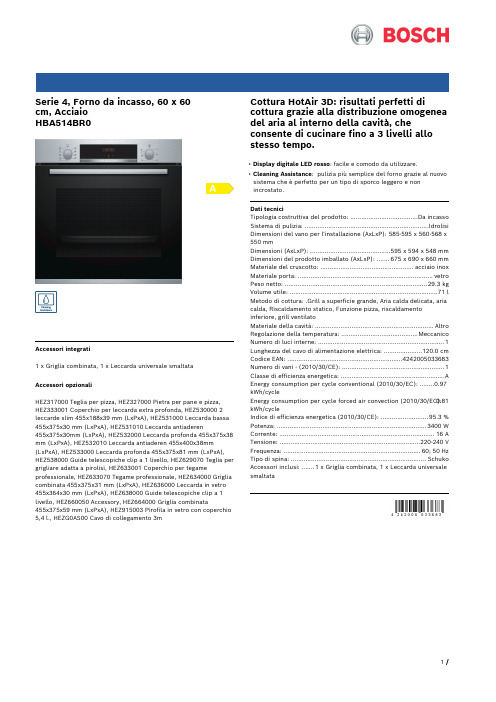

Serie 4, Forno da incasso, 60 x 60cm, AcciaioHBA514BR0Accessori integrati1 x Griglia combinata, 1 x Leccarda universale smaltataAccessori opzionaliHEZ317000 Teglia per pizza, HEZ327000 Pietra per pane e pizza, HEZ333001 Coperchio per leccarda extra profonda, HEZ530000 2 leccarde slim 455x188x39 mm (LxPxA), HEZ531000 Leccarda bassa 455x375x30 mm (LxPxA), HEZ531010 Leccarda antiaderen455x375x30mm (LxPxA), HEZ532000 Leccarda profonda 455x375x38 mm (LxPxA), HEZ532010 Leccarda antiaderen 455x400x38mm (LxPxA), HEZ533000 Leccarda profonda 455x375x81 mm (LxPxA), HEZ538000 Guide telescopiche clip a 1 livello, HEZ629070 Teglia per grigliare adatta a pirolisi, HEZ633001 Coperchio per tegame professionale, HEZ633070 Tegame professionale, HEZ634000 Griglia combinata 455x375x31 mm (LxPxA), HEZ636000 Leccarda in vetro 455x364x30 mm (LxPxA), HEZ638000 Guide telescopiche clip a 1 livello, HEZ660050 Accessory, HEZ664000 Griglia combinata455x375x59 mm (LxPxA), HEZ915003 Pirofila in vetro con coperchio 5,4 l., HEZG0AS00 Cavo di collegamento 3m Cottura HotAir 3D: risultati perfetti di cottura grazie alla distribuzione omogenea del aria al interno della cavità, che consente di cucinare fino a 3 livelli allo stesso tempo.• Display digitale LED rosso: facile e comodo da utilizzare.• Cleaning Assistance: pulizia più semplice del forno grazie al nuovo sistema che è perfetto per un tipo di sporco leggero e non incrostato.Dati tecniciTipologia costruttiva del prodotto: .....................................Da incasso Sistema di pulizia: ....................................................................Idrolisi Dimensioni del vano per l'installazione (AxLxP): 585-595 x 560-568 x 550 mmDimensioni (AxLxP): ............................................595 x 594 x 548 mm Dimensioni del prodotto imballato (AxLxP): .......675 x 690 x 660 mm Materiale del cruscotto: ...................................................acciaio inox Materiale porta: ..........................................................................vetro Peso netto: ..............................................................................29.3 kg Volume utile: .................................................................................71 l Metodo di cottura: .Grill a superficie grande, Aria calda delicata, aria calda, Riscaldamento statico, Funzione pizza, riscaldamento inferiore, grill ventilatoMateriale della cavità: .................................................................Altro Regolazione della temperatura: ..........................................Meccanico Numero di luci interne: (1)Lunghezza del cavo di alimentazione elettrica: .....................120.0 cm Codice EAN: (4242005033683)Numero di vani - (2010/30/CE): (1)Classe di efficienza energetica: .........................................................A Energy consumption per cycle conventional (2010/30/EC): ........0.97 kWh/cycleEnergy consumption per cycle forced air convection (2010/30/EC):0.81 kWh/cycleIndice di efficienza energetica (2010/30/CE): ..........................95.3 % Potenza: ..................................................................................3400 W Corrente: .....................................................................................16 A Tensione: .............................................................................220-240 V Frequenza: ...........................................................................60; 50 Hz Tipo di spina: ..........................................................................Schuko Accessori inclusi: .......1 x Griglia combinata, 1 x Leccarda universale smaltataSerie 4, Forno da incasso, 60 x 60cm, AcciaioHBA514BR0Cottura HotAir 3D: risultati perfetti di cottura grazie alla distribuzione omogenea del aria al interno della cavità, che consente di cucinare fino a 3 livelli allo stesso tempo.Caratteristiche principali- 7 programmi di cottura: MultiCottura HotAir 3D, Riscaldamento superiore e inferiore, Grill ventilato, Grill a superficie grande, Funzione pizza, Riscaldamento inferiore- Display digitale LED rosso- Volume cavità: 71 l- Regolazione della temperatura da 50 °C a 275 °C- Cleaning AssistanceAltre caratteristiche- Riscaldamento rapido- Orologio elettronico con impostazione inizio e fine cottura- Illuminazione interna alogenaAccessori- Accessori: 1 griglia combinata, 1 leccarda universale profonda smaltataEtichetta energetica- Assorbimento massimo elettrico: 3.4 kW- Classe di efficienza energetica (acc. EU Nr. 65/2014): A(in una scala di classi di efficienza energetica da A+++ a D)- Consumo energetico per ciclo durante funzionamento convenzionale:0.97 kWh- Consumo energetico per ciclo durante funzionamento ventilato:0.81 kWh- Numero di cavità: 1 Tipo di alimentazione: elettrica Volume della cavità:71 lSerie 4, Forno da incasso, 60 x 60cm, Acciaio HBA514BR0。

MICROMASTER 440通用变频器

目录1 MICROMASTER 440 变频器的参数.................................................................... ................................... 1-1 1.1 MICROMASTER 440 变频器的系统参数.................简介.......................................................................1-2 1.2 快速调试(P0010=1)..... ................... ....................................................................................................1-4 1.3 命令和驱动数据组一概览........ ............. ......................... ......................................................................1-51.4 参数的说明......................................... .................................................................................................1-62 功能框图.............................................. .................................................................................................... 2-13 二进制互联连接(BiCo)功能................................................................................................................ 3-1 3.1 概述..................................................................................................................................................... 3-2 3.2 怎样进行BiCo 设置?......................................................................................................................... 3-2 3.3 BiCo 控制字和状态字的用法................................................................................................................. 3-43.4 BiCo 的连接............................................................ ............................................................................. 3-54 通讯....................................................................... .................................................................................. 4-1 4.1 采用的串行通讯接口............................................................................................................................ 4-2 4.2 串行通讯的工作情况............................ ................................................................................................. 4-2 4.2.1 概述.................................................................................................................................................... 4-2 4.2.2 RS485 的排障..................................................................................................................................... 4-3 4.3 采用通用的串行接口协议................................................................................ ................... ...................4-3 4.3.1 通讯报文的结构............................................................ ...................................................................... 4-4 4.3.2 USS 协议有关信息的详细说明........................................... .............................................................. 4-4 4.3.3 有效的数据字符.................................................................... .............................................................. 4-5 4.3.4 USS 的任务和应答.............................................................................................................................. 4-7 4.3.5 PKW 举例:..................................................................... .................................................................4-10 4.3.6 PZD 区域(过程数据区)................................................... .................................................................4-12 4.3.7 任务报文(主站→MICROMASTER4)................................................................................................4-12 4.3.8 应答报文(MICROMASTER4→主站)............................. ..................................................................4-13 4.3.9 MICROMASTER4 有关USS 通讯的参数设置.................. ..................................................................4-15 4.3.10 基本设定................................................................................................................... ........................4-16 4.3.11 一般的高级设置.................................................................................................................................4-16 4.3.12 较复杂的高级设置.............................................................................................................................4-17 4.3.13 与早期MICROMASTER 产品的兼容性....... . ...................................................................................4-17 4.3.14 读出和写入参数............................................... .................................................................................4-18 4.3.15 广播方式............................................................................................................................................4-19 4.3.16 通过USS 利用BiCo(二进制互联连接)...... . ....................................................................................4-19 4.4 PROFIBUS....................................................... . .................................................................................. 4-20 4.4.1 概况............................................................... . .................................................................................. 4-20 4.4.2 PROFIBUS 的使用........................................ .................................................................................... 4-20 4.5 PROFIBUS 模板............................................. . .................................................................................... 4-214.5.1 PROFIBUS 模板的特点................................. . .................................................................................. 4-215 高级操作板(AOP)..................................................... . .......................................................................... 5-1 5.1 警告和说明........................................................................ .................................................................... 5-4 5.1.1 特殊键的功能...................................................................................................................................... 5-4 5.2 应用举例............................................................................... . .............................................................. 5-5 5.2.1 采用AOP 控制单台变频器.......................................................... ....................................................... 5-55.2.2.3 网络控制-PC 方式.................................................................................................................... 5-7 5.2.3 参数的“读出”.............................................................. ................................................................. 5-8 5.2.4 参数的“下载”.................................................................. ............................................................... 5-9 5.2.5 AOP 的参数.................................................................... . ..................................................................5-10 5.2.6 从站方式和DriveMonitor 的操作................ . ....................................................................................5-10 5.2.7 MM3 参数的读出..................................... . .........................................................................................5-11 5.2.8 定时器的操作........................................... . .........................................................................................5-11 5.3 AOP 开始工作........................................................................................................................................5-14 5.3.1 接通电源和初始化............. . ...............................................................................................................5-14 5.3.2 语言文本的选择...................................... . ..........................................................................................5-15 5.3.3 开机“帮助”............................... . .....................................................................................................5-15 5.3.4 常规的操作屏幕.............................. . ..................................................................................................5-15 5.3.5 主菜单(机旁操作方式).................................... . ..............................................................................5-16 5.3.6 请求等待................................................................ ............................................................................5-17 5.4 操作菜单................................................................................................................................................5-17 5.4.1 机旁操作方式下的操作........................................................................................................................5-17 5.4.1.1 通讯故障..........................................................................................................................................5-18 5.4.1.2 显示变频器的状态............... ............................................................................................................5-18 5.4.1.3 变频器类型的检验..................... ......................................................................................................5-18 5.4.2 主站方式下的操作................ . ............................................................................................................5-18 5.4.2.1 广播操作方式........................................... . .....................................................................................5-19 5.4.2.2 通讯故障..........................................................................................................................................5-19 5.5 选择操作方式.........................................................................................................................................5-19 5.5.1 机旁操作方式........................................................................................................... ......................... 5-20 5.5.2 主站方式................................................................................................................... ......................... 5-20 5.5.3 内部方式................................................................................................................... .........................5-20 5.5.4 从站方式.............................................................................................. ............................................. 5-20 5.5.5 PC 方式..................................................................................................... ........................................ 5-21 5.6 参数的访问............................................................................................................................................ 5-21 5.6.1 标准访问级的参数....................................................................... ...................................................... 5-21 5.6.2 功能键的使用................................................................................ .................................................... 5-22 5.6.2.1 屏幕显示滚动功能................................................................ .......................................................... 5-22 5.6.2.2 修改参数数值的某一位数字................................................ ............................................................ 5-22 5.6.2.3 跳转功能.......................................................................................................................................... 5-22 5.6.3 专家级参数................................................................................. ....................................................... 5-23 5.6.3.1 下标参数.............................................................................. ........................................................... 5-23 5.6.4 AOP 存储的参数组................................................................... ......................................................... 5-24 5.6.5 工程设计.................................................................................... ........................................................ 5-24 5.7 AOP 设定和组态.................................................................................................................................... 5-25 5.7.1 设定菜单..................................................................... ....................................................................... 5-25 5.7.1.1 背景亮度......................................................................................................................................... 5-25 5.7.1.2 屏幕对比度............................................................. ....................................................................... 5-26 5.7.1.3 用大字符显示.................................................................................................................................. 5-265.7.1.7 参数组的名称..................................................................................... ........................................... 5-27 5.7.1.8 设定时间/日期.......................................... ..................................................................................... 5-28 5.7.1.9 AOP 复位....................................................................................................................................... 5-28 5.8 故障指示............................................................................................................................................... 5-29 5.8.1 故障屏幕...................................................................................... ..................................................... 5-29 5.8.2 报警屏幕............................................................................................................................................ 5-30 5.8.3 多重故障................................................................................. .......................................................... 5-30 5.8.4 多重报警................................................................................. .......................................................... 5-30 5.8.5 故障和报警同时发生............................................................... .......................................................... 5-31 5.8.6 变频器的故障码....................................................................... ......................................................... 5-31 5.8.7 变频器的报警码........................................................................................ ........................................ 5-315.8.8 变频器的故障/ 报警记录(P0947).............................................................................................. 5-316 编码器模板.............................................................................................................................................. 6-1 6.1 前言...................................................................................................................................................... 6-2 6.2 一般情况............................................................................................................................................... 6-3 6.3 安装...................................................................................................................................................... 6-4 6.3.1 准备工作................................................................................... ........................................................ 6-4 6.3.1.1 变频器的准备工作........................................................................................................................... 6-4 6.3.1.2 编码器模板的准备工作.......................................................... ......................................................... 6-5 6.3.2 接线方法的举例.................................................................................................................................. 6-8 6.4 调试................................................................................................................................................................. 6-9 6.4.1 TTL 编码器............................................................. ...........................................................................6-10 6.4.2 HTL 编码器................................................................... .....................................................................6-11 6.4.3 外接电源......................................................................... ...................................................................6-11 6.4.4 编码器模板的参数化........................................................ ..................................................................6-12 6.5 故障的排除............................................................................................................................................6-14 6.5.1 LED 指示灯............................................................ ...........................................................................6-14 6.5.2 故障码....................................................................... ........................................................................6-156.6 编码器模板的技术规格................................................... ......................................................................6-157 MICROMASTER 440 变频器的制动电阻..................................... ...........................................................7-1 7.1 技术数据...................................................................................... .........................................................7-2 7.2 安装.......................................................................................................................................................7-2 7.3 接线.......................................................................................................................................................7-2 7.4 制动电阻的接线和外形尺寸...................................................................................................................7-37.5 制动电阻的选型........................................................... .........................................................................7-48 选件安装图............................................................................................................................................... 8-1插图图4-1 典型的RS485 多站接口.................................................................................................................... 4-3 图4-2 通讯报文的结构................................................................................................................................. 4-4 图4-3 地址(ADR)的位号......................................................................................................................... 4-4图6-1 编码器模板的外观........................................................................................ .................................... 6-3 图6-2 变频器的铭牌........................................................................................................... ........................ 6-4 图6-3 选件的安装顺序........................................................................................................ ....................... 6-5图6-4 屏蔽接线端和PE 端子.......................................................................................... ......................... 6-5 图6-5 编码器模板上的LED 指示灯................................................................................. ......................... 6-6 图6-6 编码器模板的DIP 开关................................................................................................ .................... 6-7 图6-7 TTL 编码器的接线(5V DC) ................................................................................ ............................ 6-8 图6-8 HTL 编码器的接线(18V DC) .................................................................................. ........................ 6-8 图6-9 具有外接电源的编码器............................................................................................. ........................ 6-9 图6-10 编码器模板的安装方法....................................................................................... ............................ 6-9 图6-11 编码器模板上的LED 指示灯..........................................................................................................6-14表格表3-1 BiCo 的连接(r0019 至r0054)..................................... ................................................................. 3-5 表3-2 BiCo 的连接(r0055 至r1119)....................................... ............................................................. 3-6 表3-3 BiCo 的连接(r1170 至r2050).......................................... .......................................................... 3-7 表3-4 BiCo 的连接(r2053 至r2294)............................................ ........................................................ 3-8 表4-1 任务识别标记ID 的定义............................................................ ....................................................... 4-7 表4-2 应答识别标记ID 的定义............................................................ ....................................................... 4-8 表4-3 对应答识别标记ID 的错误数值=“任务不能执行”的定义............... .................................................. 4-9 表4-4 PZD 区的结构..................................................................................... ..............................................4-12 表4-5 变频器的控制字(STW)................................................................ ................................................4-12 表4-6 变频器的状态字(PZD).................................................................. ...............................................4-13 表4-7 实际例子........................................................................................ ....................................................4-14 表4-8 比较表(MICROMASTER4/早期生产的MIsCROMASTER 变频器). ............................................4-18 表4-9 PROFIBUSSUB-D 插座的插针功能分配.............................................. ............................................ 4-23 表4-10 与数据传输速率相应的最大电缆长度................................................. ............................................ 4-23 表4-11 插头/座和电缆的订货号........................................................................ ............................. ........... 4-23 表4-12 技术数据.............................................................................................. ........................... .............. 4-24 表4-13 有关PROFIBUS 的订货资料................................................................... ...................................... 4-241 MICROMASTER 440 变频器的参数1.1 MICROMASTER 440 变频器的系统参数简介“参数说明”的编排格式如下。

Kuppersbusch BP 6550.0S-CN烤箱说明书

目录1. 图标的说明 (5)2. 运输与包装 (6)3. 安全须知 (7)3.1 连接与操作 (7)3.2 开启与操作 (7)3.3 烤箱 (8)3.4 家长须知 (9)3.5 首次使用 (9)3.6 环境保护 (9)3.7 能源信息 (10)3.8 用户须知 (10)4. 清洁与保养 (11)4.1 产品表面 (11)4.2 烤箱门的清洁(不包括微波炉、微烤一体机) (13)4.3 高温热解自清洁的烤箱(部分型号) (14)5. 首次使用前的注意事项 (14)5.1 重要建议 (15)6. 配件 (16)6.1 可伸缩滑动搁架 (16)6.2 滑出式搁架 (17)6.3 烤箱配件的更换 (18)7. 维护 (18)7.1 烤箱灯的更换 (18)7.2 拆卸和装配烤箱门(微烤一体机除外) (19)7.3 拆卸和装配烤箱门内玻璃 (21)7.4 拆卸和装配烤箱侧边支架 (22)7.5 拆卸后部背板 (22)8. 烤箱结构 (24)8.1 操作面板——触摸控制及屏显 (25)8.2 设置时钟 (26)9. 烧烤与烹饪菜单 (26)29.1 烹饪指南 (26)9.2 烤肉指南 (30)9.3 烧烤指南 (32)9.4 烘焙探针建议温度 (33)9.5 低温烹饪指南 (34)10. 烤箱功能 (35)10.1 烹饪功能 (35)10.2 特殊功能 (36)11. 烤箱的操作 (38)11.1 开启/关闭烤箱 (38)11.2 待机模式 (38)11.3 首次使用烤箱前的设置 (38)11.4 选择烹饪功能 (39)11.5 选择特殊功能 (40)11.6 烹饪过程中更改设置 (40)11.7 自动功能 (41)11.8 更改食材重量和温度 (42)11.9 设置时间 (43)11.10 快速加热(出厂已激活) (47)12. 菜单收藏 (47)12.1 访问收藏设定 (47)12.2 存储菜单至收藏夹 (48)12.3 删除收藏菜单 (48)13. 其他功能 (48)13.1 设置演示模式 (48)13.2 童锁 (48)13.3 恢复出厂设置 (49)13.4 自动确认 (49)13.5 ECO模式 (49)13.6 开机音设置 (50)13.7 单位设置 (50)14. 烘焙探针 (51)14.1 烹饪功能中使用烘焙探针 (52)14.2 自动功能中使用烘焙探针 (52)315. 部分型号的特殊设置、其他功能与设置 (53)15.1 高温热解功能 (53)15.2 故障原因 (54)41.图标的说明我们的产品都是通过最新最好的技术来进行生产的,但是仍会有一些使用风险存在。

PPC-4211W 用户手册说明书

用户手册PPC-4211W带21.5”彩色TFT-LCD显示器和Intel Core i处理器的微型计算机版权声明随附本产品发行的文件为研华公司2014年版权所有,并保留相关权利。

针对本手册中相关产品的说明,研华公司保留随时变更的权利,恕不另行通知。

未经研华公司书面许可,本手册所有内容不得通过任何途径以任何形式复制、翻印、翻译或者传输。

本手册以提供正确、可靠的信息为出发点。

但是研华公司对于本手册的使用结果,或者因使用本手册而导致其它第三方的权益受损,概不负责。

认可声明Intel和Pentium为Intel Corporation的商标。

Microsoft Windows®为Microsoft Corp.的注册商标。

所有其它产品名或商标均为各自所属方的财产。

产品质量保证(两年)从购买之日起,研华为原购买商提供两年的产品质量保证。

但对那些未经授权的维修人员维修过的产品不予提供质量保证。

研华对于不正确的使用、灾难、错误安装产生的问题有免责权利。

如果研华产品出现故障,在质保期内我们提供免费维修或更换服务。

对于出保产品,我们将会酌情收取材料费、人工服务费用。

请联系相关销售人员了解详细情况。

如果您认为您购买的产品出现了故障,请遵循以下步骤:1.收集您所遇到的问题信息(例如,CPU主频、使用的研华产品及其它软件、硬件等)。

请注意屏幕上出现的任何不正常信息显示。

2.打电话给您的供货商,描述故障问题。

请借助手册、产品和任何有帮助的信息。

3.如果您的产品被诊断发生故障,请从您的供货商那里获得RMA (ReturnMaterial Authorization) 序列号。

这可以让我们尽快地进行故障产品的回收。

4.请仔细地包装故障产品,并在包装中附上完整的售后服务卡片和购买日期证明(如销售发票)。

我们对无法提供购买日期证明的产品不提供质量保证服务。

5.把相关的RMA序列号写在外包装上,并将其运送给销售人员。

料号:200K421100第一版中国印刷2014年4月PPC-4211W用户手册ii符合性声明CE本设备已通过CE 测试,符合以屏蔽电缆进行外部接线的环境规格标准。

Blackfin CM-BF533 硬件用户手册说明书

Hardware User Manual CM-BF533 V2.0 (V1.3)ContactBluetechnix Mechatronische Systeme GmbHWaidhausenstr. 3/19A-1140 ViennaAUSTRIA/EUROPE*********************Document No.: 100-1203-2.0Version 6Date: 2007-04-05Table of Contents1Introduction (1)1.1Overview (1)1.2Benefits (2)1.3Applications (2)2Specification (3)2.1Functional Specification (3)2.2Boot Mode (3)2.3Memory Map (4)2.4Electrical Specification (4)2.4.1Supply Voltage (4)2.4.2Supply Voltage Ripple (4)2.4.3External Oscillator Frequency (4)2.4.4Real Time Clock Crystal (4)2.4.5Supply Current (4)2.5Environmental Specification (4)2.5.1Temperature (4)2.5.2Humidity (5)3CM-BF533 (Connector Version) (6)3.1Mechanical Outline (6)3.2Connector Footprint (7)3.3Top Mounted Connector (8)3.4Schematic Symbol (Signals of P1 and P2) (9)3.5Connectors Pin Assignment P1 – (1-60) (10)3.6Connector Pin Assignment P2 – (61-120) (11)3.7ITU656 Camera Connector P3 (1-22) (12)3.8Connector P4 (1-10) (12)4Test Points (13)4.1Footprint – Test Points (13)5Application Examples (14)5.1Sample Application (14)5.2Stand-alone Camera System (15)5.3Generic Signal Processing System (15)5.4Coprocessor Application (15)5.5Digital Video System (16)5.6Design Services (16)6Software Support (17)6.1BLACKSheep (17)6.2uClinux (17)7Known Bugs (18)8Product Changes (19)9Document Revision History (20)A List of Figures and Tables (21)Edition 2007-02© Bluetechnix Mechatronische Systeme GmbH 2007All Rights Reserved.The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.Terms of delivery and rights of technical change reserved.We hereby disclaim any warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.Bluetechnix makes and you receive no warranties or conditions, express, implied, statutory or in any communication with you. Bluetechnix specifically disclaims any implied warranty of merchantability or fitness for a particular purpose.Bluetechnix takes no liability for any damages and errors causing of the usage of this board. The user of this board is responsible by himself for the functionality of his application. He is allowed to use the board only if he has the qualification. More information is found in the General Terms and Conditions (AGB).InformationFor further information on technology, delivery terms and conditions and prices please contact Bluetechnix ().WarningsDue to technical requirements components may contain dangerous substances.BLACKFIN ProductsCore Modules:CM-BF533: Blackfin Processor Module powered by Analog Devices single coreADSP-BF533 processor; up to 600MHz, 32MB RAM, 2MB Flash,120 pin expansion connector and a size of 36.5x31.5mmCM-BF537E: Blackfin Processor Module powered by Analog Devices single coreADSP-BF537 processor; up to 600MHz, 32MB RAM, 4MB Flash,integrated TP10/100 Ethernet physical transceiver, 120 pin expansionconnector and a size of 36.5x31.5mmCM-BF537U: Blackfin Processor Module powered by Analog Devices single coreADSP-BF537 processor; up to 600MHz, 32MB RAM, 4MB Flash,integrated USB 2.0 Device, 120 pin expansion connector and a size of36.5x31.5mmTCM-BF537: Blackfin Processor Module powered by Analog Devices single coreADSP-BF537 processor; up to 500MHz, 32MB RAM, 8MB Flash,28x28mm, 120 pin expansion connector, Ball Grid Array or BorderPads for reflow soldering, industrial temperature range -40°C to+85°C.CM-BF561: Blackfin Processor Module powered by Analog Devices dual coreADSP-BF561 processor; up to 2x 600MHz, 64MB RAM, 8MBFlash, 120 pin expansion connector and a size of 36.5x31.5mmCM-BF527: From Q3 '07 a new Blackfin Processor Module powered by AnalogDevices single core ADSP-BF527 processor will be available; keyfeatures are USB OTG 2.0 and Ethernet. 2x120pin expansionconnectors are backwards compatible to other Core Modules.CM-BF548: From Q3 '07 a new Blackfin Processor Module powered by AnalogDevices single core ADSP-BF548 processor will be available; keyfeatures are 64MB DDR SD-RAM 2x100pin expansion connectors.Development Boards:EVAL-BF5xx: Low cost Blackfin processor Evaluation Board with one socket forany Bluetechnix Blackfin Core Module. Additional periphery isavailable, such as a SD-Card.DEV-BF5xxDA-Lite: Get ready to program and debug Bluetechnix Core Modules with thistiny development platform including a USB Based Debug Agent. TheDEV-BF5xxDA-Lite is a low cost starter development systemincluding VDSP++ Evaluation Software License.DEV-BF5xx-FPGA: Backfin Development Board with two sockets for any combination ofBlackfin Core Modules. Additional periphery is available, such asSD-Card, Ethernet, USB host, multi-port JTAG including a USBbased Debug Agent, connector for a LCD-TFT Display and connectorfor a digital camera system. A large on-board SPARTAN-3 FPGAand Soft IPs make this board the most flexible Blackfin developmentplatforms ever developed.Available Q2 2007EXT-Boards: The following Extender Boards are available: EXT-BF5xx-Audio,EXT-BF5xx-Video, EXT-BF5xx-Camera, EXT-BF5xx-Exp, *EXT-BF5xx-LVDS, *EXT-BF5xx-ETH-USB, *EXT-BF5xx-AD/DA.Additional boards based on customer request*Available Q2 2007Software Support:BLACKSheep: The BLACKSheep VDK is a multithreaded framework for theAnalog Devices Blackfin processor family that includes driversupport for a variety of hardware extensions. It is based on the real-time VDK kernel included within the VDSP++ developmentenvironment.LabVIEW: LabVIEW embedded support for the CM-BF537E, CM-BF537U andTCM-BF537 Core Modules based on the BLACKSheep VDK driverFramework.uClinux: All the Core Modules are supported by uClinux. The required bootloader and uClinux can be downloaded at .BLACKFIN Design ServiceBased on over three years Blackfin experience Bluetechnix offers development assistance as well as custom design services and software development.1 IntroductionThe CM-BF533 is a tiny, high performance and low power DSP/RISC core module incorporating Analog Devices Blackfin family of processors. The module allows easy integration into high demanding very space and power limited applications.1.1 OverviewThe Core Module CM-BF533 consists of the following components:Figure 1-1: Main Components of the CM-BF533 module▪Analog Devices Blackfin Processor BF533o ADSP-BF533SKBCZ600 (0°-70°C) Standard mounto ADSP-BF533SBBCZ500 (-40°-85°C) Option upon request▪32 MB SDRAMo SDRAM clock up to 133 MHzo MT48LC16M16A2BG-7 (16Mx16 at 3.3 V)▪2MB of Addressable Flasho ITLRC28F320J3C110 (2Mx16 at 3.3 V; 2MByte addressable only)o Additionally flash memory can be connected through the expansion board as parallel flash using asynchronous chip select lines or as a SPI flash.▪Low Voltage Reset Circuito Resets module if power supply goes below 2.93 V for at least 140 ms▪Dynamic Core Voltage Controlo Allows to adjust core voltage by setting software registers at the Blackfin Processoro Core voltage range: 0.8 – 1.32V▪Expansion Connector Ao Data Buso Address Buso Control Signalso Power Supply▪Expansion Connector Bo SPORT 0 and SPORT 1o JTAGo UARTo SPIo PPI (Parallel Port Interface)o GPIO’s1.2 Benefits▪The CM-BF533 is very compact and measures only 36.5x31.5mm▪Allows quick prototyping of product that comes very close to the final design ▪Reduces development costs, faster time to market▪Very cost effective for small and medium volumes1.3 Applications▪Generic high performance signal processor module▪Internet Connected Embedded System▪High performance web camera▪Robotics: Tiny processor module for mobile robots2 Specification2.1 Functional SpecificationFigure 2-1: Detailed Block DiagramFigure 2-1 shows a detailed block diagram of the CM-BF533 module. Beside the SDRAM control pins the CM-BF533 has all other pins of the Blackfin processor at its two main 60 pin connectors.Dynamic voltage control allows reducing power consumption to a minimum adjusting the core-voltage and the clock frequency dynamically in accordance to the required processing power.A low voltage reset circuit guarantees a power on reset and resets the system when the input voltage drops below 2.93V.2.2 Boot ModeDefault Boot Mode = 00 (BMODE1 = LOW, BMODE0 = LOW)BMODE0, BMODE1 has internal pull-down resistorConnect BMODE0 to Vcc and leave BMODE1 pin open for Boot Mode 01 (equals to 8 or 16 bit PROM/FLASH boot mode), this is the default boot mode of the Blacksheep software. See Blackfin Datasheets or Eval/DevBoard manuals for more details.2.3 Memory MapTable 2-1: Memory Map2.4 Electrical Specification2.4.1 Supply Voltage▪ 3.3 V DC +/-10%2.4.2 Supply Voltage Ripple▪100 mV peak to peak 0-20MHz2.4.3 External Oscillator Frequency▪25MHz2.4.4 Real Time Clock Crystal▪32.768kHz2.4.5 Supply Current▪Maximumsupplycurrent:**********▪Operating conditions:o Processor running at 600MHz, Core Voltage 1.2V, SDRAM 20% bandwidth utilization at 130MHz: 150mAo Processor running at 300MHz, Core Voltage 0.8V SDRAM 20% bandwidth utilization at 130MHz: 90mA2.5 Environmental Specification2.5.1 TemperatureDevelopment Version:▪Operating at full 600MHz: 0 to + 70° CIndustrial Version: (Only available upon request at a MOQ)2.5.2 HumidityOperating: 10% to 90% (non condensing)3 CM-BF533 (Connector Version)3.1 Mechanical OutlineTOP VIEWAll dimensions are given in millimeters!P336.517.57.059.2532.46.8526.7528.0531.522.450.60.35Ø0.652.551.7P1P27.759.0514.653452Figure 3-1: Mechanical outline and Bottom ConnectorsThe mechanical outline represents a top view of the connectors placed at the bottom of the core board.The module is shipped with two 60pin connectors.Figure 3-2: Side View with Connector mountedThe total minimum mounting height including receptacle at the motherboard is 6.1 mm.3.2 Connector FootprintIf the connector version (2x Hirose 0.6mm pitch) is used, the footprint for the baseboard may look as shown in Figure 3-3.For the baseboard the following connectors have to be used:Table 3-1: Baseboard connector typesThe connectors on the CM-BF533 are of the following type:Table 3-2: Module connector types36.526.7531.57.756.85Figure 3-3: Connector Footprint for Baseboard3.3 Top Mounted ConnectorThe optionally mounted connector P4 will not be supported in future versions.Figure 3-4: TOP VIEW3.4 Schematic Symbol (Signals of P1 and P2)SPORT0SPORT1PPIUARTSPIJTAGDataBusAddr.BusControlSignals Figure 3-5: Schematic Symbol of Module3.5 Connectors Pin Assignment P1 – (1-60)Table 3-3: Connector P1 pin assignmentAll Pin names of the connectors correspond to the names found in the Blackfin BF533 datasheet from Analog Devices.3.6 Connector Pin Assignment P2 – (61-120)Table 3-4: Connector P2 pin assignmentNon processor Pins:CLK_OUT: 25MHz buffered output clock of main oscillatorAll other pins are connected directly to the respective ADSP-BF533 processor pins.For details about the meaning of the signal names consult the Blackfin ADSP-BF533 datasheet.3.7 ITU656 Camera Connector P3 (1-22)The ITU656 connector has been tested only for the OmniVision cameras available in our camera kit Kit-CAM-OV. It is not recommended to use this connector!Table 3-5: Connector P3 pin assignment3.8 Connector P4 (1-10)The top optionally mounted connector P4 can be used as a stand-alone connector for a system requiring only power supply and one or two communication ports (UART and SPI)Table 3-6: Connector P4 pin assignment4 Test Points4.1 Footprint – Test Points9.859.251.25.057.4510.751.7524.0526.4529.7520.751233031322960596162909192119120Ø0.731.536.5Figure 4-1: Test Points of the Core Module5 Application Examples5.1 Sample ApplicationIn this minimum configuration the CM-BF533 is used as a high performance SPI-based co-processor module.Figure 5-1: Minimum Configuration with SPI and JTAG Connector5.2 Stand-alone Camera SystemThe CM-BF533 module can be used as a stand-alone module for a camera system requiring only power supply and the direct attachment of a compatible video camera. A camera kit including drivers can be purchased from Bluetechnix: KIT-CAM-OV (O.Nr 100-9901) The digital ITU656 camera directly connects to P3 while the power supply and any of two communication ports (SPI and UART) can be connected to the 10 pin P4 connector as well as over the large connectors P1 and P2 at the bottom.3.3 V Power, SPI, UARTFigure 5-2: Stand-alone Camera System5.3 Generic Signal Processing SystemFigure 5-3: Block Diagram – Analog Signal Processing Module5.4 Coprocessor ApplicationFigure 5-4: Block Diagram – Coprocessor Module5.5 Digital Video SystemFigure 5-5: Block Diagram: Digital Video System5.6 Design ServicesBluetechnix offers custom design services and software development.6 Software Support6.1 BLACKSheepThe Core Module is delivered with a pre-flashed basic version of the BLACKSheep VDK multithreaded framework. It contains a boot-loader for flashing the Core Module via the serial port.Please mind the software development documents.6.2 uClinuxThe Core Module is supported by the open source platform at . Since the Core Modules are pre-flashed with BLACKSheep you have to flash uBoot first. For flashing the uBoot you can use the BLACKSheep boot-loader.7 Known BugsTable 7-1: Known Bugs8 Product ChangesTable 8-1: Product Changes9 Document Revision HistoryTable 9-1: Revision HistoryA List of Figures and TablesFiguresFigure 1-1: Main Components of the CM-BF533 module (1)Figure 2-1: Detailed Block Diagram (3)Figure 3-1: Mechanical outline and Bottom Connectors (6)Figure 3-2: Side View with Connector mounted (6)Figure 3-3: Connector Footprint for Baseboard (7)Figure 3-4: TOP VIEW (8)Figure 3-5: Schematic Symbol of Module (9)Figure 4-1: Test Points of the Core Module (13)Figure 5-1: Minimum Configuration with SPI and JTAG Connector (14)Figure 5-2: Stand-alone Camera System (15)Figure 5-3: Block Diagram – Analog Signal Processing Module (15)Figure 5-4: Block Diagram – Coprocessor Module (15)Figure 5-5: Block Diagram: Digital Video System (16)TablesTable 2-1: Memory Map (4)Table 3-1: Baseboard connector types (7)Table 3-2: Module connector types (7)Table 3-3: Connector P1 pin assignment (10)Table 3-4: Connector P2 pin assignment (11)Table 3-5: Connector P3 pin assignment (12)Table 3-6: Connector P4 pin assignment (12)Table 7-1: Known Bugs (18)Table 8-1: Product Changes (19)Table 9-1: Revision History (20)。

Micromaster440 调试参数

Parameter (参数)Value (设定值)Description (描述)P10802最低频率P108250最高频率P112010斜坡上升时间-电动机从静止状态加速到最高频率所用的时间(如果设定的斜坡上升时间过短,就可能导致变频器跳闸--过电流)P112110斜坡下降时间-电动机从最高频率减速到静止停车所用的时间(如果设定的斜坡下降时间过短,就可能导致变频器跳闸--过电流/过电不用快速调试1结束快速调试,并按工厂设置使参数复位2结束快速调试3结束快速调试,只进行电动机数据的计算P00033P07331变频器运行准备就绪P00101P0700.01BOP 控制有效P0700.16COM 链路的通讯板(CB)设置P0733.01P0733.11P08102090.15(.F.)远程控制 (2090.F) / MCC 控制 0P0918XX 地址49CB.Address 通讯地址P1000.01电动电位计设定P1000.16通过COM 链路的CB 设定P2051.052P2051.121P2051.227P2051.353P2051.432P2051.535P0601.01PTC (正温度系数)热敏元件 第一驱动数据组(DDS )P0601.11PTC (正温度系数)热敏元件 第二驱动数据组(DDS )P0604XX 电动机温度保护的门限值0除报警外无应对措施1报警并降低最大电流Imax (引起输出频率降低)2报警和跳闸(F0011)P062520电动机运行的环境温度P0640150%电动机过载因子P3900结束快速调试P0610电动机过温应对措施↓↓进入数据计算Busy...↓主电源接触器吸合第一步完成,重新核对参数↓调设状态字 P2051↓温度保护项调设。

西门子变频器说明书下载

6SE6400-1PB00-0AA0 6SE6400-1DN00-0AA0 6SE6400-0EN00-0AA0

MICROMASTER 变频器

410

420

430

440

可以进行配置的组合

操作面板

BOP/OP

AOP

BOP-2

模块

PROFIBUS 通讯模块

4

Siemens DA51.2 • 2002

DeviceNet 通讯模块

0.12 kW 至 0.75 kW 100 V 至 120 V,单相交流 200 V 至 240 V,单相交流

控制

过程控制 输入 输出 与自动化系统的接口 附加特点

线性 V/f 控制特性 多点设定的 v/f 控制特性 (可编程的 v/f 控制特性) FCC (磁通电流控制)

-

3 个数字输入 1 个模拟输入

快速电流限制 (FCL),防止 运行中不应有的跳闸

MICROMASTER 410

说明

快速的,可重复的数字输入 响应时间

采用高分辨率的 10 位二进 制模拟输入,实现输入的精 确设定

具有一个跳转频率

用于 (中性点) 不接地的供 电电源 (IT电源) 时具有可折

卸的“Y”形接线电容器

采用 USS 协议的 RS 485 串行通讯接口

0.12 kW 至 11 kW 200 V 至 240 V,单相交流 200 V 至 240 V,三相交流 380 V 至 480 V,三相交流

线性 V/f 控制特性 多点设定的 v/f 控制特性 (可编程的 v/f 控制特性) FCC (磁通电流控制)

内置 PI 控制器

3 个数字输入 1 个模拟输入

线性 v/f 控制特性 多点设定的 v/f 控制特性 (可编程的 v/f 控制特性) FCC (磁通电流控制) 矢量控制 内置的 PID 控制器 (带参数自整定功能) 6 个数字输入 2 个模拟输入 1 个用于电动机过热保护的 PTC/KTY 输入 2 个模拟输出 3 个继电器输出 是 SIMATIC S7-200,SIMATIC S7-300/400 (TIA) 或 SIMOTION 自动化系统的理想配套设备。

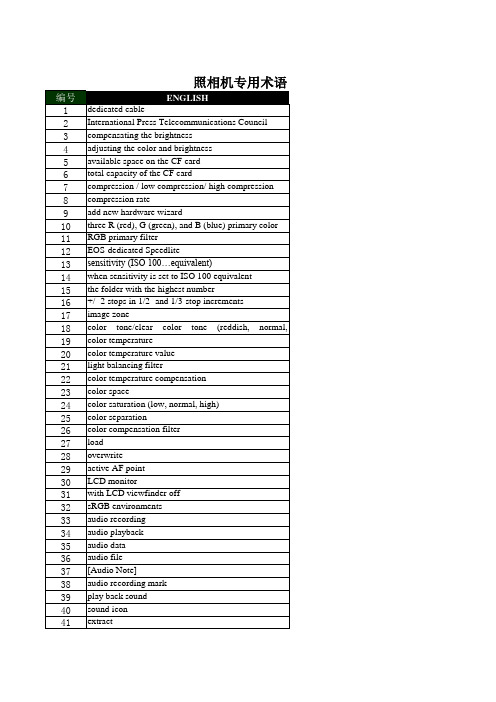

相机术语中英文对照表

62 standard white 63 false color 64 image recording quality 65 recording image quality 66 recording pixel count 67 image protection and erase 68 image recording format 69 recording media 70 cloudy 71 creative zone 72 processing 73 processing parameters 74 optical viewfinder 75 active AF point indicator 76 merge 77 frame

126 tab sheet 127 [Remove checkmark] button 128 autoflash system

129 noise reduction for long exposures 130 communication 131 TIFF format 132 TTL auto white balance 133 TTL 3 point AiAF (1 point measurement is possible) 134 apply 135 digital AF/AE SLR 136 digital signature 137 digital zoom 138 digital terminal 139 digital exposure compensation 140 digital exposure compensation amount

transmitting images to or from a CF card (while 141 connecting to a computer) 142 Design rule for Camera File system (sRGB143 cDoemsipglniarnutl)e for Camera File system, DPOF-compliant

533mcp 参数

533mcp 参数什么是533mcp?533mcp是一种参数,用于描述和控制电子设备的性能和功能。

533mcp代表着五个不同的参数,分别是:5G网络、3GB RAM、3GB存储容量、5000mAh电池容量和13MP相机。

5G网络5G网络是下一代移动通信技术,提供更快的速度、更低的延迟和更大的容量。

它将带来更好的网络体验,支持更多的设备连接和更快的数据传输。

533mcp中的5G网络意味着设备可以在5G网络下进行高速的互联网访问,观看高清视频、玩游戏和下载文件都将更加快速和稳定。

3GB RAMRAM(随机存取存储器)是电子设备中的一种内存,用于临时存储正在运行的程序和数据。

533mcp中的3GB RAM表示设备具有3GB的内存,可以同时运行多个应用程序和任务,提供流畅的用户体验。

较大的RAM容量还可以提高设备的多任务处理能力和性能。

3GB存储容量存储容量是指设备用于存储数据和文件的空间大小。

533mcp中的3GB存储容量意味着设备具有3GB的可用存储空间,可以存储大量的应用程序、照片、视频和文件。

用户可以轻松地保存和访问他们的个人和工作文件,而不必担心空间不足的问题。

5000mAh电池容量电池容量是指电池存储的电荷量,它决定了设备能够提供的使用时间和续航能力。

533mcp中的5000mAh电池容量表示设备具有5000毫安时的电池容量,可以提供较长的使用时间。

用户可以更长时间地使用设备,而不必频繁充电。

高容量的电池还可以支持设备在高负载情况下的稳定运行。

13MP相机相机是设备中的一个重要功能,用于拍摄照片和录制视频。

533mcp中的13MP相机表示设备具有1300万像素的摄像头。

较高的像素数意味着设备可以拍摄更清晰、更详细的照片和视频。

用户可以捕捉到更多的细节,并享受更好的拍摄体验。

总结533mcp参数包括5G网络、3GB RAM、3GB存储容量、5000mAh电池容量和13MP相机。

这些参数提供了一种全面、高性能的电子设备体验。

RICOH MP C3003 MP C3503 MP C4503 MP C5503 MP C60