M44C890-H中文资料

CC4H-4S中文资料

Multiport Analog Modem CardBenefits• High-density , V .92 connections • V .34/33.6K Super G3 fax with Error Correction Mode • Supports leading remote access and fax software • Universal PCI and PCI ExpressThe MultiModem ® ISI server card is ideal for small- to mid-sized companies requiring analog dial-up remote access or a dedicated fax server solution. It provides up to eight built-in V .92/56K modems for cost-effective,high-density , server-based remote access. The MultiModem ISI server card also offers V .34/33.6K Super G3 fax and Error Correction Mode, that can reduce fax transmission time by more than half when compared to traditional fax modems.Features• Four or eight integrated V .92/56K modems• V .92/56K download speeds and 48K upload speeds when connecting with V .92 servers • Class 1.0 and Class 2.1 faxing at speeds to V .34/33.6K bps (Super G3)• Error Correction Mode (ECM) provides fast and reliable fax transmissions • V .44 compression improves data throughput rates • U.S. Caller ID reporting• Sustained data rates to 460.8K per port • Phone cables included• Compatible with Windows ® 2000/XP/2003/Vista/2008 (32-bit/64-bit) and Linux • Up to 4 cards per server• Remote configuration for centralized setup and mangement • 3.3V and 5V Universal PCI or PCI Express models • Compatible with PCI-X slot (Universal PCI models)• Flash memory for easy updates • T wo-year warrantyMultiModem ®ISIWorld Headquarters Tel: (763) 785-3500 (800) EMEA Headquarters Multi-Tech Systems (EMEA)United KingdomTel: +(44) 118-959 7774Multi-Tech Systems (EMEA) FranceTel: +(33) 1 49 19 22 06HighlightsCost-Effective & Scalable. The MultiModem ISI server card provides four or eight dial-up sessions using only one server slot. When demand exceeds one modem card, you can simply add up to three additional cards.V.92 Dial-out Connections. The MultiModem ISI server card supports V .92/56K dial-out and V .34/33.6K dial-inconnections. With V .92 dial-out, you can achieve an upload speed of 48K bps (30% increase over V .90 modems).Enhanced Fax Features. The MultiModem ISI server card supports V .34 fax and Error Correction Mode providingsignificant performance and reliability enhancements over previous fax standards. V .34 sends and receives faxes at speeds up to 33.6K, more than double the speed of the V .17/14.4K fax standard. Error Correction Mode adds reliablility while increasing performance of faxtransmissions. Together these enhancements increase the performance of the MultiModem ISI server card to levels previously only found in more expensive dedicated fax boards and machines.V.44 Compression. V .44 compression standard improves V .42bis data compression anywhere from 20 to 60%, up to as much as 200% for certain types of highly compressible data. This compression technique enables data throughput rates of higher than 300K bps.Simplify Remote Access. The fully-integrated MultiModem ISI server card is easy to set up and manage. You only have to connect the phone lines. There are no external modems and power cords to hassle with; plus it saves back office space since the modems are on the prehensive Service and Support. The Multi-Techcommitment to service means we provide a two-year product warranty and service that includes free telephone technical support, 24-hour web site and ftp support.Ordering InformationProductDescriptionRegion ISI5634UPCI/8 V .92, 8-Modem Card - Universal PCI Global ISI5634UPCI/4 V .92, 4-Modem Card - Universal PCI Global ISI9234PCIE/8 V .92, 8-Modem Card - PCI Express Global ISI9234PCIE/4V .92, 4-Modem Card - PCI ExpressGlobalSpecificationsModemData: V .92, V .90, enhanced V .34, V .32bis, V .22bis Error Correction: V .42, MNP Class 3 & 4Data Compression: V .44, V .42bis, MNP Class 5FaxStandards: V .34, V .17, V .29, V .27ter, V .21, T.30, T.30Annex A, T.30 Annex F , T.31, T.31 Annex B, T.32 Annex C, TR29.2 Class 2 RecommendationRates: 33.6K, 31.2K, 28.8K, 26.4K, 24K, 21.6K, 19.2K, 16.8K, 14.4K, 12K, 9600, 7200, 4800, 2400, 300 bps Error Correction: ECMCompression: MH (T.4), MR (T.4), & MMR (T.6)Conversion: Real time (on-the-fly) compression conversionCommands: Class 1, 2, 1.0, 2.0, 2.1Bus Type3.3V & 5V Universal PCI or PCI Express (x1)Operating System SupportWindows 2000/XP/2003/Vista/2008 (32-bit/64-bit) & LinuxCablingFan out cable with 1 or 2 RJ45 connectors & 4 or 8 RJ11 connectorsPhysical DescriptionUniversal PCI Models:13.87" L × 4.97" W; 8.7 oz (35.2 cm × 12.6 cm; 247 g)PCI Express Models:13.87" L × 4.97" W; 8.5 oz (35.2 cm × 12.6 cm; 241 g)Operating EnvironmentTemperature Range: +23° to +140° F (-5° to +60° C)ApprovalsCE MarkEMC: FCC Part 15 Class B, EN 55022, EN 55024Safety: UL/cUL 60950-1, EN 60950-1, AS/NZS 60950:2000, CCCTelecom: 47CFR Part 68, CS03, TBR21Other countries also includedCopyright © 2008 by Multi-Tech Systems, Inc. All rights reserved.6/08 86000323Made in Mounds View, MN, U.S.A.Features and specifications are subject to change without notice.Trademarks / Registered Trademarks: MultiModem, Multi-Tech, and theMulti-Tech logo: Multi-Tech Systems, Inc. / All other products and technologies are the trademarks or registered trademarks of their respective holders.。

CH412 中文手册说明书

ESD 保护芯片CH412中文手册 版本:1B 1、概述CH412是四路ESD 保护二极管阵列,能够承受IEC 61000-4-2规定的最高±15KV 人体模型、±8KV 接触放电以及±15KV 气隙放电的ESD 脉冲,用于电子产品对外接口中的高速信号和差分信号以及通用信号的ESD 保护。

CH412K 提供4通道低电容二极管保护和TVS 瞬态电压抑制器箝位,适用于高速和中低速信号,可以用于USB 超速、高速和全速以及低速信号保护。

CH412Z 提供4通道TVS 瞬态电压抑制器箝位,适用于中低速信号,可以用于USB 全速和低速信号保护。

CH412K CH412Z2、特点● 支持±15KV 人体模型HBM 。

● 支持±8KV 接触放电。

● 支持±15KV 气隙放电。

● CH412K :内部4路独立箝位二极管,典型值1pF 的低输入电容,适用于高速和中低速信号。

● CH412Z :内部4路TVS 箝位保护,典型值20pF 的输入电容,适用于中低速信号。

● 采用SOT 小体积晶体管级贴片无铅封装,兼容RoHS 。

3、封装封装形式 塑体宽度 引脚间距 封装说明 订货型号 SOT363 1.25mm 49mil 0.65mm 26mil 小型6脚贴片 CH412K SOT353 1.25mm 49mil 0.65mm 26mil 小型5脚贴片 CH412Z 注:1、封装体积较小,正面印字仅有代号而不含全部型号,例如CH412Z 代号是12。

2、盘装,每盘整包装数量为3000只,可以零售,但是零售时不会逐个清点数量。

IO4 IO3 IO3 VCC IO44、型号CH412B已经停产,请换用CH412K,多出的两个通道可以悬空或并联(低速时)。

4、引脚CH412K 引脚号CH412Z引脚号引脚名称类型引脚说明2 2 GND 电源公共接地端,必须直接连接到全局地5 无VCC 电源正电源端,必须靠近引脚对GND连接0.1μF电容,用于USB信号保护时通常为3.3V(或者5V),用于其它信号须同被保护芯片的电源电压(2V~5V)1,3,4,6 1,3,4,5 IO1~IO4 信号ESD保护通道,与被保护芯片的信号引脚并联5、应用说明CH412设计用来与被保护芯片内置的ESD保护一起工作。

XMC4000中文参考手册-第12章 LED和触摸感应(LEDTS)

LEDTS 的框图见图 12-1。

参考手册 LEDTS,V1.5

12-2

V1.2, 2012-12 请遵守产品信息使用协议

Device Guide XMC4500 XMC4000 家族

LED 和触感 (LEDTS)

图 12-1

LEDTS 方框图

参考手册 LEDTS,V1.5

12-3

V1.2, 2012-12 请遵守产品信息使用协议

为下一个时间片设置行模式 为下一个时间片设置比较值 评估当前时间片的功能(尤其是分析/调试)

参阅 12.9.1 节得到位段 FNCOL 译码来确定当前有效的时间片的信息。 (已扩展的)时间帧中断指示一个触摸输入行 TSIN[x] 已经被感应到(在连续帧中的一次或几 次),应用层软件可以,例如:

在每个配置的时间片持续时间内,启用一个 LED 列引脚,可以同时间控制最多 8 个 LED。 COL [X]到引脚的分配是可配置的,这可以为具体应用的引脚提供选择。器件引脚的电流能力 也是确定 LED 功能引脚分配的考虑因素。 产品数据表提供与 LED 驱动器相关的所有 I / O 参数的数据。 12.4 触摸感应

注:该章提及 LED 或者触摸感应引脚,比如,‘引脚 COL[x]’,‘引脚 TSIN[x]’。在所有 例子中,它参考选择 LED/触摸感应功能的用户配置引脚(s)。更多详细信息参考 12.9.5 节。

表 12-2 使用分类 非机械开关 LED 反馈 简单 PWM 12.1.2 框图 LEDTS 应用 应用 HMI HMI PWM

参考手册 LEDTS,V1.5

12-8

V1.2, 2012-12 请遵守产品信息使用协议

Device Guide XMC4500 XMC4000 家族

菲尔普斯4100系列50英寸全高清LED电视说明书

Philips 4000 series Full HD LED TV with Digital Crystal Clear127 cm (50")Full HD LED TV DVB-T/T2/C50PFT4109Full HD LED TVWith Digital Crystal ClearEveryone in your home will enjoy the crisp, clear picture of the Philips 4100 series Full HD LED TV. The minimalist design, vivid images, and great sound make it the ideal choice for any room in your house.Beyond entertainment, it’s interior design •Ultra Narrow bezel gives you more picture to love •Modern design complements today's interiorWatch together—beautifully•Digital Crystal Clear: precision you’ll want to share•Full HD LED TV—brilliant LED images with incredible contrast •100Hz PMR for fluid moving imagesTelevision viewing at your convenience•Two HDMI inputs and Easylink for integrated connectivity •USB for multimedia playbackHighlightsUltra narrow bezelTraditional TVs have a bezel that wraps around the TV like a picture frame. Our Ultra Narrow bezel is modern and thin, so you have more picture to enjoy.Modern DesignDesigned with a contemporary look to blend with your décor. Because your TV should look as beautiful off as it does on.Digital Crystal ClearFor natural pictures from any source, Philips created Digital Crystal Clear. Because whether you indulge in your favorite soap, the news, or have friends over to watch a video—you'llenjoy it all in optimal contrast, color and sharpness.Full HD LED TVPicture Quality matters. Regular HDTVs deliver quality, but you expect more. Imagine crisp detail paired with high brightness, incredible contrast and realistic colors for a true to life picture.100Hz Perfect Motion RateNothing beats the adrenaline rush of gaming, fast paced sporting events or action films. That's why this Philips TV has 100Hz Perfect Motion Rate; so you’ll enjoy fluid moving images. Because even though your pulse may jump, the image you’re watching shouldn’t.Two HDMI inputs with EasylinkAvoid cable clutter with a single HDMI cable to carry both picture and audio signals from your devices to your TV. HDMI uses uncompressed signals, ensuring the highest quality from source to screen. Together with PhilipsEasylink, you’ll need only one remote control to perform most operations on your TV, DVD, Blu-ray, set top box or home theatre system.USB (photos, music, video)Share the fun. Connect your USB memory-stick, digital camera, mp3 player or other multimedia device to the USB port on your TV to enjoy photos, videos and music with theeasy to use onscreen content browser.Issue date 2019-06-28 Version: 5.0.112 NC: 8670 001 11457 EAN: 87 12581 71024 8© 2019 Koninklijke Philips N.V.All Rights reserved.Specifications are subject to change without notice. Trademarks are the property of Koninklijke Philips N.V. or their respective owners.SpecificationsPicture/Display•Display: LED Full HD•Diagonal screen size: 50 inch / 127 cm•Panel resolution: 1920x1080p•Aspect ratio: 4:3/16:9•Brightness: 250 cd/m²•Picture enhancement: Digital Crystal Clear, 100 Hz Perfect Motion RateSmart Interaction•Program: Pause TV, USB Recording*•Ease of Use: One-stop Home button •Firmware upgradeable: Firmware auto upgrade wizard, Firmware upgradeable via USB •Screen Format Adjustments: Advance - Shift, Basic - Fill Screen, Fit to Screen, Stretch, Zoom •Signal strength indication•Teletext: 1000 page Hypertext•Electronic Program Guide*: 8 days Electronic Program GuidSound•Output power (RMS): 20W•Sound Enhancement: Incredible Surround, Clear Sound, Auto Volume Leveller, Bass Enhancement Connectivity•Number of HDMI connections: 3•Number of USBs: 2•Number of scarts(RGB/CVBS):1•Other connections: CI+1.3 certified, Antenna IEC75, Common Interface Plus (CI+), Digital audio out (optical), Audio in (DVI), Headphone out, Service connector•EasyLink (HDMI-CEC): Remote control pass-through, System standby, Auto subtitle shift (Philips)*, Pixel Plus link (Philips)*, One touch play, System audio controlMultimedia Applications•Video Playback Formats: Containers: AVI, MKV, H264/MPEG-4 AVC, MPEG-1, MPEG-2, MPEG-4, WMV9/VC1•Subtitles Formats Support: .AAS, .SMI, .SRT, .SSA,.SUB, .TXT•Music Playback Formats: AAC, AMR, LPCM, M4A,MP3, MPEG1 L1/2, WMA (v2 up to v9.2)•Picture Playback Formats: JPEG, BMP, GIF, JPS,PNG, PNSSupported Display Resolution•Computer inputs: up to 1920x1080 @ 60Hz•Video inputs: 24, 25, 30, 50, 60 Hz, up to1920x1080pTuner/Reception/Transmission•Digital TV: DVB-T/T2/C•MPEG Support: MPEG2, MPEG4•Video Playback: NTSC, PAL, SECAMPower•Mains power: AC 220 - 240 V 50/60Hz•Ambient temperature: 5 °C to 35 °C•Eu Energy Label power: 62 W•Annual energy consumption: 90 kW·h•Energy Label Class: A+•Standby power consumption: < 0.3 W•Off mode power consumption: < 0.3 W•Power Saving Features: Auto switch-off timer, Ecomode, Picture mute (for radio)Dimensions•Box dimensions(W x H x D):1220 x 750 x 160 mm•Set dimensions (W x H x D): 1125 x 656 x 94 mm•Set dimensions with stand (W x H x D):1125 x 709 x 270 mm•Product weight: 10.7 kg•Product weight (+stand): 13.1 kg•Weight incl. Packaging: 15.5 kg•VESA wall mount compatible: 400 x 200 mmAccessories•Included accessories: Remote Control, Table topstand, Power cord, Quick start guide, Legal andsafety brochure, Warranty Leaflet*Software upgrade required for Pause TV and USB recording. Formore details about the software update, please visit/TV and click on support.*The TV supports DVB reception for 'Free to air' broadcast. SpecificDVB operators may not be supported. An up to date list can befound in the FAQ section of the Philips support website. For someoperators Conditional Access and subscripction are required.Contact your operator for more information.*Energy consumption in kWh per year, based on the powerconsumption of the television operating 4 hours per day for 365days. The actual energy consumption will depend on how thetelevision is used.*(Philips) only compatible with specific Philips player device.*EPG and actual visibility (up to 8 days) is country and operatordependent.。

XMC4000中文参考手册-第06章 灵活的CRC引擎(FCE)

灵活的CRC引擎(FCE)6 灵活的CRC引擎(FCE)FEC提供一个循环冗余码(CRC)算法的并行执行。

现行XMC4500微控制器的FCE版本能实现符合IEEE802.3的以太网CRC32,CCITT的CRC16和SAE J1850的CRC8多项式算法。

FCE的基本目标是作为一个为使用CRC识别标志的软件应用或操作系统服务的硬件加速引擎。

FCE作为一个标准外围总线从设备操作,通过一组配置和控制寄存器实现完全控制。

不同的CRC算法彼此相互独立,它们可以同时用在不同的软件任务上。

注:在6-11页描述为“寄存器”的FCE内核寄存器名称是参考于一个产品参考手册上的模块名称前缀“FCE_”。

参考文献[5] 一个无痛的CRC错误检测算法指南,Ross N.Williams[6] 互联网应用的32字节CRC,Philip Koopman,独立系统和网络(DSN)国际会议,2002相关标准和规范[7] IEEE 802.3 的以太网32位CRC表6-1 FCE涉及的缩写词CRC 循环冗余码FCE 灵活的循环冗余码引擎IR 输入寄存器RES 结果STS 状态CFG 配置6.1 概述本节提供了FCE模块的功能,应用和逻辑结构的概述。

6.1.1 功能FCE提供如下功能:• FCE执行如下的循环冗余码多项式:灵活的CRC引擎(FCE)— CRC内核0和1:IEEE802.3 CRC32以太网多项式:0x04C11DB71) - x32+x26+x23+x22+x16+x12+x11+x10+x8+x7+x5+x4+x2+x+1 —CRC内核2:CCITT CRC16 多项式:0x1021 - x16+x12+x5+1— CRC内核3:SAE J1850 CRC8多项式:0x1D - x8+x4+x3+x2+1• 并行CRC实现—通过FCE计算的数据块会是一个多重二次多项式—通过FCE计算的数据块的开始地址会被排列到二次多项式中• 寄存器接口:— 输入寄存器— CRC寄存器— 配置寄存器启用控制CRC操作和对信息的末端进行自动校验。

兄弟电子A4无线4合一彩色打印机MFC-J890DW说明书

A4 wireless 4-in-1colour inkjet printerMFC-J890DWwww.brother.euWIRELESSA range of connectivity options for the entire houseSleek and cleverly compact, the MFC-J890DW brings affordable, high-quality printing to your home. With a range of connectivity options to suit, connecting from multiple devices is quick and easy and you don’t even have to be in the same room either thanks to wireless printing.Easy to use with minimal interventionDesigned to make tasks easier, the MFC-J890DW comes with an intuitive 6.8cmcolour touchscreen for easy user control and a 20 sheet Automatic Document Feeder that allows you to scan and copy multi-page documents... perfect for multi-tasking!* Approx declared yield value in accordance with ISO/IEC 19798A4 Print. Copy. Scan.Fax. Cleverly compact.Space saving all-in-one A4 inkjet with touchscreen, 2-sided print, automatic feeding, NFC and wired/wireless connectivity.MFC-J890DW1 Approx declared yield value in accordance with ISO/IEC 247112 Calculated with 80g/m² paper3 Windows ® & Mac ® only4 Windows ® only5 Optional free download from the Brother Solutions Centre 6 Must be web connected7 Vertical x horizontal8 Requires Brother software9 M aximum number of printed pages per month can be used to compare designed durability between like Brother products. Formaximum printer life, it is best to choose a printer with a duty cycle that far exceeds your print requirements10 ESAT (based on ISO/IEC 24735). This spec is for ADF models onlyGeneralEngine InkjetInput Paper Capacity 150 sheets 2 standard tray, single sheet manual feed slot ADF20 sheets 2Max. Flatbed Paper Input Width / Height 215.9/297mmControl Panel6.8cm colour Touchscreen LCD On-Screen Programming YesMemory Capacity 128MBSimultaneous Operation YesLocal Interface Hi-Speed USB 2.0Colour PrinterSpeed12ipm mono & 10ipm colour based on ISO/IEC 24734Speed (Fast Mode)Up to 27 pages per minute mono & up to 23 pages per minute colour First Print Out Time 12 seconds Mono 14 seconds Colour Warm-up Time InstantResolution 7Up to 6,000 x 1,200dpi 2-Sided Print YesPaper Handling Size A4, LTR, EXE, A5, A6, Photo (10x15cm), Indexcard (13x20cm),Photo-2L (13x18cm), Com-10, DL Envelope, Monarch, C5, Photo-L (89x127mm)Media weights: Standard & photo Paper Tray 64-220g/m 2(260g/m 2 with Brother BP71 glossy paper only)Media weights Manual Feed Slot64-300g/m 2Media Weights Auto Duplex 64-105g/m 2 Media Weights ADF 64-90g/m 2Paper OutputFace Up – 50 sheets 2Media TypePlain / Inkjet / GlossyBorderless PrintingBorderless printing is available for A4, LTR, A6, Photo, Indexcard, Photo-2L Droplet SizeMinimum droplet size of 1.5pl Colour EnhancementBrother Image Enhancement allows the user to customise colour outputPrinter DriverCompatible with Windows ® 7/8/8.1/10Server 2008/2008R2/2012/2012 R2/ 2016 (Windows Server ® print only), OS X 10.10.x or laterAll specifications correct at time of printingand are subject to change. Brother is a registered trademark of Brother Industries Ltd. Brand product names are registered trademarks or trademarks of their respective companies.Ink Gauge Indication Ink levels can easily bedisplayed on the LCD using the ink management menu Power Save ButtonThis model has an On/Off button on the control panel Wired Network Interface 10/100BASE-TXWireless Network Interface 802.11b/g/nColour Copier Copy Speed6 mono/6 colour ipm ESAT(based on ISO/IEC 24735)10Resolutionup to 1,200 x 1,200dpi(Colour & Mono)Enlargement/Reduction RatioReduce or enlarge document sizes from 25% to 400% in 1% incrementsColour Scanner TechnologyCIS (Contact Image Sensor)Resolution (Optical)Up to 1,200 x 2,400dpiResolution (Interpolated)Up to 19,200 x 19,200dpi8Speed103.35 seconds Mono/4.38seconds ColourA4 @100 DPIGrey Scale256 shades of grey are availablefor copying or scanningScanner DriverThis model is TWAIN and WIAcompliant for Windows®(WIA is Windows® 7/8/10 only)‘Scan To’Allows the user to scan toE-mail, Image, File, USB FlashDrive and Media Cards,SharePoint8 & Web services6SupportingJPEG, BMP, PDF, TIFF, PNGColour DepthThis model has a 30 bit internaland 24 bit external processingcolour scannerMobile / Web Based Printing & Scanning iPrint&Scan(Android)Print directly from or scandirectly to a smart phone ortablet running the AndroidOperating SystemiPrint&Scan(iPad / iPhone / iPod)Print directly from or scandirectly to an iPad / iPhone /iPodiPrint&Scan(Windows® Phone)Print files directly from or scandirectly to a smart phonerunning the Windows® Phone7/8 Operating SystemGoogle Cloud Print 2.06Print most common file typesfrom any Google Cloud Printenabled application.Brother print service pluginPrint directly from Androiddevices without dedicated appAirPrintPrint most common file typesfrom any Apple AirPrint enabledapplicationMopriaPrint using the Mopriaprint serviceCloud Services6Scan to & print from thefollowing cloud services directfrom the control panelGoogle Drive, Dropbox,Evernote, Box and OneDriveMulti CopyUp to 99 copies of the original1 Approx declared yield value in accordance with ISO/IEC 247112 Calculated with 80g/m² paper3 Windows® & Mac® only4 Windows® only5 Optional free download from the Brother Solutions Centre 6 Must be web connected7 Vertical x horizontal8 Requires Brother software9M aximum number of printed pages per month can be used to compare designed durability between like Brother products. For maximum printer life, it is best to choose a printer with a duty cycle that far exceeds your print requirements10 ESAT (based on ISO/IEC 24735). This spec is for ADF models only All specifications correct at time of printing and are subject to change. Brother is a registered trademark of Brother Industries Ltd. Brand product names are registered trademarks or trademarks of their respective companies.Interface Network functionsPrinting, ScanningNetwork ProtocolsTCP/IP, IPv4(IPv6 turned off as default)IPv4ARP, RARP, BOOTP, DHCP,APIPA(Auto IP), WINS/NetBIOSname resolution,DNS Resolver,mDNS, LLMNR responder,LPR/LPD, Custom Raw Port/Port9100,FTP Server, SNMPv1/v2c, TFTP server, ICMP, WebServices (Print/Scan),SNTP Client IPv6NDP, RA, mDNS,LLMNR Responder, DNS Resolver, LPR/LPD,Custom Raw Port/ Port9100, FTP Server, SNMPv1/v2c, TFTP server, Web Services (Print/Scan), SNTP Client, ICMPv6 Wireless SetupWi-Fi Protected Setup™ (WPS) Wireless SecuritySSID (32 chr), WEP 64/128bit, WPA-PSK(TKIP/AES),WPA2-PSK(AES)Network Management Utilities Embedded Web ServerYesBRAdmin Light4&5Setup and LAN managementsoftwareLocal InterfaceHi-Speed USB 2.0Wired NetworkEthernet 10/100BASE-TX AutoNegotiationWireless Network InterfaceBuilt-in 802.11b/g/n Wirelessnetwork interface(Infrastructure Mode)NFC ConnectivityYes, for printing and scanningby the iPrint&Scan AppWi-Fi Direct TMPrint & scan wirelessly withouthaving to go through a wirelessaccess point or networkBrother Apps6Scan to searchable PDFOCR a document and make asearchable PDF fileWired Network InterfaceEthernet 10/100BASE-TXFax forward to CloudForward your incoming faxes tocloud storage service Enlarge text copy Enlarges only the text in a copied documentEasy Scan to Mobile Easy scan to your mobile devices without being connected to a Wi-Fi networkOffice Doc Creator Converts your scanned document into an editable Microsoft Office document Easy Scan to Email Scan directly to an email address without1 Approx declared yield value in accordance with ISO/IEC 247112 Calculated with 80g/m² paper3 Windows® & Mac® only4 Windows® only5 Optional free download from the Brother Solutions Centre 6 Must be web connected7 Vertical x horizontal8 Requires Brother software9M aximum number of printed pages per month can be used to compare designed durability between like Brother products. For maximum printer life, it is best to choose a printer with a duty cycle that far exceeds your print requirements10 ESAT (based on ISO/IEC 24735). This spec is for ADF models only All specifications correct at time of printing and are subject to change. Brother is a registered trademark of Brother Industries Ltd. Brand product names are registered trademarks or trademarks of their respective companies.Direct Printing Print From USB Flash DiveYes, USB Flash Drives Up to256GB Print From Media CardYes, SD/SDHC/SDXC,Multimedia Card/Plus/MobileDriver Deployment Wizard4Easily create print drivers forhassle free deployment overyour networkImage formatJPEGDimensions and Weights With Carton (WxDxH)477 x 294 x 457mm - 9.9KgWithout Carton (WxDxH)400 x 341 x 172mm - 7.7KgDuty Cycles Recommended Monthly50 to 1,000 pages monthlyprint volume Maximum Monthly9Up to 2,500 pages monthly print volumeEnvironment Power ConsumptionOperating - 17WRead Mode - 3.5WSleep Mode - 1.2WOff Mode - 0.2WSound Pressure Level50 dBA (Maximum)Ink Save ModeThis enables the printer toconsume less energy whennot in useEnergy StarYesBlue AngelBlue Angel expected afterinitial productionNordic SwanNordic Swan expected afterinitial ProductionSupplies Ink Cartridges1Black:LC3211BK 200 pages,LC3213BK 400 pagesCyan:LC-3211C 200 pages,LC3213C 400 pagesMagenta:LC-3211M 200 pages,LC3213M 400 pagesYellow:LC-3211Y 200 pages,LC3213Y 400 pages Carton ContentsInk Cartridges, Power SupplyCord, Driver Software, QuickSet-Up Guide, PC InterfaceCable NOT IncludedThe frequency of replacementconsumables will varydepending on the complexityof the prints, the percentage ofcoverage, paper size, page perjob, and the type of media. Forexample glossy coated paperwill result in a shortened life ofsuch supplies.1 Approx declared yield value in accordance with ISO/IEC 247112 Calculated with 80g/m² paper3 Windows® & Mac® only4 Windows® only5 Optional free download from the Brother Solutions Centre 6 Must be web connected7 Vertical x horizontal8 Requires Brother software9M aximum number of printed pages per month can be used to compare designed durability between like Brother products.For maximum printer life, it is best to choose a printer with a duty cycle that far exceeds your print requirements10 ESAT (based on ISO/IEC 24735). This spec is for ADF models only All specifications correct at time of printing and are subject to change. Brother is a registered trademark of Brother Industries Ltd. Brand product names are registered trademarks or trademarks of their respective companies.Colour FaxFax Modem 14,400bpsPC Fax send & receive 8Sends & receives faxes direct from / to your PC(Receiving is for Windows ® only)Automatic RedialAutomatic redialling if the recipient fax is busyDistinctive Ring Detection A service purchased from a telephone company that allows two or more telephone numbers to share a single fixed line, the function enables the machine to provide a different ring tone for each number(UK and Denmark only)Fax/Tel SwitchAutomatic recognition of fax and telephone reception Super FineEnables quality transmission of very small print and line drawings (B&W only)Enhanced Remote Activate Transfer a fax call, answered on an extension phone, to the fax machineMemory Transmission up to 200 pages(ITU-T Test Chart #1/MMR)Out of Paper Reception up to 200 pages(ITU-T Test Chart #1/MMR)Dual AccessAllows the operator to perform 2 different tasks on the machine at the same time (mono only)BroadcastingSend the same fax message to up to 50 locationsAuto ReductionWhen receiving a single page document more than 297mm long the fax machine will automatically reduce the message to fit onto a single A4 sheetECM(Error Correction Mode)Detects line errors during fax transmission and resends the page(s) of the document that had an error (recipient machines must share this feature for it to work)Remote Set-upAllows the user to set-up the MFC from their PC (Windows ® & Macintosh)Grey Scale256 shades of grey are available for faxing Group DialA combination of up to 6 groups can be stored for broadcasting Caller ID YesDelayed Timer No Polling NoBatch Transmission NoFax Forwarding NoRemote Access NoFax Retrieval NoAddress Book Locations 100 Address Book Locations, each location can store 2 fax numbers1Approx declared yield value in accordance with ISO/IEC 247112 Calculated with 80g/m² paper 3 Windows ® & Mac ® only 4 Windows ® only5 Optional free download from the Brother Solutions Centre 6 Must be web connected7 Vertical x horizontal8 Requires Brother software9 M aximum number of printed pages per month can be used to compare designed durability between like Brother products.For maximum printer life, it is best to choose a printer with a duty cycle that far exceeds your print requirements10 ESAT (based on ISO/IEC 24735). This spec is for ADF models onlyAll specifications correct at time of printingand are subject to change. Brother is a registered trademark of Brother Industries Ltd. Brand product names are registered trademarks or trademarks of theirrespective companies.N ORD IC E C O L AB EL315025Working with you for a better environmentAt Brother, our green initiative is simple. We strive to take responsibility, act respectfully and try to make a positive difference to help build a society where sustainable development can be achieved. We call this approach Brother Earth. All specifications correct at time of printing and are subject to change. Brother is a registered trademark of Brother Industries Ltd. Brand product names are registered trademarks or trademarks of their respective companies.。

EH4使用说明书

美国劳雷工业有限公司

目录

..................... 2 0.0 简介.............................................................................................................. .................... .................... ....................2 1.0 系统配件 .................................................................................................................... . ......................... 3 标准接收机配件................................................................................................................ ...................... 3 可选接收机组件 ................................................................................................................. . ...................3 2 发射机组件(400 统) 安系统) …….......................................................................... …. ……………………………….3. .2 发射机组件(5000安系统)……

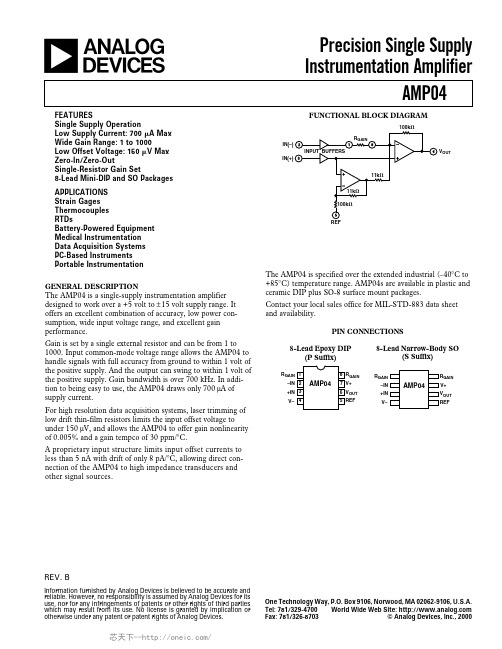

AMP04FSZ,AMP04FPZ,AMP04EPZ,AMP04FSZ-RL,AMP04FSZ-R7,AMP04FS-REEL7,AMP04ESZ-R7, 规格书,Datasheet 资料

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site:

Fax: 781/326-8703

© Analog Devices, Inc., 2000

For high resolution data acquisition systems, laser trimming of low drift thin-film resistors limits the input offset voltage to under 150 µV, and allows the AMP04 to offer gain nonlinearity of 0.005% and a gain tempco of 30 ppm/°C.

1000 1 0.005 0.015 0.025 30

0.75 %

1.0 %

0.75

%

1000 V/V

%

%

%

50

ppm/°C

OUTPUT Output Voltage Swing High

Output Voltage Swing Low Output Current Limit

VOH

RL = 2 kΩ

Contact your local sales office for MIL-STD-883 data sheet and availability.

PIN CONNECTIONS

8-Lead Epoxy DIP (P Suffix)

8-Lead Narrow-Body SO (S Suffix)

25

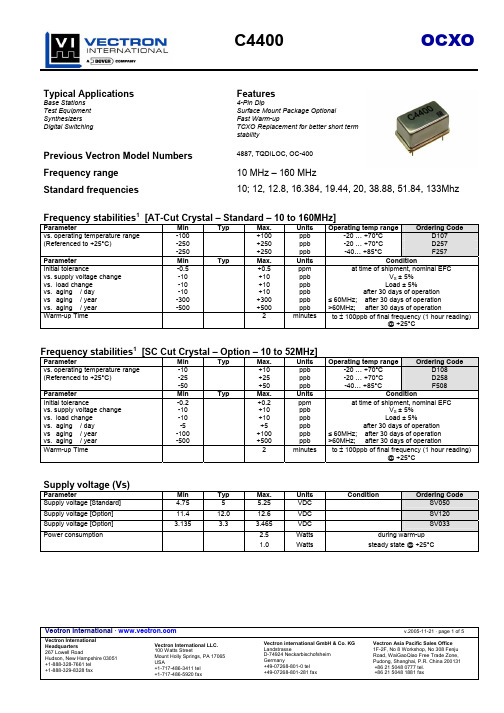

C4400中文资料

Vectron International · v.2005-11-21 · page 1 of 5Vectron International Vectron international GmbH & Co. KG Vectron Asia Pacific Sales OfficeTypical ApplicationsFeaturesBase Stations 4-Pin Dip Test Equipment Surface Mount Package OptionalSynthesizers Fast Warm-up Digital Switching TCXO Replacement for better short termstabilityPrevious Vectron Model Numbers4887, TQDILOC, OC-400Frequency range10 MHz – 160 MHzStandard frequencies10; 12, 12.8, 16.384, 19.44, 20, 38.88, 51.84, 133MhzFrequency stabilities 1 [AT-Cut Crystal – Standard – 10 to 160MHz]ParameterMin Typ Max. Units Operating temp range Ordering Code vs. operating temperature range -100 +100 ppb -20 … +70°C D107(Referenced to +25°C) -250+250 ppb -20 … +70°C D257-250+250 ppb -40… +85°C F257 Parameter Min Typ Max. Units Condition Initial tolerancevs. supply voltage change vs. load change vs. aging / day vs aging / year vs. aging / year -0.5 -10 -10 -10 -300 -500 +0.5 +10 +10 +10 +300 +500 ppm ppb ppbppbppbppbat time of shipment, nominal EFC V S ± 5%Load ± 5% after 30 days of operation ≤ 60MHz; after 30 days of operation >60MHz; after 30 days of operation Warm-up Time2 minutes to ± 100ppb of final frequency (1 hour reading)@ +25°CFrequency stabilities 1 [SC Cut Crystal – Option – 10 to 52MHz]ParameterMin Typ Max. Units Operating temp range Ordering Code vs. operating temperature range -10 +10 ppb -20 … +70°C D108(Referenced to +25°C) -25+25 ppb -20 … +70°C D258-50+50 ppb -40… +85°C F508 Parameter Min Typ Max. Units Condition Initial tolerancevs. supply voltage change vs. load change vs. aging / day vs aging / year vs. aging / year -0.2 -10 -10 -5 -100 -500 +0.2 +10 +10 +5 +100 +500 ppm ppb ppbppbppbppbat time of shipment, nominal EFC V S ± 5%Load ± 5% after 30 days of operation ≤ 60MHz; after 30 days of operation >60MHz; after 30 days of operation Warm-up Time2 minutes to ± 100ppb of final frequency (1 hour reading)@ +25°CSupply voltage (Vs)ParameterMin Typ Max. Units Condition Ordering CodeSupply voltage [Standard] 4.75 5 5.25 VDC SV050Supply voltage [Option] 11.4 12.0 12.6 VDC SV120 Supply voltage [Option] 3.135 3.3 3.465 VDCSV033Power consumption 2.5 Watts during warm-up1.0Wattssteady state @ +25°CVectron International · v.2005-11-21 · page 2 of 5Vectron International Vectron international GmbH & Co. KG Vectron Asia Pacific Sales Office RF outputParameterMin Typ Max. Units Condition Ordering CodeSignal [Standard] HCMOS RFHLoad 15 pF Signal Level (Vol) 0.5 VDC with Vs=12.0V or 5.0V and 15pF load0.3 VDC with Vs=3.3V and 15pF load Signal Level (Voh) 3.7 VDC with Vs=12.0V or 5.0V and 15pF load2.4 VDC with Vs=3.3V and 15pF load Duty cycle45 55 % @ (Voh-Vol)/2Frequency Tuning (EFC) 10 to 80MHzParameterMin Typ Max. Units Condition Tuning Range ±5.0 ±12ppm with AT cut Crystal Tuning Range ±1.0 ±3ppm with SC cut Crystal Linearity 5 %Tuning SlopePositiveControl Voltage Range 0 2 4 VDC with Vs=12.0V or 5.0VControl Voltage Range0.01.42.8VDCwith Vs=3.3VAdditional parametersParameter Min Typ Max. Units ConditionPhase Noise 3-65 dBc/Hz 1 Hz @ 10 MHz -95 dBc/Hz 10 Hz -120 dBc/Hz 100 Hz -140 dBc/Hz 1 kHz -145 dBc/Hz 10 kHz Weight 8.0 g Processing & Packing Handling & processing noteAbsolute Maximum RatingsParameter Min Typ Max. Units Condition Supply voltage (Vs) 7.0 V with Vs=5.0VDC 28 V with Vs =12VDC 7.0 V with Vs =3.3VDC Output Load 50 pF Operable temperature range -55 +85 °C Storage temperature range -55 +125 °CVectron International · v.2005-11-21 · page 3 of 5Vectron InternationalVectron international GmbH & Co. KG Vectron Asia Pacific Sales OfficeDimensions: mmPin Connections1 Electrical Frequency Adjust Input (EFC) 7 Ground (Case) 8 RF Output14Supply Voltage InputStandard Shipping Method (For Type B Enclosures)AXVectron International · v.2005-11-21 · page 4 of 5 Vectron International Vectron international GmbH & Co. KGVectron Asia Pacific Sales OfficeVectron International · v.2005-11-21 · page 5 of 5Vectron International Vectron international GmbH & Co. KG Vectron Asia Pacific Sales Office How to Order this Product:Step 1Use this worksheet to forward the following information to your factory representative: Model Stability Code Supply Voltage Code RF Output CodePackage CodeFrequencyC4400RFHExample:C4400D207SV050RFHA110.000 MhzStep 2 The factory representative will then respond with a Vectron Model Number in the following configuration: Model Package CodeDash Dash NumberC4400[Customer Specified Package Code]-[Factory Generated 4 digit number]Typical P/N = C4400A1-0001Notes:1 Contact factory for improved stabilities or additional product options. Not all options and codes are available at all frequencies.2 Unless otherwise stated all values are valid after warm-up time and refer to typical conditions for supply voltage, frequency control voltage, load, temperature (25°C)3 Phase noise degrades with increasing output frequency.4 Subject to technical modification.5 Contact factory for availability.。

S04xxxH中文资料

o

1.5 1

I T(AV)(A)

-120

0.5

Tamb ( C)

o

1.5

2

2.5

3

3.5

4

0 0

20

40

60

80

100

120

-125 140

Fig.3 : Average on-state current versus case temperature.

I T(AV) (A)

Fig.4 : Relative variation of thermal impedance versus pulse duration.

Zth/Rth 1

5

DC

4 3

0Байду номын сангаас1

Zt h( j-c)

Zt h( j-a)

2 1

= 180

o

Tcase ( C)

o

tp (s)

0

0

10

20

30

40

50

60

70

80

90 100 110 120 130

0.01 1E-3

1E-2

1E-1

1E +0

1 E +1

1E +2 5 E+2

Fig.5 : Relative variation of gate trigger current and holding current versus junction temperature.

tq

ORDERING INFORMATION

S

SCR MESA GLASS CURRENT

2/5

04

10

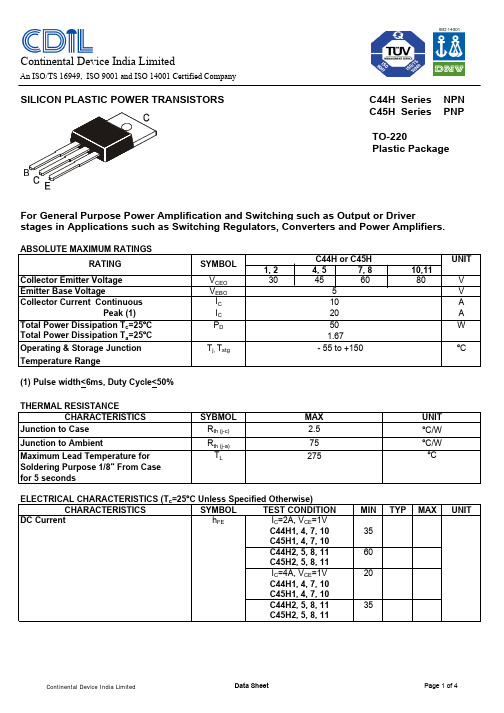

C44H中文资料

SILICON PLASTIC POWER TRANSISTORSC44H Series NPN C45H Series PNPTO-220Plastic PackageFor General Purpose Power Amplification and Switching such as Output or Driverstages in Applications such as Switching Regulators, Converters and Power Amplifiers.(1) Pulse width<6ms, Duty Cycle<50%THERMAL RESISTANCECHARACTERISTICSSYBMOL Junction to Case R th (j-c)Junction to AmbientR th (j-a)Maximum Lead Temperature for T LSoldering Purpose 1/8" From Case for 5 secondsELECTRICAL CHARACTERISTICS (T c =25ºC Unless Specified Otherwise)CHARACTERISTICS SYMBOL TEST CONDITIONMIN TYP MAX UNITDC Currenth FE I C =2A, V CE =1V C44H1, 4, 7, 1035C45H1, 4, 7, 10C44H2, 5, 8, 1160C45H2, 5, 8, 11I C =4A, V CE =1V 20C44H1, 4, 7, 10C45H1, 4, 7, 10C44H2, 5, 8, 1135C45H2, 5, 8, 11ºCUNIT ºC/W ºC/W 2.5MAX 75275Continental Device India LimitedAn ISO/TS 16949, ISO 9001 and ISO 14001 Certified CompanySILICON PLASTIC POWER TRANSISTORS C44H Series NPNC45H Series PNPTO-220Plastic PackageELECTRICAL CHARACTERISTICS (T c=25ºC Unless Specified Otherwise)CHARACTERISTICS SYMBOL TEST CONDITION MIN TYP MAX UNIT Collector Cut Off Current I CES V BE=0, V CE=Rated V CEO10µA Emitter Cut Off Current I EBO V EB=5V, I C=0100µA Collector Emitter Saturation Voltage V CE(sat)I C=8A, I B=0.4AC44H/C45H2, 5, 8, 11 1.85VI C=8A, I B=0.8A 1.0C44H/C45H1, 4, 7, 10Base Emitter Saturation Voltage V BE(sat)I C=8A, I B=0.8A 1.5VDYNAMIC CHARACTERISTICSCollector Capacitance C Cb V CB=10V, f=1MHzC44H Series130pFC45H Series230Current Gain Product f T I C=0.5A,V CE=10V,f=20MHzC44H Series50MHzC45H Series40SWITCHING TIMESDelay And Rise Time t d+t r I C=5A, I B1=0.5AC44H Series300nsC45H Series135Storage Time t s I C=5A, I B1= I B2= 0.5A500nsC44H Series500C45H SeriesFall Time t f I C=5A, I B1= I B2= 0.5AC44H Series140nsC45H Series100C44H Series NPN C45H SeriesPNPTO-220Plastic PackageTO-220 Plastic PackageTO-220 Tube PackingTO-220 / FP200 pcs/polybag 50 pcs/t u b e 396 g m /200 pcs 120 g m /50 pcs3"x 7.5" x 7.5"3.5" x 3.7" x 21.5"1.0K 1.0K17" x 15" x 13.5"19" x 19" x 19"16.0K 10.0K36k g s 29 k g sPACKAGEN e t W e ight/Q t yDetailsSTANDARD PACKINNER CARTON BOXQ t y OUTER CARTON BOXQ t y G r W t SizeSizePacking DetailPin Configuration 1. Base 2. Collector 3. Emitter 4. CollectorNotes C44H Series NPNC45H Series PNPTO-220Plastic PackageC44H_C45HRev040202E DisclaimerThe product information and the selection guides facilitate selection of the CDIL's Discrete Semiconductor Device(s)best suited for application in your product(s)as per your requirement.It is recommended that you completely review our Data Sheet(s)so as to confirm that the Device(s)meet functionality parameters for your application.The information furnished in the Data Sheet and on the CDIL Web Site/CD is believed to be accurate and reliable.CDIL however,does not assume responsibility for inaccuracies or incomplete information.Furthermore,CDIL does not assume liability whatsoever,arising out of the application or use of any CDIL product;neither does it convey any license under its patent rights nor rights of others.These products are not designed for use in life saving/support appliances or systems.CDIL customers selling these products(either as individual Discrete Semiconductor Devices or incorporated in their end products),in any life saving/support appliances or systems or applications do so at their own risk and CDIL will not be responsible for any damages resulting from such sale(s).CDIL strives for continuous improvement and reserves the right to change the specifications of its products without prior notice.CDIL is a registered Trademark ofContinental Device India LimitedC-120 Naraina Industrial Area, New Delhi 110 028, India.Telephone + 91-11-2579 6150, 5141 1112 Fax + 91-11-2579 5290, 5141 1119email@ 。

PT3C-0494 隔爆型热量计 OHC-800 使用说明书

PT3C-0494防爆型热量计OHC-800使用说明书邮编:174-8744 日本东京都板桥区小豆泽2-7-6网页 https://www.rikenkeiki.co.jp/=====目录 ==================================页码1. 安全重要事项1.1 危险事项 ...................................................................................................................... 1-1 1.2 警告事项 ...................................................................................................................... 1-2 1.3 注意事项 ...................................................................................................................... 1-3 1.4 标准及防爆规格的确认方法 .......................................................................................... 1-3 1.5 防爆性能相关的信息(日本国内防爆规格).................................................................. 1-41.5.1 关于OHC-800 .............................................................................................. 1-41.5.2 技术数据....................................................................................................... 1-41.5.3 在危险场所使用时的系统构成 ....................................................................... 1-5 1.6 防爆性能相关的信息(海外防爆规格)......................................................................... 1-61.6.1 关于OHC-800 .............................................................................................. 1-61.6.2 技术数据....................................................................................................... 1-61.6.3 在危险场所使用时的系统构成 ....................................................................... 1-71.6.4 关于安全相关的通知 ..................................................................................... 1-82. 产品的构成2.1 产品的使用目的和特点 ................................................................................................. 2-1 2.2 测定器及标准附件 ........................................................................................................ 2-2 2.3 产品内部的名称............................................................................................................ 2-3 2.4 显示部的名称和功能..................................................................................................... 2-43. 设置方法3.1 设置场所的注意事项..................................................................................................... 3-1 3.2 设置方法和必要的维护空间 .......................................................................................... 3-2 3.3 接线方法 ...................................................................................................................... 3-33.3.1 端子台的说明................................................................................................ 3-33.3.2 推荐电缆....................................................................................................... 3-53.3.3 电缆的拉入/连接方法.................................................................................. 3-63.3.4 保护接地....................................................................................................... 3-83.3.5 电气施工的注意事项 ..................................................................................... 3-9 3.4 配管方法 .................................................................................................................... 3-123.4.1 采样装置..................................................................................................... 3-123.4.2 推荐外部配管系统....................................................................................... 3-133.4.3 配管施工的注意事项 ................................................................................... 3-144. 测定模式时的操作方法4.1 接通电源后从显示到开始测定....................................................................................... 4-1 4.2 显示画面的切换方法..................................................................................................... 4-2 4.3 切换到其他模式............................................................................................................ 4-3 4.4 自我诊断监视功能 ........................................................................................................ 4-4 4.5 关于正常恢复时的接点/显示/信号输出的动作................................................................ 4-55. 检查模式时的操作方法5.1 检查模式的菜单项目..................................................................................................... 5-1 5.2 各项目和详情 ............................................................................................................... 5-25.2.1 光学传感器单元状态的确认"OPTICAL SENSOR UNIT CONDITION" .......... 5-25.2.2 音速传感器单元状态的确认"SONIC SENSOR UNIT CONDITION” .............. 5-35.2.3 主控制器状态的确认"MAIN CONTROLLER CONDITION" .......................... 5-35.2.4 热量测量条件的确认"CALORIFIC VALUE PARAMETER" ........................... 5-45.2.5 密度测量条件的确认"DENSITY PARAMETER" ........................................... 5-45.2.6 4-20mA设定的确认"4-20mA PARAMETER" ............................................... 5-55.2.7 压力传感器输出的确认"PRESSURE SENSOR READINGS" ....................... 5-55.2.8 温度传感器输出的确认"TEMPERATURE SENSOR READINGS" ................ 5-55.2.9 热量计算设定的确认"CALCULATION FACTOR (CALORIFIC VALUE)" ........ 5-65.2.10 密度计算设定的确认"CALCULATION FACTOR (DENSITY) " ..................... 5-65.2.11 声光计算过程的确认"OPT-SONIC READINGS" .......................................... 5-75.2.12 显示/接点设定的确认"DISP. & CONTACT PARAMETER" ........................... 5-85.2.13 显示/接点的保持解除"LATCHING RESET (DISP. & CONTACT)" ................ 5-96. 设置模式时的操作方法6.1 设置模式的项目............................................................................................................ 6-2 6.2 各项目和详情 ............................................................................................................... 6-36.2.1 热量计算的条件设定"CALCULATION FACTOR (CALORIFIC VALUE)" .......... 6-36.2.2 密度计算的条件设定"CALCULATION FACTOR (DENSITY)" ...................... 6-46.2.3 4-20mA的条件设定"4-20mA SETTINGS" ................................................... 6-56.2.4 4-20mA 输出调整"4-20mA ADJUSTMENT" ................................................ 6-66.2.5 4-20mA 输出测试"4-20mA TEST" .............................................................. 6-76.2.6 基准校准"REF. CALIBLATION" ................................................................... 6-86.2.7 补偿调整"OFFSET ADJUSTMENT" ............................................................ 6-96.2.8 显示/接点动作设定"DISP. & CONTACT SETTINGS" ................................ 6-106.2.9 LCD显示的设定"LCD DISPLAY SETTINGS" ............................................ 6-116.2.10 RS-485(MODBUS)通信的设定"RS-485(MODBUS)SETTINGS" ....... 6-126.2.11 接点的励磁设定变更"CONTACT SETTINGS" ........................................... 6-136.2.12 接点动作确认"CONTACT TEST" ............................................................... 6-136.2.13 密码的变更"PASSWORD SETUP (SETUP MODE)" ................................. 6-146.2.14 日志数据下载"IrDA COMMUNICATION" ................................................... 6-157. 保养点检7.1 点检的频度和点检项目 ................................................................................................. 7-17.1.1 日常点检....................................................................................................... 7-17.1.2 每月定期点检................................................................................................ 7-27.1.3 6个月定期点检............................................................................................. 7-3 7.2 推荐定期更换部件 ........................................................................................................ 7-48. 关于储存、移设及废弃8.1 储存或长期不使用时的处理 .......................................................................................... 8-1 8.2 移设或重新使用时的处理.............................................................................................. 8-1 8.3 产品的废弃................................................................................................................... 8-19. 故障检修9.1 异常状态<FAILURE>............................................................................................... 9-1 9.2 规格范围外<OUT OF SPECIFICATION>................................................................. 9-4 9.3 维护要求<MAINTE. REQUIRED>............................................................................ 9-6 9.4 功能确认<FUNCTION CHECK>.............................................................................. 9-7 9.5 注意显示<CAUTION!>............................................................................................. 9-8 9.6 其他 ............................................................................................................................. 9-9 9.7 不符合画面显示内容时 ................................................................................................. 9-910. 产品规格10.1 产品规格 .................................................................................................................... 10-1 10.2 产品原理 .................................................................................................................... 10-210.2.1 声光计算(热量)....................................................................................... 10-210.2.2 声光计算(比重)....................................................................................... 10-410.2.3 光学传感器的原理....................................................................................... 10-610.2.4 音速传感器的原理....................................................................................... 10-711. 术语的定义11.1 使用说明书中使用的术语的定义 ................................................................................. 11-1 11.2 “测定气体规格书”中使用的术语的定义 ..................................................................... 11-2===== 1. 安全重要事项============================= 1.1 危险事项危险<关于防爆>・请遵照设置要件进行设置。

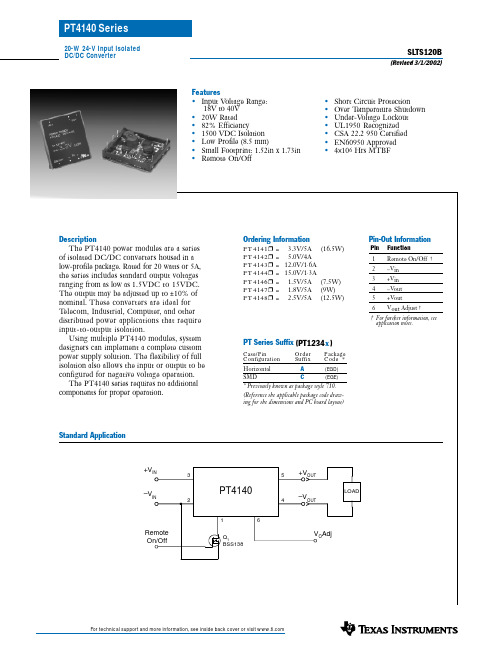

PT4144C中文资料

+VIN

3

–VIN

2

Remote On/Off

PT4140

1

6

Q1 BSS138

5

+VOUT

4

–VOUT

LOAD

VOAdj

For technical support and more information, see inside back cover or visit

元器件交易网 PT4140 Series

(2) The Remote On/Off (pin 1) has an internal pull-up, and if it is left open circuit the module will operate when input power is applied. Refer to the application notes for interface considerations.

Between +Vo and –Vo Input to output

Over Vin range — Per Bellcore TR-332 50% stress, Ta =40°C, ground benign Per Mil-Std-883D, method 2002.3, 1mS, half-sine, mounted to a fixture Per Mil-Std-883D, method 2007.2, 20-2000Hz, soldered in a PC board — Materials meet UL 94V-0

(3) See Safe Operating Area curves or contact the factory for the appropriate derating.

AC 890 模块化系统驱动器商品介绍说明书

AC 890 Modular Systems Drive AC Drives 0.55 – 1200kW (0.75 – 1500 HP)AC 890 Modular Systems DrivesAC Drives 0.55 – 1200kW (0.75 – 1500 HP)Product OverviewThe AC890 is a compact, modular systems drive engineered to control speed and position of open-loop and closed-loop AC motors or servo motors.The AC890 meets the requirements of all variable speed applications, from simple motor speed control to the most sophisticated integrated multi-drive systems.One Drive Fits AllThe AC890 is compatible with any AC motor and virtually any speed/position feedback option. With this flexibility you may not even need to replace your existing AC motor to achieve high performance, saving you time and money.Feedback Options • Incremental encoder • EnDat 21 (SinCos) encoder • ResolverInduction motorsTorque motorsBrushless motorsThe AC890 can be user configured for 5 different operating modesOpen-Loop (volts/frequency) ControlThis mode is ideal for basic motor speed control. Sensorless Vector ControlWith its ultra highperformance sensorless vector algorithm, it delivers a combination of both high torque and close speedregulation without the need for any speed measuring transducer.Closed-Loop Vector Control Full closed-loop flux vector performance can be achieved with the AC890 by simply adding an encoder feedback ‘technology box’. This provides 100% continuous full load standstill torque, plus a highly dynamic speed loop more than sufficient for the most demanding applications.Servo ControlDesigned for the mostdemanding servo systems. The ultra fast control loops and process bus make the AC890 ideal for single or multi axis applications.4 Quadrant Active front-end power supply module With this configuration, the energy is fed back into the mains supply with sinusoïdal currents and unity power factor; a very low currentharmonic content is achieved.Modular DesignAvailable in two stylesPerformance Level OptionsAdvanced PerformanceMotion control firmware with added position loop, motion control function blocks, move incremental, move absolute, move home, line drive master ramp and section control, winder blocks (speed winder, current winder), full function PID, machine state, and others.High PerformanceAll Advanced features plus: Library of pre-engineered application specific LINK VM function blocks such as: Shaftless Printing, cut-to-length, advanced winding, advanced traversing and others.Stand Alone VersionCommon Bus VersionCommon Bus DriveThe AC890 is also available in a common bus platform, where individual motor output drives are easily connected to a common bus supply.Common Bus Drive (CD) Features:Power output to 900 kW(1200 HP) in 9 frame sizes access to all feedback and networking options24 VDC control board supply for programming without power USB programming port torque and speed analogue outputsCommon Bus Supply Module (CS) Features:built-in dynamic braking unit diagnostic operator panel 208-500 VAC power supply up to 162A output per module•••••••••The Complete DriveThe AC890 Series Stand Alone Drive provides a complete AC input to AC motor output, with power input and output terminals. Other features of the Stand Alone Drive include:Power output to 900 kW (1200 HP) in 9 frame sizes access to all feedback and networking optionsbuilt-in dynamic brake switch –provisions to add external braking resistor24 VDC control board supply for programming without power USB programming port torque and speed analogue outputs208-500 VAC input supply•••••••FeaturesHigh Speed feedbackResolverProcess Port 125µs cycle timebetween drives•••••BenefitsMinimal delay between the fieldbus setpoints and the control loops Designed to integrate in existing automation systems, the AC890 features high performance portslinked directly to the fast controlloops of the drive.Minimum delay exists between yourdigital setpoint sent through a fieldbus and the control loops.Replacement of analogue solutionsYour existing analogue setpoint-based solutions can be replaced by a digital fieldbus-based solution with minimal bandwidth loss. Flexible feedbackThe AC890 offers system designers complete flexibility in their choice of feedback technology.Open standards for protection of investmentThe AC890 has been deliberately designed to integrate seamlessly into your automation network.To connect to your PLC or fieldbus network you can simply choose from the wide range of communication technology boxes.O pen Communica fast 150Mhz microprocessor, the AC890 drive can achieve very high-bandwidth control loops.This allows you to use the drive for the most demanding industrial applications e.g. printing, cut-to-length, rotary shear, converting and slitting.A High Performance DesignCompact space savingWe have designed the AC890 with your panel space in mind:The AC890 benefits from the latest advances in semiconductor cooling technology which make it extremely compact.The control terminal connectors are removable for easy mon bus configuration can help you achieve a smaller systems design footprint.Common Bus Version*Stand alone version shownModular function blocks for fastand easy project creationDSE, the development environmentfor AC890 drives, has been designedto assist you in the creation andmanagement of your project.At the project creation stage,the project tree contains all thesections or axis of the machine.Function blocks reusabilityDSE offers user-defined macros thatcan be reused. The LINKprogramming environment, withPLC-like function blocks, makesapplication programming simpleand reduces the training needs ofthe technical staff.Built-in library of function blocksfor advanced applicationsDSE comes with a library ofbuilt-in function blocks foradvanced applications at noextra cost:Shaftless printingWinderRegistrationSection controlThe configuration of the mostcomplex machines is fast anderror-free.Parameters setting and projectcreationHigh bandwidth digitaloscilloscopeMonitoring and online tuning••••••Drive System Explorer Configuration and Programming SoftwareChart Variables on lineMonitoringand on linetuningTotally FlexibleLINK Block DiagramAC890 Application ExamplesCorrugated CuttingLaminatingOverload RatingsVector: 150% for 60 secs / 180% for 0.5 secs Servo: 200% for 4 secs Output Frequency0 -1000 Hz; V/Hz mode0 - 350 Hz; closed loop vector mode 0 - 120 Hz; sensorless vector mode 0 - 350 Hz; Servo Switching FrequencyFrame size B - D: 3,6 or 9 KHz (Vector), 4 KHz (Servo) Frame size E: 3 or 6 KHz (Vector) 4KHz (Servo) Frame size F - K: 3 KHz (Vector) 4KHz (Servo) Frame size G - H: 2.5KHz (Vector) 4KHz (Servo) Frame size J: 2KHz (Vector) 4KHz (Servo)Some exceptions apply. All with audibly silent switching frequency Dynamic BrakingAll drive modules have either regenerative braking or dynamic resistor options Operating Temperature0°C to 45°C (32°F to 113°F) for frames B-F 0°C to 40°C (32°F to 104°F) for frames G-KProduct Enclosure Rating - IP21Frame size B-E Open or Enclosed (Type1), frame size F-K Open type suitable for cubicle mount only.Cubicle RatingCubicle to provide 10dB attenuation to radiated emissions between 30-100MHz. Cubicle may also require tool for opening or removing any door or panel.HumidityMaximum 85% relative humidity at 40°C non-condensing AtmosphereNon flammable, non corrosive and dust free Climatic ConditionsClass 3k3, as defined by EN50178 (1998)VibrationTest Fc of EN60068-2-6StandardsPollution DegreePollution Degree ll (non-conductive pollution, except for temporary condensation)EuropeWhen installed in accordance with the manual, this product conforms to the Low Voltage Directive 2006/95/EC.North AmericaComplies with US requirements (UL508C) and Canadian requirements (C22.2 No. 14). (1) Not tested.Globally CertifiedEMC Directive 2004/108/EC Low Voltage Directive 2006/95/ECGlobally certified and compliant with themost stringent international regulations, the AC890 can be used anywhere in the world.Dimensions are in millimeters (inches)Horsepower ratings correspond to appropriate motor ratings.K-frame dimensions include NEMA 12 ventilated enclosures with flange disconnect option *6-pulse input (12-pulse optional)**6-pulse input (18-pulse optional)Please refer to your local regional office for dimensionaldrawings for each Frame.AustraliaParker Hannifin Pty Ltd9 Carrington RoadPrivate Bag 4, Castle Hill NSW 1765Tel: +61 2 9634 7777 Fax: +61 2 9899 6184BelgiumParker Hannifin SA NVParc Industriel Sud Zone 11 23, Rue du BosquetNivelles B -1400 Belgium Tel: +32 67 280 900 Fax: +32 67 280 999BrasilParker Hannifin Ind. e Com. Ltda. Av. Lucas Nogueira Garcez, 2181 Esperança - Caixa Postal 148 Tel: +55 0800 7275374 Fax: +55 12 3954 5262CanadaParker Motion and Control 160 Chisolm Drive MiltonOntario L9T 3G9Tel: +1(905)693 3000 Fax: +1(905)876 1958ChinaParker Hannifin Motion & Control (Shanghai) Co. Ltd. SSD DrivesSuite B2109 21st Floor Hanwei Plaza7 Guanghua Road Chaoyang District Beijing 100004 P.R.ChinaTel: +86(10)6561 0520/1/2/3/4/5 Fax: +86(10)6561 1070FranceParker SSD Parvex 8 Avenue du Lac B.P. 249F-21007 Dijon Cedex Tel: +33 (0)3 80 42 41 40 Fax: +33 (0)3 80 42 41 23GermanyParker Hannifin GmbH Von-Humboldt-Strasse 10 64646 Heppenheim GermanyTel: +49(0)6252 798200 Fax: +49(0)6252 798205IndiaSSD Drives India Pvt Ltd 151 Developed Plots Estate Perungudi,Chennai, 600 O96, India Tel: +91 44 43910700 Fax: +91 44 43910700ItalyParker Hannifin SPA Via Gounod 120092 Cinisello Balsamo Milano ItalyTel: +39 02 66012459 Fax: +39 02 66012808SingaporeParker Hannifin Singapore Pte Ltd 11, Fourth Chin Bee Rd Singapore 619702 Tel: +65 6887 6300 Fax: +65 6265 5125Sales OfficesCatalogue HA50-0346 (Issue 1 Oct. 2007)Your local authorized Parker distributorH Y G E E d . 2007-08-16SpainParker Hannifin (Espana) S.A. Parque Industrial Las Monjas Calle de las Estaciones 8 28850 Torrejonde Ardoz Madrid SpainTel: +34 91 6757300 Fax: +34 91 6757711SwedenParker Hannifin AB Montörgatan 7SE-302 60 Halmstad SwedenTel: +46(35)177300 Fax: +46(35)108407UKParker Hannifin Ltd. Tachbrook Park Drive Tachbrook Park Warwick CV34 6TUTel: +44(0)1926 317970 Fax: +44(0)1926 317980USAParker Hannifin Corp. SSD Drives Division 9225 Forsyth Park Drive CharlotteNorth Carolina 28273-3884 Tel: +1(704)588 3246 Fax: +1(704) 588-3249© 2007 Parker Hannifin Corporation. All rights reserved.Parker Hannifin Ltd SSD Drives DivisionNew Courtwick Lane, Littlehampton,West Sussex BN17 7RZ United KingdomTel: +44 (0) 1903 737 000 Fax: +44 (0) 1903 737 100*********************** 。

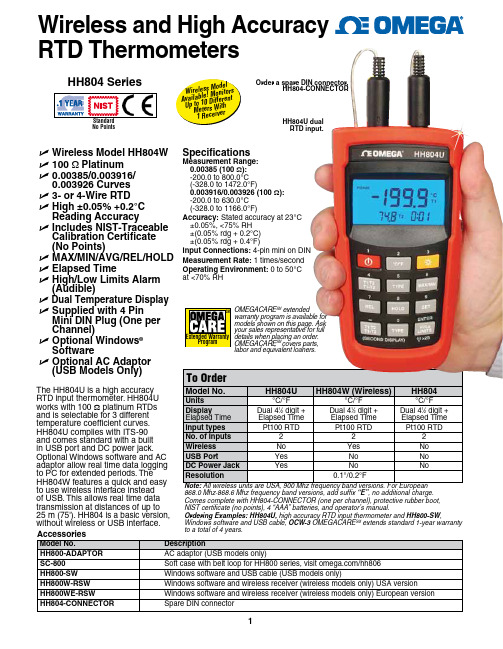

Omega HH804系列产品说明书

1HH804 SeriesThe HH804U is a high accuracy RTD input thermometer. HH804U works with 100 Ω platinum RTDs and is selectable for 3 different temperature coefficient curves. HH804U complies with ITS-90 and comes standard with a built in USB port and DC power jack. Optional Windows software and AC adaptor allow real time data logging to PC for extended periods. The HH804W features a quick and easy to use wireless interface instead of USB. This allows real time data transmission at distances of up to 25 m (75'). HH804 is a basic version, without wireless or USB interface.U W ireless Model HH804W U 100 Ω Platinum U 0.00385/0.003916/ 0.003926 Curves U 3- or 4-Wire RTD U H igh ±0.05% +0.2°C Reading Accuracy U I ncludes NIST-Traceable Calibration Certificate (No Points)U M AX/MIN/AVG/REL/HO LD U E lapsed Time U H igh/Low Limits Alarm (Audible)U D ual Temperature DisplayU S upplied with 4 Pin Mini DIN Plug (One per Channel)U O ptional Windows ® SoftwareU O ptional AC Adaptor (USB Models Only)No Points868.0 Mhz ˜ 868.6 Mhz frequency band versions, add suffix “E”, no additional es complete with HH804-CONNECTOR (one per channel), protective rubber boot, NIST certificate (no points), 4 “AAA” batteries, and operator’s manual.Ordering Examples: HH804U, high accuracy RTD input thermometer and HH800-SW , Windows software and USB cable, OCW-3 OMEGACARE SM extends standard 1-year warranty to a total of 4 years.W i r e l e s s M o d el A v a i l a b l e ! M o n i t o r s U p t o 10 D i f f e r e n tM e t e r s W i t h 1 R e c e i v e r Order a spare DIN connector, HH804-CONNECTOR HH804U dual RTD input.Wireless and High Accuracy RTD Thermometers OMEGACARE SM extended warranty program is available for models shown on this page. Ask your sales representative for full details when placing an order. OMEGACARE SM covers parts, labor and equivalent loaners.Specifications Measurement Range: 0.00385 (100 Ω): -200.0 to 800.0°C (-328.0 to 1472.0°F) 0.003916/0.003926 (100 Ω): -200.0 to 630.0°C (-328.0 to 1166.0°F)Accuracy: Stated accuracy at 23°C ±0.05%, <75% RH ±(0.05% rdg + 0.2°C) ±(0.05% rdg + 0.4°F) Input Connections: 4-pin mini on DIN Measurement Rate: 1 times/second Operating Environment: 0 to 50°C at <70% RH。

8904资料