谈VHDL Verilog的可综合性以及对初学者的一些建议

VHDL编程的一些心得体会(共五则)

VHDL编程的一些心得体会(共五则)第一篇:VHDL 编程的一些心得体会VHDL 是由美国国防部为描述电子电路所开发的一种语言,其全称为(Very High Speed Integrated Circuit)Hardware Description Language。

与另外一门硬件描述语言 Verilog HDL 相比,VHDL 更善于描述高层的一些设计,包括系统级(算法、数据通路、控制)和行为级(寄存器传输级),而且VHDL 具有设计重用、大型设计能力、可读性强、易于编译等优点逐渐受到硬件设计者的青睐。

但是,VHDL 是一门语法相当严格的语言,易学性差,特别是对于刚开始接触VHDL 的设计者而言,经常会因某些小细节处理不当导致综合无法通过。

为此本文就其中一些比较典型的问题展开探讨,希望对初学者有所帮助,提高学习进度。

一.关于端口VHDL 共定义了5 种类型的端口,分别是In, Out,Inout, Buffer 及 Linkage,实际设计时只会用到前四种。

In 和 Out 端口的使用相对简单。

这里,我们主要讲述关于 buffer和inout 使用时的注意事项。

与 Out 端口比,Buffer 端口具有回读功能,也即内部反馈,但在设计时最好不要使用 buffer,因为 buffer类型的端口不能连接到其他类型的端口上,无法把包含该类型端口的设计作为子模块元件例化,不利于大型设计和程序的可读性。

若设计时需要实现某个输出的回读功能,可以通过增加中间信号作为缓冲,由该信号完成回读功能。

双向端口Inout 是四种端口类型中最为特殊的一种,最难以学习和掌握,为此专门提供一个简单程序进行阐述,部分程序如下:...…① DataB<=Din when CE=’1’ and Rd=’0’ else②(others=>’Z’);③ Dout<=DataB when CE=’1’ and Rd=’1’ else④(others=>’1’);… …程序中 DataB 为双向端口,编程时应注意的是,当 DataB 作为输出且空闲时,必须将其设为高阻态挂起,即有类似第②行的语句,否则实现后会造成端口死锁。

verilog和VHDL混合编译仿真

verilog和VHDL混合编译仿真在实际项⽬中,由于项⽬经历了较多的版本更迭或者设计⼈员的技术⽔平限制,有些时候难免有使⽤到verilog的代码和VHDL代码共同存在⼀个项⽬中的情况,那这个时候我们要怎样进⾏混合编译仿真验证呢?这⾥以使⽤vcs⼯具编译verdi查看波形为例:如果我们设计代码是vhdl版本的,但是还想使⽤更⾼级的代码verilog或者systemverilog作为它的顶层tb,并且还想使⽤uvm的组件来搭建更⽅便的验证环境,那么整个环境的编译和执⾏过程如下:1.需要准备的软件vcs-mx和verdi,其中vcs-mx版本会有vlogan和vhdlan两个编译程序2.开始编译编译vhdl的代码,dut_src.f是vhdl的⽂件列表:vhdlan -nc dut_src.f -l cmp_vhdl.log编译uvm库的sv代码:vlogan -full64 -timescale=1ns/1ps +v2k -sverilog -ntb_opts uvm -l cmp_uvm.log编译我们⾃⼰设计的sv代码和⾃⼰设计的uvm各个组件部分的代码,tb.f是⽂件列表:vlogan -full64 -timescale=1ns/1ps +v2k -sverilog tb.f -ntb_opts uvm -l cmp_verilog.log编译vhdl和verilog各⾃的库⽣成可执⾏⽂件simv:vcs -timescale=1ns/1ps -ntb_opts uvm -top tb_top -debug_access+pp -fsdb -j56 -cm line+fsm+tgl+cond -lint=TFIPC-L +nbaopt +rad +notimingchecks +nospecify +error+30run起来,⽣成波形,其中TC_NAME是传⼊的tc参数:./simv -cm line+fsm+tgl+cond +fsdb+force +fsdbfile+../wave/tb_top.fsdb +UVM_TESTNAME=$(TC_NAME)3.查看波形编译出verdi可以查看的库,使⽤vhdlcom是编译vhdl⽂件的库,vericom是编译verilog⽂件的库vhdlcom -lib my_work dut_src.fvericom -lib my_work -sv tb_top.sv使⽤verdi打开波形⽂件:verdi -lib my_work -top tb_top -ssf tb_top.fsdb。

verilog综合心得

综合:不可综合的运算符:= = = ,!= =,/(除法),%(取余数)。

1、不使用初始化语句。

2、不使用带有延时的描述。

3、不使用循环次数不确定的循环语句,如:forever、while等。

4、尽量采用同步方式设计电路。

5、除非是关键路径的设计,一般不调用门级元件来描述设计的方法,建议采用行为语句来完成设计。

6、用always过程块描述组合逻辑,应在信号敏感列表中列出所有的输入信号。

7、所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。

8、在verilog模块中,任务(task)通常被综合成组合逻辑的形式,每个函数(function)在调用时通常也被综合为一个独立的组合电路模块。

9、用户自定义原语(UDP)是不可综合的,它只能用来建立门级元件的仿真模型。

移位运算符:Verilog HDL提供向右(>>)及向左(<<)两种运算符,运算符高位或地位一旦移出即予丢弃,其空缺的位则予以补零。

连续赋值语句(assign)、case语句、if…else语句都是可以综合的initial 语句内若包含有多个语句时,必须以begin end 作聚合;单一的初值赋值,因此并不需以begin end做聚合。

循环(Loops)并不能单独地在程序中存在,而必须在initial和always块中才能使用。

initial过程块中的语句仅执行一次,而always块中的语句是不断重复执行的。

编写顶层模块的注意事项每个端口除了要声明是输入、输出还是双向外,还要声明其数据类型,是连线型(wire)还是寄存器型(reg),如果没有声明则综合器默认为wire型。

1、输入和双向端口不能声明为寄存器型。

2、在测试模块中不需要定义端口。

编写testbentch所归纳的心得module 模块名称;将input 定义为reg;将output定义为wire;引用欲测试的module 别名initial begin设定reg 初始值endalways处理变化值endmodule在always 、initial 过程块内,被赋值的每一个信号都必须定义成寄存器型。

verilog语言的综合与不可综合

Verilog的综合与不可综合综合说明编的代码可以对应出具体的电路,不可综合说明没有对应的电路结构。

不可综合的代码编译通过,只能看到输出,不能实现电路,就是不能用来制作具体的芯片。

一、基本Verilog中的变量有线网类型和寄存器类型。

线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器。

二:verilog语句结构到门级的映射1、连续性赋值:assign连续性赋值语句逻辑结构上就是将等式右边的驱动左边的结点。

因些连续性赋值的目标结点总是综合成由组合逻辑驱动的结点。

Assign语句中的延时综合时都将忽视。

2、过程性赋值:过程性赋值只出现在always语句中。

阻塞赋值和非阻塞赋值就该赋值本身是没有区别的,只是对后面的语句有不同的影响。

建议设计组合逻辑电路时用阻塞赋值,设计时序电路时用非阻塞赋值。

过程性赋值的赋值对象有可能综合成wire,latch,和flip-flop,取决于具体状况。

如,时钟控制下的非阻塞赋值综合成flip-flop。

过程性赋值语句中的任何延时在综合时都将忽略。

建议同一个变量单一地使用阻塞或者非阻塞赋值。

3、逻辑操作符:逻辑操作符对应于硬件中已有的逻辑门4、算术操作符:Verilog中将reg视为无符号数,而integer视为有符号数。

因此,进行有符号操作时使用integer,使用无符号操作时使用reg。

5、进位:通常会将进行运算操作的结果比原操作数扩展一位,用来存放进位或者借位。

如:Wire [3:0] A,B;Wire [4:0] C;Assign C=A+B;C的最高位用来存放进位。

6、关系运算符:关系运算符:<,>,<=,>=和算术操作符一样,可以进行有符号和无符号运算,取决于数据类型是reg,net还是integer。

7、相等运算符:==,!=注意:===和!==是不可综合的。

可以进行有符号或无符号操作,取决于数据类型8、移位运算符:左移,右移,右边操作数可以是常数或者是变量,二者综合出来的结果不同。

verilog中的可综合与不可综合语句

verilog中的可综合与不可综合语句

verilog中可综合语句:input,output,parameter,reg,wire,always,assign,

begin...end,case,for,posedge,negedge,or,and,default,if,function,generate,integer,while,repeat(while、repeat循环可综合时,要具有明确的循环表达式和循环条件,for可综合时也要有具体的循环范围),·define

不可综合语句:initial,fork...join,wait,time,display,forever。

保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点:(1)不能使⽤initial,initial⼀般使⽤在测试程序,做初始化。

(2)不建议使⽤延时,#1,这种只是模拟数字电路中因为布线产⽣的信号延时,不可综合,但也不会报错。

(3)不能使⽤循环次数不确定的函数,但forever在综合设计中禁⽌使⽤,只能使⽤在仿真测试程序中。

(4)尽量使⽤同步电路设计⽅式。

(5)除⾮关键电路设计,⼀般不建议调⽤门级元件进⾏设计,⼀般使⽤⾏为级进⾏设计。

(6)当使⽤always进⾏组合逻辑设计时,敏感列表⾥⾯的要列出所有输⼊信号。

(7)在进⾏时序电路进⾏编写时,采样⾮阻塞赋值。

组合逻辑设计时,采样阻塞赋值,但是不能在同⼀个always语句⾥两种混合使⽤。

(8)为避免产⽣锁存器,if,case要进⾏完整的语句赋值,且case语句中避免使⽤X值,Z值。

使用Verilog HDL进行数字逻辑设计、综合、仿真的步骤及工具软件使用简要说明

使用Verilog HDL进行数字逻辑设计、综合、仿真的步骤及工具软件使用简要说明综合工具使用synplify pro 7.0仿真工具使用modelsim 5.5e (几个菜单排列与5.6有不同,文中有介绍)布局布线工具及时序仿真模型生成使用maxplusII 10.0一.写在开干之前1.涉及到的文件a.源程序(*.v)用户编写的用于描述所需电路的module (可能有多个文件,多个module相互调用)如果用于综合,则源程序内用于描述的V erilog语言必须是可综合风格的。

否则将只能做功能仿真(前仿真),而不能做综合后的仿真和时序仿真(后仿真)。

b.综合后的V erilog HDL 模型(网表) (*.vm)用综合工具synplify对a 进行综合后生成的电路的V erilog HDL 描述。

由synplify自动生成(必须在Implementation Option —Implementation results选项中选中write mapped verilog netlist后才会生成vm文件)。

此文件用于作综合后的仿真c.布局布线后生成的时序仿真模型(网表) (*.vo)文件使用maxplusII对设计进行布局布线之后,生成的带有布局布线及具体器件延迟特性等参数的电路模型的V erilog HDL描述。

要让maxplusII生成vo文件,必须在maxplusII的compile interface中选中verilog netlist writer。

此文件用于作时序仿真(后仿真)d.测试文件(*.v或*.tf)用户编写的V erilog HDL源程序。

用于测试源程序(a,b,c)中所描述电路。

在测试文件中调用被测试的module,生成被测点路所需的输入信号。

所用V erilog HDL语句不需要是可以综合的,只需语法正确。

如果被测试的模型为a,则对应的仿真为前仿真(功能仿真)如果被测试的模型为b, 则对应的仿真为综合后仿真如果被测试的模型为c, 则对应的仿真为后仿真2.强烈建议a.在写用于综合的源程序时,一个源程序文件里只写一个moduleb.源程序文件名与其内所描述的module名相同(如module myadder 文件名myadder.v)c.为了方便管理文件,为每一个设计都单独创建一个目录,目录内创建source, test子目录分别用于存放源程序(用于综合的)和测试文件。

verilog语句可综合vs不可综合

1)所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri,supply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。

2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。

3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。

建立可综合模型的原则要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点:1)不使用initial。

2)不使用#10。

3)不使用循环次数不确定的循环语句,如forever、while等。

4)不使用用户自定义原语(UDP元件)。

5)尽量使用同步方式设计电路。

6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。

7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。

8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。

9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。

对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。

但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。

10)不能在一个以上的always过程块中对同一个变量赋值。

verilog之可综合与不可综合

verilog之可综合与不可综合可综合的意思是说所编写的代码可以对应成详细的,不行综合就是所写代码没有对应的电路结构,例如行为级语法就是一种不行综合的代码,通常用于写测试文件。

建立可综合模型时,需注重以下几点:不用法initial不用法10之类的延时语句不用法循环次数不确定的循环语句,如forever,while等不用法用户自定义原语(UDP元件)尽量用法同步方式设计电路用always块来描述组合规律时,应列出全部输入信号作为敏感信号列表,即always@(*)全部的内部寄存器都应当能够被复位,在用法实现设计时,尽量用法器件的全局复位端作为系统的总复位对时序规律描述和建模,尽量用法非堵塞赋值的方式,对组合规律描述和建模,虽然堵塞和非堵塞赋值的方式都可以,但在同一过程快中最好不要同时用法堵塞赋值和非堵塞赋值。

我个人比较推举用堵塞赋值的方式描述组合规律不能在多个always块中对同一个变量举行赋值。

对同一个对象不能既用法非堵塞赋值,又用法堵塞赋值假如不决定让变量生成锁存器,那么必需在用法if语句或case语句时补全全部条件不行综合语句:initial 初始化语句,只能在testbench中用法,不行综合event event在同步testbench时更实用,不能综合real 不支持real数据类型的综合time 不支持time数据类型的综合assign 和 deassign 不支持对reg数据类型赋值的综合,但支持wire类型赋值的综合以开始的延时语句不能被综合verilog是一种硬件描述语言,我们在写verilog 代码时,首先要有所要写的module在硬件上如何实现的概念,而不是去想编译器如何说明这个module。

比如在打算是否用法 reg 定义时,要问问自己物理上是不是真正存在这个 register, 假如是,它的clock 是什么? D 端是什么?Q 端是什么?有没有清零和置位?同步还是异步?再比如上面研究的三态输出问题,首先想到的应当是在 register 的输出后面加一个三态门,而不是如何才干让编译器知道要“赋值”给一个信号为三态。

VHDL与Verilog语言

VHDL与Verilog语言VHDL(VHSIC hardware description language)和Verilog是用于电子系统设计的硬件描述语言(HDL)。

这两种语言被广泛应用于数字逻辑设计和仿真,以及硬件描述、验证和综合。

1. VHDL(VHSIC hardware description language)VHDL是一种结构化的硬件描述语言,最初由美国国防部高速集成电路计划办公室(VHSIC,Very High Speed Integrated Circuits)开发。

VHDL以其强大的功能和灵活性而闻名,并被广泛用于数字系统的设计和验证。

VHDL的编写包括实体(Entity)和体(Architecture)两个主要部分。

实体部分描述了数字系统的输入输出接口、信号和组件的声明,而体部分描述了实体的内部结构、信号处理和逻辑功能。

VHDL具有丰富的数据类型、运算符和控制结构,可以方便地描述数字电路的行为和结构。

它还提供了强大的仿真和验证功能,使设计人员能够在开发和测试阶段快速迭代和调试设计。

2. VerilogVerilog是一种硬件描述语言,最初由Gateway Design Automation公司(现在是Cadence Design Systems的一部分)开发。

Verilog以其简洁的语法和易学易用的特性而受到广泛欢迎,并成为工业界标准。

Verilog的设计由模块(Module)组成,每个模块描述了一个黑盒子,包含输入和输出端口以及内部的逻辑功能。

模块可以进行层次化组合,从而实现较复杂的系统级设计。

Verilog的语法类似于C语言,具有类似的数据类型、运算符和控制结构。

它还提供了时序建模的能力,使设计人员能够描述数字电路的时序行为。

3. VHDL与Verilog的比较VHDL和Verilog在语法和功能上有一些区别,但它们都可以用于数字电路的设计和仿真。

以下是它们之间的一些比较:3.1 语法风格VHDL采用结构化的编程风格,需要明确的体、过程和信号声明,可以更好地控制和描述系统的结构和行为。

Verilog学习心得

Verilog学习心得因为Verilog是一种硬件描述语言,所以在写Verilog语言时,首先要有所要写的module在硬件上如何实现的概念,而不是去想编译器如何去解释这个module. 比如在决定是否使用reg定义时,要问问自己物理上是不是真正存在这个register, 如果是,它的clock是什么? D端是什么?Q端是什么?有没有清零和置位?同步还是异步?再比如上面讨论的三态输出问题,首先想到的应该是在register的输出后面加一个三态门,而不是如何才能让编译器知道要“赋值”给一个信号为三态。

同样,Verilog中没有“编译”的概念,而只有综合的概念。

写硬件描述语言的目的是为了综合,所以说要想写的好就要对综合器有很深的了解,这样写出来的代码才有效率。

曾经接触过motorola苏州设计中心的一位资深工程师,他忠告了一句:就是用verilog描述电路的时候,一定要清楚它实现的电路,很多人只顾学习verilog语言,而不熟悉它实现的电路,这是设计不出好的电路来的.一般写verilog code时,对整个硬件的结构应该是很清楚了,最好有详细的电路图画出,时序问题等都应该考虑清楚了。

可以看着图直接写code。

要知道,最初Verilog是为了实现仿真而发明的.不可综合的Verilog 语句也是很重要的.因为在实际设计电路时,除了要实现一个可综合的module外,你还要知道它的外围电路是怎样的,以及我的这个电路与这些外围电路能否协调工作.这些外围电路就可以用不可综合的语句来实现而不必管它是如何实现的.因为它们可能已经实际存在了,我仅是用它来模拟的.所以,在写verilog的时候应该要先明确我是用它来仿真的还是综合的.要是用来综合的话,就必须要严格地使用可综合的语句,而且不同的写法可能产生的电路会有很大差别,这时就要懂一些verilog综合方法的知识.就像前面说的,脑子里要有一个硬件的概念.特别是当综合报错时,就要想一想我这种写法能不能用硬件来实现,verilog毕竟还不是C,很多写法是不可实现的.要是这个module仅是用来仿真的,就要灵活得多了,这时你大可不必太在意硬件实现.只要满足它的语法,实现你要的功能就行了.有网友说关于#10 clk=~clk的问题,虽然这种语句是不可综合的,但是在做simulation和verification是常常用它在testbench中来产生一个clock信号。

选择VHDL还是Verilog

选择VHDL还是Verilog?有很多的初学者对选择哪一门语言进行学习总是很迷惑,本文将剖析这两种语言的优势和不足,好给大家一个参考。

技术上:VHDL语法严谨、规范,结构性好,适用于较高抽象层次的描述,但比较复杂。

Verilog简单易用,语法具有亲和力,可描述底层晶体管,但先天上的语法不够严谨的特点也让其在很多领域的发展受限制。

地域上:VHDL在欧洲用的比较多,Verilog在美洲用的比较多。

在中国国内,由于VHDL推广较早,所以应用广泛,尤其在研究所和高校中,但近几年,Verilog也受到了很多企业的青睐。

应用上:在许多大型的需要更多行为级描述的场合,VHDL比较适用,在需要底层描述的地方,用Verilog比较合适。

综合还说,VHDL和Verilog两种语言以及其衍生的工具在全球EDA市场上的占有率,难分伯仲。

就个人而言,选择那种语言在很大程度上并不随意而定的,而是要结合实际的工作环境、手边的工具、资料以及以往的设计和周边人群而定。

我们建议在学习这两种语言时,要精通一种,而另一种达到了解就可以,这是一种比较好的选择。

这两天在更新教程的时候想到的:很多初学者在学习初期,经常为是学习VHDL还是学习Verilog间纠结。

其实,与其纠结,还不如静下心,抓紧时间,就某种语言好好学习。

我以前也纠结过,在那段时间里不断的咨询别人学那个好,一上网就查哪个更受欢迎,就怕学了个偏门的,白费力气白学一场…..但现在回过头来看看,觉的当初真没有必要。

既然这两种语言在市场上存在了这么久,那就说明它们是适应市场需要的,既然谁都没有灭掉谁,那说明两者语言各个利弊。

而且学会了一种后,另外一种也能很快学会,我觉的这可能是因为这两种语言最终的目的都是在逻辑器件上形成硬件电路,所以语言中也贯穿这可编程逻辑器件的一些本质的东西(e.g.并行处理)。

所以,学好了某种语言,掌握了这些本质,然后再去学另一种语言,也就有点似曾相识,融会贯通的感觉了。

Verilog语言的可综合性

V e r i l o g 语言的可综合性可综合的Verilog HDL 语句都是V e r i l o g H D L 标准( I E E E 1 3 6 4 ) 的一个子集,并且因所用工具不同而异。

在设计中不能采用不可综合的语句( 测试代码除外) 。

下面我们讨论一下大部分综合工具都支持的语句,具体到某种工具的特性还要查看说明文档。

对于数据类型、运算符、赋值语句、基本门级元件等的可综合性问题,因为都有固定的规定,这里就不多讨论了。

组合逻辑和时序逻辑的可综合性: 用a s s i g n 语句对w i r e 型变量进行赋值,综合后的结果是组合逻辑电路。

用a l w a y s @ ( 电平敏感变量表) ,即电平敏感的a l w a y s 块描述的电路综合后的结果是组合逻辑电路或电平敏感的锁存器,此时,a l w a y s 块内赋值语句左边的变量是r e g或i n t e g e r 型,块中要避免组合反馈回路,每次执行a l w a y s 块时,在生成组合逻辑的a l w a y s 块中被赋值的所有信号必须都在敏感电平列表中列出,否则在综合时将会为没有列出的信号隐含的产生一个透明的锁存器,这时综合后的电路已不是纯组合电路了。

用a l w a y s @( p o s e d g e c l o c k ) 或a l w a y s @ ( n e g e d g e c l o c k ) 块描述的电路综合为同步时序逻辑电路,设计同步时序逻辑电路的关键是建立描述该电路状态转移的可综合的有限状态机模型,在V e r i l o g H D L语言中最常用的描述同步时序状态机的结构是a l w a y s 和块内的c a s e . i f 语句,除了紧跟在a l w a y s 后的@( p o s e d g e c l o c k ) , @ ( n e g e d g e c l o c k ) 外,a l w a y s 块中不允许其他的@ ( e v e n t ) 语句,目前大多数综合工具不能综合V e r i l o g H D L描述的异步状态机,所以用V e r i l o g 设计的时序电路应该是同步时序电路。

VHDL和 verilogHDL的区别

4.布局布线:将.edf文件调入PLD厂家提供的软件中进行布线,即把设计好的逻辑安放到PLD/FPGA内

5.时序仿真:需要利用在布局布线中获得的精确参数,用仿真软件验证电路的时序。(也叫后仿真)

选择VHDL还是verilog HDL?

这是一个初学者最常见的问题。其实两种语言的差别并不大,他们的描述能力也是类似的。掌握其中一种语言以后,可以通过短期的学习,较快的学会另一种语言。选择何种语言主要还是看周围人群的使用习惯,这样可以方便日后的学习交流。当然,如果您是集成电路(ASIC)设计人员,则必须首先掌握verilog,因为在IC设计领域,90%以上的公司都是采用verilog进行IC设计。对于PLD/FPGA设计者而言,两种语言可以自由选择。

2. 用硬件电路设计思想来编写HDL:

学好HDL的关键是充分理解HDL语句和硬件电路的关系。编写HDL,就是在描述一个电路,我们写完一段程序以后,应当对生成的电路有一些大体上的了解,而不能用纯软件的设计思路来编写硬件描述语言。要做到这一点,需要我们多实践,多思考,多总结。

3.语法掌握贵在精,不在多

另外,学习过Verilog HDL的朋友应该知道,Verilog HDL很具有C语言的风格,不能说“所以”,但结果差不多,也具有C语言一样的不严密性。所以在硬件电路设计时就得有相应的考虑

Hale Waihona Puke 以上是我去年学数逻在网上查到的 希望对你有所帮助

�

HDL开发流程

用VHDL/VerilogHD语言开发PLD/FPGA的完整流程为:

可综合的verilog语句

可综合的verilog语句摘要:一、引言1.Verilog 简介2.Verilog 语句的可综合性二、可综合的Verilog 语句1.基本赋值语句2.组合逻辑实现3.时序逻辑实现4.实例化模块三、Verilog 语句的可综合性分析1.基本赋值语句的可综合性2.组合逻辑实现的可综合性3.时序逻辑实现的可综合性4.实例化模块的可综合性四、提高Verilog 代码可综合性的方法1.遵循可综合编程规范2.使用可综合的语法结构3.模块划分与层次设计五、总结1.Verilog 语句可综合性的重要性2.提高代码可综合性的实际应用价值正文:【引言】Verilog 是一种广泛应用于数字电路设计和验证的硬件描述语言。

在Verilog 中,语句的可综合性指的是能否将Verilog 代码转换为实际硬件电路。

了解可综合的Verilog 语句对于编写高效的硬件描述语言代码至关重要。

本文将介绍可综合的Verilog 语句及其可综合性分析,并提出提高代码可综合性的方法。

【可综合的Verilog 语句】Verilog 中有很多可综合的语句,包括基本赋值语句、组合逻辑实现、时序逻辑实现和实例化模块。

1.基本赋值语句基本赋值语句包括阻塞赋值(assignment)和非阻塞赋值(non-blocking assignment)。

这两种赋值语句都是可综合的。

2.组合逻辑实现组合逻辑实现通常使用与门(and)、或门(or)、非门(not)等基本逻辑门实现。

这些逻辑门的Verilog 实现都是可综合的。

3.时序逻辑实现时序逻辑实现通常使用寄存器(register)、计数器(counter)等元件实现。

这些元件的Verilog 实现都是可综合的。

4.实例化模块实例化模块是通过使用`实例化`关键字将一个模块复制多次。

实例化模块的Verilog 实现也是可综合的。

【Verilog 语句的可综合性分析】1.基本赋值语句的可综合性基本赋值语句的可综合性取决于赋值的目标。

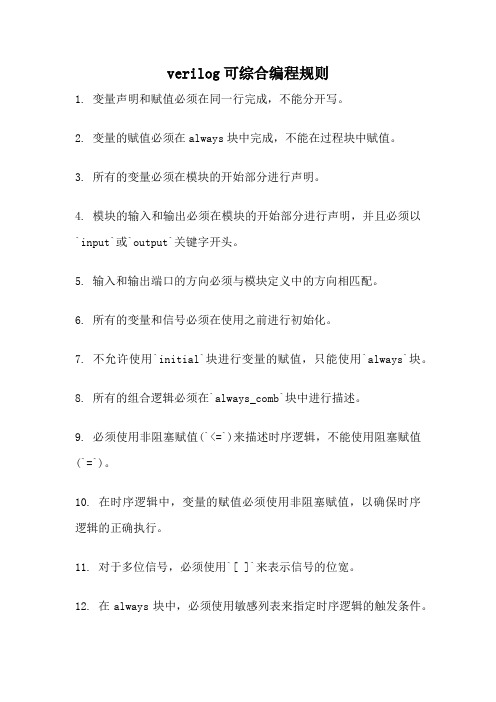

verilog可综合编程规则

verilog可综合编程规则1. 变量声明和赋值必须在同一行完成,不能分开写。

2. 变量的赋值必须在always块中完成,不能在过程块中赋值。

3. 所有的变量必须在模块的开始部分进行声明。

4. 模块的输入和输出必须在模块的开始部分进行声明,并且必须以`input`或`output`关键字开头。

5. 输入和输出端口的方向必须与模块定义中的方向相匹配。

6. 所有的变量和信号必须在使用之前进行初始化。

7. 不允许使用`initial`块进行变量的赋值,只能使用`always`块。

8. 所有的组合逻辑必须在`always_comb`块中进行描述。

9. 必须使用非阻塞赋值(`<=`)来描述时序逻辑,不能使用阻塞赋值(`=`)。

10. 在时序逻辑中,变量的赋值必须使用非阻塞赋值,以确保时序逻辑的正确执行。

11. 对于多位信号,必须使用`[ ]`来表示信号的位宽。

12. 在always块中,必须使用敏感列表来指定时序逻辑的触发条件。

13. 在always块中,必须使用`posedge`或`negedge`关键字来指定时钟信号的边沿。

14. 不允许在always块中使用`if`语句进行分支控制,只能使用`case`或`if-else`语句。

15. 在always块中,不允许出现死循环或无限循环。

16. 在模块的输出端口中,必须使用`assign`关键字进行赋值。

17. 在模块之间进行连接时,必须使用连线操作符`wire`或`reg`来声明信号。

18. 不允许在模块中使用的信号在模块之间进行连接。

19. 必须使用`endmodule`关键字来结束模块的定义。

20. 必须使用`module`关键字来定义模块。

这些规则是基本的Verilog综合编程规则,遵循这些规则可以确保Verilog代码的正确性和可综合性。

Verilog HDL和VHDL的比较

Verilog HDL和VHDL的比较这两种语言都是用于数字电子系统设计的硬件描述语言,而且都已经是IEEE 的标准。

VHDL 1987 年成为标准,而Verilog 是1995 年才成为标准的。

这个是因为VHDL 是美国军方组织开发的,而Verilog 是一个公司的私有财产转化而来的。

为什么Verilog 能成为IEEE 标准呢?它一定有其优越性才行,所以说Verilog 有更强的生命力。

这两者有其共同的特点:1. 能形式化地抽象表示电路的行为和结构;2. 支持逻辑设计中层次与范围地描述;3. 可借用高级语言地精巧结构来简化电路行为和结构;具有电路仿真与验证机制以保证设计的正确性;4. 支持电路描述由高层到低层的综合转换;5. 硬件描述和实现工艺无关;6. 便于文档管理;7. 易于理解和设计重用但是两者也各有特点。

Verilog HDL 推出已经有20 年了,拥有广泛的设计群体,成熟的资源也比VHDL 丰富。

Verilog 更大的一个优势是:它非常容易掌握,只要有 C 语言的编程基础,通过比较短的时间,经过一些实际的操作,可以在 2 ~3 个月内掌握这种设计技术。

而VHDL 设计相对要难一点,这个是因为VHDL 不是很直观,需要有Ada 编程基础,一般认为至少要半年以上的专业培训才能掌握。

目前版本的Verilog HDL 和VHDL 在行为级抽象建模的覆盖面范围方面有所不同。

一般认为Verilog 在系统级抽象方面要比VHDL 略差一些,而在门级开关电路描述方面要强的多。

近10 年来,EDA 界一直在对数字逻辑设计中究竟用哪一种硬件描述语言争论不休,目前在美国,高层次数字系统设计领域中,应用Verilog 和VHDL 的比率是80 %和20 %;日本和台湾和美国差不多;而在欧洲VHDL 发展的比较好。

在中国很多集成电路设计公司都采用Verilog ,但VHDL 也有一定的市场。

1、最近和朋友談到這個問題, 他們選的是Verilog 原因是, IP 供應商大多提供Verilog, 如果你的Project 是由頭做到尾都自己來, 不用別人的IP 那麼, 我想問題不大, 但如果你未來會開ASIC 需要整合IP 供應商的IP 那麼建議你用Verilog!2、以前的一个说法是:在国外学界VHDL比较流行,在产业界Verilog比较流行。

最流行的硬件设计语言,VHDL和Verilog比较

最流行的硬件设计语言,VHDL和Verilog比较

当前最流行的硬件设计语言有两种,即VHDL 与Verilog HDL,两者各有优劣,也各有相当多的拥护者。

VHDL 语言由美国军方所推出,最早通过国际电机工程师学会(IEEE)的标准,在北美及欧洲应用非常普遍。

而Verilog HDL 语言则由Gateway 公司提出,这家公司辗转被Cadence所购并,并得到Synopsys的支持。

在得到这两大EDA 公司的支持后,也随后通过了IEEE 标准,在美国、日本及中国台湾地区使用非常普遍。

我们把这两种语言具体比较下:

1.整体结构

点评:

两者结构基本相似,并行语句的种类也类似;

VHDL语言需要进行大量说明,程序通常比较长;

Verilog HDL通常不进行说明,或只进行非常简短的说明,程序比较简短。

2.数据对象及类型

VHDL

常量信号变量 9种预定义类型各类用户定义类型

可描述各类不同的量

必须进行类型说明

运算时必须考虑类型的一致性和适用性

Verilog HDL

常量:数量,参量

变量:网络型寄存器型

类型种类少

运算时所受的约束少

3.运算符号。

VHDL的优缺点

• 第三点往往在商业领域被提及。 第三点往往在商业领域被提及。 • 综合技术的成熟过程尤如C编译器所走过 综合技术的成熟过程尤如 编译器所走过 的途径一样。一段时期以前,一般C编译器所 的途径一样。 一段时期以前 , 一般 编译器所 产生成的可执行码往往无效, 产生成的可执行码往往无效,以致不如设计者 自己去写机器码来替代。今天, 自己去写机器码来替代。今天,仍有一些作业 需采用低级语言或机器码来写, 需采用低级语言或机器码来写,但大多数代码 必须用高级语言来写, 编译器已在那些不能 必须用高级语言来写 , C编译器已在那些不能 熟练书写机器码来编程序的工程师中广泛使用。 熟练书写机器码来编程序的工程师中广泛使用。

硬件描述语言VHDL

• VHDL(VHSIC Hardware Description Language)是一种 是一种 标准的硬件描述语言, 它是在20世纪 世纪70~80年代中, 由 年代中, 标准的硬件描述语言, 它是在 世纪 年代中 美国国防部资助的VHSIC(Very High Speed Integrated 美国国防部资助的 Circuit)项目开发的产品。 在这个语言首次开发出来时, 项目开发的产品。 在这个语言首次开发出来时, 项目开发的产品 其目标仅是使电路文本化的一种标准, 其目标仅是使电路文本化的一种标准 , 为了使人们采用 文本方式描述的设计, 能够被其他人所理解。 同时, 文本方式描述的设计, 能够被其他人所理解。 同时, 它 也被用来作为模型语言, 用于进行仿真验证模拟。 也被用来作为模型语言, 用于进行仿真验证模拟。

• 第二点是对于工具的逻辑综合有效性的担心, 第二点是对于工具的逻辑综合有效性的担心, 且往往不是没有根据的。 且往往不是没有根据的。 VHDL编译器并不一 编译器并不一 定总能生成令人满意的设计, 定总能生成令人满意的设计, 因为优化的结果 往往依赖于设计的目标。 往往依赖于设计的目标。 编译器采用一定的算 由标准的设计行为决定设计的实现, 法, 由标准的设计行为决定设计的实现, 而 算法从某种角度出发, 沿一定路径进行, 算法从某种角度出发, 沿一定路径进行, 并 不能发现设计中的所有问题。 有时, 不能发现设计中的所有问题。 有时, 当人们 希望按自己的要求来控制设计实现时, 希望按自己的要求来控制设计实现时,没有什 么能够替代人的创造力。 么能够替代人的创造力。

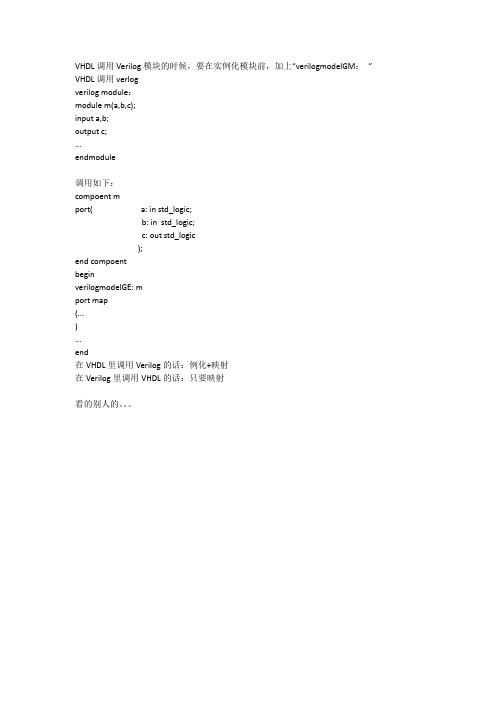

VHDL和Verilog的混合编程

VHDL调用Verilog模块的时候,要在实例化模块前,加上“verilogmodelGM:”VHDL调用verlogverilog module:module m(a,b,c);input a,b;output c;...endmodule调用如下:compoent mport( a: in std_logic;b: in std_logic;c: out std_logic);end compoentbeginverilogmodelGE: mport map(...)...end在VHDL里调用Verilog的话:例化+映射在Verilog里调用VHDL的话:只要映射看的别人的。

被骗了,所以发点实在的,VHDL与verilog调用这里用VHDL调用VERILOG写好的模块.先按VHDL的语法声明实体(也就是你用Verilog写的模块),然后按VHDL的语法例化实体就行了 .这样就不用转换了,或者可以少用转换了.例子.library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use work.dt16_pkg.all;entity clk_alm isport (reset : in std_logic;fck32m : in std_logic; --来自背板的32M帧头clk32m : in std_logic; --来自背板的32M时钟refclk2m : in std_logic; --2M参考时钟clklos : out std_logic --时钟告警输出);end clk_alm;architecture arch_clk_alm of clk_alm iscomponent clk_dogport(reset : in std_logic;clock : in std_logic;--work clockrefclk : in std_logic;--reference clockalm : out std_logic);end component;component ALM --声明port(XMCLK : in std_logic;RST : in std_logic;M_CLK : in std_logic;LOST_ALM : out std_logic);end component;signal alm_clk: std_logic;signal alm_fck: std_logic;signal refclk2m_div: std_logic;signal count: std_logic_vector(2 downto 0); signal delay_los: std_logic;beginclk_dog0: clk_dogport map (reset => reset ,clock=>clk32m ,refclk =>refclk2m ,alm =>alm_clk);fck_dog0: ALM --例化PORT MAP(XMCLK => fck32m ,RST => reset ,M_CLK => refclk2m_div ,LOST_ALM => alm_fck);process(reset,refclk2m)beginif reset='1' thencount<=(others=>'0');elsif refclk2m'event and refclk2m='1' thencount<=count+1;end if;end process;refclk2m_div<=count(2);clklos<=not(alm_clk and alm_fck);end arch_clk_alm;-----------------以下是verilog写的module----------------- module ALM (XMCLK, RST, M_CLK, LOST_ALM);input XMCLK ;input RST ;input M_CLK ;output LOST_ALM ;reg LOST_ALM;reg [2:0]ALM_STATE;reg [2:0]COUNTA;reg [2:0]COUNTB;reg [2:0]COUNTC;always @(negedge RST or posedge XMCLK)beginif (!RST)COUNTA <= 0;else if (COUNTA == 7)COUNTA <= 0;else COUNTA <= COUNTA + 1;endalways @(posedge M_CLK) beginif (!RST)beginCOUNTB <= 0;COUNTC <= 0;endelsebeginCOUNTC <= COUNTB;COUNTB <= COUNTA;endendalways @(negedge M_CLK) beginif (!RST)ALM_STATE <= 0;else if (ALM_STATE == 7) ALM_STATE <= 0;else if (COUNTC == COUNTB) ALM_STATE <= ALM_STATE + 1; else ALM_STATE <= 0;endalways @(posedge M_CLK) beginif (!RST)LOST_ALM <= 1;else if (ALM_STATE == 7) LOST_ALM <= 0;else LOST_ALM <= 1;endendmodule。

VHDL和VERILOG的比较——很好

7.顺序语句 : 赋值语句

VHDLBiblioteka Verilog HDL信号赋值

非阻塞赋值

变量赋值

阻塞赋值

例:b<=a;c<=b

过程结束时赋值,c落后b一个时钟周期;

b=a;c=b; 立即赋值,b与c相同。

VHDL 与 Verilog HDL 的对比

7.顺序语句 :条件语句 if case 两者基本相同;

例:if(reset) qout=0; else if(load) qout=data; else qout=qout+1;

3.数据对象和数据类型 Verilog HDL的数据对象有常量和变量; 其中变量分为连线型(wire)和寄存器型 (reg),wire型类似于信号,而reg型类似于 变量,只能在子程序块中赋值; 数据变量默认为wire型。

VHDL 与 Verilog HDL 的对比

4.主要运算:逻辑运算 VHDL中 有常用的6种,可以对1位的逻辑量 或逻辑数组进行运算; Verilog HDL中有3类共14种,分为一般逻辑 运算,位逻辑运算,缩减逻辑运算;

VHDL 与 Verilog HDL 的对比

5.并行语句 两种语言的语句都分为并行语句和顺序语句; 并行语句在主程序中使用; 顺序语句只能在子结构中使用。 并行语句可以分为三类:

赋值语句、元件语句、进程语句

VHDL 与 Verilog HDL 的对比

5.并行语句 :赋值语句 VHDL 信号赋值语句 (直接赋值、条件赋值、选择赋值) Verilog HDL assign语句(连续赋值)

Verilog HDL ' include

VHDL 与 Verilog HDL 的对比 9. 简单模块的对比: 8位4选1MUX

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

谈VHDL/Verilog的可综合性以及对初学者的一些建议

一、HDL不是硬件设计语言

过去笔者曾碰到过不少VHDL或Verilog HDL的初学者问一些相似的问题,诸如如何实现除法、开根号,如何写循环语句等等。

在这个论坛上,也时常能看到一些网友提出这一类的问题。

对于这些问题,首先要明确的是VHDL和Veriglog并非是针对硬件设计而开发的语言,只不过目前被我们用来设计硬件。

HDL是Hardware Description Language的缩写,正式中文名称是“硬件描述语言”。

也就是说,HDL并不是“硬件设计语言(Hardware Design Langu age)”。

别看只差这一个单词,正是这一个单词才决定了绝大部分电路设计必须遵循RTL的模式来编写代码,而不能随心所欲得写仅仅符合语法的HDL代码。

二、HDL的来历

之所以是“硬件描述语言”,要从HDL的来历说起。

VHDL于1980年开始在美国国防部的指导下开发,完成于1983年,并于1987年成为IE EE的标准。

当初开发这种语言,是出于美国国防部采购电子设备的需要。

美军的装备采购自私人企业,时常要面对这样一种风险:如果某种武器大量装备部队,而其中某个零件的供应商却在几年后倒闭了,那这种武器的再生产、维修和保养都会出现大问题。

而电子设备、尤其是集成电路的内部结构较为复杂,若出现前面所说的情况要找其他公司生产代用品非常困难。

于是美国防部希望供应商能以某种形式留下其产品的信息,以保证一旦其破产后能由其他厂商迅速生产出代用品。

显然,当初的设计文档显然是不能交出来的,这在美国会涉及商业机密和知识产权问题。

于是美国防部就想出了一种折衷的方法——描述硬件的语言,也就是VHDL。

通过VHDL,供应商要把自己生产的集成电路芯片的行为描述出来:比如说,加了什么样的信号后过多少时间它能输出什么等等。

这样,如果有必要让其他厂商生产代用品,他们只需照着VHDL文档,设计出行为与其相同的芯片即可。

这样的代用品相当于是新厂商在不了解原产品结构的情况下独立设计的,所以不太会涉及知识侵权。

Verilog HDL也形成于差不多的年代,是由Gateway Design Automation公司大约在198 3年左右开发的。

其架构同VHDL相似,但主要被用来进行硬件仿真。

或许私人公司更注重实用,Verilog要比VHDL简洁得多。

由此可见,这两种最流行的用于电路设计的语言,没有一种是为了设计硬件而开发的(更何况80年代还没有现在的那些功能强大的EDA软件呢)。

因此,当初制订HDL语言标准的时候,并没有考虑这些代码如何用硬件来实现。

换句话说,有些代码写起来简单,实现起来却可能非常复杂,或者几乎不可能实现。

三、HDL代码的可综合性

现在回到最初的问题上。

为什么诸如除法、循环之类的HDL代码总是会出错?

由上一部分可知,任何符合HDL语法标准的代码都是对硬件行为的一种描述,但不一定是

可直接对应成电路的设计信息。

行为描述可以基于不同的层次,如系统级,算法级,寄存器传输级(RTL)、门级等等。

以目前大部分EDA软件的综合能力来说,只有RTL或更低层次的行为描述才能保证是可综合的。

而众多初学者试图做的,却是想让软件去综合算法级或者更加抽象的硬件行为描述。

比如说,要想实现两个变量相除的运算,若在代码中写下C=A/B,你将会发现只有一些模拟软件在前仿真中能正确执行这句代码,但几乎任何软件都不能将其综合成硬件。

不要怪软件太笨。

试想一下,如果我们自己笔算除法是怎么做的?从高位到低位逐次试除、求余、移位。

试除和求余需要减法器,商数和余数的中间结果必须有寄存器存储;而此运算显然不能在一个时钟周期里完成,还需要一个状态机来控制时序。

一句简单的C=A/B同所有这些相比显得太抽象,对于只能接受RTL或更低层次描述的EDA软件来说确实太难实现。

而如果代码是类似于(Verilog)

always @(posedge clk)

c<=A/B; 这样的,要求除法在一个时钟延上完成,那更是不可能实现的。

(注:有些FPGA 的配套软件提供乘除法的运算模块,但也只能支持直接调用,不支持把形如C=A/B的语句综合成除法模块。

)

又比如,一个很多初学者常见的问题是试图让HDL进行循环运算,形同(Verilog):

for (i=0; iparity = parity xor data[i];

一些功能比较简单的综合软件会完全拒绝综合循环语句;而一些功能较强的软件仅当wordl ength是常数的时候能综合;当wordlength为变量时,任何软件都不能综合上面的语句。

这是因为硬件规模必须是有限的、固定的。

当综合软件遇到循环语句时,总是将其展开成若干条顺序执行的语句,然后再综合成电路。

若wordlength是常数,则展开的语句数是确定的,具有可综合性;而若它是变量时,展开的语句数不确定,对应的硬件电路数量也不能确定,无法被综合。

或许有人说用计数器就能实现变量循环,但这情形又和上面的除法运算相同。

那需要额外的硬件,用来存储中间结果和进行时序控制,象上面那样的循环语句对此描述得太抽象,软件接受不了。

四、如何判断自己写的代码是可综合的?

用一句简单的话概括:电脑永远没有你聪明。

具体来说,通常EDA软件对HDL代码的综合能力总是比人差。

对于一段代码,如果你不能想象出一个较直观的硬件实现方法,那ED A软件肯定也不行。

比如说,加法器、多路选择器是大家都很熟悉的电路,所以类似A B-C,(A>B)?C这样的运算一定可以综合。

而除法、开根、对数等等较复杂的运算,必须通过一定的算法实现,没有直观简单的实现方法,则可以判断那些计算式是不能综合的,必须按它们的算法写出更具体的代码才能实现。

此外,硬件无法支持的行为描述,当然也不能被综合(比如想在FPGA上实现DDR内存那样的双延触发逻辑,代码很容易写,但却不能实现)。

不过,这样的判断标准非常主观模糊,遇到具体情况还得按设计人员自己的经验来判断。

如

果要一个相对客观的标准,一般来说:在RTL级的描述中,所有逻辑运算和加减法运算、以及他们的有限次组合,基本上是可综合的,否则就有无法综合的可能性。

当然,这样的标准仍然有缺陷,更况且EDA的技术也在不断发展,过去无法综合的代码或许将来行,某些软件不支持的代码换个软件或许行。

比如固定次数的循环,含一个常数参数的乘法运算等等,有些EDA软件支持对它们的综合,而有些软件不行。

所以,正确的判断仍然要靠实践来积累经验。

当你可以较准确判断代码的可综合性的时候,你对HDL的掌握就算完全入门了。