适用于中频采样的CMOS自举采样开关

栅压自举开关的设计与仿真

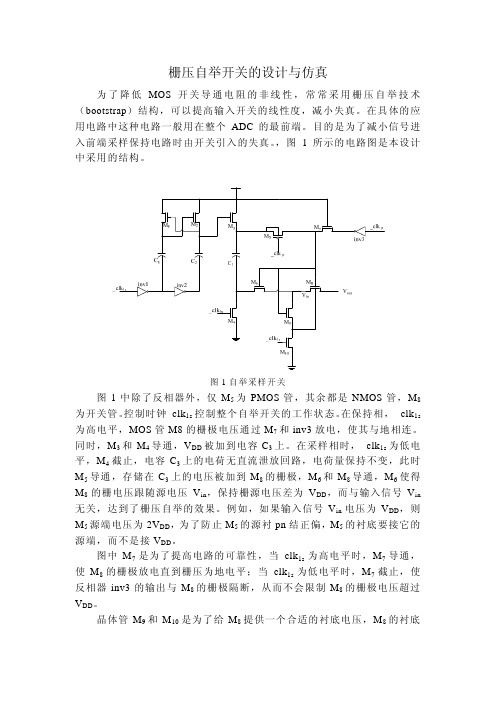

为 了 降 低 MOS 开 关 导 通 电 阻 的 非 线 性 , 常 常 采 用 栅 压 自 举 技 术 ( bootstrap )结构,可以提高输入开关的线性度,减小失真。在具体的应 用电路中这种电路一般用在整个 ADC 的最前端。目的是为了减小信号进 入前端采样保持电路时由开关引入的失真。 ,图 1 所示的电路图是本设计 中采用的结构。

VG VS C3 VDD C3 C p

其中 Cp 为与 C 3 上极板连接的所有寄生电容。在本设计中 C 3 约为 7.2pF , 约为寄生电容的 10 倍,大大减小寄生电容对开关管栅压的影响。

ห้องสมุดไป่ตู้M 1 、M 2 、C 1 和 C 2 组成时钟倍乘电路 [39] ,它确保 C 1 和 C 2 的初始状态,

图 2 自举采样开关 V gs 仿真波形图

图 3 自举采样开关的输入输出关系图

本课题设计的采样保持电路为差分结构,因此将图 1 所示的两个开关 连成差分形式,输入信号频率为 48.83MHz ,采样频率为 100MHz ,在时域 很难看出开关的性能,对频域输出做 2048 个点的 DFT 分析 , 频域输出如图

图 1 自举采样开关

图 1 中除了反相器外,仅 M 5 为 PMOS 管,其余都是 NMOS 管, M 8 为开关管。 控制时钟 _clk 1s 控制整个自举开关的工作状态。 在保持相, _clk 1s 为高电平, MOS 管 M8 的栅极电压通过 M 7 和 inv3 放电,使其与地相连。 同时, M 3 和 M 4 导通, V DD 被加到电容 C 3 上。在采样相时, _clk 1s 为低电 平, M 4 截止,电容 C 3 上的电荷无直流泄放回路,电荷量保持不变,此时 M 5 导通,存储在 C 3 上的电压被加到 M 8 的栅极, M 6 和 M 8 导通, M 6 使得 M 8 的栅电压跟随源电压 V in ,保持栅源电压差为 V DD ,而与输入信号 V in 无关,达到了栅压自举的效果。例如,如果输入信号 V in 电压为 V DD ,则 M 5 源端电压为 2V DD ,为了防止 M 5 的源衬 pn 结正偏,M 5 的衬底要接它的 源端,而不是接 V DD 。 图中 M 7 是为了提高电路的可靠性,当 _clk 1s 为高电平时, M 7 导通, 使 M 8 的栅极放电直到栅压为地电平;当 _clk 1s 为低电平时, M 7 截止,使 反相器 inv3 的输出与 M 8 的栅极隔断,从而不会限制 M 8 的栅极电压超过 V DD 。 晶体管 M 9 和 M 10 是为了给 M 8 提供一个合适的衬底电压, M 8 的衬底

基于新型电容阵列切换方式的10位低功耗SAR ADC

基于新型电容阵列切换方式的10位低功耗SAR ADC孙甜甜【摘要】文中提出了一种10位低功耗逐次逼近(Successive-Approximation-Register,SAR)模/数转换器(Analog-to-Digital Converter,ADC),内部数/模转换网络采用一种新型的电容阵列开关切换方式,通过分段电容阵列、时序初始化和子参考电压来降低能耗,相比传统结构电容阵列的转换能耗减小了97.6%,单位电容数量减小了87%.整个ADC采用65 nm CMOS工艺进行设计,当采样频率为50 KS/s,输入正弦波信号频率为1.5 kHz左右时,ADC的有效位数(Effective Number of Bits,ENOB)为9.91位,总功耗低于450 nW,面积为136μm×176μm,非常适合植入式生物医疗电子的应用.%A 10-bit low power SAR (Successive-Approximation-Register, SAR) ADC (Analog-to-Digital Converter, ADC) is proposed in this paper. The internal digital-to-analog conversion is designed with an improved capacitive switching scheme. By using split-capacitor array, sequence initialization and sub-reference voltage, the switching energy is reduced by 97.6% and the number of the unit capacitor is reduced by 87%, compared with the traditional structure. The 10-bit ADC is designed based on a 65nm CMOS process. When 1.5 kHz fully-differential input signals are sampled at 50 KS/s sampling rate , the ENOB of the ADC is 9.91. The power consumption of this ADC is less than 450nW , and the area is 136μm × 176μm, making this proposed ADC very suitable to implantable bioelectronics.【期刊名称】《电子设计工程》【年(卷),期】2017(025)002【总页数】5页(P80-84)【关键词】模/数转换器;逐次逼近;新型电容开关切换技术;分段电容;低功耗【作者】孙甜甜【作者单位】西安邮电大学电子工程学院,陕西西安 710121【正文语种】中文【中图分类】TP302目前集成电路特征尺寸已经减小到纳米级,片上系统(System-on-Chip,SoC)的集成度也大幅提高。

一种高线性度CMOS自举采样开关

p ryo e a pe nlgs n l i cl. h o l eri c s a l c c t rc c e ru h ui fh m l a a g a d et T e ni a t s u h mpe l k ie, l k edt o g t t s d o i r y n n ie s a s o jt o f h

( ADC)电路是 实现从 模拟到数字 的转 换接 口,对 于

1 引 言

随着 C MOS集 成 电路 工艺技术 的迅 速发展 ,芯 片集 成度 不断提 高 ,片上 系统 ( OC)是 现在集 成 S

a dc ag jcino tesmpigs thcnb jce ral ya ihl e ryCMOSsmpigs th n h rei et f h a l c a e ee tdg et b g n ai n o n wi r y h i t a l c . n wi

pi g s i h i s use . e o d y asmpl i h l e rt l w t sdic s d S c n l , i n c eh g n aiy CM O Sb o srp d s m p ig s th i e i n d. i o tta pe a l wic sd sg e n

(. 1 无锡市商业职 业技术学院 ,江苏 无锡 2 4 5 ;2北京华航无线 电测量研究所 ,北京 10 1 ; 1 13 . 0 0 3

3中 国 电子 科 技 集 团 公 司第 5 研 究 所 ,江 苏 无 锡 2 4 3 ) . 8 1 0 5

摘

要 :作 为 ADC 系统与外界 的接 口,采样开 关 的性 能优 劣直接 决 定 了ADC所接 收到 的信号 纯

一种新型栅压自举开关的设计

一种新型栅压自举开关的设计卞腾飞;莫冰;高城;高磊;傅文渊【摘要】设计一种新型自举开关(Boost Bootstrap)电路结构,应用于SAR ADC的采样保持电路中,从而实现over-rail input range.此结构改进了之前同种电路输入电压不能高于2*VDD的不足.采用SMIC 55nm低压工艺,电源电压0.6V,在Cadence Spectre环境下进行电路仿真.结果表明:该电路在采样期间基本保持输出电压比输入信号大1.15V,满足SAR ADC中采样保持电路的应用需求.【期刊名称】《现代计算机(专业版)》【年(卷),期】2018(000)001【总页数】4页(P69-72)【关键词】栅压自举开关;Cadence Spectre;SARADC;采样保持;低压工艺【作者】卞腾飞;莫冰;高城;高磊;傅文渊【作者单位】华侨大学信息科学与工程学院,厦门 361021;华侨大学信息科学与工程学院,厦门 361021;华侨大学信息科学与工程学院,厦门 361021;华侨大学信息科学与工程学院,厦门 361021;华侨大学信息科学与工程学院,厦门 361021【正文语种】中文0 引言随着CMOS工艺的不断迅速发展,工艺尺寸也在不断地降低,电源电压也按一定比例降低,因此对模数转换器(ADC)要求也越来越苛刻。

由于在现有的ADC架构中逐次逼近模数转换器(SAR ADC)中等精度、低功耗等特点,适应于低压小尺寸CMOS工艺,广泛应用于传感器网络、微处理器中。

SAR ADC的主要结构包括:采样保持电路、比较器、DAC、逻辑控制模块等。

高性能采样保持电路是ADC重要组成部分,其动态性能直接影响SAR ADC的性能。

为了提高ADC的线性度。

在栅压自举开关工作过程中部分节点电压会高于供电电压,以达到一个合理的等效电阻。

本文设计了一种新型栅压自举开关电路,并实现over-rail输入。

1 采样保持电路[1-2]一个MOS管在大信号工作的情况下,利用其导通和截止特性可以简单的构成一个开关。

常用CMOS模拟开关引脚功能和工作原理

开关在电路中起接通信号或断开信号的作用。

最常见的可控开关是继电器,当给驱动继电器的驱动电路加高电平或低电平时,继电器就吸合或释放,其触点接通或断开电路。

CMOS模拟开关是一种可控开关,它不象继电器那样可以用在大电流、高电压场合,只适于处理幅度不超过其工作电压、电流较小的模拟或数字信号。

一、常用CMOS模拟开关引脚功能和工作原理1.四双向模拟开关CD4066CD4066 的引脚功能如图1所示。

每个封装内部有4个独立的模拟开关,每个模拟开关有输入、输出、控制三个端子,其中输入端和输出端可互换。

当控制端加高电平时,开关导通;当控制端加低电平时开关截止。

模拟开关导通时,导通电阻为几十欧姆;模拟开关截止时,呈现很高的阻抗,可以看成为开路。

模拟开关可传输数字信号和模拟信号,可传输的模拟信号的上限频率为40MHz。

各开关间的串扰很小,典型值为-50dB。

2.单八路模拟开关CD4051CD4051 引脚功能见图2。

CD4051相当于一个单刀八掷开关,开关接通哪一通道,由输入的3位地址码ABC来决定。

其真值表见表1。

“INH”是禁止端,当“INH”=1时,各通道均不接通。

此外,CD4051还设有另外一个电源端VEE,以作为电平位移时使用,从而使得通常在单组电源供电条件下工作的 CMOS电路所提供的数字信号能直接控制这种多路开关,并使这种多路开关可传输峰-峰值达15V的交流信号。

例如,若模拟开关的供电电源VDD=+5V, VSS=0V,当VEE=-5V时,只要对此模拟开关施加0~5V的数字控制信号,就可控制幅度范围为-5V~+5V的模拟信号。

表13.双四路模拟开关CD4052CD4052的引脚功能见图3。

CD4052相当于一个双刀四掷开关,具体接通哪一通道,由输入地址码AB来决定。

其真值表见表2。

4.三组二路模拟开关CD4053CD4053的引脚功能见图4。

CD4053内部含有3组单刀双掷开关,3组开关具体接通哪一通道,由输入地址码ABC来决定。

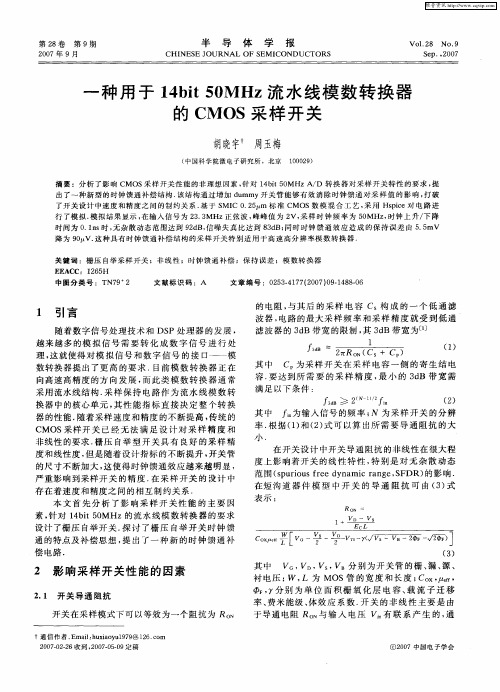

一种用于14bit 50MHz流水线模数转换器的CMOS采样开关

时 间 为 0 1 s , 杂 散 动 态 范 围达 到 9 d 信 噪 失 真 比达 到 8 d 同 时 时 钟 馈 通 效 应 造 成 的保 持 误 差 由 5 5 .n 时 无 2 B, 3 B; . mV

胡晓宇 周玉梅

( 国科 学 院 微 电 子 研 究 所 ,北 京 10 2 ) 中 0 0 9

摘 要 :分 析 了影 响 CMOS采 样 开 关性 能 的 非理 想 因 素 , 对 1 bt 0 针 4 i5 MHzA D 转 换 器 对 采 样 开 关 特 性 的 要 求 , / 提 出 了一 种 新 型 的时 钟 馈 通 补 偿 结 构 . 该结 构通 过 增 加 d mmy开 关 管 能 够 有 效 消 除 时 钟 馈 通 对 采 样 值 的 影 响 , 破 u 打 了开 关 设 计 中速 度 和 精 度 之 间 的 制 约 关 系 . 于 S C 0 2 标 准 CMOS数 模 混 合 工 艺 , 用 H pc 对 电路 进 基 MI .5 m 采 si e

的电阻 , 与其 后 的采 样 电容 c 构 成 的一 个 低 通 滤 波器, 电路 的最大 采 样 频率 和采 样 精 度 就 受 到低 通 滤 波器 的 3 B带宽 的限制 , 3 B带 宽为 [ d 其 d 1 ] ,a s e () 1

其 中 c。 为采 样 开关 在 采 样 电容 一侧 的 寄生 结 电 容 . 达 到所 需 要 的采 样 精 度 , 小 的 3 B 带 宽 需 要 最 d 满足 以下 条件 :

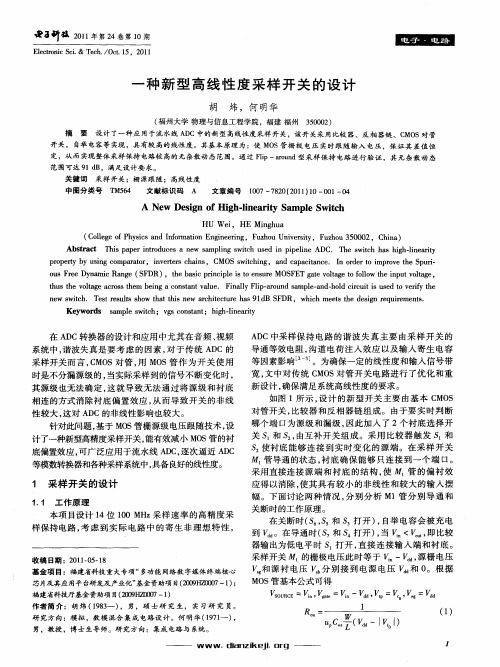

一种新型高线性度采样开关的设计

计了一种新型高精度采样开关 , 能有效减小 M S管的衬 O

底偏 置效应 , 可广 泛应 用 于流 水线 A C 逐 次逼 近 A C D , D 等模数转换 器和各种 采样 系统 中, 具备 良好 的线性度 。

如 图 1 示 , 计 的新 型 开 关 主 要 由基 本 C S 所 设 MO 对 管 开关 , 比较 器 和 反 相 器 链组 成 。由 于要 实 时 判 断 哪个 端 口为源 级 和漏 级 , 因此 加入 了 2个 衬底 选 择 开 关5 和 J , s 由互 补 开关 组 成 。采 用 比较 器 触 发 5 : 和

Ke wo ds s mpe s th; v sc n t n ;h g -i e rt y r a l wi c g o sa t ih l a i n y

在 A C转换器 的设 计 和应 用 中尤 其在 音 频 、 D 视频 系统 中 , 波失 真 是 要 考 虑 的 因素 , 于传 统 A C的 谐 对 D

HU e . HE n h a W i Mi g u

( o eeo P yi n fr a o n i eig uhuU i r t,F zo 50 2 hn ) C l g f hs s dI o t nE g er ,F zo n e i l ca n m i n n v sy uhu3 00 ,C ia

摘

要

设 计了一种应 用于流 水线 A C中的新型 高线性度 采样开关 ,该开关采用 比较 器、反相 器链 、C S对 管 D MO

开关 ,自举 电容 等  ̄J - E,具有较 高的线性度 。其基本原理 为 :使 MO . S管栅极 电压 实时跟 随输 入 电压 ,保证 其差值 恒

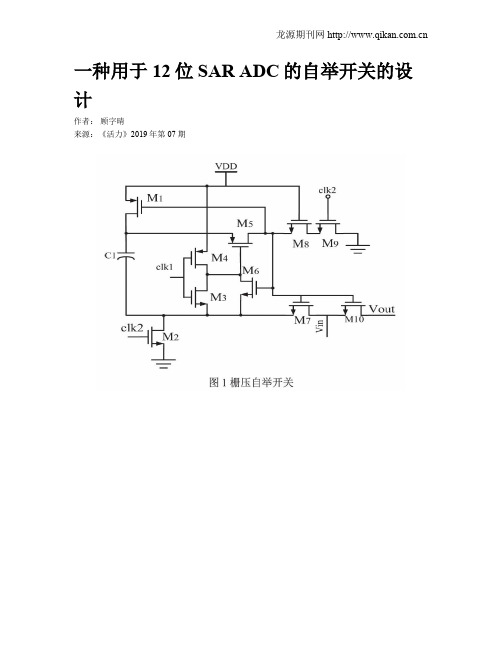

一种用于12位SAR ADC的自举开关的设计

一种用于12位SAR ADC的自举开关的设计作者:顾字晴来源:《活力》2019年第07期【摘要】在传统自举开关的基础上,设计了一款应用于12位$AR ADC的栅压自举开关电路。

电路采用0.18um标准CMOS工艺,仿真结果显示该电路可实现栅压自举,有效位数高达14位,满足各项性能指标。

【关键词】自举开关;SARADC;有效位数CMOS导通电阻虽然很小,当工作电压转向低压时,开关在小幅度信号控制下不能充分完成导通关断操作,很难完成高线性度的采样工作,当采样完成后开关开路,会有电荷注入问题影响SAR ADC输入信号的精度。

所以需要采样更好性能的开关,栅压自举开关应运而生。

一、电路设计在设计中,采样保持电路的精度一般都要比ADC设计精度高2位以上,才能很好地完成采样工作。

但传统开关都无法满足12位SARADC的线性度要求,所以本文设计了图1所示的栅压自举开关电路。

图1结构的自举开关与传统结构的自举开关相比,显著的优势是减少了电荷泵电路,同时将M1管换成了PMOS管,这样能在版图设计中减少电容面积的消耗同时降低了功耗。

图中CIk1信号和CIk2信号是一组反相时钟。

当cIk2信号是高电平时,cIkl信号为低电平。

此时,M2管导通,电路对c1进行充电,同时M9将M10栅极电压接地,M5此时关断,使c1和采样管M10隔开。

当CIk2为低电平,M2、M9关断,充电结束,此时clk1电平为高,CIk1通过反相器M3、M4管将M5的栅极拉低,M6、M7栅电位拉到高电路开始导通,完成栅压自举的过程,此时M10栅极电压等于VDD加上Vim信号。

M6、M8是保护管,为了让电路更加可靠。

二、仿真结果及分析对栅压自举开关搭建电路进行仿真,负载电容为2.56pF,采样频率80MHz,Voutp和Voutn输入信号采用为39.76MHz,幅度为500mV,相位相反,采样点数4096。

图2给出了自举开关瞬态仿真波形图。

从图2中可以看出,栅极电压与源极输入信号之间保持一个恒定的差值,即栅源电压恒定,不受输入信号的影响,达到了栅压自举的设计目标。

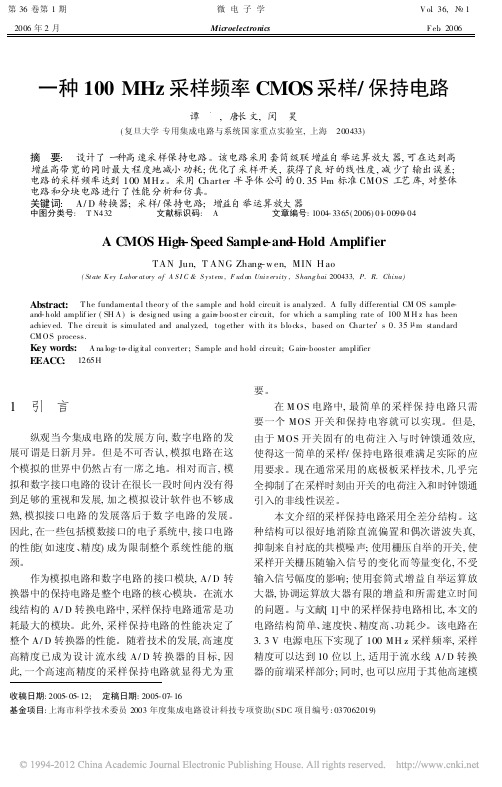

一种100MHz采样频率CMOS采样_保持电路

Abstract: T he fundamenta l theor y of the sample and hold circuit is analyzed. A fully differential CM OS sample-

and- hold amplif ier ( SH A ) is desig ned using a gain- boo st er cir cuit, for which a sampling rate of 100 M H z has been achiev ed. T he circuit is simulated and analyzed, tog ether with it s blo cks, based on Char ter s 0. 35 m standard CM O S process.

间, 使运放能够稳定地工作, 要求自举运放的单位增 益频率 3 满足 2 < 3 < 5 的条件( 其中, 5 是整个 运放的第二极点) 。为了满足设计要求, 在半个时间 周期( 5 ns) 之内完全建立, 需要对自举运放进行电 容补偿, 使其带宽满足上述要求, 从而消除由自举运 放引入的零点和极点问题。

92

谭 等: 一种 100 M H z 采样频 率 CM OS 采样/ 保持电路

2006 年

图 2 自举电路中采样开关的栅源电压

4 套筒式增益增强运算放大器的设计

采样保持电路中的核心部件是运算放大器, 其 性能直接决定了采样保持电路是否可以实现功能。 运算放大器的整体电路如图 3 所示。

度和输入输出电压的指标要求。对于自举运放, 并 不需要很高的增益, 但是希望得到较大的动态范围。 在设计的过程中, 要考虑自举运放和整体运放直接 带宽的相互关系[ 4] 。

自举采样开关原理

自举采样开关原理采样电路,具有一个模拟信号输入,一个控制信号输入和一个模拟信号输出。

该电路的原理是在某个规定的时刻接收输入电压,并在输出端保持该电压直至下次采样开始为止。

采样电路通常有一个模拟开关,一个保持电容和一个单位增益为1的同相电路构成。

采样工作在采样状态和保持状态的两种状态之一。

在采样状态下,开关接通,它尽可能快地跟踪模拟输入信号的电平变化,直到保持信号的到来;在保持状态下,开关断开,跟踪过程停止,它一直保持在开关断开前输入信号的瞬时值。

功放电路工作原理:利用三极管的电流控制作用或场效应管的电压控制作用将电源的功率转换为按照输入信号变化的电流。

因为声音是不同振幅和不同频率的波,即交流信号电流,三极管的集电极电流永远是基极电流的B倍,B是三极管的交流放大倍数,应用这一点,若将小信号注入基极,则集电极流过的电流会等于基极电流的B倍,然后将这个信号用隔直电容隔离出来,就得到了电流(或电压)是原先的B倍的大信号。

要是过压取样一般去找稳压二极管,如果过压了稳压管击穿,这个电压经过稳压管送样PWM调制电路,要是过流取样一般找过流取样电阻,此电阻与负载串联在一起,比如在开关管的源极接一个对地阻值小于1欧姆的电阻,当负载短路时开关管电流过大,自然在电阻上产生一个较大的压降,这个电压在反馈到PWM调制电路采样电阻即是Sense电阻,采样电阻是控制变压器初级绕组的电感电流Ipk的,Ipk越大,输出功率越大,即OCP和OPP越大。

Ipk不能无限的大,需要满足Bmax前提下增大,否则会炸机。

采样电阻即是Sense电阻,采样电阻是控制变压器初级绕组的电感电流Ipk的,Ipk越大,输出功率越大,即OCP和OPP越大。

Ipk不能无限的大,需要满足Bmax前提下增大,否则会炸机。

开关电源,如果采样的输出端的电压,则基本上都是采用大阻抗电阻,再串联一个小电阻或电位器,再在这个位置采样,采样输出端电流则是串联一个精度较高的低阻抗大功率电阻,然后在取这个电阻上的电压(因为这个电压和电流成正比例),如果采样的是全桥或半桥附近的电流一般都用互感器。

一种适用于高速CMOS图像传感器中的采样保持电路设计

一种适用于高速CMOS图像传感器中的采样保持电路设计蔡坤明;丁扣宝;罗豪;韩雁【摘要】设计了一种适用于高速CMOS图像传感器中积分器阵列的采样保持电路.在采样保持电路的保持路径中采用一种抑制衬底偏压效应的T型开关,取代传统的CMOS传输门开关,可以抑制衬底偏压效应带来的阈值变化,保证开关导通电阻的线性度,同时由于在开关设计中引入了T型结构,减少高速输入下寄生电容引入的信号馈通效应,可以实现更为优化的关断隔离.基于SMIC(中芯国际)0.13 μm标准CMOS工艺设计了一个适用于高速采样积分器阵列中的CMOS采样保持电路.Cadence Spectre仿真结果表明在输入信号达到奈奎斯特频率时,电路信噪失真比(SINAD)达到了85.5 dB, 无杂散动态范围 (SFDR)达到92.87 dB,而功耗仅为32.8 mW.【期刊名称】《传感技术学报》【年(卷),期】2010(023)007【总页数】5页(P963-967)【关键词】图像传感器;衬底偏压抑制T型开关;积分器阵列;采样保持电路【作者】蔡坤明;丁扣宝;罗豪;韩雁【作者单位】浙江大学微电子与光电子研究所,杭州,310027;浙江大学微电子与光电子研究所,杭州,310027;浙江大学微电子与光电子研究所,杭州,310027;浙江大学微电子与光电子研究所,杭州,310027【正文语种】中文【中图分类】TN402积分器阵列作为CMOS图像传感器的核心模块,主要完成模数转换之前的信号处理功能。

积分器阵列由多通道积分器、采样保持电路、时序控制电路和降噪声机制[1]组成。

其中的采样保持电路主要对多通道积分器产生的电压信号进行采样和输出,其性能高低直接决定了整个系统性能的好坏。

随着CMOS图像传感器在医疗成像、安全检测和军事侦查等领域的广泛应用,对积分器阵列的性能提出了更高的要求。

特别在当今数字信号处理技术不断发展,军事侦查应用不断出现的背景下,出现了对高速高精度积分器阵列的需求,这些都给阵列积分器电路的设计带来了新的挑战[2]。

一种高速高精度的开环CMO S采样保持电路

一种高速高精度的开环CMO S采样保持电路唐小丽;段吉海;徐卫林;向指航【摘要】In order to improve the nonlinearity caused by switch changing with the input signal amplitude,an open-loop sam-ple and hold circuit based on a gate voltage bootstrapped switch with auxiliary capacitor is proposed.Double capacitance sampling method is adopted to eliminate the charge inj ection effect.And the input switch with traditional double capacitance structure is replaced by a grid bootstrapped switch,the input switch conduction resistance is effectively reduced,which makes conduction resistance independent of the input signal and improves the linearity of the circuit.The circuit is fabricated in SMIC 0.18μm CMOS process.Simulation results show that the improved circuit spurious-free-dynamic range is 92.49 dB,signal-to-noise ratio is 124.98 dB,the effective number of bit is 14.98 bit on the condition that 40 MHz input signal at 500 MHz sample frequency and 1.8 V supply voltage.%针对开关随输入信号幅度变化而导致的非线性,提出了一种基于栅压自举开关、带辅助电容的开环采样保持电路。

自举开关电路专利技术综述

自举开关电路专利技术综述毕爽君;李华芳;孙旭【摘要】本文从专利文献的角度对自举开关电路的发展进行分析,介绍了自举开关电路技术发展路线以及国内外重要技术的发展路线.【期刊名称】《河南科技》【年(卷),期】2017(000)016【总页数】3页(P52-54)【关键词】自举开关;专利;技术发展【作者】毕爽君;李华芳;孙旭【作者单位】国家知识产权局专利局专利审查协作河南中心,河南郑州 450000;国家知识产权局专利局专利审查协作河南中心,河南郑州 450000;国家知识产权局专利局专利审查协作河南中心,河南郑州 450000【正文语种】中文【中图分类】TN710.2Abstract:This paper analyzes the development of bootstrap switch circuit technology from the perspective of patent,then introduces the technical development route of bootstrap switch circuit,and the development direction of domes⁃tic important technology.Key word:bootstrap switch;patent;technology development在采样保持电路中,采样开关的性能决定了信号的采样精度和采样速度。

采样开关一般由MOS开关管实现,MOS开关管的导通电阻由式(1)决定。

从式(1)可看出,导通电阻Ron与栅源电压有关。

一般MOS开关管的源端接输入信号,当输入信号变化时,其栅源电压发生变化,从而使其导通电阻不为一恒定值,降低了MOS 开关管的线性度,最终导致输出信号产生谐波失真。

为了消除上述因素导致的MOS开关管的非线性,通常采用栅压自举开关电路结构[1]。

使MOS管的栅源电压保持为一恒定电压V1,根据式(1)即保证MOS管的导通电阻Ron不随栅源电压的变化而改变,降低对电路的动态性能的影响。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

适 用 于 中频 采 样 的 C MOS 自举 采 样 开 关

钱 宏文 , 朱燕君 , 季惠才 , 陈珍海

( 中国电子科 技 集 团公 司第 5 8研 究所 , 江 苏无锡

摘

2 1 4 0 3 5 )

要: 分析 了影 响 C MO S采样 开 关性 能的 非 理 想 因素 , 针 对 中频采 样 A / D转 换 器对 采样 开 关特

Th i s me t h o d i s e s p e c i a l l y u s e f u l or f h i g h s p e e d hi g h r e s o l u t i o n I F s a mp l i n g ADCs . Ke y wo r ds:a na l o g t o d i g i t a l c o n v e r t e r;I F s a mp l i ng;b o o t s t r a p pe d s wi t c h;MOS s wi t c h

第 2期 2 0 1 3年 4月

中 I 鼋 鼋; 珂譬 研宪 障碍瓤

J o u r n a l o f C AE I T

Vo l _ 8 No . 2 Ap r . 201 3

d o i :1 0 . 3 9 6 9 / j . i s s n . 1 6 7 3 - 5 6 9 2 . 2 0 1 3 . 0 2 . 0 1 9

性 的要 求 , 改进 得 到 了一种 新型 的 C MO S自举 采样 开 关 。较 之传 统 栅 压 自举 开 关 , 此新 型 MO S采

样 开 关 能够 消除 由于 阈值 电压 随输 入 信 号 变化 所 产 生 的 非 线性 。基 于 0 . 1 8 I x m标准 C MO S数模

( T h e 5 8 t h R e s e a r c h I n s t i t u t e o f C E T C , J i a n g s u Wu x i 2 1 4 0 3 5 ,C h i n a )

Ab s t r a c t : T h e m a j o r f a c t o r s t h a t a f f e c t t h e p e r f o r m a n c e o f a C MO S a n a l o g s a m p l i n g s w i t c h i s d i s c u s s e d .

CM OS Bo o t s t r a p p e d Ci r c u i t S u i t a b l e f o r I F S a mp l i n g

Q I A N H o n g - w e n , Z HU Y a n - j u n , J I H u i — c a i , C H E N Z h e n — h a i

d B左 右 。试验 结果表 明该栅 增压 电路 非 常适 用于 高速 中频采 样 。 关键 词 : 模 数 转换 器 ; 中频采 样 ; 栅 压 自举 开关 ; MO S开 关

中 图分类 号 : T N 7 9 2 文献标 识 码 : A 文章 编号 : 1 6 7 3 - 5 6 9 2 ( 2 0 1 3 ) 0 2 - 2 0 9 - 0 4

f r e e d y n a mi c r a n g e o f 1 1 6 . 7 d B f o r a 2 . 3 9 MHz , 2 V Vp — P i n p u t s i g n a l ,s a mp l e d a t a r a t e o f 1 0 0 MS / s .

混合 工 艺对 电路 进行 了模 拟 , 模拟 结 果显 示 , 在 输入 信 号 为 2 . 3 9 MH z 正 弦波 , 峰峰 值 为 2 V, 采 样

时钟频 率为 1 0 0 MH z时 , 开 关的无 杂散 动 态范 围达 到 l l 6 . 7 d B, 较之 传 统 自举 采样 开 关提 高 了 1 5