Digitally-Assisted Analog and RF CMOS Circuit Design for Software-Defined Radio

半导体测试原理

半导体测试公司简介Integrated Device Manufacturer (IDM):半导体公司,集成了设计和制造业务。

IBM:(International Business Machines Corporation)国际商业机器公司,总部在美国纽约州阿蒙克市。

Intel:英特尔,全球最大的半导体芯片制造商,总部位于美国加利弗尼亚州圣克拉拉市。

Texas Instruments:简称TI,德州仪器,全球领先的数字信号处理与模拟技术半导体供应商。

总部位于美国得克萨斯州的达拉斯。

Samsung:三星,韩国最大的企业集团,业务涉及多个领域,主要包括半导体、移动电话、显示器、笔记本、电视机、电冰箱、空调、数码摄像机等。

STMicroelectronics:意法半导体,意大利SGS半导体公司和法国Thomson半导体合并后的新企业,公司总部设在瑞士日内瓦。

是全球第五大半导体厂商。

Strategic Outsourcing Model(战略外包模式):一种新的业务模式,使IDM厂商外包前沿的设计,同时保持工艺技术开发Motorola:摩托罗拉。

总部在美国伊利诺斯州。

是全球芯片制造、电子通讯的领导者。

ADI:(Analog Devices, Inc)亚德诺半导体技术公司,公司总部设在美国,高性能模拟集成电路(IC)制造商,产品广泛用于模拟信号和数字信号处理领域。

Fabless:是半导体集成电路行业中无生产线设计公司的简称。

专注于设计与销售应用半导体晶片,将半导体的生产制造外包给专业晶圆代工制造厂商。

一般的fabless公司至少外包百分之七十五的晶圆生产给别的代工厂。

Qualcomm:高通,公司总部在美国。

以CDMA(码分多址)数字技术为基础,开发并提供富于创意的数字无线通信产品和服务。

如今,美国高通公司正积极倡导全球快速部署3G网络、手机及应用。

Broadcom:博通,总部在美国,全球领先的有线和无线通信半导体公司。

FPGA可编程逻辑器件芯片XC7VX690T-3FFG1926I中文规格书

Virtex-5 Family OverviewDS100 (v5.1) August 21, 2015Product SpecificationDigitally Controlled Impedance (DCI)Active I/O Termination•Optional series or parallel termination •Temperature and voltage compensation •Makes board layout much easier−Reduces resistors −Places termination in the ideal location, at the signalsource or destination Configuration •Support for platform Flash, standard SPI Flash, or standard parallel NOR Flash configuration •Bitstream support with dedicated fallback reconfiguration logic •256-bit AES bitstream decryption provides intellectual property security and prevents design copying •Improved bitstream error detection/correction capability •Auto bus width detection capability •Partial Reconfiguration via ICAP port Advanced Flip-Chip Packaging •Pre-engineered packaging technology for proven superior signal integrity−Minimized inductive loops from signal to return −Optimal signal-to-PWR/GND ratios •Reduces SSO induced noise by up to 7x •Pb-Free and standard packages System Monitor •On-Chip temperature measurement (±4°C)•On-Chip power supply measurement (±1%)•Easy to use, self-contained −No design required for basic operation −Autonomous monitoring of all on-chip sensors −User programmable alarm thresholds for on-chip sensors•User accessible 10-bit 200kSPS ADC −Automatic calibration of offset and gain error −DNL = ±0.9 LSBs maximum •Up to 17 external analog input channels supported −0V to 1V input range −Monitor external sensors e.g., voltage, temperature −General purpose analog inputs •Full access from fabric or JT AG TAP to System Monitor •Fully operational prior to FPGA configuration and during device power down (access via JTAG T AP only)65-nm Copper CMOS Process • 1.0V Core Voltage •12-layer metal provides maximum routing capability and accommodates hard-IP immersion •Triple-oxide technology for proven reduced static power consumption System Blocks Specific to the LXT, SXT, TXT, and FXT DevicesIntegrated Endpoint Block for PCI ExpressCompliance•Works in conjunction with RocketIO GTP transceivers (LXT and SXT) and GTX transceivers (TXT and FXT)to deliver full PCI Express Endpoint functionality withminimal FPGA logic utilization.•Compliant with the PCI Express Base Specification 1.1•PCI Express Endpoint block or Legacy PCI Express Endpoint block•x8, x4, or x1 lane width •Power management support •Block RAMs used for buffering •Fully buffered transmit and receive •Management interface to access PCI Express configuration space and internal configuration•Supports the full range of maximum payload sizes •Up to 6x 32 bit or 3x 64 bit BARs (or a combination of 32 bit and 64 bit)Tri-Mode Ethernet Media Access Controller •Designed to the IEEE 802.3-2002 specification •Operates at 10, 100, and 1,000 Mb/s •Supports tri-mode auto-negotiation •Receive address filter (5 address entries)•Fully monolithic 1000Base-X solution with RocketIO GTP transceivers •Supports multiple external PHY connections (RGMII,GMII, etc.) interfaces through soft logic and SelectIO resources •Supports connection to external PHY device through SGMII using soft logic and RocketIO GTP transceivers •Receive and transmit statistics available through separate interface •Separate host and client interfaces •Support for jumbo frames •Support for VLAN •Flexible, user-configurable host interface •Supports IEEE 802.3ah-2004 unidirectional modeVirtex-5 Family OverviewDS100 (v5.1) August 21, 2015Product Specification Table 1:Virtex-5 FPGA Family Members Device Configurable Logic Blocks (CLBs)DSP48E Slices (2)Block RAM Blocks CMTs (4)PowerPC Processor Blocks Endpoint Blocks for PCI ExpressEthernet MACs (5)Max RocketIO Transceivers (6)Total I/O Banks (8)Max User I/O (7)Array (Row x Col)Virtex-5 Slices (1)Max Distributed RAM (Kb)18Kb (3)36Kb Max (Kb)GTP GTX XC5VLX3080x 304,8003203264321,1522N/A N/A N/A N/A N/A 13400XC5VLX50120x 307,2004804896481,7286N/A N/A N/A N/A N/A 17560XC5VLX85120x 5412,96084048192963,4566N/A N/A N/A N/A N/A 17560XC5VLX110160x 5417,2801,120642561284,6086N/A N/A N/A N/A N/A 23800XC5VLX155160x 7624,3201,6401283841926,9126N/A N/A N/A N/A N/A 23800XC5VLX220160x 10834,5602,2801283841926,9126N/A N/A N/A N/A N/A 23800XC5VLX330240x 10851,8403,42019257628810,3686N/A N/A N/A N/A N/A 331,200XC5VLX20T60x 263,1202102452269361N/A 124N/A 7172XC5VLX30T80x 304,8003203272361,2962N/A 148N/A 12360XC5VLX50T120x 307,20048048120602,1606N/A 1412N/A 15480XC5VLX85T120x 5412,960840482161083,8886N/A 1412N/A 15480XC5VLX110T160x 5417,2801,120642961485,3286N/A 1416N/A 20680XC5VLX155T 160x 7624,3201,6401284242127,6326N/A 1416N/A 20680XC5VLX220T 160x 10834,5602,2801284242127,6326N/A 1416N/A 20680XC5VLX330T 240x 10851,8403,42019264832411,6646N/A 1424N/A 27960XC5VSX35T 80x 345,440520192168843,0242N/A 148N/A 12360XC5VSX50T 120x 348,1607802882641324,7526N/A 1412N/A 15480XC5VSX95T 160x 4614,7201,5206404882448,7846N/A 1416N/A 19640XC5VSX240T 240x 7837,4404,2001,0561,03251618,5766N/A 1424N/A 27960XC5VTX150T 200x 5823,2001,500804562288,2086N/A 14N/A 4020680XC5VTX240T 240x 7837,4402,4009664832411,6646N/A 14N/A 4820680XC5VFX30T 80x 385,12038064136682,4482114N/A 812360XC5VFX70T 160x 3811,2008201282961485,3286134N/A 1619640XC5VFX100T 160x 5616,0001,2402564562288,2086234N/A 1620680XC5VFX130T 200x 5620,4801,58032059629810,7286236N/A 2024840XC5VFX200T 240x 6830,7202,28038491245616,4166248N/A 2427960Notes:1.Virtex-5 FPGA slices are organized differently from previous generations. Each Virtex-5 FPGA slice contains four LUTs and four flip-flops (previously it was two LUTs and two flip-flops.)2.Each DSP48E slice contains a 25x 18 multiplier, an adder, and an accumulator.3.Block RAMs are fundamentally 36Kbits in size. Each block can also be used as two independent 18-Kbit blocks.4.Each Clock Management Tile (CMT) contains two DCMs and one PLL.5.This table lists separate Ethernet MACs per device.6.RocketIO GTP transceivers are designed to run from 100Mb/s to 3.75Gb/s. RocketIO GTX transceivers are designed to run from 150Mb/s to 6.5Gb/s.7.This number does not include RocketIO transceivers.8.Includes configuration Bank 0.。

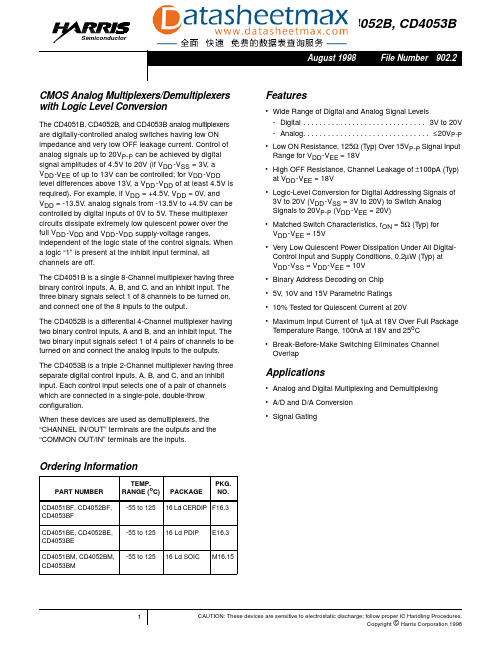

IC资料-CD4501B资料

• 10% Tested for Quiescent Current at 20V

• Maximum Input Current of 1µA at 18V Over Full Package Temperature Range, 100nA at 18V and 25oC

DC Input Voltage Range . . . . . . . . . . . . . . . . . . -0.5V to VDD +0.5V DC Input Current, Any One Input. . . . . . . . . . . . . . . . . . . . . . ±10mA

76543210 4 2 5 1 12 15 14 13

TG

TG

TG

TG

TG

TG

TG

TG

COMMON OUT/IN

3

8 VSS

7 VEE

2

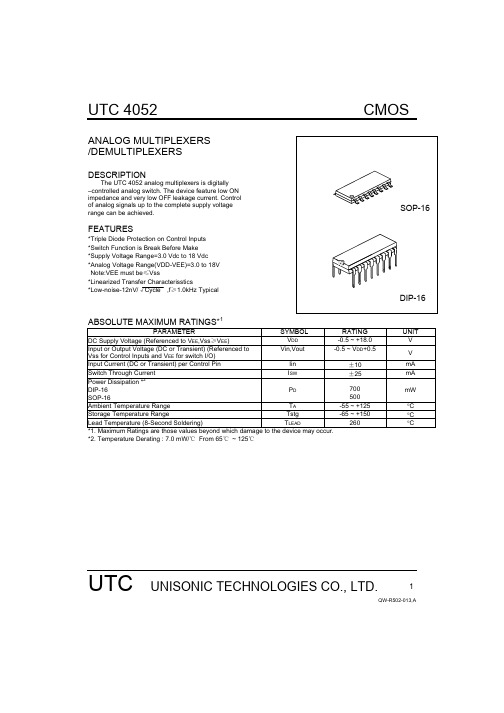

CD4051B, CD4052B, CD4053B

Functional Block Diagrams (Continued)

CD4052B

X CHANNELS IN/OUT 3210 11 15 14 12

15 2 14 1

X CHANNELS IN/OUT

13 COMMON “X” OUT/IN

12 0 11 3

X CHANNELS IN/OUT

10 A

9B

by 1 IN/OUT bx 2

cy 3 OUT/IN CX OR CY 4

IN/OUT CX 5 INH 6 VEE 7 VSS 8

16 VDD 15 OUT/IN bx OR by 14 OUT/IN ax OR ay 13 ay

600_electrical_engineering_books

這600本書幾乎包括了電氣工程專業的所有內容。

例如:電子學最基礎的《Circuit.Analysis.Theory.And.Practice.》(電路分析)、哈佛大學的經典教材《The.Art.of.Electronics》(電子學的藝術)、DSP.Facts.and.Equipment。

詳細書籍名:Wireless.Securit.PrivacyBest.Practices.and.Design.Techniques.Artech-Interference.Analysis.and.Reduction.for.Wireless.Systems.munications.works.munications.Network.Design._20-_20.Wiley._.Sons.802.11.Security.N.Fundamentals.Cisco.Press.eBookwork.Site.Surveying.and.Installation.Cisco.Press.Nov.2004.eBookA.First.Course.in.Corporate.Finance.b.in.Circuits.and.Electronics.munication.er_27s.Guide.to.Aspect.Ratio.Conversion.A.wavelet.tour.of.signal.processing.Mallat.S..draft_.2005.MNw.ponent.Modeling.Morgan.Kaufmann.eBook.-.LiB. Abstract.Harmonic.Analysis.of.Continuous.Wavelet.Transforms.Adaptive.Digital.Filters.Second.Edition.putational.Intelligence.Perspective.Adaptive_20Control_20Systems.Addison.Wesley._20-_20.RTP..Audio.and.Video.for.the.Internet.Advanced.Digital.Signal.Processing.and.Noise.Reduction.2nd.Edition.Advanced.Techniques.in.RF.Power.Amplifier.Design.works.Springer.eBook.Advanced_20Control_20Engineering.Advances.in.Fingerprint.Technology.Second.Edition.eBookworks.Artech.House.Publishers.Jun.2005.eBook. Aerials..Air.and.Spaceborne.Radar.Systems.An.Introduction.2001.WilliamAndrewPublishing.RR. munication.Systems.And.Their.Applications.Alternative.Breast.Imaging.Kluwer.Academic.Publishers.eBook.An.Introduction.To.Statistical.Signal.Processing.An.Introduction.to.Digital.Audio.An.Introduction.to.Pattern.Recognition.An_20Introduction_20to_20the_20Theory_20of_20Microwave_20Circuits_20_Kurokawa_. Analog.BiCMOS.Design.Practices.and.Pitfalls.Analog.Circuit.Design.Analog.Circuits.Cookbook.Analog.Integrated.Circuit.Design.Analog.and.Digital.Circuits.for.Electronic.Control.System.Applications..Analog_20And_20Digital_20Control_20System_20Design.Analysis.And.Design.Of.Analog.Integrated.Circuits.Analysis_20and_20Design_20of_20Integrated_20Circuit-Antenna_20Modules.Antenna_20Arraying_20Techniques_20In_20The_20Deep_20Space_20Network.Antenna_20handbook.rmation.Super.Skyways.Institute.of.Physics.Publishing.Feb.2004.eBook-DDU. Application.-.Specific.Integrated.Circuits.-.Addison.Wesley.Michael.John.Sebastian.Smith. munications.2002.Art.And.Business.Of.Speech.Recognition.Addison.Wesley.eBook.yout.Artech..Radio.Frequency.Integrated.Circuit.Design.Artech.House.GPRS.for.Mobile.Internet.rmation.theory.Asynchronous.Circuit.Design..Audel.Electrical.Course.for.Apprentices.and.Journeymen.eBook.Automated.Fingerprint.Identification.Systems..AFIS..Academic.Press.eBookAutomotive_20Computer_20Controlled_20Systems_20Diagnostic_20Tools_20And_20Techniques. Bandwidth.efficient.digital.modulation.in.deep.munications.ponents._.Hardware.-.I.CFS.ponents._.Hardware.-.II.CFS.Basic.Theory.and.Application.of.Transistors.Bebop.to.the.Boolean.Boogie.Bluetooth.Application.Developers.Guide.Bluetooth.Demystified.Bluetooth.Security.2004.BluetoothGuide.Broadband.Bible.John.Wiley.and.Sons.eBook.Broadband.Bringing.Home.the.Bits.Broadband.Microwave.Amplifiers.Artech.House.eBook-TLFeBOOK.Building.Financial.Models.McGraw-Hill.2004.works.with.802.11.eBook.C.Algorithms.for.Real._20-_20.time.DSP.1995.CAD_20of_20Microstrip_20Antennas_20for_20Wireless_20Applications.CDMA.Capacity.and.Quality.Optimization.CDMA.Mobile.Radio.Design.Artech.House.CDMA.RF.System.Engineering.CDMA.Systems.Capacity.Engineering.Artech.House.Publishers.eBook._20-_20.kB.CMOS.Analog.Circuit.Design.CMOS.Electronics.How.It.Works.How.It.Fails.yout.CMOS.Integrated.ADC.and.DAC.2ndEd..CMOS.PLL.Synthesizers.Analysis.and.Design.Springer.Nov.2004.eBook.-.LinG.CMOS.memory.circuits.CRC.Press.munications.Facility.Design.Handbook.CRC_20Press_20-_20Intelligent_20Control_20Systems_20Using_20Soft_20Computing_20Metho dologies.Cellular.Mobile.Radio.Systems.Designing.Systems.For.Capacity.Optimization.Circuit.-.techniques-for-low-voltage-high-speed-ADCs.Circuit.Analysis.Theory.And.Practice.Circuit.Design.for.RF.Transceivers.munications.Circuits.for.the.Hobbyist.Closed.Circuit.Television.Closing.The.Gap.Between.ASIC.and.Custom.Tools.And.Techniques.of.High.Performance.ASIC.Desig n.work.Test.and.Measurement.Handbook.works._20-_20.Fundamental.Concepts.-.McGraw.Hill.-.Leon-Garcia_.Widjaja. Communications.Receivers.DSP_.Software.Radios_.and.Design_.Third.Edition.Compact_20and_20Broadband_20Microstrip_20Antennas.Complete.Wireless.Design.Computer.Explorations.in.Signals.and.Systems.Computer.imaging.recipes.in.C.Myler.H.R._.Weeks.A.R..PH_.1993pi.T.munication.Consumer_27s.Guide.to.Cell.Phones.and.Wireless.Service.Plans.Continuous.-.Time.Active.Filter.Design.Control_20EngineeringGuide_20For_20Beginners.Coplanar_20Waveguide_20Circuits__20Components__20and_20Systems.Crane.R..Simplified.approach.to.image.processing.in.C.PH_.1997.T.ISBN.0132264161.DOE.Fundamentals.Handbook_.Electrical.Science.vol.1.DOE.Fundamentals.Handbook_.Electrical.Science.vol.2.DOE.Fundamentals.Handbook_.Electrical.Science.vol.3.DOE.Fundamentals.Handbook_.Electrical.Science.vol.4.DSP.Facts.and.Equipment.DSP.Realtime.Operating.Systems.for.Embedded.Systems.DSP.for.In.Vehicle.and.Mobile.Systems.Springer.eBook-YYePG.working.Devices._20-_20.Fourth.Edition.Data.Conversion.Handbook.Elsevier.eBook.-.LinG.Deep.Submicron.CMOS.Circuit.Design.Simulator.In.Hands.Delmar.Digital.Signal.Processing._20-_20.-Filtering.Approach.Delmar.Fiber.Optics.Technician_27s.Manual.2nd.Ed..Design.Of.Linear.RF.Outphasing.Power.Amplifiers.Artech.House.eBookNs.Springer.Sep.2005. Design.of.Analog.CMOS.Integrated.Circuits.Design_20of_20RF_20And_20Microwave_20Amplifiers_20And_20Oscillators..Designing.Analog.Chips.work.works.Developments.in.Speech.Synthesis.John.Wiley.Sons.Apr.2005.eBook._20-_20.LinG. Dictionary.of.Video.Television.Technology.Dielectric_20Resonator_20Antennas.Digital.Audio.Broadcasting.munication.Over.Fading.Channels.munications.Design.for.the.Real.World.Digital.Design.Fundamentals.Digital.Design.Principles.and.Practices.Digital.Electronics.Digital.Frequency.Synthesis.Demystified.Digital.Integrated.Circuits.wo02_8.munication.Digital.Logic.And.Microprocessor.Design.With.VHDL.Digital.Signal.Processing.Handbook.VK.Madisetti_DB.Williams_CRC.ing.C.bVIEW.Newnes.Jun.2005.eBook._20-_20.D DU.munications.Ieee.Digital.Switching.Systems.System.Reliability.and.Analysis.Digital.Synthesizers.and.Transmitters.for.Software.Radio.Springer.Jul.2005.eBook._20-_20.DDU. Digital.Systems.Engineering..Digital.Video.Quality.Vision.Models.and.Metrics.John.Wiley.and.Sons.Mar.2005.eBook._20-_20.D DU.Digital.Video.for.Dummies.Wiley..2003._.3Ed.Digital.image.processing._20-_20.B.Jahne.Digital.signal.Processing.Digitally.Assisted.Pipeline.ADCs.Theory.and.Implementation.Discovering.Bluetooth.Sybex.Discrete.Time.Signal.Processing._20-_20.Oppenheim.Distortion.Analysis.of.Analog.Integrated.Circuits.Distortion.in.rf.power.amplifiers.ebook._20-_20.lib.Duda.R.O._.Hart.P.E._.Stork.D.G..Pattern.classification.02ed._.Wiley.C.738s.EDGE.for.Mobile.Internet.ESD.In.Silicon.Integrated.Circuits.Electrical.Circuits.plante_CRC.Electrical._.Electronic.Principles._.Technology.-.0750665505.Newnes.John.Bird.Electrician_27s.Exam.Question.and.Answers.Electromagnetic_20Waves_20and_20Antennas.Electronics.for.Dummies.John.Wiley.and.Sons.eBook.-.LinG.Electronics.for.Hobbyists.1.Electronics.for.Hobbyists.2.Electronics.for.Hobbyists.3.Electronics.for.Hobbyists.4.Electronics.for.Hobbyists.5.Electronics.for.Hobbyists.6.Electronics.for.Hobbyists.7.work.Technologies.Springer.Sep.2004.eBook._20-_20.LinG. working.Engineer_27s.Mini.-._5bNotebook.-.555_5d.-.Timer.IC.Circuits.Engineer_27s.Notebook.II.A.Handbook.Of.Integrated.Circuit.Applications.-.Forrest.Mims. Engineering.Digital.Design.rmation.Theory.Error.control.coding..From.theory.to.practice.Sweeney.P..Wiley_2002.Essentials.of.Managing.Corporate.Cash.-.John.Wiley.Sons.Experimental.Approach.CDMA._.Interference.From.Architecture.Through.VLSI.Fast.Forward.MBA.in.Finance.Feedback.Amplifiers.Theory.and.Design.Feedback.Circuit.Analysis.Feedback.Linearization.of.RF.Power.Amplifiers.Feedbackcontroltheory.munication.Systems.Fiber.Optic.Sensors.Fiber.to.the.Home.The.New.Empowerment.Wiley.Interscience.Oct.2005.eBook._20-_20.LinG. Fibre.Channel.for.Mass.Storage._20-_20.Prentice.Hall.Fibre.Channel.for.SANs.Filter.Handbook.a.Practical.Design.Guide.-.S..Niewiadomski.Finance.for.Non.-.Financial.Managers.Financial.Engineering.Principles.A.Unified.Theory.Financial.Risk.Manager.Handbook.Wiley.Second.Edition.Financial.modeling.with.jump.processes.Finite_20Antenna_20Arrays_20and_20FSS.First.course.on.wavelets.Hernandez_.Weiss..CRC_.1996.T.ISBN.0849382742.Fixed.Broadband.Wireless.System.Design._20-_xxuss.For.Dummies.HDTV.For.Dummies.Nov.2004.eBook._20-_20.DDU.Fundamental_20Limitations_20In_20Filtering_20And_20Control.Fundamentals.Of.Electric.Circuits..Fundamentals.Of.RF.Circuit.Design.With.Low.Noise.Oscillators.munication.Fundamentals.of.Global.Positioning.System.Receivers.Fundamentals.of.Telecommunications.Fundamentals.of.wavelets..Theory_.algorithms_.and.applications.Goswami_.Chan..Wiley.T.319s. Fuzzy_20Control_20Systems_20-_20Design_20and_20Analysis.munications.works..Protocols.Terminology.and.Implementation.GSM.Switching.Services.and.Protocols.Getting.Started.As.a.Financial.Planner.Rev.and.Updated.Guide.To.Budgets.And.Financial.Management.Guide.To.Digital.Signal.Processing.HF_20Antenna_20Cookbook.HF_20Filter_20Design_20and_20Computer_20Simulation.Handbook.Of.Time.Series.Analysis_.Signal.Processing_.And.Dynamics.Handbook.of.Multisensor.Data.Fusion.puting.munications.works.Harjani.Design.Of.Modulators.For.Oversampled.Converters.Wang.-.1998.High.-.Speed.Signal.Propagation.Advanced.Black.Magic.Prentice.eBook-LiB.High.-.speed.Digital.Design.-.Johnson._.Graham.High.Frequency.Techniques.An.Introduction.to.RF.and.Microwave.Engineering.Wiley-IEEE.Press.. High_20Performance_20Control.IEE.Tutorial.Meeting.on.Digital.Signal.Processing.for.Radar.and.Sonar.Applications_.1990. IEEE.._20-_20..Telecommunications.Performance.Engineering.IEEE._20-_20.Adaptive.fuzzy.power.control.for.CDMA.mobile.radio.systems.IEEE._20-_work.Modeling_.Planning.and.Design.work.Design.Guide.IP.Routing.working_3b.Straight.to.the.Core.Ieee._20-_munication.Circuits.And.Systems.works.Springer.Sep.2005.eBook._20-_20.DDU. bVIEW.And.IMAQ.Vision.Prentice.eBook._20-_20.LiB.Image.Processing.in.C.Image.Recognition.and.Classification..algorithms-marcel.dekker.-.2002.-.isbn.0824707834.-.49. works.Newnes.Jul.2004.eBook._20-_20.DD U.Implementing.Bluetooth.in.an.Embedded.Device.Industrial.electronics.for.engineers_.chemists_.and.technicians.Industrial_20Control.Integrated.Electronics.Integrated.Fiber.Optic.Receivers.Buchwald.Intermodulation_20Distortion_20in_20Microwave_20and_20Wireless_20Circuits. Introduction.To.Error.Correcting.Codes.Introduction.To.Logic.Design.-.Shiva.S.G..-.M.Dekker.1998.2Ed.Introduction.To.Sound.Processing.work.Engineering.Introduction.to.03G_munications.Introduction.to.Airborne.Radar.Introduction.to.Bluetooth.Technology_.Market_.Operation_.Profiles_._.Services. Introduction.to.CPLD.and.FPGA.Design.Introduction.to.Fiber.Optics.Introduction.to.RF.Equipment.and.System.Design.Introduction.to.RF.Propagation.Wiley.Interscience.Sep.2005.eBook._20-_20.DDU. Introduction.to.Wireless.Local.Loop.Introduction_to_Wave_Propagation_Transmission_Lines_and_Antennas.John.Wiley.And.Sons.An.Introduction.To.Parametric.Digital.Filters.And.Oscillators.John.Wiley.And.Sons.Device.Modeling.For.Analog.And.RF.CMOS.Circuit.Design.John.Wiley.And.Sons.Digital.Logic.Testing.And.Simulation.John.Wiley._20-_20.Fundamentals.of.Digital.Television.Transmission.John.Wiley._20__20.Sons._20-_works.John.Wiley._20__20.Sons._20-_20.Mobile.and.Wireless.Design.Essentials.work.Design.Aug.2004.eBook._2 0-_20.DDU.John.Wiley.and.Sons.Multi.Carrier.and.Spread.Spectrum.Systems.works.Karu.J..Signals.and.systems_.made.ridiculously.simple.2001.L.T.ISBN.0964375214.Kay.S.M..Fundamentals.of.statistical.signal.processing...estimation.theory.PH.L.T.30.Ken.Martin.Digital.Integrated.Circuit.Design.300dpi.ponents.eBook.-.LiB. works.eBook._20-_20.LiB. Kluwer.Reuse.Methodology.Manual.for.System.-.on-a-Chip.Designs.3rd.Ed..LabVIEW.Digital.Signal.Processing.McGraw.Hill.Professional.May.2005.Layout.CMOS..Circuit.Design._.Li.Simulation.Baker._Boyce.-.1997.2.Linear_20Control_20System_20Analysis_20and_20Design_20Fifth_20Edition.Linear_20Optimal_20Control.Liquidity.Liabilities.Cash.Management.Balancing.Financial.Risks.Wiley.Low-Angle_Radar_Land_Clutter_-_Measurements_and_Empirical_Models.Lumped_20Elements_20for_20RF_20and_20Microwave_20Circuits.MPEG.7.Audio.and.Beyond.Audio.Content.Indexing.and.Retrieval.John.Wiley.and.Sons.Jan.2006. puter.Vision.Springer.Aug.2005.eBook._20-_20.DDU.McGraw.-.Hill.Teach.Yours.Electricity.and.ElectronicsEbook-FLY.McGraw.Hill.-.Principles.and.applications.of.Electrical.Engineering.McGraw.Hill.Financial.Analysis.Tools.and.Techniques.a.Guide.for.Managers.McGraw.Hill._20-_ponents.McGraw.Schaum_27s.Outlines.of.Digital.Signal.Processing.McGraw.Schaum_27s.Outlines.of.Signals._.Systems.McGraw._20-_20.Hill.-.Broadband.Crash.Course.-.2002.McGraw._20-_20.Hill.-.Wireless.A.to.Z.puter._20-_20._20T.266s_20.-.oriented.Approach.to.Pattern.Recognition.AP_.19 72.Microstrip_20Filters_20For_20RF_20Microwave_20Applications.Microwave_20Circuit_20Modeling_20Using_20Electromagnetic_20Field_20Simulation. Microwave_20Component_20Mechanics.Microwave_20Electronics_20Measurement_20and_20Materials_20Characterization. Microwave_20Resonators_20and_20Filters_20For_20Wireless_20Communication.Microwave_engineering_using_microstrip_circuits_.Microwaves.and.Wireless.Simplified.Artech.House.2nd.Edition.Apr.2005.Millimeter.-.wave.Integrated.Circuits.Springer.eBook-YYePG.Mixed.Signal.And.DSP.Design.Techniques.working._20-_20.John.Wiley._.Sons.-.IEEE.Press.munications.Engineering._20-_20.Theory.and.Applications_.Second.Edition. munications.Mobile.Location.Services.The.Definitive.Guide._20-_20.Prentice.Hall.works.Wiley._20-_20.eBOOK.Model.Based.Signal.Processing.Wiley.IEEE.Press.Oct.2005.eBook._20-_20.LinG.Modern.Antenna.Design.Jun.2005.eBook-DDU.munication.Circuits.Modern.Receiver.Front.Ends.Systems.Circuits.and.Integration.Wiley.Feb.2004.eBook-DDU. Modern.Signal.Processing.Modern_20Control_20Engeneering__203rd_20ed_5d._5bOgata_5d_5bPrentice_20Hall_5d. Morgan.Kaufmann.._20-_20..Digital.Video.And.Hdtv.Algorithms.And.Interfaces.2003.Multi.-.Standard.CMOS.Wireless.Receivers_.Analysis._.Design.Multicarrier.Techniques.for.04G_munications.Multivariable.Control.Systems.An.Engineering.Approach.Springer.eBook-TLFeBOOK.Nano.CMOS.Circuit.and.Physical.Design.Network.Calculus.A.Theory.of.Deterministic.Queuing.Systems.for.the.Internet.Networks_20and_20Devices_20Using_20Planar_20Transmissions_20Lines.Neural_20Systems_20For_20Control.New.technologies.for.WLAN.munications.Pocket.Book.Newnes.Guide.to.Television._.Video.Technology.Newnes.Radio.and.RF.Engineering.Pocket.Book.Newnes_20Industrial_20Control_20Wiring_20Guide.Next.Generation.Mobile.Systems.3G.and.Beyond.John.Wiley.and.Sons.May.2005.eBook._20-_20. DDU.Nixon_.Aguado..Feature.Extraction.and.Image.Processing.2002.Noise.In.Receiving.Systems.Nonlinear.Microwave.And.RF.Circuits.2nd.Edition.Nonlinear_20Microwave_20Circuit_20Design.ON.Analog.Integrated.Circuits.OReilly.Digital.Video.Hacks.May.2005.eBook._20-_20.DDU.OReilly.RFID.Essentials.Jan.2006.O_27Reilly._20-_20._20802._20-_works-.The.Definitive.Guide. Observers_20in_20Control_20Systems.Op.Amp.Applications..Op.Amps.Design.Application.and.Troubleshooting.Op.Amps.for.Everyone.Design.Reference.Operational.Amplifiers.Design.and.Applications.munications.Essentials.munications.Rules.of.Thumb.working.Handbook.Mcgraw._20-_20.Hill.Optical.System.Design.Optical.Through._20-_munications.Handbook.Optical.signal.processing.Vanderlugt.A..Wiley_.1991pi.L.T.180s.PEo.Optimal.Filtering.Optimal_20Control_20Linear_20Quadratic_20Methods.Optimal_20Sampled_20Data_20Control_20Systems.Optimizing.Wireless._20-_20.RF.Circuits.work.Handbook.Pattern.Classification.And.Learning.Theory.Lugosi.nguage.Processing.works.Polling_.Scheduling_.and.Traffic.Cont rol.munications.Phased.Array.Antenna.Handbook.Artech.House.Publishers.Second.Edition.eBook-kB.Phased_20Array_20Antennas_20Hansen_20R.C._20_Wiley_1998__ISBN_20047153076X__200dp i__T__504s__EE_.Photodetection._20__20.Measurement._20-_20.Maximizing.Performance.in.Optical.Systems. Practical.Analog.And.Digital.Filter.Design.Practical.Electronics.for.Inventors.Practical.FPGA.Programming.in.C.Prentice.Hall.PTR.Apr.2005.yout._20-_e.of.Stock.Lenses.Practical.Rf.Pcb.Design.Geoff.Smithson.Scanned.Practical.Rf.System.Design._20-_20.Egan.Practical_20Applications_20of_20Computational_20Intelligence_20for_20Adaptive_20Control. Practical_20Approach_20to_20Signals_20Systems_20and_20Control.Pragmatic.Introduction.to.Electronic.Engineering.0._v1_.works.John.Wiley.and.Sons.munication.system.simulation.with.wireless.applications._20-_20.Prentice.Hall. Principles.Of.Corporate.Finance.Principles.of.Asynchronous.Circuit.Design.-.A.Systems.Perspective.Principles.of.Digital.Transmission.With.Wireless.Applications.Principles.of.Sigma.Delta.Conversion.for.Analog.to.Digital.Converters.munication.Systems.eBook._20-_20.TLFeBOOK. Programmable.Digital.Signal.Processors.Architecture.Programming_.and.Applications. munication.System.Design.QoS.in.Integrated.03GNetworks.2002.Quantitative.Finance.for.Physicists.An.Introduction.Queueing.Theory.With.Applications.to.Packet.Telecommunication.Springer.eBook._20-_20.YYePG. RDS..The.Radio.Data.System.RF-Microwave_20Circuit_20Design_20for_20Wireless_20Applications.ponents.and.Circuits.munications.munications.RFID.Field.Guide.Deploying.Radio.Frequency.Identification.Systems.Feb.2005.eBook._20-_20.LiB. RFID.For.Dummies.Mar.2005.eBook._20-_20.LinG.RFID.Sourcebook.Prentice.Hall.PTR.RFID._20-_20.Read.My.Chips_.RF_20__20Microwave_20Radiation_20Safety_20Handbook.RF_20and_20Microwave_20Wireless_20Systems.Radar.Systems_.Peak.Detection.and.Tracking.Radar.Technology.Encyclopedia._20-_20.1998.Radar_20Principles.munication.and.Sensor.Applications.Radio.Engineers_27.Handbook._20-_20._2001e_20-_20.-.d.-.Terman.Radio.Frequency.Circuit.Design.Radio.Frequency.Transistors.Radio.Shack.-.Getting.started.in.electronics.Radio.Shack.Engineer_27s.Mini.-._5bNotebook.T.52s_5d.Radio._.Electronics.Cookbook.Radio_20Frequency_20and_20Microwave_20Communication_20Circuits.Radiometric.Tracking.Techniques.for.Deep.Space.Navigation.Radiosity.and.realistic.image.synthesis.Cohen.M.F._.Wallace.J.R..AP_.1995.Real.802.11.Security.Wi._20-_20.Fi.Protected.Access.And.802.11i.Addison.Wesley.eBook-LiB. Real.Analog.Solutions.for.Digital.Designers.Real.World.Digital.Audio.Peachpit.Press.No05._20v.200.Real._20-_pression--Techniques.And.Algorithms.Rf.Cmos.Power.Amplifier._20-_20.Ebook.Kluwer.Inter.Hella._.Ismall.Risk.Management.And.Capital.Adequacy.McGraw.Hill.SIP.Demystified.MUNICATIONS.HANDBOOK.munication.Engineering.eBook._20-_20.EEn.Satellite.Handbook.working.Principles.and.Protocols.John.Wiley.and.Sons.Oct.2005.eBook._20-_20.DDU. Schaums.Outline.Of.Theory.And.Problems.Of.Electric.Circuits.eBook.Secrets.of.RF.Circuit.Design._.Third.Edition.Securing.and.managing.WLAN.Shannon._20-_20.TheoryComm.munication.Fundamentals.of.RF.System.Design.and.Application. Signal.Analysis.Alfred.Mertins.Signal.Analysis.Time.Frequency.Scale.and.Structure.RL.Allen_ls.Signal.Detection.and.Estimation.munications.Handbook._20-_20.CRC.Press.-.2005.Signal.analysis.wavelets.filter.banks-Mertins.A..Wiley_.1999.Signals.And.Systems.Signals._20__20.Systems.with.MATLAB.Applications._20-_20.Orchard.Publications. munications.Sliding_20Mode_20Control_20in_20Engineering.Smart.Antennas.CRC.Press.Jan.2004.eBook-DDU.Some.Design.Aspects.on.RF.CMOS.LNAs.and.Mixers.Sonet.or.SDH.Demystified.Space._20-_20.Time.Coding.John.Wiley.And.Sons.eBook.Space._20-_munications.Specification.of.the.Bluetooth.System.Spectrum.Wars.Speech.Coding.Algorithms.Foundation.and.Evolution.of.Standardized.Coders.Wiley.eBook._20-_2 0.KB.works.Speech.Separation.By.Humans._20__20.Machines.Springer.eBook._20-_20.YYePG.Stability_20Analysis_20of_20Nonlinear_20Microwave_20Circuits.pression.to.Advanced.Video.Coding.IEEE.Standard.Handbook.of.Audio.and.Radio.Engineering.Standard.Handbook.of.Video.and.Television.Engineering_.4th.ed.Starting.Electronics.-.Elsevier.-.3rd.Edition.-.2005.Statistical.and.Adaptive.Signal.Processing.Supervised.and.Unsupervised.Pattern.Recognition.Synthesis.and.optimization.of.DSP.algorithms.Constantinides_.Cheung_.Luk..Kluwer_.2004.T.144s_20Bayesian.Approach.to.Image.Interpretation.Kopparapu_.Desai..Kluwer_.2002.T.181s_20Wavelets_.with.applications.in.signal.and.image.processing.Bultheel.A..2002.T.212s_20Brandwood..Fourier.transforms.in.radar.and.signal.processing.2003.T.359s_20Mann.S..Intelligent.image.processing.Wiley_.2002.T.406s_20Dudgeon.D._.Mersereau.R._.Merser.R._.Multidimensional.Digital.Signal.Processing.199 5.T.548s_20Ballard.D.H._.Computer.vision.Brown.C.M..PH_.1982.ISBN.0131653164.T.621s_20Image.analysis.and.mathematical.morphology.Serra.J..AP_.1982.300dpi.CsIp.TAB.Electronics.Guide.to.Understanding.Electricity.and.Electronics.eBook.-.EEn.Telecom.Crash.Course.Telecom.Dictionary.Telecommunication.Circuit.Design._20-_20.Second.Edition.Telecommunications.Essentials.CHM.Telecommunications.Regulation.Teletraffic.Engineering.Handbook.The.Art.and.Science.of.Analog.Circuit.Design.The.Art.of.Electronics.02ed.munications.Professional..A.Guide.for.Engineers.and.Managers. working.The.Engineer_27s.Guide.to.Decoding._.Encoding.The.Engineer_27s.Guide.to.Standards.Conversion.The.Great.Telecom.Meltdown.Artech.House.Jan.2005.eBook._20-_20.LiB.works.munications.Handbook.The.Mobile.Radio.Propagation.Channel._20-_20.Second.Edition.-.Wiley.The.Personal.Finance.Calculator.McGrawHill.munication.Applications.Handbook.The.Telecommunications.Handbook.The.Wireless.Data.Handbook._20-_20.Fourth.Edition.Thetrated.dictionary.of.electronics.Troubleshooting.Analog.Circuits.US.Navy._20-_20.Digital.Data.Systems.Ultra.Wideband.Radio.Technology.ing.Coded.Signals.Understanding.Cellular.Radio.munications.Understanding.Digital.Signal.Processing.Understanding.Digital.Terrestrial.Broadcasting.MAZ._20-_20.Artech.House. munications.Understanding.Telephone.Electronics.Understanding_20Microwaves_20_Scott_.rmation.Retrieval.IRM.eBook._20-_20.YYePG.Video.Demystified.A.Handbook.For.The.Digital.Engineer.munications.Voice.Over.802.11.W._20-_20._20for.03G_works.munications.System.Waveguide_20Handbook.Wavelets.For.Kids.A.Wavelets.For.Kids.B.Wideband.TDD.WCDMA.for.the.Unpaired.Spectrum.John.Wiley.Sons.May.2005.eBook._20-_20.Lin G.Wiley.-.Essentials.of.Financial.Analysis.Wiley._20-_works_.IP.and.the.Internet.-.Protocols_.Design.and.Operation.Wiley._20-_20.Digital.Image.Processing.WK.Pratt.-.Third.Edition.2001.munication.Systems._20-_20.Prentice.Hall.PTR.munication.Technologies.munication.Technology.munications.Wireless.Data.Demystified.McGraw.Hill.eBook._20-_20.LiB.Wireless.Data.Technologies.Reference.Handbook.John.Wiley.and.Sons.Wireless.Foresight.Scenarios.of.the.Mobile.World.in.2015.John.Wiley.and.Sons.eBook._20-_20.Li B.Wireless.Internet.Telecommunications.Artech.House.Publishers.eBook._20-_20.YYePG. working.with.ANSI._20-_20._2041__20-_20.-.Second.Edition.works.First._20-_20.Step..2005.munication.Systems.Springer.Verlag.Telos.Sep.2004.ISBN0387227849. Wireless.Technology.Protocols.Standards.and.Techniques.Young_.Gerbrands_.van.Vliet..Fundamentals.of.image.processing.Delft.U._.1998.T.11._5bT.270s_5dJohnson.D.H._.Wise.J.D..Fundamentals.of.electrical.engineering.1999._5bT.498s_5dGustafsson.F..Adaptive.Filtering.and.Change.Detection.Wiley_.2000._Delmar__20Modern_20Control_20Technology--Components_20__20Systems_20_2nd_20Ed._. dsp.algorithms.for.programmers.eWiley.Mobile.Fading.Channels._20-_20.-Modelling_.Analysis._.Simulation.electronics_20technician_20volume_201_20-_20safety.electronics_20technician_20volume_202_20-_20administration.electronics_20technician_20volume_203_20-_20communications_20systems.electronics_20technician_20volume_204_20-_20radar_20systems.electronics_20technician_20volume_206_20-_20digital_20data_20systems.electronics_20technician_20volume_207_20-_20antennas_20and_20wave_20propagation. low.power.asynchronous.DSP.numerical_20methods_20in_20electromagnetics.operational.amplifiers.-.2nd.edition.practical_aspects_of_feedback_control.structure.and.interpretation.of.signals.and.systems.下載地址:/file/f5ddfade86600_electrical_engineering_books.rar。

低噪放

(一) 国际发展现状

国际上的一些著名大学、研究机构以及 IC公司都己对多模多频段低噪声放大器的设 计做了广泛的研究,并且己经有了相当多的 成果。 2011年8月,日本的Lime Microsystems 公司推出了一款多模多频无线收发芯片 LMS6002,该芯片的工作频率为375MHz--4GHz,可用于3GPP ( WCDMA,HSPA和LTE), 3GPP2 (CDMA2000)以及WiMAX的应用上,其低噪声放大器的噪声系数不超过3dB。 2012年3月,富士通半导体公司推出了单芯片的2G13G/4G收发芯片MB86L1A,该芯 片支持LTE ( FDD和TDD), EDGE, EDGE-EVO, WCDMA,GSM, HSPA+, CDMA以及TD-SCDMA等多 种通信模式。 2013 年1 月,MTK 推出MT3332/MT3333 SoC(片上系统)芯片如图所示,可支持 GPS、北斗、GLONASS、伽利略及QZSS 等5 种全球卫星导航系统的信号,藉由多系统的 相互辅助,能大幅提升导航定位的精度和可靠性,避免误差随时间推移及行程增加而 累积。

传统的单频段LNA技术已趋于成熟,具有源级电感负 反馈结构的LNA由于其低噪声低功耗的特点而得到广泛应 用。 但是,面对多模多频段的需求,基于这种结构的LNA 设计遇到新的困难。首先,其窄带的输入阻抗匹配特点。 源级电感退化LNA输入阻抗只匹配在一个频点上,而多模 多频段需要低噪声放大器在多个频段都能实现匹配。虽然 二阶乃至高阶的输入阻抗匹配以及负载谐振网络能够支持 相隔比较远的两个或多个频带的低噪声放大,但是其在低 噪声放大方面的优势被削弱。

(一) 国际发展现状

2013 年11 月,高通与三星合作推出支持北斗卫星定位功能的旗舰智能手机 GALAXY Note 3(配备高通骁龙800 移动处理器MSM8974),成为首批支持北斗系统 的智能手机。 2013 年12 月,博通公司宣布推出一款支持北斗系统的卫星导航芯片BCM47531 (见图6),它能够同时使用从5 个卫星系统(GPS、GLONASS、QZSS、SBAS 和北斗 卫星)发出的信号来产生定位数据,提高 了导航定位精度,尤其是在性能受建筑和 掩体影响的城区,效果更为明显。 2014 年2 月,MTK 发布了全球首款支 持4G LTE 网片——MT6630,支持20/40/80 MHz 频道带宽,支持低功耗蓝牙,整合了 ANT +(蓝牙健康与健身聚合器套件)技 术,可广泛应用于运动健身配件/ 可穿戴 设备,同时支持GPS、北斗、GLONASS、 伽利略、QZSS 系统。

可变增益放大器VGA研究笔记

Performance summary of the proposed VGA

13

Proposed exponential function generator

It consists of a voltage-to-current converter (VIC), a linear current

减网络,构成VGA。

9

模拟和数字信号控制的比较

In general, digitally controlled VGAs use binary weighted arrays of resistors for gain variations and analog VGAs adopt a variable transconductance to control the gain. For a code division multiple access system requiring a power control range larger than 80dB, the VGA with continuously variable gains is preferred because it avoids signal phase discontinuity that is expected to cause problems, and it reduces the large number of control bits required with digitally controlled VGAs.

15

Linear current multiplier

I(T)是PATA电流,由于M1、M2与M3、M4的栅

极电压对应相等,则有(其中Itot是常数电流):

RS2253 三路双通道模拟多路复用 多路解复用 CMOS 电路芯片说明书

CMOS Triple 2-Channel Analog Multiplexer/DemultiplexerFEATURES•-3dB Bandwidth: 180MHz•Single Supply Operation +2.5V to +5.5V •Low ON Resistance, 48Ω(TYP) With 5V Supply•High Off-Isolation: -83dB (RL = 50Ω,f = 1MHz)•Break-Before-Make Switching•Binary Address Decoding on Chip •Operating Temperature Range:-40°C to +125°C•PACKAGES: SOIC-16(SOP16), SSOP-16, TSSOP-16 and QFN-3×3-16LAPPLICATIONS•Sensors•Analog and Digital Multiplexing and Demultiplexing•A/D and D/A Conversion•Signal Gating•Battery-Operated Equipment•Factory Automation•Appliances•Communications Circuits DESCRIPTIONThe RS2253 is a CMOS analog IC configured as three single-pole/double-throw (SPDT) switches. This CMOS device can operate from 2.5 V to 5.5 V.The RS2253 device are digitally-controlled analog switches. It has low on-resistance (48Ω TYP) and very low off-leakage current (1nA TYP).The RS2253 is available in Green SOIC-16, SSOP-16, TSSOP-16 and QFN-3×3-16L packages. It operates over an ambient temperature range of -40°C to +125°C.Functional Diagrams of RS2253PIN CONFIGURATIONS(TOP VIEW)SOIC-16(SOP16)/SSOP-16/TSSOP-16ENABLEYV CC X X1X0B CAXNC QFN-3×3-16LAX0X1(TOP VIEW)PIN DESCRIPTIONFUNCTION TABLEX=Don’t careNOTE: Input and output pins are identical and inter-changeable. Either may be considered an input or output; signals pass equally well in either direction.ABSOLUTE MAXIMUM RATINGS(1)V CC to GND..........................................................−0.3 to 6VInput Terminals, Voltage. (2) .................– 0.3 to (V+) + 0.3V Continuous Current into Any Terminal......................±20mAPeak Current, X_(Pulsed at 1ms,10% duty cycle)…………………….. ±40mA Storage Temperature ……….……………−65°C to +150°C Operating Temperature ……….…….……−40°C to +125°C Junction Temperature...............................................+150°C Package Thermal Resistance @ T A = +25°CQFN-3×3-16L………………….………..……………. 80°C/WSSOP-16……….…………........................................64°C/WSOIC-16, TSSOP-16………….……….…………….100°C/WLead Temperature (Soldering, 10s) …………….........260°CESD SusceptibilityHBM (1000V)MM (100V)(1) Stresses above these ratings may cause permanent damage. Exposureto absolute maximum conditions for extended periods may degradedevice reliability. These are stress ratings only, and functionaloperation of the device at these or any other conditions beyond thosespecified is not implied.(2) Input terminals are diode-clamped to the power-supply rails. Inputsignals that can swing more than 0.3V beyond the supply rails shouldbe current-limited to 10mA or less.PACKAGE/ORDERING INFORMATIONPRODUCT ORDERING NUMBER TEMPERATURERANGEPACKAGE LEADPACKAGEMARKINGPACKAGE OPTIONRS2253 RS2253XS16 -40°C ~+125°C SOIC-16(SOP16) RS2253 Tape and Reel,3000 RS2253XSS16 -40°C ~+125°C SSOP-16 RS2253 Tape and Reel,3000 RS2253XTSS16 -40°C ~+125°C TSSOP-16 RS2253 Tape and Reel,3000 RS2253XTQC16 -40°C ~+125°C QFN-3×3 -16L RS2253 Tape and Reel,3000ESD damage can range from subtle performancedegradation to complete device failure. Precisionintegrated circuits may be more susceptible todamage because very small parametric changescould cause the device not to meet its publishedspecifications.ESD SENSITIVITY CAUTIONELECTRICAL CHARACTERISTICSV CC = 5.0 V or 3.3V, FULL= –40°C to +125°C,Typical values are at TA = +25°C. (unless otherwise noted)(1) All unused digital inputs of the device must be held at V IO or GND to ensure proper device operation.ELECTRICAL CHARACTERISTICS (continued)V CC= 5.0 V or 3.3V, FULL= –40°C to +125°C Typical values are at TA = +25°C (unless otherwise noted)TYPICAL CHARACTERISTICSParameter Measurement InformationTest Circuit 1. Address Transition Times (t TRANS)Test Circuit 2. Switching Times (t ON, t OFF)Test Circuit 3. Break-Before-Make Time Delay (t D)Parameter Measurement Information (continued)Test Circuit 4. Charge Injection (Q)Test Circuit 5. Off Isolation, On LossTest Circuit 6. CapacitanceAPPLICATION NOTESThe RS2253 device is a triple 2-channel multiplexer having three separate digital control inputs, A, B, and C, and an inhibit input. Each control input selects one of a pair of channels which are connected in a single-pole, double-throw configuration.When the devices are used as demultiplexers, the CHANNEL IN/OUT terminals are the outputs and the COMMON OUT/IN terminals are the inputs.BINARY TO 1 OF 2Figure 1. The RS2253 Functional Block DiagramPACKAGE OUTLINE DIMENSIONSSOIC-16RECOMMENDED LAND PATTERN (Unit: mm)SSOP-16RECOMMENDED LAND PATTERN (Unit: mm)TSSOP-16RECOMMENDED LAND PATTERN (Unit: mm)QFN-3x3-16LSIDE VIEWTOP VIEW BOTTOM VIEW(Unit: mm)。

外文翻译---相控阵和雷达技术的突破

毕业设计(论文)外文文献翻译翻译(1)题目相控阵和雷达技术的突破翻译(2)题目发射KU-波段的相控阵天线在FSS通信系统中的应用学院电子信息学院专业英文译文1:相控阵和雷达技术的突破【摘要】许多人认为雷达是一个成熟的领域,不会发生任何新的变化,这种看法存在很久了,没有比这个看法更错误的了。

当我1950年参与到雷达领域的时候,我也有过同样的看法,例如,我认为麻省理工学院的雷达丛书已经是包罗万象了,不需要增加任何新的内容。

然而我是多么的错啊,从那时起雷达技术领域中已经发生了许多令人眼花缭乱的发展,雷达一直受益于Moore s定律和许多新的技术上的成果,例如,MMIC GaAs T/R组件和相控阵组件。

现在雷达技术发展得更快了,在这篇文章里,我将给出某些最近突破的例子。

【关键词】雷达;有源相控阵;MMIC;MEMS;T/R组件;相控阵;AESA;电扫;GaAs;GaN;SiC;CMOS;数字波束形成;自适应阵列;旁瓣对消器;超宽带天线;金属材料;电子管;真空电子器件;回旋管;磁控管;速调管;行波管;微波功率组件;MPM;功率放大组件;SBX;GBR—P0:SEA-BASED X-波段雷达24层楼高的SEA-BASED X-波段相控阵雷达是一个世界奇迹。

1:GaAs MMIC T/R模块(单片微波集成电路)在过去的十年成功和广泛的应用了MMIC和AESA(有源电子扫描阵)2:低成本¥19K AESA谁说AESA是非常昂贵的,在DARPA(Defense Advanced Research Projects Agency美国国防部先进研究项目局)的低资金¥19K资助下使35GHZ相控阵成为可能。

DARPA 已经资助发展了¥10 X-band,10’smW,单T/R芯片模块。

3:低成本的MEMS(微机电系统)相控阵即使我们只有一个低损耗的移相器,那么就能够用在一个模块上安装很多的移相而MEMS提供了这个可能。

数字化辅助的CBL在研究生正畸-正颌外科联合治疗教学中的应用

数字化辅助的CBL在研究生正畸-正颌外科联合治疗教学中的应用作者:胡芝爱邹淑娟祝颂松陈建伟来源:《中国美容医学》2024年第07期[摘要]目的:探討数字化辅助的案例教学法(Case-based learning,CBL)在研究生正畸-正颌外科联合治疗教学中的应用,以提供教学模式新思路。

方法:将30名口腔正畸专业一年级研究生随机分为两组,对照组采用PPT讲解知识点配合病例图片展示的传统教学模式,实验组在传统教学模式基础上增加三维数字化辅助的CBL教学,即在常规讲授教学前组织研究生学习三维数字化软件在正畸-正颌外科联合治疗典型病例中的应用。

采用随堂测验和问卷调查法对学生知识点掌握情况和教学满意度进行综合评价。

结果:随堂测验中,对照组得分为(9.87±1.71)分,实验组得分为(11.40±1.99)分,实验组对知识点的掌握情况显著优于对照组(P<0.05)。

两组学生在课前对此次课程的期待程度比较,差异无统计学意义(P>0.05),课程满意度综合评价中,实验组得分均显著高于对照组(P<0.05)。

结论:将三维数字化辅助的CBL教学模式应用于研究生正畸-正颌外科联合治疗教学,更能激发学生的学习兴趣,有助于学生在课堂上注意力的集中,使得教学内容更加容易理解,值得在正畸研究生教学中推广。

[关键词]数字化技术;案例教学法;正畸-正颌外科联合治疗;研究生教学;教学模式;教学质量[中图分类号]G642 [文献标志码]A [文章编号]1008-6455(2024)07-0156-04Application of Digitally Assisted CBL in the Teaching of Combined Orthodontic and Orthognathic Surgical Treatment for Postgraduate StudentsHU Zhiai1, ZOU Shujuan1, ZHU Songsong2, CHEN Jianwei1( 1.Department of Orthodontics, State Key Laboratory of Oral Diseases, National Clinical Research Center for Oral Diseases, West China Hospital of Stomatology, Chengdu 610041,Sichuan, China ; 2. Department of Orthognathic and Joint Surgery, West China Hospital of Stomatology, Sichuan University, Chengdu 610041, Sichuan, China )Abstract: Objective To explore the application of digitally assisted CBL in the teaching of combined orthodontics and orthognathic surgical treatment for postgraduate students, so as toprovide new ideas for the teaching model. Methods 30 first-year postgraduates majoring in orthodontics were randomly divided into two groups. In the control group, the traditional teaching mode of PPT with case pictures was used to explain the knowledge points. In the experimental group, digitally assisted CBL teaching was added to the traditional teaching mode, and the postgraduate students were organized to learn the application of 3D digital software in typical cases of combined orthodontic-orthognathic surgical treatment before the conventional lecture teaching. The students' knowledge and satisfaction of teaching were evaluated by means of a follow-up quiz and questionnaire. Results In the follow-up test, the score of the control group was (9.87±1.71)points, and the score of the experimental group was (11.40±1.99) points. The mastery of knowledge points in the experimental group was significantly better than that of the control group (P <0.05). There was no significant difference between the two groups in terms of students' expectations of this course before class (P>0.05). In the comprehensive evaluation of course satisfaction, the scores of the experimental group were significantly higher than those of the control group (P<0.05). Conclusion The application of digitally assisted CBL in the teaching of combined orthodontics and orthognathic surgical treatment for postgraduate students can better stimulate students' interest in learning, help them concentrate in class, and make the teaching content easier to be understood, which is worth promoting in orthodontic postgraduate teaching.Key words: digital technology; case-based learning; combined orthodontics and orthognathic surgical treatment; postgraduate teaching; teaching mode; teaching quality我国错牙合畸形发病率为67.82%,其中约5%为颌骨发育异常引起的牙颌面畸形[1]。

时间交织ADc

Bibliography[1] A.M.Abo,Design for reliability of low-voltage,switched-capacity circuits.Ph.D.Thesis,University of California,Berkeley,1999[2] A.M.Abo,P.R.Gray,A1.5-V,10-bit,14.3-MS/s CMOS pipeline analog-to-digital converter.IEEE J.Solid-State Circuits34(5),599–606(1999)[3] B.K.Ahuja,An improved frequency compensation technique for CMOS operational ampli-fiers.IEEE J.Solid-State Circuits18(6),629–633(1983)[4]V.J.Arkesteijn,Analog front-ends for software-defined radio receivers.Ph.D.dissertation,University of Twente,2007[5]V.J.Arkesteijn,E.A.M.Klumperink,B.Nauta,Jitter requirements of the sampling clock insoftware radio receivers.IEEE Trans.Circuits Syst.(TCAS)II53(2),90–94(2006)[6] C.W.Barbour,Simplified PCM analog to digital converter using capacity charge transfer,inProc.of the Telemetering Conf.(1971),pp.4.1–4.11[7] A.Barna,D.I.Porat,Integrated Circuits in Digital Electronics(Wiley,New York,1973),pp.353–354[8]W.C.Black,D.A.Hodges,Time interleaved converter arrays.IEEE J.Solid-State Circuits15(6),1022–1029(1980)[9]M.Boulemnakher,E.Andre,J.Roux,F.Paillardet,A1.2V4.5mW10b100MS/s pipelinedADC in65nm CMOS,in ISSCC Dig.Tech.Papers(2008),pp.250–251[10]T.B.Cho,P.R.Gray,A10b,20Msample/s,35mW pipeline A/D converter.IEEE J.Solid-State Circuits30(3),166–172(1995)[11]R.H.Dennard,F.H.Gaensslen,H.N.Yu,V.L.Rideovt,E.Bassous,A.R.LeBlanc,Design ofion-implanted MOSFET’s with very small physical dimensions.IEEE J.Solid-State Circuits 256–268(1974)[12]S.Devarajan,L.Singer,D.Kelly,S.Decker,A.Kamath,P.Wilkins,A16b125MS/s385mW78.7dB SNR CMOS pipeline ADC,in ISSCC Dig.Tech.Papers(2009),pp.86–87 [13] A.G.F.Dingwall,Monolithic expandable6bit20MHz CMOS/SOS A/D converter.IEEE J.Solid-State Circuits14(6),926–932(1979)[14]M.El-Chammas,B.Murmann,General analysis on the impact of phase-skew in time-interleaved ADCs,in IEEE International Symposium on Circuits and Systems(ISCAS) (2008),pp.17–20[15]S.L.J.Gierkink,Control linearity and jitter of relaxation oscillators.Ph.D.dissertation,Uni-versity of Twente,1999[16]S.K.Gupta,M.A.Inerfield,J.Wang,A1-GS/s11-bit ADC with55-dB SNDR,250-MAWpower realized by a high bandwidth scalable time-interleaved architecture.IEEE J.Solid-State Circuits41(12),2650–2657(2006)[17]K.Hadidi,A.Khoei,A highly linear cascode-driver CMOS source-follower buffer,in IEEEIntl.Conf.on Electronics,Circuits and Systems(1996),pp.1243–1246S.M.Louwsma et al.,Time-interleaved Analog-to-Digital Converters,131 Analog Circuits and Signal Processing,DOI10.1007/978-90-481-9716-3,©Springer Science+Business Media B.V.2011132Bibliography [18] C.-C.Hsu,F.-C.Huang,C.-Y.Shih,C.C.Huang,Y.-H.Lin,C.-C.Lee,B.Razavi,An11b800MS/s time-interleaved ADC with digital background calibration,in ISSCC Dig.Tech.Papers(2007),pp.464–465[19] E.Iroaga,B.Murmann,L.Nathawad,A background correction technique for timing errors intime-interleaved analog-to-digital converters,in IEEE International Symposium on Circuits and Systems(ISCAS),vol.6(2005),pp.5557–5560[20] E.A.M.Klumperink,B.Nauta,Systematic comparison of HF CMOS transconductors.IEEETrans.Circuits Syst.II,Analog Digit.Signal Process.50(20),728–741(2003)[21]N.Kurosawa,H.Kobayashi,K.Maruyama,H.Sugawara,K.Kobayashi,Explicit analysisof channel mismatch effects in time-interleaved ADC systems.IEEE Trans.Circuits Syst.I, Fundam.Theory Appl.48(3),261–271(2001)[22] F.Kuttner,A1.2V10b20MSample/s non-binary successive approximation ADC in0.13µmCMOS,in ISSCC Dig.Tech.Papers(2002),pp.176–177[23]Y.Z.Lin,S.J.Chang,Y.T.Liu,C.C.Liu,G.Y.Huang,A5b800MS/s2mW asynchronousbinary-search ADC in65nm CMOS,in ISSCC Dig.Tech.Papers(2009),pp.80–81 [24]S.M.Louwsma,E.J.M.van Tuijl,M.Vertregt,B.Nauta,A1.6GS/s,16times interleavedtrack&hold with7.6ENOB in0.12µm CMOS,in Proc.ESSCIRC(2004),pp.343–346 [25]S.M.Louwsma,E.J.M.van Tuijl,M.Vertregt,B.Nauta,A1.35GS/s,10b,175mW time-interleaved AD converter in0.13µm CMOS,in Proceedings of the Symposium on Very Large Scale Integration(VLSI)Circuits(2007),pp.62–63[26]S.M.Louwsma,E.J.M.van Tuijl,M.Vertregt,B.Nauta,A time-interleaved track&holdin0.13µm CMOS sub-sampling a4GHz signal with43dB SNDR,in Proceedings of the Custom Integrated Circuits Conference(CICC)(2007),pp.329–332[27]S.M.Louwsma,A.J.M.van Tuijl,M.Vertregt,B.Nauta,A1.35GS/s,10b,175mW time-interleaved AD converter in0.13µm CMOS.IEEE J.Solid-State Circuits43(4),778–786 (2008)[28]J.McCreary,P.Gray,All-MOS charge redistribution analog-to-digital conversion techniques.IEEE J.Solid-State Circuits10(6),371–379(1975)[29] E.Mensink,E.A.M.Klumperink,B.Nauta,Distortion cancellation by polyphase multipathcircuits.IEEE Trans.Circuits Syst.I,Regul.Pap.52(9),1785–1794(2005)[30]G.E.Moore,Cramming more components onto integrated circuits,in Electronics(1965),pp.114–2117[31] B.Murmann,A/D converter trends:power dissipation,scaling and digitally assisted architec-tures,in Proceedings of the Custom Integrated Circuits Conference(CICC),(2008),pp.751–758[32] B.Murmann,ADC Performance Survey1997–2009.Available online:http://www./~murmann/adcsurvey.html(2009)[33]K.Nagaraj, D.A.Martin,M.Wolfe,R.Chattopadhyay,S.Pavan,J.Cancio,T.R.Viswanathan,A dual-mode700-Msamples/s6-bit200-Msamples/s7-bit A/D converter in a0.25-µm digital CMOS process.IEEE J.Solid-State Circuits35(12),1760–1768(2000) [34]Y.Nakagome,H.Tanaka,K.Takeuchi,E.Kume,Y.Watanabe,T.Kaga,Y.Kawamoto,F.Murai,R.Izawa,D.Hisamoto,T.Kisu,T.Nishida,E.Takeda,K.Itoh,Experimental1.5-V 64-Mb DRAM.IEEE J.Solid-State Circuits26(4),465–472(1991)[35] B.Nauta,Analog CMOS low power design considerations,in Low Power Workshop on ES-SCIRC Conference(1996)[36] B.Nikoli´c,V.G.Oklobdžija,V.Stojanovi´c,W.Jia,J.K.S.Chiu,M.M.T.Leung,Improvedsense-amplifier-basedflip-flop:design and measurements.IEEE J.Solid-State Circuits35(6), 876–884(2000)[37]H.Pan,M.Segame,M.Choi,J.Cao,A.A.Abidi,A3.3-V12-b50-MS/s A/D converter in0.6-µm CMOS with over80-dB SFDR.IEEE J.Solid-State Circuits35,1769–1780(2000) [38]M.J.M.Pelgrom,A.C.J.Duinmaijer,A.P.G.Welbers,Matching properties of MOS transis-tors.IEEE J.Solid-State Circuits24(5),1433–1439(1989)Bibliography133 [39]K.Poulton,J.J.Corcoran,T.Hornak,A1-GHz6-bit ADC System.IEEE J.Solid-State Cir-cuits22(6),962–970(1987)[40]K.Poulton,R.Neff,B.Setterberg,B.Wuppermann,T.Kopley,R.Jewett,J.Pernillo,C.Tan,A.Montijo,A20GS/s8b ADC with a1MB memory in0.18µm CMOS,in ISSCC Dig.Tech.Papers(2003),pp.318–496[41] B.Razavi,Rf Microelectronics(Prentice Hall,New York,1998)[42] D.Schinkel,E.Mensink,E.A.M.Klumperink,A.J.M.van Tuijl,B.Nauta,A double-taillatch-type voltage sense amplifier with18ps setup+hold time,in ISSCC Dig.Tech.Papers (2007),pp.314–315[43] D.Schinkel,E.Mensink,E.A.M.Klumperink,A.J.M.van Tuijl,B.Nauta,A low-offsetdouble-tail latch-type voltage sense amplifier,in Proceedings of the18th ProRisc Workshop (2007)[44]H.Schmidt,Analog-Digital Conversion(Van Nostrand-Reinholt,New York,1970)[45] A.J.Scholten,G.D.J.Smit,B.A.D.Vries,L.F.Tiemeijer,J.A.Croon,D.B.M.Klaassen,R.van Langevelde,X.Li,W.Wu,G.Gildenblat,The new CMC standard compact MOS model PSP:advantages for RF applications,in IEEE Radio Frequency Integrated Circuits Symposium(2008),pp.247–250[46]T.Sepke,P.Holloway,C.G.Sodini,H.S.Lee,Noise analysis for comparator-based circuits.IEEE Trans.Circuits Syst.I,Regul Pap.56,541–553(2009)[47]R.C.Taft,P.A.Francese,M.R.Tursi,O.Hidri,A.MacKenzie,T.Hoehn,P.Schmitz,H.Werker,A.Glenny,A1.8V1.0GS/s10b self-calibrating unified-folding-interpolatingADC with9.1ENOB at Nyquist frequency,in ISSCC Dig.Tech.Papers(2009),pp.78–79 [48]H.P.Tuinhout,G.Hoogzaad,M.Vertregt,R.L.J.Roovers,C.Erdmann,Design and character-ization of a high precision resistor ladder test structure,in Proceedings of the IEEE Interna-tional Conference on Microelectronic Test Structures(ICMTS),vol.15(2002),pp.223–228 [49]R.C.H.van de Beek,High-speed low-jitter frequency multiplication in CMOS.Ph.D.disser-tation,University of Twente,2004[50]R.J.van de Plassche,Integrated Analog-to-Digital and Digital-to-Analog Converters(Kluwer Academic,Dordrecht,1994)[51]R.J.van de Plassche,R.E.J.van der Grift,A high-speed7bit A/D converter.IEEE J.Solid-State Circuits14(6),938–943(1979)[52]G.van der Plas,B.Verbruggen,A150MS/s133µW7b ADC in90nm digital CMOS using acomparator-based asynchronous binary-search sub-ADC,in ISSCC Dig.Tech.Papers(2008), pp.242–243[53]H.van der Ploeg,Calibration techniques in two-step a/d converters.Ph.D.dissertation,Uni-versity of Twente,2005[54]M.van Elzakker,A.J.M.van Tuijl,P.F.J.Geraedts,D.Schinkel,E.A.M.Klumperink,B.Nauta,A1.9µW4.4fJ/conversion-step10b1MS/s charge-redistribution ADC,in ISSCCDig.Tech.Papers(2008),pp.245–245[55] A.J.M.van Tuijl,personal communication[56] A.Verma,B.Razavi,A10b500MHz55mW CMOS ADC,in ISSCC Dig.Tech.Papers,(2009),pp.84–85[57]M.Vertregt,The analog challenge of nanometer CMOS,in International Electron DevicesMeeting(IEDM)(2006),pp.1–8[58]M.Vertregt,H.P.Tuinhout,personal communication[59]Video-transcript,Excerpts from a conversation with Gordon Moore:Moore’s law.ftp:///museum/Moores_Law/Video-Transcripts/Excepts_A_Conversation _with_Gordon_Moore.pdf(2005)[60]R.H.Walden,Analog-to-digital converter survey and analysis.IEEE J.Sel.Areas Commun.17(4),539–550(1999)[61] B.Wicht,T.Nirschl,D.Schmitt-Landsiedel,Yield and speed optimization of a latch-typevoltage sense amplifier.IEEE J.Solid-State Circuits39(7),1148–1158(2004)134Bibliography [62]Wikipedia,Orthogonal frequency-division multiplexing./wiki/Orthogonal_frequency-division_multiplexing(2009)[63]K.L.J.Wong,C.K.K.Yang,Offset compensation in comparators with minimum input-referred supply noise.IEEE J.Solid-State Circuits39(5),837–840(2004)[64]W.Yang,D.Kelly,L.Mehr,M.T.Sayuk,L.Singer,A3-V340-mW14-b75-Msample/sCMOS ADC with85-dB SFDR at Nyquist input.IEEE J.Solid-State Circuits36(12),1931–1936(2001)Index3D EM-field simulation,16AAD-Convertercounting,40flash,3,39,93folding,39pipeline,28,29,31,40,45,48,59,63–68, 93SA-ADC,40–57,91,94–108slope,40two-step,40amplifier,40,59,64,92,93,122interstage,108–111architectureTrack&Holdwith frontend sampler,17–20without frontend sampler,13–17Bbandwidthinput,16,19,30body effect,23bootstrapping,78–85bottom-plate sampling,6,28,29bufferbandwidth requirement,26distortion,23implementation,90input,14open-loop,22source follower,23,24,26,38,90,91Ccalibration,32–35,58,72,85,113,115,118 background,33bandwidth,12,22,35foreground,33gain,34,114offset,34,57,63,114,115timing,34,121,123 capacitancebuffer,input,25input,13,15–17interconnect,9capacitive load,26channel-charge injection,80,84,85 charge redistribution,27,83,110,111 clock feed-through,84,85clock generation,68,72,73,75,88,95 comparator,54–57,59,97,98Ddecoder,105digital control,40,41,94,99Eerrorgain,5offset,5timing,5Ffeedback,22Hhold-mode,5Jjitter,34–37,73,78,85,120,121,123S.M.Louwsma et al.,Time-interleaved Analog-to-Digital Converters,Analog Circuits and Signal Processing,DOI10.1007/978-90-481-9716-3,©Springer Science+Business Media B.V.2011135136IndexLladder connections,106layout,15,16,86,116look-ahead logic,53,99,101,103Mmatchingcapacitor,10Miller effect,25,109mismatchbandwidth,9–12between channels,6gain,6,7offset,6timing,6Nnoiseamplifier,64kT/C,16,58–61,64,85,111variance,59,64–66non-interleaved,5,6,22,26,30,39,68Ooffsetchannel,6comparator,57opamp,28,29,31,57,58,63,67,91,93,104, 108,109Pphase-differences,8Rreliability,79,82,83reset switch,15resistanceinterconnect,9switch,9,10,19,51,79Ssettling,14settling time,19,28,41–44,48,49single-sided overrange technique,46,47,49, 94,99,101spectrum,6spurious tones,6switchto avoid distortion,27switch-driver,85Ttechnology,10,14,16,19,22,32timing-misalignment,8,17Track and Holdbuffer,22–28track-mode,5track-timereduction,14,18track-time reduction,29 transconductance amplifier,59 transmission lines,13。

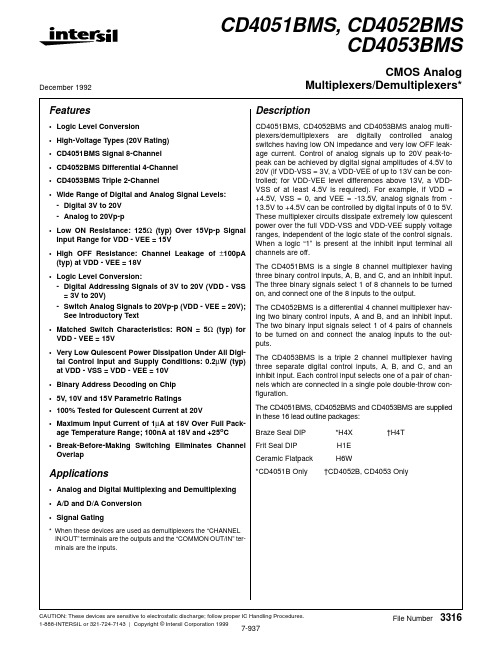

CD4052BMS中文资料

BINARY TO

1 OF 4 DECODER

WITH INHIBIT

TG

COMMON X

OUT/IN

TG

13

TG

3

COMMON Y

TG

OUT/IN

*

INH 6

8 VSS

LOGIC LEVEL CONVERSION

*

A 11

*

B 10

*

C9

*

INH 6

TG

7 VEE

TG 1524 0123 Y CHANNELS IN/OUT

H1E

H6W

†CD4052B, CD4053 Only

• Analog and Digital Multiplexing and Demultiplexing

• A/D and D/A Conversion

• Signal Gating

* When these devices are used as demultiplexers the “CHANNEL IN/OUT” terminals are the outputs and the “COMMON OUT/IN” terminals are the inputs.

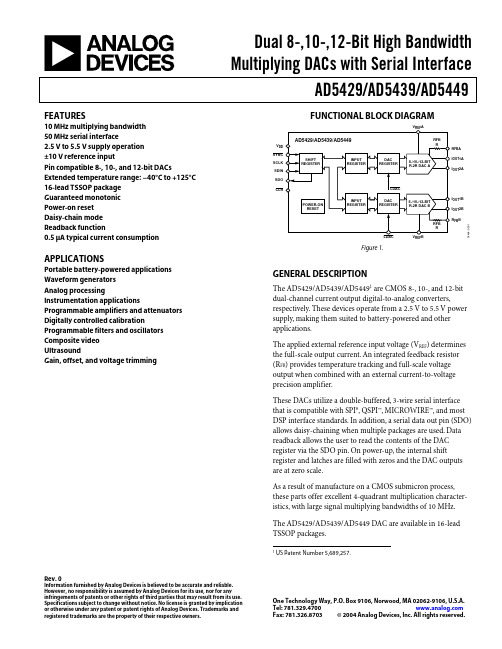

AD5449资料