以DE3FPGA平台实现HDMIFull_HD1080p分割画面的技术剖析

基于FPGA的超高清视频解码技术研究

基于FPGA的超高清视频解码技术研究随着科学技术的不断发展和社会的不断进步,人们对视频解码技术的要求越来越高。

基于FPGA的超高清视频解码技术,因其高效、稳定和实时性等特点,成为现在发展趋势。

本文主要探讨基于FPGA的超高清视频解码技术的研究进展、发展现状、应用前景等。

一、近几年基于FPGA的视频解码技术研究进展1.1 VHDL在超高清视频解码中的应用VHDL (VHSIC Hardware Description Language) 是一种硬件描述语言,可用于描述数字电路的行为和结构。

现在,FPGA中运用了许多种数字电路以支持超高清视频解码。

大部分数字电路被设计成基于VHDL的暂态状态图,并且进行了验证、仿真,最终被烧录到FPGA中。

1.2 视频编解码器与片上处理器视频编解码器 (Codec) 和片上处理器 (SoC) 是基于FPGA的视频解码技术中的基本组件。

编解码器负责将原始视频信号转换为可传输的格式,并负责解码接收到的视频信号。

SoC则用于将 Codec 和其它组件(如内存和网络接口)整合到FPGA板上。

1.3 基于FPGA的视频解码控制系统基于FPGA的视频解码控制系统应该实现以下功能:视频解码、捕获和显示;编/解码器的配置;编/解码器的数据流量;FPGA的中断控制(IRQ)以及系统总线控制等。

可以说,实现以上功能,是基于FPGA的视频解码技术的关键。

二、基于FPGA的超高清视频解码技术的发展现状近年来,FPGA 的集成度不断提高,计算能力不断增强,以及新兴技术不停突破,叠加在一起,为基于FPGA的超高清视频解码技术的发展提供了有力保障。

2.1 4K技术在FPGA中的应用4K技术指的是电视屏幕最小分辨率为3840×2160像素,这样的分辨率大大增加了图像的清晰度。

FPGA在4K技术的发展中起到了非常重要的作用。

一些公司对FPGA中4K技术的应用进行了深入的研究,结合ASIC等芯片和软件算法,大大提高了FPGA的性能和效率。

以DE3 FPGA平台实现HDMI Full-HD 1080p分割画面的技术剖析

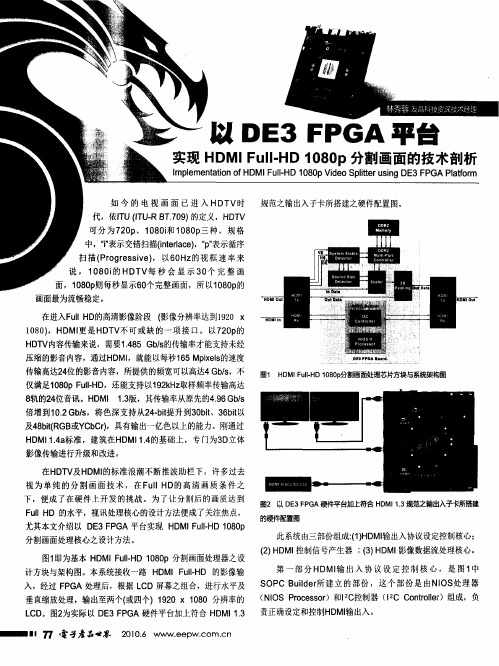

图2 以 D 3 P A硬件平台 E G F 加上符合 H M .规范之输出入子卡所搭建 DI3 1

的硬件配置图

l 的水平,视讯处理核心的设计方法便成了关注焦点。 D : 文介绍以 D 3F G E P A平台实现 H M u・ D 1 8 p D I lH 0 0 Fl 面处理核心之设计方法。 j即为基本 H MI u.D 1 8 p分割画面处理器之设 1 D l 00 F 1 H 与架构图。本系统接收一路 H MIF l D 的影像输 D u. 1 H

i G 或Y b r t B C C) ( R ,具有输出一亿色以上的能力。刚通过

14 标 准 ,建 筑在H MI.的基 础上 ,专 门为3 立 体 . a D 4 1 D

输进行升级和改进。 :D V H T 及H MI D 的标准浪潮不断推波助栏下,许多过去 纯 的分割 画面技术 ,在 F lH 的高清画质条件之 ul D

置。源分辨率计数器负责根据前端影像源和后端显示的分辨 率,设定适当的缩放参数,边框大小和显示位置。 D R D 2多端 口控 制 器 负责垂 直分 割 的 内存器 存 取控 制,D R D 2内存器要规划成 Pn —o gB f r i P n u e 的结构 ( 3 g 图 所示为垂直方向一分为二的例子) ,利用两个相 同的帧储存 器,一帧用来写,另一帧用来读,可避免画面闪烁 (c ) l f k 和不 i 连续 ( ai ) t rg 的副作用。若垂直方向是一分为二,D R e n D 2多 端 口控制器,必须规划成一写二读,在写入的时候也要规划

i 4 达2 位的影音内容,所提供的频宽可以高达4 bs 图1 HD I u1 D 1 8 p /,不 G M l 0 0 分割画面处理芯片方块与系统架构图 F . H

基于FPGA的高清视频信号输出扩展卡的设计与实现的开题报告

基于FPGA的高清视频信号输出扩展卡的设计与实现的开题报告一、选题背景与意义随着高清视频技术的不断进步,高清视频已经逐渐普及到人们的生活中,成为人们娱乐和工作中不可或缺的一部分。

同时,随着FPGA技术的不断成熟,FPGA已经广泛应用于高速数据传输、数码信号处理、嵌入式系统等领域,成为具有较高性能和灵活性的硬件设计平台。

本课题旨在研究基于FPGA的高清视频信号输出扩展卡的设计与实现,提供一种高清视频信号输出解决方案,满足高清视频处理的需求,同时也为FPGA技术在高清视频领域的应用提供了一个实践平台。

二、研究目标本课题的主要研究目标如下:1.设计一款基于FPGA的高清视频信号输出扩展卡,能够实现高清视频信号的输出,并具备信号调节、时序处理等功能;2.实现基本的高清视频信号处理算法,包括缩放、裁剪、色彩空间转换、图像滤波等;3.实现基于FPGA的高速数据传输模块,通过高速数据传输模块将处理后的视频信号输出至扩展卡接口,实现高清视频信号的稳定输出。

三、研究内容本课题的主要研究内容如下:1. FPGA技术与高清视频信号处理的理论基础研究,包括高清视频信号的特点、高清视频信号处理技术、FPGA技术的基本原理等;2. 设计高清视频信号输出扩展卡的硬件系统,包括高清视频信号输入模块、显示控制模块、高速数据传输模块等;3.实现高清视频信号处理算法模块,包括图像缩放、裁剪、色彩空间转换、图像滤波等,提高视频信号输出的质量和效率;4.测试和验证实现的高清视频信号输出扩展卡的性能,包括输出信号质量、输出速度、功耗等。

四、研究方法本课题主要采用以下研究方法:1.文献综述法,对相关领域的理论和技术进行梳理和分析,为后续的研究提供基础和指导;2.硬件设计方法,采用模块化设计思想,将高清视频信号处理的各个模块进行分离和设计,最终实现高清视频信号输出扩展卡;3.软件设计方法,利用硬件描述语言(VHDL或Verilog)对设计的各个模块进行编程实现,完成高清视频信号处理算法模块等;4.测试和验证方法,通过实际测试和验证,分析和评估实现的高清视频信号输出扩展卡的性能和效果。

基于FPGA的VGA和HDMI视频拼接系统设计毕业设计论文

基于FPGA的VGA和HDMI视频拼接系统设计摘要随着图像显示技术的快速发展,图像用户界面和人机交互界面正朝着智能化、高速化、大屏幕化方向迈进。

目前图像显示系统多数是采用早期的专用处理芯片,其运算速度和设计灵活性一般都较低。

FPGA 的发展为图像存储与显示系统的高速和高集成度提供了新的方法和解决思路,FPGA 本身拥有着强大的逻辑资源,并利用片外的配置资源和模块化的设计思路,可实现图像存储与显示系统。

论文采用 Altera 公司推出的Cyclone IV FPGA,结合该系列芯片的结构特点,对其功能以及配置方式做了详细的说明,并简要的介绍了系统设计中所涉及的软硬件开发环境和显示原理,重点研究基于 FPGA 的图像信号剪切、存储和显示,系统采用基于FPGA的高速阵列的信号处理模式,提出了一种基于硬件的图像存储与显示的视频拼接显示方法。

该设计以 FPGA 为数字处理的核心,分为图像处理模块、图像存储模块和图像显示模块,通过处理输入的视频信号,把视频剪切成两部分,分别以VGA和HDMI在两个显示器里分别显示,实现了视频的拼接显示功能。

关键字:FPGA VGA HDMI 拼接显示VGA and HDMI video splicing FPGA-based displayABSTRACTAs the image shows the rapid development of technology, graphical user interface and interactive interface is moving intelligent, high-speed, large screen direction. At present, the majority of the image display system is the use of dedicated processing chip early, usually its speed of operation and design flexibility are low.FPGA development for high-speed and highly integrated image storage and display system provides a new approach and solution ideas, FPGA itself has a powerful logic resources and use off-chip resource allocation and modular design ideas can be realized Images storage and display system.Thesis, Altera has introduced Cyclone IV FPGA, combined with the structural characteristics of the chips and their functions as well as a detailed configuration instructions, and a brief description of the system involved in the design of hardware and software development environment and display principle focus Cut image signal based on FPGA, storage and display, the system uses the signal processing FPGA-based high-speed mode arrays, we propose a hardware-based image storage and display method for displaying video splicing.The digital processing designed to FPGA core, divided into an image processing module, an image storage module and an image display module, by processing the input video signal, the video cut into two parts, respectively in the two VGA monitors and HDMI Lane respectively display, to achieve a video mosaic display function.Key words: FPGA VGA HDMI Tiled Display目录1 绪论 ........................................................... 错误!未定义书签。

基于FPGA的视频图像画面分割器的设计

基于FPGA的视频图像画面分割器的设计采用软件来实现视频的画面分割处理,往往消耗大量的CPU资源.本文介绍了一种采用FPGA的画面分割实现技术.方案采取比较先进的图象算法,分割处理清晰,画面干净,图象失真小,可供参考第六图书馆在基于FPGA的视频图像画面分割器设计中,首先将多路模拟视频信号经过视频解码芯片SAA7113转换成CCIR656个格式数字信号;然后按照分割画面分割的要求由FPGA对有效信号进行抽取并存储到SRAM中,再将抽取的信号进行帧合成;最后经过SAA7121视频编码芯片把处理过的信号转换成模拟信号输出到显示器,实现在一个屏幕显示多路视频画面的目的。

在基于FPGA的视频图像画面分割器设计中,首先将多路模拟视频信号经过视频解码芯片SAA7113转换成CCIR656个格式数字信号;然后按照分割画面分割的要求由FPGA对有效信号进行抽取并存储到SRAM中,再将抽取的信号进行帧合成;最后经过SAA7121视频编码芯片把处理过的信号转换成模拟信号输出到显示器,实现在一个屏幕显示多路视频画面的目的。

FPGACCIR656帧合成画面分割现代电子技术齐本胜付富壮杨书生河海大学计算机及信息工程学院,江苏常州2130022007第六图书馆第六图书馆采用软件来实现视频的画面分割处理,往往消耗大量的CPU资源.本文介绍了一种采用FPGA的画面分割实现技术.方案采取比较先进的图象算法,分割处理清晰,画面干净,图象失真小,可供参考采用软件来实现视频的画面分割处理,往往消耗大量的CPU资源.本文介绍了一种采用FPGA的画面分割实现技术.方案采取比较先进的图象算法,分割处理清晰,画面干净,图象失真小,可供参考采用软件来实现视频的画面分割处理,往往消耗大量的CPU资源.本文介绍了一种采用FPGA的画面分割实现技术.方案采取比较先进的图象算法,分割处理清晰,画面干净,图象失真小,可供参考。

基于FPGA的立体视频画面分割模块的设计与实现

l 【 要】 摘 在偏光式立体投影机领域, 复合立体视频的分解主要通过计算机显卡的双屏输出功能来 》实现 , 系统的视频接收模块和外部连接结构复杂, 视频播放依赖于特定硬件需求的计算机。为解决这一

;问题 , 出了一种应用于偏光式 3 提 D投影 系统的视频画面分割模块的设计和实现方法。 视频画面分割模 ;块基于 F G P A技术, 采用 S R M作为图像帧缓存 , DA 对立体视频 中左右画面进行 实时分割和同步传输 , }能够替代计算机显卡的双屏输出功能。模块易于集成在投影 系统中, 可简化 系统的视频接收模块和外 ;部连接结构, 实现独立立体视频播放 功能。 l 关键词 : 立体视频 ; 画面分割 ;P A; D A FG S R M i 【 btat / e edo oai dtre dm ninl r etrcm l re dm ni a v es A s c】 nt l r hf i fp l z e- ies a Po co,o pe t e - i s nl i o re h o j xh e o d

算 i

■ ・ 卜一 i —

陈鼎如 苏 萍 马建设 ( 清华大 学 深圳研 究生院 , 深圳 5 8 5 ) 10 5 De in a d L l me t t fF sg n mp e n a i o PGA- a e D Vi e c u e Se on b s d 3 d o Pit r gme t t n Mo l n a i due o

;hpjt st , d reemdent rf ot eea 。 ei t c p t rei ye t i。e r 。 za etc, fh r nc 凡r 。 l e oc 凡 s, h e c “ dhs u t l nt 2 m e ‘。 ne “ ℃ e nc 。 e ,

利用FPGA实现的一种机载高清视频处理模块

利用FPGA实现的一种机载高清视频处理模块现代飞机座舱显示技术的进展日新月异,需要显示各种信息的数据已经达到海量规模。

飞翔员在不同飞翔时段获得的信息也越来越多,为了使飞翔员能够在某特定的飞翔时段认读和处理更为精确的信息,并且各种传感器信息融合在同一个坐标系中,因此需要讨论机载环境中高清视频处理技术,讨论在较大尺寸的上显示处理高清视频信号。

高清视频处理模块位于显示分系统中,加速显示高清视频信号,实现高清视频的缩放和叠加。

满足了飞翔员对大尺寸和高清楚视频显示的需求。

模块接收显示指令和视频数据,将融合信息加速显示到显示器上,同时接收解码两路高清外视频信号,在芯片中实现内视频和外视频的运算处理,包括缩放和叠加,并且将处理后的视频信息根据不同的要求输出到显示器上。

高清视频处理模块系统结构高清视频处理模块内部包含图形处理器,它接收显示指令和数据,加速渲染图形画面,输出为高清视频信号,在FPGA中运算融合外视频信号,两路分离输出到外部显示器上,视频格式分离为高清LVDS和高清DVI。

高清视频处理模块主要功能包括图形处理器电路、视频叠加和缩放规律电路、编解码电路和供电复位时钟电路。

模块系统组成框图1所示。

高清视频处理模块硬件电路设计图形处理器电路图形处理器电路主要负责内部高清视频的生成和视频输出控制。

它将绘图数据和指令通过二维和三维图形加速管线加速生成并且存储在显存中,输出控制部件将显存中的数据根据相应格式输出视频信号。

图形处理器选用AMD公司的M9000芯片,该芯片支持高清视频处理,支持二维和三维图形硬件加速,OpenGL图形接口标准,工作频率高达250MHz,64MByte的显存容量,两路自立的显示输出通道,可挑选LVDS、第1页共5页。

基于FPGA的双摄像头HDMI视频系统的设计与研究

基于FPGA的双摄像头HDMI视频系统的设计与研究基于FPGA的双摄像头HDMI视频系统的设计与研究摘要:随着科技的发展,图像与视频处理技术在各个领域应用得越来越广泛。

本文基于FPGA设计了一个双摄像头HDMI视频系统,通过对两路摄像头的捕获、处理和输出,实现了高清视频的实时传输。

本文首先介绍了HDMI和FPGA的基本概念和原理,然后详细阐述了双摄像头系统的硬件设计和软件编程过程,最后通过实验验证了系统的性能和可靠性。

1. 引言随着高清视频技术的发展,越来越多的应用领域需要实时传输高清视频信号。

传统的视频传输方式存在着带宽限制、传输延迟等问题,而FPGA作为一种高度可编程的硬件平台,具备了处理高速数据流的能力,逐渐成为实时高清视频处理的重要组成部分。

本文将基于FPGA设计一个双摄像头HDMI视频系统,以满足高清视频实时传输的需求。

2. HDMI和FPGA基础知识2.1 HDMIHDMI(High-Definition Multimedia Interface)是一种数字化高清多媒体接口,用于在各种设备之间传输高质量的音频和视频信号。

HDMI接口具有高速传输、高清晰度和高质量音频等特点,广泛应用于电视、电脑、摄像机等设备中。

2.2 FPGAFPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有灵活性高、性能强的特点。

FPGA可以通过编程实现各种数字逻辑电路,因此被广泛应用于数码通信、图像处理、高性能计算等领域。

3. 双摄像头HDMI视频系统的设计与实现3.1 硬件设计本系统采用两个摄像头进行视频采集,通过HDMI接口将视频信号传输到FPGA进行处理。

在硬件设计上,需要设计视频采集模块、视频处理模块和视频输出模块。

3.2 软件编程在软件编程上,首先需要进行图像采集配置和控制,实时捕获两个摄像头的视频信号。

然后,进行图像处理算法的开发和实现,如图像滤波、边缘检测等。

基于FPGA的HDMI视频显示系统设计

信息,将高清图像数据存入 FPGA 的 DDR3,再经过一系列图像、算法处理,最后用 HDMI 显示器进行显示。与传统的监控设

备相比,采用 FPGA 架构进行设计的一个优点是可以将整个系统的处理延迟降到最低,通过调整 DDR3 存储中的缓存数据,

可以将延迟缩短为 1 帧。另一个优点是借助于 FPGA 丰富的引脚和强大的并行处理能力,可以同时采集并处理多路视频信

Aug. 2021 Vol. 44 No. 16

35

基于 FPGA 的 HDMI 视频显示系统设计

张振利,韩凌锋

(江西理工大学 电气工程与自动化学院,江西 赣州 341000)

摘 要:针对国内外的研究方向以及市场对于高清图像采集与显示的需求,文中分析了国内外高清视频采集与显示技

术的现状和最新成果,主要研究一种基于 FPGA(现场可编程门阵列)为核心视频显示系统。采用图像传感器实时采集图像

息,在降低成本的同时也提高了数据的处理速度。通过实验验证,该文系统可以对 60 f/s 1 920×1 080 视频图像进行有效快

速的处理,从而验证了该文系统的有效性和优越性。

关键词:视频显示;HDMI;FPGA;图像信息采集;图像处理;仿真测试

中图分类号:TN986⁃34;TP273

文献标识码:A

文章编号:1004⁃373X(2021)16⁃0035⁃05

Design of HDMI video display system based on FPGA

ZHANG Zhenli,HAN Lingfeng

(Electrical Engineering and Automation Institute,Jiangxi University of Science and Technology,Ganzhou 341000,China)

102英寸的1080p画面

102英寸的1080p画面

王祎

【期刊名称】《微型计算机》

【年(卷),期】2006(000)002

【摘要】有人说36英寸是CRT电视机的极限。

的确,我们很难再见到更大的CRT电视机,有专家说65英寸是平板电视机的极限,是的,在商场里面我们也很难再要到更大的平板电视机。

你现在可以不管什么极限和专家了,三星Z102将颠覆所有的定论。

【总页数】2页(P144-145)

【作者】王祎

【作者单位】无

【正文语种】中文

【中图分类】TN949.12

【相关文献】

1.以DE3 FPGA平台实现HDMI Full-HD 1080p分割画面的技术剖析 [J], 林秀蓉

2.电视画面构图和拍摄运动画面应注意的几个问题 [J], 高鲁

3.音乐是纪录片流动的画面

——音乐与纪录片画面的信息性 [J], 周红

4.对游戏直播画面之著作权问题的类型化研究

——以游戏直播画面之作品属性与主播地位为视角 [J], 曹舒然

5.“多媒体画面语言”系列讲座(二) 画面语义学——画面语言是如何表现教学内容的 [J], 游泽清

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的视频图像画面分割器设计

基于FPGA的视频图像画面分割器设计曹旭东;王程锦;孙云龙【摘要】为了解决在一个屏幕上收看多个信号源的问题,对基于FPGA技术的视频图像画面分割器进行了研究.研究的主要特色在于构建了以FPGA为核心器件的视频画面分割的硬件平台,首先,将DVI视频信号,经视频解码芯片转换为数字视频图像信号后送入异步FIFO缓冲.然后,根据画面分割需要进行视频图像数据抽取,并将抽取的视频图像数据按照一定的规则存储到图像存储器.最后,按照数字视频图像的数据格式,将四路视频图像合成一路编码输出,实现了四路视频图像分割的功能,提高了系统集成度,并可根据系统需要修改设计和进一步扩展功能,增加了系统的灵活性,适用于多种不同领域.【期刊名称】《电子设计工程》【年(卷),期】2014(022)001【总页数】4页(P44-46,50)【关键词】FPGA;DDR2 SDRAM;视频提取;图像合成【作者】曹旭东;王程锦;孙云龙【作者单位】中国石油大学(北京) 北京102200;中国石油大学(北京) 北京102200;中国石油大学(北京) 北京102200【正文语种】中文【中图分类】TN98随着计算机、DSP、超大规模集成电路等技术的发展,画面分割器开始采用硬件设计。

首先,将各路视频信号转换成数字视频信号;然后,在数字领域对各路视频信号进行处理。

使电路的设计、调试得到了很大的改善。

但是,设计中所使用的独立的逻辑电路较多,有的甚至使用专用的DSP芯片去处理视频画面的分割。

虽然可以满足对视频图像数据处理速度的要求,但是还需要外加CPU去协调系统工作,使得整个系统仍显得体积较大,而且系统成本较高。

随着半导体加工工艺的不断发展,FPGA在结构、速度、工艺、集成度和性能方面都取得了很大的进步和提高。

本文将详细介绍基于FPGA开发技术的视频图像画面分割器的软硬件设计与实现。

1 系统总体设计本系统选用Altera公司的Cyclone III系列中的EP3C40F780C7型号FPGA作为核心处理芯片,提出和设计了一个多路视频图像数据的采集、处理、显示,实现视频图像画面分割器。

用FPGA实现高清视频去隔行功能

逐行帧的带宽加倍, HD 视频的带宽会更大。计算带宽时,需要计算去隔行器要访问的帧数,然后加上总 带宽。将其与需要的 DDR 存储器接口带宽相比较,它取决于吞吐量以及存储器接口位宽。

表 1 列出了采用 Altera® Cyclone® III 和 Stratix® III FPGA 实现 PAL 视频源运动自适应去隔行算法需要的资 源。该表对比了运动自适应方法需要的资源以及简单场合并方法所需要的资源。请注意,场合并技术即使 用在分辨率较高的图像上,需要的存储器也很少。

表 1. 在 FPGA 架构上实现去隔行功能需要的硬件资源

5

使用 FPGA 实现高清晰视频去隔行功能

图 7. 3:2 场格式转换从两帧视频中产生 5 场,从 24 帧视频中产生 60 场

Altera 公司

有时候会提取出第十二场,以加速影片,将其插到某一时间片中。虽然普通观众很难注意到这一点,但它 导致了 3:2:3:2:2 的场格式转换节奏:

帧 1: 3 场 帧 2: 2 场 帧 3: 3 场 帧 4: 2 场 帧 5: 2 场 重复

白皮书

使用 FPGA 实现高清晰视频去隔行功能

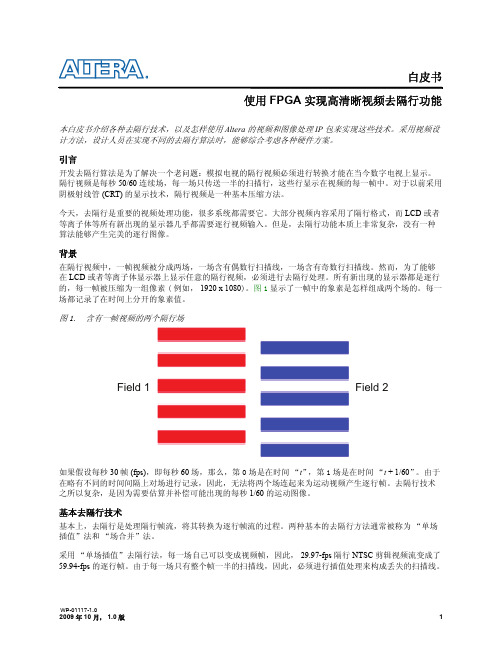

本白皮书介绍各种去隔行技术,以及怎样使用 Altera 的视频和图像处理 IP 包来实现这些技术。采用视频设 计方法,设计人员在实现不同的去隔行算法时,能够综合考虑各种硬件方案。

引言

开发去隔行算法是为了解决一个老问题:模拟电视的隔行视频必须进行转换才能在当今数字电视上显示。 隔行视频是每秒 50/60 连续场,每一场只传送一半的扫描行,这些行显示在视频的每一帧中。对于以前采用 阴极射线管 (CRT) 的显示技术,隔行视频是一种基本压缩方法。

基于FPGA的DVI HDMI接口设计

在过去几年中,具有高清晰度视频显示器的一些产品大幅度增加。

高清晰度视频显示器被集成在这些产品的内部,或者放在产品的外面。

原始设备制造商正在期望能够利用标准的平板显示器及接口技术来降低产品的成本,并提供长期的解决方案。

设计界面对着这种挑战,并继续实施低成本平板显示器驱动器,在接口的后端中提供专用化和增值的功能。

在消费市场上,平板显示技术的增长有助于统一接口选择和降低成本。

尽管首个高清晰度显示器使用了模拟分量视频接口(YCrCb),数字技术,诸如数字视频接口(DVI)和高清晰度多媒体接口(HDMI)已经取代了大多数模拟接口。

庭影院市场爆炸式的增长需要更新DVI标准。

然而,需要一个庞大连接器的DVI接口限制了对数字版权管理(DRM)的支持,且缺少对单声道或多声道音频的支持。

为满足演变的HDMI标准要求,它使用相同的如DVI这样的基本信号传输,支持较小的连接器,以及更大带宽(1080p分辨率)、DRM和8个通道的多格式音频。

基于在平板领域中占主导地位的DVI和HDMI协议,原始设备制造商正在越来越多地追求他们自己的集成一种或两种技术的产品开发。

DVI 和HDMI标准HDMI规范可以传输和接收未压缩的数字流的音频/视频标准。

它可以将视频和多声道音频组合至单一的数字连接,节省了多条线路连接及相关成本。

对于没有音频要求的1080i分辨率显示,HDMI信号传输与DVI是向下兼容的。

DVI和HDMI是基于称为最小化传输差分信号(T M D S)的信号传输技术。

T M D S也有类似CML的物理信号传输电平(电流模式逻辑)。

图1给出了简化的HDMI链路框图。

图1:简化的HDMI链路框图。

HDMI接口是一种带有三个T M D S通道的屏蔽电缆。

默认配置是RGB ,每个通道传送一种颜色。

与DVI不同,HDMI支持亮度及色度的分量(YCbCr 4:4:4和4:2:2),并通过3个T M D S链路,支持多达8个音频通道。

一种基于FPGA的多路图像拼接的4K高清显示设计

一种基于FPGA的多路图像拼接的4K高清显示设计邹江;江国海;曾丽娟【摘要】目前各大电视、显示器厂商的4k高清技术处理方案主要是采用基于台湾晨星等4k处理芯片设计的,而采用该方案若需要增加新的图像数据处理功能或者改变某一项功能却显得尤为困难.本文采用基于FPGA的多路图像拼接的4K高清显示设计方案,即利用FPGA将4路分辨率为1920*1080的图像信号拼接为一幅分辨率为3840*2160的4K图像信号,并通过DisplayPort接口发送到高清4K显示器进行显示.本文详细介绍了DVI数据处理硬件电路、DisplayPort接口硬件电路设计过程,并介绍了FPGA的DDR3设计及DisplayPort接口程序设计流程,最后通过试验验证设计的正确性.【期刊名称】《电子制作》【年(卷),期】2017(000)012【总页数】4页(P18-21)【关键词】4k高清;DVI;DisplayPort;DDR3【作者】邹江;江国海;曾丽娟【作者单位】遵义师范学院;遵义师范学院;遵义师范学院【正文语种】中文近年来,随着4K高清电视、显示器的普及,使得4k的高清技术得到越来越广泛的应用,目前各大电视、显示器厂商的4k高清技术处理芯片主要基于台湾晨星等4k处理芯片设计的,但增加功能或者更改设计比较困难,无法做到自主可控设计的目的。

目前基于FPGA的处理图像的速度与能力得到了较大的提高,已经可以满足4k高清显示对图像数据处理的高速要求,采用FPGA作为4K图像处理的主控芯片方案已经得到了充分的验证,本文主要是针对特殊图像拼接领域里面利用FPGA进行多路图像拼接设计的。

本系统要求将4路分辨率为1920*1080的DVI视频图像拼接成1路3840*2160分辨率的4k高清图像并发送至4K高清显示器进行显示。

具体设计思路为将PC主机提供的4路DVI图像信号连接到本系统的DVI输入接口,4路图像信号经过DVI信号调理芯片DS16EV5110A进行信号调理,经调理的DVI信号利用DVI 时序转换器TFP410A进行转换为标准的DVI时序信号,标准的DVI时序包括RGB数据、行同步HSYNC、场同步VSYNC和DE信号;FPGA采集4路DVI图像信号存入DDR3芯片,待4路DVI图像信号全部存入DDR3芯片MT41J256M16HA之后,再将4路DVI图像数据从DDR3芯片同时读出,最终通过displayport接口发送到4k高清显示器进行显示,SN65DP130S为displayport信号调理芯片,对displayport信号的增加和减弱具有重要的调节作用,系统总体框图如图1所示。

hdmi分配原理

hdmi分配原理

HDMI分配是一种视频和音频信号的传输技术,它基于高清多媒体接口(HDMI)标准,用于将一个源信号分配到多个显示设备上。

这种技术常用于家庭影院系统、会议室和数字广告牌等场合,可以实现多个屏幕同时显示相同的内容。

HDMI分配的原理是通过HDMI分配器或分配矩阵来实现的。

HDMI分配器通常具有一个HDMI输入端口和多个HDMI输出端口,可以将一个源设备(如蓝光播放器、电视盒子或游戏机)连接到多个显示设备(如电视、投影仪或显示器)上。

当源设备的信号通过HDMI分配器的输入端口进入时,它会被复制并传输到每个输出端口上。

每个输出端口上的信号可以连接到一个显示设备,因此可以实现将同一个视频和音频信号同时显示在多个屏幕上。

HDMI分配矩阵是一种更为复杂的设备,它可以支持多个源设备和多个显示设备之间的分配。

分配矩阵通常具有多个输入端口和多个输出端口,可以自由选择将哪些源设备的信号传输到哪些显示设备上。

使用HDMI分配器或分配矩阵可以为用户带来很多便利。

比如在家庭影院系统中,用户可以通过一个蓝光播放器将高清电影同时传输到多个电视上,让家庭成员在不同的房间里同时欣赏电影。

在会议室中,用户可以将演示文稿实时显示在多个投影仪或显示器上,方便与会人员观看。

在数字广告牌中,用户可以通过HDMI分配器将相同的广告内容同时显示在多个屏

幕上,增加宣传效果。

总而言之,HDMI分配通过使用分配器或分配矩阵将一个源信

号传输到多个显示设备上,实现多个屏幕同时显示相同的内容,为用户带来更好的观看和使用体验。