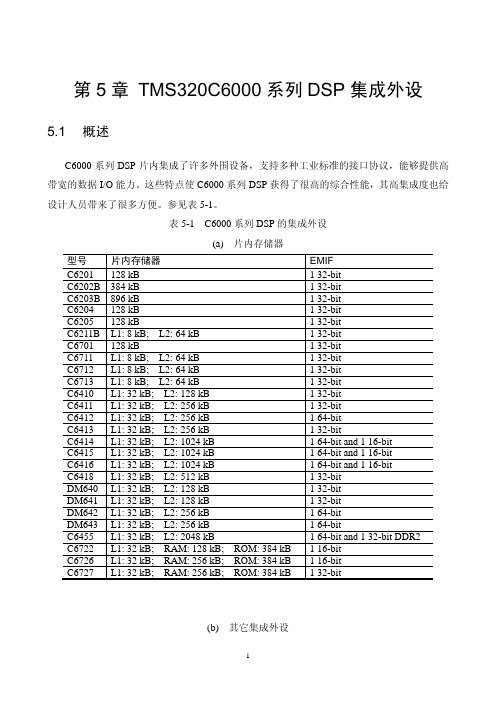

第五章C6000系列DSPs的集成外设1

DSP大作业 C500C6000的比较

TMS320C54x是TI公司为实现低功耗、高速实时信号处理而专门设计的16位定点数字信号处理器,采用改进的哈佛结构,具有高度的操作灵活性和运行速度,适应于远程通信等实时嵌入式应用的需要,现已广泛地应用于无线电通信系统中。

C54x硬件结构基本上可分为3大块:(1)CPU 包括算术逻辑运算单元(ALU)、乘法器、累加器、移位寄存器、各种专用寄存器、地址生成器及内部总线。

(2)存储器系统ROM、SARAM、DARAM、外接存储器接口。

(3)片内外设与专用硬件电路包括片内的定时器、各种类型的串口、主机接口、片内锁相环(PLL)时钟发生器及控制电路。

C54X硬件结构如下图:TMS320C54x主要特性1.CPU部分(1)先进的多总线结构(1条程序总线、3条数据总线和4条地址总线)。

(2)40位的ALU,包括1个40位的桶形移位寄存器和2个独立的40位累加器。

(3)17×17位并行乘法器。

(4)比较、选择、存储单元(CSSU),用于加法/比较选择。

(5)指数编码器(6)双地址生成器,8个辅助寄存器和2个ARAU(辅助寄存器运算单元)。

2.存储器系统(1)具有192K字可寻址存储空间:64K字程序存储器空间、64K字数据存储空间及64K字I/O空间。

(2)片内双寻址RAM(DARAM)。

CPU可以在一个机器周期内对同一DARAM块读出1次和写入1次。

(3)片内单寻址RAM(SARAM)3.片内外设(1)软件可编程等待状态发生器(2)可编程分区转换逻辑电路(3)片内锁相环(PLL)时钟发生器(4)串口C54x系列DSP串口分4种:标准同步串口(SP)、带缓冲的串行口(BSP)、时分复用(TDM)串行口和多通道带缓冲串行口(McBSP)。

(5)8位或16位主机接口(HPI)(6)外部总线关断控制,以断开外部的数据总线、地址总线和控制信号。

(7)数据总线具有总线保持特性(8)可编程的定时器4.指令系统(1)单指令重复和块指令重复操作。

TMS320C6000系列DSPs简介

C6000系列DSPs的CPU结构

• C62xx和C67xx系列的CPU结构相同,包括以下 几个部分

– 程序取指单元(Program Fetch) – 指令分配单元(Program Dispatch) – 指令译码单元(Instruction Decode) – 32个32位寄存器,分为两组,每组 16个(Register

TMS320C6000系列DSPs简介

• 使用DSPs的必要性 • 实时DSP系统的构成 • DSPs针对DSP算法的结构特点 • 衡量DSPs性能的一些常用指标 • TMS320C6000系列概况 • C6000的总体结构 • C6000的CPU结构特点 • C6000的片内集成外设

使用DSPs的必要性

– 数据收发采用多级缓冲结构,片内数据搬移可与片 外通信同时进行。

• Power-Down 逻辑

Power-Down 逻辑的功能是关闭芯片的一些开关操作, 在不丢失数据的前提下,显著降低芯片的功耗。共有 三种模式:PD1、PD2、PD3 • PD1模式用于在CPU边沿处屏蔽时钟输入

• PD2模式用于挂起PLL输出后的整个时钟系统

• PD3模式不仅暂停内部时钟系统而且还短开PLL于外时 钟的连接,因而功耗最小。

外引脚PD用于反应DSP当前的PD状态

• 扩展总线XB(C6202、C6203)

XB是在HPI的基础上发展的,同时也可用做第二条外 部总线。XB既可以当作HPI增强版使用,又可以当作 第二个I/O口使用。

– 在用作主机口HPI时,提供了同步/异步两种模式。 同步模式相当于32bitHPI;异步模式支持多种协议。

c2000,c5000,c6000系列DSP编程方法

二、TI公司三大系列内部结构的简介 1、C2000系列的内部结构1,C2000系列基于改进的哈佛结构,支持分开的程序空间和数据空间。

还有第三个空间,即I/O空间,用于片外总线接口。

外设总线映射到数据空间,因此,运行在数据空间的所有指令,都可以运行于所有的外设寄存器。

C2000系列的CPU包括:一个32位的中心算术逻辑单元(CALU)、一个32位的累加器(ACC)、CALU具有输入和输出数据定标移位器、一个16x16位乘法器、一个乘积定标移位器、数据地址产生逻辑:包括8个辅助寄存器和1个辅助寄存器算术单元(ARAU)、程序地址产生单元C2000系列采用2xLPASIC核,其内部设有6组16位的数据与程序总线。

这6组总线是:PAB(ProgramAddr.Bus)程序地址总线DRAB(Data-ReadAddr.Bus)数据读地址总线; DWAB(Data-WriteAddr.Bus)数据写地址总线; PRDB(ProgramReadBus)程序读总线;DRDB(DataReadBus)数据读总线;DWEB(DataWriteBus)数据写总线。

将数据读地址总线(DRAB)和数据写地址总线(DWAB)分开,CPU就可以在同一个机器周期内读和写数据。

C2000系列具有以下类型的片内存储器:双访问RAM(DARAM),即一个机器周期内可以访问两次的存器;FlashEEPROM或工厂掩模的ROM。

C2000系列的存储器分为单独可选择的4个空间,总共的地址范围为224K字:程序存储器(64K字);局部数据存储器(32K字);全局数据存储器(64K字);输入/输出(64K字)。

2、C5000系列的内部结构C5000系列中央处理单元CPU包括算术逻辑单元、乘法器、累加器、移位寄存器、各种专门用途的寄存器、地址发生器、比较选择单元、指数编码器。

具体内容如下①先进的多总线结构,具有1条程序存储器数据总线、3条数据存储器数据总线和4条地址总线;②40位算术逻辑单元(ALU),包括40位的桶形移位寄存器和2个独立的40位的累加器;③17位乘17位的并行乘法器与一个40位的专用加法器结合在一起,用于单周期乘/累加操作;④比较、选择和存储单元(CSSU),用于Viterbi操作(一种通信的编码方式)中的加/比较选择;⑤指数编码器用于在单周期内计算40位累加器的指数值;⑥2个地址生成器,包括8个辅助寄存器和2个辅助寄存器算术单元[6]。

C6000 DSP软件开发环境CCS介绍

CCS-RTDX(1)

}

RTDX,即Real-time Data Exchange

} } }

提供了一种实时,连续的观测手段,不打断DSP运行 不打断DSP运行的情况下,主机和DSP间传递数据 回传到主机的数据可以在“OLE自动化客户”中显示

CCS-RTDX(2)

CCS小结

} } }

不仅仅是代码生成工具,对软件开发的各个阶段 都有支持 提供底层实时操作系统DSP/BIOS 提供RTDX新的实时调试手段,与CCS集成,不需 要自己添加额外的用于调试的硬件 8Kbyte/s(XDS510),2Mbyte/s(XDS560)

}

包括Host方和Target方

} }

Target方编程接口 RTDX target API Host方编程接口 RTDX COM API(组件对象模型COM是 windows下一种编程技术)

CCS的文件与环境变量

} } }

.pjt .lib .obj .out .wks 可编辑文件:.c .asm .h .cmd (.sa) 三个环境变量:C6X_A_DIR,C6X_C_DIR, PATH

提供通常的RTOS的功能(任务调度,任务间通讯) 提供驱动程序模型,层次化地设计应用程序 DSP/BIOS以CCS插件的形式提供一些实时分析工具

} } }

程序跟踪:观察任务的调度、切换 性能监视:观察CPU的负载

}

状态统计:对事件做统计 提供RTDX(实时数据交换),不打断DSP运行的情况下实现主 机和DSP的数据交换

C6000 DSP软件开发环境 --CCS介绍

田黎育

内容安排

} 1、DSP软件开发环境发展历史 } 2、CCS中代码开发流程 } 3、RTDX(实时数据交换技术) }4

有关C6000DSP的Cache的操作教学内容

有关C6000D S P的C a c h e的操作篇幅之一 TI C64x+ DSP CACHE 一致性分析与维护作者: DSP 技术应用工程师陈永康摘要在各种数字信号处理系统中,CACHE被广泛用于弥补Core与存储器之间的速度差异。

在CACHE 的使用过程中,存在不同类型存储器之间数据是否一致的问题。

本文着重分析TI高性能C64x+ DSP系列中各级CACHE之间数据一致性问题以及如何进行一致性维护。

1. 概述CACHE作为Core和低速存储器之间的桥梁,基于代码和数据的时间和空间相关性,以块为单位由硬件控制器自动加载Core所需要的代码和数据。

如果所有程序和数据的存取都由Core完成,基于CACHE的运行机制,Core始终能够得到存储器中最新的数据。

但是当有其它可以更改存储器内容的部件存在时,例如不需要Core干预的直接数据存取(DMA)引擎,就可能出现由于CACHE的存在而导致Core或者DMA不能够得到最新数据的现象,也就是CACHE一致性的问题。

2. C64x+ 存储器组织结构TI对高性能C64x核进行了改进,使其性能大大提升,称之为C64x+DSP核。

基于C64x+核开发的DSP芯片,所有部件都以交换网络(SCR)为核心连接起来。

SCR上的部件分为两类:Master和Slave。

Master包括Core、EDMA以及串行高速IO(sRIO),EMAC等外设。

Master可以直接通过SCR发起到Slave的数据传输。

Slave包括每一个Core的内存,DDR2外存以及其它不能直接发起数据传输的外设,Slave之间的数据传输,需要通过DMA协助完成。

各款基于C64x+DSP的数据手册上详细描述了SCR的配置和Master、Slave的情况。

C64x+系统的存储器框图如图 1所示。

存储器被分成了三级:第一级是L1,包含数据存储器(L1D)和代码存储器(L1P);第二级是代码和数据共用存储器(L2);第三级是外部存储器,主要是DDR2存储器。

DSPC5000结构与外围功能

视频硬件扩展 - C5510、C5509

为 C55x DSP 系列仔细定制的三种硬件扩展是: 离散余弦变换 (DCT)/反向 DCT 像素插值 运动估值 提供不寻常的视频编解码器性能,从而释放了一半以上的 CPU 带宽来处理附加功能,如颜色空间转换、用户接口功 能、TCP/IP 以及视频处理。 高度优化的 C 编程等效、可使用 C 调用的函数,这些函数作 为 TMS320C55x DSP 图像/视频处理库 (IMGLIB) 的一部分来 提供,可从 TI 基础库下载。

全速 USB 2.0 (12Mbps) - C5509

与其它符合 USB 的设备的无缝互操作性。由 USB 实现者论坛 认证以确保数据传输速率高达 12Mbps。 仅用于控制传输的两个控制端点 用于其它类型的传输的十四个通用端点,这些传输可以是: 大量、中断和异步传输 用于快速数据吞吐量的可选双缓冲存储器方案 用于在通用端点和 DSP 存储器之间传输数据,而不会中断 CPU 的专用 DMA 通道。

新型 C55x™ DSP 结构的最新动态

新型 C55x™ DSP 结构的最新动态

新型 C55x DSP 系列以 C54x 系列为基础构建,是业界功耗最 低的 DSP。C55x DSP 内核支持新的编程功能,同时保持与 现有 C54x 代码的完整软件兼容性。C55x DSP 内核的创建 旨在推动未来从便携式因特网设备到高速无线再到基础设 施等数字应用,其特定功能包括:

结果是极其高效的电量使用和更低的系统成本。通过使用较少电量并散发更少的热量, C55x DSP 内核赋予设计人员有关电路板设计的更高灵活性。 C55x DSP 内核最具创新的特色之一是其支持可变长度指令(基于新的字节寻址方案): 指令长度可以是 8、16、24、32、40 或 48 位。 指令提取从 16 位增加到 32 位。 片上指令缓冲存储器单元会自动取出指令以最充分使用每个时钟周期。 C55x DSP 内核存储器总线活动的降低可以降低电量要求,同时在每个时钟周期,更长的指 令可以执行更多的功能,从而提高了性能并降低了系统成本。 C55x DSP 内核对于增强并行功能的关注使以下设备的周期效率得到改进: 附加硬件 - 双 17 x 17 位 MAC、另一个 16 位 ALU、四个新的数据寄存器(可用于简单计算 )以及四个 40 位累加器,这使每个周期能完成更多的工作,从而显著地降低整体的电 量要求。 新指令功能: 自动并行指令 隐式或内置并行指令 用户编程并行指令 提高正交性的附加指令 附加总线和扩展寻址 - 为确保吞吐量可以获取理论上新的计算硬件使之成为可能的最大吞 吐量,C55x DSP 内核采用以下总线: 三条 16 位数据读总线 两条 16 位数据写总线 一条 32 位程序总线 六条 24 位地址总线

TMS320C6000系列DSP程序固化方式分析

TMS320C6000系列DSP程序固化方式分析TMS320C6000系列DSP程序固化方式分析引言本章内容主要针对TMS320C6000系列芯片,其他类型芯片可能会有差别,但总体思路应该都有指导作用。

随着近年来数字信号处理器(DSP)技术的迅猛发展,其中,TI公司推出的TMS320C6000系列DSP器件更是在许多需要进行大量数字信号处理运算并兼顾高实时性要求的场合得以应用。

TMS320C6000系列DSP的系统设计过程中,DSP器件的程序加载是较难解决的问题之一。

C6000系列DSP的加载方式包括不加载、主机加载和EMIF加载3种。

不加载[No boot]:方式仅限于存储器0地址不是必须映射到RAM空间的器件,否则在RAM空间初始化之前CPU会读取无效的代码而导致错误;主机加载[Host boot]:要求必须有一外部主机控制DSP的初始化,这将增加系统的成本和复杂度,在很多实际场合是难以实现的;EMIF加载[EMIF boot]:DSP与外部ROM/Flash接口较为自由,但片上Bootloader工具自动搬移的代码量有限(1 KB/64 KB)。

本文讨论的就是在EMIF加载方式下的程序各种不同的固化方式。

包括在线烧写,使用CCS提供的FlashBurn工具,使用专有烧写工具[编程器],一、DSP加载方式的选择DSP使用哪种加载方式进行启动,是通过硬件配置的方式选择,当DSP的RESET引脚无效后,DSP读入外围的配置引脚信息,确定加载启动的具体方式。

具体的配置管脚设定可以参考< >literature number: SPRS200二、EMIF加载方式启动过程当RESET变成高电平的时候,在CE1空间开始的1K字节的ROM 代码通过EDMA 被复制到地址为0 的地方(用DSP EMIF最慢的时序),在此期间DSP核一直处于“停止”状态。

数据被存储成系统所用的字节序格式。

在这种情况下,EMIF自动的把要搬移的8位宽数据拼接为32位指令字。

C6000与C2000系列DSP之间串行数据通讯的研究与实现(精)

C6000与C2000系列DSP之间串行数据通讯的研究与实现TMS320C6711是TI公司TMS320C6000系列32位浮点DSP,它具有专用硬件逻辑的CPU、片内存储器、片内外设,支持汇编和C语言的单独或混合编程。

该系列DSP最主要的特点是采用了VLIW体系结构,因此可以单周期发射多条指令,实现很高的指令级并行效率。

其计算和处理速度非常快,系统单指令周期可达到6.67ns,被广泛用于DSL、无线基站、雷达声纳、数字图像处理等方面。

在TMS320C6711中有2个多通道缓冲串行接口McBSP,McBSP不仅可以配制成串行TMS320C6711是TI公司TMS320C6000系列32位浮点DSP,它具有专用硬件逻辑的CPU、片内存储器、片内外设,支持汇编和C语言的单独或混合编程。

该系列DSP最主要的特点是采用了VLIW体系结构,因此可以单周期发射多条指令,实现很高的指令级并行效率。

其计算和处理速度非常快,系统单指令周期可达到6.67ns,被广泛用于DSL、无线基站、雷达声纳、数字图像处理等方面。

在TMS320C6711中有2个多通道缓冲串行接口McBSP,McBSP不仅可以配制成串行接口,还可以独立配制成通用的输入(GPI)、输出(GPO)和输入输出端口(GPIO)。

其优点是数据处理能力强大,但控制接口少,片内集成外部设备少,控制能力较弱。

TI公司的TMS320LF2407为16位定点DSP微控制器,内嵌有看门狗定时器(WDT)、CAN总线控制器、模数转换器(ADC)、串行外设接口(SPI)、异步串行口(SCI)等多种外设模块,并有大量输入输出引脚(GPIO),可以满足控制系统多方面的控制需求。

但由于TMS320LF2407的指令周期最短为25ns(40MHz 主频),对于数据处理运算量特别大的系统,其运算速度略显不足。

多数数字图像处理应用系统既要求系统有强大的数据处理能力,以满足对图像处理的实时性要求,又要求系统有强大的控制能力,以便实现对外部众多设备的控制。

C6000系列DSP的CPU结构概述

允许寄存器产生的数据地址支 持同侧寄存器到存储器的存取 操作.

也允许寄存器产生的数据地址 支持另一侧寄存器到存储器的 存取操作

ST1a 32MSB

TMS320C64x存储器读取通路

控制寄存器

控制寄存器缩写 AMR

控制寄存器名称 寻址模式寄存器

描述 指定是否使用线性或循环寻址,也包括循环寻址的尺寸

CSR

C6000系列CPU结构介绍

2 个对称的可进行数据处理的数据通路(A 和 B)

16个(C64x有32个)32位 通用寄存器

16个(C64x有32个)32位通 用寄存器

每个数据通路的4个功能单元有单一的 数据总线连接到 CPU 另一侧的寄存器上

4个功能单元 (.L、.S、.M和.D)

4个功能单元 (.L、.S、.M和.D)

指定条件寄存器

源2使用交叉通路 目的寄存器为A组或B组

TMS320C6000.L/.M指令操作码映射图

指令操作码映射

基址寻址寄存器

寻址模式 LDDW位 选择D1或D2

寄存器偏移量/5位无符号常量

load/store指令域

TMS320C6000.D指令操作码映射图

指令操作码映射

TMS320C6000 NOP 指令操作码映射图

CPU数据通路与控制

功能单元

每个功能单元都有各自到 通用寄存器的读写端口, 其中2个32读端口,1个32 写端口。

.L1、.L2、.S1和.S2另有 8位读端口和写端口,支 持40位操作数的读写。

同一周期8个功能单元可 并行使用。

C64x 的.M 单元可以返回 64 位结果,所以它还多 了一个 32 位写端口。.M 单元long dst是32MSB ,dst是 32 LSB。

C6000 DSP

C6000 DSP概况近年来,以高速数字信号处理器(DSP)为基础的实时数字信号处理技术飞速发展,并获得了广泛的应用。

TMS320C6000系列DSP是德州仪器公司(TI)推出的定点、浮点系列DSP,其中定点产品峰值处理能力达到4800MIPS,浮点产品峰值处理能力达到1350MFLOPS,是目前国际上性能最高的DSP之一,其卓越的性能使得它在传统的DSP领域、雷达、无线电基站等高端领域,以及宽带媒体、身份识别等新兴领域都有很好的应用前景。

随着DSP性能和功能的不断增强,应用系统的设计越来越复杂,要将DSP的性能充分释放出来,合理的板级设计是DSP系统开发人员面临的一个关键性的问题。

TI公司的三种新型TMS320 DSP系列和OMAP系列1.TMS320C2000——作控制用的最佳DSP,可以替代老的C1X和C2X。

TMS320C20X系列DSP芯片具有如下特点:(1)处理能力强:指令周期最短是25nm,运算处理能力达40MIPS。

(2)片内具有较大的FLASH存储器:TMS320C20X是最早使用片内FLASH存储器的DSP芯片,FLASH存储器具有比ROM灵活、比RAM便宜的特点,TMS320F206和TMS320F207的片内具有32KB的FLASH存储器和4.5KB的RAM。

(3)芯片的功耗低:TMS320C20X 系列DSP芯片在5V工作时每个MIPS消耗1.9mA电流,在3.3V工作时每个MIPS消耗1.1mA电流4)芯片的资源配置灵活。

TMS320C2000系列DSP芯片价格低,具有较高额性能和适用于控制领域的功能,因此可以广泛地应用于工业自动化、电机控制、运动控制、电力电子、家用电器等领域.现在有趋势集中在以下两个方向上(1)C20X16位定点DSP,速度为20MIPS,主要用途是电话、数字相机、售货机等,其中:F206带有闪速存储器。

(2)C24X16位定点DSP,速度为20MIPS,用作数字马达控制、工业自动化、电力转换系统、空调等。

C6000 DSP技术 实验指导书

《DSP技术》实验指导书--基于TMS320C6x萍乡高专机电系电子教研室肖永江编著2011-03-01目录实验1 、CCS 的简单应用程序的建立--------------------------------------------------------------3 实验2 、汇编语言编程实验---------------------------------------------------------------------------8 实验3 、数字IO实验----------------------------------------------------------------------------------11 实验4 、SDRAM 读写实验--------------------------------------------------------------------------15 实验5、定时器实验-----------------------------------------------------------------------------------20 实验6 、McBSP通信实验----------------------------------------------------------------------------23 实验7、FIR滤波器实验------------------------------------------------------------------------------25 实验8、FFT实验---------------------------------------------------------------------------------------32 实验9 、软件中断实验---------------------------------------------------------------------------------39 实验10、EDMA实验------------------------------------------------------------------------------------41基础实验1:CCS 的简单应用程序的建立1.1 实验目的1.熟悉Code Composer Studio2.21集成开发环境,掌握工程的生成方法;2.熟悉ICETEK-DM642-B实验环境;3.掌握CCS 集成开发环境的调试方法;1.2 实验内容1. DSP 源文件的建立;2. DSP 程序工程文件的建立;3. 学习使用CCS 集成开发工具的调试工具1.3 实验步骤1.3.1 创建工程文件1. 打开CCS,点击Project-->New,弹出如下对话框,创建一个新工程,其中工程名及路径可任意指定。

DSP器件原理与应用-05 TMS320C6000系列DSP集成外设

2

1

13

2

1

13

2

1

13

1

1

13

2

1 2 64-bit TCP2 VCP2

2

2

21

3

2

21

3

2

21

5.2 片内存储器

5.2.1 简介

C6000 系列 DSP 片内集成了大容量存储器,存储器的容量和结构随芯片不同而有所差别。 对于 C620x/C670x,片内存储器分为程序区间和数据区间两部分,其中程序区间可以作为 普通 SRAM 映射到存储空间,也可以作为高速缓存。 对于 C621x/C671x/C64x,片内采用二级存储器结构。第 1 级存储器包括相互独立的程序 缓存(L1P)和数据缓存(L1D),只能作为高速缓存被 CPU 访问。第 2 级存储器(L2)是一 个统一的程序/数据空间,可以整体作为 SRAM 映射到存储空间,也可以整体作为第 2 级缓存, 或者按比例组合。

10/100

10/100

10/100

10/100

10/100/1000

HPI

1 16-bit

1 16-bit 1 16-bit 1 16-bit

1 16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit 1 32/16-bit

Map 0

0140 0000h – 0140 FFFFh 0140 0000h – 0141 FFFFh 0142 0000h – 0143 FFFFh 0140 0000h – 0143 FFFFh 0144 0000h – 0145 FFFFh 0140 0000h – 0140 FFFFh 0140 0000h – 0140 FFFFh 0140 0000h – 0140 FFFFh

浅谈C2000、C5000、C6000的内部结构和区别

浅谈C2000、C5000、C6000的内部结构和区别浅谈C2000、C5000和C6000的内部结构和区别摘要:德仪公司的DSP分为多种系列,其中TI公司的TMS320系列的DSP在全球应用中较为广泛。

本文重点对TMS320系列下的C2000系列,C5000系列,C6000系列的内部结构做重点介绍,并对其内部结构进行比较。

为了更好地了解其内部结构下面主要从三大方面进行总结,分别是:中央处理单元(CPU)、存储器和I/O空间、外围设备。

关键词:内部结构C2000系列C5000系列C6000系列Introduction to the internal structure and distinction ofC2000,C5000,C6000Abstract:The digital signal processors of the TI company are the widely used for many years.the IT company's DSP is divided into several series,in which TMS320 series have an wide application in the global .Toward the C2000 series, C5000 series, C6000 series which belong to TMS320 series,this paper mainly makes summary and comparison about their internal structure. In order to better understand its internal structure below summarizes mainly from three aspects, respectively is: the central processing unit (CPU), memory and I/O space, and peripheral devices.Keywords:Digital signal processing The internal structure C2000 series C5000 series C6000 series 一、引言在生产数字信号处理的全球企业中,美国的德仪公司生产的数字信号处理器多年来一直占据了较大的DSP生产市场,并且在不断的扩大。

DSP_C6000软件优化__线性汇编

zero sum .reg伪指令 伪指令: loop: ldh *p_m++, m .reg伪指令: •声明符号变量,变量由优化器 ldh *p_n++, n 选择与功能单元一致的寄存器 mpy m, n, prod •.reg在.(c)proc/ .endproc内有效 add prod, sum, sum •当变量为40/64bit时,变量使用 [count] sub count, 1, count 寄存器对格式:如ahi:alo [count] b loop .endproc

远见品质

.mdep伪指令

假如你需要指明2个或更多的存储体的相关性,你可以 使用.mdep伪指令。用存储体相关性标号来注释你的代 码,并且在线性汇编函数中加上.mdep伪指令。 当使用了.no_mdep或-mt后,才需要使用.mdep伪指令。

.mdep伪指令表明从LDW指令到STW指令中有存储体相关 性。这就意味着STW指令必须在LDW指令后执行。.mdep 伪指令不表明在STW指令到LDW指令中存在存储体相关性。 要处理后一种情况,还需要一个.mdep伪指令。

C64的 L1D的 存储体结构: 8×32bit

远见品质

流水线停顿

同一周期对同一bank的两次读取引起流水线阻塞的情况。 LDW .D1 *A4++,A5 ; load 1, A4 address is in bank 0 || LDW .D2 *B4++,B5 ; load 2, B4 address is in bank 0

线性汇编文件基本考虑事项

线性汇编文件使用“.sa”扩展名 仅对指定的代码段进行优化,指定代码段 外的代码被拷贝为输出“.asm”文件 线性汇编过程可以: 传递参数 返回结果 使用符号变量 不考虑流水线问题

集成外设及DSPBIOS应用实例(下)(1)

集成外设及DSP/BIOS应用实例(下)5 TMS320C6000的DMA控制器设计本节主要介绍C6000系列的直接存储器访问(DMA,Direct Memory Access)控制器其中介绍硬件特点、DMA通道与寄存器。

5.1 DMA硬件介绍DMA控制器最大的特点是可以在没有CPU参与的情况下完成映射存储空间中的数据搬移。

这些数据搬移可以是在片内存储器、片内外设或是外部器件之间,而且是在CPU后台进行的。

DMA控制器具有4个相互独立编程的传输通道,允许进行4个不同内容的DMA传输。

另外,还有一个辅助通道用来服务于主机口接口读写访问。

在讨论DMA操作时,需要了解C6000的DMA传输中的几个概念:(1)数据的读传输(read transfer):DMA控制器从源地址存储器中读取数据。

(2)数据的写传输(write transfer):DMA控制器将读取的数据写入目标地址存储器中。

(3)数据单元传输(element transfer):一个数据单元的读传输和写传输的结合。

(4)帧传输( transfer):帧的大小可编程设置。

完成一个帧传输即传输一定数量的数据单元。

(5)块传输(block transfer):每个DMlA通道也可以独立定义每块中帧的数量。

完成一个块传输即传输一定数量的帧。

(6).发送数据单元的传输(transmit element transfer):在通道分割模式下,数据单元从源地址中读出并写入分割目的地址。

(7)接受数据单元的传输(receive element transfer):在通道分割模式下,数据单元从分割源地址中读出并写入目的地址。

DMA控制器有如下主要特点:(1)后台操作:DMA控制器可以独立于CPU工作。

(2)高吞吐率:可以以CPU时钟的速度进行数据传输。

(3)4个通道:DMA摔制器可以控制4个独立通道的传输。

(4)辅助通道:主机口用辅助通道来访问CPU的存储空间。

TMS320C6000 DSPs的Power-down 逻辑和中断控制

00100b EXT_INT4 00101b EXT_INT5 00110b EXT_INT6 00111b EXT_INT7

01000b EDMA_INT EDMA通道中断

INT9

INT10 INT11 INTSEL10 INTSEL11 INTSEL12 INTSEL13 INTSEL14

TMS320C6000 DSPs的 Power-down 逻辑和中断控制

一、Power-down(断电模式) 逻辑

• Power-down逻辑的功能

CMOS芯片的主要功耗都发生在内部电路的开关动作中。 Power-down逻辑功能可以在不丢失数据的前提下,阻止 部分逻辑甚至整个芯片的开关操作,因此能够明显减小芯 片的功耗。

IFm IACK

INUM Execute packet n n+1 n+2 n+3 0 0 0 0 0 0 0 m 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

DC E1 E2

E3 E4 E5 E6 E7

E8 E9 E10 E7 E8 E9 E10 E6 E7 E8 E9 E10 E6 E7 E8 E9 E10

2

3

4

5

6

7

8

9 10 11 12 13 14 15 16 17 18 19 20 21 22

IF4 IACK

INUM

1CLKOUT1 0100 CLKOUT2 2CLKOUT2

IACK pin 4CLKOUT2 INUM pins 0100

Power-down的逻辑框图

(2) PD2模式:完 成附加的功耗节 省; 整个片上 时钟结构(包括 多个缓冲器)被 暂停

(3) PD3模式:与PD2模 式类似;还会断开外 部时钟源(CLKIN)与 PLL的连接;唤醒时间 比PD2要长,因为PLL 需要重新锁定,过程 与上电过程类似

C6000 DSP硬件板卡开发1

3.DSP最小系统设计

3.电源功耗分析

(1)典型功耗估计

(2)按利用率估计

3.DSP最小系统设计

3.电源--器件选择

3.DSP最小系统设计

3.电源—散热

3.DSP最小系统设计

4.时钟—输入

3.DSP最小系统设计

4.时钟

单端1驱多

单端转差分1驱多

3.DSP最小系统设计

5.复位电路

Date: Sunday Aug. 20, 2006 Time: 22:50:14 Show Latest Waveform = YES, Show Previous Waveform = YES

-3.000 0.000

10.00

20.00

30.00

40.00

50.00 Time (ns)

60.00

DSP芯片 电源 时钟源 复位电路 JTAG电路 程序ROM 对芯片所做的设置。

3.DSP最小系统设计

3.DSP最小系统设计

1.功能设置

3.DSP最小系统设计

2.程序ROM-接口

3.DSP最小系统设计

2.程序ROM-编程

3.DSP最小系统设计

2.程序ROM-自加载

差分解决方案

5.Q6455板设计流程

5.时钟设计—Switch

差分时钟需求

5.Q6455板设计流程

5.时钟设计—PCI

5.Q6455板设计流程

5.复位设计 --仔细阅读勘误表

5.Q64PMC

5.Q6455板设计流程

6.PCB前仿真—需求

基于TMS320C6000系列DSP器件实现嵌入式系统的优化设计

基于TMS320C6000系列DSP器件实现嵌入式系统的优化设计1TMS320C6000的硬件设计和指令系统TMS320C6000系列DSP(数字信号处理器)是TI公司最新推出的一种并行处理的数字信号处理器。

它是基于TI的VLIW技术的,其中,TMS320C62xx是定点处理器,TMS320C67xx 是浮点处理器。

本文主要讨论TMS320C6201。

该处理器的工作频率最高可以采用50MHz,经内部4倍频后升至200MHz,每个时钟周期最多可以并行执行8条指令,从而可以实现1600MIPS的定点运算能力,而且完成1024定点FFT的时间只需70μs。

1.1TMS320C6000的硬件结构TMS320C6000的CPU有两个数据通道A和B,每个通道有16个32位字长的寄存器(A0~A15,B0~B15),四个功能单元(L,S,M,D),每个功能单元负责完成一定的算术或者逻辑运行。

A、B两通道的寄存器并不是完全共享,只能通过TM320C6000提供的两个交换通道1X、2X,才能实现处理单元从不同通道的寄存器堆那里获取32位字长的操作数。

TMS320C6000的地址线为32位,存储器寻址空间是4G。

C6201片内集成有1MbitSRAM——512Kbit的程序存储器(根据需要可全部配置成Cache)和512Kbit的数据存储器。

通过片内的程序存储空间控制器,CPU一次可以取出256bit,即一次最多可以取出8条32位指令。

C6201有32位的外部存储接口EMIF为CPU访问外围设备提供了无缝接口。

外围设备可以是同步动态存储器(SDRAM)、同步突发静态存储器(SBSRAM)、静态存储器(SRAM)、只读存储器(ROM),也可以是FIFO寄存器。

为了便于进行多信道数字信号处理,TMS320C6000配备了多信道带缓冲能力的串口McBSP。

McBSP的功能非常强大,除具有一般DSP串口功能之外,还可以支持T1/E1、ST-BUS、IOM2、SPI、IIS等不同标准。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

64MB~ 3C20 0000~7FFF FFFF 1GB 256MB 8000 0000~8FFF FFFF 256MB 9000 0000~9FFF FFFF 256MB A000 0000~AFFF FFFF 256MB B000 0000~BFFF FFFF 1GB C000 0000~FFFF FFFF

双路组相联

直接映射

Cache RAM 4KB

snoop address

L1 program cache(L1P) data controller

address

Program Address(32bit)

Program Data (256b)

数据地址 32bit; 数据8, 16, 32bit

Cache RAM 4KB

4KB

L1D结构

2路组联想

L1P结构

直接映射

L1D CPU访问时间 单周期

L1P CPU访问时间 单周期

L1D 行容量

32B

L1P 行容量

64B

L1D置换策略

2路LRU(最近很少使用)

L1P存储体构造

1256bit存储体 L1D存储体构造 64bit宽度双口RAM

L1P读缺失的分配 L1P中分配一行

2

TMS320C6713 – 225MHz Audio DSP

TMS320C6713 Floating-Point DSP

EMIF

McBSP 0

OR

McASP 0

Level 1 Program

Cache 4K Bytes

Enhanced DMA Controller (EDMA) 16 Channel

第五章 C6000系列DSPs的集成 外设与硬件开发

1

• (1) 片内程序存储器和数据存储器 • (2)外部存储器接口(EMIF)的设计 • (3) 直接存储器访问(DMA)和扩展的直

接存储器访问(EDMA) • (4)多通道缓冲串口(McBSP) • (5)主机口(HPI)和PCI接口 • (6)芯片的设置和其他片内集成外设

6

621x/671x/64x的片内2级存储器

TMS320C6713 Floating-Point DSP

EMIF

McBSP 0

OR

McASP 0

Level 1 Program

Cache 4K Bytes

Enhanced DMA Controller (EDMA) 16 Channel

Level 2 Cache/Memory 256K Bytes SRAM

存储器组描 组大小 十六进制地址范围 述

McBSP0 数据 McBSP1 数据 保留

McASP0 数据 McASP1 数据 保留

EMIF CE0

EMIF CE1

EMIF CE2

EMIF CE3 保留

64MB 3000 0000~33FF FFFF

64MB 3400 0000~37FF FFFF

64MB 3800 0000~3BFF FFFF 1MB 3C00 0000~3C0F FFFF

Level 2 Cache/Memory 256K Bytes SRAM

McBSP1

OR

IIC 1

HPI

OR

GPIO McASP 1

IIC 0

2 Timers PLL

Power Down Logic

Boot Configuration

C67xTM DSP Core

Level 1 Data Cache

256KB 0190 0000~0193 FFFF

存储器组描 组大小 十六进制地址范围 述

Timer 0 寄存器

256KB 0194 0000~0197 FFFF

Timer 1 寄存器

256KB 0198 0000~019B FFFF

中断向量寄 存器

配置寄存器

512B 4B

019C 0000~ 019C 01FF 019C 0200~019C 0203

L1P读命中的分配 L1P中读取数据

L1P写缺失的分配 不支持L1P写

L1P写命中的分配 支持L1P写

L1PL2申请

2次存取/L1P行

L1P协议

读分配L1Pຫໍສະໝຸດ 储器单周期RAML1P L2申请时CPU 5周期 阻塞

L1D读 缺失的分配 L1D中分配一行

L1D读命中的分配 L1D中读取数据

L1D写缺失的分配 L1D中不分配,数据送入

256KB~ 0004 0000~017F FFFF 24MB 256KB 0180 0000~0183 FFFF

128KB 0184 0000~0185 FFFF

128KB 0186 0000~0187 FFFF

256KB 256KB

0188 0000~018B FFFF

018C 0000~018F FFFF

(1) L1P和L1D相互独立,只能作为Cache被CPU访问

(2) L2是一个统一的程序/数据空间,可以整体作为 SRAM映射到存储空间,也可整体作为第2级Cache, 或者是二者按比例的一种组合

11

621x/671x片内存储器结构

片内cache RAM 结构 2级缓存

L1D容量

4KB

L1P容量

相联(associative): 是在每一组(set)中行帧的数目。行帧是Cache 中保存缓 存数据(一行)、联合寻址标记和行状态数据的一个位置。状态数据指明 该行有效或重写。重写指的是Cache的一行保存的数据有效且被CPU修改 过,但是这种修改没有在下一更高级内存中更新

侦听snoop:是一种高级存储器查询低级存储器以确定两者是否含有同一 地址的数据的方法。在两级存储器系统中,当数据从高级存储器中移出 时,必须侦听低级存储器来确定逐出的地址是否与低级存储器中的同一 地址不一致。

5

存储器组描 述

I2C0寄存器

组大小 16KB

十六进制地址范围 01B4 0000~01B4 3FFF

I2C1寄存器 16KB 01B4 4000~01B4 7FFF

保留

16KB 01B4 8000~01B4 FFFF

McASP0 寄存器

McASP1 寄存器 保留

16KB 01B4 C000~01B4 FFFF 16KB 01B5 0000~01B5 3FFF 160KB 01B5 4000~01B7 BFFF

L1D

L1D写命中的分配 数据送入L1D命中区

L1DL2申请

2次存取/L1D行

L1D协议

读分配

L1D L1D申请时 4周期 CPU阻塞

12

621x/671x片内存储器结构(续1)

L2容量

64KB

L2 cache容量 0/16/32/64KB

L2 SRAM容量 64/48/32/16/0KB

L2结构

McBSP1

OR

IIC 1

HPI

OR

GPIO McASP 1

IIC 0

2 Timers PLL

Power Down Logic

Boot Configuration

C67xTM DSP Core

Level 1 Data Cache

4K Bytes

• 片内采用2级高速缓 存结构,程序和数据 拥有各自独立的高速 缓存。

有

GPIO

有

内部集成的电路模块I2C总线 2组

锁相环(PLL)控制器

有

3

存储器映射

• C6000DSP系统通过EMIF(外部存储器接口)可以使用外 部存储器。

• L1P、L1D、L2分别由各自的控制器控制 • C6000DSP总的存储地址范围为4GB(相应使用32位内

部地址表示0000 0000~FFFF FFFF)。每种存储器映射 都被分为片内程序存储器、片内数据存储器、片外存 储器、片内外设空间 • C6211/C6711/C6713只有1种存储器映射方式:片内存 储器始终位于地址0处,可以当作程序或数据存储空间 • C6211/C6711/C6713的存储器映射方式只需2位进行设 置,即通过对主机口的HD[4:3]设置引导方式,利用电 阻上拉或下拉设置引导方式

10

C6713DSP的片内存储器配置

内部存储器结 构 哈佛结构(L1) Unified (L2)

注意:

存储器总量 程序存储器 数据存储器

(KB)

L1P(KB)

L1D(KB)

264

4 (Cache)

(L1P)

4 (Cache)

(L1D)

Unified 存储器L2(KB)

64(映射/Cache) 192(映射)

Program fetch

C6713 CPU

Data path A Data path B

L2 cache controller

L1 data cache(L1D) controller

address data data snoop address

RAM 64KB

EDMA

9

直接映射cache:包含能缓存特定的高级存储器的唯一Cache行。这并 不意味着该cache 像它所缓存的存储器一样包含很多行,而是指一 个存储器地址只能由专门的行来缓存。例如,一个存储器地址被 缓存在直接映射cache位置A,清除cache之后再缓存,它还是只能 被缓存在位置A。

PLL寄存器 8KB 01B7 C000~01B7 DFFF

保留

QDMA 寄存器 保留

保留

520KB ~4MB

52B

01B7 E000~01FF FFFF 0200 0000~0200 0033