PSpice仿真教程8-差分放大电路分析解读

差分放大电路的分析与仿真

差分放大电路的分析与仿真摘要:差分放大电路是模拟电路学习中常用到的放大电路,其抑制零点飘移的良好电气特性,使它经常被用作多级放大电路的输入级。

本文通过对差分电路的静态及动态分析及仿真,让学生能够对差分放大电路有深入的了解。

关键词:零点漂移;差分放大;仿真分析中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2018)09-0246-011 引言当今世界之所以能称之为智能化的时代,是由于各种智能化的设备得到了普及,而这些智能化设备之所以能够智能化,离不开功能各异的各种传感器,而这些传感器所采集到的电信号一般都很微弱,同时这些微弱的电信号往往不是周期性的,所以对这些信号进行放大处理时,需要采用直接耦合放大电路进行放大,所谓直接耦合即输入信号引入放大电路及放大电路与其负载的连接都是靠导线直接连接,因此直接耦合连接方式有很好的低频特性同时又很容易做成集成电路。

直接耦合放大电路虽然有以上几大优势,但普通的直接耦合放大电路存在零点漂移现象,所谓“零点漂移”,就是当输入信号为零时面输入信号不为零。

差分放大电路是一种直接耦合放大电路,差分电路本身具有良好的电气对称性,使其对模性号有很强的抑制作用,所以能有效地抑制零点漂移现象的发生。

2 差分放大电路抑制温漂的原理分析零点漂移现象的产生,其原因有很多,但最为主要的原因还是晶体管受到外部温度变化所引起的静态工作点的波动,所以零点漂移也常被称为温度漂移,简称温漂。

那差分放大电路是如何做到抑制温漂的呢?图1所示电路为长尾差分放大电路,当两端的输入信号电压uI1=uI2=0时,也就是电路处于完全的直流分量控制静态状态,因为T1与T2管的电气特性完全相同,其外接电阻参数也都相同,那么就有集电极对地电位UCQ1=UCQ2的结果,所以静态时的输出电压UO=0。

如果外界温度升高了,ICQ1和ICQ2也会同时增大,而且其增大幅度完全相同,从而导致两个集电极电阻上的压降出现等值幅度的增大,进而使UCQ1和UCQ2同时等值幅度变小,所以输出UO=UCQ1CUCQ2=0保持不变。

PSPICE仿真流程

PSPICE仿真流程(2013-03—18 23:32:19)采用HSPICE 软件可以在直流到高于100MHz 的微波频率范围内对电路作精确的仿真、分析和优化。

在实际应用中,HSPICE能提供关键性的电路模拟和设计方案,并且应用HSPICE进行电路模拟时,其电路规模仅取决于用户计算机的实际存储器容量。

二、新建设计工程在对应的界面下打开新建工程:2)在出现的页面中要注意对应的选择3)在进行对应的选择后进入仿真电路的设计:将生成的对应的库放置在CADENCE常用的目录中,在仿真电路的工程中放置对应的库文件。

这个地方要注意放置的.olb库应该是PSPICE文件夹下面对应的文件,在该文件的上层中library 中的.olb中的文件是不能进行仿真的,因为这些元件只有.olb,而无网表。

lib。

4)放置对应的元件:对于项目设计中用到的有源器件,需要按照上面的操作方式放置对应的器件,对于电容,电阻电感等分离器件,可以在libraries中选中所有的库,然后在滤波器中键入对应的元件就可以选中对应的器件,点击后进行放置.对分离元件的修改直接在对应的元件上面进行修改:电阻的单位分别为:k m;电容的单位分别为:P n u ;电感的单位分别为:n 及上面的单位只写量级不写单位.5)放置对应的激励源:在LIBRARIES中选中所有的库,然后键入S就可以选中以S开头的库。

然后在对应的库中选中需要的激励源.激励源有两种一种是自己进行编辑、手工绘制的这个对应在库中选择:另外一种是不需要自己进行编辑:该参数的修改可以直接的在需要修改的数值上面就行修改,也可以选定电源然后点击右键后进行对应的修改。

6)放置地符号:地符号就是在对应的source里面选择0的对应的标号.7)直流电源的放置:电源的选择里面应该注意到选择source 然后再选定VDC或者是其它的对应的参考。

8)放置探头:点击对应的探头放置在感兴趣的位置处.6 对仿真进行配置:1)对放置的项目的名称进行设置,也就是设置仿真的名称.2)对仿真进行配置:对仿真的配置主要是对两个对应的选项进行操作,Analysis中的对应操作:这个里面主要对应analysis type 以及的操作,对应扫描频率,需要注意MEG的频率单位.在configuration Files里面要注意category 中应该选择library,在filename 中选择对应的IC的库文件,选定后再选择add as global 按键,然后点击确认就可以了。

PSpice实例教程-差分放大电路分析

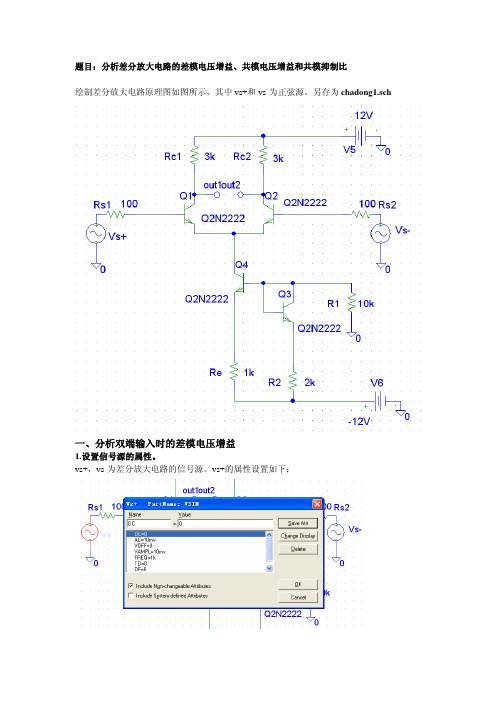

题目:分析差分放大电路的差模电压增益、共模电压增益和共模抑制比绘制差分放大电路原理图如图所示,其中vs+和vs-为正弦源。

另存为chadong1.sch一、分析双端输入时的差模电压增益1.设置信号源的属性。

vs+,vs-为差分放大电路的信号源。

vs+的属性设置如下:Vs-的属性设置如下:vs+的“AC”项设为10mv,vs-的“AC”项设为-10mv。

这样才能起到差模输入的作用。

2. 设置分析类型3. AnalysisÆSimulate,调用Pspice A/D对电路进行仿真计算。

4.测得恒流源给出的静态电流为1.849mA,晶体管Q1和Q2的发射极电流相等,都为0.9246mA。

(思考为什么是相等的)5. 在probe下,单击TraceÆAdd,在Trace Expression中输入要显示的变量。

若要观察单端输出时的差模电压增益,编辑表达式为:V(out1) / (V(Vs+:+)-V(Vs-:+));若要观察双端输出时的差模电压增益,编辑表达式为:(V(out1)-V(out2)) / (V(Vs+:+)-V(Vs-:+))。

得到结果如下:6. 用游标测量,双端输出时的差模电压增益为100.68,单端输出时的差模电压增益为50.34.是双端输出时的一半(为什么)。

两条曲线的上限截止频率点都是3.3843Mhz。

二、分析双端输入时的共模电压增益将原理图chadong1.sch打开,另存为chadong2.sch1.设置信号源的属性。

vs+的属性设置不变。

Vs-的“AC”属性设置为10mv,使其和信号源vs+一样,这样就相当于在两个输入端加上了相同的信号,起到共模输入的作用。

2. 设置分析类型3. AnalysisÆSimulate,调用Pspice A/D对电路进行仿真计算。

4. 在probe下,单击TraceÆAdd,在Trace Expression中输入要显示的变量。

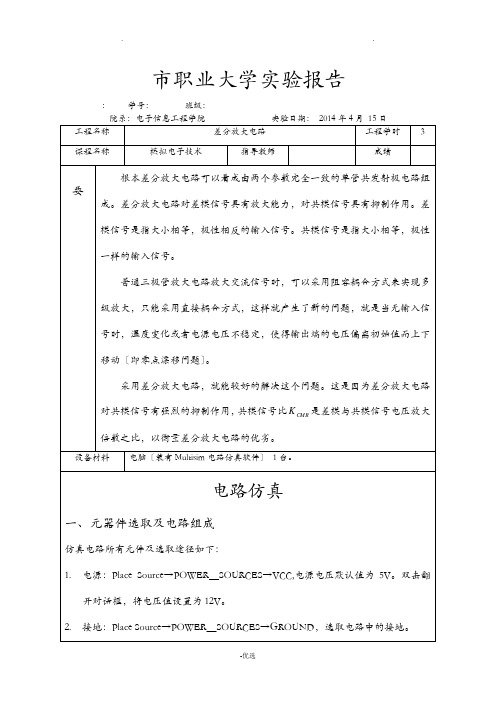

差分放大电路仿真

市职业大学实验报告:学号:班级:结果如图3所示,测得A I B μ151=,mA I C 089.11=,V U CE 303.5= 。

2. 测量差模放大倍数将函数信号发生器XFG1的"+〞端接放大电路的R1输入端,"—〞端接R2输入端,端接地。

调节信号频率为1kHz ,输入电压10mV,调入双踪示波器,分别接输入输出,如图4所示,观察波形变化,示波器观察到的差分放大电路输入、输出波形如图5所示。

图2 差分放大器电路调零图5 差模输入差分放大电路输入、输出波形图3.测量共模放大倍数将函数信号发生器XFG1的"+〞端接放大电路的共同输入端,接地,构成共模输入方式,如图6所示。

在输出负载端用万用表测量输出电压值,翻开仿真开关,测得8R两端输出电压值为pV.1,几乎为0,所以共模双端输出放大倍数也就近038似为0。

图6 共模输入、双端输出电压放大倍数测量示波器观察到的差分放大电路输入、输出波形如图7所示。

图7共模输入差分放大电路输入、输出波形R1 2k¦¸R22k¦¸R36.8k¦¸R46.8k¦¸R55.1k¦¸R6 510¦¸R7 510¦¸R812k¦¸Rp1100¦¸Key=A50%V112 VV212 VQ12N3903Q22N390316710110 2XSC1A B Ext Trig++__+_5XFG13489图8 单端输出差分放大电路图9 单端输出差分放大电路波形图总结通过这次实验仿真,对Multisim仿真软件的了解,在实践过程中也不断地积累了经历,能够独立完成电路的连接,并且能够熟练使用仪表元件进展测试。

通过仿真实验可以看到,差分放大电路只放大差模信号,对共模信号有很强的抑制作用。

差分放大电路仿真分析报告

差分放大电路仿真剖析差分放大电路是集成运算放大器的主要单元电路之一,它拥有很强的克制零点漂移的能力。

作为集成运算放大器的输入级,差分放大电路几乎完整决定着集成运算放大器的差模输入特征、共模克制特征、输入失调特征和噪声特征。

差分放大电路经由两个参数完整同样的晶体管构成,电路构造对称。

电路具有两个输入端和两个输出端,所以差分放大电路拥有四种形式:单端输入单端输出、单端输入双端输出、双端输入单端输出以及双端输入双端输出。

实验内容:一、理想差分放大电路1、绘制电路图启动 Capture CIS 程序,新建工程,利用 Capture CIS 画图软件,绘制以下的电路原理图。

双击正弦电压源VS+的图标,在弹出的窗口中设置AC为 10mV,DC为 0V,VOFF 为 0,VAMPL为 10m,VFREQ1kHz。

VS-的设置除 AC为-10mV外,其他均与 VS+同。

2、直流工作点剖析选择 Spice | New Simulation Profile功能选项或单击按钮,翻开NewSimulation 对话框,在Name文本框中输入Bias ,单击 Create按钮,弹出Simulation Settings-Bias对话框,设置以下:保留设置,启动 PSpice A/D 仿真程序,调出 PSpice A/D 窗口,能够在 PSpice A/D 窗口中选择 View | OutPut Filse 功能菜单项选择项,查察输出文件。

在 Capture CIS 窗口中,单击 I 、 V 按钮,此时电路图中显示电路的静态工作电压与电流值,以下列图:3、双端输入是的基本特征上边的电路是双端输入的形式,能够利用上边的电路来剖析双端输入时的电路特征。

将剖析种类设为沟通扫描剖析AC Sweep。

选择 PSpice | New Simulation Profile 功能选项或单击按钮,翻开New Simulation对话框,在Name文本框中输入 AC,单击 Create 按钮,弹出 Simulation Settings-AC 对话框,设置以下:启动 PSpice A/D 仿真程序,显示空的 PSpice A/D 窗口,选择 Trace | Add Trace 命令,在 Add Trace 窗口中设置以下列图,即察看单端输出时的电压增益:V(OUT1)/ (V(VS+:+)-V(Vs-:+)) 。

PSPICE仿真讲解学习

P S P I C E仿真目录介绍: (3)新建PSpice仿真 (4)新建项目 (4)放置元器件并连接 (4)生成网表 (6)指定分析和仿真类型 (7)Simulation Profile设置: (8)开始仿真 (8)参量扫描 (11)Pspice模型相关 (13)PSpice模型选择 (13)查看PSpice模型 (13)PSpice模型的建立 (14)介绍:PSpice是一种强大的通用模拟混合模式电路仿真器,可以用于验证电路设计并且预知电路行为,这对于集成电路特别重要。

PSpice可以进行各种类型的电路分析。

最重要的有:●非线性直流分析:计算直流传递曲线。

●非线性瞬态和傅里叶分析:在打信号时计算作为时间函数的电压和电流;傅里叶分析给出频谱。

●线性交流分析:计算作为频率函数的输出,并产生波特图。

●噪声分析●参量分析●蒙特卡洛分析PSpice有标准元件的模拟和数字电路库(例如:NAND,NOR,触发器,多选器,FPGA,PLDs和许多数字元件)分析都可以在不同温度下进行。

默认温度为300K电路可以包含下面的元件:●Independent and dependent voltage and current sources 独立和非独立的电压、电流源●Resistors 电阻●Capacitors 电容●Inductors 电感●Mutual inductors 互感器●Transmission lines 传输线●Operational amplifiers 运算放大器●Switches 开关●Diodes 二极管●Bipolar transistors 双极型晶体管●MOS transistors 金属氧化物场效应晶体管●JFET 结型场效应晶体管●MESFET 金属半导体场效应晶体管●Digital gates 数字门●其他元件 (见用户手册)。

新建PSpice仿真新建项目如图 1所示,打开OrCAD Capture CIS Lite Edition,创建新项目:File > New > project。

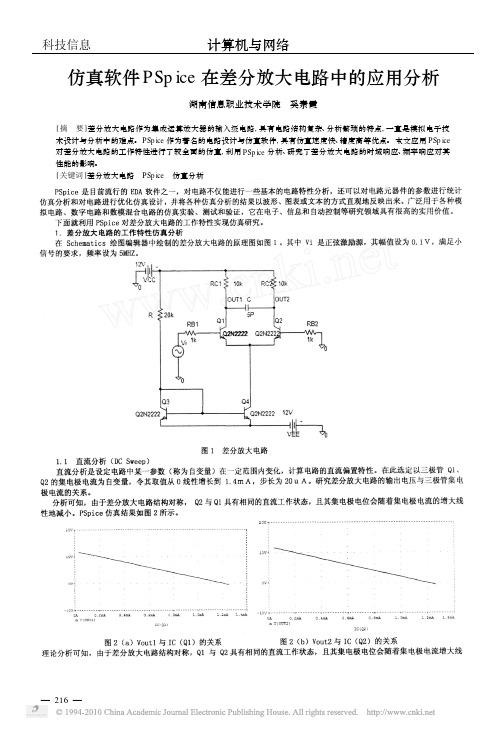

仿真软件PSpice在差分放大电路中的应用分析

仿真软件PSp ice在差分放大电路中的应用分析

湖南信息职业技术学院 奚素霞

[摘 要]差分放大电路作为集成运算放大器的输入级电路,具有电路结构复杂、分析繁琐的特点,一直是模拟电子技术设计与分析中的难点。

PSp ice作为著名的电路设计与仿真软件,具有仿真速度快、精度高等优点。

本文应用PSp ice 对差分放大电路的工作特性进行了较全面的仿真,利用PSp ice分析、研究了差分放大电路的时域响应、频率响应对其性能的影响。

[关键词]差分放大电路 PSp ice 仿真分析

—

—

2

6

1

—712—。

Pspice电路分析的基本概念

Pspice电路分析的基本概念关于Pspice电路分析的基本概念PSPICE是由SPICE(Simulation Program with Integrated Circuit Emphasis)发展而来的用于微机系列的通用电路分析程序。

下面yjbys店铺为大家准备了关于Pspice电路分析的基本概念,欢迎阅读。

1、直流分析:主要是对电路中的非线性大信号进行的分析,它是针对电路中直流偏压值因某一参数(电源、元件参数等)的改变所做的分析,直流分析是交流分析时确定小信号线性模型参数和瞬态分析之前确定初始值所需的分析。

主要内容:各节点电压值、各环路电流值等。

2、交流分析:主要是对电路中交流小信号进行的分析,此时半导体均采用其特定模型(如线性模型等)。

它是针对电路性能因信号频率、幅值的改变而变动所做的分析,它能够获得电路的幅频响应和相频响应以及转移导纳等特性参数。

3、参数分析:参数分析就是针对电路中的某一参数在一定的范围内作调整,根据分析期望得到这一参数的最佳值。

主要用于电路中参数不确定的情况,依据此分析做最优参数确定。

4、瞬态分析:使用Pspice软件可对大信号非线性电子电路进行瞬态分析,也就是求电路的时域响应,它可在给定激励信号情况下,求电路输出的时间相应、延迟特性;也可在没有任何激励信号的情况下,求振荡信号、振荡周期等。

瞬态分析运用最多,也最复杂,而且也是计算机资源耗费最高的部分。

5、最坏情况分析:属容差分析,是指电路中的元件参数在其容差域边界点上取某种组合时所引起的电路性能的'最大偏差。

最坏情况分析就是在给定电路元器件参数容差的情况下,估算出电路性能相对标称值时的最大偏差。

如果存在最大偏差时都能满足设计要求,那当然就是最佳方案。

WCase分析是一种统计分析。

6、蒙特卡洛分析:属容差分析,此分析使用统计模拟方法,在给定电路元件参数容差的统计分布规律的情况下,用一组伪随机数求得元器件参数的随机抽样序列,估算出电路性能的统计分布规律,如电路性能的中心值、方差,以及电路合格率、成本等等。

PSPice相关17.差分电路仿真

实验3.1.3 差分放大电路仿真分析

1. 输入编辑电路图 2. 仿真分析静态工作点和电压传输特性 3. 仿真差模电压放大倍数和差模输入电阻 4. 分析共模电压放大倍数和共模输入电阻 5. 分析单端输入时的vO1、vO2、vO、vE波形 6. 分析双端输入时的vO1、vO2、vO、vE波形

vO2、vO、vE的波形,并写出其表达式。

实验内容

1. 输入编辑电路图

▪ 设置合适的元件和信号源参数

实验内容

2. 仿真分析静态工作点和电压传输特性

▪ 将输入方式改接为单端输入;

▪ 设置直流扫描分析,以Vi为扫描 对象;

实验说明 查看分析设置

▪ 分析差分放大电路的静态工作点 IC1Q、VC1Q、VC2Q、VEQ;

5. 分析单端输入时的vO1、vO2、vO、vE波形

▪ 将输入方式改接为单端输入 (取 vI1 10 sin t mV)

▪ 设置瞬态分析;

▪ 查看vO1、vO2、vO、vE的波形; ▪ 注意它们的相位和大小。

实验说明 查看分析设置

查看仿真结果

实验内容

6. 分析双端输入时的vO1、vO2、vO、vE波形

返回

共模特性仿真分析设置 交流分析

瞬态分析

返回

共模特性(out1端输出时频率特性)

共模特性(out2端输出时频率特性)

共模特性(双端输出时频率特性)

返回

共模输入电阻

返回

共模特性仿真(输入输出电压相位关系)

返回

单端输入仿真分析设置

返回

单端输入时电压波形

返回

双端输入仿真分析设置

返回

双端输入时电压波形

直流扫描分析设置

返回

用PSPICE进行电路分析

第三节 PSPICE电路分析功能简介

这一节中我们将着重介绍PSPICE的主要 分析功能,在PSPICE输入语句中,通常用 以 “·” 开 头 的 语 句 描 述电路分析类型, 电路元器件模型和一些分析控制命令。在 PSPICE的所有分析类型中,直流、交流小 信号和瞬态分析最重要的,最常用的三大分 析功能, 以它们为主线对多数分析与控制 命令进行分组有利于了解这些语句的应用。

2.2.1 电路的输入语句和格式 PSPICE的文本输入任务是构造一个文本输入文件,文件名后缀 为*· CIR,它有如下六种类型的语句: <1>电路的标题语句 <2>电路的描述语句 电路元器件、 元器件模型、电源和信号源 Ex1 lowpass filter VIN 6 0 sin(0 10 1khz) R1 6 5 50 C1 5 0 3.18uf L1 5 2 15.9MH C2 2 0 3.18UF R2 2 0 50 · TRAN 10US 3MS · PLOT TRAN V(2) V(6) · PROBE · END

Spice家族中以metesoftware公司的Hspice和microsim 公司推出的Pspice最为出名,Pspice是microsim公司与 1984年推出一个通用的电路分析程序,在输入和输出; 图形处理、算法的可靠性和收敛性、仿真的速度、模拟 功能扩展以及模型参数库和宏模型库等方面都有改善和 扩充。

第二节 PSPICE软件组成和输入输出方式简介

2.1 PSPICE8.0 软件基本组成

1.

PSpice8.0仿真教程

PSpice8.0仿真教程PSpice仿真电路的应⽤技巧应⽹友之约将Pspice8.0的⼀些基本使⽤⽅法提供给⼤家,我们共同探讨;希望对⼤家有所帮助,由于本⼈⽔平有限还望谅解,只当抛砖引⽟吧,不妥之处请予以指出。

⼀、先了解Pspice8.0的使⽤基本程序项1、Schematics:绘制、修改电路原理图⽣成*。

CIR⽂件,或打开已有的*。

CIR⽂件;调⽤电路分析程序进⾏分析,并可调⽤图形后处理程序(Probe)查看分析结果。

2、Pspice A/D:打开已有的⽂本⽂件(*。

CIR)进⾏⽂本规定的分析,分析结果存⼊*。

DAT ⽂件中。

Schematicscs程序项的菜单中有运⾏Psoice程序的命令。

3、Parts:元件编辑程序,新建或修改元件的特性,模型。

4、Probe:图象后处理,可观察分析结果的图形。

Schematicscs程序项的菜单中有运⾏Prode程序的命令5、Stmed(Stimlus Editor)⽤于建⽴独⽴信号激励源和修改已建⽴的激励源波形。

6、Optimizer:Psoice优化设置程序7、Texte dit:⽂本编辑器。

8、PCB:上⾯8项是Psoice的基本程序,他们之间是相互关联的,最主要的是Schematicscs项,使⽤绘图程序项Schematicscs绘制好电路原理图,设置好相关模拟运⾏参数就可以对所画电路原理图进⾏模拟仿真了。

⼆、绘制电路原理图绘制电路原理图是运⾏Pspice程序的第⼀项作业,使⽤绘图⼯具能很⽅便的进⾏原理图的绘制。

1、打开Schematicscs项Schematicscs项是pspice应⽤程序的主窗⼝,可调⽤其它5个基本程序项。

下⾯是Schematicscs窗⼝的界⾯,主要⼯具⽤途已标明在案图上。

2、绘图常⽤命令项:Schematicscs程序项窗⼝有11个常⽤命令项:1)FIile(⽂件)--------------------------------省略2)Edit(编辑)---------------------------------省略3)Draw(绘图)和窗⼝⼯具⼀样--------省略4)Navigate(导航)---------------------------省略5)View(查看)-------------------------------省略Options(任选项)给出绘图参数设置命令,⽤来设置显⽰和打印环境。

OrCADPspice仿真分析功能介绍全解

直流工作点分析(Bias Point) 瞬态分析 (Time Domain Transient) 直流扫描分析(DC Sweep) 交流扫描分析和噪声分析(AC Sweep/Noise Analysis) 参数扫描分析(Parametric Sweep) 温度分析(Temperature Sweep) 灵敏度分析(Sensitivity) 蒙特卡罗分析与最坏情况分析(Monte Carlo/Worst Case)

图1 分析类型设置

直流扫描分析 加载基本偏置点 保存基本偏置点 交流扫描分析 蒙特卡罗分析与 最坏情况分析 显示输出基本偏 置点的偏置信息 参数扫描分析 灵敏度分析 温度分析 传输特性分析

瞬态分析

1、直流工作点分析(Bias Point)

电子电路中通常含有非线性元件(如二极管、三极管),其参数 取决于工作点。这个工作点称做基本偏置点或静态工作点,因此 直流工作点分析也叫基本偏置点分析或静态工作点分析。 直流工作点分析是在电路中把电感看成短路、电容看成开路的 情况下,计算电路的静态工作点。 PSpice在进行直流扫描分析或传输特性分析时需计算出直流工 作点,以便计算非线性元件的小信号参数。

扫描变量类型

扫描方式

直流扫描分析的参数设置对话框

类别 扫 描 变 量 类 型 扫 描 方 式

参数名 Voltage Soure Temperater Current Soure Model Parameter Global Parameter Linear Octave 电压源 温度 电流源 模型参数 全局参数

瞬态分析的参数

3、直流扫描分析(DC Sweep)

直流扫描分析是指在指定的范围内,某一个(或两个)独立源或 其他电路元件参数步进变化时,计算电路直流输出变量的相应的 变化曲线。 直流扫描分析采取使设定电路中某一参数(称为自变量)在一定 范围内变化,然后对自变量的每一个取值,计算电路的直流偏置 特性(称为输出变量)的分析过程。 直流扫描分析允许独立电源或其他点参量按照指定规律变化, 从而实现电路特性的研究。

差分放大电路的pspice分析

差分放大电路的pspice分析摘要:差分放大电路作为集成运算放大器的输入级电路.具有电路结构复杂、分析繁琐的特点,一直是模拟电子技术设计与分析中的难点。

PSPICE作为著名的电路设计与仿真软件,具有仿真速度快、精度高等优点。

本文应用PSPICE对差分放大电路的工作特性进行了较全面的仿真,利用PSPICE分析、研究了差分放大电路的时域响应、频率响应以及温度对其性能的影响关键词:差分放大电路PSpice 仿真分析引言PSPICE (Personal Simulation Program with IC Emphasis)是目前流行的EDA软件之一,相较其它EDA设计分析软件,其最大优势在于世界各大著名电子器件公司为它提供了几万种模拟和数字元件模型,使PSPICE的仿真结果更加真实并且十分接近实际电路的分析结果。

PSPICE用于电路仿真时,以源程序或图形方式输入,能自动进行电路检查,生成图表,模拟和计算电路。

它不仅可以对模拟电子线路进行不同输入状态的时间响应、频率响应、噪声和其他性能的分析优化,以使设计电路达到最优的性能指标,还可以分析数字电子线路和模数混合电路。

典型差分放大电路在模拟集成电路中,集成运算放大器是应用极为广泛的一种。

集成运算放大器是一种具有高电压增益、高输入电阻和低输出电阻的多级直接耦合放大电路,它的输入级一般是由BJT、JFET或MOSFET组成的差分式放大电路,其工作原理是利用差分放大电路的对称性来提高整个电路的共模抑制比和其它方面的性能,从而有效地抑制零点漂移。

但是差分电路结构复杂、分析繁琐,特别是其对差模输入和共模输入信号有不同的分析方法,难于理解,因而一直是模拟电子技术中的难点。

图1是一个典型的差分放大电路,其中Q1与Q2是一对NPN型的BJT差分对管,型号为Q2N2222。

Q3与Q4组成镜像电流源,其电流大小基本恒定(约为VDD-VEE/R1)。

恒流源的作用是充当有源负载,即利用其具有很高的交流电阻的特点作为Q1与Q2的发射极电阻下面利用PSPICE对差分放大电路的工作特性进行仿真研究:差分放大电路的原理图如图1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

题目:分析差分放大电路的差模电压增益、共模电压增益和共模抑制比

绘制差分放大电路原理图如图所示,其中vs+和vs-为正弦源。

另存为chadong1.sch

一、分析双端输入时的差模电压增益

1.设置信号源的属性。

vs+,vs-为差分放大电路的信号源。

vs+的属性设置如下:

Vs-的属性设置如:

vs+的“AC”项设为10mv,vs-的“AC”项设为-10mv。

这样才能起到差模输入的作用。

2. 设置分析类型

3. Analysis→Simulate,调用Pspice A/D对电路进行仿真计算。

4.测得恒流源给出的静态电流为1.849mA,晶体管Q1和Q2的发射极电流相等,都为0.9246mA。

(思考为什么是相等的)

5. 在probe下,单击Trace→Add,在Trace Expression中输入要显示的变量。

若要观察单端输出时的差模电压增益,编辑表达式为:V(out1) / (V(Vs+:+)-V(Vs-:+));

若要观察双端输出时的差模电压增益,编辑表达式为:

(V(out1)-V(out2)) / (V(Vs+:+)-V(Vs-:+))。

得到结果如下:

6. 用游标测量,双端输出时的差模电压增益为100.68,单端输出时的差模电压增益为50.34.是双端输出时的一半(为什么)。

两条曲线的上限截止频率点都是3.3843Mhz。

二、分析双端输入时的共模电压增益

将原理图chadong1.sch打开,另存为chadong2.sch

1.设置信号源的属性。

vs+的属性设置不变。

Vs-的“AC”属性设置为10mv,使其和信号源vs+一样,这样就相当于在两个输入端加上了相同的信号,起到共模输入的作用。

2. 设置分析类型

3. Analysis Simulate,调用Pspice A/D对电路进行仿真计算。

4. 在probe下,单击Trace→Add,在Trace Expression中输入要显示的变量。

若要观察单端输出时的共模电压增益,编辑表达式为:V(out1) / V(Vs+:+);

若要观察双端输出时的共模电压增益,编辑表达式为:(V(out1)-V(out2)) / V(Vs+:+)。

得到结果如下:

5. 用游标测量,

双端输出时的共模电压增益为1.000E-30,(Pspice中用1.000E-30表示0),所以双端时的共模电压增益为0。

在中低频段的单端输出共模电压增益为0.000733,也已经非常小,说明单端输出情况下也具有良好的抑制共模信号的特性。

但随着频率的进一步增大,共模电压增益将会急剧增大,增加到一定程度后,将不会再有剧烈的增减,但是共模电压增益总是小于1。

三、分析差分放大电路的共模抑制比

第一步:打开chadong1.sch,作如下修改,以建立底层的电路图文件:

1. 将其另存为x1.sch。

2. 删除信号源vs+和vs-。

将电阻RS1和RS2移到合适位置,并设置其阻值为1000g(Pspice中不允许有悬空的节点,当某些节点确实要悬空时,就需要在它与地之间接一个特别大的电阻)。

3.设置层次电路的接口。

Get New Part→IF IN 和IF OUT。

IF IN 表示输入端口。

IF OUT表示输出端口。

修改后的电路图如下所示:

4.保存,并将其另存为x2.sch。

第二步:设计高层次的电路。

1. 在schematics下,单击File→New新建立一个电路图文件。

并另存为CMMR.sch。

2. Draw→Block,取出两个块,分别命名为Cmod和Dmod,分别表示测量共模增益和差模

增益的块。

如图所示:

3. 双击Cmod→Browser→选择电路图文件x1.sch,

双击Dmod→Browser→选择电路图文件x2.sch。

这样使高层次电路图中的各个模块与低层次的电路图文件连接了起来。

如图所示:

4. 放置两个正弦源作为信号源。

最后绘制好的测量差分放大电路共模抑制比的高层次电路原理图如图所示:

正弦源v1的属性设置如下:

正弦源v2的属性设置如下:

5. 设置分析类型

6. Analysis →Simulate ,调用Pspice A/D 对电路进行仿真计算。

7. 在probe 下,单击Trace →Add ,在Trace Expression 中输入要显示的变量。

共模抑制比的表达式为vc

V D

V C

V D A A A A lg

20lg

20lg

20-=,所以编辑表达式为:

DB(V(Dmod:out+)/(V(Dmod:vin+)-V(Dmod:vin-)))- DB(V(Cmod:out+)/V(Cmod:vin+)) 得到仿真结果图如下:

8. 利用游标测得在中低频段共模抑制比为96.9DB 。

上限截止频率为37.832kHz 。