基于模拟集成电路BIST的ARMA模块设计

深亚微米CMOS模拟集成电路设计

中 国科技 售息 2 0 1 4 年凳 0 6 期 ・ C HI N A S C I E N C E AND T E C H N OL O G Y I N F O R MA T I ON Ma r . 2 0 1 4

深亚微米C M O S 模拟集成 电路设计

运 行频率 ( k } { z ) 作 者:[ 美] B a n g - S u p S o n g著 刘力源 译

图8原边 电源V A 值需求曲线 理论上说 ,系统原边的 电源供给VA 值和传输给负载 的功率一致 。图8 是负载2 0 k VA 时候随着频率的变化对原

年 任厄 巴纳伊利诺伊大学电子和计 算机工程系 以及协同科 学 实验室 ( C o o r d i n a t e d S c i nc e e L a b o r a t o r y )教授。1 9 9 9 年 ,进入加 州大学圣地亚哥分校 电子和计算机 工程 系 ,被授予无线通信领 域C h a r l e s L e e P o we l l 讲席教授职位。

T r a n s a c t i o n s o n I n d u s t r y A p p l i c a t i o n s ,2 0 0 0 ,3 6 ( 2 ) :4 4 4 - 4 5 1 .

[ 3 ] J . M .B a r n a r d ,J . A .g e r r e i r a , J .D . V a n W y k .S l i d i n g t r a n s f o r m e r s

国防科学研究所 ( A g e n c y f o r D e f e n s e D e v e l o p m e n t ,K o r e a )。 1 9 8 3 年至1 9 8 6 年 供职于新泽西州默里 山AT a T 贝尔实验室 ,同 时任新泽西州罗格斯大学 电子工程系访问学者 。1 9 8 6 年至1 9 9 9

改进的基于STUMPS架构的BIST电路设计

1 1 S U S基本 结构 . T MP

S TUM P E 0 S l Te t g Usn M I R n S 0 ]( ef s i ig , - n S ad

U dr et , n e s)还有做签章分析用的多输入特征寄存 T

器 MIR( l peIp t in tr gse 对测试 S Mut l n u g aueRe i ) i S t

结果 做压 缩处 理 。 S UMP T S的测试 流程 为 : 由 L S 先 F R产 生长 度

P r l R G) a l l S 结合 了 内建 自测 试 BS B i ae S IT( u dI l n SlT s) Sa et e et和 cnT s 两种测试电路 的优点 , f 常被 用来测试大型电路的测试架构 。其主要结构如 图 1

所 示 : 用 线 性 反 馈 移 位 寄 存 器 L S Lna 采 F R( ier

为 I的测试 向量 , 中 I为最长扫描链 Sa- a 其 cnc i hn 的长 度 , 用测 试 向量一 位一 位 的填满 整个 扫描链 , 并 对于较短 的扫描链 , 超过其长度 的测试 向量直接送 MIR做 特征 字分 析 ; 后启 动 测试 , 扫 描链 中的 S 然 将 测试向量送 人 C T进行测试 ; U 最后将 测试 结果传

回扫 描链 , 由扫 描 链 将结 果 送 入 MIR做 特 征 分 再 S

析。

F e-akS i ei e) edb c hf R g tr组成 的伪随机 向量生成 t s

得 了令人满意的结果。

关键词 : 可测性设计 ; 内建 自测 试; s P rCo k 测试 向量压缩 Tet e- lc ; - 中图分类号 : 4 7 TN 0

基于march c-算法的sram bist电路的设计

基于march c-算法的sram bist电路的设计SRAM BIST(Built-In Self-Test)电路是在静态随机存储器(SRAM)中集成的一个用于自测试的电路。

它可以在不需要外部测试设备的情况下对SRAM进行测试和诊断。

在设计SRAM BIST电路时,可以采用March C算法。

March C算法是SRAM 测试中经常使用的一种算法,它可以实现全面的SRAM测试和故障诊断。

以下是基于March C算法设计SRAM BIST电路的步骤:

1.确定SRAM的大小和位宽。

这将决定BIST电路的复杂度和测试时间。

2.根据SRAM的大小和位宽,设计SRAM测试模式生成器。

该模块生成March C测试序列,包括读取、写入和比较操作。

3.设计比较器模块,用于比较读取的SRAM数据和预期结果。

比较器可以使用位宽和诊断能力进行自定义。

4.设计控制器模块,用于控制测试模式和测试结果的生成。

该模块还可以包括故障诊断和报告功能。

5.验证SRAM BIST电路设计的正确性,并进行仿真和模拟。

6.将SRAM BIST电路集成到目标系统中进行测试。

总的来说,基于March C算法的SRAM BIST电路设计需要进行多方面的考虑和测试,以确保其正确性和可靠性。

基于DSP+ARM的双核低压智能断路器控制器系统设计研究

基于DSP+ARM的双核低压智能断路器控制器系统设计研究任瑾;倪元相;龙小丽;唐东成【摘要】为了满足智能电网的发展需求,设计了一种由DSP和ARM组成的双核控制器结构的低压智能断路器控制系统.对新型智能控制器的总体结构、硬件组成、测量保护算法、控制程序等进行介绍.针对采用傅里叶算法时衰减的直流分量会对计算的电力参数引入误差,提出采用改进的傅里叶测量算法进行修正,进一步提高电力参数的准确性,并根据三段电流保护特性原理对系统进行保护控制.实验证明:所提出的方法能有效提高计算参数的精度,系统在实现基本的智能保护功能外,还可以对低压配电系统的状态进行网络化的实时监测,提高智能断路器的可靠性,具有较好的实用性.【期刊名称】《现代机械》【年(卷),期】2017(000)003【总页数】5页(P90-94)【关键词】DSP;ARM;双核控制器;智能断路器;改进的傅里叶算法;三段电流保护【作者】任瑾;倪元相;龙小丽;唐东成【作者单位】广东理工学院,广东肇庆526100;广东理工学院,广东肇庆526100;广东理工学院,广东肇庆526100;广东理工学院,广东肇庆526100【正文语种】中文【中图分类】TM561低压断路器作为一种重要的开关装置直接连接着用电终端,在电力系统中主要用于线路的接通和分断,是必不可少的开关电器。

整个线路能否安全稳定运行直接取决于断路器功能和性能的好坏[1]。

在智能电网发展的大背景下出现了很多新型保护理念和方案,对低压电网中的开关设备提出了较高的智能化要求,这使得对低压智能断路器控制器系统的研究设计十分必要[2]。

低压智能断路器的核心技术在于研制具有线路保护功能、满足电力行业通信规约和可靠性高的智能控制器。

本文所研究设计的低压智能断路器控制器系统,除了具备一般断路器对线路基本的三段保护功能外,还具备了对线路的相关数据进行实时监测、保护功能的扩展、通信将数据传送给主控室等功能,以构成智能化的监控、保护和信息网络系统[3]。

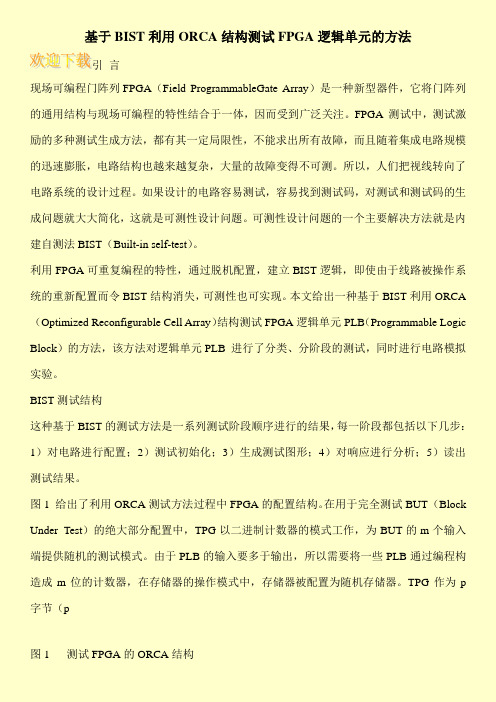

基于BIST利用ORCA结构测试FPGA逻辑单元的方法

基于BIST利用ORCA结构测试FPGA逻辑单元的方法引言现场可编程门阵列FPGA(Field ProgrammableGate Array)是一种新型器件,它将门阵列的通用结构与现场可编程的特性结合于一体,因而受到广泛关注。

FPGA 测试中,测试激励的多种测试生成方法,都有其一定局限性,不能求出所有故障,而且随着集成电路规模的迅速膨胀,电路结构也越来越复杂,大量的故障变得不可测。

所以,人们把视线转向了电路系统的设计过程。

如果设计的电路容易测试,容易找到测试码,对测试和测试码的生成问题就大大简化,这就是可测性设计问题。

可测性设计问题的一个主要解决方法就是内建自测法BIST(Built-in self-test)。

利用FPGA可重复编程的特性,通过脱机配置,建立BIST逻辑,即使由于线路被操作系统的重新配置而令BIST结构消失,可测性也可实现。

本文给出一种基于BIST利用ORCA (Optimized Reconfigurable Cell Array)结构测试FPGA逻辑单元PLB(Programmable Logic Block)的方法,该方法对逻辑单元PLB 进行了分类、分阶段的测试,同时进行电路模拟实验。

BIST测试结构这种基于BIST的测试方法是一系列测试阶段顺序进行的结果,每一阶段都包括以下几步:1)对电路进行配置;2)测试初始化;3)生成测试图形;4)对响应进行分析;5)读出测试结果。

图1 给出了利用ORCA测试方法过程中FPGA的配置结构。

在用于完全测试BUT (Block Under Test)的绝大部分配置中,TPG以二进制计数器的模式工作,为BUT的m个输入端提供随机的测试模式。

由于PLB的输入要多于输出,所以需要将一些PLB通过编程构造成m位的计数器,在存储器的操作模式中,存储器被配置为随机存储器。

TPG作为p 字节(p图1 测试FPGA的ORCA结构。

基于ARM微处理器的电力开关柜智能操控装置设计

器 A 9 S M7 。 其 片 内 除 具 有 A M7内 核 的 T 1 A A3 R

AR 7 D M T MI , 还 集 成 了 2 6 B FahR 外 5 K ls OM、

为 满 足配 电 要 求 ,操 控 装 置 需 要 根 据 开 关 柜 接 线

方 案 完 成 如 下 功 能 : )能 够 动 态 模 拟 出一 次 系统 1 图 ; )根 据 工 作 情 况 实 时 显 示 断 路 器 、手 车 及 接 2 地 开 关 位 置 、联 锁 状 态 ; )动 态 显 示 电压 、 电流 3 等 电力参 数 值 ; )断 路器 手 车 进 出控 制 准确 平 稳 ; 4 5 )能 够 进 行 断路 器 分 合 闸、接 地 开 关 分 合 闸 、紧 急 分 闸 、解 锁 操 作 及 柜 内照 明 ; )能 够 对 柜 内温 6 湿 度进 行 自动 调节 ; ) 够进 行就 地 / 7能 远程 操控 开

能 化 、集成 化 、网络化 方 向的快 速发 展 ,对 电力 开

关 设备 的操 作 与控制 ,也提 出 了许 多新的 、更高 的

2 操控装置的设计

21 装 置整体 结构 及工 作原 理 . 根 据 上 述 要 求 ,设 计 了结 构 如 图 1 示 操 控 所

系统 。

丽磊

露尔 电 流 传 藤 器 — —— —

钟

旭 ,李飞 燕

ZHO NG . l e . a Xu L i n F y

( 广东技术 师范 学院 电子与信息学 院,广州 5 6 5 1 6) 0

摘

要 ; 利用 3 位A M微处理器AT 1 AM7 及 多功 能电能计量专用芯片AD 7 5设 计了一种 电力开 2 R 9 S A3 E 78

模拟CMOS集成电路设计 拉扎维 ——复旦大学课件

参杂半导体

• 掺入三家获五价原子,提供一个载流子。

• N型:掺入五价元素,如磷(P)、砷(As),

提供一个电子,电子导电。

若:ND 是参杂浓度,D代表施主浓度 多子(电子)浓度: nn = ND

少子(空穴)浓度:

Pn

=

n

2 i

/

ND

• P型:掺入三价元素,如硼(B),

提供一个空穴,空穴导电。

若:NA 是参杂浓度,A代表施主浓度 多子(空穴)浓度: Pp = NA

参数化模块/单元 layout

宏模型 Matlab…

器件

器件特性

版图描述 design rule

器件模型 spice model

模拟集成电路的应用

• 模拟电路本质上是不可替代的

– 自然界是“模拟”的

• 集成传感器、显示驱动 • 模数和数模转换

– 数字信号经过传输后à模拟信号

• 无线和有线通讯 • 磁盘驱动

单极点低通Gm-C滤波器

Gm由偏置电流或电压确定,易受工艺、温度和电源 电压变化的影响

磁盘驱动器中的模块电路(2)

• 模数转换器(ADC)

– 6位ADC, – 由VCO提供采样时钟。采样频率由数字时钟恢复电路控

制。 – 偏移控制:采集63个比较器的失调电压,反馈到输入

端,抵消由此引起的失真。

• 数字信号处理

dQn dVR

=

ε 0ε si 2 ΦB

qN D + VR

1

2

=

Cj0

1

1

+

VR ΦB

2

C j0

=

ε

0ε si qN 2Φ B

D

2

= ε0εsi xn

基于高层次综合工具的BIST控制器设计

基于高层次综合工具的BIST控制器设计!蔡红艳",杜涛",孟祥刚2,李国峰+#梁科+#陈新伟4,5(1.天津市光电传感器与传感网络技术重点实验室,天津300350;2.天津市光电子薄膜器件与技术重点实验室,天津300350 ;3.南开大学1C设计与系统集成实验室,天津300350;4.工业机器人应用福建省高校工程研究中心,福建福州35010R;5.福州市机器人技术应用联合实验室,福建福州350108)摘要:存储器内建自测试(M B I S T)技术在存储器测试中具有广泛应用,针对传统寄存器传输级描述语言设计B IST 控制器的过程相对繁琐、专用E D A工具定义算法的灵活性差和电路结构固定等问题,提出采用高层次综合工具设计B I S T控制器的方法。

以S R A M为对象,采用C语言描述M A R C H算法,并采取端口分配、流水线优化和数组分割等优化方案完善设计。

最后借助F P G A平台验证评估了高层次综合工具输出的R T L级代码电路的功能可靠性和规模可控性。

相对于传统的两种方法,摆脱了算法实现和电路结构设计的局限性,缩短了算法实现周期。

关键词!B I S T控制器;高层次综合;M A R C H算法中图分类号:T N432 文献标识码:A D0I :10.16157/j.issn.0258-7998.174735中文引用格式:蔡红艳,杜涛,盂祥刚,等.基于高层次综合工具的BIST控制器设计[J].电子技术应用,2018,44(8):27-30.英文弓I用格式:Cai Hongyan,Du Tao,Meng Xianggang,et al. BIST controller design with high - level synthesis[J]. Application of Electronic Technique,2018,44(8) :27-30.BIST controller design with high-level synthesisCai Hongyan1,Du Tao1,Meng Xianggang2,Li Guofeng3,Liang K e3,Chen Xinwei4,5(1.Tianjin Key Laboratory of Optoelectronic Sensor and Sensing Network Technology,Tianjin 300350,China ;2.Tianjin Key Laboratory of Photo-electronics Thin Film Devices and Technique,Tianjin 300350,China ;3. Laboratory of Integrated Circuit and System Integration,Nankai University,Tianjin 300350,China ;4.Fujian Provincial Key Laboratory of Information Processing and Intelligent Control,Fuzhou 350108,China;5.Fuzhou Joint Laboratory of Robot Technology Application,Fuzhou 350108,China)Abstract :MBIST(Memory Built-In Self-Test) technology has extensive application in the memory test. In view of the traditional BIST controller register transfer level description language design process is relatively complicated, special flexibility EDA tools to define algorithm flexibility is poor, and the circuit structure is fixed, this paper proposes the use of high -level synthesis tools BIST controller design method. This paper takes SRAM as the object, describes the MARCH algorithm in C language, and uses port allocation, pipeline optimization and array segmentation to optimize the design. Finally, with the tools of the FPGA platform it verifies and evaluates the function reliability and scle controllability of the high-level synthesis synthesized RTL code level circuit. Compared with the two traditional methods, the limitation of algorithm implementation and circuit structure is eliminated, and the implementation period of the algorithm is reduced.Key words :BIST controller ; high level synthesis ; MARCH algorithm〇引言随着集成电路复杂度的不断提升,嵌入式存储器测试面临着很大的挑战。

哈尔滨工业大学模拟集成电路课程设计

一、功能描述设计二级运算放大器,采用电阻和电容进行补偿。

其中负载电容C L=10pF。

运算放大器满足如下要求:A vo≥3000,增益带宽积GBW≥5MHz,SR>10V/μs,相位裕度PM达到60°,输入共模范围(ICMR)为 1.5~4.5V,输出摆幅范围为0.5~4.5V,P diss≤2mW。

假定已知NMOS参数为。

PMOS管参数为。

二、电路设计1.电路设计过程(1)电路图图1总体电路图(2)电路设计过程2.仿真验证进入目录training/ic/spice_labs,启动cadence环境平台,新建two_stage_amp的cellview,按照之前的电路绘制要求放置mos管(mos元件选择chrt35dg_SiGe中的nmos5p0、pmos5p0),设置宽长比。

放置其他元件并连线,检查无误并保存。

电路绘制完成后建立电路symbol,确认无误后保存。

电路如图1所示,symbol如图2所示。

图2电路图symbol(1)采用闭环仿开环的方式对运放进行直流、交流、瞬态以及噪声分析。

建立一个仿真电路图,命名为cut_two_stage_amp,电路图结构如下图所示。

为了便于对变量的值进行控制和修改,图中的变量都没有进行赋值,而是在Analog Design Environment中进行统一赋值,便于进行电路调试。

电路绘制完成后,打开Analog Design Environment,设置变量值和仿真参数,仿真需要设置四项、分别为直流、交流、瞬态和noise。

设置完成后的ADE如图4所示(只显示进行设置的部分)。

图4闭环仿开环ADE①直流仿真对电路运行直流仿真,使用calculator的OP功能查看电路中各个器件工作点,使用VDC查看输出电压值,直流仿真输出结果如图5所示。

图5直流仿真结果可以看出,运放中的mos管均满足饱和区条件,处于饱和区,静态功耗1.39mW,满足设计要求,当输入为2.5V时,输出也约为2.5V。

基于低功耗的BIST测试生成结构优化设计

基于低功耗的BIST测试生成结构优化设计姚丽婷;谈恩民【摘要】针对内建自测试(Built-In Self-Test,BIST)技术的伪随机测试生成具有测试时间过长,测试功耗过高的缺点,严重影响测试效率等问题,提出一种低功耗测试生成方案,该方案是基于线性反馈移位寄存器(LFSR)设计的一种低功耗测试序列生成结构--LP-TPG(Low Power Test Pattern Generator),由于CMOS电路的测试功耗主要由电路节点的翻转引起,所以对LFSR结构进行改进,在相邻向量间插入向量,这样在保证原序列随机特性的情况下,减少被测电路输入端的跳变,以ISCAS'8585基准电路作为验证对象,组合电路并发故障仿真工具fsim,可得到平均功耗和峰值功耗的降低,从而达到降低功耗的效果.验证结果表明,该设计在保证故障覆盖率的同时,有效地降低了测试功耗,缩短了测试序列的长度,具有一定的实用性.【期刊名称】《电子设计工程》【年(卷),期】2010(018)008【总页数】4页(P71-74)【关键词】线性反馈移位寄存器;LP-TPG;低功耗;平均功耗;峰值功耗【作者】姚丽婷;谈恩民【作者单位】桂林电子科技大学电子,工程学院,广西,桂林,541004;桂林电子科技大学电子,工程学院,广西,桂林,541004【正文语种】中文【中图分类】TN47现今的SOC测试设计中,面临着许多问题,尤其是在降低功耗方面。

由于在测试模式下,功耗消耗比正常模式下高很多[1],为了解决测试功耗问题,许多学者从许多不同的角度进行了各种改进尝试。

在VLSI电路设计中,低功耗问题已成为测试问题的首选。

在电路测试过程中由于测试向量的伪随机特性导致测试效率随测试向量的增加迅速下降,要达到一定的故障覆盖率必须需要产生很长的测试向量集,测试向量的伪随机特性和无效测试向量(对故障覆盖率没有贡献的测试向量)导致测试功耗增加。

因此,在测试模式下电路的功耗要比正常工作模式下要高很多,可以达到两倍以上。

基于IGBT技术风电变流器Crowbar电路设计

在风力发电技术较为发达的一些国家,如丹麦、德国等陆续制定了新的电网运行准则,要求风力发电系统具有一定的低电压穿越能力(1ow voltage ride—through,LVRT),我国颁布的《国家电网公司风电场接入电网技术规定》对风力发电低电压穿越的能力也做了明确规定[2]。

图1-1国家电网公司对低电压穿越的规定

This article makes a study based on wind power converter circuit protection device-crowbar, with the IGBT used as the main switching devices in crowbar circuit. The article detailedly analyzed the performance characteristics of the IGBT and designed the driver of IGBT and protection circuit. Based on theState Grid Corporation’s requirement of wind power grid integration and when voltage drop the DFIG and direct drive wind power system, the work process and methods,the paper designed the direct-drive crowbar circurt and double-fed crowbar circuit. Thes paper also took the 1.5MW doubly-fed converter and 850KW full power converter for an example to make a design of the drive circuit and protection circuit,with main switching device selected.Results of simulation and verification are analyzed in paper. Thesimulationresultsshow that the designed of Crowbar not only can protect the converter better,but also do a good work with the function of Low voltage ride through during the voltage drop.

基于折叠集的混合模式BIST的低功耗设计

基于折叠集的混合模式BIST的低功耗设计

陈卫兵

【期刊名称】《电子质量》

【年(卷),期】2005(000)003

【摘要】文章提出了一种基于折叠集的混合模式BIST低功耗设计方案,该设计方案通过对混合模式BIST的优化设计,得到伪单输入跳变的测试向量集,从而达到降低待测电路功耗的目的.

【总页数】3页(P8-10)

【作者】陈卫兵

【作者单位】合肥工业大学计算机与信息学院,合肥,230009;阜阳师范学院物理系,阜阳,236032

【正文语种】中文

【中图分类】TP302

【相关文献】

1.一种基于扫描结构的混合模式BIST的低功耗设计 [J], 陈卫兵

2.一种新型混合模式BIST的低功耗设计 [J], 赵明;陈卫兵

3.基于折叠集合的确定模式BIST的低功耗设计 [J], 谈恩民;梁晓琳;刘建军

4.基于折叠重排的低功耗BIST技术研究 [J], 谈恩民;詹琰;刘建军

5.一种混合模式BIST的低功耗设计 [J], 陈卫兵;赵明

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的板级BIST设计和实现策略

基于FPGA的板级BIST设计和实现策略

杜影;赵文彦;安佰岳

【期刊名称】《计算机测量与控制》

【年(卷),期】2008(16)3

【摘要】为解决复杂电路板的测试问题,边界扫描、内建自测试等可测性设计技术相继发展,针对目前板级可测性设计发展状况,提出了基于FPGA的板级BIST设计策略;通过阐述存储器模块、逻辑模块和模拟模块三大部分的BIST设计,说明了基于FPGA进行板级模块BIST设计的灵活性和优势;最后,给出了在FPGA内构建BIST控制器的方法,并介绍了FPGA自测试的实现以及在板级设计过程中要考虑的问题.

【总页数】3页(P389-391)

【作者】杜影;赵文彦;安佰岳

【作者单位】北京航天测控技术开发公司,北京,100037;北京航天测控技术开发公司,北京,100037;北京航天测控技术开发公司,北京,100037

【正文语种】中文

【中图分类】TP274

【相关文献】

1.板级SRAM的内建自测试(BIST)设计 [J], 张勇;谈恩民

2.基于边界扫描技术的板级内测试方案及实现策略 [J], 刘冠军;黎琼炜

3.基于FPGA的RFID板级标签设计与实现 [J], 邓方东;谢泽明;伍继雄

4.边界扫描环境下的板级互连测试及其BIST实现 [J], 钟波;孟晓风;季宏;陈晓梅

5.FPGA板级自动化仿真测试环境框架设计 [J], 高虎;郑军;田曾昊

因版权原因,仅展示原文概要,查看原文内容请购买。

一种实现数模混合电路中的DAC测试的BIST结构

一种实现数模混合电路中的DAC测试的BIST结构

唐玉兰;陶伟;于宗光

【期刊名称】《电子器件》

【年(卷),期】2006(029)001

【摘要】由于超大规模集成电路技术的快速进步,测试数模混合电路变得越来越困难.针对DAC的测试问题,采用了一种内建自测试(BIST)的测试结构,用模拟加法器把电压测量转换成时间测量的方法,分析并给出了如何利用该结构计算DAC的静态参数.利用该方法,既可以快速得到DAC的静态参数,又提高了测试精度,使得测试电路简单、紧凑和有效.

【总页数】4页(P231-234)

【作者】唐玉兰;陶伟;于宗光

【作者单位】江南大学信息工程学院,江苏,无锡,214122;江南大学信息工程学院,江苏,无锡,214122;江南大学信息工程学院,江苏,无锡,214122;中国电子科技集团公司第五十八研究所,江苏,无锡,214122

【正文语种】中文

【中图分类】TN79.2

【相关文献】

1.电成像测井仪器中ADC-BIST测试方法研究及实现 [J], 赵建武;师奕兵;王志刚

2.定点DSP芯片的一种BIST结构设计与实现 [J], 张松;魏敬和;董玲;于宗光;须文波;薛忠杰

3.SOC中MBIST结构的设计与实现 [J], 黄玮

4.一种有效的双矢量测试BIST实现方案 [J], 张金林;陈朝阳;沈绪榜;张晨

5.一种实现数模混合电路中ADC测试的BIST结构 [J], 李杰;杨军;李锐;吴光林因版权原因,仅展示原文概要,查看原文内容请购买。

MADBIST系统中正弦信号发生器的设计与仿真

MADBIST系统中正弦信号发生器的设计与仿真

陈列;颜学龙

【期刊名称】《半导体技术》

【年(卷),期】2003(28)8

【摘要】在一个SoC系统中,数模混合内建自测试(MADBIST)的建立需要直接数字频率综合(DDFS)与Delta-sigma调制滤波两项技术的支持。

本文先就其原理进行分析,后用VHDL语言编程实现一个由二阶无损数字波形发生器与二阶Δ-Σ调制器合成的具体电路。

在得到良好仿真结果的同时,该设计降低硬件资源,减少量化噪声,具有一定的现实意义。

【总页数】5页(P18-21)

【关键词】MADBIST系统;正弦信号发生器;数模混合内建自测试;直接数字频率合成;△—Σ调制

【作者】陈列;颜学龙

【作者单位】桂林电子工业学院电子工程系

【正文语种】中文

【中图分类】TN74

【相关文献】

1.数字信号处理(DSP)系统的正弦波发生器 [J], 孙清

2.用单片机产生正弦波信号——基于单片机的CTCSS信号发生器设计 [J], 张政;刘奎武

3.基于Multisim的非正弦波信号发生器设计与仿真 [J], 张爱英;毛战华

4.基于DDS技术的数字移相正弦信号发生器的CPLD设计与仿真 [J], 雷能芳;苏变玲

5.电磁成像系统正弦信号发生器的设计 [J], 于长敏;申海

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘 要 :针对模拟集成 电路在线测试困难的特点 ,本文基于B S 结构对模 拟集 成电路 的测试提 出了一种新 的测 IT 试方案 ,这种算法在测试 电路 中易于实现 ,并且容 易嵌入到待测芯片 中,为模拟集成 电路可测试性设计提 出 了一种新的测试结构和测试算法。 关键词 :模拟集 成电路 ;B S IT;A MA R 模块

Ab t a tBae n t e d f c l c d i n l e ts n f n l g i tg a e ic i e me s r me th sb e sr c : s d o h i u t r e n o — i e t g o ao n e r t d cr u t n w a u e n a e n i f yi n i a ,a

pr po e t BI o s d wih ST tucur ,w h c c n be u e o nao ic tt si sr t e ih a s d f ra l g cr ui etng. Thi m eho c n be e sl m plm e t d i s t d a aiy i e n e n cr u ta e e be de n t et se ic i. ic i nd b m d di h e td cr u t

测试响应将 被串行地移 出触发器到达 芯片 引脚 ,从

而控制和观 测 电路状态 。扫描 测试将复 杂的时序 电

义上说 ,B S IT是把 “ 测试仪 ”做到 了电路 内部 ,因

为它既 要对待测 电路提供输入 的测试向量 ,又要对

路 测 试 问题 简化 为 较 易处 理 的组 合 电路 测 试 问题 , 其输 出的响应产生 的特 征与期望 的特 征比较 以给 出

个 片上 系统 ( O S C o在 航空 、移动通 信及 消 费

类电子产 品的 巨大市场需求 推动下 ,S C芯 片已经 O

由数字 S C转向包含了复杂数字信号处理器 、 O 存

储器 、高性能模拟和 混合信 号功能 以及实时操作 系 统 的混合信号 S 。随着芯片集成度的增 试带来 了新 的困 O

数字部分常用的测试技术是扫描。它将时序

电路 中的触发器 改换 成扫描触发器并将扫描 触发器

串连成扫描链 ,在测试过程 中,测试激励从 测试设

备通道输人芯 片引脚 ,串行地移入各个 触发 器 ,然

后捕获 电路状 态 ,捕获到 的 电路状态 称为测试响应 , 的支持是 B S IT设 计要 考虑 的关键 问题 。从 某种 意

传 输率 、通道 时 钟稳 定 度 ,与 S C需求 之 间的 差 O 距越来越 大 。传统 的全扫 描结构 具有串行移位 时间

例如 ,它 的测 试向量产 生器 ( ae G nrt ,简 Ptm ee o t ar

称P G)只能提 供 预先设 计好 的测 试 向量序 列 ( 如 用伪随机序列发生器产生伪随机 的测试 向量序列 ) 。 BS IT的 P G是 一 个 自动 有 限状 态 机 ,它 除 了 时 钟 输 入 以外 没 有 其 他 外 部 输 入 。典 型 的 P G是

缩 短了测试 向量生成时 间 ,提 高了故 障覆 盖率 。随

着 S C规模和工作频 率迅速 增长 ,测试设备的测试 O

测试通过与否的结果 。所不 同的是 , 设计的这个 “ 测

试仪 ”专 门为这个待测 电路而工作 ,功能单一 固定 。

能 力 ,例如通道数 、通道 存储深 度 、高速通道数 据

中 国分 类 号 : 文献 标 识 码 :

D e i n fAR M A odul s d n s e hnol sg o m e ba e o bitt c ogy

^ ‘ ● ● ● ●

ot ana og nt gr t d i cui l i e a e cr t

Ke wo d : a g I tg ae r u t S AR M A d l y r s An l e r t d Ci i BIT; . o n c ; mo u e

0 引言

超深亚微米 ( DS )半导体技 术的进展 允许 V M 将一个复杂的 电子系统集成在单一芯 片上 ,即构成

一

难 。就数 字的可 测试性设计而 言 ,有扫描 测试 、边 界 扫描测 试 、内建 自测 试 (ul i sl t t B S ) bi—n e -e , IT t f s 和测试点插入 等。B S 术由于把测试激励源的生 IT技 成 电路嵌人被测 芯核 ,因此能够提供 真速 测试 ,并 且 具有测 试 引脚不 受 S C 引脚 数 限制等 优点 ,已 O 经越来越受 到人们的关注 。

j a i i gY ne g。 YuS a g a g u i n , a a fn , h o u n 2 Jx J n 。

(Mi olc o i C ne, o ee fnoma o n ier g Not ia iesyo eh ooy B in 1 c e t nc etrC n g fr t nE gnei , r Chn vrt f cn lg , e i r er oI i n h Un i T jg 10 4 ,hn ;2 e i stto A t— e ig eh oo , e i , 00 8 Chn) 0 14C ia B in I tue f uo T sn c n lg B in 10 8 , ia jgni t T y jg

21 o o年 2月 篦 2鞭

电 子 漏 试

ELEcT R0NI C T EST

F b. e 2o1 o No. 2

基于模拟集成 电路B S IT的A MA R 模块设计

鞠家欣 ’ 姜岩峰 。 , ,于韶光

( 北方工业大学信息工程学院微电子中心 , 1 北京 ,104 2 北京 自动测试技术研究所 北京 108 ) 001 008