16位模型机的设计

计算机硬件课程设计报告——拓展接口的复杂模型机设计

计算机硬件课程设计报告——拓展接口的复杂模型机设计学院:计算机科学与工程学院专业:计算机科学与技术班级:组员1:组员2:起止时间:目录一、实验目的 (3)二、实验内容 (3)三、实验思路 (3)四、实验原理 (3)五、实验步骤 (10)六、实验设计 (11)七、实验心得 (14)一、实验目的经过一系列硬件课程的学习及相关实验后,做一个综合的系统性的设计,这在硬件方面是一个提高,进一步培养实践能力。

二、实验内容搭建一台有拓展接口的8位模型机,指令系统要求有10条以上,其中包括运算类指令、传送类指令、控制转移类指令、输入输出指令、停机指令等。

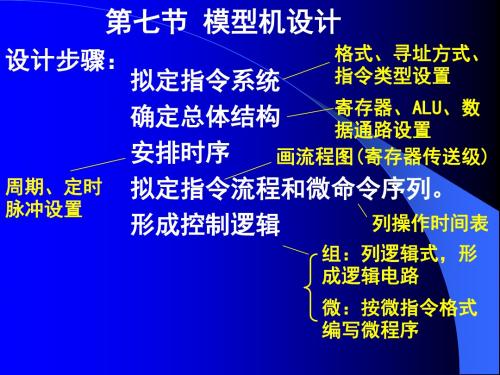

三、实验思路1、确定设计目标:确定所设计计算机的功能和用途。

2、确定指令系统:确定数据的表示格式、位数、指令的编码、类型、需要设计哪些指令及使用的寻址方式。

3、确定总体结构与数据通路:总体结构设计包含确定各部件设置以及它们之间的数据通路结构,列出各种信息传送路径以及实现这些传送所需要的微命令。

4、设计指令执行流程:数据通路确定后,就可以设计指令系统中每条指令的执行流程。

根据指令的复杂程度。

每条指令所需要的机器周期数。

对于微程序控制的计算机,根据总线结构,需要考虑哪些微操作可以安排在同一个微指令中。

5、确定微程序地址:根据后续微地址的形成方法,确定每条微程序地址及分支转移地址。

6、根据微指令格式,将微程序流程中的所有微操作进行二进制代码化,写入到控制存储器中的相应单元中。

7、组装、调试:在总装调试前,先按功能模块进行组装和分调,因为只有功能模块工作正常后,才能保证整机的运行正确。

四、实验原理1、指令系统及指令格式(1)数据格式8位。

(2)指令格式:指令系统应包括:算术逻辑运算指令、访存指令、控制转移指令、I/O指令、停机指令。

一般指令格式如下:O P-C O D E(4位)R S(2位)R D(2位)D A T A /A D D R (8位)其中R S 、R D 可以是R 0、R 1、R 2中任一个,它们的代码分别为00、01、10。

计算机组成原理课程设计报告_基本模型机的设计与实现

本次课程设计的任务是完成一个基本模型机的设计与实现。

设计经过综合运用了以前所学计算机原理的知识,依照设计要求和指导,实现了一个基本的模型计算机。

本模型机实现的功能有:IN(输入),OUT(输出),ADD(加法),SUB(减法),STA(存数),JMP(跳转)。

设计进行开始,在了解微程序的基本格式, 及各个字段值的作用后, 按微指令格式参照指令流程图,设计出程序以及微程序,将每条微指令代码化,译成二进制代码表,并将二进制代码转换为联机操作时的十六进制格式文件。

根据机器指令系统要求,设计微程序流程图及确定微地址。

设计的加法和减法中, 被加数和被减数都由调试人员输入, 而加数和减数都从存储器中读取. 最后上机调试,各个功能运行结果正确。

关键词:基本模型机;机器指令;微指令目录1、课程设计题目-----------------------------------------------12、实验设备---------------------------------------------------13、课程设计步骤-----------------------------------------------13.1、所设计计算机的功能和用途------------------------------13.2、指令系统----------------------------------------------23.3、总体结构与数据通路------------------------------------23.4、设计指令执行流程--------------------------------------33.5、微指令代码化------------------------------------------43.6、组装和调试----------------------------------------------54、课程设计总结-----------------------------------------------75、附录-----------------------------------------------------------------------------------8附录1:数据通路图----------------------------------------------------------8 附录2:微程序流程图--------------------------------------------------------9 附录3:实验接线图------------------------------------------------------------10 附录4:实验程序及微程序---------------------------------------------------11 附录5:参考文献(资料)-----------------------------------121、课程设计题目基本模型机的设计与实现2、实验设备TDN—CM++计算机组成原理教学实验系统一台,微机,虚拟软件,排线若干。

CPU-与简单模型机设计实验

评语: 课中检查完成的题号及题数:课后完成的题号与题数:成绩: 自评成绩: 85实验报告实验名称:CPU 与简单模型机设计实验日期:2015.11.17 班级: 2 学号:13 姓名:周小多一、实验目的:1. 掌握一个简单CPU 的组成原理。

2. 在掌握部件单元电路的基础上,进一步将其构造一台基本模型计算机。

3. 为其定义五条机器指令,编写相应的微程序,并上机调试掌握整机概念。

二、实验内容:1.要实现一个简单的CPU,并且在此CPU 的基础上,继续构建一个简单的模型计算机。

CPU 由运算器(ALU)、微程序控制器(MC)、通用寄存器(R0),指令寄存器(IR)、程序计数器(PC)和地址寄存器(AR)组成,如图2-1-1 所示。

这个CPU 在写入相应的微指令后,就具备了执行机器指令的功能,但是机器指令一般存放在主存当中,CPU 必须和主存挂接后,才有实际的意义,所以还需要在该CPU 的基础上增加一个主存和基本的输入输出部件,以构成一个简单的模型计算机。

2.本模型机和前面微程序控制器实验相比,新增加一条跳转指令JMP,共有五条指令:IN(输入)、ADD(二进制加法)、OUT(输出)、JMP(无条件转移),HLT(停机),其指令格式如下(高4位为操作码):助记符机器指令码说明IN 0010 0000 IN→R0ADD 0000 0000 R0 + R0→R0OUT 0011 0000 R0→OUTJMP addr 1100 0000 addr→ PCHLT 0101 0000 停机3. 设计一段机器程序,要求从IN 单元读入一个数据,存于R0,将R0 和自身相加,结果存于R0,再将R0 的值送OUT 单元显示。

根据要求可以得到如下程序,地址和内容均为二进制数。

地址内容助记符说明00000000 00100000 ; START: IN R0 从IN 单元读入数据送R000000001 00000000 ; ADD R0,R0R0 和自身相加,结果送R000000010 00110000 ; OUT R0R0 的值送OUT 单元显示00000011 11100000 ; JMP START跳转至00H 地址00000100 0000000000000101 01010000 ; HLT停机三、项目要求及分析:1. 试修改现有的指令系统,将加法指令的功能修改为R0的内容和某个存储单元的内容相加;增加存数、取数和减法三条机器指令,指令助记符分别为STA、LAD 和SUB,指令操作码分别为十六进制的60、70和80。

基本模型机的设计与实现

基本模型机的设计与实现1.设计目的1、在掌握部件单元电路实验的基础上,进一步将其组成系统构造一台基本模型计算机。

2、为其定义五条机器指令,并编写相应的微程序,具体上机调试,掌握整机软硬件组成概念。

2.设计内容2.1设计原理部件实验过程中,各部件单元的控制信号是人为模拟产生的,而本次实验将能在微程序控制下自动产生各部件单元控制信号,实现特定指令的功能。

这里,计算机数据通路的控制将由微程序控制器来完成,CPU从内存中取出一条机器指令到指令执行结束的一个指令周期全部由微指令组成的序列来完成,即一条机器指令对应一个微程序。

2.1.1有关微控制器部分的介绍微程序控制电路:微程序控制器的组成见图10,其中控制存储器采用3片2816的E2PROM,具有掉电保护功能,微命令寄存器18位,用两片8D触发器(74273)和一片4D(74175)触发器组成。

微地址寄存器6位,用三片正沿触发的双D触发器(7474)组成,它们带有清“0”端和预置端。

在不判别测试的情况下,T2时刻打入微地址寄存器的内容即为下一条微指令地址。

当T4时刻进行测试判别时,转移逻辑满足条件后输出的负脉冲通过强置端将某一触发器置为“1”状态,完成地址修改。

在该实验电路中设有一个编程开关(位于实验板右上方),它具有三种状态:PROM (编程)、READ(校验)、RUN(运行)。

当处于“编程状态”时,实验者可根据微地址和微指令格式将微指令二进制代码写入到控制存储器2816中。

当处于“校验状态”时,可以对写入控制存储器中的二进制代码进行验证,从而可以判断写入的二进制代码是否正确。

当处于“运行状态”时,只要给出微程序的入口微地址,则可根据微程序流程图自动执行微程序。

图中微地址寄存器输出端增加了一组三态门,目的是隔离触发器的输出,增加抗干扰能力,并用来驱动微地址显示灯。

微指令格式:上图为地址转移逻辑电其中UA5--UA0为6位的后续微地址,A,B,C为三个译码字段,分别由三个控制位译码出多个微命令。

16位全加器电路的设计与实1

16位全加器电路的设计与实现(课程设计)默认分类2010-06-29 11:07:45 阅读282 评论0 字号:大中小订阅四川理工学院课程设计任务书设计题目:采用门电路设计一个16位的全加器电路系别: 计算机学院专业: 计算机科学与技术08级6班指导教师: 朱文忠学生姓名: 杨世刚目录? 引言 (1)1、设计背景 (1)2、关键技术的介绍及设计分工 (1)? 设计过程 (2)1、设计目的 (2)2、设计的内容 (2)3、设计的组成原理分析 (3)? 硬件方案 (4)1、半加器原理 (4)2、全加器原理 (5)3、一位全加器 (7)4、四位先行进位加法器的逻辑设计 (8)5、十六位全加器的设计 (10)6、十六位全加器的基本原理 (10)7、真值表的建立 (11)8、十六位全加器的功能及电路图设计 (12)? 软件方案 (14)1、用VHDL编写代码验证 (14)? 可行性论证 (19)1、课程设计的可行性分析 (19)2、结果分析 (19)? 总结 (20)1、实验结论 (20)? 参考文献 (21)? 引言设计的背景:全加器的运用是相当的广泛的,像各种各样的CPU和某些模型机,然而对于快速正确的加法器的设计是相当的重要的,所以在这次课程设计我选择对全加器的设计与实现。

总的来说多位加法器的构成有两种方式:并行进位(又叫超前进位)和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。

并行进位的并行加法器又可以分为组内并行、组间串行的进位链和组内并行、组间并行的进位链。

通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

它们的目的就是要进位信号的产生尽可能的快,因此产生了二重进位链或更高重进位链,显然进位速度的提高是以硬件设计的复杂化为代价来实现的。

另外一个器件需要进一步的更新换代,在我们所学的知识领域里面,我们认为应该需要两个方面,一个是设计,有一个好的设计,它就像一种需求一样,即使这种设计在实际上暂时无法得到应用,但是,在一定时期以后,它是可以实现的。

简单模型机的微程序设计

微指令000001001110000000001010

执行的操作是:存储器CE有效,存储器读,LDAR,转微地址:0A

微指令000001001010000000001011

执行的操作是:存储器CE有效,存储器读,LDDR1,转微地址:0B

微指令000001110000101000000001

执行的操作是:算术:A,数码管LEDB有效,写LED,ALU→B,转微地址:01

异或指令XOR RD,RS:(RS)异或(RD)→(RD)

四.进度安排

共1.5周11天的时间,具体安排如下:

1~2天:对整个课程设计的内容做详细的讲解,并辅导学生完成课程设计指导书的学习,使其掌握和理解课程设计的核心内容;

3 ~5天:学生在机房学习熟悉课程设计所使用的仿真软件,并深入了解该仿真软件所实现 的模型机的指令系统(原有的5条指令)和微程序设计方法;

6~9天:在原有5条机器指令的基础上增加实现下述各功能的机器指令,试设计相应的机器指令的格式并改写原来的微程序使其可以运行所有的机器指令;

10~11天:根据自己设计的微程序系统写出相应的课程设计实验报告;

五.成绩评定

六.正文

一、模型机的CPU及系统硬件

基本模型机的CPU及系统硬件组成如图1所示

图1 模型机的CPU及系统硬件组成

课程设计报告

Autodesk Inventor设计的优势

Autodesk Inventor设计的优势Autodesk Inventor设计的优势(一)----重焕青春Autodesk的Inventor处理大型组装模型具有极佳的交互性能。

图示模型是加工汽车引擎部件的传输线的一部分,共包含3,100个组件。

Inventor在Pentium III 500工作站上加载该模型只需39秒。

Autodesk重焕青春我们经常抱怨CAD软件的缔造者不能及时创新产品取代业已过时的软件。

Autodesk打破了这个成规,于近日首次展出了Autodesk Inventor _ 第一个基于其旗舰产品AutoCAD的机械CAD软件产品。

AutoCAD的问世可以回溯到1981年。

代号为Rubicon的Autodesk Inventor是一种尺寸驱动的实体造型系统,它意在与Pro/Engineer、CATIA、Unigraphics、I-DEAS Master 系列、SolidWorks和Solid Edge等相似的产品进行竞争。

类似于这些程序,Inventor也使用结构化的技术,包括草绘二维界面轮廓以及拉伸、旋转和扫掠草图形成实体模型。

软件将单个零件组合起来形成产品部件,并且允许通过将实体模型投影到平面上创建零件或部件的工程图。

最初编写AutoCAD时,16位的个人计算机拥有很低的处理能力和很少的内存,程序员的精力集中在如何使CAD程序在16位的个人计算机上顺利运行等技术难题上。

在80年代早期,使计算机画直线或圆弧的算法优化都是一种挑战。

开发Inventor的Autodesk小组已经将注意力集中于如何使Inventor比竞争产品更简单和方便地使用。

用户界面使用Microsoft的窗口基本类创建工具按钮、菜单和带标签的次级窗口。

这意味着临时用户也可以不用研究手册就可以执行基本的操作。

Autodesk也致力于在实体和工程图中简化设计过程。

例如,在草图管理器中水平和垂直的约束被自动地应用。

重点章节例题作业汇总

1、(P68 3.14)求补码和1)X=0.11001,Y=-0.10111 2)X=0.10010,Y=0.110002、(P68 3.15)求补码差1)X=-0.01111,Y=0.00101 2)X=0.11011,Y=-0.100103、(第三章测试)设机器字长为8位(含1位符号位),X=115,Y=-24,用补码运算规则计算[X-Y]补并判断是否溢出。

4、(P68 3.18)已知x = 0.1010 y = -0.0110 求用补码一位乘求x • y5、(第三章测试)用补码一位乘(布斯公式法)计算[x×y]补。

设x=0.11011,y=-0.111016、(P68 3.19)x =– 0.10110,y = 0.11111,用加减交替原码一位除求[X/Y]原7、(第三章测试)设浮点数格式为:阶码5位(含1位阶符),尾数11位(含1位数符)。

写出-86.5所对应的尾数规格化的机器数。

要求如下:1)阶码和尾数均为原码。

2)阶码为移码,尾数为补码。

8、(第三章测试)设浮点数格式为:阶码4位(含1位阶符),尾数7位(含1位数符)。

按机器补码浮点运算步骤计算 [x-y]补x=2-011×0.101100,y=2-010×(-0.011100)9、见教材P68 3.21(1)1、(补充作业)用16K×16位的SRAM芯片构成32K×32位的存储器,试画出该存储器的组成逻辑图。

2、(补充作业)下图为由8片2114芯片构成的4K×8位的存储器,与8位的一个微处理器相连,2114芯片为1K×4位的SRAM芯片,问:1)每一组芯片组的地址范围和地址线数目2)4KB的RAM寻址范围是多少?3)存储器有没有地址重叠?3、见教材P86 4.6第五章1、(例题)某16位模型机,主存容量为64K字,采用单字长单地址指令,共有40种指令,试采用直接、立即、变址、相对四种寻址方式设计指令格式。

计算机组成原理实验指导书-CPTH

DJ-CPTH计算机组成原理实验系统实验指导阜阳师范学院计算机与信息学院2008年3月目录目录 (1)实验一认识实验装置 (2)实验二寄存器实验 (10)实验三运算器实验 (18)实验四数据输出和移位实验 (22)实验五存储器实验 (26)实验六uPC和PC 实验 (32)实验七微程序存储器uM实验 (37)实验八模型机综合实验一 (39)实验九模型机综合实验二 (46)实验十微程序设计实验 (55)实验十一扩展实验 (60)附录1:CPTH 集成开发环境使用 (63)附录2:指令/微指令表(insfile1.mic) (68)附录3:实验用芯片介绍 (79)实验一认识实验装置实验目的:了解实验仪的特点及组成;掌握实验仪键盘的使用。

实验器材:DJ-CPTH实验仪实验要求:1、认真填写预习报告,包括对实验仪器组成的理解、实验操作步骤等。

2、实验之后写出实验报告,包括实验过程中遇到的问题,解决方法,实验后的心得体会及对该次实验的建议与意见。

实验原理及步骤:一、DJ-CPTH特点1、采用总线结构总线结构的计算机具有结构清晰,扩展方便等优点。

DJ-CPTH实验系统使用三组总线即地址总线ABUS、数据总线DBUS、指令总线IBUS和控制信号,CPU、主存、外设和管理单片机等部件之间通过外部数据总线传输,CPU内部则通过内部数据总线传输信息。

各部件之间,通过三态缓冲器作接口连接,这样一方面增强总线驱动能力,另一方面在模型机停机时,三态门输出浮空,能保证不管模型机的CPU工作是否正常,管理单片机总能读/写主存或控存。

2、计算机功能模块化设计DJ-CPTH为实验者提供运算器模块ALU,众多寄存器模块(A,W,IA ,ST,MAR,R0…R3等),程序计数器模块PC,指令部件模块IR,主存模块EM,微程序控制模块〈控存〉uM,微地址计数器模块UPC,组合逻辑控制模块及I/O等控制模块。

各模块间的电源线、地线、地址总线和数据总线等已分别连通,模块内各芯片间数据通路也已连好,各模块的控制信号及必要的输出信号已被引出到主板插孔,供实验者按自己的设计进行连接。

体系结构课后习题答案

体系结构课后习题答案3.某模型机有10条指令I1~I10,它们的使⽤频度分别为0.3,0.24,0.16,0.12,0.07,0.04,0.03,0.02,0.01,0.01。

(1)计算采⽤等长操作码表⽰时的信息冗余量。

(2)要求操作码的平均长度最短,试设计操作码的编码,并计算所设计操作码的平均长度。

(3)只有⼆种码长,试设计平均码长最短的扩展操作码编码并计算平均码长。

(4)只有⼆种码长,试设计平均码长最短的等长扩展码编码并计算平均码长。

3.(1)采⽤等长操作码表⽰时的信息冗余量为33.5%。

(2)操作码的Huffman编码法如表2.2所⽰,此种编码的平均码长为2.7位。

表2.2 操作码的Huffman编码法、2-5扩展码和2-4等长扩展码编码法(3)操作码的2-5扩展码编码法如表2.2所⽰,此种编码的平均码长为2.9位。

(4)操作码的2-4等长扩展码编码法如表2.2所⽰,此种编码的平均码长为2.92位。

5.若某机设计有如下格式的指令:三地址指令12种,⼀地址指令254种,设指令字的长度为16位,每个地址码字段的位数均为4位。

若操作码的编码采⽤扩展操作码,问⼆地址指令最多可以设计多少种?5.⼆地址指令最多可以设计48种。

6.⼀台模型机共有9条指令I1~I9,各指令的使⽤频度分别为30%,20%,20%,10%,8%,6%,3%,2%,1%。

该模型机有8位和16位两种指令字长。

8位字长指令为寄存器-寄存器(R-R)⼆地址类型,16位字长指令为寄存器-存储器(R-M)⼆地址变址寻址类型。

(1)试设计有⼆种码长的扩展操作码,使其平均码长最短,并计算此种编码的平均码长。

(2)在(1)的基础上,该机允许使⽤多少个可编址的通⽤寄存器?(3)若采⽤通⽤寄存器作为变址寄存器,试设计该机的两种指令格式,并标出各字段的位数。

(4)计算变址寻址的偏移地址范围。

6.(1)操作码的2-5扩展码编码法如表2.3所⽰,此种编码的平均码长为2.9位。

RISC模型机的设计及实现

《计算机组成与系统结构》课程设计报告报告题目:RISC模型机的设计及实现作者所在系部:计算机科学与工程系作者所在专业:计算机科学与技术作者所在班级:0作者姓名:0指导教师姓名:0完成时间:0目录目录 (1)内容摘要 (2)关键词 (2)课程设计任务书 (3)第1章绪论 (4)1.1 设计地点 (4)1.2 设计目的 (4)1.3 设计内容 (4)1.4 实验的环境: (4)第2章基础知识 (5)2.1 概述 (5)2.2 主要技术要点 (6)2.2.1 ALU部件 (6)2.2.2. 存储体 (6)2.2.3 控制器 (6)第3章系统设计与实现 (7)3.1 模型机结构 (7)3.2 程序设计原理 (7)3.2.1 数据格式及指令格式 (7)3.2.2 指令系统 (8)3.3 机器指令设计 (9)3.4 联机实验 (10)3.4.1 实验连线 (10)3.4.2 实验步骤 (10)3.4.3 实验测试: (12)第4章实验总结 (13)参考资料 (13)内容摘要计算机系统是包括计算机硬件和软件的一个整体,两者不可分割,但处于不同的层次上。

计算机系统的层次结构模型中,第0层是硬件内核(逻辑线路),第1、2层是指令系统和实现该指令系统所采用的技术(组合逻辑技术、微程序控制技术、PLA控制技术),第3、4层为系统软件,第5层为应用软件,第6层是系统分析。

计算机组成原理涉及到的是第0、1、2这3层。

本次计算机组成原理的课程设计主要是实现一个较完整的模型机,在实验中了解,熟悉完整的单台计算机基本组成原理,掌握计算机中数据表示方法、运算方法、运算器的组成、控制器的实现、存储器子系统的结构与功能、输入/输出系统的工作原理与功能。

以及增强自己的动手能力。

课设主要依托组成原理实验室设备EL-JY-II来完成的,在实验当中利用了实验设备厂商开发的工具以及部分源程序代码。

在此说明。

在实验中我要感谢杨老师的辛勤付出,每天来到实验室指导我们进行实验,在此特别提出感谢。

计算机硬件课程设计(微程序)

1.指令系统及指令格式 1.指令系统及指令格式

指令系统应包括:算术逻辑运算指令、访存指令、控制转 移指令、I/O指令、停机指令。一般指令格式如下: 移指令、I/O指令、停机指 0

OP-CODE DATA / RS ADDR RD

指令系统如: 指令系统如: ADD RS,RD MOV DATA,RD MOV RS,[ADDR] JZ ADDR IN RD HALT 其中RS RD为R0、R1、R2中之一( 其中RS 、RD为R0、R1、R2中之一(为00,01,10) ,DATA为立即数,ADDR DATA为立即数,ADDR 为内存地址。

七、具体要讲的几个问题

1、指令格式、指令系统:讲各种指令格式,寻址方式 指令格式、指令系统:讲各种指令格式, 举例讲微操作流程, RS,RD: 2、举例讲微操作流程,如ADD RS,RD: 举例讲微指令编写: 3、举例讲微指令编写: 微程序的入口地址形成及微指令的后续地址: 4、微程序的入口地址形成及微指令的后续地址: 装载微程序的格式: 5、装载微程序的格式: 模型机的时序电路: 6、模型机的时序电路: 运行模型机:运行前先要复位( RESET或拨动CLR开关 或拨动CLR开关1 7、运行模型机:运行前先要复位(按RESET或拨动CLR开关1-0),按单微指令按钮进行单步调试 按单微指令按钮进行单步调试, 1),按单微指令按钮进行单步调试,按连续按钮进行连续运 行; 模型机电路图:双击CMPP20 在帮助中找到“ CMPP20, 8 、模型机电路图:双击CMPP20,在帮助中找到“复杂模型机 图” 9、模型机调度过程中常见问题及解决办法

寄存器地址译码电路

5.微程序装载格式 5.微程序装载格式

机器指令格式: 机器指令格式: $Pxxxx 微指令格式: 微指令格式: $Mxxxxxxxx

简单模型机实验报告

简单模型机实验报告篇一:模型机实验报告HUNAN UNIVERSITY课程实习报告题目:模型机学生姓名学生学号 XX0801328专业班级计算机科学与技术(3)班指导老师方恺晴完成日期 XX.5.28思考题:1. 给定一个复合运算式子以及指令码IR[7..5]与八位BUS总线对应情况。

要求写出七条指令新的指令码并写出复合运算执行mif文件。

修改模型机电路调试程序以实现复合运算。

例:已知A=55H,B=8AH,C=F0H;IR[7..5]对应BUS8,BUS1,BUS3;写出(Aplus/B)^(/(/CplusB))的mif文件,并在模拟机上实现。

答:模拟机电路修改如下:存储器预设指令重设:计算结果:(A+/B)^(/(/C+B))=42H2. Microcomputer.vhd代码中进程ct1,ct2,ct3,ct4功能划分依据是什么?ct1:微序列控制器下址跳转。

ct2:实现各种指令,主要集中在实现从存储器或者寄存器释放数据到总线上。

ct3:完成各种指令,从总线上装载数据到相应的存储器或者寄存器中。

ct4:生成下址,判断下址生成方式,根据不太那个的方式生成下址。

3. Microcomputer.vhd代码中如何定义并初始化RAM?type ram is array(0 to 37)of std_logic_vector(7 downto 0); --38*8ramsignal ram8:ram:=(x”20”, x”1e”, x”80”, x”40”, x”20”, x”20”, x”1d”, x”c0”, x”20”, x”40”, x”21”, x”20”, x”1f”, x”80”, x”40”, x”22”, x”20”, x”1e”, x”c0”, x”22”, x”80”, x”e0”, x”21”, x”40”, x”23”, x”60”, x”23”, x”a0”, x”00”, x”55”, x”8a”, x”f0”,others=>x”00”) –initialize ram44. Microcomputer.vhd代码中bus_reg_t2 将ram8存储器中对应于ar中地址单元的数据取出来放到bus_reg_t2寄存器中。

《计算机组成原理》教学模型机的设计与实现

充当简单的外设 。各控制信号都是断开的, 没有连接, 目的就是让学生 自己连接 , 以完成演示性和验证性的 实验 , 同时也为了让学生设计 出各式各样的整机电路。

本实验装置利用 了现有实验箱的单脉冲发生器 、 连续脉 冲发生器 ( 、 H) 电平检测器 、 电源电路和电平发 生器( 0K 5 。所有控制信号的高低 电平均可由开关 K . 1 提供 。 I . 1) ( 0K 5

2 运算执行部件和数据通路模块的设计与实现

如图 1 所示 , D 由L E数据指示器( 0B 发光二极管)7 L 1 1数据输入开关 D P 、4 S 7 、4 S7 B -7 、 S8 、 4 I3 7L 337L 23 等器件组成。它能提供不同指令所要求的各种数据通路和 1至 4 个通用寄存器 。当虚线连通 时, 整机 内部

学生手动操作完成数据传输实验及运算功能验证实验 , 还可作为整机 的执行部件。

图 1 实验装置 系统原理图

3 主存部件和读 写逻辑 电路模块 的设计与实现

存储器读写有 时序要求 。计算机大部 分的时间都在与存储器 打交道 。进行 一次存储器 的读写 , 需要

T 、2T 、4 1T 、 3T 这四个 T周期 , 即一个 C U周期( P 也称为机器周期 ) 。在对存储器读写的过程中要随时注意 当前所处的状态 , 否则不能正常进行读写操作。电路的工作原理是在 1 以前要给地址锁存器 A R准备好地

收稿 日期:0 7 1 一 7 20 — O 2 作者简介: 明海( 9 3 , , 梁 1 6 一) 男 汉族 广西扶绥人 , 广西工学院计算机工程系讲1 卷 8

片 7L 11 4 S 8 组成E 。它的运算对象是挂在总线上的两个暂存器 D 1 D 2. 4 S 8 的具体运算功能由 ¨ R 和 R 7L 11 控制信号 ¥ S S S 和 M、 N决定。它的逻辑功能表参见有关的教材[ 。运算器的进位输出被保存在标志 3 2 10 C ¨ 寄存器中, 可供操作控制器使用。如果学生所设计的整机不需要实现所有的运算功能, 只需实现几种常用的 算术和逻辑运算 , 那么某些控制信号也可以接到固定电位上 , 不必加以控制。本 电路模块可单独使用 , 支持

计算机发展历史上的第一

计算机发展历史上的第⼀计算机发展历史上的第⼀11623年,法国数学家、物理学家帕斯卡(Blaise Pascal),制造出第⼀台机械加法器Pascaline。

这台机器由⼀套8个可旋转的齿轮系统组成,只能进⾏加法和减法,实现⾃动进位,并配置⼀个可显⽰计算结果的窗⼝。

21834年,英国数学家Charles Babbage发明解析机(Analytical Engine),⾸度提出近似现代电脑组织的观念。

虽因机器结构太复杂,⾮当时技术所能制造,以致Babbage赍志以殁。

但解析机的设计理念和Babbage的⾄交Ada Lovelace⼥⼠(⾸位程序设计师)的程式构想,却开启了近代计算机的先河。

31932年,美国科学家Vannevar Bush研制成功微分分析仪(Differential Analyzer),微分分析仪是电⼦计算机的⿐祖。

Bush 在1945年写的《As We May Think》⼀⽂,预测了未来计算机、数据库、数位相机、语⾳识别、Internet等功能,⼈们因此称他为电脑之⽗。

41936年,德国⼯程师楚泽(Konrad Zuse)研制出了机械可编程计算机Z1,并采⽤了⼆进制形式,其理论基础即来源于布尔代数。

它的功能⽐较强⼤,⽤类似电影胶⽚的东西作为存储介质。

可以运算七位指数和16位⼩数。

可以⽤⼀个键盘输⼊数字,⽤灯泡显⽰结果。

51942年,美国爱荷华州⽴学院数学系教授阿特纳索夫和他的学⽣助⼿贝利设计成功阿特纳索夫-贝利-计算机(简称ABC)模型,ABC模型能做加法和减法运算,能存储300个数字,15秒中能进⾏⼀次运算,这就是有史以来⼈类第⼀次看到⽤电⼦管为元件的,有再⽣存储功能的数字计算机。

61944年,美国哈佛⼤学艾肯(Aiken)博⼠在IBM的赞助下设计完成Mark I,⼜叫做“⾃动序列受控计算机”。

它的外壳⽤钢和玻璃制成,装备了3000多个继电器,共有15万个元件和长达800公⾥的电线,⽤穿孔纸带输⼊。

3CPU-6设计模型机.解答

双操作数指令格式:

4

3

3

3

3

操作码 寄存器号 寻址方式 寄存器号 寻址方式

目的地址

单操作数指令格式:

4

6

操作码 (可扩展)

源地址

3

3

寄存器号 寻址方式

转移指令格式: 15 12 11 9 8

目的地址

6 5432 1 0

操作码 寄存器号 寻址方式 方式 N′Z′V′C′

3.7.3 组合逻辑控制器设计

1.时序系统

(1)工作周期

取指周期FT 源周期ST 目的周期DT 执行周期ET 中断周期IT DMA周期DMAT

用于指令正常执行 用于I/O传送控制

设置6个触发器分别 1 工作周期开始 作为各周期状态标志 0 工作周期结束 在整个指令周期中,任何时候必须、且只能有一

个工作周期状态标志为“1”。

内总线

移位器

R0

ALU

R1

AB DB CB

MAR

MDR

M I/O

A

B

R2

R3

R0~R3 R0~R3

C

CD CD

SP PC PSW MDR D

与系统总线 的连接通过 MDR MAR、MDR实现。

IR

PC

控制

逻辑

SP

PSW

从内总线输入(打入) 输入 从DB输入 (置入)

输出

输出至DB 输出至ALU的B门

R0~R3 R0~R3

C

CD CD

IR

PC

控制

逻辑

SP

SP PC PSW MDR D

PSW

3)转移地址

寄存器寻址:R0 B ALU 移 内 打入 PC

简单模型机的微程序设计

《计算机组成原理课程设计》简单模型机的微程序设计学生姓名:学号:系别:班级:专业:指导教师:一. 课程设计的目的1.计算机的硬件基本组成2.计算机中机器指令的设计3.计算机中机器指令的执行过程4.微程序控制器的工作原理5.微指令的格式设计原则在此基础上设计可以运行一些基本机器指令的微程序的设计二. 课程设计的内容和要求1.通过使用作者开发的微程序分析和设计仿真软件,熟悉介绍的为基本模型机而设计的微程序的执行过程。

必须充分理解并正确解释下些问题:(1)微程序中的微指令的各个字段的作用。

哪些字段是不译码的,哪些字段是直接译码的,哪些字段又可以看成是字段间接编码的。

答:直接译码的是A、B、C字段;不译码的是S3~B0字段;而间接编码的是uA6~uA1。

(2)微程序中的微指令是否是顺序执行的,如果不是,那么次地址是如何产生的。

什么情况下,次地址字段才是将要执行的微指令的地址。

答:微程序中的微指令不是顺序执行的,如果遇到P(1)~P(4)测试时,则根据机械指令,uA5~uA其他有关部件的内容,产生下一条微指令在空存中的微地址,是微程序转入相应的微地址入口,从而实现微程序的顺序、分支、循环运行等。

例如遇到P(1)测试,则下一条微指令在空存中的微地址的4~1位是用次地址字段NA(4~1位)或指令寄存器IR(8~5位)所产生,下一条微指令的微地址仍为 NA字段的6~5位。

如果没有遇到P(1)~P(4)测试的话,那么次地址即为该微指令地址字段所指向的微地址。

(3)在微程序中如何根据机器指令中的相关位实现分支,据此,在设计机器指令时应如何避免和解决与其它指令的微指令的微地址冲突。

答:微程序中是根据测试程序的机器指令中的8~5位和微程序中后六位进行“或”运算来实现分支的。

避免和解决与其它指令的微指令的微地址冲突的方法就是不用已经被其它微指令用过的微地址。

(4)哪些微指令是执行所有指令都要用到的。

答:00:00000101111011011000000101:000001001100000001000000(5)解释一条机器指令的微程序的各条微指令的微地址是否连续?这些微指令的微地址的安排的严重原则是什么?答:不连续。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

16位CPU的设计要求:此模型机的功能是将存储区的数据块复制到另一个存储区。

汇编代码如下:START:LOADI R1,0010H ;源操作数地址送R1LOADI R2,0030H ;目的操作数地址送R2LOADI R6,002FH ;结束地址送R6NEXT:LOAD R3,[R1] ;取数STORE [R2],R3 ;存数BRANCHGTI START ;如果R1>R6,则转向STARTINC R1 ;修改源地址INC R2 ;修改目的地址BRANCHI NEXT ;转向NEXT1.16位CPU的组成结构2.指令系统的设计一、指令格式1)单字指令格式2)双字指令格式操作码指令功能00001 LOAD 装载数据到寄存器00010 STORE 将寄存器的数据存入到存储器00100 LOADI 将立即数装入到寄存器00101 BRANCHI 无条件转移到由立即数指定的地址00110 BRANCHGTI 如果源寄存器容大于目的寄存器的容,则转移到由立即数指定的地址00111 INC 寄存器容加1指令依据以上设计的指令系统,则完成数据块复制的程序如下:地址机器码指令功能说明0000H0001H2001H0010HLOADI R1,0010H 源操作数地址送R1一、程序包:说明运算器的功能、移动寄存器的操作、比较器的比较类型和用于CPU控制的状态类型。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;package cpu_lib issubtype t_shift is unsigned (3 downto 0);constant shftpass :unsigned(3 downto 0):="0000";constant sftl :unsigned(3 downto 0):="0001";constant sftr:unsigned(3 downto 0):="0010";constant rotl :unsigned(3 downto 0):="0011";constant rotr :unsigned(3 downto 0):="0100";subtype t_alu is unsigned(3 downto 0);constant alupass :unsigned(3 downto 0):="0000";constant andOp :unsigned(3 downto 0):="0001";constant orOp:unsigned(3 downto 0):="0010";constant notOp :unsigned(3 downto 0):="0011";constant xorOp :unsigned(3 downto 0):="0100";constant plus :unsigned(3 downto 0):="0101";constant alusub :unsigned(3 downto 0):="0110";constant inc :unsigned(3 downto 0):="0111";constant dec :unsigned(3 downto 0):="1000";constant zero:unsigned(3 downto 0):="1001";subtype t_comp is unsigned 2 downto 0);constant eq :unsigned(2 downto 0):="000";constant neq :unsigned(2 downto 0):="001";constant gt:unsigned(2 downto 0):="";constant gte :unsigned(2 downto 0):="011";constant lt :unsigned(2 downto 0):="100";constant lte :unsigned(2 downto 0):="101";subtype t_reg is std_logic_vector(2 downto 0);type state is (reset1,reset2,reset3,reset4,reset5,reset6,execute,nop,load,store,move, load2,load3,load4,store2,store3,store4,move2,move3,move4,incPc,incPc2,incPc3,incPc4,incPc5,incPc6,loadPc,loadPc2,loadPc3,loadPc4,bgtI2,bgtI3,bgtI4,bgtI5,bgtI6,bgtI7,bgtI8,bgtI9,bgtI10,braI2,braI3,braI4,braI5,braI6, loadI2,loadI3,loadI4,loadI5,loadI6,inc2,inc3,inc4);subtype bit16 is std_logic_vector(15 downto 0);end cpu_lib;二、基本部件的设计1)运算器的设计功能library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use work.cpu_lib.all;entity alu isport(a,b:in bit16;sel:in t_alu;c:out bit16);end alu;architecture rt1 of alu isbeginprocess(a,b,sel)begincase sel iswhen alupass=> c<=a after 1ns;when andop=> c<=a and b after 1ns;when orop=> c<=a or b after 1ns;when xorop=> c<=a xor b after 1ns;when notop=> c<= not a after 1ns;when plus=> c<=a + b after 1ns;when alusub=> c<=a - b after 1ns;when inc => c<=a +"0000000000000001" after 1ns; when dec => c<=a -"0000000000000001" after 1ns; when zero => c<="0000000000000000" after 1ns; when others => c<="0000000000000000" after 1ns; end case;end process;end rt1;2)比较器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;use work.cpu_lib.all;entity comp isport (a,b:in bit16;sel:in t_comp;compout:out bit); end comp;architecture rt1 of comp isbeginprocess(a,b,sel)begincase sel iswhen eq => if a=b then compout <='1' after 1ns;else compout<='0' after 1ns;end if;when neq => if a/=b then compout <='1' after 1ns;else compout<='0' after 1ns;end if;when gt => if a>b then compout <='1' after 1ns;else compout<='0' after 1ns;end if;when gte => if a>=b then compout <='1' after 1ns;else compout<='0' after 1ns;end if;when lt => if a<b then compout <='1' after 1ns;else compout<='0' after 1ns;end if;when lte => if a<=b then compout <='1' after 1ns;else compout<='0' after 1ns;end if;when others=> compout<='0' after 1ns;end case;end process;end rt1;3)移位寄存器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use work.cpu_lib.all;entity shift isport(a:in bit16;sel:in t_shift;y:out bit16);end shift;architecture rt1 of shift isbeginprocess(a,sel)begincase sel iswhen shftpass => y<=a after 1 ns;when sftl=> y<=a(14 downto 0) &'0' after 1 ns;when sftr=> y<='0'& a(15 downto 1) after 1 ns;when rotl=> y<=a(14 downto 0) & a(15) after 1 ns;when rotr=> y<= a(0) & a(15 downto 1) after 1 ns;when others=> y<="0000000000000000" after 1 ns; end case;end process;end rt1;4)寄存器library ieee;use ieee.std_logic_1164.all;use work.cpu_lib.all;entity reg isport(a:in bit16;clk:in std_logic;q:out bit16);end reg;architecture rt1 of reg isbeginprocessbeginwait until clk'event and clk='1';q<=a after 1ns;end process;end rt1;5)寄存器组library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use work.cpu_lib.all;entity regarray isport(data:in bit16;sel:in t_reg;en,clk:in std_logic;q:out bit16);end regarray;architecture rt1 of regarray istype t_ram is array (0 to 7) of bit16;signal temp_data:bit16;beginprocess(clk,sel)variable ramdata:t_ram;beginif clk'event and clk='1' then ramdata(conv_integer(sel)):=data;end if;temp_data<=ramdata(conv_integer(sel)) after 1 ns;end process;process(en,temp_data)beginif en='1' then q<=temp_data after 1 ns;else q<="ZZZZZZZZZZZZZZZZ" after 1 ns;end if;end process;end rt1;6)三态寄存器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use work.cpu_lib.all;entity trireg isport(a:in bit16;en,clk:in std_logic;q:out bit16);end trireg;architecture rt1 of trireg issignal val:bit16;beginprocessbeginwait until clk'event and clk='1';val<=a;end process;process(en,val)beginif en='1' then q<=val after 1 ns;elsif en='0' then q<="ZZZZZZZZZZZZZZZZ" after 1 ns;else q<="XXXXXXXXXXXXXXXX" after 1 ns;end if;end process;end rt1;7)控制器采用状态机实现library IEEE;use IEEE.std_logic_1164.all;use work.cpu_lib.all;entity control isport( clock,reset,compout:in std_logic; instrReg:in bit16;progCntrWr,progCntrRd,addrRegWr,outRegWr,outRegRd:out std_logic;shiftSel:out t_shift; aluSel:out t_alu; compSel:out t_comp;opRegRd,opRegWr,instrWr,regRd,regWr,rw,vma:out std_logic;regSel:out t_reg );end control;architecture rtl of control issignal current_state, next_state : state;beginprocess( current_state, instrReg, compout)beginprogCntrWr <= '0'; progCntrRd <= '0'; addrRegWr <= '0';outRegWr <= '0';outRegRd <= '0'; shiftSel <= shftpass; aluSel <= alupass;compSel <= eq;opRegRd <= '0'; opRegWr <= '0'; instrWr <= '0'; regSel <= "000";regRd <= '0'; regWr <= '0'; rw <= '0'; vma <= '0';case current_state iswhen reset1=> aluSel<=zero after 1 ns; shiftSel<=shftpass; next_state<=reset2;when reset2 => aluSel<=zero; shiftSel<=shftpass; outRegWr<='1'; next_state<=reset3;when reset3 => outRegRd<='1'; next_state<=reset4;when reset4 => outRegRd<='1'; progCntrWr<='1';addrRegWr<='1'; next_state<=reset5;when reset5 => vma<='1'; rw <= '0'; next_state <= reset6;when reset6 => vma<='1'; rw<='0';instrWr<='1'; next_state<=execute;when execute => case instrReg(15 downto 11) iswhen "00000" => next_state <= incPc ;-- nopwhen "00001" => regSel<=instrReg(5 downto 3); regRd<='1';next_state<=load2;when "00010" => regSel<=instrReg(2 downto 0); regRd<='1';next_state<=store2;-- storewhen "00011" => regSel<=instrReg(5 downto 3); regRd<='1';aluSel<=alupass;shiftSel<=shftpass; next_state<=move2;when "00100" => progcntrRd<='1'; alusel<=inc; shiftsel<=shftpass;next_state<=loadI2;when "00101" => progcntrRd<='1'; alusel<=inc; shiftsel<=shftpass;next_state<=braI2;when "00110" => regSel<=instrReg(5 downto 3);regRd<='1';next_state<=bgtI2;--BranchGTImm when "00111" => regSel<=instrReg(2 downto 0); regRd<='1'; alusel<=inc;shiftsel<=shftpass; next_state<=inc2;when others =>next_state <= incPc;end case;when load2 => regSel <= instrReg(5 downto 3); regRd <= '1';addrregWr <= '1';next_state <= load3;when load3 => vma <= '1'; rw <= '0'; next_state <= load4;when load4 => vma <= '1'; rw <= '0'; regSel <= instrReg(2 downto 0);regWr <= '1';next_state <= incPc;when store2 => regSel <= instrReg(2 downto 0); regRd <= '1';addrregWr <= '1';next_state <= store3;when store3 => regSel <= instrReg(5 downto 3); regRd <= '1';next_state <= store4;when store4 => regSel <= instrReg(5 downto 3); regRd <= '1'; rw <= '1'; next_state <= incPc;when move2 => regSel <= instrReg(5 downto 3); regRd <= '1';aluSel <=alupass;shiftsel <= shftpass; outRegWr <= '1'; next_state <= move3;when move3 => outRegRd <= '1'; next_state <= move4;when move4 =>outRegRd <= '1';regSel <= instrReg(2 downto 0); regWr <= '1';next_state <= incPc;when loadI2 => progcntrRd <= '1'; alusel <= inc; shiftsel <= shftpass;outregWr <= '1';next_state <= loadI3;when loadI3 => outregRd <= '1'; next_state <= loadI4;when loadI4 => outregRd <= '1'; progcntrWr<='1'; addrregWr<='1';next_state<=loadI5;when loadI5 => vma <= '1'; rw <= '0'; next_state <= loadI6;when loadI6 => vma <= '1'; rw <= '0';regSel <= instrReg(2 downto 0);regWr <= '1';next_state <= incPc;when braI2 => progcntrRd <= '1'; alusel <= inc; shiftsel <= shftpass;outregWr <= '1';next_state <= braI3;when braI3 => outregRd <= '1'; next_state <= braI4;when braI4 => outregRd<='1'; progcntrWr<='1'; addrregWr<='1';next_state<=braI5;when braI5 => vma<='1'; rw<='0'; next_state <= braI6;when braI6 => vma <= '1'; rw <= '0';progcntrWr <= '1'; next_state <= loadPc; when bgtI2 => regSel <= instrReg(5 downto 3); regRd <= '1';opRegWr <= '1';next_state <= bgtI3;when bgtI3 => opRegRd <= '1'; regSel <= instrReg(2 downto 0);regRd <= '1';compsel <= gt; next_state <= bgtI4;when bgtI4 => opRegRd <= '1' after 1 ns;regSel <= instrReg(2 downto 0); regRd <= '1';compsel <= gt;if compout = '1' then next_state <= bgtI5;else next_state <= incPc;end if;when bgtI5 => progcntrRd<='1'; alusel<=inc; shiftSel<=shftpass;next_state<=bgtI6;when bgtI6 => progcntrRd <= '1'; alusel <= inc; shiftsel <= shftpass;outregWr <= '1'; next_state <= bgtI7;when bgtI7 => outregRd <= '1'; next_state <= bgtI8;when bgtI8 =>outregRd <= '1';progcntrWr <= '1'; addrregWr <= '1'; next_state <= bgtI9;when bgtI9 => vma <= '1'; rw <= '0'; next_state <= bgtI10;when bgtI10 => vma <= '1'; rw <= '0'; progcntrWr <= '1'; next_state <= loadPc; when inc2 => regSel <= instrReg(2 downto 0); regRd <= '1'; alusel <= inc;shiftsel <= shftpass; outregWr <= '1'; next_state <= inc3;when inc3 => outregRd <= '1'; next_state <= inc4;when inc4 => outregRd <= '1'; regsel <= instrReg(2 downto 0);regWr <= '1'; next_state <= incPc;when loadPc => progcntrRd <= '1'; next_state <= loadPc2;when loadPc2 => progcntrRd <= '1'; addrRegWr <= '1'; next_state <= loadPc3; when loadPc3 => vma <= '1'; rw <= '0'; next_state <= loadPc4;when loadPc4 => vma <= '1'; rw <= '0'; instrWr <= '1'; next_state <= execute;when incPc => progcntrRd<='1'; alusel<=inc; shiftsel<=shftpass;next_state<=incPc2;when incPc2 => progcntrRd <= '1'; alusel <= inc; shiftsel <= shftpass;outregWr <= '1'; next_state <= incPc3;when incPc3 => outregRd <= '1'; next_state <= incPc4;when incPc4 => outregRd<='1'; progcntrWr<='1';addrregWr<='1'; next_state<=incPc5;when incPc5 => vma <= '1'; rw <= '0'; next_state <= incPc6;when incPc6 => vma <= '1'; rw <= '0'; instrWr <= '1'; next_state <= execute;when others => next_state <= incPc;end case;end process;process(clock, reset)beginif reset = '1' then current_state <= reset1 after 1 ns;elsif clock'event and clock = '1'then current_state <= next_state after 1 ns;end if;end process;end rtl;8)存储器的设计LPM_RAM定制首先,定制初始化数据文件,建立Memory Initialization File(.mif)文件,选择File→New 命令,并在New窗口选择Other file选项,再选择Memory Initialization File选项。