可编程片上系统开发平台

赛普拉斯 PSoC 4000S 系列数据手册说明书

请注意赛普拉斯已正式并入英飞凌科技公司。

此封面页之后的文件标注有“赛普拉斯”的文件即该产品为此公司最初开发的。

请注意作为英飞凌产品组合的部分,英飞凌将继续为新的及现有客户提供该产品。

文件内容的连续性事实是英飞凌提供如下产品作为英飞凌产品组合的部分不会带来对于此文件的任何变更。

未来的变更将在恰当的时候发生,且任何变更将在历史页面记录。

订购零件编号的连续性英飞凌继续支持现有零件编号的使用。

下单时请继续使用数据表中的订购零件编号。

PSoC 4:PSoC 4000S 系列数据手册可编程片上系统(PSoC)概述PSoC ® 4是一个可扩展和可重配置的平台架构,用于基于Arm ® Cortex ®-M0+ CPU 的可编程嵌入式系统控制器系列。

它集成了可编程和可重新配置的模拟和数字模块,并且能够灵活自动地路由资源。

PSoC 4000S 产品系列是PSoC 4平台架构的一个成员。

该产品系列集成了下列四项:拥有标准通信和时序外设的微控制器、具有一流性能的电容式触摸感应(CapSense )系统、可编程的通用、连续和带有开关电容的模拟模块以及可编程接口。

针对新应用和设计的要求,PSoC 4000S 产品与PSoC 4平台系列产品向上兼容。

特性32位MCU 子系统■48 MHz Arm Cortex-M0+ CPU,配置单周期倍频 ■包含读取加速器的闪存容量可达32 KB ■SRAM 的容量高达4 KB可编程模拟资源■由电容式感应模块提供的单斜10位ADC 功能■可用在任意引脚上的两个电流DAC (IDAC ),用于通用目的或电容式感应应用■可在深度睡眠模式下工作的两个低功耗比较器可编程数字资源可编程逻辑模块支持在输入和输出端口上执行Boolean (布尔)操作低功耗操作模式的电压范围:1.71 V ~ 5.5 V■在深度睡眠模式下,模拟系统可正常工作,并且数字系统仅消耗2.5 μA 的电流电容式感应■赛普拉斯的CapSense Sigma-Delta (CSD )模块提供了一流的信噪比(SNR > 5:1)和防水功能■赛普拉斯提供的软件组件使电容式感应设计变为更加简单■自动硬件调校(SmartSense™)串行通信■两个运行时可重新配置的独立串行通信模块(SCB ),可配置为I2C 、SPI 或UART 功能LCD 驱动能力■GPIO 上的LCD segment 驱动能力定时和脉冲宽度调制器■五个16位定时器/计数器/脉冲宽度调制器(TCPWM )模块■支持中心对齐、边沿对齐和伪随机模式■基于比较器触发的“Kill ”信号,适用于电机驱动和其它高可靠性数字逻辑的应用多达36个可编程的GPIO 引脚■48-TQFP 、40-pin QFN ,32-pin QFN 、24-pin QFN ,32-pin TQFP 和25-ball WLCSP 封装■任何GPIO 引脚都可用作CapSense 、模拟或数字引脚■可编程驱动模式、强度和转换速率时钟源■32-kHz 监视晶振 (WCO)■±2%精度内部主振荡器(IMO)■32-kHz I 内部低速振荡器 (ILO)ModusToolbox™ 软件■多平台工具和软件库的综合集合。

Xilinx FPGA的嵌入式系统开发过程

Xilinx FPGA的嵌入式系统开发过程由创新网小编于星期四, 01/10/2013 - 11:03 发表随着FPGA 技术的迅速发展,可编程片上系统(SOPC)作为一种特殊的嵌入式微处理器系统,融合了SoC和FPGA 各自的优点,并具备软硬件在系统可编程、可裁减、可扩充、可升级的功能,已逐渐成为一个新兴的技术方向。

SOPC的核心是在FPGA上实现的嵌入式微处理器核,目前主要有Xilinx公司集成的32位软核MicroBlaze[1] ,32位PowerPC系列处理器硬核PowerPC405、PowerPC440,ARM公司的CortexA9,以及Altera公司的Nios系列微处理器软核等。

本文主要介绍Xilinx公司的MicroBlaze 软核结构,对其体系结构、设计流程和相关开发工具一一进行介绍,并在实际的无线电监测系统[2]中采用此方案,构建了一个小型化、智能化、网络化的软件无线电处理平台。

1 MicroBlaze处理器结构MicroBlaze软核处理器是可配置的精简指令集(RISC)32位CPU,该RISC核针对Xilinx公司的FPGA芯片进行了优化。

设计人员可以根据设计定制处理器的可选配置,根据版本的不同,配置不同的选项。

该软核处理器具有以下几个方面的特征:◆32个32位通用寄存器;◆32位3个操作数的指令字,指令字有2种寻址模式;◆分离的32位地址总线和数据总线;◆具有高速的指令和数据缓存,3级和5级流水线操作;◆灵活的总线结构,支持LMB、OPB、PLB、XCL、FSL片上总线接口等,新推出的系列还支持AXI总线接口;◆支持MMU存储管理、FPU浮点单元、高速缓存、异常处理和调试逻辑等可根据性能需求和逻辑区域成本任意裁减的高级特性。

MicroBlaze的这些特性极大地扩展了其应用范围,MicroBlaze处理器的内核仍在不断更新之中,目前使用的版本MicroBlaze v7.1,其内部架构如图1所示。

quartus软件的安装及使用手册

第一章 概述Altera公司的QuartusII软件提供了可编程片上系统(SOPC)设计的一个综合开发环境,是进行SOPC设计的基础。

QuartusII集成环境包括以下内容:系统级设计,嵌入式软件开发,可编程逻辑器件(PLD)设计,综合,布局和布线,验证与仿真。

QuartusII设计软件根据设计者需要提供了一个完整的多平台开发环境,它包含整个FPGA和CPLD设计阶段的解决方案。

图1-1说明了QuartusII软件的开发流程。

图1-1 QuartusII软件开发流程此外,QuartusII软件允许用户在设计流程的每个阶段使用QuartusII图形用户界面、EDA工具界面或命令行界面。

在整个设计流程中可以使用这些界面中的一个,也可以在不同的设计阶段使用不同的界面。

Altera技术领先的QuartusII设计软件配合一系统可供客户选择的IP核,可使设计人员在开发和推出FPGA、CPLD和结构化的ASIC设计的同时,获得无与伦比的设计性能、一流的易用性以及最短的市场推出时间。

这是设计人员首次将FPGA移植到结构化的ASIC中,能够对移植后的性能和功耗进行准确的估算。

QuartusII软件支持VHDL和Verilog硬件描述语言(HDL)的设计输入、基于图形的设计输入方式以及集成系统设计工具。

QuartusII软件可以将设计、综合、布局和布线以及系统的验证全部整合到一个无缝的环境之中。

其中还包括第三方EDA工具的接口如MATLAB等。

QuartusII软件包括SOPC Builder工具。

SOPC Builder针对可编程片上系统(SOPC)的各种应用自动完成IP核(包括嵌入式处理器、协处理器、外设、数字信号处理器、存储器和用户设定的逻辑)的添加、参数设置和连接进行操作。

SOPC Builder节约了原先系统集成工作中所需要大量时间,使设计人员能够在同几分钟内将概念转化成真正可运行的系统。

QuartusII与MAXPLUSII的设计方式基本一致。

全新片上可编程系统(SOPC)多参监护仪专用主控板简介

3 8

《 中国医疗器械信息 》2 0 年第 1 卷第1 v 1 4N 08 4 ut n sr yFo u r m

维普资讯

形 象 ; 够利用 网络 / 能 网格 技 术 在 P S上 作 更 广 泛 为一 门 自从体系的学科后 ,成为与影像诊断学平行的 AC 的共 享 及 互 动 。 16 年 曹 老 与 邹 仲教 授 一 起 完 成 的我 两种序列发展的学科 。由于影像技术必须与 临床诊断 90

的设计 ,称 为可 编程 片上 系统 , 简称 S P (y t n O CSsm O e

P o rmma l hp. r ga beC i)

3 利 用S C 技 术建 立 的X .OP .0 多参 监护 仪专 OP JS C 1 4

用 主控 板

我 们采用 了上 述 F GA嵌 入软 核 I P P的 S P O C新技 术 , 用 Ata 司的 S P 使 lr 公 e O C硬 件 开发 工具平 台 (O C S P B i r Q ats I、软 件开 发调 试工 具平 台 ( I SI ul 和 ur ) e uI NO I

勉强解决一些问题 , 但在生产和调试的具体实施上存在 本构件。它们都以硬件描述语言为主要设计手段 , 借助 较大技术难度 ,而且存在费用较高、灵活性差和不易更 于以计算机为平 台的 E DA工具进行。专用 S P O C芯片

新换 代 等 缺点 。更 重 要 的是 这些 在 P B板 上通 过 “ C 打 设计技术主要是指面向单片专用 S C芯片设计技术的 O 补丁 ”补 上去 的 电路 ,不属 于 AR 微处 理器 系统 的一 计算机技术 , M 与通用 S C芯片设计技术相比, O 其特点有:

・

设计技术直接面向用户 ,即专用集成电路的被动

可编程片上系统psoc简介

• 152•定了整车机械系统的设计安装和改进方案。

硬件系统布置如图3所示,仿真结果如图4道路图像所示。

图3 整车布局图 图4 道路图像图5 实物图4 结语利用摄像头和电感对道路图像和电磁的检测来实现自动寻迹,能够有效解决智能小车自动寻迹以及模拟现实生活中汽车在遇到的一些特殊路况下小车自动寻迹的问题。

本文所设计和制作的智能小车在第十四届全国大学生智能汽车竞赛中得到实际应用,实现了在赛道上的自动寻迹。

参考:第十四届“恩智浦”杯全国大学生智能汽车竞赛细则[EB/OL].https:///index/;宋雪丽,王虎林等.基于单片机的寻迹机器人的系统设计,仪表技术[J].2016(4):102-105;高中正,赵丽娜等.基于摄像头的智能车控制系统设计,自动化与仪表[J].2015(6):1-5;李全福,万彦辉,郭华.模糊PID 控制算法在电动舵机控制中的应用[J].微电机,2008(12):28-30;李全利.单片机原理及应用技术[M].高等教育出版社,2010;刘乐善.微型计算机接口技术及应用[M].武汉:华中科技大学出版社,2004。

作者简介:范作鑫(1997—),山东潍坊人,大学本科,现就读于山东协和学院。

在文中介绍了可编程片上系统PSoC ,及PSoC 的开发环境、设计流程等,对PSoC 的优点与可编程门阵列FPGA 和可编程模拟器件ispPAC 进行总结对比。

1 PSoC简介可编程片上系统PSoC ,是美国Cypress 半导体公司在2000年推出的一种独特的系统架构。

它内部包含CPU 内核(M8C)、多种模拟和数字器件阵列集、微型处理器及外围单元和外围接口电路等系统,无需外接芯片及晶振,集成度非常高,实现了在线“系统单片化可编程”(张志文,胡志洁.PSoC 的多路陀螺输出脉冲计数系统设计[J].西安工业大学学报,2011年第6期),成为第一种真正具有混合信号处理能力的SOC 。

在PSoC 中,所有的模块都可以根据设计者设计需求的不同,进行动态重构,在芯片内部即可调用不同的模块来完成功能设计(胡志浩.基于PSoC 的陀螺组合测试技术的研究[D].西安工业大学,2011)。

嵌入式填空题

填空题1、ARM微处理器有7种工作模式它们分为两类非特权模式、特权模式。

其中用户模式属于非特权模式2、ARM支持两个指令集,ARM核因运行的指令集不同,分别有两个状态ARM、Thumb,状态存放器CPSR的T位反映了处理器运行不同指令的当前状态3、ARM核有多个存放器,其局部用于通用存放器,有小局部作为专用存放器,R15存放器用于存储PC,R13通常用来存储SP。

ARM处理器有两种总线架构,数据和指令使用同一接口的是诺依曼,数据和收指令分开使用不同接口的是哈佛构造4、ARM微处理器复位后PC的地址通常是0*0初始的工作模式是Supervisor。

5、ARM微处理器支持虚拟存它是通过系统控制协处理器CP15和MMU存储管理部件来进展虚拟存的存储和管理。

当系统发生数据异常和指令领取异常时异常处理程序透过嵌入式操作系统的存管理机制通过MMU交换物理存和虚拟存的页面以保证程序正常执行。

6、编译代码时有两种存储代码和数据的字节顺序一种是小端对齐另一种是大端对齐。

7、构建嵌入式系统开发环境的工具链有多种其中开放源码的工具链是GNU工具链ARM公司提供的工具链是ADS工具链计算机有CISC和RISC两种类型以ARM微处理器为核心的计算机属于RISC 类型其指令长度是定长的9.一般而言嵌入式系统的构架可以分为4个局部分别是处理器、存储器、输入/输出和软件一般软件亦分为操作系统相关和应用软件两个主要局部。

10、根据嵌入式系统使用的微处理器可以将嵌入式系统分为嵌入式微控制器、嵌入式DSP 处理器、嵌入式微处理器以及片上系统。

11、操作系统是联接硬件与应用程序的系统程序,其根本功能有进程管理、进程间通信、存管理、I/O资源管理。

12、从嵌入式操作系统特点可以将嵌入式操作系统分为实时操作系统和分时操作系统其中实时系统亦可分为硬实时系统和软实时系统。

13、核负责管理各个任务或者为每个任务分配CPU时间并且负责任务之间的通信,核的根本效劳是任务切换。

可编程片上系统开发平台

基于设计人员选择的板子,设计人员通过BSB选择并 配置基本的元素,比如:处理器类型、调试接口、缓存配 置、存储器类型和大小、外设等。 对于BSB不支持的目标系统,设计人员可以选择定制 板选项。使用这个选项时,必须指定未来板子的硬件,并 且要给出用户约束文件UCF。 如果选择的是支持的目标板,BSB向导自动的加入 UCF文件。当退出BSB时,BSB所建立的MHS和MSS文 件自动加入到XPS工程中,设计人员能在XPS中进行更进 一步的设计。

软件开发

Library Generator(Libgen)

构建一个软件平台,该软件平台由定制的软件库、驱动程序和OS构成。

GNU Compiler Tools(GCC)

基于库产生器建立的平台,建立软件应用程序。

验证

Xilinx Microprocessor Debugger(XMD)

打开shell用于软件下载和调试,也提供通道用于GNU调试器访问设备。

设计流程及EDK工具 - Xilinx Platform Studio(XPS)

XPS提供下面的特性: (1) 能够添加核,编辑核参数和进行总线和信号连接,产生MHS 文件; (2) 能够产生和修改MSS文件; (3) 支持表5.1内的所有工具; (4) 能够产生和观察系统块图和设计报告; (5) 多用户软件应用支持; (6) 项目管理; (7) 过程和工具流程依赖管理; (8) 输出MHS文件到SDK工具

在主机上建立一个MFS存储器镜像,该镜像并被下载到嵌入式系统存储器。

Platform Specification Utility

自动产生微处理器外设定义MPD数据文件,该文件要求创建EDK兼容的制定外设。

片上可编程系统原理及应用课程设计

片上可编程系统原理及应用课程设计一、前言随着科学技术的发展,片上可编程系统逐渐成为了计算机科学的研究热点。

为了让学生掌握这一领域的基础原理和实践应用,本文将介绍片上可编程系统原理及应用课程的设计。

二、课程设计目标本课程的设计目标主要是让学生掌握片上可编程系统的原理、结构、设计方法、应用等基本概念和技术,能够利用片上可编程系统进行数字电路设计,完成简单的软硬件系统设计和仿真,并能够在实际的项目开发实践中应用所学知识。

三、课程内容本课程包括以下三个部分内容:3.1 片上可编程系统基础理论通过学习片上可编程系统的原理和结构,学生将掌握片上可编程系统的组成和设计方法,如CPU、FPGA等基本概念和技术。

具体内容包括:•片上可编程系统的组成结构及原理。

•片上可编程系统设计的基本步骤和方法。

•CPU和FPGA的基本原理和功能。

•片上可编程系统的应用。

3.2 片上可编程系统设计方法与实践通过学习片上可编程系统的设计方法和实践应用,学生将掌握片上可编程系统的数字电路设计方法、软硬件系统设计和仿真方法。

具体内容包括:•数字电路设计方法和工具的使用。

•软硬件系统设计与仿真方法。

•项目管理和团队协作能力。

3.3 片上可编程系统应用案例分析本部分主要通过实际的片上可编程系统应用案例,让学生掌握应用能力。

具体内容包括:•基于片上可编程系统的数字信号处理设计。

•基于片上可编程系统的控制系统设计。

•其它应用案例分析。

四、课程设计方法本课程设计采用了以下几种教学方法:4.1 讲授教学通过课堂讲授、案例分析、实验等方式,让学生掌握片上可编程系统的理论知识和实践能力。

4.2 实验教学通过实验教学,让学生了解和掌握片上可编程系统的设计方法和实践应用能力,提高实际应用能力。

4.3 自主学习让学生自主学习一些国内外的片上可编程系统研究论文和相关领域的最新进展,提高学生创新能力。

五、课程设计实施本课程设计分为三个阶段:5.1 第一阶段在第一阶段,主要是介绍片上可编程系统基础理论和设计方法。

ARM考试题

一、选择题(选15题,每小题2分,共30分)1. ARM 属于(A )[A] RISC 架构[B] CISC架构2. ARM 指令集是(C)位宽,Thumb 指令集是(B)位宽的。

[A] 8位[B] 16 位[C] 32位[D] 64位3. ARM 指令集是(H )字节对齐,Thumb 指令集是(F )字节对齐的[E] 1[F] 2 [G] 3 [H] 44. 复位后,ARM处理器处于(B )模式,(D )状态[A] User[B] SVC [C] System [D] ARM [E] Thumb5. ARM处理器总共(E )个寄存器,System模式下使用(A )个寄存器,SVC模式下使用( B )个寄存器。

[A] 17个[B] 18个[C] 32个[D] 36个[E] 37个6. ARM处理器中优先级别最高的异常为(E ),(AC )异常可以用来相应中断[A] FIQ[B] SWI [C] IRQ [D] SVC [E] RESET7. ARM数据处理指令中有效的立即数是(ACEGH )[A] 0X00AB0000[B] 0X0000FFFF [C ] 0XF000000F [D ] 0X08000012[E] 0X00001F80 [F] 0XFFFFFFFF [G] 0 [H] 0XFF0000008. ATPCS规定中,推荐子函数参数最大为(D )个[A] 1[B] 2 [C ] 3 [D ] 49. ATPCS规定中,栈是(B )[A] 满加[B] 满减[C ] 空加[D ] 空减10. 在用ARM汇编编程是,其寄存器有多个别名,通常PC是指(D ),LR 是指(C ),SP是指(B )[A] R12[B] R13 [C ] R14 [D ] R1511. CPSR寄存器中反映处理器状态的位是(D )[A] J位[B] I位[C ] F位[D ] T位12. 下面属于ARM 子程序调用指令的是(C )[A] B[B] BX [C ] BL [D ] MOV13. ARM7属于(A )结构,ARM9属于(B )结构。

NIOSII SOPC实例1

一.关于SOPC1)SOPC英文全名为:System-On-a-Programmable-Chip,即可编程片上系统。

SOPC 用可编程逻辑技术把整个系统放到一块硅片上,来用于嵌入式系统研究和电子信息处理。

SOPC是一种特殊的嵌入式系统,它是片上系统(System-On-a -Chip,SOC),即由单个芯片完成整个系统的主要逻辑功能但它不是简单的SOC,它也是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

SOPC设计包括以32位NIOSII软核处理器为核心的嵌入式系统的硬件配置、硬件设计、硬件仿真、软件设计以及软件调试等。

SOPC系统设计的基本软件工具有:1)QuartusII:用于完成NIOSII系统的综合、硬件优化、适配、编程下载以及硬件系统调试等;2)SOPC Builder:Altera NiosII嵌入式处理器开发软件包,用于实现NiosII 系统的配置、生成,内嵌于QuartusII软件中;3)ModelSim: 用于对SOPC生成的NiosII系统的HDL描述进行系统的功能仿真;4)NiosII IDE:用于进行软件的开发、调试,以及向目标开发板进行Flash下载;二.关于NIOSII处理器NIOSII 是一个可配置的软核处理器。

“可配置”的意思是设计者可以根据性能和成本的要求来增加或删减处理器的功能。

ALTERA公司并不销售NIOSII处理器芯片,而是销售空的FPGA,并提供NIOSII 系统相应的IP核来组成NIOSII系统,然后将这个系统下载到FPGA中实现。

1)关于AVALONAvalon总线是SOPC硬件系统的重要组成部分,Avalon总线规范是为了开发SOPC 环境下外设而设计的。

图1-1 一个SOPC的示例二. SOPC简单实例:软核控制LCD液晶字母显示器1.系统构成规划1)系统功能:在character LCD上显示”Hello LCD from NiosII!”2)本系统中需要的外围器件:(1)L CD:输出显示(2)S RAM存储器:程序运行时将其导入SRAM3)SOPC中建立系统需要添加的模块包括:(1)N ios II 32bit CPU(2)L CD display(3)外部RAM总线(4)外部RAM接口(5)J TAG UART Interface(6)定时器2.硬件系统的建立1)首先打开Quartus II 建立工程文件:将工程文件命名为hello_lcd,顶层文件与工程文件同名。

POSC

课程目标

在课程培训结束后,你将会能够:

• 列出嵌入式系统使用PSoC的优势 • 描述PSoC器件的主要特征 • 使用PSoC Designer进行项目设计 • 描述PSoC各种开发工具 • 列举Cypress的各种技术支持服务 • 了解PSoC的主流解决方案

3

nvSRAM Product Training – Cypress Conf idential

System BOM using PSoC = $4.80

11

nvSRAM Product Training – Cypress Conf idential

PSoC –可编程片上系统芯片

设计挑战 产品差异化

PSoC 方案 : 外围和引脚功能定义可以在产品的最后一分钟定制 ,轻松实现

减少材料数量,降低成本和减小PCB空间体积,提

“功能定制”

可以有无数种配置方案实现客户的要求。

下面这两个器件都是同一颗PSoC芯片实现的:

器件1

• • • • • • • • 1个8位计数器 1个16位定时器 1个波特率可变的全双工UART 1个SPI从模块 1个4路输入的8位sigma-delta AD 1个6位AD 1个位DA 2个低通滤波器

DR0 DB

DR1

DB

DB DR1 DI

DR0

DO

DB DI DO

DR2

• 通讯模块

DATA

IN PROC

TXD RXD CLK COMM ONLY

CLK

OUT PROC

TXD CLK RXD COMM ONLY

- 功能级可编程 - 非门级可编程

CLKS

INPUT REG

CR1

CONFIG

PSoC

PSoC(可编程片上系统)PSoC(可编程片上系统)是Cypress半导体生产的包含有8位微处理器核和数字与模拟混合信号阵列的可编程片上系统。

其应用领域与8位的MCU相同。

区别于8位的MCU,PSoC的周边数字资源(如定时器、PWM、UART等等)和周边模拟资源(放大器、比较器、滤波器等等)以数字模块和模拟模块的方式提供。

不同型号的PSoC芯片的差异主要在于其拥有的数字模块和模拟模块的数量的不同。

用户可以根据自己的需要来定义这些模块。

PSoC的集成开发环境PSoC Designer也预先为用户定义了七十多个常用的数字和模拟资源供用户选择。

如数字资源有:定时器、PWM、UART、SPI、CRC、PRS等等;模拟资源有放大器、比较器、滤波器等等;AD和DA转换器由若干数字模块和模拟模块组合而成。

所有这些预定义的模块被称之为用户模块。

PSoC Designer也为用户提供这些用户模块的API函数供用户编程时调用。

在PSoC Express出现以前,开发PSoC的应用项目与MCU的应用开发相似,使用PSoC Designer集成开发环境根据项目的需要调用和配置资源(用户模块),编写代码(C或汇编),编译,调试….现在由于PSoC Express可以在更高的抽象概念水平上运行,且无需汇编或C的软件开发,因此设计人员只需要数小时或数天时间即可完成对PSoC器件的新设计开发、仿真及编程,而不再耗时数周乃至数月。

由于其采用无缝多重处理器架构、具有设计可视化功能,包含丰富的驱动程序库和多种传输函数的评估器以及软仿真功能,因此系统开发工程师采用PSoC Express工具能够更快地完成设计工作,并实现更高的可靠性。

在PSoC Express中,尤其值得提到它的Monitor功能,它使得PSoC的无代码、可视化应用开发变得透明化。

对某些比较复杂的应用,需要及时调节或修改某些参数时,不会再有那种捉摸不定和黑匣子的感觉。

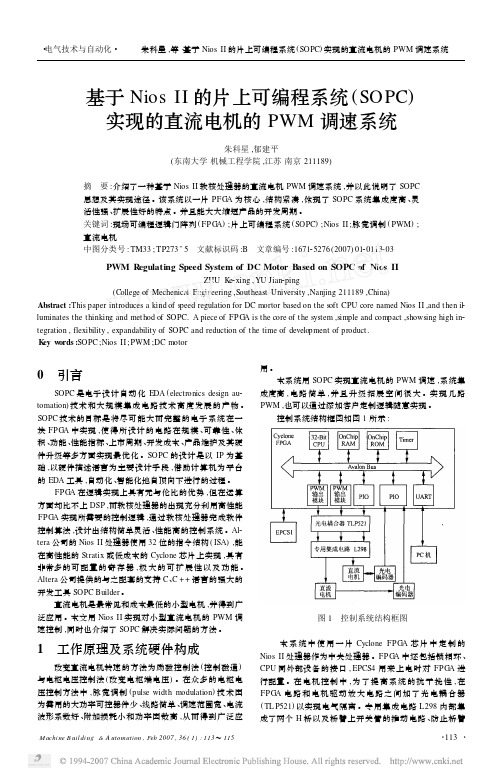

基于NiosII的片上可编程系统_SOPC_实现的直流电机的PWM调速系统

基于Nios II的片上可编程系统(SOPC)实现的直流电机的PWM调速系统朱科星,郁建平(东南大学机械工程学院,江苏南京211189)摘 要:介绍了一种基于Nios II软核处理器的直流电机PWM调速系统,并以此说明了SOPC思想及其实现途径。

该系统以一片PF G A为核心,结构紧凑,体现了SOPC系统集成度高、灵活性强、扩展性好的特点。

并且能大大缩短产品的开发周期。

关键词:现场可编程逻辑门阵列(FPG A);片上可编程系统(SOPC);Nios II;脉宽调制(PWM);直流电机中图分类号:TM33;TP273+5 文献标识码:B 文章编号:167125276(2007)0120113203PWM R egulating Speed System of DC Motor B ased on SOPC of Nios IIZHU K e2xing,YU Jian2ping(College of Mechenical Engineering,S outheast University,Nanjing211189,China)Abstract:This paper introduces a kind of s peed regulation for DC mortor based on the soft CPU core named Nios II,and then il2 luminates the thinking and method of SOPC.A piece of FPG A is the core of the system,simple and compact,showsing high in2 tegration,flexibility,expandability of SOPC and reduction of the time of develo pment of product.K ey w ords:SOPC;Nios II;PWM;DC motor0 引言SOPC是电子设计自动化EDA(electronics design au2tomation)技术和大规模集成电路技术高度发展的产物。

第5讲SOPCBuilder使用简介

System on Chip

片上系统

与基于ASIC的SOC相比,SOPC具有更多的特点与吸

引力:

开发软件成本低 硬件实现风险低

产品上市效率高

产品设计成本低

系统结构可重构及硬件可升级

5.1.2 SOPC Builder 简介 SOPC Builder 是Altera公司推出的一种可加快在 PLD内实现嵌入式处理器相关设计的工具。它是一个 革命性的系统级开发工具,旨在提高设计者的效率。

利用图形用户界面,用户可以快速方便地定义和连

接复杂的系统。如图5.1所示,用户可从左边的库中添加 所需的部件,然后在右边的表中配置它们。

图5.1 SOPC Builder的图形用户界面

2. 自动生成和集成软件与硬件 SOPC Builder会生成每个硬件部件以及连接部件的片 内总线结构,仲裁和中断逻辑。它也会产生系统可仿真的 RTL描述以及为特定硬件配置设计的测试平台,能够把硬 件系统综合到单个网表中。 另外,SOPC Builder还能够生 成C和汇编头文件,这些头文件定义了存储器映射、中断 优先级和每个外设寄存器空间的数据结构。这样的自动生 成过程可以帮助软件设计者处理硬件潜在的变化性。如果 硬件改变了,SOPC Builder会自动更新这些头文件。SOPC Builder也会为系统中现有的每个外设生成定制的C和汇编 函数库。例如,如果系统包括一个UART,SOPC Builder 就会访问UART的寄存器并定义一个C结构,生成通过 UART发送和接收数据的C和汇编例程。

SOPC Builder GUI引导用户完成两部分的配置:部件 配置和系统配置。部件配置需要汇总参数,Class PTF文件 标准包括了为这一要求定义GUI的格式。当需要时, SOPC Builder读取该格式,产生相应的部件向导 (Component Wizard),收集所需的用户数据。然后SOPC Builder把收集的参数值存放在System PTF文件中。系统配 置是指把用户提供的有关处理器的配置、外设连接等数据 写入System PTF中。 当这两部分配置都完成后,SOPC Builder进入到生成 阶段,生成设计的输出文件。SOPC Builder查阅每个Class PTF文件,允许相关的部件生成程序,它们会正确地输出 特定系统配置的硬件和/或软件文件。

基于FPGA的可编程片上系统SOPC

1 可编 程 片上 系 统 S C 导 致嵌 入 式 系统设 计 的 变革 OP

目前 。 以嵌 入 式 系 统 所 采 用 的 核 心 器 件 — — 处 理 器 进 行 划 分 , 入 式 系 统 可 分 为 3种 类 型 : 若 嵌 基 于微 控制 器 ( U) 嵌 入式 系统 , 于 信号 处理 器 ( S 的嵌入 式 系统 , 于 微 处理 器 ( U) MC 的 基 D P) 基 MP 的嵌入式 系统 . 论哪 种嵌 入式 系统 , 经典 设计方 法仍 然是一 种 板级 电子 系统设 计方 法 : 先 , 无 其 首 根 据 嵌 入 式 系 统 的 设 计 要 求 , 一 定 的 设 计 规 则 , 整 个 嵌 入 式 系 统 分 成 具 有 特 定 功 能 的 若 干 个 功 按 将 能模块 , 处 理器 模 块 、 号采 集 模块 、 行 机 构控 制模 块 等 ; 后 , 据 系 统模 块划 分 的结 果 , 如 信 执 然 根 选 择 现 成 已商 品 化 的模 块 或 自行 研 制 各 功 能 模 块 ; 后 , 这 些 模 块 组 合 成 一 个 完 整 的 嵌 入 式 系 统 . 最 把 随 着 集 成 电 路 技 术 的 发 展 , 嵌 入 式 系 统 小 型 化 、 型 化 等 方 面 的 要 求 越 来 越 高 , 入 式 系 统 的 核 对 微 嵌

量 , 少 了 电 磁 兼 容 问 题 , 高 了 系 统 的 可 靠 性 . P D/ P 减 提 C L F GA 的 可 编 程 能 力 , 使 得 C L F G 还 P D/ P A 不仅 能实现 一个高 度 复杂 的 系统 , 且 能快 速改变 系统 的特性 . 而 片 上 可 编 程 系 统 S C 在 电 子 设 计 技 术 上 给 出 了 一 种 以 人 的 基 本 能 力 为 依 据 的 软 硬 件 综 合 解 OP

PSoC5:可编程片上系统

10 2 mA- 2 0 1 7 mA。该元器件包括 铁氧体磁芯 ,工作温度 范

围为 一 5 ~ 1 Oc,ML 0 0还提供 自定义配置 。该 5℃ +3 o RF 1 1

G S和锂离子便携设备。 P 瞄团目固

Faichi r l l Il f r hid d ^ ^1 aic l sem Lc n , , or

\ ≤

. .

无源元件

的峰值效率 ,同时在 1 A m 轻 负 载 条 件 下 保 持 超 过 8 % 的效 率。当电池 电压 6 接近其 范围的较低端 时 ,

ML 1 1 : RF 0 0RF电感

Go n a Ee t nc wa d lcr i o s推 出 符 合 QP L军 事 认 证 的 小 型 RF电 感 ,ML F 1 1 F电 感 系 列 尺 寸 为 R 0 0R 25 mm .4 .4 X 5 mm,符 合 MI— R 一 3 4 /4标 准的 QP 2 L P F8 4 60 L

F AN5 6 : 压 转 换 器 3 2降

飞兆半导体公 司推出一款 采用专有 的同步整流架构 的

台包括 了开发工具 、样片和 P o rao。 S C C e tr

P o S C 5架构 有 P o e tr S C Crao 集成 开发 环境 提 供支

3 z5 0 MH 0 mA同步 降压 转换 器 产 品 F 5 6 ,适 用 于需 AN 3 2

ML O 0RF设 计 用 于 军 事 、航 空 航 天 和 国 防 RF 1 1 R F应 用 中。该 表 面 贴 装 器 件 电感 值 为 00 p - 7 H, .1 H 2 p

感共 用时 ,可选 择 占用 线路板空 间较少 、成 本较低 的片状

SOPCBuilder使用简介

第5讲 SOPC Builder开发工具

SOPC Builder可以快速地开发定制新方案,重建已 经存在的方案,并为其添加新的功能,提高系统的性 能。通过自动集成系统组件,SOPC Builder允许用户将 工作的重点集中到系统级的需求上,而不是从事把一 系列的组件装配在一起这种普通的、手工的工作。所 有版本的Altera Quartus Ⅱ的设计软件都已经包含了 SOPC Builder。设计者采用SOPC Builder,能够在一个 工具内定义一个从硬件到软件的完整系统,而花费的 时间仅仅是传统SOC设计的几分之一。

第5讲 SOPC Builder开发工具 3. 开放性 SOPC Builder开放了硬件和软件接口,允许第三方

像Altera一样有效地管理SOPC部件,用户可以根据需要 将自己设计的部件添加到SOPC Builder 的列表中。 5.1.4 SOPC Builder的优点

(2) 由于SOPC具有基于EDA技术标准的设计语言与系 统测试手段、规范的设计流程与多层次的仿真功能以及高 效率的软硬件开发与实现技术,使得SOPC及其实现技术 无可争议地成为现代电子技术最具时代特征的典型代表。

第5讲 SOPC Builder开发工具

Application Specific Integrated Circuit 专用集成电路

1. 具有直观的图形用户界面(GUI) 利用图形用户界面,用户可以快速方便地定义和连 接复杂的系统。如图5.1所示,用户可从左边的库中添加 所需的部件,然后在右边的表中配置它们。

第5讲 SOPC Builder开发工具 图5.1 SOPC Builder的图形用户界面

第5讲 SOPC Builder开发工具

Nios/Nios Ⅱ嵌入式软核处理器。所有的Quartus Ⅱ 用户都能够把一个基于Nios/Nios Ⅱ处理器的系统经过生 成、仿真和编译进而下载到Altera FPGA中,进行实时评 估和验证。

可编程片上系统项目化教学设计探讨

1 . 引 言

其 他 资 源 完 成接 口 以及 S O P C , S y s t e m 0 1 3 a F P G A 的优势 。 因此 ,本文 进 行基 于F P G A的 嵌 入 I P 软 P r o g r a m m a b l e C hi P ) 结 合 了S O C( 片 上 系 统) 和P L D( 可 编 程逻 辑 器 件 ) 、F P G A( 现 场 核的S O P C 开发 的教 学设计 。

四川交通职业技 术学院 自 动化 工程 系 张丽霞

ZH AN G Li —xi a

( S i c h u a n Vo c a t i o n a l a n d Te c h n i c a l Co l l e g e o f Co mmu n i c a t i o n s De p a r t me n t o f a u t o ma t i o n e n g i n e e r i n g , Ch e n g d u,s i c h u a n p r o v i n c e ,6 1 1 1 3 0)

o f he t c o u r s e ,a n dma d e d i s c u s s i o n a b o u t d e s i g n o f p r o j e c i f z e dt e a c in h g a c c o r d i n gt h e p r a c d c  ̄s i t u a t i o n o f o u r s c h o o l Ke y wo r d s :S OP C:p r o j e c i f z e d t e a c h i n g ;NI OS Ⅱ

I 一 数学鳗地………………………….

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计流程及EDK工具 - Platform Generator(Platgen)

Platgen读取MHS文件作为基本的设计输入。Platform 也从EDK库和用户IP库中读取不同的处理器核硬件描述文 件(MPD,PAO)。 Platgen为嵌入式系统产生顶层HDL设计文件,该文件 包含所有参数化了的IP核。 在这个过程中,将MHS中所有高层总线连接变成连接 处理器、外设和片上存储器的真实信号。它也调用XST编 译器综合每个例化的IP核(Platgen产生的系统级网表也用 来作为FPGA实现过程的一部分)。 此外,Platgen也产生BMM(BRAM Memory Map)文 件,该文件包含所用到的片上BRAM的地址。

软件统计分析 芯片配置

芯片配置

图5.1 EDK嵌入式设计流程

设计流程及EDK工具 -建立硬件平台

Xilinx的FPGA技术允许设计者在处理器子系统中定制 硬件逻辑。这种定制不可能使用标准的现成的微处理器或 控制器芯片。“硬件平台”是指设计人员根据应用的需要 而 使用Xilinx的技术建立的灵活地、嵌入式处理子系统。 硬件平台是由一个或多个处理器或外设连接到处理器 总线构成的。 EDK通过微处理器硬件规范(Microprocessor Hardware Specification,MHS)文件记录硬件平台信息。

可编程片上系统开发平台

何宾 2012.02

本章内容

该章描述在Xilinx嵌入式开发套件(Xilinx Development Kit,XDK)嵌入式系统工具的结构和设计流 程。XDK用于开发基于MicroBlaze软核和PowerPC硬核处 理器的SOPC系统。该章的主要内容包括:EDK简介、设 计流程概述、平台开发结构的工具。 Xilinx的EDK工具主要包含:Xilinx Platfrom Studio (XPS)人机界面、嵌入式系统工具套件、嵌入式处理IP 核,例如处理器和外设、 Platform Studio SDK(Software Development Kit,SDK)。SDK基于Eclipse开放源码框 架,可以选择使用SDK开发自己的嵌入式软件应用程序 (从EDK13.1开始,必须在SDK内开发软件应用程序)。

设计流程及EDK工具 -芯片配置

一旦软件和硬件平台建立完成,设计人员可以为FPGA 建立一个的配置比特文件。 对于原型设计,当连接主机和芯片时,设计者可以在 下载比特流时,将希望运行在嵌入式平台上的软件同时下 载。 对于产品,设计人员将配置比特流和软件保存在和 FPGA连接的非易失性存储器中。

设计流程及EDK工具 -EDK工具

设计流程及EDK工具 - Platform Generator,Platgen

平台产生器Platgen将对嵌入式系统的高级描述编译成能 在目标FPGA芯片上实现的HDL网表。 嵌入式系统硬件平台典型的由一个或多个处理器和不同 的外设和存储器模块组成,这些模块通过处理器总线连 接。每个外设的IP核有很多的参数,通过调整这些参数来 定制行为。这些参数也用来为这些存储器和外设进行地址 映射。由于EDK提供可选择的特性,FPGA只需要实现应用 程序所要求的功能子集。 硬件平台保存了MHS文件。MHS文件是表示所设计的 嵌入式系统的硬件元件的最主要文件。MHS文件以ASCII码 形式存在。

Configure Coprocessor Wizard Platform G具 -EDK工具

软件开发 Library Generator(Libgen) GNU Compiler Tools(GCC) 验证 Xilinx Microprocessor Debugger(XMD) GNU Debugger(GDB) Simulation Model Generator(Simgen) Simulation Library Compiler(CompEDKLib) Bus Functional Model Compiler(BFM) 打开shell用于软件下载和调试,也提供通道用于 GNU调试器访问设备。 调试软件的GUI,基于仿真模型或目标设备。 产生硬件仿真模型和编译脚本文件用于对完整系 统的仿真。 在开始对设计进行仿真时,为目标仿真器编译 EDK仿真库。 通过建立一个总线环境的模型去代替真实的嵌入 式系统来帮助简化定制外设的验证。 构建一个软件平台,该软件平台由定制的软件库、 驱动程序和OS构成。 基于库产生器建立的平台,建立软件应用程序。

设计流程及EDK工具 -使用仿真的硬件平台验证

验证硬件平台的正确功能,设计人员可以建立一个仿 真模型,并且在HDL仿真器上运行。当仿真系统时,处理 器运行可执行文件。 设计人员可以选择建立行为、结构或者精确的时序仿 真模型。

设计流程及EDK工具 --使用调试的软件验证

调试嵌入式软件的基本技术是加载设计到所支持的开 发板和使用调试工具去调试处理器。 作为可选择的方式,设计人员可以使用指令集仿真器 或简化系统仿真器模型(“虚拟平台”)运行在主机上来 调 试设计代码。 设计人员可以通过概要分析代码的执行来估计系统性 能。

Format Revision(revup)Tool and Revup工具更新设计文件(例如MHS)到当前的 Version Management Wizard 版本。版本管理向导帮助将先前EDK建立的IP和 驱动更新到当前的版本。 LibXil Memory File System Generator (LibXil MFS) Platform Specification Utility 在主机上建立一个MFS存储器镜像,该镜像并被 下载到嵌入式系统存储器。 自动产生微处理器外设定义MPD数据文件,该 文件要求创建EDK兼容的制定外设。

设计流程及EDK工具 -Xilinx Software Development Kit,SDK

(7)提供现成的简单软件工程来测试硬件和软件功能; (8)通过GUI接口为软件应用程序、编程FPGA芯片和编 程并行flash存储器产生链接脚本; (9)应用程序的建立配置和自动的MAKE文件生成; (10)错误浏览; (11)为无缝调试和概要分析目标提供了好的集成环境;

设计流程及EDK工具 - Xilinx Platform Studio(XPS)

XPS提供下面的特性:

(1) 能够添加核,编辑核参数和进行总线和信号连接,产生MHS 文件; (2) 能够产生和修改MSS文件; (3) 支持表5.1内的所有工具; (4) 能够产生和观察系统块图和设计报告; (5) 多用户软件应用支持; (6) 项目管理; (7) 过程和工具流程依赖管理; (8) 输出MHS文件到SDK工具

设计流程及EDK工具 - 建立和导入IP向导

该向导帮助设计人员建立自己的外设并且将它们导入 相应的XPS工程中。 在创建模式下,创建和输入外设向导建立很多文件, 这些文件的一些是模板文件帮助设计人员实现外设,而不 需要详细的知道总线协议,命名规则和特殊接口文件的格 式。通过参考模板中的例子和使用不同的辅助设计支持文 件,设计人员可以很快的进行逻辑定制。 在导入模式下,该工具帮助设计人员建立接口文件和 目录结构。对于这种操作模式,必须遵守EDK的命名规 则。一旦导入完成,用户的定制外设在EDK外设库中可以 使用。

设计流程及EDK工具 -The Base System Builder(BSB) Wizard

BSB向导帮助设计人员快速建立一个嵌入式系统工 程。对于更复杂的工程,BSB向导提供基本的系统,通过 这个系统设计人员可以定制完成嵌入式设计。为了高效率 的建立工程,Xilinx推荐使用BSB向导。

设计流程及EDK工具 -The Base System Builder(BSB) Wizard

基于设计人员选择的板子,设计人员通过BSB选择并 配置基本的元素,比如:处理器类型、调试接口、缓存配 置、存储器类型和大小、外设等。 对于BSB不支持的目标系统,设计人员可以选择定制 板选项。使用这个选项时,必须指定未来板子的硬件,并 且要给出用户约束文件UCF。 如果选择的是支持的目标板,BSB向导自动的加入 UCF文件。当退出BSB时,BSB所建立的MHS和MSS文 件自动加入到XPS工程中,设计人员能在XPS中进行更进 一步的设计。

设计流程及EDK工具 - Xilinx Platform Studio(XPS)

XPS提供了集成环境为基于MicroBlaze和PowerPC处理 器的嵌入式处理器系统创建软件和硬件规范流程。 XPS也提供编辑器和项目管理接口用来创建和编辑源 代码。 XPS提供工具流程配置选项的定制和提供图形化的系 统编辑器用来连接处理器、外设和总线。 XPS可以在Windows、Solaris和Linux平台下使用。 从XPS中,设计人员可以运行所有的用于处理硬件和 软件的嵌入式系统工具。在XPS环境下可以进行系统的验 证。

图5.2 EDK工具的结构

设计流程及EDK工具 -EDK工具

设计环境 Xilinx Platform Studio(XPS) Xilinx Software Development Kit(SDK) EDK命令行或“非Windows”模式 硬件开发 The Base System Builder(BSB)向 导 The Create and Import IP Wizard 通过使用支持的开发板或通用的基本功能,允许设 计人员快速地建立一个嵌入式设计。Xilinx推荐 使用BSB建立最初的项目创建。 辅助设计人员添加自己的外设到设计中。建立相关 的目录或数据文件,保证外设能被EDK工具识 别。 帮助设计人员添加协处理器到CPU。 以HDL或实现的网表文件在片上构造可编程系统 集成设计环境GUI,在这个集成环境中可以创建完 整的嵌入式设计。 集成设计环境GUI,是对XPS的补充,用来帮助设 计人员开发软件应用功能(从13.1开始,专用 于软件应用的开发)。 允许设计人员运行嵌入式设计流程或从命令行改变 工具选项。

设计流程及EDK工具 -Xilinx Software Development Kit(SDK)