基于Quartet测试系统的高速DAC芯片测试

test造句简单

test造句

1、We designed the experiment to test the new drug.

我们计划用这个试验来检验这种新药。

2、Testing of High Speed DAC Chipset by using Test System Quartet

基于Quartet测试系统的高速DAC芯片测试

3、There is a new aero package that's coming for the last test in Jerez that will improve the car.

在Jerez进行的最后一次测试中我们新的空力套件将面世,那将对赛车有所改进。

4、Industry Test of KC Flotation cell at SZY Metals Mine

柿竹园多金属矿KC浮选机工业试验

5、The research reported on applying plate agglutination test to diagnose pheasant tuberculosis.

本项研究应用平板凝集试验诊断雉鸡结核病。

6、The other parts of the EJBServletTestCase are self-explanatory and contain the actual test methods.

EJBServletTestCase的其它部分是不须说明的,它们包含真正的测试方法。

7、The design and test of digital transmission system.

数字传输系统的设计和实验。

基于FPGA的高性能DAC芯片测试与研究

基于FPGA的高性能DAC芯片测试与研究

D/A 转换器作为连接数字系统与模拟系统的桥梁,不仅要求快速、灵敏,而且线性误差、信噪比和增益误差等也要满足系统的要求[1]。

因此,研究

DAC 芯片的测试方法,对高速、高分辨率DAC 芯片的研发具有十分重要的意义。

目前,波形测量和分析协会已提出了DAC 测试的技术标准IEEE Std.1057,里面的术语和测试方法为DAC 测试提供了更多的参考。

传统的标准测试只适于信号发生器、示波器等测试仪器,但是测试精度不高;大规模芯片测试时则使用自动测试设备(ATE),但是成本很高;最近提出的DAC 的测试方法,比如结合V777 数字测试系统可以进行DAC 测试,应用模拟滤波器进行音频DAC 测试,利用数模混合信号测试系统Quartet 对高速DAC 进行测试,等等[5],这些方法在通用性、精确度和成本方面无法同时满足。

为了达到上述要求,提出了基于FPGA 的高性能DAC 芯片回路测试法。

1 DAC 主要技术参数

DAC 的主要技术参数基本上可以分为静态特性参数和动态特性参数。

DAC 的静态特性参数用来确定其转换的精确度,主要包括失调误差(Offset Error)、增益误差(Gain Error)、积分非线性误差(INL)以及微分非线性误差(DNL)等。

DAC 动态特性参数用来确定其交流条件下的性能,主要包括信噪比(SNR)、信号噪声和失真比(SINAD)、有效位数(ENOB)、总谐波失真(THD),以及无杂散动态范围(SFDR)等。

2 测试方案

2.1 设计原理

DAC 芯片参数回路测试法,就是将待测信号形成一个完整的信号回路。

高速ADC、DAC测试原理及测试方法

高速ADC/DAC 测试原理及测试方法随着数字信号处理技术和数字电路工作速度的提高,随着数字信号处理技术和数字电路工作速度的提高,以及对于系统灵敏度等以及对于系统灵敏度等要求的不断提高,对于高速、高精度的ADC ADC、、DAC 的指标都提出了很高的要求。

比如在移动通信、图像采集等应用领域中,一方面要求ADC 有比较高的采样率以采集高带宽的输入信号,另一方面又要有比较高的位数以分辨细微的变化。

因此,保证ADC/DAC 在高速采样情况下的精度是一个很关键的问题。

ADC/DAC 芯片的性能测芯片的性能测试试是由芯片芯片生产厂家完成生产厂家完成生产厂家完成的,的,的,需需要借助昂贵借助昂贵的的半导体测试仪器试仪器,,但是对于是对于板级板级板级和系统和系统和系统级级的设计人员来说设计人员来说,,更重更重要的是如要的是如要的是如何验何验何验证芯片在证芯片在板级或板级或系统系统系统级级应用应用上上的真正真正性能指标。

性能指标。

一、ADC的主要参数ADC 的主要指标分要指标分为静态为静态为静态指标和动指标和动指标和动态态指标2大类大类。

静态静态指标指标指标主主要有要有::•Differential Non-Linearity (DNL)•Integral Non-Linearity (INL)•Offset Error•Full Scale Gain Error动态指标指标主主要有要有::•Total harmonic distortion (THD)•Signal-to-noise plus distortion (SINAD)•Effective Number of Bits (ENOB) •Signal-to-noise ratio (SNR) •Spurious free dynamic range (SFDR)二、ADC 的测试方案要进行ADC 这些众多这些众多指标的指标的指标的验验证,证,基本基本基本的方的方的方法法是给ADC 的输入的输入端端输入一个理想的信号,的信号,然后然后然后对对ADC 转换转换以以后的数的数据进行据进行据进行采集和分采集和分采集和分析析,因此,,因此,ADC ADC 的性能测的性能测试试需要多台仪器多台仪器的的配合并配合并用用软件软件对测对测对测试结果进行试结果进行试结果进行分分析。

高端HIFI发烧音频DAC解码芯片排名

高端HIFI发烧音频DAC解码芯片排名本文尝试对当前最优秀的高端音频DAC芯片的结构、技术和性能等做简单介绍,作一个排名,以供大家参考。

尽管如此,任何一个优质的音频DAC芯片(无关排名),都有可能被用来实现整机的好声音。

想必,我们要客观地认识DAC芯片的重要性,更要客观地认识芯片的整机配合的重要性。

所以,本文并不提倡唯“芯”主义。

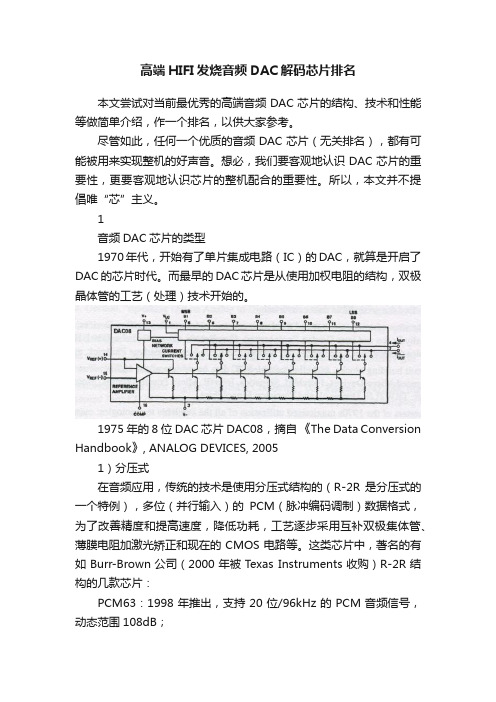

1音频DAC芯片的类型1970年代,开始有了单片集成电路(IC)的DAC,就算是开启了DAC的芯片时代。

而最早的DAC芯片是从使用加权电阻的结构,双极晶体管的工艺(处理)技术开始的。

1975年的8位DAC芯片DAC08,摘自《The Data Conversion Handbook》, ANALOG DEVICES, 20051)分压式在音频应用,传统的技术是使用分压式结构的(R-2R是分压式的一个特例),多位(并行输入)的PCM(脉冲编码调制)数据格式,为了改善精度和提高速度,降低功耗,工艺逐步采用互补双极集体管、薄膜电阻加激光矫正和现在的CMOS电路等。

这类芯片中,著名的有如Burr-Brown公司(2000年被Texas Instruments收购)R-2R结构的几款芯片:PCM63:1998年推出,支持20位/96kHz的PCM音频信号,动态范围108dB;PCM1702:1995年推出,20位,动态范围110dB;PCM1704:1999年推出,24位,动态范围112dB。

这些芯片都采用了一些特别手段来改善性能,如使用“符号量级(sign-magnitude)”架构在零位附近采用小的级差、互补的两套DAC电路来产生绝对的电流,激光矫正的电阻等措施,来减少过零失真和差分误差。

R-2R DAC芯片PCM1704,摘自《PCM1704 24-Bit, Datasheet》,Burr-Brown Corporation, February, 1999 Philips半导体公司(2006年与Motorola半导体合并成立成为NXP半导体公司)还推出了的数字流(串行输入)的DAC芯片如:TDA1541/TDA1541A:16位,推出时间分别为1985年和1991年,信噪比95dB和110dB,使用10位+6位的分压器,其中低位6位使用3个2位进行轮换,实现动态元件适配(DEM)功能,来降低失真,TDA1541A按差分线性误差从高到低还分为/N2/R1、/N2和/N2/S1的级别;TDA1547:1991年推出,1位(支持20位PCM信号),信噪比113dB,动态范围108dB,需与SAA7350数字流电路配合使用。

EPOCH XT型探伤仪DAC制作使用方法

EPOCH XT型探伤仪爬波使用方法1、仪器的调节设定1)按开/关键开机,仪器进行系统启动及自检,50秒钟后进入实时分屏显示屏幕。

2)按测量设置键,通过→键,把光标移动到选项,按确认键两次,再按F1键关闭ASME,按测量重置键返回。

3)连续按确认键,将光标移到时间,通过→←↑↓键,调探伤方式为DUAL (一发一收模式)4)按声速键,通过→←↑↓键,调节声速为6350m/s5)按角度键,通过→←↑↓键,调节角度为82.0度2、作DAC曲线:1)预置空间:按2ndF键、ID键,按→键,按确认键选递增,再按确认键,在文件光标里输入文件名,输入后按确认键,前缀可以输0,也可以不输,按↓键,将起始点输入1,按F1键创建。

2)按确认键,按→←↑↓键,将光标移动到刚才建的文件名,按F1键,打开。

3)调比例尺:探头前沿对准标准瓷试块1mm深的人工割口,使波幅落在1格线上,往后拉动探头到4mm的距离,此时的波幅落在8格上,落不到时调整零位键及范围键(范围键的值根据经验:横坐标一格代表5mm时为50;横坐标一格代表10mm时为100),零位键为波形左右平移键,范围键为设置测量范围键,反复调整几次使之符合要求,比例尺调整完毕后,此时从1格开始向右,每格代表工件上的距离5mm.4)调灵敏度:采用标准瓷试块,将探头置于试块,找出距探头前沿1mm深度模拟裂纹的最强反射波,调整至90-95%波高,即为探伤灵敏度。

5)作DAC曲线:按测量设置键,通过→键,把光标移动到选项,按确认键两次,再按F2键打开ASME,按测量重置键返回。

在距探头前沿0mm深度1mm 模拟裂纹90-95%波高,按闸门键使红色闸门压在伤波波形上,按F1键,伤波尖波出现×,往后拉动探头5mm,使伤波在2格出现(出现的位置应为衰减8-10dB),再把探头拉动到30mm,使伤波在6格上,依次类推,直到40mm,作完DAC曲线后,按F2键完成,按保存键保存。

高速高精度DAC关键性能测试方法研究

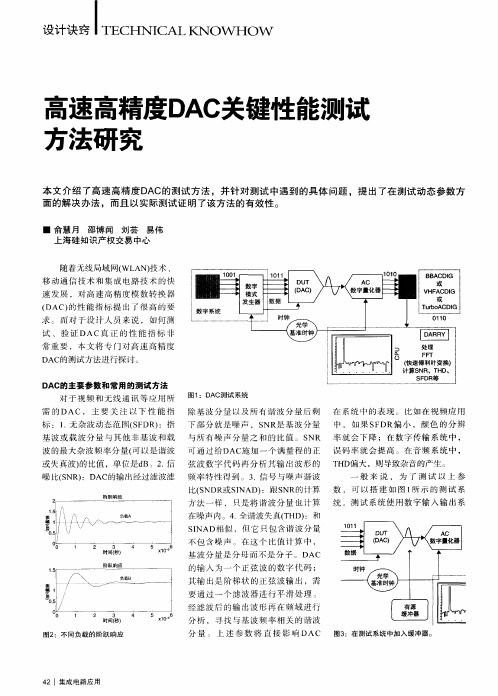

阶跃 响应

的输人为一个正弦波的数字代码 ; 其 输 出是 阶 梯 状 的 正 弦 波 输 出 ,需 要通过一个滤波器进行平滑处理 。 经 滤 波 后 的 输 出 波 形再 在 颁 域 进 行

分 析 ,寻 找 与 基 波 频 率 相 关 的 谐 波

■ 俞 慧 月 邵博 闻 刘芸 易伟 上 海 硅 知 识产 权 交易 中心

随着无 线局 域 网( A 技 术 、 WL N) 移 动 通 信 技 术 和 集 成 电 路 技 术 的 快

速 发 展 ,对 高 速 高 精 度 模 数 转 换 器

( DAC) 的性 能 指 标 提 出 r很 高 的 要

所  ̄( NDP或 SNAD1 S . I :跟s NR的计 算 数 , 可 以 搭 建 如 图 1 示 的 测 试 系

方 法 一 样 , 只是 将谐 波 分 量 也 计 算 统 。测 试 系 统 使 用 数 字 输 入 输 出系

在 噪声 内。4 伞谐 波 失真 (HD :和 . T )

sN 相 似 ,但 它 只包 含 谐 波 分 量 I AD 不 包 含 噪 声 。 在 这 个 比值 计 算 中 ,

需 的 DAC,主 要 关 注 以 下 性 能 指 除 基波 分 量 以及 所 有 谐 波分 量 后 剩 在 系 统 中的 表 现 。 比如 在 视 频 应 用

标 :1 无 杂 波 动态 范 同( F . S DR) :指 下 部 分就 是 噪声 ,S NR是 基 波 分量 中 , 如 果 S DR 小 ,颜 色 的 分 辨 F 偏

在 的问题

不 确 定 的 负 载 ,导 致 不 能 确 定 内置 (cieb f r 解决 驱动 负载不 确定 at uf ) v e来 在 一 定 的时 间 内稳 定 下来 。这 样 系

一种高速DAC测试系统和方法[发明专利]

![一种高速DAC测试系统和方法[发明专利]](https://img.taocdn.com/s3/m/b406239ddc3383c4bb4cf7ec4afe04a1b071b0c9.png)

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 201710182502.4(22)申请日 2017.03.24(71)申请人 厦门优迅高速芯片有限公司地址 361000 福建省厦门市软件园二期观日路52号402(72)发明人 肖翔 陈哲 赵龙 李豹 程玉华 高泉川 黄秋伟 (74)专利代理机构 厦门市首创君合专利事务所有限公司 35204代理人 连耀忠 林燕玲(51)Int.Cl.H04B 10/077(2013.01)H04B 10/61(2013.01)H04B 17/20(2015.01)H04B 17/391(2015.01)H04B 17/336(2015.01)H04B 1/00(2006.01)(54)发明名称一种高速DAC测试系统和方法(57)摘要一种高速DAC测试系统和方法,包括:仿真模块,用于产生DP-QPSK数据流,实现DP-QPSK编码调制、解码和恢复,进行比对实现测试;任意波形发生器,用于接收DP-QPSK数据流,输出时钟信号;码型发生器,用于接收DP-QPSK数据流,输出低速数字信号及控制信号;高速缓存电路,用于将低速数字信号转换为高速数字信号;高速DAC,用于根据时钟信号将高速数字信号转换为高速模拟信号;高速示波器,用于将高速模拟信号发送至仿真模块。

本发明的系统和方法单独对高速DAC进行测试,实现方式和方法简单、成本低。

权利要求书2页 说明书5页 附图2页CN 107171718 A 2017.09.15C N 107171718A1.一种高速DAC测试系统,包括仿真模块,包括DP-QPSK信号源单元、DP-QPSK单元和光接收机,该DP-QPSK信号源单元用于产生DP-QPSK数据流,该DP-QPSK单元用于实现DP-QPSK编码调制得到DP-QPSK调制光信号;该光接收机与DP-QPSK单元相连以将DP-QPSK调制光信号进行解码和恢复;任意波形发生器,与仿真模块相连以接收DP-QPSK数据流,输出时钟信号;码型发生器,与仿真模块相连以接收DP-QPSK数据流,输出低速数字信号及控制信号;高速缓存电路,与码型发生器相连,用于将低速数字信号转换为高速数字信号;高速DAC,与任意波形发生器和高速缓存电路相连,用于根据时钟信号将高速数字信号转换为高速模拟信号;高速示波器,与高速DAC相连,用于将高速模拟信号发送至仿真模块;仿真模块接收高速模拟信号,结合DP-QPSK单元实现DP-QPSK编码调制,经光接收机进行信号解码和恢复,将恢复的信号与DP-QPSK数据流进行比对实现测试。

一种高精度dac芯片的设计

研制开发图1电容式DAC电路图电容阵列式DAC除了需要电源电压和地电压外,还需要一个标准的参考电压,这个电压要求要能够输出非常稳定的电压值作为参考使用。

在本设计中我们采用标准带隙基准来作为参考电压提供源。

电路结构所示。

该结构为一种普通带隙基准电路,能够提供的稳定电压。

· 11 信号仿真为该电容式DAC的总体仿真结果图。

图3电容式DAC仿真结果图仿真时间周期为520 μs,图3中下方为8位输入信号,在时间0时刻,输入信号从高位到低位均为0,到520 μs处走完一个周期,8位输入信号均为1。

即从“00000000”逐次增加到“11111111”,增量步长为1,共256步。

图3中上方斜线为DAC输出电压值。

从图3中可以明显看到,随着输入8位信号的逐步增加,输出信号呈现明细那逐步上升态势,且线性度良好,斜率稳定。

根据实际数据与理想曲线非线性误差,可得微分非线性公式(DNL)有:DNL(q)=x(q)-1LSB (1)其中,x(q)为输入信号码的实际台阶高度,对于每个输入信号,DNL都有:-1LSB<DNL(q)<1LSB (2)而微分非线性误差积分总量即积分非线性INL公式如下:()()1qiINL q DNL i−==∑且有:INL(0)=0此外,DAC还具备静态误差和分辨率,其最小值为1LSB。

动态特性反映了DAC对于数字输入信号的响应速度快慢。

3 版图设计完成了电路设计并通过仿真确认设计正常之后,还需要将所设计的电路转化为版图才能用于集成电路生产。

图4为根据本文所设计DAC电路绘制的版图图4电容式DAC版图图2本文所用的带隙基准电路结构图(下转第14页)· 12 ·分布式交易平台PC端交易系统APP数据接口服务接口服务接口区块链节点交易节点负载均衡发电用户居民用户工/商用户交易单元补贴表交易单元计量表交易单元计量表区块链节点区块链节点数据节点数据节点4 结 论[3] Alan Hastings.模拟电路版图的艺术[M ].张为,译.北京:(上接第12页)。

一种高效的超高精度dac的合成方法及装置

一种高效的超高精度dac的合成方法及装置一种高效的超高精度DAC(数字模拟转换器)合成方法及装置是指可以将数字信号转换为模拟信号的装置,并且能够实现非常高的精度和效率。

该装置的合成方法主要包括以下几个步骤:1. 数字信号输入:将需要转换的数字信号输入到DAC装置中。

数字信号可以通过各种传输方式传输,例如串行或并行输入。

2. 数字信号解码:DAC装置将输入的数字信号进行解码,将其转换为二进制码。

3. 输出电压量化:经过解码的二进制码将被转换为相应的电压值。

这个步骤需要使用一组合适的参考电压,并对其进行量化操作,以确保输出电压的精度和稳定性。

4. 数字到模拟转换:量化后的电压值将通过一组可变增益放大器或可编程增益放大器进行放大。

这些放大器可以根据需要调整放大倍数,以实现更高的精度和精确的输出。

5. 模拟滤波:放大后的电压信号可能会包含一些高频噪音或杂散信号。

为了去除这些信号,需要进行模拟滤波操作,使用一些滤波器或低通滤波器来去除非基频成分。

6. 输出模拟信号:经过滤波和调整后的电压信号将作为输出模拟信号供外部使用。

输出电压可以通过一组输出电缆或连接器传输到其他设备或系统。

除了上述的合成方法,高效的超高精度DAC装置还应该具备以下几个特点:1. 低噪声:为了实现高精度的信号转换,DAC装置应该具备较低的噪声水平。

这样可以保证输出的模拟信号不会受到噪声的干扰,从而提高转换的精度。

2. 高线性度:DAC装置应该具备较高的线性度,以保证输入数字信号和输出模拟信号之间的对应关系是准确的。

这样可以避免非线性失真,提高转换精度。

3. 高速率:高效的DAC装置应该具备较高的转换速率,可以快速将输入的数字信号转换为模拟信号。

这样可以提高转换的效率和响应时间。

4. 低功耗:为了提高装置的能效,高效的DAC装置应该具备较低的功耗。

这样可以减少能源消耗,并且降低系统的热量产生,提高系统的可靠性和寿命。

综上所述,一种高效的超高精度DAC的合成方法及装置包括数字信号输入、数字信号解码、输出电压量化、数字到模拟转换、模拟滤波和输出模拟信号等步骤。

sigma delta dac 数字预失真

Sigma-delta DAC(数字模数转换器)是一种常用于数字音频系统中的重要器件,其原理和工作方式对于理解数字音频处理技术至关重要。

本文将从基本概念、原理和应用等方面对sigma-delta DAC进行介绍,希望能够为读者提供一些有益的信息和知识。

1. 基本概念Sigma-delta DAC是一种利用sigma-delta调制技术实现数字到模拟转换的器件,通常用于数字音频系统中,其主要作用是将数字信号转换为模拟信号,从而实现声音的输出。

相比传统的DAC,sigma-delta DAC具有更高的分辨率和更低的失真,因此在音质上有着更好的表现。

2. 原理Sigma-delta DAC的工作原理主要基于sigma-delta调制技术,其核心思想是通过高速采样和高阶过采样来实现信号的数字化和噪声的抑制。

具体来说,sigma-delta DAC首先对输入的数字信号进行高速采样,然后通过一个带有负反馈的积分器将其进行过采样,并且将过采样后的信号与输入信号进行比较,最后将比较结果转换为模拟信号输出。

这种工作原理能够有效地抑制量化噪声和失真,提高输出信号的质量。

3. 应用Sigma-delta DAC广泛应用于各种数字音频系统中,例如CD播放器、数字音频放大器、数字音频接口等。

由于其高分辨率和低失真的优势,sigma-delta DAC在音频领域有着重要的地位,能够为音频系统的性能和音质提供良好的支持。

sigma-delta DAC是一种重要的数字音频器件,其通过sigma-delta调制技术实现高质量的数字到模拟转换,具有较高的分辨率和较低的失真,应用广泛。

希望本文能够为读者提供一些有益的信息和知识,帮助大家更好地了解和理解这一领域的技术。

Sigma-delta DAC技术是一种在数字音频系统中广泛应用的数字到模拟转换技术。

在其应用中,有一些特定的优势和特点,例如高分辨率、低失真和广泛的应用领域等。

本文将进一步介绍sigma-delta DAC技术的优势和应用,并探讨其在数字音频系统中的未来发展趋势。

高精度ADC和DAC转换器测试平台开发

The program has devoloped the DSP,CPLD and C8051 firmware, realized the test patten generation and the test result analysis.

The actual test and the movement result indicated that this principle of design analysis is correct, each technical specification of this test equipment satisfies the design requirements.

Keywords DAC;DSP;Coherent Sampling

- II -

哈尔滨工业大学工程硕士学位论文

目录

摘要 ......................................................................................................................................I Abstract............................................................................................................................... II

基于Quartet测试系统的高速DAC芯片测试

基于Quartet测试系统的高速DAC芯片测试

赵步云;管杰;戴昌培

【期刊名称】《电子工业专用设备》

【年(卷),期】2005(34)8

【摘要】介绍了通用DAC芯片的主要测量参数及其测试方法.并以12-bit高速DAC芯片ISL5861为例,利用Credence公司的数模混合信号测试系统Quartet 实现对高速数模转换芯片进行测试.

【总页数】6页(P37-42)

【作者】赵步云;管杰;戴昌培

【作者单位】北京半导体行业协会测试中心,北京,1000;北京半导体行业协会测试中心,北京,1000;北京半导体行业协会测试中心,北京,1000

【正文语种】中文

【中图分类】TN606

【相关文献】

1.基于ISO14443A协议的RFID集成电路芯片测试系统的研究设计分析 [J], 贾应炜

2.基于DSP和LabVIEW的1553B总线芯片测试系统的设计与实现 [J], 孙先松;王鲁涛

3.基于RT-Thread操作系统的LPDDR4芯片测试系统设计 [J], 陈鑫旺;马茂松;刘建斌

4.基于虚拟仪器的RFID芯片测试系统 [J], 刘春来;张东;赵永峰

5.基于FPGA的存储芯片测试系统设计 [J], 王展意

因版权原因,仅展示原文概要,查看原文内容请购买。

一款发烧DAC音频解码器的设计与制作

⼀款发烧DAC⾳频解码器的设计与制作⼀款发烧DAC⾳频解码器的设计与制作摘要:随着数字⾳频时代的来临,数字⾳源也不断丰富,然⽽这些数字⾳频设备内建的DAC采⽤⼀体化设计,易受⼲扰,解码出来的声⾳并不尽⼈意。

⼀般的数字⾳源如CD、DVD、⽹络机顶盒等都配备了光纤和同轴输出接⼝,把数字⾳频信号绕开机内的DAC,直接送到专门的⾳频解码器,由专门的解码器完成D/A转换,实现声⾳的⾼保真重放。

本⽂本着hi-fi的设计原则,设计⼀款⽴体声DAC⾳频解码器,由LM317、TL431组成多路甲类并联稳压供电,采⽤经典的⾼性能的CS8412-CP负责数字信号的接收与解调、DF1700P数字滤波、R-2R架构的PCM1702-K做D/A转换、挑选发烧运放担任I/V和LPF,完成数字信号的接收并转换成⾼保真的⾳频信号,再通过⼀级电⼦管校⾳线路,输出驱动信号可以直接推动后级的甲类晶体管功放。

实现hi-fi 效果的重放。

关键词:DAC⾳频解码器 PCM1702-K 电⼦管校⾳⾼保真甲类并联稳压1. 引⾔:⼀些低中档数字⾳源输出的⾳频声⾳⽣硬,数码声重,⾳质刺⽿烦躁,不耐听,满⾜不了⾳响发烧友的听觉需求。

主要是因为这些机器内建的⾳频DAC性能差,模拟滤波、放⼤器件普通,供电也过于简单造成。

好在这些机器⼀般都配有光纤或者同轴输出端⼝,提供数字⾳频信号输出,供⾼档的DAC⾳频解码还原⾼保真的声⾳。

有动⼿能⼒的烧友都喜欢DIY⼀台⾼性能的DAC⾳频解码器以重放hi-fi的⾳响效果,满⾜⾃⼰的听觉需求。

2. DAC⾳频解码器电路的设计2.1 DAC⾳频解码器电路组成DAC⾳频解码器由数字信号接收器、数字滤波器、D/A转换器、I/V转换器、LPF滤波器将数字⾳频还原还原成模拟⾳频信号,再通过电⼦管组成的和⽥茂⽒线路校⾳、开机延迟吸合电路控制输出模拟⾳频信号推动后级功放。

电路的组成及其信号流如图1:图1 DAC⾳频解码器组成及信号流程2.2 数字信号接收与⾳频解码电路数字信号的接收与解码电路关系到⾳频信号还原的质量,想要得到⾼保真的声⾳,必需采⽤⾼性能的器件担当⾳频DAC解码的重任,这是重点部分,电路原理图见图2,下⾯对其原理作进⼀步的分析:2.2.1 数字信号接收器数字信号接收采⽤美国CRYSTAL公司的带有PLL的解调芯⽚CS8412-CP担任,能⾃动识别32K-48K采样率。

高精度音频∑-ΔDAC的设计

高精度音频∑-ΔDAC的设计邓玉清;唐宁;曹杰【期刊名称】《电视技术》【年(卷),期】2011(035)007【摘要】In this paper, an efficient way to 18 bit signa-delta digital-to-analog converter (DAC) intended for protable digital-audio is presented. The oversampling ratio of interpolation filter is 128 with the sample rate of 48 kHz and the resolution of 18 bit, and ∑-Δ modulator adopts structure of 4 order and 3 bit output, MASH architecture.With ModelSim EDA tools, the simulation results illustrate that the design gives out the feasibility of program.%提出了一种用于音频领域的18 bit∑-ΔDAC设计,其中采样率为48kHz的18bit数据经过插值滤波器的过抽样率为128,∑-Δ调制器选用4阶3bit输出的MASH结构,在Matlab下进行了系统仿真,测试结果表明方案可行.【总页数】3页(P56-58)【作者】邓玉清;唐宁;曹杰【作者单位】桂林电子科技大学通信与信息学院,广西桂林,541004;桂林电子科技大学通信与信息学院,广西桂林,541004;桂林电子科技大学通信与信息学院,广西桂林,541004【正文语种】中文【中图分类】TN912【相关文献】1.高精度∑-△音频DAC省面积插值器的设计与ASIC实现 [J], 付洁;邹月娴2.18位高精度音频∑-△DAC设计 [J], 徐双武;白天蕊;胡纯意;陶而芳;杨修3.音频通信中过采样DAC设计及FPGA实现 [J], 苏航;吴召平;苗东亮4.24位高精度音频ΣΔDAC [J], 黄薇;郑士源5.一种面积优化的高精度音频∑-△DAC数字前端实现 [J], 黄春波;张涛因版权原因,仅展示原文概要,查看原文内容请购买。

dac曲线实验报告

dac曲线实验报告DAC曲线实验报告实验目的:通过实验观察和分析DAC(数字模拟转换器)曲线的特性,了解DAC的工作原理和性能。

实验原理:DAC是一种用于将数字信号转换为模拟信号的电路器件,它常用于数字系统和模拟系统之间的接口。

DAC曲线是指DAC输出的模拟电压与输入数字代码之间的关系曲线,通过观察DAC曲线可以了解DAC的线性度、分辨率、非线性误差等性能指标。

实验装置:实验中使用的DAC芯片为AD5570,实验装置包括信号发生器、示波器和数字万用表。

实验步骤:1. 将信号发生器的正弦波输出接入DAC的数字输入端,并将DAC的模拟输出端接入示波器。

2. 通过信号发生器调节输入信号的频率和幅值,观察示波器上的模拟输出波形。

3. 使用数字万用表测量DAC输出的模拟电压值,并记录下相应的数字输入代码。

4. 根据测得的数据绘制DAC曲线。

实验结果:通过实验观察和测量,得到了AD5570 DAC的曲线特性。

在不同的数字输入代码下,DAC输出的模拟电压与输入代码之间存在一定的线性关系,但同时也存在一定的非线性误差。

此外,随着输入代码的增加,DAC输出的模拟电压也会逐渐增加,但存在一定的分辨率限制。

实验分析:通过实验结果的分析,可以得出DAC的性能指标,包括线性度、分辨率、非线性误差等。

对于实际应用中,需要根据具体的要求选择合适的DAC芯片,以满足系统的性能要求。

结论:通过本次实验,我们对DAC的工作原理和性能有了更深入的了解,同时也掌握了实验测试DAC曲线的方法和技巧。

这对于我们在数字系统和模拟系统的接口设计和应用中具有重要的指导意义。

总结:DAC曲线实验报告详细介绍了DAC的工作原理、实验步骤、结果分析和结论,帮助读者更好地理解DAC的特性和性能。

通过实验结果的分析,可以为实际应用中的DAC芯片选择和设计提供参考。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

;B1),3.) :>8EGHM6F= E@= CAGAL=E=G A8M E=DE E=F@8HNHB7 HI FHLLH8 (*?O *8M <8 E@<D CAC=G >PNN <8EGHM6F= @HQ EH 6D= E@= E=DE D7DE=L R6AGE=E EH E=DE @<B@ DC==M L<S=M D<B8AN F@<CD=E T7 6D<8B >KU#’-& &! $T<E &1"VKWX ?V4KX @<B@ DC==M ()* FH8Y=GE=GO E’CF+,0 :3<B@ DC==M ()* FH8Y=GE=GZ *[9)*?WZ +=DE<8B HI L<S=M D<B8AN F@<CD=E

65’5 -. 64:%’54 9/:1/.’ <Z(<2.’024 6YI 6;< ;.542: Q5[/F201 Y’%4%’"

7

87 9:$) ;<6 5=>?@A8 测试

7B8 芯片概述 -9?8KA> 是 >) 位 、 >L@E9M、 高速低功耗 <EN9 6(; 转换器。特别为高性能 通讯系统设计,例如用于 )O8 P 或 L P 无线通讯收发 Q<6E;, I6<6E; 机 站 , 等。此芯片的特点是高速低 功耗,采样频率最高可达 >L@EJR, )@ 1; 在 >L@ EJR、 时, 功耗为 >@L 1Q。此芯片

"!

F23!%

)! F23*#

! 为幅值)6B9P10Q,*。公式中分母的 F23#,-R 式中: , !%R#R;…… )#* 信 号 噪 声 和 失 真 比 (EI&+ .7 EKI’&) : EI&+ 是基波与噪声和失真的比值。它表现了基波 的幅值与所有其他频率幅值的比率。 经 44S 变换得 到除基波外的其他所有信号的值: ! F23M EKI’& ! #>/.8

电子工业专用设备

!"#$%&’() *+, !-’.),+($. /,+0#.)1 23(#*3.)#,$(4

56 芯片测试

基于 Quartet 测试系统的高速 DAC 芯片测试

赵步云, 管杰, 戴昌培

( 北京半导体行业协会测试中心, 北京 !""" ) 摘 要 : 介 绍 了 通 用 ’() 芯 片 的 主 要 测 量 参 数 及 其 测 试 方 法 。 并 以 %"*+,- 高 速 ’() 芯 片

’ "%

"!

F23!%

)! F23*#

式中:分母中 F23 #-。注意到分母的总和中没有 F23 >, 因为 F23 > 是直流分量, 既不包含噪声也不包 含谐波数据, 同样分母中也不包含 F23 -, 因为它是 基波。分子则是 F23 - 的幅值。 );* 全部谐波失真 (ST&) :与运算放大器中 ST& 参数的含义相同, 但与 &’( 中 ST& 的测量方 法不同, 因为其输出的模拟信号是离散的。将正弦 波的二进制代码送到 &’( 输入端, 则在 &’( 输出 端的模拟信号经防混滤波和波形数字化, 而输出波 形采样值, 再经 44S 变换得到 &’( 输出波的频谱, 在频域中进行分析, 找出任意一个含有谐波的信号 与基波的关系:

56 芯片测试

!"#$%&’ 频率 ($%()) 。 *+, 互调失真(-.’/0123$45’%2. 6%&’20’%2.) : 互调 失真是测试出现在一个器件信号中的非谐波产生 项, 它是由一个信号中的两个频率成份的非期望的 调制引起的。此调制是被测器件的非线性特征产生 的结果。此参数的测试是通过将两个不同频率的正 弦曲线进行叠加后输入器件, 并寻找频率成份之和 及频率之差的 7%.。 *8, 建立时间(9/’’%.: ’%1/) : 对于 6;< 器件建 &&/’ 立时间 (&&/’) 是用来定量描述其转换速度的参数。 的定义是: 从输入数字量发生突变开始, 直到输出 电压进入与稳态值相差 =>() ?97 范围以内的这段 时间。因为输入数字量的变化越大建立时间越长, 所以一般产品给出的都是从全 @ 跳变为全 > 时的 建立时间。 *A, 无杂散动态范围(9B6C) 9B6C 是指基波 : 的幅值与非基波 7%. 最高幅值之比。它表现的是器 件工作的频谱下绝对噪声和无动态失真范围。同 9!C 相同, 9B6C 也是反映了器件在有噪声、 干扰或 阻塞条件下检测小信号的能力: 9B6C D )@42: ! 7%.E ! &F30G15H 对于不同的 6;< 芯片,动态参数的范围也不 IJ6、 9B6C 这几个参数的数 尽相同,特别是 9!C、 值受芯片的采样频率、 输入频率和分辨率的影响较 大。

56 芯片测试

电子工业专用设备

!"#$%&’() *+, !-’.),+($. /,+0#.)1 23(#*3.)#,$(4

经 !"# 处理器作 $$% 变换后得到被测 !&’ 输出信 号的频谱数据, 为动态参数的计算奠定了基础。 根据此芯片的特性、测试条件和 ()*+,-, 测试 系统的硬件结构对芯片的测试参数做以下分类: 接 触测试, 直流参数测试, 静态参数测试和动态参数 测试。 ./0接触测试 (’12,*3, ,-4,) : 通过对测试引脚加 载测试图形 (5*67829 :) 或使用 #;< 直接测量, 检 查其是否与测试板接触良好, 引脚与 =1*> ?1*+> 是 否有短路和断路发生,芯片内部是否有短路和断 路。 .@0 直流参数测试 (!’ ,-4,) : 包括静态 $>> 和引 脚漏电流 $8A 测试。 .B0 静态误差参数测试(",*,83 C*+*D-,-+ ,-4,) : E*DC FG= !G= 1HHI 通过加载测试图形 ,测量包括 , , 4-, -++1+ 和 J*82 -++1+ 在内的参数。 .K0 动 态 误 差 参 数 测 试 (!L2*D83 C*+*D-,-+ ,-4,) : 通 过 加 载 测 试 图 形 "M)*+-, 对 器 件 的 EF"NO%F;N、 $&==O%F;N、 #EP#O!N=&Q 进行测试。 "!E、 "G!E、 "$I 通过加载测试图形 "82-,对 "GE、 !E、 ;&J$<G!、 !’OP$$"N% 参数进行测试。其中 对于 ()*+,-, 测试系统,参数 "!E 与其他测试系统 所指的 %R! 相同,参数 "G!E 与其他测试系统所 指的 "FG&! 相同。 789 :;6 测试与系统的适配 ./0对于芯片参考电压及 "6--C ;1>- 的选择: 引 EN$=P 均与内部基准电源电压相连, 脚 EN$FP, 对 $ 的电容在与之最近的 于引脚 EN$FP 推荐用 ST/μ EN$=P 引脚为内外基准电 位置相连并接到模拟地。 压选通引脚。 接地时选用内部基准电压, 此时 % $"&!UV /T@ W,即等于内部基准电压值。当 EN$=P 引脚与 &W!! 相连时, 即接为高, 选用外部电压作为基准, & "N% 是 此时输出电流 $P<%.$)66 "3*6-0V .% $"!UX& "N%0YB@, 一个可调电阻。对于 "6--C C82 也可考虑两种方案, 当 "6--C C82 接模拟地时, 芯片正常工作, 当接 ZSTB W 时芯片进入睡眠态。 .@0 由于接触测试, F8A 和 ",*,83 F>> 测试与一般 的芯片测试差别不大, 所以在这里就不再说明。本 文将主要对动态参数, 时间参数的测试作详细的讨 40 (总第 !"# 期) ! "#$ "%%&

’ "#

ST& ! #>/.8

"!

F23!,-

)! F23*#

! F23M

;, @ ……。注意到此公式忽略了 式中: 分子中 , !#, 在 F23> 的 &( 成份,并假设感兴趣的最大频率为

电子工业专用设备

!"#$%&’() *+, !-’.),+($. /,+0#.)1 23(#*3.)#,$(4

7

9:; .+(<’,)’, ) 数 8 模转换器(

换器性能优劣的主要标志。 ()* 转换器的主要技术参数可分为静态参数 和动态参数,它们用来描述 ()* 转换器的转换精 度、 转换速度及温度特性。 ()* 转换器的转换精度通常用分辨率和转换误 差来描述。()* 转换器选定的转换基准电压 $ %& 与 称为分辨率。 最大输入码 !’$& 之比,

./0$12% 为例,利用 )3454674 公司的数模混合信号测试系统 89:3-4- 实现对高速数模转换芯片进

行测试。 关键词: 高速数模转换器芯片; 任意波型产生器 # 模拟捕捉器; 数模混合信号芯片测试

+,-"中图分类号:

* 文献标识码:

&"".$.#"%/!""#0"’$""1%$"文章编号: