超大规模集成电路工艺的后道互连寄生电容电阻的建模方法的制作技术

集成电路常用器件版图 ppt课件

PPT课件

40

(1)反相输出 I/O PAD

考虑到电子迁移率比空穴约大2.5 倍,所以, PMOS 管的尺寸比NMOS 管大,这样可使倒 相器的输出波形对称。

PPT课件

16

5.2 电阻常见版图画法

PPT课件

17

5.2 电阻常见版图画法

PPT课件

18

5.2 电阻常见版图画法

PPT课件

19

5.2 电阻常见版图画法

对于无法使用串、并联关系来构建的电阻, 可以在单元电阻内部取部分进行构建。

图7.18的实现方式。

PPT课件

20

电阻匹配设计总结

(1)采用同一材料来制作匹配电阻

电容值。

做在场氧区,电容值较小。

PPT课件

24

5.3 电容版图设计

(4)MIM电容 金属层之间距离较大,因此电容较小。

减小电容面积、提高电容值:叠层金属电容 器,即将多层金属平板垂直的堆叠在一起, 将奇数层和偶数层金属分别连在一起,形成 两个梳状结构的交叉。图7.21

PIP和MIM电容由于下极板与衬底距离较远, 寄生电容较小,精度较好。

5.2 电阻常见版图画法

2、电阻的版图设计

(1)简单的电阻版图

电 电阻阻的 的阻 阻值 值=电R阻的WL方dd 块R■数×方块电阻。

这种阻值计算比较粗糙,没有计入接触孔电阻 和头区电阻。

PPT课件

12

5.2 电阻常见版图画法

(2)高阻值第精度电阻版图 对上拉电阻和下拉电阻:对电阻阻值以及匹

《超大规模集成电路设计》考试习题(含答案)完整版分析

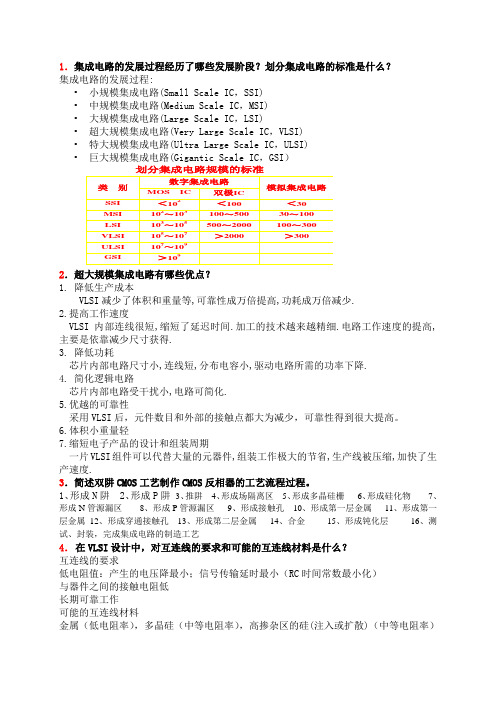

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

超大规模集成电路物理设计中的数学方法

超大规模集成电路物理设计中的数学方法超大规模集成电路(VLSI)物理设计中的数学方法主要包括以下几个

方面:

1.几何设计:VLSI物理设计需要涉及到大量的几何形状,如线、多

边形、圆等。

因此,几何设计是VLSI物理设计中最基础的数学方法之一。

几何设计主要包括计算空间坐标、几何对象的交点、物体的位置和方向等。

2.模拟电路设计:VLSI中一些电路是由模拟电路组成的。

随着工艺

的不断发展,对于更高的精度和更紧凑的布局,将意味着更复杂的电路。

因此,数学方法对于支持模拟电路设计非常重要。

3.逻辑综合:逻辑综合是将一个逻辑电路转换成该电路所需的标准器

件的转换过程。

逻辑综合算法可以用来生成RTL级代码、约束条件、特定

顺序等。

4.等效振幅的计算:在VLSI设计中,传输线中不同的信号会相互干扰,因此需要计算等效振幅来消除干扰。

等效振幅可以通过数学方法计算

得到。

5.点击方案生成:VLSI设计中需要生成变量的点击方案。

这可以通

过一种数学方法来实现,从而使设计工程师在实现的过程中能够对点击方

案进行调整和优化。

总的来说,数学方法是VLSI物理设计中的基础和重要工具,它可以

协助设计师进行更有效、更可靠和更紧凑的电路设计。

电子与通信技术:集成电路工艺原理考试资料(题库版)

电子与通信技术:集成电路工艺原理考试资料(题库版)1、问答题简述引线框架材料?正确答案:引线框架作为集成电路的芯片载体,是一种借助于键合材料(金丝、铝丝、铜丝)实现芯片内部电路引出端与外引线的电气连接,形成电气回路的关(江南博哥)键结构件,它起到了和外部导线连接的桥梁作用。

引线框架材料的要求为:热匹配,良好的机械性能,导电、导热性能好,使用过程无相变,材料中杂质少,低价,加工特性和二次性能好。

2、问答题简述MCM的概念、分类与特性?正确答案:概念:将多块半导体裸芯片组装在一块布线基板上的一种封装。

分类:MCM-L是采用片状多层基板的MCM、MCM-C是采用多层陶瓷基板的MCM、MCM-D是采用薄膜技术的MCM。

特性:尺寸小、技术集成度高、数据速度和信号质量高、可靠性高、成本低、PCB板设计简化、提高圆片利用率、降低投资风险。

可大幅度提高电路连线密度,增加封装效率;可完成轻、薄、短、小的封装设计;封装的可靠性提升。

3、问答题矩形片式电阻由哪几部分组成?各部分的主要作用是什么?正确答案:基板:基板要具有良好的电绝G8P-1A4PDC12缘性、导热性和机械强度高等特征。

一般基板的材科多采用高纯度的(96%)AL203陶瓷。

其工艺要求表面平整、划线准确,以确保电阻、电极浆料印制到位。

电极:片式电阻器一般都采用三层电极结构,最内层的是内层电极,它是连接电阻体位于中间层的是中间电极,它是镀镍(Ni)层,也被称为阻挡层,其主要作用是提高电阻器在焊接时的耐热性,避免造成内层电极被溶蚀。

位于最外层的是外层电极,它也被称为可焊层,该层除了使电极具有良好的可焊性外,还可以起到延长电极保存期的作用。

通常,外层电极采用锡一铅(S。

-PB.合金电镀而成。

电阻膜:电阻膜是采用具有一定电阻率的电阻浆料印制在陶瓷基板上,然后再经过烧结而成的厚膜电阻。

保护层:保护层位于电阻膜的外部,主要起保护作用。

它通常可以细分为封包玻璃保护膜、玻璃釉涂层和标志玻璃层。

半导体集成电路制造过程中电阻和电容的制作

半导体集成电路制造过程中电阻和电容的制作下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

半导体集成电路制造过程中电阻和电容的制作该文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document 半导体集成电路制造过程中电阻和电容的制作 can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop providesyou with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to knowdifferent data formats and writing methods, please pay attention!半导体集成电路制造是一项复杂而精密的工艺,其中包括了电阻和电容的制作。

超大规模集成电路设计导论考试题及答案

1、MOS集成电路的加工包括哪些基本工艺?各有哪些方法和工序?答:(1)热氧化工艺:包括干氧化法和湿氧化法;(2)扩散工艺:包括扩散法和离子注入法;(3)淀积工艺:化学淀积方法:1 外延生长法;2 热CVD法;3 等离子CVD 法;物理淀积方法:1 溅射法;2 真空蒸发法(4)光刻工艺:工序包括:1 涂光刻胶;2 预烘干;3 掩膜对准;4 曝光;5 显影;6 后烘干;7 腐蚀;8 去胶。

2、简述光刻工艺过程及作用。

答:(1)涂光刻胶:为了增加光刻胶和硅片之间的粘附性,防止显影时光刻胶的脱落,以及防止湿法腐蚀产生侧向腐蚀;(2)预烘干:以便除去光刻胶中的溶剂;(3)掩膜对准:以保证掩模板上的图形与硅片上已加工的各层图形套准;(4)曝光:使光刻胶获得与掩模图形相同的感光图片;(5)显影:将曝光后的硅片浸泡在显影液中,使正光刻胶的曝光部分和负光刻胶的未曝光部分被溶解掉;(6)后烘干:使残留在光刻胶中的有机溶剂完全挥发掉,提高光刻胶和硅片的粘接性及光刻胶的耐腐蚀性;(7)腐蚀:以复制在光刻胶上图形作为掩膜,对下层材料进行腐蚀,将图形复制到下层材料中;(8)去胶:除去光刻胶。

3、说明MOS晶体管的工作原理答:MOS晶体管有四种工作状态:(1)截止状态:即源漏之间不加电压时,沟道各电场强度相等,沟道厚度均匀,S、D之间没有电流I ds=0;(2)线性工作状态:漏源之间加电压Vds时,漏端接正,源端接负,沟道厚度不再均匀,在D端电位升为V d,栅漏极电位差为Vgs-Vtn,电场强度变弱,反型层变薄,并在沟道上产生由D到S的电场E ds,使得多数载流子由S端流向D端形成电流I ds,它与V ds变化呈线性关系:I ds=βn[(V gs-V tn)-V ds/2]V ds(3)饱和工作状态:Vs继续增大到V gs-V tn时,D端栅极与衬底不足以形成反型层,出现沟道夹断,电子运动到夹断点V gs-V ds=V tn时,便进入耗尽区,在漂移作用下,电子被漏极高电位吸引过去,便形成饱和电流,沟道夹断后,(V gs-V tn)不变,I ds 也不变,即MOS工作进入饱和状态,I ds=V gs-V tn/R c(4)击穿状态:当Vds增加到一定极限时,由于电压过高,晶体管D端得PN结发生雪崩击穿,电流急剧增加,晶体管不能正常工作。

《超大规模集成电路设计》习题(含答案)

《超大规模集成电路设计》习题1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?5.在进行版图设计时为什么要制定版图设计规则?在芯片尺寸尽可能小的前提下,使得即使存在工艺偏差也可以正确的制造出IC,尽可能地提高电路制备的成品率6.版图验证和检查主要包括哪些方面?◆DRC(Design Rule Check):几何设计规则检查;对IC的版图做几何空间检查,保证能在特定的工艺条件下实现所设计的电路,并保证一定的成品率;◆ ERC(Electrical Rule Check):电学规则检查;检查电源(power)/地(ground)的短路,浮空的器件和浮空的连线等指定的电气特性;◆ LVS(Loyout versus Schematic):网表一致性检查;将版图提出的网表和原理图的网表进行比较,检查电路连接关系是否正确,MOS晶体管的长/宽尺寸是否匹配,电阻/电容值是否正确等;◆LPE(Layout Parameter Extraction):版图寄生参数提取;从版图中提取晶体管的尺寸、结点的寄生电容、连线的寄生电阻等参数,并产生SPICE 格式的网表,用于后仿真验证;◆ POSTSIM:后仿真,检查版图寄生参数对设计的影响;提取实际版图参数、电阻、电容,生成带寄生量的器件级网表,进行开关级逻辑模拟或电路模拟,以验证设计出的电路功能的正确性和时序性能等,并产生测试向量。

集成电路物理模型的建立及仿真

集成电路物理模型的建立及仿真随着信息化技术的蓬勃发展,集成电路已经成为现代电子设备的核心组成部分,其集成度和性能已经达到了前所未有的高度。

在众多集成电路设计中,物理仿真是最为重要的一步。

因为通过物理仿真,设计人员可以了解电路的实际工作情况,发现和解决一些潜在的问题,进而提高电路的可靠性和性能。

建立合适的电路物理模型是实现物理仿真的前提条件。

电路模型是对电路的描述,它可以描述电路的基本物理特性和功能。

在物理仿真中,精确的电路模型可以让仿真数据更加真实、可靠。

目前,常见的电路模型包括传输线模型、开关模型、二极管模型、MOSFET模型、BJT模型等。

其中,MOSFET模型是目前应用最广泛的电路模型之一。

MOSFET(金属-氧化物半导体场效应晶体管)是一种常用的半导体器件。

MOSFET的物理结构简单,同时具有电阻大、噪声低等优点,因此MOSFET已经成为现代数字和模拟电子电路的重要构件。

MOSFET模型的建立是进行电路仿真的前提条件。

MOSFET模型的建立方法有很多,其中最为常见的是SPICE模型。

SPICE(模拟嵌入式集成电路)是由美国加州大学伯克利分校开发的一种电路仿真器,它可以仿真各种数字和模拟电路。

由于SPICE模型可用性广泛,因此在现代电路设计中被广泛使用。

SPICE模型的建立有两种方法,一种是手工建模,另一种是自动建模。

手工建模需要设计人员具有较强的电路知识和模型制作技能,时间和精力成本也相对较高。

因此,自动建模方法正逐渐成为MOSFET模型建立的主流技术。

目前,常用的自动建模技术主要有改进模型拟合算法、统计建模技术、神经网络建模方法等。

MOSFET模型的建立不完全是一项独立的工作,它还包括电路参数的提取。

由于MOSFET的参数会随着工作条件的变化而变化,在建立MOSFET模型时,必须考虑各种参数的影响。

电路参数的提取主要包括DC参数提取、小信号参数提取等。

在DC参数提取过程中,需要测量MOSFET的器件电流、触发电压等;在小信号参数提取过程中,需要测量MOSFET的转移电导、转移电容等。

CMOS集成电路设计中电阻设计方法

CMOS集成电路设计中电阻设计方法的研究[日期:2008-11-18 15:47:00] 作者:未知来源:电阻在集成电路中有极其重要的作用他直接关系到芯片的性能与面积及其成本讨论了集成电路设计中多晶硅条电阻、MOS管电阻和电容电阻等3种电阻器的实现方法,论述了他们各自的优点、缺点及其不同的作用;介绍了他们各自的计算方法并给出了MOS管电阻与电容电阻的实现方法并对实例进行了详细的分析,比较了不同电阻在面积上的不同能更好地了解不同电阻在不同情况下的使用对MOS管实现交流电阻中出现的体效应给出了解决方法在集成电路的设计中,电阻器不是主要的器件,却是必不可少的如果设计不当,会对整个电路有很大的影响,并且会使芯片的面积很大,从而增加成本目前,在设计中使用的主要有3种电阻器:多晶硅、MOS管以及电容电阻在设计中,要根据需要灵活运用这3种电阻,使芯片的设计达到最优1多晶硅电阻集成电路中的单片电阻器距离理想电阻都比较远,在标准的MOS工艺中,最理想的无源电阻器是多晶硅条一个均匀的平板电阻可以表示为:式中:ρ为电阻率;t为薄板厚度;R□=(ρ/t)为薄层电阻率,单位为Ω/□;L/W为长宽比由于常用的薄层电阻很小,通常多晶硅最大的电阻率为100 Ω/□,而设计规则又确定了多晶硅条宽度的最小值,因此高值的电阻需要很大的尺寸,由于芯片面积的限制,实际上是很难实现的当然也可以用扩散条来做薄层电阻,但是由于工艺的不稳定性,通常很容易受温度和电压的影响,很难精确控制其绝对数值寄生效果也十分明显无论多晶硅还是扩散层,他们的电阻的变化范围都很大,与注入材料中的杂质浓度有关不容易计算准确值由于上述原因,在集成电路中经常使用有源电阻器2MOS管电阻MOS管为三端器件,适当连接这三个端,MOS管就变成两端的有源电阻这种电阻器主要原理是利用晶体管在一定偏置下的等效电阻可以代替多晶硅或扩散电阻,以提供直流电压降,或在小范围内呈线性的小信号交流电阻在大多数的情况下,获得小信号电阻所需要的面积比直线性重要得多一个MOS器件就是一个模拟电阻,与等价的多晶硅或跨三电阻相比,其尺寸要小得多简单地把n沟道或p沟道增强性MOS管的栅极接到漏极上就得到了类似MOS晶体管的有源电阻对于n沟道器件,应该尽可能地把源极接到最负的电源电压上,这样可以消除衬底的影响同样p沟道器件源极应该接到最正的电源电压上此时,VGS=VDS,如图1(a),(b)所示图1(a)的MOS晶体管偏置在线性区工作,图2所示为有源电阻跨导曲线ID-VG S的大信号特性这一曲线对n沟道、p沟道增强型器件都适用可以看出,电阻为非线性的但是在实际中,由于信号摆动的幅度很小,所以实际上这种电阻可以很好地工作根据公式其中:K′=μ0C0X可以看出,如果VDS<(VGS-VT),则ID与VDS之间关系为直线性(假定VGS与VDS 无关,由此产生一个等效电阻R=KL/W,K=1/[μ0C0X(VGS-VT)],μ0为载流子的表面迁移率,C0X为栅沟电容密度;K值通常在1 000~3 00 0Ω/□实验证明,在VDS<0.5(VGS-V T)时,近似情况是十分良好的图1(c),(d)虽然可以改进电阻率的线性,但是牺牲了面积增加了复杂度用有源电阻得到大的直流电压需要大的电流,或者远小于1的W/L比值可以采用级连的方法克服这一问题即将每一级的G,D与上一级的S相连这样可以使W/L接近于1且使用较小的直流电流在设计中有时要用到交流电阻,这时其直流电流应为零图1所示的有源电阻不能满足此条件,因为这时要求其阻值为无穷大显然这是不可能的这时可以利用MOS管的开关特性来实现,如图3(a)所示MOS 开关的特性近似为直线,没有直流失调这时通过控制栅源之间的电压值就可以得到ΔV为1 V的线性交流电阻为了尽可能夸大线性区并抵消体效应,电阻往往以差动方式成对出现,如图3(b)所示的一对差动结构的交流电阻注意,加到电阻器左边的是差动信号(V1);右边则处于相同电位3电容电阻交流电阻还可以采用开关和电容器来实现经验表明,如果时钟频率足够高,开关和电容的组合就可以当作电阻来使用其阻值取决于时钟频率和电容值图4是一种电阻模拟方法,称为“并联开关电容结构”在特定的条件下,按照采样系统理论,可以近似为图4(b)所示的电阻其中V1和V2为两个独立的直流电压源,其按照足够高的速率采样,在周期内的变化可忽略不计通过计算可得:其中,fc=1/T是信号Φ1和Φ2的频率这种方法可以在面积很小的硅片上得到很大的电阻例如,设电容器为多晶硅多晶硅型,时钟频率100 kHz,要求实现1 MΩ的电阻,求其面积根据式(3)可知电容为10 pF假设单位面积的电容为0.2 pF/mil2则面积为50 mil2如果用多晶硅,取最大可能值100 Ω,并取其最小宽度,那么需要900 mil2当然在开关电容电阻中除了电容面积外还需要两个面积极小的MOS管做开关可以看出,电容电阻比多晶硅电阻的面积少了很多而在集成电路设计中这是十分重要的,虽然增加了2个MOS管,但与所减少的面积相比是可忽略的实际上所节省的面积远不止此,因为多晶硅条的电阻率很难达到100 Ω/□当然,利用电容实现电阻还有其他的方法,在此不再赘述4结语本文集中讨论了怎样在物理层上实现电阻实际上,MOS工艺在这方面提供了不少方便这些电阻器可以与其他的元器件一起使用使用开关和电容模拟电阻,可以减轻漏极电流受漏—源电压的影响对于电容电阻器,由于其电阻值与电容大小成反比,因此有效的RC时间常数就与电容之比成正比,从而可以用电容和开关电容电阻准确的实现电路中要求的时间常数;而使用有源器件的电阻,可以使电阻尺寸最小多晶硅电阻则是最简单的在设计中要灵活运用这三种不同的方式超大规模集成电路内部有电阻电容电感么?以及这3种的大致的,ic内部制造方法?请举例说明!高分详细求解!问题补充:多谢各位大大回答,小弟拜谢,小弟最想知道的是,超大规模集成电路的多层结构中的多层,是如何制造的?在第一层上制造第二层的基质材料,是如何超平面化,即是如何镜面化的,是用物理的激光,还是化学或电化学抛光?第一层和第二层是用什么技巧联通的?-----dreamwolf 兄的lm1875的内部图,没看到电容啊,那图的电容是针脚外面!-----电容,电阻是在硅片内部,还是在ic封装的基板(硅玻璃、pcb等)上?电感因该没法做吧,作出来的电感是平面电感(类似rf芯片的线圈)么?-----firevortex大能,请问,已经做好一层,第二层是在同一个衬底上作,还是在另用一块衬底做?多晶硅栅极是如何到达氧化层上部的?MOS的源漏都通过衬底连接到一起,衬底是高导电率的么?-----firevortex达人?1.2.3都明白了,mos类ic第二层若是在同一个已有一层的衬底上做,那么是否要在第一层上进行一次二氧化硅(或其他什么隔离层、或衬底)沉积?沉积后的二氧化硅(或衬底)如何做成绝对光滑(否则光刻图像无法正确显影)?------俺问这个,主要是想比较下,ic的工艺和液晶面板薄膜晶体管的工艺之间的区别!冒似inter,amd的cpu都是7-9层的VLSI是无法像PCB一样使用宏观元件实现电路的(因为VLSI所有元件是集成在一般硅上的,即全部在硅上进行氧化,光刻,掺杂,最后形成完整电路),而电路功能的实现决定了必须使用电阻、电容和电感(电感我还真不知道怎么在VLSI上实现:)这样的话,就必须用VLSI物理版图的不同layer来构成电阻和电容。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本技术公开了一种超大规模集成电路工艺的后道互连寄生电容电阻的建模方法,互连技术文档(ITF)是表征晶体管制备过程中工艺波动的文件,包含不同金属层数、不同线宽、不同间距和不同密度条件下的厚度尺寸与线宽尺寸等波动因素。

该方法在提取后道寄生电容的波动参数部分,结合Raphael工具仿真数据与晶圆测试中值,通过StarRC工具校准提取出电容相关厚度与线宽尺寸波动参数。

在提取后道寄生电阻的波动参数部分,将在寄生电容提取过程中得到的厚度与线宽尺寸波动代入到寄生电阻的提取中,然后对电阻的电阻率值进行计算、校准拟合。

结果显示,本技术对于后道电容电阻的波动尺寸因素实现了一致性匹配,有效降低了后道电容电阻的StarRC抽取值与晶圆测试中值的误差。

技术要求1.一种超大规模集成电路工艺的后道互连寄生电容电阻的建模方法,其特征在于,该方法包括以下具体步骤:步骤1:设计提取后道金属互连层的同层寄生与邻层寄生的测试结构,制造后道金属互连层寄生电容电阻的测试结构,对金属互连层的测试结构进行电容电阻的电学特性的测量,测量得到的数据称为晶圆测试中值;步骤2:提取后道互连寄生电容部分的工艺波动参数通过使用RaphaelRC2工具还原金属互连层的测试结构,结合透射电子显微镜切片收集后道互连工艺波动信息参考,调整厚度尺寸波动与线宽尺寸波动在不同的线宽和间距时的工艺波动大小,写入RaphaelRC2文件,对同层间寄生电容结构、临层间寄生电容结构进行仿真求解电容值;记录金属互连层的尺寸工艺波动和金属间介质层厚度的工艺波动,写入互连技术文档;步骤3:使用StarRC对互连技术文档进行电容抽取并与晶圆测试中值进行对比对于偏差大于10%的测试结构,再次对该测试结构对应的工艺尺寸波动进行校准拟合,重复步骤2,将StarRC抽取的电容数据与晶圆测试中值之间的误差降低到至多10%,确定金属互连层的尺寸工艺波动和金属间介质层厚度的工艺波动;步骤4:提取后道互连寄生电阻部分的工艺波动参数直接采用步骤3在修正寄生电容过程中得到的厚度尺寸波动和线宽尺寸波动参数,将具有不同金属线宽和间距的电阻结构的晶圆测试中值作为电阻建模的目标值,再代入电阻的尺寸信息、金属厚度尺寸波动和线宽尺寸波动数值,计算得出考虑波动因素修正后的电阻率,写入互连技术文档;步骤5:使用StarRC对互连技术文档进行电阻抽取并与晶圆测试中值进行对比对于偏差大于10%的测试结构,再次对该测试结构对应的的电阻率波动进行校准拟合,重复步骤4,将StarRC抽取的电阻数据与晶圆测试中值之间的误差降低到至多10%,确定金属互连层的尺寸工艺波动和金属电阻率的工艺波动。

2.根据权利要求1所述的后道互连寄生电容电阻的建模方法,其特征在于,步骤4所述的计算得出考虑波动因素修正后的电阻率,具体包括:依照式(1)计算金属方块电阻:Rsquare=Res*(WIDTH-2*ETCH)/L (1)式(1)中,Rsquare是金属方块电阻,Res是关键测试用例的实际测试数据,WIDTH是关键测试用例的金属线宽,ETCH是线宽尺寸波动,L是关键测试用例的金属长度;依照式(2)计算波动后修正的电阻率:RHO=Rsquare*T*(1-THICKNESS) (2)式(2)中,RHO是金属电阻率,T是金属层厚度,THICKNESS是厚度尺寸波动。

3.根据权利要求1所述的后道互连寄生电容电阻的建模方法,其特征在于,步骤5所述对电阻率波动进行校准拟合时,不修改厚度尺寸波动与线宽尺寸波动,将计算得到的电阻率作为参数进行StarRC抽取值与晶圆测试中值的对比校准,以寄生电容提取出的厚度尺寸波动和线宽尺寸波动及校准过的电阻率来表征后道互连寄生电阻的波动。

技术说明书超大规模集成电路工艺的后道互连寄生电容电阻的建模方法技术领域本技术属于互补金属氧化物半导体(CMOS)超大集成电路(VLSI)中的制备工艺与工艺波动参数表征提取领域,具体涉及一种超大规模集成电路工艺的后道互连寄生电容电阻的建模方法。

背景技术集成电路版图寄生参数提取(Layout Parasitic Extraction,LPE)是集成电路设计与验证的关键步骤,其提取的对象主要分为两类:一是针对前端工艺,识别并抽取版图中可能存在的寄生有源器件,如寄生场效应管等;另一类则是针对后端工艺,识别并抽取版图中互连线等效的寄生电阻、寄生电容等。

集成电路版图寄生参数提取的相关工具通过读取版图的几何参数和波动参数,计算寄生元器件值,输出SPICE等格式的网表文件,供集成电路仿真软件进行电路仿真。

随着工艺代不断更新,纳米级集成电路中互连线延时逐渐增大,已超过半导体器件延时成为影响集成电路时序主要因素。

因此精准拟合多层互连线延迟对正确评估高端芯片的性能至关重要,参数提取方法的准确与否很大程度影响电路仿真的准确性,因此互连线寄生参数的提取准确性则日益关键。

随着集成电路进入纳米时代,集成电路关键尺寸越来越小,集成电路互连线的特征尺寸也进一步减小。

这种尺寸持续缩小使得互连线的许多工艺参数包括金属互连线电阻率、电介质层介电常数等的都在不断增大。

同时,集成电路互连线更加易于受半导体芯片制造中的工艺波动影响。

传统的互连线RC寄生参数抽取方法通常将工艺参数(例如金属层厚度、电介质层厚度等)的典型值在互连技术文档一一定义,以此为基础生成抽取规则。

人们在后道提取寄生电容与寄生电阻的情况下,会分别根据硅片的实测数据与StarRC的计算数据进行寄生电阻与寄生电容波动的提取。

因此,采用传统的方法,在同一套工艺条件下,获取了基于寄生电容的厚度尺寸波动与线宽尺寸波动及基于寄生电阻的厚度尺寸波动与线宽尺寸波动,而寄生电容的厚度尺寸波动与寄生电阻的厚度尺寸波动往往不同,也就产生了寄生电阻电容的波动不匹配的问题。

技术内容本技术的目的是针对目前的超大规模集成电路工艺的后道互连寄生电容电阻的建模方法,对其中对参数提取流程的改进,提出了一种新的建模方法,克服了原有方法的电容电阻波动尺寸参数不匹配的问题,同时依据本方法提取的互连技术文档,在StarRC抽取仿真数据与硅片测量数据实现了更好的匹配。

实现本技术目的的具体技术方案是:一种超大规模集成电路工艺的后道互连寄生电容电阻的建模方法,其特征在于,该方法包括以下具体步骤:步骤1:设计提取后道金属互连层的同层寄生与邻层寄生的测试结构,制造后道金属互连层寄生电容电阻的测试结构,对金属互连层的测试结构进行电容电阻的电学特性的测量,测量得到的数据称为晶圆测试中值;步骤2:提取后道互连寄生电容部分的工艺波动参数通过使用RaphaelRC2工具还原金属互连层的测试结构,结合透射电子显微镜切片收集后道互连工艺波动信息参考,调整厚度尺寸波动与线宽尺寸波动在不同的线宽和间距时的工艺波动大小,写入RaphaelRC2文件,对同层间寄生电容结构、临层间寄生电容结构进行仿真求解电容值;记录金属互连层的尺寸工艺波动和金属间介质层厚度的工艺波动,写入互连技术文档;步骤3:使用StarRC对互连技术文档进行电容抽取并与晶圆测试中值进行对比对于偏差大于10%的测试结构,再次对该测试结构对应的工艺尺寸波动进行校准拟合,重复步骤2,将StarRC抽取的电容数据与晶圆测试中值之间的误差降低到至多10%,确定金属互连层的尺寸工艺波动和金属间介质层厚度的工艺波动;步骤4:提取后道互连寄生电阻部分的工艺波动参数直接采用步骤3在修正寄生电容过程中得到的厚度尺寸波动和线宽尺寸波动参数,将具有不同金属线宽和间距的电阻结构的晶圆测试中值作为电阻建模的目标值,再代入电阻的尺寸信息、金属厚度尺寸波动和线宽尺寸波动数值,计算得出考虑波动因素修正后的电阻率,写入互连技术文档;步骤5:使用StarRC对互连技术文档进行电阻抽取并与晶圆测试中值进行对比对于偏差大于10%的测试结构,再次对该测试结构对应的的电阻率波动进行校准拟合,重复步骤4,将StarRC抽取的电阻数据与晶圆测试中值之间的误差降低到至多10%,确定金属互连层的尺寸工艺波动和金属电阻率的工艺波动。

所述方法在得到晶圆测试中值后,不采用对电容和电阻两种寄生进行分别波动参数提取的方式,而是优先对后道互连电容的波动参数进行提取。

将步骤3得到的后道金属互连层电容提取得到的厚度尺寸波动和线宽尺寸波动直接应用到后道寄生电阻的波动参数提取中。

步骤4所述的计算得出考虑波动因素修正后的电阻率,具体包括:依照式(1)计算金属方块电阻:Rsquare=Res*(WIDTH-2*ETCH)/L (1)式(1)中,Rsquare是金属方块电阻,Res是关键测试用例的实际测试数据,WIDTH是关键测试用例的金属线宽,ETCH是线宽尺寸波动,L是关键测试用例的金属长度;依照式(2)计算波动后修正的电阻率:RHO=Rsquare*T*(1-THICKNESS) (2)式(2)中,RHO是金属电阻率,T是金属层厚度,THICKNESS是厚度尺寸波动。

步骤5所述对电阻率波动进行校准拟合时,不修改厚度尺寸波动与线宽尺寸波动,将计算得到的电阻率作为参数进行StarRC抽取值与晶圆测试中值的对比校准,以寄生电容提取出的厚度尺寸波动和线宽尺寸波动及校准过的电阻率来表征后道互连寄生电阻的波动。

本技术的一种超大规模集成电路工艺的后道互连寄生电容电阻的建模方法,所述方法在得到晶圆测试中值后,不采用独立对电容和电阻两种寄生进行建模的方式,而是优先对后道互连电容进行建模。

根据后道互连电容提取得到的厚度尺寸波动和线宽尺寸波动,将此结果代入到后道寄生电阻的建模中,通过计算电阻率并对电阻率进行计算和校准,以寄生电容提取出的厚度尺寸波动和线宽尺寸波动及校准过的电阻率来表征后道互连寄生电阻的波动,从而克服了原本独立提取寄生电容电阻建模时存在的电容尺寸波动与电阻尺寸波动不一致的问题。

结果显示,在后道寄生电阻建模中,以此方法提取的波动因素写入互连技术文档,有效降低了后道寄生电阻的StarRC的仿真数据与晶圆测试中值的误差。

附图说明图1为本技术流程图。

具体实施方式以下结合附图及实施例对本技术进行详细描述。

实施例本实施例包括以下具体步骤:1、获取初始误差根据工艺尺寸的大小,设计提取寄生电容寄生电阻的关键测试用例。

通过直接交流测试(AC法)硅片上的可测性结构获得的晶圆测试中值,通过透射电子显微镜对关键测试用例的切片作为参照,提取厚度尺寸波动和线宽尺寸波动,同时用RaphaelRC2还原流片时采用的关键测试用例。

首先对寄生电容进行建模,对同层间寄生电容结构、临层间寄生电容结构等电容测试结构进行仿真。

先对RahpaelRC2仿真数据与硅片测试数据进行对比。

将Raphael提取的寄生电容厚度尺寸波动,线宽尺寸波动进行校准,写入到互连技术文档中,获取StarRC抽取的电容和电阻值与后道互连关键测试用例晶圆测试中值之间的误差。