K4S560832D中文资料

K4H560838D-TCB0

- Changed operating condition. from Vil/Vih(ac) VIL/VIH(dc) Vref +/- 0.35V Vref +/- 0.18V to Vref +/- 0.31V Vref +/- 0.15V

- Added Overshoot/Undershoot spec . Vih(max) = 4.2V, the overshoot voltage duration is ≤ 3ns at VDD. . Vil(min) =- 1.5V, the overshoot voltage duration is ≤ 3ns at VSS. - Changed AC parameters as follows. from tDQSQ tDV tQH tHP - Added DC spec values. +/- 0.5(PC266), +/- 0.6(PC200) +/- 0.35tCK to +0.5(PC266), +0.6(PC200) tHPmin - 0.75ns(PC266) tHPmin - 1.0ns(PC200) tCLmin or tCHmin New Definition Removed New Definition Comments

Version 0.71 (April, 2000) - Corrected a typo for tRAS at 133Mhz/CL2.5 from 48ns t0 45ns. - Corrected a typo in "General Information" table from 64Mx4 to 8Mx16. Version 0.72(May,2000) - Changed DC spec item & test condition Version 0.73(June,2000) - Added updated DC spec values - Deleted tDAL in AC parameter Version 1.0(November,2000) - Eliminate "preliminary"

K4H560838F-UCCC中文资料

256Mb F-die DDR400 SDRAM Specification66 TSOP-II with Pb-Free(RoHS compliant)Revision 1.1Rev. 1.1 August. 2003256Mb F-die Revision HistoryRevison 1.0 (June. 2003)1. First releaseRevison 1.1 (August. 2003)1. Added x8 org (K4H560838F)Rev. 1.1 August. 2003Rev. 1.1 August. 2003• 200MHz Clock, 400Mbps data rate.• VDD= +2.6V + 0.10V, VDDQ= +2.6V + 0.10V• Double-data-rate architecture; two data transfers per clock cycle • Bidirectional data strobe(DQS)• Four banks operation• Differential clock inputs(CK and CK)• DLL aligns DQ and DQS transition with CK transition • MRS cycle with address key programs-. Read latency 3 (clock) for DDR400 , 2.5 (clock) for DDR333 -. Burst length (2, 4, 8)-. Burst type (sequential & interleave)• All inputs except data & DM are sampled at the positive going edge of the system clock(CK)• Data I/O transactions on both edges of data strobe • Edge aligned data output, center aligned data input • LDM,UDM for write masking only (x16)• Auto & Self refresh• 7.8us refresh interval(8K/64ms refresh) • Maximum burst refresh cycle : 8• 66pin TSOP II Pb-Free package • RoHS compliantOrdering InformationPart .Max Freq.Interface Package K4H560838F-UCCC 32M x 8 CC(DDR400@CL=3)SSTL266pin TSOP IIK4H560838F-UCC4 C4(DDR400@CL=3)K4H561638F-UCCC 16M x 16CC(DDR400@CL=3)SSTL266pin TSOP IIK4H561638F-UCC4C4(DDR400@CL=3)Key Features*CL : CAS LatencyOperating Frequencies- CC(DDR400@CL=3)- C4(DDR400@CL=3)Speed @CL3200MHz 200MHz CL-tRCD-tRP 3 - 3 - 33 -4 - 4Rev. 1.1 August. 2003Pin DescriptionDM is internally loaded to match DQ and DQS identically.256Mb Package PinoutRow & Column address configurationV DD 166Pin TSOP II (400mil x 875mil)DQ 02V DDQ 3NC 4DQ 15V SSQ 6NC 7DQ 28V DDQ 9NC 10DQ 311V SSQ 12BA 020CS 19RAS 18CAS 17WE 16NC 15V DDQ 14NC 13V DD 27A 326A 225A 124A 023AP/A 1022BA 121V SS 54DQ 753V SSQ 52NC 51DQ 650V DDQ 49NC 48DQ 547V SSQ 46NC 45DQ 444V DDQ 43A 113536CKE 37CK 38DM 39V REF 40V SSQ 41NC 42V SS55A 456A 557A 658A 759A 860A 934(0.65mm Pin Pitch)333231302928616263646566NC NC NC NC NC V DDNC DQS NC V SS CK NC A 12 16Mb x 16V SS DQ 15V SSQ DQ 14DQ 13V DDQ DQ 12DQ 11V SSQ DQ 10DQ 9V DDQ A 11CKE CK UDM V REF V SSQ DQ 8V SSA 4A 5A 6A 7A 8A 9NC UDQS NC V SS CK NC A 12V DD DQ 0V DDQ DQ 1DQ 2V SSQ DQ 3DQ 4V DDQ DQ 5DQ 6V SSQ BA 0CS RAS CAS WE LDM V DDQ DQ 7V DD A 3A 2A 1A 0AP/A 10BA 1NC LDQS NC NC NC V DDBank Address BA0~BA1Auto PrechargeA10OrganizationRow Address Column Address32Mx8A0~A12A0-A916Mx16A0~A12A0-A832Mb x 8Package Physical Demension66pin TSOPII / Package dimensionRev. 1.1 August. 2003CK, CKADDCK, CK CKE CS RAS CAS WE Data StrobeBlock Diagram (8Mb x 8 / 4Mb x 16 I/O x 4 Banks)L(U)DMRev. 1.1 August. 2003SYMBOL TYPE DESCRIPTIONCK, CK Input Clock : CK and CK are differential clock inputs. All address and control input signals are sam-pled on the positive edge of CK and negative edge of CK. Output (read) data is referenced to both edges of CK. Internal clock signals are derived from CK/CK.CKE Input Clock Enable : CKE HIGH activates, and CKE LOW deactivates internal clock signals, and device input buffers and output drivers. Deactivating the clock provides PRECHARGE POWER-DOWN and SELF REFRESH operation (all banks idle), or ACTIVE POWER-DOWN (row ACTIVE in any bank). CKE is synchronous for all functions except for disabling outputs, which is achieved asynchronously. Input buffers, excluding CK, CK and CKE are disabled dur-ing power-down and self refresh modes, providing low standby power. CKE will recognize an LVCMOS LOW level prior to VREF being stable on power-up.CS Input Chip Select : CS enables(registered LOW) and disables(registered HIGH) the command decoder. All commands are masked when CS is registered HIGH. CS provides for external bank selection on systems with multiple banks. CS is considered part of the command code.RAS, CAS, WE Input Command Inputs : RAS, CAS and WE (along with CS) define the command being entered.LDM,(UDM)Input Input Data Mask : DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with that input data during a WRITE access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading. For the x16, LDM corresponds to the data on DQ0~D7 ; UDM corresponds to the data on DQ8~DQ15. DM may be driven high, low, or floating during READs.BA0, BA1Input Bank Addres Inputs : BA0 and BA1 define to which bank an ACTIVE, READ, WRITE or PRE-CHARGE command is being applied.A [0 : 12]Input Address Inputs : Provide the row address for ACTIVE commands, and the column address and AUTO PRECHARGE bit for READ/WRITE commands, to select one location out of the mem-ory array in the respective bank. A10 is sampled during a PRECHARGE command to deter-mine whether the PRECHARGE applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1. The address inputs also provide the op-code during a MODE REGISTER SET command. BA0 and BA1 define which mode register is loaded during the MODE REGISTER SET command (MRS or EMRS).A12 & A13 are used on device densities of 256Mb and greater, and A13 is used only on 1Gb decices.DQ I/O Data Input/Output : Data busLDQS,(U)DQS I/O Data Strobe : Output with read data, input with write data. Edge-aligned with read data, cen-tered in write data. Used to capture write data. For the x16, LDQS corresponds to the data on DQ0~D7 ; UDQS corresponds to the data on DQ8~DQ15NC-No Connect : No internal electrical connection is present.VDDQ Supply DQ Power Supply : +2.6V ± 0.1V.VSSQ Supply DQ Ground.VDD Supply Power Supply : +2.6V ± 0.1V (device specific).VSS Supply Ground.VREF Input SSTL_2 reference voltage.Input/Output Function DescriptionRev. 1.1 August. 2003Command Truth Table (V=Valid, X=Don′t Care, H=Logic High, L=Logic Low)COMMAND CKEn-1CKEn CS RAS CAS WE BA0,1A10/AP A0 ~ A9,A11, A12NoteRegister Extended MRS H X L L L L OP CODE1, 2 Register Mode Register Set H X L L L L OP CODE1, 2Refresh Auto RefreshHHL L L H X3SelfRefreshEntry L3Exit L HL H H HX3H X X X3Bank Active & Row Addr.H X L L H H V Row AddressRead & Column Address Auto Precharge DisableH X L H L H VLColumnAddress4 Auto Precharge Enable H4Write & Column Address Auto Precharge DisableH X L H L L VLColumnAddress4 Auto Precharge Enable H4, 6Burst Stop H X L H H L X7Precharge Bank SelectionH X L L H LV LXAll Banks X H5Active Power Down Entry H LH X X XXL V V VExit L H X X X XPrecharge Power Down Mode Entry H LH X X XXL H H HExit L HH X X XL V V VDM(UDM/LDM for x16 only)H X X8No operation (NOP) : Not defined H X H X X XX9 L H H H91. OP Code : Operand Code. A0 ~ A12 & BA0 ~ BA1 : Program keys. (@EMRS/MRS)2. EMRS/MRS can be issued only at all banks precharge state.A new command can be issued 2 clock cycles after EMRS or MRS.3. Auto refresh functions are same as the CBR refresh of DRAM.The automatical precharge without row precharge command is meant by "Auto".Auto/self refresh can be issued only at all banks precharge state.4. BA0 ~ BA1 : Bank select addresses.If both BA0 and BA1 are "Low" at read, write, row active and precharge, bank A is selected.If BA0 is "High" and BA1 is "Low" at read, write, row active and precharge, bank B is selected.If BA0 is "Low" and BA1 is "High" at read, write, row active and precharge, bank C is selected.If both BA0 and BA1 are "High" at read, write, row active and precharge, bank D is selected.5. If A10/AP is "High" at row precharge, BA0 and BA1 are ignored and all banks are selected.6. During burst write with auto precharge, new read/write command can not be issued.Another bank read/write command can be issued after the end of burst.New row active of the associated bank can be issued at t RP after the end of burst.7. Burst stop command is valid at every burst length.8. DM(x4/8) sampled at the rising and falling edges of the DQS and Data-in are masked at the both edges (Write DM latency is 0).UDM/LDM(x16 only) sampled at the rising and falling edges of the UDQS/LDQS and Data-in are masked at the both edges (Write UDM/LDM latency is 0).9. This combination is not defined for any function, which means "No Operation(NOP)" in DDR SDRAM.Note :Rev. 1.1 August. 20038M x 8bit x 4 Banks / 4M x 16Bit x 4 Banks Double Data Rate SDRAMGeneral DescriptionThe K4H560838F / K4H561638F is 268,435,456 bits of double data rate synchronous DRAM organized as 4x 8,388,608 / 4x 4,194,304 words by 8 / 16bits, fabricated with SAMSUNG′s high performance CMOS technology. Synchronous features with Data Strobe allow extremely high performance up to 400Mb/s per pin. I/O transactions are possible on both edges of DQS. Range of operating frequen-cies, programmable burst length and programmable latencies allow the device to be useful for a variety of high performance memory system applications.Absolute Maximum RatingsParameter Symbol Value Unit Voltage on any pin relative to V SS V IN, V OUT-0.5 ~ 3.6V Voltage on V DD & V DDQ supply relative to V SS V DD, V DDQ-1.0 ~ 3.6V Storage temperature T STG-55 ~ +150°CPower dissipation P D 1.5WShort circuit current I OS50mANote : Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.Functional operation should be restricted to recommend operation condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliability.DC Operating Conditions Recommended operating conditions(Voltage referenced to V SS=0V, T A=0 to 70°C) Parameter Symbol Min Max Unit Note Supply voltage(for device with a nominal V DD of 2.5V)V DD 2.5 2.75I/O Supply voltage V DDQ 2.5 2.7V5I/O Reference voltage V REF0.49*VDDQ0.51*VDDQ V1I/O Termination voltage(system)V TT V REF-0.04V REF+0.04V2 Input logic high voltage V IH(DC)V REF+0.15V DDQ+0.3VInput logic low voltage V IL(DC)-0.3V REF-0.15VInput Voltage Level, CK and CK inputs V IN(DC)-0.3V DDQ+0.3VInput Differential Voltage, CK and CK inputs V ID(DC)0.36V DDQ+0.6V3V-I Matching: Pullup to Pulldown Current Ratio VI(Ratio)0.71 1.4-4 Input leakage current I I-22uAOutput leakage current I OZ-55uAOutput High Current(Normal strengh driver) ;V OUT = V TT + 0.84V I OH-16.8mAOutput High Current(Normal strengh driver) ;V OUT = V TT - 0.84V I OL16.8mAOutput High Current(Half strengh driver) ;V OUT = V TT + 0.45V I OH-9mAOutput High Current(Half strengh driver) ;V OUT = V TT - 0.45V I OL9mANote :1.VREF is expected to be equal to 0.5*VDDQ of the transmitting device, and to track variations in the dc level of same.Peak-to peak noise on VREF may not exceed +/-2% of the dc value.2. V TT is not applied directly to the device. V TT is a system supply for signal termination resistors, is expected to be set equal toV REF, and must track variations in the DC level of V REF3. V ID is the magnitude of the difference between the input level on CK and the input level on CK.4. The ratio of the pullup current to the pulldown current is specified for the same temperature and voltage, over the entiretemperature and voltage range, for device drain to source voltages from 0.25V to 1.0V. For a given output, it represents the maximum difference between pullup and pulldown drivers due to process variation. The full variation in the ratio of themaximum to minimum pullup and pulldown current will not exceed 1/7 for device drain to source voltages from 0.1 to 1.0.5. This is the DC voltage supplied at the DRAM and is inclusive of all noise up to 20MHz. Any noise above 20MHz at the DRAMgenerated from any source other than the DRAM itself may not exceed the DC voltage range of 2.6V +/-100mV.Rev. 1.1 August. 2003DDR SDRAM Spec Items & Test ConditionsConditions Symbol Operating current - One bank Active-Precharge;tRC=tRCmin; tCK=5ns for DDR400; DQ,DM and DQS inputs changing once per clock cycle;address and control inputs changing once every two clock cycles; CS = high between valid commands.IDD0Operating current - One bank operation ; One bank open, BL=4, Reads- Refer to the following page for detailed test condition; CS = high between valid commands.IDD1 Percharge power-down standby current; All banks idle; power - down mode; CKE = <VIL(max); tCK=5ns forDDR400; Vin = Vref for DQ,DQS and DM.IDD2P Precharge Floating standby current; CS# > =VIH(min);All banks idle; CKE > = VIH(min); tCK=5ns for DDR400;Address and other control inputs changing once per clock cycle; Vin = Vref for DQ,DQS and DMIDD2F Precharge Quiet standby current; CS# > = VIH(min); All banks idle;CKE > = VIH(min); tCK=5ns for DDR400; Address and other control inputs stable at >= VIH(min) or =<VIL(max);Vin = Vref for DQ ,DQS and DMIDD2QActive power - down standby current ; one bank active; power-down mode; CKE=< VIL (max); tCK=5nsDDR400; Vin = Vref for DQ,DQS and DMIDD3PActive standby current; CS# >= VIH(min); CKE>=VIH(min);one bank active; active - precharge; tRC=tRASmax; tCK=5ns for DDR400; DQ, DQS and DM inputs changing twiceper clock cycle; address and other control inputs changing once per clock cycleIDD3NOperating current - burst read; Burst length = 2; reads; continguous burst; One bank active; address and controlinputs changing once per clock cycle; CL=3 at 5ns for DDR400;50% of data changing on every transfer; lout = 0 mAIDD4ROperating current - burst write; Burst length = 2; writes; continuous burst;One bank active address and control inputs changing once per clock cycle; CL=3 at tCK=5ns for DDR400; DQ, DMand DQS inputs changing twice per clock cycle, 50% of input data changing at every transferIDD4W Auto refresh current; tRC = tRFC(min) - 14*tCK for DDR400 at tCK=5ns; IDD5Self refresh current; CKE =< 0.2V; External clock on; tCK = 5ns for DDR400.IDD6 Input/Output Capacitance(V DD=2.6, V DDQ=2.6V, T A= 25°C, f=1MHz) Parameter Symbol Min Max Delta Unit NoteInput capacitance(A0 ~ A12, BA0 ~ BA1, CKE, CS, RAS,CAS, WE)CIN1230.5pF4Input capacitance( CK, CK)CIN2230.25pF4Data & DQS input/output capacitance COUT450.5pF1,2,3,4Input capacitance(DM for 8, UDM/LDM for x16)CIN345pF1,2,3,41.These values are guaranteed by design and are tested on a sample basis only.2. Although DM is an input -only pin, the input capacitance of this pin must model the input capacitance of the DQ and DQS pins.This is required to match signal propagation times of DQ, DQS, and DM in the system.3. Unused pins are tied to ground.4. This parameteer is sampled. VDDQ = +2.6V +0.1V, VDD = +2.6V +0.1V, f=100MHz, tA=25°C, Vout(dc) =VDDQ/2, Vout(peak to peak) = 0.2V. DM inputs are grouped with I/O pins - reflecting the fact that they are matched in loading (to facilitate trace matching at the board level).Note :Rev. 1.1 August. 2003DDR SDRAM I DD spec table (V DD=2.7V, T = 10°C)Symbol32Mx8Unit Notes - CC(DDR400@CL=3)- C4(DDR400@CL=3)IDD0105100mAIDD1130130mAIDD2P44mAIDD2F3030mAIDD2Q2525mAIDD3P5555mAIDD3N7575mAIDD4R185185mAIDD4W220220mAIDD5200200mAIDD6Normal33mA Low power 1.5 1.5mA Optional IDD7A350350mASymbol16Mx16Unit Notes - CC(DDR400@CL=3)- C4(DDR400@CL=3)IDD0110105mAIDD1150145mAIDD2P44mAIDD2F3030mAIDD2Q2525mAIDD3P5555mAIDD3N7575mAIDD4R220220mAIDD4W250250mAIDD5200200mAIDD6Normal33mALow power 1.5 1.5mA Optional IDD7A380380mARev. 1.1 August. 2003< Detailed test conditions for DDR SDRAM IDD1 & IDD7A >IDD1 : Operating current: One bank operation1. Only one bank is accessed with tRC(min), Burst Mode, Address and Control inputs change logic state once per Deselect cycle.Iout = 0mA2. Timing patterns- CC/C4(200Mhz,CL=3) : tCK=5ns, CL=3, BL=4, tRCD=3*tCK(CC) 4*tCK(C4), tRC=11*tCK(CC) 12*tCK(C4), tRAS=8*tCKSetup : A0 N N R0 N N N N P0 N NRead : A0 N N R0 N N N N P0 N N - repeat the same timing with random address changing*50% of data changing at every transferIDD7A : Operating current: Four bank operation1. Four banks are being interleaved with tRC(min), Burst Mode, Address and Control inputs on Deselet edge are not changing.Iout = 1mA2. Timing patterns- CC/C4(200Mhz,CL=3) : tCK=5ns, CL=3, BL=4, tRCD=3*tCK(CC) 4*tCK(C4), tRC=11*tCK(CC) 12*tCK(C4), tRAS=8*tCKSetup : A0 N A1 RA0 A2 RA1 A3 RA2 N RA3 N NRead : A0 N A1 RA0 A2 RA1 A3 RA2 N RA3 N N - repeat the same timing with random address changing*50% of data changing at every transferLegend : A = Activate, R=Read, W=Write, P=Precharge, N=NOPRev. 1.1 August. 2003Rev. 1.1 August. 2003AC Operating ConditionsParameter/ConditionSymbol Min Max-10Unit NoteInput High (Logic 1) Voltage, DQ, DQS and DM signals VIH(AC)VREF + 0.31V Input Low (Logic 0) Voltage, DQ, DQS and DM signals.VIL(AC)VREF - 0.31V Input Differential Voltage, CK and CK inputs VID(AC)0.7VDDQ+0.6V 1Input Crossing Point Voltage, CK and CK inputsVIX(AC)0.5*VDDQ-0.20.5*VDDQ+0.2V2AC Overshoot/Undershoot specification for Address and Control PinsParameterSpecification DDR400Maximum peak amplitude allowed for overshoot 1.5V Maximum peak amplitude allowed for undershoot1.5V The area between the overshoot signal and VDD must be less than or equal to 4.5V-ns The area between the undershoot signal and GND must be less than or equal to4.5V-ns543210-1-2-3-4-50.50.68751.01.52.02.53.03.5 4.04.55.05.5 6.06.31256.57.0VDDOvershootMaximum Amplitude = 1.5VArea = 4.5V-nsMaximum Amplitude = 1.5V undershootGNDV o l t s (V )Tims(ns) AC overshoot/Undershoot DefinitionNotes :1. VID is the magnitude of the difference between the input level on CK and the input level on /CK.2. The value of VIX is expected to equal 0.5*VDDQ of the transmitting device and must track variations in the dc level of the same.Rev. 1.1 August. 2003Overshoot/Undershoot specification for Data, Strobe, and Mask PinsParameterSpecification DDR400Maximum peak amplitude allowed for overshoot 1.2V Maximum peak amplitude allowed for undershoot1.2V The area between the overshoot signal and VDD must be less than or equal to2.5V-ns The area between the undershoot signal and GND must be less than or equal to2.5V-ns543210-1-2-3-4-500.51.01.421.52.02.53.03.54.04.55.05.55.686.06.57.0VDDQOvershootMaximum Amplitude = 1.2VArea = 2.5V-nsMaximum Amplitude = 1.2VundershootGNDV o l t s (V )Tims(ns)DQ/DM/DQS AC overshoot/Undershoot DefinitionAC Timing Parameters and SpecificationsParameter Symbol - CC(DDR400@CL=3)- C4(DDR400@CL=3)Unit Note Min Max Min MaxRow cycle time tRC5560ns Refresh row cycle time tRFC7070ns Row active time tRAS4070K4070K ns RAS to CAS delay tRCD1518ns Row precharge time tRP1518ns Row active to Row active delay tRRD1010ns Write recovery time tWR1515ns Internal write to read command delay tWTR22tCKClock cycle time CL=3.0tCK510510ns16 CL=2.5612612nsClock high level width tCH0.450.550.450.55tCKClock low level width tCL0.450.550.450.55tCKDQS-out access time from CK/CK tDQSCK-0.55+0.55-0.55+0.55nsOutput data access time from CK/CK tAC-0.65+0.65-0.65+0.65nsData strobe edge to ouput data edge tDQSQ-0.4-0.4ns13 Read Preamble tRPRE0.9 1.10.9 1.1tCKRead Postamble tRPST0.40.60.40.6tCKCK to valid DQS-in tDQSS0.72 1.280.72 1.28tCKWrite preamble setup time tWPRES00ps5 Write preamble tWPRE0.250.25tCKWrite postamble tWPST0.40.60.40.6tCK4 DQS falling edge to CK rising-setup time tDSS0.20.2tCKDQS falling edge from CK rising-hold time tDSH0.20.2tCKDQS-in high level width tDQSH0.35 0.35 tCKDQS-in low level width tDQSL0.35 0.35 tCKAddress and Control Input setup time tIS0.60.6ns h,7~10 Address and Control Input hold time tIH0.60.6ns h,7~10 Data-out high impedence time from CK/CK tHZ- tAC max- tAC max ns3 Data-out low impedence time from CK/CK tLZ tAC min tAC max tAC min tAC max ns3 Mode register set cycle time tMRD22tCKDQ & DM setup time to DQS, slew rate 0.5V/ns tDS0.40.4ns i, j DQ & DM hold time to DQS, slew rate 0.5V/ns tDH0.40.4ns i, j DQ & DM input pulse width tDIPW 1.75 1.75ns9 Control & Address input pulse width for each input tIPW 2.2 2.2ns9 Refresh interval time tREFI7.87.8us6Output DQS valid window tQHtHP-tQHS-tHP-tQHS-ns12Clock half period tHPmintCH/tCL-mintCH/tCL-ns11, 12Rev. 1.1 August. 2003Rev. 1.1 August. 2003Component Notes1.V ID is the magnitude of the difference between the input level on CK and the input level on CK.2. The value of VIX is expected to equal 0.5*VDDQ of the transmitting device and must track variations in the dc level of the same.3. tHZ and tLZ transitions occur in the same access time windows as valid data transitions. these parameters are not referenced to a specific voltage level but specify when the device output in no longer driving (HZ), or begins driving (LZ).4. The maximum limit for this parameter is not a device limit. The device will operate with a greater value for this parameter, but sys tem performance (bus turnaround) will degrade accordingly.5. The specific requirement is that DQS be valid (HIGH, LOW, or at some point on a valid transition) on or before this CK edge. A valid transition is defined as monotonic and meeting the input slew rate specifications of the device. when no writes were previ ously in progress on the bus, DQS will be tran sitioning from High- Z to logic LOW. If a previous write was in progress, DQS could be HIGH, LOW, or transitioning from HIGH to LOW at this time, depending on tDQSS.6. A maximum of eight AUTO REFRESH commands can be posted to any given DDR SDRAM device.7. For command/address input slew rate ≥ 0.5 V/ns8. For CK & CK slew rate ≥ 0.5 V/ns9. These parameters guarantee device timing, but they are not necessarily tested on each device. They may be guaranteed by device design or tester correlation.10. Slew Rate is measured between VOH(ac) and VOL(ac).11. Min (tCL, tCH) refers to the smaller of the actual clock low time and the actual clock high time as provided to the device (i.e. this value can be greater than the minimum specification limits for tCL and tCH).....For example, tCL and tCH are = 50% of theperiod, less the half period jitter (tJIT(HP)) of the clock source, and less the half period jitter due to crosstalk (tJIT(crosstalk)) into the clock traces.12. tQH = tHP - tQHS, where:tHP = minimum half clock period for any given cycle and is defined by clock high or clock low (tCH, tCL). tQHS accounts for 1) The pulse duration distortion of on-chip clock circuits; and 2) The worst case push-out of DQS on one tansition followed by the worst case pull-in of DQ on the next transition, both of which are, separately, due to data pin skew and output pattern effects, and p- channel to n-channel variation of the output drivers.13. tDQSQConsists of data pin skew and output pattern effects, and p-channel to n-channel variation of the output drivers for any given cycle.14. tDAL = (tWR/tCK) + (tRP/tCK)For each of the terms above, if not already an integer, round to the next highest integer. Example: For DDR400(CC) at CL=3 and tCK=5ns tDAL = (15 ns / 5 ns) + (15 ns/ 5ns) = {(3) + (3)}CLK tDAL = 6 clocks15. In all circumstances, tXSNR can be satisfied using tXSNR=tRFCmin+1*tCK16. The only time that the clock frequency is allowed to change is during self-refresh mode.ParameterSymbol - CC(DDR400@CL=3)- C4(DDR400@CL=3)Unit Note MinMax MinMax Data hold skew factortQHS 0.50.5ns 12Auto Precharge write recovery + precharge time tDAL ----ns 14Exit self refresh to non-READ command tXSNR 7575ns 15Exit self refresh to READ commandtXSRD200-200-tCKRev. 1.1 August. 2003Table 4 : Input/Output Setup & Hold Derating for Rise/Fall Delta Slew RateTable 5 : Output Slew Rate Characteristice (X8 Devices only)Table 6 : Output Slew Rate Characteristice (X16 Devices only)Table 7 : Output Slew Rate Matching Ratio CharacteristicsDelta Slew Rate tDS tDH Units Notes +/- 0.0 V/ns 00ps i +/- 0.25 V/ns +50+50ps i +/- 0.5 V/ns+100+100psiSlew Rate CharacteristicTypical Range(V/ns)Minimum (V/ns)Maximum (V/ns)Notes Pullup Slew Rate 1.2 ~ 2.5 1.0 4.5a,c,d,f,g Pulldown slew1.2 ~2.51.04.5b,c,d,f,gSlew Rate CharacteristicTypical Range(V/ns)Minimum (V/ns)Maximum (V/ns)Notes Pullup Slew Rate 1.2 ~ 2.50.7 5.0a,c,d,f,g Pulldown slew1.2 ~2.50.75.0b,c,d,f,gAC CHARACTERISTICSDDR400PARAMETERMINMAX Notes Output Slew Rate Matching Ratio (Pullup to Pulldown)--e,kSystem Characteristics for DDR SDRAMThe following specification parameters are required in systems using DDR400 devices to ensure proper system perfor-mance. these characteristics are for system simulation purposes and are guaranteed by design.Table 1 : Input Slew Rate for DQ, DQS, and DMTable 2 : Input Setup & Hold Time Derating for Slew RateTable 3 : Input/Output Setup & Hold Time Derating for Slew RateAC CHARACTERISTICSDDR400PARAMETERSYMBOL MIN MAX Units Notes DQ/DM/DQS input slew rate measured between VIH(DC), VIL(DC) and VIL(DC), VIH(DC)DCSLEW0.54.0V/nsa, kInput Slew RatetIS tIH Units Notes 0.5 V/ns 00ps h 0.4 V/ns +500ps h 0.3 V/ns+100pshInput Slew RatetDS tDH Units Notes 0.5 V/ns 00ps j 0.4 V/ns +75+75ps j 0.3 V/ns+150+150psjSystem Notes :a. Pullup slew rate is characteristized under the test conditions as shown in Figure 1.Test pointOutput50ΩVSSQFigure 1 : Pullup slew rate test loadb. Pulldown slew rate is measured under the test conditions shown in Figure 2.VDDQ50ΩOutputTest pointFigure 2 : Pulldown slew rate test loadc. Pullup slew rate is measured between (VDDQ/2 - 320 mV +/- 250 mV)Pulldown slew rate is measured between (VDDQ/2 + 320 mV +/- 250 mV)Pullup and Pulldown slew rate conditions are to be met for any pattern of data, including all outputs switching and only one output switching.Example : For typical slew rate, DQ0 is switchingFor minmum slew rate, all DQ bits are switching from either high to low, or low to high.For Maximum slew rate, only one DQ is switching from either high to low, or low to high.The remaining DQ bits remain the same as for previous state.d. Evaluation conditionsTypical : 25 °C (T Ambient), VDDQ = 2.6V, typical processMinimum : 70 °C (T Ambient), VDDQ = 2.5V, slow - slow processMaximum : 0 °C (T Ambient), VDDQ = 2.7V, fast - fast processe. The ratio of pullup slew rate to pulldown slew rate is specified for the same temperature and voltage, over the entire temperature and voltage range. For a given output, it represents the maximum difference between pullup and pulldown drivers due to process variation.f. Verified under typical conditions for qualification purposes.g. TSOPII package divices only.h. A derating factor will be used to increase tIS and tIH in the case where the input slew rate is below 0.5V/nsas shown in Table 2. The Input slew rate is based on the lesser of the slew rates detemined by either VIH(AC) to VIL(AC) orVIH(DC) to VIL(DC), similarly for rising transitions.i. A derating factor will be used to increase tDS and tDH in the case where DQ, DM, and DQS slew rates differ, as shown in Tables 3 & 4. Input slew rate is based on the larger of AC-AC delta rise, fall rate and DC-DC delta rise, Input slew rate is based on the lesser of the slew rates determined by either VIH(AC) to VIL(AC) or VIH(DC) to VIL(DC), similarly for rising transitions.The delta rise/fall rate is calculated as:{1/(Slew Rate1)} - {1/(Slew Rate2)}For example : If Slew Rate 1 is 0.5 V/ns and slew Rate 2 is 0.4 V/ns, then the delta rise, fall rate is - 0.5ns/V . Using the table given, this would result in the need for an increase in tDS and tDH of 100 ps.Rev. 1.1 August. 2003。

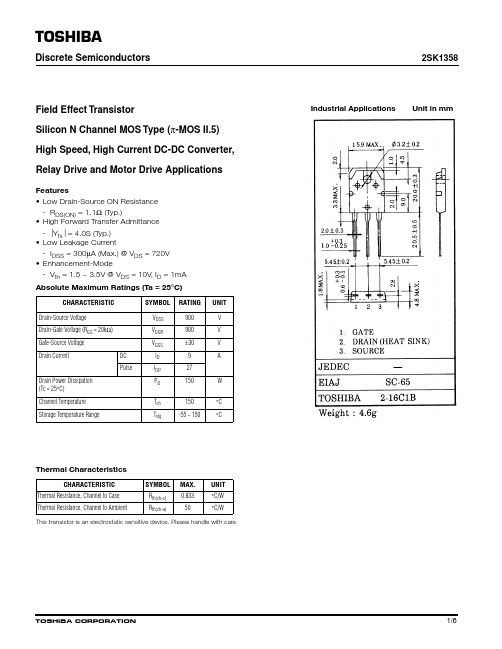

2SK1358中文资料

MIN.

– – 900 1.5 – 2.0 – – – – – – –

TYP.

– – – – 1.1 4.0 1300 100 180 25 40 20 100

MAX.

±100 300 0 50 80 40 200

UNIT

nA µA V V Ω S pF

2sk1358 toshibatoshiba corporation 1/6 discrete semiconductors 2sk1358 field effect transistor silicon channelmos type -mosii.5) high speed, high current dc-dc converter, relay drive motordrive applications features lowdrain-source highforward transfer admittance 4.0s(typ.) lowleakage current electrostaticsensitive device. please handle care.absolute maximum ratings (ta characteristicsymbol rating unit drain-source voltage dss900 drain-gatevoltage dgr900 gate-sourcevoltage draincurrent dc dp27 drain power dissipation (tc channeltemperature ch150 storagetemperature range stg-55 thermalcharacteristics characteristic symbol max. unit thermal resistance, channel th(ch-c)0.833 thermalresistance, channel th(ch-a)50 mmindustrial applications 2/6 toshiba corporation 2sk1358 source-drain diode ratings characteristics(ta electricalcharacteristics (ta characteristicsymbol test condition min. typ. max. unit gate leakage current 100na drain cut-off current drain-sourcebreakdown voltage (br)dss 0v900 gatethreshold voltage

K9S5608V0C资料

tCH tCSTO tWHR tCHZ

RE

tDS

tDH tIR

tRSTO tRHZ

Status Output

I/O0~7

70h

tCLS

CLE

tCLS tCLH tCS

CE

tWP

WE

tCH tCEA tWHR tCHZ

RE

tDH tDS

I/O0~7 70h

tIR

tREA tRHZ

Status Output

≈

1

元器件交易网

K9S5608V0C/B K9S2808V0C/B

Revision History

Revision No

0.4

K9S6408V0C/B

SmartMediaTM

History

1. Unified access timing parameter definition for multiple operating modes - Changed AC characteristics (Before) Parameter ALE to RE Delay (ID read) ALE to RE Delay (Read cycle) RE Low to Status Output CE Low to Status Output RE access time(Read ID) - AC characteristics (After) . Deleted tRSTO, tCSTO and tREADID / Added tCLR, tCEA Parameter ALE to RE Delay (ID read) ALE to RE Delay (Read cycle) CLE to RE Delay CE Access Time Symbol tAR1 tAR2 tCLR tCEA Min 50 50 10 45 Max ns Unit Symbol tAR1 tAR2 tRSTO tCSTO tREADID Min 100 100 Max 35 45 35detailed features and specifications including FAQ, please refer to Samsung Flash web site. /Products/Semiconductor/Flash/TechnicalInfo/datasheets.htm The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have any questions, please contact the SAMSUNG branch office near your office.

K4S280832O 三星 SDRAM 规格书

K4S280832OSAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or other-wise.Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.For updates or additional information about Samsung products, contact your nearest Samsung office.All brand names, trademarks and registered trademarks belong to their respective owners.ⓒ2010 Samsung Electronics Co., Ltd. All rights reserved.K4S281632O128Mb O-die SDRAM54TSOP(II) with Lead-Free & Halogen-Free (RoHS compliant)datasheetRev. 1.0 K4S280832OK4S281632O datasheet SDRAM Revision HistoryRevision No.History Draft Date Remark Editor1.0- First Spec. Release May. 2010-S.H.KimTable Of Contents128Mb O-die SDRAM1. KEY FEATURES (4)2. GENERAL DESCRIPTION (4)3. ORDERING INFORMATION (4)4. PACKAGE PHYSICAL DIMENSION (5)5. FUNCTIONAL BLOCK DIAGRAM (6)6. PIN CONFIGURATION (TOP VIEW) (7)7. INPUT/OUTPUT FUNCTION DESCRIPTION (7)8. ABSOLUTE MAXIMUM RATINGS (8)9. DC OPERATING CONDITIONS (8)10. CAPACITANCE (8)11. DC CHARACTERISTICS (x8) (9)12. DC CHARACTERISTICS (x16) (10)13. AC OPERATING TEST CONDITIONS (11)14. OPERATING AC PARAMETER (12)15. AC CHARACTERISTICS (13)16. DQ BUFFER OUTPUT DRIVE CHARACTERISTICS (13)17. IBIS SPECIFICATION (14)18. SIMPLIFIED TRUTH TABLE (18)1. KEY FEATURES• JEDEC standard 3.3V power supply • LVTTL compatible with multiplexed address • Four banks operation• MRS cycle with address key programs-. CAS latency (2 & 3)-. Burst length (1, 2, 4, 8 & Full page) -. Burst type (Sequential & Interleave)• All inputs are sampled at the positive going edge of the system clock. • Burst read single-bit write operation • DQM (x8) & L(U)DQM (x16) for masking • Auto & self refresh• 64ms refresh period (4K Cycle)• 54pin TSOP II Lead-Free and Halogen-Free package • RoHS compliant2. GENERAL DESCRIPTIONThe K4S280832O / K4S281632O is 134,217,728 bits synchronous high data rate Dynamic RAM organized as 4 x 4,194,304 words by 8 bits / 4 x 2,097,152 words by 16 bits, fabricated with SAMSUNG ′s high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.3. ORDERING INFORMATION[ Table 1 ] Row & Column address configurationPart ainization Max Freq.InterfacePackageK4S280832O-LC/L7516Mb x 8 133MHz (CL=3)LVTTL54pin TSOP(II)Lead-Free & Halogen-FreeK4S280832O-LC/L6016Mb x 8 166MHz (CL=3)K4S281632O-LC/L758Mb x 16133MHz (CL=3)K4S281632O-LC/L608Mb x 16166MHz (CL=3)OrganizationRow Address Column Address16Mx8A0~A11A0-A98Mx16A0~A11A0-A84. PACKAGE PHYSICAL DIMENSIONFigure 1. 54Pin TSOP(II) Package Dimension5. FUNCTIONAL BLOCK DIAGRAMBank SelectData Input Register4M x 8 / 2M x 164M x 8 / 2M x 16Sense AMPOutput BufferI/O ControlColumn DecoderLatency & Burst Length Programming RegisterAddress RegisterRow BufferRefresh CounterRow DecoderCol. BufferLRASLCBRLCKELRASLCBRLWELDQMCLK CKE CS RAS CAS WE L(U)DQMLWE LDQMDQiCLK ADDLCAS LWCBR 4M x 8 / 2M x 164M x 8 / 2M x 16Timing Register* Samsung Electronics reserves the right to change products or specification without notice.6. PIN CONFIGURATION (TOP VIEW)7. INPUT/OUTPUT FUNCTION DESCRIPTIONPin Name Description CLK System clock Active on the positive going edge to sample all inputs.CS Chip select Disables or enables device operation by masking or enabling all inputs except CLK, CKE and DQMCKE Clock enable Masks system clock to freeze operation from the next clock cycle. CKE should be enabled at least one cycle prior to new command. Disable input buffers for power down in standby.A0 ~ A11Address Row/column addresses are multiplexed on the same pins. Row address : RA0 ~ RA11,Column address : (x8 : CA0 ~ CA9), (x16 : CA0 ~ CA8)BA0 ~ BA1Bank select address Selects bank to be activated during row address latch time. Selects bank for read/write during column address latch time.RAS Row address strobe Latches row addresses on the positive going edge of the CLK with RAS low. Enables row access & precharge.CAS Column address strobe Latches column addresses on the positive going edge of the CLK with CAS low. Enables column access.WE Write enable Enables write operation and row precharge. Latches data in starting from CAS, WE active.DQM Data input/output mask Makes data output Hi-Z, tSHZ after the clock and masks the output. Blocks data input when DQM active.DQ0 ~ N Data input/output Data inputs/outputs are multiplexed on the same pins. (x8 : DQ0 ~ 7), (x16 : DQ0 ~ 15)V DD/V SS Power supply/ground Power and ground for the input buffers and the core logic.V DDQ/V SSQ Data output power/ground Isolated power supply and ground for the output buffers to provide improved noise immunity.N.C/RFU No connection/reserved for future useThis pin is recommended to be left No Connection on the device.54Pin TSOP(400mil x 875mil)(0.8 mm Pin pitch)123456789101112131415161718192021222324252627545352515049484746454443424140393837363534333231302928V DDDQ0V DDQN.CDQ1V SSQN.CDQ2V DDQN.CDQ3V SSQN.CV DDN.CWECASRASCSBA0BA1A10/APA0A1A2A3V DDV SSDQ7V SSQN.CDQ6V DDQN.CDQ5V SSQN.CDQ4V DDQN.CV SSN.C/RFUDQMCLKCKEN.CA11A9A8A7A6A5A4V SSV DDDQ0V DDQDQ1DQ2V SSQDQ3DQ4V DDQDQ5DQ6V SSQDQ7V DDLDQMWECASRASCSBA0BA1A10/APA0A1A2A3V DDV SSDQ15V SSQDQ14DQ13V DDQDQ12DQ11V SSQDQ10DQ9V DDQDQ8V SSN.C/RFUUDQMCLKCKEN.CA11A9A8A7A6A5A4V SSx16x8x16x88. ABSOLUTE MAXIMUM RATINGSParameter Symbol Value Unit Voltage on any pin relative to V SS V IN, V OUT-1.0 ~ 4.6V Voltage on V DD supply relative to V SS V DD, V DDQ-1.0 ~ 4.6V Storage temperature T STG-55 ~ +150°C Power dissipation P D1WShort circuit current I OS50mA NOTE : Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded.Functional operation should be restricted to recommended operating condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliability.9. DC OPERATING CONDITIONSRecommended operating conditions (Voltage referenced to V SS = 0V, T A = 0 to 70°C)Parameter Symbol Min Typ Max Unit NOTE Supply voltage V DD, V DDQ 3.0 3.3 3.6VInput logic high voltage V IH 2.0 3.0V DD+0.3V1 Input logic low voltage V IL-0.300.8V2 Output logic high voltage V OH 2.4--V I OH = -2mA Output logic low voltage V OL--0.4V I OL = 2mA Input leakage current I LI-10-10uA3 NOTE :1. V IH (max) = 5.6V AC. The overshoot voltage duration is ≤ 3ns.2. V IL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.3. Any input 0V ≤ V IN≤ V DDQ.Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State outputs.10. CAPACITANCE(VDD = 3.3V, TA = 23°C, f = 1MHz, VREF =1.4V ± 200 mV)Pin Symbol Min Max Unit Clock CCLK 2.5 3.5pF RAS, CAS, WE, CS, CKE, DQM CIN 2.5 3.8pF Address CADD 2.5 3.8pF (x8 : DQ0 ~ DQ7), (x16 : DQ0 ~ DQ15) COUT 4.0 6.0pF(Recommended operating condition unless otherwise noted, TA = 0 to 70°C)NOTE :1. Measured with outputs open.2. Refresh period is 64ms.3. K4S280832O-LC4. K4S280832O-LL5. Unless otherwise noticed, input swing level is CMOS(V IH /V IL =V DDQ /V SSQ ).ParameterSymbolTest ConditionVersion UnitNOTE6075Operating current (One bank active)ICC1 Burst length = 1 tRC ≥ tRC(min) IO = 0 mA4040mA 1Precharge standby current in power-down modeICC2PCKE ≤ V IL (max), tCC = 10ns22mAICC2PS CKE & CLK ≤ V IL (max), tCC = ∞22Precharge standby current in non power-down modeICC2NCKE ≥ V IH (min), CS ≥ V IH (min), tCC = 10ns Input signals are changed one time during 20ns1515mAICC2NSCKE ≥ V IH (min), CLK ≤ V IL (max), tCC = ∞Input signals are stable 1010Active standby current in power-down modeICC3PCKE ≤ V IL (max), tCC = 10ns55mA ICC3PS CKE & CLK ≤ V IL (max), tCC = ∞55Active standby current in non power-down mode (One bank active)ICC3N CKE ≥ V IH (min), CS ≥ V IH (min), tCC = 10ns Input signals are changed one time during 20ns 2525mA ICC3NSCKE ≥ V IH (min), CLK ≤ V IL (max), tCC = ∞Input signals are stable 2020mAOperating current (Burst mode)ICC4IO = 0 mA Page burst4Banks Activated tCCD = 2CLKs 6060mA 1Refresh current ICC5tRC ≥ tRC(min)100100mA 2Self refresh currentICC6CKE ≤ 0.2VC 22mA 3L0.80.8mA4(Recommended operating condition unless otherwise noted, TA = 0 to 70°C)NOTE :1. Measured with outputs open.2. Refresh period is 64ms.3. K4S281632O-LC4. K4S281632O-LL5. Unless otherwise noticed, input swing level is CMOS(V IH /V IL =V DDQ /V SSQ ).ParameterSymbolTest ConditionVersion UnitNOTE6075Operating current (One bank active)ICC1 Burst length = 1 tRC ≥ tRC(min) IO = 0 mA4040mA 1Precharge standby current in power-down modeICC2PCKE ≤ V IL (max), tCC = 10ns22mAICC2PS CKE & CLK ≤ V IL (max), tCC = ∞22Precharge standby current in non power-down modeICC2NCKE ≥ V IH (min), CS ≥ V IH (min), tCC = 10ns Input signals are changed one time during 20ns1515mAICC2NSCKE ≥ V IH (min), CLK ≤ V IL (max), tCC = ∞Input signals are stable 1010Active standby current in power-down modeICC3PCKE ≤ V IL (max), tCC = 10ns55mA ICC3PS CKE & CLK ≤ V IL (max), tCC = ∞55Active standby current in non power-down mode (One bank active)ICC3N CKE ≥ V IH (min), CS ≥ V IH (min), tCC = 10ns Input signals are changed one time during 20ns 2525mA ICC3NSCKE ≥ V IH (min), CLK ≤ V IL (max), tCC = ∞Input signals are stable 2020mAOperating current (Burst mode)ICC4IO = 0 mA Page burst4Banks Activated tCCD = 2CLKs 6060mA 1Refresh current ICC5tRC ≥ tRC(min)100100mA 2Self refresh currentICC6CKE ≤ 0.2VC 22mA 3L0.80.8mA4Figure 3. AC output load circuitFigure 2. DC output load circuit13. AC OPERATING TEST CONDITIONS(V DD = 3.3V ± 0.3V, T A = 0 to 70°C)Parameter Value Unit Input levels (Vih/Vil)2.4/0.4V Input timing measurement reference level 1.4V Input rise and fall timetr/tf = 1/1ns Output timing measurement reference level 1.4VOutput load conditionSee Figure 33.3V1200Ω870ΩOutput50pFV OH (DC) = 2.4V, I OH = -2mA V OL (DC) = 0.4V, I OL = 2mAVtt = 1.4V50ΩOutput50pFZ0 = 50Ω14. OPERATING AC PARAMETER(AC operating conditions unless otherwise noted)NOTE : 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle timeand then rounding off to the next higher integer.2. Minimum delay is required to complete write.3. All parts allow every cycle column address change.4. In case of row precharge interrupt, auto precharge and read burst stop.5. In 100MHz and below 100MHz operating conditions, tRDL=1CLK and tDAL=1CLK + 20ns is also supported. SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + tRP .6. t RC = t RFC , t RDL = t WRParameterSymbol VersionUnit 6075Row active to row active delay tRRD(min)1215ns RAS to CAS delay tRCD(min)1820ns Row precharge time tRP(min)1820ns Row active time tRAS(min)4245ns tRAS(max)100us Row cycle timetRC(min)6065ns Last data in to row precharge tRDL(min)2CLK Last data in to Active delaytDAL(min) 2 CLK + tRP-Last data in to new col. address delay tCDL(min)1CLK Last data in to burst stoptBDL(min)1CLK Col. address to col. address delay tCCD(min)1CLK Number of valid output dataCAS latency=32eaCAS latency=2-115. AC CHARACTERISTICS(AC operating conditions unless otherwise noted)NOTE : 1. Parameters depend on programmed CAS latency.2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.3. Assumed input rise and fall time (tr & tf) = 1ns.If tr & tf is longer than 1ns, transient time compensation should be considered, i.e., [(tr + tf)/2-1]ns should be added to the parameter.4. tSS applies for address setup tiem, clock enable setup time, commend setup tiem and data setup time.tSH applies for address setup tiem, clock enable setup time, commend setup tiem and data setup time.16. DQ BUFFER OUTPUT DRIVE CHARACTERISTICSNOTE : 1. Rise time specification based on 0pF + 50 Ω to VSS, use these values to design to.2. Fall time specification based on 0pF + 50 Ω to VDD, use these values to design to.3. Measured into 50pF only, use these values to characterize to.4. All measurements done with respect to VSS.ParameterSymbol6075Min Max Min Max CLK cycle time CAS latency=3tCC 610007.51000CAS latency=2-10CLK to valid output delay CAS latency=3tSAC 5 5.4CAS latency=2-6Output data hold timeCAS latency=3tOH 2.53CAS latency=2-3CLK high pulse width tCH 2.5 2.5CLK low pulse width tCL 2.5 2.5Input setup time tSS 1.5 1.5Input hold time tSH 10.8CLK to output in Low-Z tSLZ11CLK to output in Hi-ZCAS latency=3tSHZ5 5.4CAS latency=2-6ParameterSymbol ConditionMin TypMax Unit NOTE Output rise time trh Measure in linear region : 1.2V ~ 1.8V 1.37 4.37Volts/ns 3 Output fall time tfh Measure in linear region : 1.2V ~ 1.8V 1.30 3.8Volts/ns 3 Output rise time trh Measure in linear region : 1.2V ~ 1.8V 2.8 3.9 5.6Volts/ns 1,2 Output fall timetfhMeasure in linear region : 1.2V ~ 1.8V2.02.9 5.0Volts/ns1,217. IBIS SPECIFICATION [ Table 2 ] IOH Characteristics (Pull-up)Voltage 200MHz166MHz133MHzMin200MHz166MHz133MHzMax(V)I (mA)I (mA) 3.45 -2.4 3.3 -27.3 3.0 0.0 -74.1 2.6-21.1-129.2 2.4-34.1-153.3 2.0-58.7-197.0 1.8-67.3-226.2 1.65-73.0-248.0 1.5-77.9-269.7 1.4-80.8-284.3 1.0-88.6-344.5 0.0-93.0-502.40 -100 -200 -300 -400 -500 -600030.51 1.52 2.5 3.5VoltagemAI OH Min (200MHz/166MHz/133MHz)I OH Max (200MHz/166MHz/133MHz)Figure 4. 200MHz/166MHz/133MHz Pull-upFigure 5. 200MHz/166MHz/133MHz Pull-down[ Table 3 ] IOL Characteristics (Pull-down)Voltage 200MHz 166MHz 133MHz Min 200MHz 166MHz 133MHz Max (V)I (mA)I (mA)0.0 0.0 0.00.427.5 70.2 0.6541.8107.5 0.8551.6133.81.058.0151.21.470.7187.71.572.9194.4 1.6575.4202.51.877.0208.6 1.9577.6212.03.080.3219.6 3.4581.4222.6250200150100500030.511.522.53.5Voltagem AI OL Min (200MHz/166MHz/133MHz)I OL Max (200MHz/166MHz/133MHz)Figure 6. Minimum V DD clamp current (Referenced to V DD )V DD (V)I (mA)0.0 0.00.2 0.00.4 0.00.6 0.00.7 0.00.8 0.00.9 0.01.0 0.231.2 1.341.4 3.021.6 5.061.8 7.352.0 9.832.212.482.415.302.618.31201510500312Voltagem AI (mA)Figure 7. Minimum V SS clamp currentV SS (V)I (mA)-2.6-57.23-2.4-45.77-2.2-38.26-2.0-31.22-1.8-24.58-1.6-18.37-1.4-12.56-1.2 -7.57-1.0 -3.37-0.9 -1.75-0.8 -0.58-0.7 -0.05-0.6 0.0-0.4 0.0-0.2 0.0 0.00.0m AI (mA)0-10-20-30-40-30-2-1-50-60Voltage18. SIMPLIFIED TRUTH TABLE(V=Valid, X=Don ′t care, H=Logic high, L=Logic low)NOTE :1. OP Code : Operand codeA0 ~ A11 & BA0 ~ BA1 : Program keys. (@ MRS)2. MRS can be issued only at all banks precharge state.A new command can be issued after 2 CLK cycles of MRS.3. Auto refresh functions are as same as CBR refresh of DRAM.The automatical precharge without row precharge command is meant by "Auto". Auto/self refresh can be issued only at all banks precharge state.4. BA0 ~ BA1 : Bank select addresses.If both BA0 and BA1 are "Low" at read, write, row active and precharge, bank A is selected. If BA0 is "High" and BA1 is "Low" at read, write, row active and precharge, bank B is selected. If BA0 is "Low" and BA1 is "High" at read, write, row active and precharge, bank C is selected. If both BA0 and BA1 are "High" at read, write, row active and precharge, bank D is selected. If A10/AP is "High" at row precharge, BA0 and BA1 is ignored and all banks are selected.5. During burst read or write with auto precharge, new read/write command can not be issued. Another bank read/write command can be issued after the end of burst.New row active of the associated bank can be issued at tRP after the end of burst.6. Burst stop command is valid at every burst length.7. DQM sampled at positive going edge of a CLK and masks the data-in at the very CLK (Write DQM latency is 0), but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)CommandCKEn-1CKEn CS RAS CAS WE DQM BA 0,1A10/AP A0 ~ A9, A11,NOTE Register Mode register set HX L L L L X OP code1,2RefreshAuto refreshH H L L L H X X 3Self refreshEntryL 3ExitL H L H H H X X3H X X X 3Bank active & row addr.H X L L H H X V Row address Read &column address Auto precharge disable H X L H L H X V L Column address 4Auto precharge enable H 4,5Write &column address Auto precharge disable H X L H L L X V L Column address4Auto precharge enableH 4,5Burst stop HX L H H L X X6PrechargeBank selection H X L L H L X V L XAll banksXH Clock suspend or active power downEntry H L H X X X X XL V V V Exit L H X X X X X Precharge power down modeEntryH L H X X X XXL H H H ExitL HH X X X X LV VVDQMH X V X 7No operation commandHXH X X X XXLHHH。

K4S560832E-TC75中文资料

CMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)256Mb E-die SDRAM SpecificationRevision 1.5May 2004* Samsung Electronics reserves the right to change products or specification without notice.CMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)Revision HistoryRevision 1.0 (May. 2003)- First release.Revision 1.1 (June. 2003)- Correct TypoRevision 1.2 (June. 2003)- Added 166MHz speed bin in x16Revision 1.3 (September. 2003)- Corrected typo in ordering information.Revision 1.4 (February, 2004) - Corrected typo.Revision 1.5 (May, 2004)Added Note 5. sentense of tRDL parameterCMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)Part No.Orgainization Max Freq.InterfacePackageK4S560432E-TC(L)7564M x 4 133MHz (CL=3)LVTTL54pin TSOP(II)K4S560832E-TC(L)7532M x 8 133MHz (CL=3)K4S561632E-TC(L)60/7516M x 16166MHz (CL=3)The K4S560432E / K4S560832E / K4S561632E is 268,435,456 bits synchronous high data rate Dynamic RAM organized as 4 x 16,777,216 words by 4 bits / 4 x 8,388,608 words by 8bits / 4 x 4,194,304 words by 16bits, fabricated with SAMSUNG's high perfor-mance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.• JEDEC standard 3.3V power supply • LVTTL compatible with multiplexed address • Four banks operation• MRS cycle with address key programs -. CAS latency (2 & 3)-. Burst length (1, 2, 4, 8 & Full page) -. Burst type (Sequential & Interleave)• All inputs are sampled at the positive going edge of the system clock. • Burst read single-bit write operation• DQM (x4,x8) & L(U)DQM (x16) for masking • Auto & self refresh• 64ms refresh period (8K Cycle)GENERAL DESCRIPTIONFEATURES16M x 4Bit x 4 Banks / 8M x 8Bit x 4 Banks / 4M x 16Bit x 4 Banks SDRAMOrdering InformationRow & Column address configurationOrganizationRow Address Column Address 64Mx4A0~A12A0-A9, A1132Mx8A0~A12A0-A916Mx16A0~A12A0-A8CMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)54Pin TSOP(II) Package DimensionPackage Physical DimensionCMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)FUNCTIONAL BLOCK DIAGRAMLWE LDQMDQi* Samsung Electronics reserves the right to change products or specification without notice.CMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)PIN CONFIGURATION (Top view)V DD N.C V DDQ N.C DQ0V SSQ N.C N.C V DDQ N.C DQ1V SSQ N.C V DD N.C WE CAS RAS CS BA0BA1A10/APA0A1A2A3V DD123456789101112131415161718192021222324252627545352515049484746454443424140393837363534333231302928V SS N.C V SSQ N.C DQ3V DDQ N.C N.C V SSQ N.C DQ2V DDQ N.C V SSN.C/RFU DQM CLK CKE A12A11A9A8A7A6A5A4V SS54Pin TSOP(400mil x 875mil)(0.8 mm Pin pitch)PIN FUNCTION DESCRIPTIONPin NameInput FunctionCLK System clock Active on the positive going edge to sample all inputs.CS Chip select Disables or enables device operation by masking or enabling all inputs except CLK, CKE and DQMCKEClock enableMasks system clock to freeze operation from the next clock cycle.CKE should be enabled at least one cycle prior to new command.Disable input buffers for power down in standby.A 0 ~ A 12AddressRow/column addresses are multiplexed on the same pins.Row address : RA 0 ~ RA 12,Column address : (x4 : CA 0 ~ CA 9,CA 11), (x8 : CA 0 ~ CA 9), (x16 : CA 0 ~ CA 8)BA 0 ~ BA 1Bank select address Selects bank to be activated during row address latch time.Selects bank for read/write during column address latch time.RAS Row address strobe Latches row addresses on the positive going edge of the CLK with RAS low.Enables row access & precharge.CAS Column address strobe Latches column addresses on the positive going edge of the CLK with CAS low.Enables column access.WE Write enableEnables write operation and row tches data in starting from CAS, WE active.DQM Data input/output mask Makes data output Hi-Z, t SHZ after the clock and masks the output.Blocks data input when DQM active.DQ 0 ~ N Data input/output Data inputs/outputs are multiplexed on the same pins.(x4 : DQ 0 ~ 3), (x8 : DQ 0 ~ 7), (x16 : DQ 0 ~ 15)V DD /V SS Power supply/ground Power and ground for the input buffers and the core logic.V DDQ /V SSQ Data output power/ground Isolated power supply and ground for the output buffers to provide improved noise immunity.N.C/RFUNo connection/reserved for future useThis pin is recommended to be left No Connection on the device.V DD DQ0V DDQ N.C DQ1V SSQ N.C DQ2V DDQ N.C DQ3V SSQ N.C V DD N.C WE CAS RAS CS BA0BA1A10/AP A0A1A2A3V DD V SS DQ7V SSQ N.C DQ6V DDQ N.C DQ5V SSQ N.C DQ4V DDQ N.C V SSN.C/RFU DQM CLK CKE A12A11A9A8A7A6A5A4V SSV DD DQ0V DDQ DQ1DQ2V SSQ DQ3DQ4V DDQ DQ5DQ6V SSQ DQ7V DD LDQM WE CAS RAS CS BA0BA1A10/AP A0A1A2A3V DD V SS DQ15V SSQ DQ14DQ13V DDQ DQ12DQ11V SSQ DQ10DQ9V DDQ DQ8V SSN.C/RFU UDQM CLK CKE A12A11A9A8A7A6A5A4V SSx16x8x4x16x8x4CMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)ABSOLUTE MAXIMUM RATINGSParameter Symbol Value Unit Voltage on any pin relative to Vss V IN , V OUT -1.0 ~ 4.6V Voltage on V DD supply relative to Vss V DD , V DDQ-1.0 ~ 4.6V Storage temperature T STG -55 ~ +150°C Power dissipation P D 1W Short circuit currentI OS50mAPermanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded.Functional operation should be restricted to recommended operating condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliability.Note :DC OPERATING CONDITIONSRecommended operating conditions (Voltage referenced to V SS = 0V, T A = 0 to 70°C) Parameter Symbol Min Typ Max Unit NoteSupply voltage V DD , V DDQ3.0 3.3 3.6V Input logic high voltage V IH 2.0 3.0V DD +0.3V 1Input logic low voltage V IL -0.300.8V 2Output logic high voltage V OH 2.4--V I OH = -2mA Output logic low voltage V OL --0.4V I OL = 2mAInput leakage currentI LI-10-10uA31. V IH (max) = 5.6V AC. The overshoot voltage duration is ≤ 3ns.2. V IL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.3. Any input 0V ≤ V IN ≤ V DDQ .Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State outputs.Notes :CAPACITANCE (V DD = 3.3V, T A = 23°C, f = 1MHz, V REF =1.4V ± 200 mV)PinSymbol Min Max Unit ClockC CLK 2.5 3.5pF RAS, CAS, WE, CS, CKE, DQM C IN 2.5 3.8pF AddressC ADD2.53.8pF (x4 : DQ 0 ~ DQ 3), (x8 : DQ 0 ~ DQ 7), (x16 : DQ 0 ~ DQ 15) C OUT4.06.0pFCMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)(Recommended operating condition unless otherwise noted, T A = 0 to 70°C)ParameterSymbolTest ConditionVersion Unit Note75Operating current (One bank active)I CC1 Burst length = 1 t RC ≥ t RC (min) I O = 0 mA80mA 1Precharge standby current in power-down mode I CC2P CKE ≤ V IL (max), t CC = 10ns 2mAI CC2PS CKE & CLK ≤ V IL (max), t CC = ∞2Precharge standby current in non power-down mode I CC2NCKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns20mAI CC2NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 10Active standby current in power-down mode I CC3PCKE ≤ V IL (max), t CC = 10ns6mA I CC3PS CKE & CLK ≤ V IL (max), t CC = ∞6Active standby current in non power-down mode (One bank active)I CC3N CKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns 25mA I CC3NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 25mAOperating current (Burst mode)I CC4 I O = 0 mA Page burst4banks Activated.t CCD = 2CLKs 100mA 1Refresh current I CC5t RC ≥ t RC (min)180mA 2Self refresh currentI CC6CKE ≤ 0.2VC 3mA 3L1.5mA41. Measured with outputs open.2. Refresh period is 64ms.3. K4S5604(08)32E-TC4. K4S5604(08)32E-TL5. Unless otherwise noticed, input swing level is CMOS(V IH /V IL =V DDQ /V SSQ ).Notes :DC CHARACTERISTICS (x4, x8)CMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)(Recommended operating condition unless otherwise noted, T A = 0 to 70°C)ParameterSymbolTest ConditionVersion Unit Note6075Operating current (One bank active)I CC1Burst length = 1t RC ≥ t RC (min)I O = 0 mA14090mA 1Precharge standby current in power-down modeI CC2P CKE ≤ V IL (max), t CC = 10ns 2mA I CC2PS CKE & CLK ≤ V IL (max), t CC = ∞2Precharge standby current in non power-down mode I CC2N CKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns 20mAI CC2NS CKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 10Active standby current in power-down mode I CC3P CKE ≤ V IL (max), t CC = 10ns 6mA I CC3PS CKE & CLK ≤ V IL (max), t CC = ∞6Active standby current in non power-down mode (One bank active)I CC3N CKE ≥ V IH (min), CS ≥ V IH (min), t CC = 10nsInput signals are changed one time during 20ns 25mA I CC3NSCKE ≥ V IH (min), CLK ≤ V IL (max), t CC = ∞Input signals are stable 25mAOperating current (Burst mode)I CC4I O = 0 mA Page burst4banks Activated.t CCD = 2CLKs 170130mA 1Refresh current I CC5t RC ≥ t RC (min)200180mA 2Self refresh currentI CC6CKE ≤ 0.2VC 3mA 3 L1.5mA41. Measured with outputs open.2. Refresh period is 64ms.3. K4S561632E-TC4. K4S561632E-TL5. Unless otherwise noticed, input swing level is CMOS(V IH /V IL =V DDQ /V SSQ ).Notes :DC CHARACTERISTICS (x16)CMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)AC OPERATING TEST CONDITIONS (V DD = 3.3V ± 0.3V, T A = 0 to 70°C)Parameter Value Unit AC input levels (Vih/Vil)2.4/0.4V Input timing measurement reference level 1.4V Input rise and fall timetr/tf = 1/1ns Output timing measurement reference level 1.4VOutput load conditionSee Fig. 23.3V1200Ω870ΩOutput50pFV OH (DC) = 2.4V, I OH = -2mA V OL (DC) = 0.4V, I OL = 2mAVtt = 1.4V50ΩOutput50pFZ0 = 50Ω(Fig. 2) AC output load circuit(Fig. 1) DC output load circuit OPERATING AC PARAMETER(AC operating conditions unless otherwise noted)ParameterSymbol VersionUnit Note 6075Row active to row active delay t RRD (min)1215ns 1RAS to CAS delay t RCD (min)1820ns 1Row precharge time t RP (min)1820ns 1Row active time t RAS (min)4245ns 1t RAS (max)100us Row cycle timet RC (min)6065ns 1Last data in to row precharge t RDL (min)2CLK 2,5Last data in to Active delayt DAL (min) 2 CLK + tRP-5Last data in to new col. address delay t CDL (min)1CLK 2Last data in to burst stopt BDL (min)1CLK 2Col. address to col. address delay t CCD (min)1CLK 3Number of valid output dataCAS latency=32ea4CAS latency=2-11. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle timeand then rounding off to the next higher integer.2. Minimum delay is required to complete write.3. All parts allow every cycle column address change.4. In case of row precharge interrupt, auto precharge and read burst stop.5. In 100MHz and below 100MHz operating conditions, tRDL=1CLK and tDAL=1CLK + 20ns is also supported. SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + tRP .Notes :CMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)DQ BUFFER OUTPUT DRIVE CHARACTERISTICSParameterSymbol ConditionMin TypMax Unit Notes Output rise time trh Measure in linear region : 1.2V ~ 1.8V 1.37 4.37Volts/ns 3 Output fall time tfh Measure in linear region : 1.2V ~ 1.8V 1.30 3.8Volts/ns 3 Output rise time trh Measure in linear region : 1.2V ~ 1.8V 2.8 3.9 5.6Volts/ns 1,2 Output fall timetfhMeasure in linear region : 1.2V ~ 1.8V2.02.9 5.0Volts/ns1,21. Rise time specification based on 0pF + 50 Ω to V SS , use these values to design to.2. Fall time specification based on 0pF + 50 Ω to V DD , use these values to design to.3. Measured into 50pF only, use these values to characterize to.4. All measurements done with respect to V SS .Notes :AC CHARACTERISTICS (AC operating conditions unless otherwise noted)ParameterSymbol 6075Unit Note Min Max Min Max CLK cycle time CAS latency=3t CC 610007.51000ns 1CAS latency=2-10CLK to valid output delay CAS latency=3t SAC 5 5.4ns 1,2CAS latency=2-6Output data hold timeCAS latency=3t OH 2.53ns 2CAS latency=2-3CLK high pulse width t CH 2.5 2.5ns 3CLK low pulse width t CL 2.5 2.5ns 3Input setup time t SS 1.5 1.5ns 3Input hold time t SH 10.8ns 3CLK to output in Low-Z t SLZ 11ns2CLK to output in Hi-ZCAS latency=3t SHZ5 5.4nsCAS latency=2-61. Parameters depend on programmed CAS latency.2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.3. Assumed input rise and fall time (tr & tf) = 1ns.If tr & tf is longer than 1ns, transient time compensation should be considered, i.e., [(tr + tf)/2-1]ns should be added to the parameter.Notes :CMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)0-100-200-300-400-500-600030.511.522.53.5Voltagem A100MHz/133MHz Pull-upI OH Min (100MHz/133MHz)I OH Max (66 and 100MHz/133MHz)250200150100500030.511.522.53.5Voltagem A100MHz/133MHz Pull-downI OL Min (100MHz/133MHz)I OL Max (100MHz/133MHz)I OH Characteristics (Pull-up)Voltage 100MHz 133MHz Min 100MHz 133MHz Max (V)I (mA)I (mA) 3.45 -2.43.3 -27.33.0 0.0 -74.12.6-21.1-129.22.4-34.1-153.32.0-58.7-197.01.8-67.3-226.2 1.65-73.0-248.01.5-77.9-269.71.4-80.8-284.31.0-88.6-344.50.0-93.0-502.4IBIS SPECIFICATIONI OL Characteristics (Pull-down)Voltage 100MHz 133MHz Min 100MHz 133MHz Max (V)I (mA)I (mA)0.0 0.0 0.00.427.5 70.2 0.6541.8107.5 0.8551.6133.81.058.0151.21.470.7187.71.572.9194.4 1.6575.4202.51.877.0208.6 1.9577.6212.03.080.3219.6 3.4581.4222.6CMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)V DD Clamp @ CLK, CKE, CS, DQM & DQV DD (V)I (mA)0.00.00.20.00.40.00.60.00.70.00.80.00.90.01.0 0.231.2 1.341.4 3.021.6 5.061.8 7.352.0 9.832.212.482.415.302.618.31V SS Clamp @ CLK, CKE, CS, DQM & DQV SS (V)I (mA)-2.6-57.23-2.4-45.77-2.2-38.26-2.0-31.22-1.8-24.58-1.6-18.37-1.4-12.56-1.2 -7.57-1.0 -3.37-0.9 -1.75-0.8 -0.58-0.7 -0.05-0.6 0.0-0.4 0.0-0.2 0.0 0.00.0201510500312Voltagem AI (mA)Voltagem AI (mA)Minimum V DD clamp current(Referenced to V DD )Minimum V SS clamp current0-10-20-30-40-30-2-1-50-60CMOS SDRAMRev. 1.5 May 2004SDRAM 256Mb E-die (x4, x8, x16)SIMPLIFIED TRUTH TABLE (V=Valid, X=Don't care, H=Logic high, L=Logic low)CommandCKEn-1CKEnCSRASCASWEDQMBA 0,1A 10/APA 0 ~ A 9 A 11, A 12NoteRegisterMode register set H X L L L L X OP code1,2RefreshAuto refreshH H L L L H X X 3Self refreshEntry L 3ExitL H L H H H X X3H X X X 3Bank active & row addr.H X L L H H X V Row address Read &column address Auto precharge disable H X L H L H X V L Column address 4Auto precharge enable H 4,5Write &column address Auto precharge disable H X L H L L X VL Column address4Auto precharge enableH 4,5Burst stop HX L H H L X X 6Precharge Bank selection H X L L H L X V L XAll banksX H Clock suspend or active power downEntry H L H X X X X XL V V V Exit L H X X X X X Precharge power down modeEntryH L H X X X XXL H H H ExitL HH X X X X L V V V DQMH X V X 7No operation commandHXH X X X XXLHHHNotes :1. OP Code : Operand codeA 0 ~ A 12 & BA 0 ~ BA 1 : Program keys. (@ MRS)2. MRS can be issued only at all banks precharge state.A new command can be issued after 2 CLK cycles of MRS.3. Auto refresh functions are as same as CBR refresh of DRAM.The automatical precharge without row precharge command is meant by "Auto". Auto/self refresh can be issued only at all banks precharge state.4. BA 0 ~ BA 1 : Bank select addresses.If both BA 0 and BA 1 are "Low" at read, write, row active and precharge, bank A is selected. If BA 0 is "High" and BA 1 is "Low" at read, write, row active and precharge, bank B is selected. If BA 0 is "Low" and BA 1 is "High" at read, write, row active and precharge, bank C is selected. If both BA 0 and BA 1 are "High" at read, write, row active and precharge, bank D is selected. If A 10/AP is "High" at row precharge, BA 0 and BA 1 is ignored and all banks are selected.5. During burst read or write with auto precharge, new read/write command can not be issued. Another bank read/write command can be issued after the end of burst.New row active of the associated bank can be issued at t RP after the end of burst.6. Burst stop command is valid at every burst length.7. DQM sampled at positive going edge of a CLK and masks the data-in at the very CLK (Write DQM latency is 0), but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)。

SDRAM存储器k4s641632详细参数及说明