AX88760_Reference_Schematic_v100-5

Atmel CryptoAuthentication

Application Note Single-Wire and I2C Interfaces Seamless DebuggingUsing Saleae Logic AnalyzerATSHA204A, ATECC108A, and ATECC508A Prerequisites●Hardware PrerequisitesAtmel® AT88CK490 or AT88CK590 Demo-Evaluation Board orAtmel AT88CK101-() KitSaleae Logic Analyzer●Software PrerequisitesAtmel Crypto Evaluation Studio (ACES)IntroductionThe purpose of this document is to help the user gain a better understanding of how to use the Atmel CryptoAuthentication™ ATSHA204A, ATECC108A, and ATECC508A devices (crypto device) with the Saleae Logic Analyzer. The Saleae Logic Analyzer is a powerful tool to debug and evaluate the commands coming to and from these devices. The tool supports both the standard I2C and the Atmel Single-Wire Interface (SWI) protocols.The goal of this application note is to:●Understand the bus interfaces of the crypto device using the Saleae LogicAnalyzer.●Develop and debug with the crypto device using the Saleae Logic Analyzer. SummaryThe Saleae Logic Analyzer provides an in depth tool to quickly develop and debug integration of the crypto device into a customer’s system. The bus decoding allows for easy understanding of all bus traffic to the crypto device. By reducing the development time, the Saleae Logic Analyzer greatly reduces the cost of adding the crypto device.CryptoAuthentication for Single-Wire and I 2C Interfaces Seamless Debugging Using SaleaeLogic Analyzer [APPLICATION NOTE]Atmel-8847B-CryptoAuth-SWI-I2C-Seamless-Debugging-Saleae-Logic-Analyzer-ApplicationNote_08201521.Saleae Logic AnalyzerOn load of the analyzer, either 8 or 16 channels will display depending on the analyzer used. Protocol specific settings are located on the far right under the heading, Analyzers .Figure 1-1.Channels and Protocol SettingsThe crypto device supports either a Single-Wire Interface (SWI) or I 2C Interface depending on the P/N. ●SWI — Supported through the use of a DLL library. Use version 1.1.16 or greater. This version comes with support on Win, LNX, and IOS.●I 2C — Supported by the use of the built-in I 2C interface that is included in the Saleae download.3CryptoAuthentication for Single-Wire and I 2C Interfaces Seamless Debugging Using SaleaeLogic Analyzer [APPLICATION NOTE]Atmel-8847B-CryptoAuth-SWI-I2C-Seamless-Debugging-Saleae-Logic-Analyzer-ApplicationNote_0820152.Single-Wire Interface (SWI)Use the SWI DLL library version 1.1.16 or greater.1.Copy the DLL into the Saleae LLC\Analyzers directory on the user’s PC. Once the driver has been copied to the correct folder, the Atmel SWI option will appear and be listed in the Analyzer drop-down options. The SWI Analyzer has three display modes:Token Byte Packet (as described in the datasheet)Figure 2-1.Atmel SWI Option2.Select the Atmel SWI Analyzer from the list. 3.After selecting Atmel SWI Analyzer , rename the channel when prompted, 4.Select the Falling Edge Trigger option and start sampling. Using ACES, select a command and send it to the device. For an overview of the ACES tool, please see “Using ACES Application Note”. This will cause the bus to become active and the Analyzer will trigger on the first falling edge and data line.In the screen shot below, the Wake command has been captured followed by Wake Status Read. The Wake command is a special token designed to wake the device and reset the watchdog timer.Figure 2-2.Wake Command Followed by Wake Status ReadEnlargement ofthe Analyzerpull-down options.CryptoAuthentication for Single-Wire and I 2C Interfaces Seamless Debugging Using SaleaeLogic Analyzer [APPLICATION NOTE]Atmel-8847B-CryptoAuth-SWI-I2C-Seamless-Debugging-Saleae-Logic-Analyzer-ApplicationNote_0820154The token view displays each logic bit which is made up of seven bits on the wire. Each group of seven bits is encoded either as a Logic 1 or Logic 0 as follows:●A Logic 1 is one low bit followed by six high bits. ● A Logic 0 is one low bit followed by one high bit, then by one low bit, and then by four high bits.Figure 2-3.Token View Figure 2-4.Logic BitsThe byte view builds on the token view by combining eight tokens into a single byte. This view allows for easy matching of information on the data bus to the command set defined in the datasheet. The byte view istransmitted with the less significant bit first.Figure 2-5.BytesThe packet view further builds on the byte view by ordering the data into logic packets based on the datasheet definition. This allow for quick and easy review of the commands without the need to reference the datasheet.Figure 2-6.Packets0x880x045CryptoAuthentication for Single-Wire and I 2C Interfaces Seamless Debugging Using SaleaeLogic Analyzer [APPLICATION NOTE]Atmel-8847B-CryptoAuth-SWI-I2C-Seamless-Debugging-Saleae-Logic-Analyzer-ApplicationNote_0820153.I 2C InterfaceThe crypto device supports an I 2C interface that is directly supported by the Saleae tool.1.To configure the Analyzer for I 2C , select the I2C option from the Analyzer drop-down list and follow the configuration guide.Figure 3-1.I2C Analyzer Option 2.Select the clock and data channels that will be used for the I2C bus. Different encoding options can also be selected. The crypto device uses the default 8-bit encoding.Figure 3-2.Clock and Data Channels Enlargement ofthe Analyzerpull-down options.CryptoAuthentication for Single-Wire and I 2C Interfaces Seamless Debugging Using SaleaeLogic Analyzer [APPLICATION NOTE]Atmel-8847B-CryptoAuth-SWI-I2C-Seamless-Debugging-Saleae-Logic-Analyzer-ApplicationNote_0820156 3.Next, the Update Channel Names dialog box will be prompted to rename the channels to reflect SCL andSDA. This is an optional step, but helps when analyzing more then one bus at a time.Figure 3-3.Update Channel Names 4.Now that the analyzer is configured, set-up the trigger settings. The Saleae has a One Shot trigger thatcan be triggered on either the falling or rising edge of the SCL channel. The bus is normally held high;therefore, setting a falling edge trigger is recommended.Figure 3-4.Trigger Settings7CryptoAuthentication for Single-Wire and I 2C Interfaces Seamless Debugging Using SaleaeLogic Analyzer [APPLICATION NOTE]Atmel-8847B-CryptoAuth-SWI-I2C-Seamless-Debugging-Saleae-Logic-Analyzer-ApplicationNote_0820155.Once the analyzer has been started, execute a command in order to generate data on the bus.Figure 3-5.Execute a Command After the Analyzer has been triggered, it will collect the waveform information and display it in the viewer. The first token shown is the ATSHA204 Wake.Figure 3-6.First Token — ATSHA204 WakeThe Wake command is a special command that is required to wake-up the device. The command consists of a I 2C Start event followed by a long period of Logic 0 on the SDA line, then followed a Stop event.Figure 3-7.Wake CommandCryptoAuthentication for Single-Wire and I 2C Interfaces Seamless Debugging Using SaleaeLogic Analyzer [APPLICATION NOTE]Atmel-8847B-CryptoAuth-SWI-I2C-Seamless-Debugging-Saleae-Logic-Analyzer-ApplicationNote_0820158After a Wake command, an optional Read can be performed to read the status of the crypto device as shown in the waveform below. After the Read command is issued, the device will send four bytes of data (1-count, 1-data, and 2-CRC).Figure 3-8.Read WaveformThe Saleae tool supports a variety of display options for the I 2C interface including Binary, Hex, and ASCII to help quickly and easily evaluate the data. It can be selected by clicking the Configuration button next to the analyzer of interest on the right.Figure 3-9.Display Options4.Revision HistoryX X X X X XAtmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311F: (+1)(408) 436.4200| © 2015 Atmel Corporation. / Rev.: Atmel-8847B-CryptoAuth-SWI-I2C-Seamless-Debugging-Saleae-Logic-Analyzer-ApplicationNote_082015.Atmel ®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities ®, CryptoAuthentication ™, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended,authorized, or warranted for use as components in applications intended to support or sustain life.SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (“Safety-Critical Applications”) without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems.Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.。

aix常用命令及问题解决

AIX中测试端口的方法下面以80端口为例,介绍测试某一个端口是否工作的方法:1. 编辑/etc/services文件,找到如下两行http 80/tcp # World Wide Web HTTPhttp 80/udp # World Wide Web HTTP用#将这两行注释掉,并添加新的两行,即如下:#http 80/tcp # World Wide Web HTTP#http 80/udp # World Wide Web HTTPtelnet2 80/tcptelnet2 80/udp2. 编辑/etc/inetd.conf文件,找到如下一行telnet stream tcp6 nowait root /usr/sbin/telnetd telnetd -a在其下添加一行telnet2 stream tcp6 nowait root /usr/sbin/telnetd telnetd -a3. # refresh -s inetd4. # lssrc -ls inetd在输出中确认有一行telnet2 /usr/sbin/telnetd telnetd -a active5. # netstat -an该命令的输出中能看到80端口在侦听,即tcp 0 0 *.80 *.* LISTEN6. 尝试从别的AIX机器上用如下命令登陆这个服务器,如果能正常登陆,说明80端口工作正常。

# telnet <ip_address> 807. # netstat -an | grep 80可以看到通过80端口建立了连接,类似如下输出:tcp4 0 0 9.181.50.90.80 9.181.50.107.3750 ESTABLISHED8. 测试完成。

请注意,测试完成后,请将/etc/services和/etc/inetd.conf文件修改回之前的状态,并刷新inetd服务:# refresh -s inetd拨号访问RS/6000的快速配置方法AIX/RS6000 支持多种拨号访问的方法.如PPP/SLIP等,但其配置较为复杂.现介绍一种使用WIN95的超级终端Hyper Terminal访问RS/6000的方法RS/6000 端:1. 定义tty, 并设置enable login , flow control=rts2. 编辑/etc/uucp/Devices, 加入一行:Direct tty# - 9600 direct3. 连接Modem到tty# port4. #pdisable tty#5. #cu -ml tty#6. at<---/7. ats0=18. ~.<----/9. penable tty#WIN95/98 端:拨号方问RS/6000关于/etc/security/limits的中文解释前一阵子,跟公司的数据库工程师为新机器P560Q和P55A安装系统和数据库,AIX为5304,oracle9207,在oracle建库是总是在jvm处失败,并报了一堆错,经查与/etc/security/limits限制有关,下面是这个文件的解释:time(seconds) unlimited此用户的一个进程能占用的CPU处理时间file(blocks) unlimited此用户的进程可以生成和扩展的最大文件大小data(kbytes) 131072此用户的进程可分配使用的最大数据段大小(数据段可以有多个)stack(kbytes) 32768此用户的进程可使用的最大堆栈段大小memory(kbytes) 32768一个用户进程可以使用的最大物理内存数量(系统并不强制限制)coredump(blocks) 2097151可生成的最大coredump文件大小nofiles(descriptors) 2000一个用户进程可同时打开的文件描述符数量(基本等同于可打开文件数量)将这几个值都改成了-1,安装成功!Oracle的网络参数的设置/usr/sbin/no –p -o udp_sendspace=65536/usr/sbin/no –p -o udp_recvspace=655360/usr/sbin/no –p -o tcp_sendspace=65536/usr/sbin/no –p -o tcp_recvspace=65536word格式-可编辑-感谢下载支持/usr/sbin/no –p -o rfc1323=1卷组问题问题:由于操作失误(chdev -l hdiskx -a pv=yes) 使得hdiskx 的PVID发生改变,硬盘上的内容尽管没被破坏,但由于与VGDA区的描述不一致,造成卷组无法访问, 该怎么办?可用recreatevg命令来重新创建一内容相同的卷组, 以达到修复的目的。

中兴交换机配置

一、系统的启动过程如下。

1、上电后,首先进行硬件启动,当硬件检测无误后,管理终端上出现下列信息:Welcome to use ZTE eCarrier!!Copyright(c) 2004-2006, ZTE Co。

, Ltd.System Booting..。

.。

CPU: S3C45010 ARM7TDMIBSP version: 1.2/0Creation date: Feb 11 2004, 09:37:01Press any key to stop auto-boot。

..72、出现上述信息后,等待大约7 秒,用户可以在这段时间内按任意键进入boot 状态,修改启动参数.当系统在规定时间未检测到用户输入时,系统便开始自动加载版本,并提示下列信息:auto—booting。

..boot device : secEndunit number : 0processor number : 0host name : tigerfile name : vxWorksinet on ethernet (e) : 10.40.92。

106host inet (h) : 10。

40.92.105flags (f) : 0x80Attaching to TFFS.。

done。

Loading version:/kernel.。

.1459932 + 75292 + 6358852Starting at 0x1656e0...Attaching interface lo0。

.。

done(省略)Welcome !ZTE Corporation。

All rights reserved.login:adminpassword:*********3、系统启动成功后,出现提示符login:,要求输入登录用户名和密码,缺省用户名是admin,密码是zhongxing。

二、配置开始工作1.打开超级终端,输入连接的名称,如ZXR10,并选择一个图标。

爱立信4G常见告警

是

License Key File Fault

安装的许可秘钥文件不可用

是

License Mismatch

证书不匹配

是

LicenseKeyMissing

容量功能许可证密钥丢失

是

LicenseKeyMissing

附加功能许可证密钥丢失

是

LinkFailure

链路故障 (Ri端口)

是

LinkFailure

是

ResourceConfigurationFailure

资源配置错误(电调)

是

ResourceConfigurationFailure

资源配置错误(小区)

是

ResourceConfigurationFailure

资源配置错误(扇区)

是

RetFailure

电调故障

是

RetFailure

电调故障

是

SecurityLevelFault

中文解释

是否派 单

无法自动配置板卡

是

自动创建CV失败

否

DU板件过热

是

由于同步问题时钟校准即将失效

是

CV损坏

否

电流过高

是

SUP失去连接

是

EC BUS失去连接

是

辅基站失去连接

是

风扇单元失去连接

是

PDU单元失去连接

是

C磁盘空间已满

否

D磁盘空间已满

否

重复IP地址冲突

是

当激活紧急状态时,会产生这个alarm 否

电池电压过低,主路掉电

BatteryVoltageTooLowPrioLoadDisconnected CalibrationFailure

AX88772B_Datasheet_亚信

FeaturesSingle chip USB 2.0 to 10/100M Fast Ethernet controllerSingle chip USB 2.0 to RMII, support HomePNAand HomePlug PHYSingle chip USB 2.0 to Reverse-RMII,supportsglueless MAC-to-MAC connectionsUSB Device InterfaceIntegrates on-chip USB 2.0 transceiver andSIE compliant to USB Spec 1.1 and 2.0Supports USB Full and High Speed modeswith Bus-Power or Self-Power capabilitySupports 4 or 6 programmable endpoints onUSB interfaceSupports AutoDetach power saving. Detachfrom USB host when Ethernet cable isunpluggedHigh performance packet transfer rate overUSB bus using proprietary burst transfermechanism (US Patent Approval)Fast Ethernet ControllerIntegrates 10/100Mbps Fast EthernetMAC/PHYIEEE 802.3 10BASE-T/100BASE-TXcompatibleIEEE 802.3 100BASE-FX compatibleSupports twisted pair crossover detection andauto-correction (HP Auto-MDIX)Embedded SRAM for RX/TX packetbufferingSupports IPv4/ IPv6 packet ChecksumOffload Engine(COE) to reduce CPU loading,including IPv4 IP/TCP/UDP/ICMP/IGMP &IPv6 TCP/UDP/ICMPv6 checksum check &generationSupports full duplex operation with IEEE802.3x flow control and half duplex operationwith back-pressure flow controlSupports 2 VLAN ID filtering, receivedVLAN Tag (4 bytes) can be stripped off orpreservedPHY loop-back diagnostic capabilitySupport Wake-on-LAN FunctionSupports Suspend Mode and Remote Wakeupvia Link-change, Magic packet, MS wakeupframe and external wakeup pinSupports Protocol Offload (ARP & NS) forWindows 7 Networking Power ManagementOptional PHY power down during SuspendModeVersatile External Media InterfaceOptional RMII interface in MAC mode allowsAX88772B to work with HomePNA andHomePlug PHYOptional Reverse-RMII interface in PHYmode allows AX88772B to support gluelessMAC-to-MAC connectionsAdvanced Power Management FeaturesSupports dynamic power management toreduce power dissipation during idle or lighttrafficSupports very low power Wake-on-LAN(WOL) mode when the system enters suspendmode and waits for network events to wake itup.Supports 256/512 bytes (93c56/93c66) of serialEEPROM (for storing USB Descriptors)Supports embedded Device Descriptors ROM and512 bytes ID-SRAM (online programmablememory for USB Device Descriptors, etc) tosave external EEPROMSupports automatic loading of Ethernet ID, USBDescriptors and Adapter Configuration fromEEPROM after power-on initializationIntegrates on-chip voltage regulator and onlyrequires a single 3.3V power supplySingle 25MHz clock input from either crystal oroscillator sourceIntegrates on-chip power-on reset circuitSmall form factor with 64-pin LQFP RoHScompliant packageOperating commercial temperature range 0°C to70°C or industriure range -40 to +85°CDocument No: AX88772B/V1.04/08/10/11Target ApplicationsPC/InternetConsumer ElectronicsFigure 1: Target ApplicationsPocketable ComputerUSB DongleDocking StationCard Reader USB KVMESwitchInternet SecurityUSB Key Port Replicatorfor Mobile ComputerUWB/802.11n/WiMAXUSB DongleMedia GatewayUMPC Portable Media Player ePianoIPTVIP STB TiVo Box Game ConsoleDVD-Recorder/DVRTypical System Block Diagramsz Hosted by USB to operate with internal Ethernet PHY onlyFigure 2: USB 2.0 to LAN Adaptor (MAC mode)zHosted by USB to operate with either internal Ethernet PHY or RMII (in MAC mode)Figure 3: USB 2.0 to Fast Ethernet and external PHYceiver Combo (MAC mode)Ethernet PHYORAX88772BEthernet PHYORzHosted by USB to operate with either internal Ethernet PHY (in MAC mode) or Reverse-RMII (in PHY mode)Figure 4: Bridging Embedded MCU to USB 2.0 Host Interface (PHY mode)Figure 5: USB 2.0 to HomePlug Adaptor (PHY mode)Ethernet PHYOREthernet PHYORCopyright © 2010-2011 ASIX Electronics Corporation. All rights reserved.DISCLAIMERNo part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of ASIX. ASIX may make changes to the product specifications and descriptions in this document at any time, without notice.ASIX provides this document “as is” without warranty of any kind, either expressed or implied, including without limitation warranties of merchantability, fitness for a particular purpose, and non-infringement.Designers must not rely on the absence or characteristics of any features or registers marked “reserved”, “undefined” or “NC”. ASIX reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Always contact ASIX to get the latest document before starting a design of ASIX products.TRADEMARKSASIX, the ASIX logo are registered trademarks of ASIX Electronics Corporation. All other trademarks are the property of their respective owners.Table of Contents1 INTRODUCTION (10)1.1 G ENERAL D ESCRIPTION (10)1.2 B LOCK D IAGRAM (10)1.3 P INOUT D IAGRAM (11)2 SIGNAL DESCRIPTION (12)2.1 AX88772B64-PIN P INOUT D ESCRIPTION (12)2.2 H ARDWARE S ETTING F OR O PERATION M ODE AND M ULTI-F UNCTION P INS (15)3 FUNCTION DESCRIPTION (17)3.1 USB C ORE AND I NTERFACE (17)3.2 10/100M E THERNET PHY (17)3.3 MAC C ORE (17)3.4 C HECKSUM O FFLOAD E NGINE (COE) (18)3.5 O PERATION M ODE (18)3.6 S TATION M ANAGEMENT (STA) (21)3.7 M EMORY A RBITER (23)3.8 USB TO E THERNET B RIDGE (23)3.8.1 Ethernet/USB Frame Format Bridge (23)3.9 S ERIAL EEPROM L OADER (23)3.10 G ENERAL P URPOSE I/O (23)3.11 C LOCK G ENERATION (24)3.12 R ESET G ENERATION (25)3.13 V OLTAGE R EGULATOR (25)4 SERIAL EEPROM MEMORY MAP (26)4.1 D ETAILED D ESCRIPTION (27)4.2 I NTERNAL ROM D EFAULT S ETTINGS (30)4.2.1 Internal ROM Description (31)4.2.2 External EEPROM Description (33)5 USB CONFIGURATION STRUCTURE (34)5.1 USB C ONFIGURATION (34)5.2 USB I NTERFACE (34)5.3 USB E NDPOINTS (34)6 USB COMMANDS (35)6.1 USB S TANDARD C OMMANDS (35)6.2 USB V ENDOR C OMMANDS (36)6.2.1 Detailed Register Description (38)6.3 I NTERRUPT E NDPOINT (63)6.4 B ULK-O UT T IMER AND M ONITOR (BOTM) (64)7 EMBEDDED ETHERNET PHY REGISTER DESCRIPTION (65)7.1 PHY R EGISTER D ETAILED D ESCRIPTION (65)7.1.1 Basic Mode Control Register (BMCR) (66)7.1.2 Basic Mode Status Register (BMSR) (67)7.1.3 PHY Identifier Register 1 (PHYIDR1) (68)7.1.4 PHY Identifier Register 2 (PHYIDR2) (68)7.1.5 Auto Negotiation Advertisement Register (ANAR) (68)7.1.6 Auto Negotiation Link Partner Ability Register (ANLPAR) (69)7.1.7 Auto Negotiation Expansion Register (ANER) (69)8 STATION MANAGEMENT REGISTERS IN PHY MODE (70)8.1 PHY M ODE D ETAILED R EGISTER D ESCRIPTION (71)8.1.1 PHY Mode Basic Mode Control Register (PM_BMCR) (71)8.1.2 PHY Mode Basic Mode Status Register (PM_BMSR) (72)8.1.3 PHY Mode PHY Identifier Register 1 (PM_PHYIDR1) (73)8.1.4 PHY Mode PHY Identifier Register 2 (PM_PHYIDR2) (73)8.1.5 PHY Mode Auto Negotiation Advertisement Register (PM_ANAR) (73)8.1.6 PHY Mode Auto Negotiation Link Partner Ability Register (PM_ANLPAR) (74)8.1.7 PHY Mode Auto Negotiation Expansion Register (PM_ANER) (74)8.1.8 PHY Mode Control Register (PM_Control) (75)9 ELECTRICAL SPECIFICATIONS (76)9.1 DC C HARACTERISTICS (76)9.1.1 Absolute Maximum Ratings (76)9.1.2 Recommended Operating Condition (76)9.1.3 Leakage Current and Capacitance (77)9.1.4 DC Characteristics of 3.3V I/O Pins (77)9.1.5 DC Characteristics of 3.3V with 5V Tolerance I/O Pins (78)9.1.6 DC Characteristics of Voltage Regulator (78)9.2 T HERMAL C HARACTERISTICS (79)9.3 P OWER C ONSUMPTION (79)9.4 P OWER-UP S EQUENCE (80)9.5 AC T IMING C HARACTERISTICS (81)9.5.1. Clock Timing (81)9.5.2. Reset Timing (81)9.5.3. Serial EEPROM Timing (82)9.5.4. Station Management Timing (83)9.5.5. RMII / Reverse-RMII Timing (84)9.5.6. 10/100M Ethernet PHY Interface Timing (85)9.5.7. USB Transceiver Interface Timing (86)10 PACKAGE INFORMATION (88)10.1 AX88772B64-PIN LQFP PACKAGE (88)11 ORDERING INFORMATION (89)12 REVISION HISTORY (90)APPENDIX A. DEFAULT WAKE-ON-LAN (WOL) READY MODE (91)APPENDIX B. ETHERNET PHY POWER AND RESET CONTROL (94)APPENDIX C. EXTERNAL EEPROM / INTERNAL ROM / INTERNAL ID-SRAM OF VENDER DESCRIPTIONS SELECTION (96)List of FiguresF IGURE 1 :T ARGET A PPLICATIONS (2)F IGURE 2 :USB2.0 TO LAN A DAPTOR (MAC MODE) (3)F IGURE 3 :USB2.0 TO F AST E THERNET AND EXTERNAL PHY CEIVER C OMBO (MAC MODE) (3)F IGURE 4 :B RIDGING E MBEDDED MCU TO USB2.0H OST I NTERFACE (PHY MODE) (4)F IGURE 5 :USB2.0 TO H OME P LUG A DAPTOR (PHY MODE) (4)F IGURE 6 :AX88772B B LOCK D IAGRAM (10)F IGURE 7 :AX88772B P INOUT D IAGRAM (11)F IGURE 8 :I NTERNAL D ATA PATH D IAGRAM OF 10/100M E THERNET PHY AND RMII/R EVERSE-RMII I NTERFACES .. 17 F IGURE 9 :AX88772B RMII TO E XTERNAL PHY CHIP WITH 50MH Z OSC (19)F IGURE 10 :AX88772B RMII I NTERFACE TO E XTERNAL PHY CHIP (19)F IGURE 11 :AX88772B R EVERSE-RMII TO E XTERNAL MAC D EVICE WITH 50MH Z OSC (20)F IGURE 12 :AX88772B R EVERSE-RMII I NTERFACE TO E XTERNAL MAC D EVICE (20)F IGURE 13 :I NTERNAL C ONTROL MUX OF S TATION M ANAGEMENT I NTERFACE IN MAC MODE (21)F IGURE 14 :I NTERNAL C ONTROL MUX OF S TATION M ANAGEMENT I NTERFACE IN PHY MODE (22)F IGURE 15 :O NE EXTERNAL 1M OHM RESISTOR ON 25MH Z CRYSTAL OSCILLATOR IS NECESSARY (25)F IGURE 16 :W ATER LEVEL SETTING FOR FLOW CONTROL (29)F IGURE 17 :M ULTICAST F ILTER E XAMPLE (43)F IGURE 18 :M ULTICAST F ILTER A RRAY H ASHING A LGORITHM (44)F IGURE 19 :M ULTICAST F ILTER A RRAY B IT M APPING (44)F IGURE 20 :802.1Q VLAN P ACKET F ORMAT (54)F IGURE 21 :S TATION M ANAGEMENT F RAME FOR PHY M ODE (70)F IGURE 22 :E THERNET PHY O SCILLATOR/PLL B LOCK D IAGRAM (94)F IGURE 23 :E THERNET PHY P OWER-UP &R ESET T IMING D IAGRAM (95)F IGURE 24 :E XTERNAL EEPROM/I NTERNAL ROM/I NTERNAL ID-SRAM OF V ENDER D ESCRIPTIONS SELECTION 97List of TablesT ABLE 1 :AX88772B P INOUT D ESCRIPTION (14)T ABLE 2 :MFA_3~MFA_0 PIN CONFIGURATION (15)T ABLE 3 :AX88772B PHY_ID D EFINITION S OURCE (18)T ABLE 4 :T HE EXTERNAL 25M HZ C RYSTAL U NITS SPECIFICATIONS (24)T ABLE 5 :S ERIAL EEPROM M EMORY M AP (26)T ABLE 6 :I NTERNAL ROM M EMORY M AP (30)T ABLE 7 :I NTERNAL ROM D ESCRIPTION (31)T ABLE 8 :USB S TANDARD C OMMAND R EGISTER M AP (35)T ABLE 9 :USB V ENDOR C OMMAND R EGISTER M AP (37)T ABLE 10 :W AKE-UP F RAME A RRAY R EGISTER (WUD3~0)S TRUCTURE D EFINITION (50)T ABLE 11 :VID1,VID2 SETTING TO FILTER RECEIVED PACKET (53)T ABLE 12 :E MBEDDED E THERNET PHY R EGISTER M AP (65)T ABLE 13 :S TATION M ANAGEMENT R EGISTER M AP IN PHY M ODE (70)T ABLE 14 :P OWER CONSUMPTION (79)T ABLE 15 :R EMOTE W AKEUP T RUTH T ABLE (92)1 Introduction1.1 General DescriptionThe AX88772B Low-power USB 2.0 to 10/100M Fast Ethernet controller is a high performance and highly integrated ASIC which enables low cost, small form factor, and simple plug-and-play Fast Ethernet network connection capability for desktops, notebook PC’s, Ultra-Mobile PC’s, docking stations, game consoles, digital-home appliances, and any embedded system using a standard USB port.The AX88772B features a USB interface to communicate with a USB Host Controller and is compliant with USB specification V1.1 and V2.0. The AX88772B implements a 10/100Mbps Ethernet LAN function based on IEEE802.3, and IEEE802.3u standards with embedded SRAM for packet buffering. The AX88772B integrates an on-chip 10/100Mbps Ethernet PHY to simplify system design.The AX88772B provides an optional Multi-Function-Bus portion A and B (MFA and MFB) for external PHY or external MAC for different application purposes. The MFA/MFB can be a reduce-media-independent interface (RMII) for implementing HomePlug, HomePNA, etc. functions. The MFA/MFB can also be a Reverse Reduced-MII (Reverse-RMII) for glueless MAC-to-MAC connections to any MCU with Ethernet MAC RMII interface. In addition, the MFA/MFB can be configured as general purpose I/O. 1.2 Block DiagramFigure 6: AX88772B Block DiagramDP/DMSEEPROM Loader I/FGeneral PurposeI/O 3.3 to 1.8V RegulatorPLL Clock GeneratorsPower-On-Reset & Reset Gen.RESET_NXTL25P, XTL25N1.3 Pinout Diagramz AX88772B in 64-pin LQFP packageG N DT E S T 0T E S T 1R E S E T _NV C C 3I OT C L K _E NT C L K _0T C L K _1E E D I OE E C SE E C K G N DV C C KM F B 0M F B 1M F B 2V C C 18X T L 25X T L 25G N D 18R S E T _B V C C 3A S G N D 18R X I R X I V C C 18T X O T X O G N D 18G N V C C 3I OFigure 7: AX88772B Pinout Diagram2 Signal DescriptionThe following abbreviations apply to the following pin description table.I18 Input, 1.8V AI Analog Input I3 Input, 3.3V AO Analog Output I5 Input, 3.3V with 5V tolerant AB Analog Bi-directional I/O O3 Output, 3.3V PU Internal Pull Up (75K) B5 Bi-directional I/O, 3.3V with 5V tolerant PD Internal Pull Down (75K) P Power Pin S T Schmitt Trigger Tri-stateable Note: Every output or bi-directional I/O pin is 8mA driving strength.2.1 AX88772B 64-pin Pinout DescriptionPin NameTypePin NoPin DescriptionUSB InterfaceDP AB 56 USB 2.0 data positive pin. DM AB 57 USB 2.0 data negative pin. V_BUS I5/PD/S 50 VBUS pin input. Please connect to USB bus power. RREF AI 58 For USB PHY’s internal biasing. Please connect to analog GND through aresistor (12.1Kohm ±1%).Serial EEPROM InterfaceEECK B5/PD/T 38 EEPROM Clock. EECK is an output clock to EEPROM to provide timingreference for the transfer of EECS, and EEDIO signals. EECK only drivehigh / low when access EEPROM otherwise keep at tri-state and internal pull-down.EECS B5/PD/T 39 EEPROM Chip Select. EECS is asserted high synchronously with respect torising edge of EECK as chip select signal. EECS only drive high / low whenaccess EEPROM otherwise keep at tri-state and internal pull-down.EEDIO B5/PU/T 40 EEPROM Data In. EEDIO is the serial output data to EEPROM’s data inputpin and is synchronous with respect to the rising edge of EECK. EEDIOonly drive high / low when access EEPROM otherwise keep at tri-state and internal pull-up.Ethernet PHY InterfaceXTL25P I18 2 25Mhz ± 0.005% crystal or oscillator clock input. This clock is needed forthe embedded 10/100M Ethernet PHY to operate.XTL25N O18 3 25Mhz crystal or oscillator clock output. RXIP AB 9 Receive data input positive pin for both 10BASE-T and 100BASE-TX. RXIN AB 10 Receive data input negative pin for both 10BASE-T and 100BASE-TX. TXOP AB 12 Transmit data output positive pin for both 10BASE-T and 100 BASE-TX TXON AB 13 Transmit data output negative pin for both 10BASE-T and 100 BASE-TX RSET_BG AO 5 For Ethernet PHY’s internal biasing. Please connect to GND through a12.1Kohm ±1% resistor.Misc. PinsRESET_N I5/PU/S 45 Chip reset input. Active low. This is the external reset source used to resetthis chip. This input feeds to the internal power-on reset circuitry, which provides the main reset source of this chip. After completing reset, EEPROM data will be loaded automatically.EXTWAKEUP_N I5/PU/S 23 Remote-wakeup trigger from external pin. EXTWAKEUP_N should beasserted low for more than 2 cycles of 25MHz clock to be effective.GPIO_2 B5/PD 25 General Purpose Input/ Output Pin 2. GPIO_1 B5/PD 26 General Purpose Input/ Output Pin 1. This pin is default as input pin afterpower-on reset. This pin is also for Default WOL Ready Mode setting;please refer to section 2.2 Settings.GPIO_0/PME B5/PD 27 General Purpose Input/ Output Pin 0 or PME (Power Management Event).This pin is default as input pin after power-on reset. GPIO_0 also can bedefined as PME output to indicate wake up event detected. Please refer tosection 2.2 Settings.MFB7 B5/PUI5I5 28 This is a multi-function pin. Please refer to section 2.2 Settings.MFB7:RMII : RXD0Reverse_RMII : TXD0MFB6 B5/PUI5I5 29 This is a multi-function pin. Please refer to section 2.2 Settings.MFB6:RMII : RXD1Reverse_RMII : TXD1MFB5/ REF50 B5/PUB530 This is a multi-function pin. Please refer to section 2.2 Settings.MFB5:When RMII enable, The REF50 in/out direction is determined by EEPROMFlag [1] setting. Please refer to section 2.2 Settings.MFB4 B5/PUO3O3 31 This is a multi-function pin. Please refer to section 2.2 Settings.RMII : TXD0Reverse_RMII : RXD0MFB3 B5/PUO3O3 32 This is a multi-function pin. Please refer to section 2.2 Settings.RMII : TXD1Reverse_RMII : RXD1MFB2 B5/PUO3O3 33 This is a multi-function pin. Please refer to section 2.2 Settings.RMII : TXENReverse_RMII : CRSDVMFB1 B5/PUI5I5 34 This is a multi-function pin. Please refer to section 2.2 Settings.RMII : CRSDVReverse_RMII : TXENMFB0 B5/PU35 This is a GPIO pin. Please refer to section 2.2 Settings.MFA3/ PHY_NO3I5/PU21 It is a multi-function pin. The default is USB Speed indicator. When USBbus is in Full speed, this pin will tri-state continuously. When USB bus is inHigh speed, this pin drives low continuously. This pin tri-state and drive lowin turn (blinking) to indicate TX data transfer going on whenever the hostcontroller sends bulk out data transfer.MFB1~7 bus is determined by setting of this input pin when MFA2 sets 0:0: Reverse_RMII (PHY mode).1: RMII (MAC mode).Please refer to PIN configuration of MFA and MFB in section 2.2 Settings.MFA2/ RMII_NO3I5/PU19 It is a multi-function pin. The default is Link status LED indicator.This pin drives low continuously when the Ethernet link is up and drives lowand high in turn (blinking) when Ethernet PHY is in receiving ortransmitting state.MFB1~7 function is determined by setting of this input pin:0: Reverse_RMII/RMII .1: MFB bus as GPIO function.Please refer to PIN configuration of MFA and MFB in section 2.2 Settings.MFA1/ MDIOO3B5/PU18 It is a multi-function pin. The default is Ethernet speed LED indicator.This pin drives low when the Ethernet PHY is in 100BASE-TX mode anddrives high when in 10BASE-T mode.This pin can perform as MDIO when enabling Reverse_RMII/RMII.MFA0/MDCO3O3I5/PU 17 It is a multi-function pin. The default is Full Duplex and collision detectedLED indicator.This pin drives low when the Ethernet PHY is in full-duplex mode and drives high when in half duplex mode. When in half duplex mode and the Ethernet PHY detects collision, it will be driven low (or blinking).This pin can perform as MDC when enabling Reverse_RMII/RMII:RMII : Output.Reverse_RMII : Input.SD I 7 Fiber signal detectedTwisted pair operation: Please connect to GND directly or through aresistor.Fiber operation: Please connect to the fiber transceiver signal detect outputpin.TEST0 I5/S 47 Test pin. For normal operation, user should connect to ground.TEST1 I5/S 46 Test pin. For normal operation, user should connect to ground.X1 I3 62 Test pin. For normal operation, user should connect to ground.X2 O3 61 Test pin. No connectionTCLK_EN I5/PD/S 43 Test pin. For normal operation, user should keep this pin NC.TCLK_0 I5/PD 42 Test pin. For normal operation, user should keep this pin NC.TCLK_1 I5/PD 41 Test pin. For normal operation, user should keep this pin NC.On-chip Regulator PinsVCC3R3 P 52 3.3V Power supply to on-chip 3.3V to 1.8V voltage regulator.GND3R3 P 53 Ground pin of on-chip 3.3V to 1.8V voltage regulator.V18F P 51 1.8V voltage output of on-chip 3.3V to 1.8V voltage regulator.Power and Ground PinsVCCK P 20, 24, 36, 49Digital Core Power. 1.8V.VCC3IO P 16, 44 Digital I/O Power. 3.3V.GND P 15, 22, 37, 48Digital Ground.VCC33A_H P 60 Analog Power for USB transceiver. 3.3V.GND33A_H P 55 Analog Ground for USB transceiver.VCC33A_PLL P 59 Analog Power for USB PLL. 3.3V.GND33A_PLL P 54 Analog Ground for USB PLL.VCC3A3 P 6 Analog Power for Ethernet PHY bandgap. 3.3V.VCC18A P 1, 11 Analog Power for Ethernet PHY and 25Mhz crystal oscillator.1.8V.GND18A P 4, 8, 14 Analog Ground for Ethernet PHY and 25Mhz crystal oscillator. VCC18A_PLL P 64 Analog Power for USB PLL. 1.8V.GND18A_PLL P 63 Analog Ground for USB PLL.Table 1: AX88772B Pinout Description2.2 Hardware Setting For Operation Mode and Multi-Function PinsThe following hardware settings define the desired function or interface modes of operation for some multi-function pins. The logic level shown on setting pin below is loaded from the chip I/O pins during power on reset based on the setting of the pin’s pulled-up (as logic ‘1’) or pulled-down (as logic ‘0’) resister on the schematic.z Chip Operation Mode setting :Pin# 19, Pin #21 Operation Modes Remarks 1x (default) MAC mode Internal PHY The Chip Operation Mode is determined by Pin# 19(MFA2/RMII_N) and Pin #21 (MFA3/PHY_N) value of AX88772B, which is called hardware setting. 01 MAC mode RMII00 PHY mode Reverse-RMIIz EECK pin: USB force to Full Speed mode :EECK Description 0 Normal operation (default). 1 USB force to Full Speed mode. External pull-up resistor must be 4.7Kohm.z GPIO_1 pin: Determines whether this chip will go to Default WOL Ready Mode after power on reset. The WOLstands for Wake-On-LAN.GPIO_1 Description0 Normal operation mode (default, see Note 1). 1 Enable Default WOL Ready Mode. Notice that the external pulled-up resistor must be 4.7Kohm.For more details, please refer to APPENDIX A. Default Wake-On-LAN (WOL) Ready ModeNote 1: This is the default with internal pulled-down resistor and doesn’t need an external one.z EEPROM Flag [12]: Defines the multi-function pin GPIO_0 / PMEGPIO_0 is a general purpose I/O normally controlled by vendor commands. Users can change this pin to operate as a PME (Power Management Event) for remote wake up purpose. Please refer to 4.1.2 Flag of bit 12 (PME_PIN).z MFA_3 ~ MFA_0 pins: There are 4 multi-function pins for LED display purpose and as GPIO control by vendorcommand.Table 2: MFA_3 ~ MFA_0 pin configurationPIN Name Default definitionVendor Command LED_MUX Vendor CommandVMFAIORMII_N enableMFA3 LED_USB indicater Sel_LED3 MFAIO_3- MFA2 LED_Ethernet_LINK_Active Sel_LED2MFAIO_2-MFA1 LED_Ethernet_Speed Sel_LED1 MFAIO_1 MDIO MFA0 LED_Ethernet_Duplex_Collision Sel_LED0MFAIO_0MDCz PIN configuration of MFA and MFBPin# 19 MFA2/RMII_NPin #21MFA3/PHY_NDescription1: MFB7~MFB0 0: RMII 1: MAC Mode0: PHY ModePINNameFunction Pin Type1 X MFB0 MFBIO0 Bidirection, controlled by MFBIOEN01 X MFB1 MFBIO1 Bidirection, controlled by MFBIOEN11 X MFB2 MFBIO2 Bidirection, controlled by MFBIOEN21 X MFB3 MFBIO3 Bidirection, controlled by MFBIOEN31 X MFB4 MFBIO4 Bidirection, controlled by MFBIOEN41 X MFB5 MFBIO5 Bidirection, controlled by MFBIOEN51 X MFB6 MFBIO6 Bidirection, controlled by MFBIOEN61 X MFB7 MFBIO7 Bidirection, controlled by MFBIOEN71 X MFA0 Refer to MFAConfiguration1 X MFA1 Refer to MFAConfiguration1 X MFA2 Refer to MFAConfiguration1 X MFA3 Refer to MFAConfiguration0 1 MFB0 MFBIO0 Bidirection, controlled by MFBIOEN00 1 MFB1 CRSDV Input0 1 MFB2 TXEN Output0 1 MFB3 TXD1 Output0 1 MFB4 TXD0 Output0 1 MFB5 REF50 Input/Output control by EEPROM flag[1] 0 1 MFB6 RXD1 Input0 1 MFB7 RXD0 Input0 1 MFA0 MDC Output0 1 MFA1 MDIO I/O0 0 MFB0 MFBIO0 Bidirection, controlled by MFBIOEN00 0MFB1TXEN Input 0 0MFB2CRSDV Output 0 0MFB3RXD1 Output 0 0MFB4RXD0 Output 0 0 MFB5 REF50 Input/Output control by EEPROM flag[1] 0 0MFB6TXD1 Input 0 0MFB7TXD0 Input 0 0MFA0MDC Input 0 0MFA1MDIO I/O3 Function Description3.1 USB Core and InterfaceThe USB core and interface contains a USB 2.0 transceiver, serial interface engine (SIE), USB bus protocol handshaking block, USB standard command, vendor command registers, logic for supporting bulk transfer, and an interrupt transfer, etc. The USB interface is used to communicate with a USB host controller and is compliant with USB specification V1.1 and V2.0.3.2 10/100M Ethernet PHYThe 10/100M Fast Ethernet PHY is compliant with IEEE 802.3 and IEEE 802.3u standards. It contains an on-chip crystal oscillator, PLL-based clock multiplier, and a digital phase-locked loop for data/timing recovery. It providesover-sampling mixed-signal transmit drivers compliant with 10/100BASE-TX transmit wave shaping / slew rate control requirements. It has a robust mixed-signal loop adaptive equalizer for receiving signal recovery. It contains a baseline wander corrective block to compensate data dependent offset due to AC coupling transformers. It supports auto-negotiation and auto-MDIX functions.3.3 MAC CoreThe MAC core supports 802.3 and 802.3u MAC sub-layer functions, such as basic MAC frame receive and transmit, CRC checking and generation, filtering, forwarding, flow-control in full-duplex mode, and collision-detection and handling in half-duplex mode, etc. It provides a reduce-media-independent interface (RMII) for implementing Fast Ethernet and HomePNA functions.The MAC core interfaces to external RMII/Reverse-RMII interfaces and the embedded 10/100M Ethernet PHY. The selection among the interfaces is done via setting Pin# 19 (MFA2/RMII_N) and Pin #21 (MFA3/PHY_N) of AX88772B package pinout during power on reset (see 2.2) and using the USB vendor command, Software Interface Selection register . Figure 8 shows the data path diagram of 10/100M Ethernet PHY and RMII/Reverse-RMII interfaces to MAC core.Figure 8: Internal Data path Diagram of 10/100M Ethernet PHY and RMII/Reverse-RMII InterfacesREFCLK, RXD [1:0], CRSDV, TXD [1:0], TXEN RXIP/RXIN TXOP/TXON3.4 Checksum Offload Engine (COE)The Checksum Offload Engine (COE) supports IPv4, IPv6, layer 4 (TCP, UDP, ICMP, ICMPv6 and IGMP) header processing functions and real time checksum calculation in hardwareThe COE supports the following features in layer 3:z IP header parsing, including IPv4 and IPv6z IPv6 routing header type 0 supportedz IPv6 in IPv4 tunnel supportedz IPv4 header checksum check and generation (There is no checksum field in IPv6 header)z Version error detecting on RX direction for IP packets with version != 4 or 6z Detecting on RX direction for IP packets with error header checksumThe COE supports the following features in layer 4:z TCP and UDP checksum check and generation for non-fragmented packetz ICMP, ICMPv6 and IGMP message checksum check and generation for non-fragmented packetz Packet filtering or checksum error indication on RX direction for TCP/UDP/ICMP/ICMPv6/IGMP packets with error checksum3.5Operation ModeFor simple USB 2.0 to Ethernet applications, user can use the AX88772B, which operates with internal Ethernet PHY. AX88772B supports following three operation modes: (Ref. 2.2 Hardware Setting For Operation Mode AndMulti-Function Pins)1.MAC mode2.PHY modeBelow provides a detailed description for the three operation modes:z In MAC mode, the AX88772B Ethernet block is configured as an Ethernet MAC. From a system application standpoint, AX88772B can be used as a USB 2.0 to LAN Adaptor (see Figure 2) or a USB 2.0 to Fast Ethernet and HomePNA Combo (see Figure 3).In MAC mode, the AX88772B internal datapath can work with internal Ethernet PHY or RMII interface bysetting Software Interface Selection register. Note that the PHY_ID for the internal Ethernet PHY and external one are defined in below Table 3. Please refer to below Figure 9, Figure 10 for RMII example.z In PHY mode, the AX88772B Ethernet block is configured as an Ethernet PHY interface. In this case, an external microcontroller with Ethernet MAC can interface with AX88772B as if it were to interface with an Ethernet PHY chip, and AX88772B can act as a USB to Reverse-RMII bridge chip for the microcontroller to provide USB 2.0 device interface for some system applications (see Figure 4).Please refer to below Figure 11, Figure 12 for Reverse-RMII example.STA PHY_ID MAC mode PHY modeEmbedded Ethernet PHYPHY_ID [4:0]10h 10hExternal Media Interface PHY_ID [4:0] {Secondary PHY_ID[4:0]}{Secondary PHY_ID [4:1], 0}Note: The value of Secondary PHY_ID [4:0] is defined in EEPROM memory map 4.1.6 Table 3: AX88772B PHY_ID Definition Source。

Freescale - MPC8308-RDB 参考板产品概述说明书

Freescale - MPC8308-RDB - Reference Board MPC8308 Product Overview:The MPC8308-RDB reference platform is ideal forhardware and software development for embeddedapplications including consumer printers, wireless accesspoints, industrial control and factory automation equipment.The MPC8308-RDB integrates : 5 x Gigabit Ethernet ports,1 x USB 2.0, x1 mini PCI Express connector and anSD/MMC card interface The MPC8308-RDB incorporates areinstalled board support package (BSP) containing a bootloader (u-boot)—a generic Power Architecture technologysystem based on the Linux kernel. The u-boot and Linuxkernel reside in the on-board flash memory and launch when the board is powered up.Kit Content:∙MPC8308-RDB board∙Cables∙Power supply∙Bill of materials∙Schematics∙Gerber files∙User guide∙Free six-month evaluation license foro CodeWarrior™ toolsKey Features:∙MPC8308 PowerQUICC II Pro processor up to 333/266 MHz (CPU/DDR2)∙ Etherneto4-port Gigabit Ethernet switch, supporting RGMII/MIIo Single Gigabit Ethernet PHY (RGMII)∙PCI Express interconnecto Mini PCI Express for WLAN∙ TwoI2Co Connected to real-time clocko May be eliminated using the MCU∙ Dual UARTo Connectors for debug connectivity∙ Local buso NAND flash/NOR flash memory∙High-Speed USB 2.0o Single USB 2.0 supporting host, device or OTG∙ Memoryo32-bit DDR2 with population option for 16-bit∙ eSDHCo Single-port SD/MMC connector∙IEEE 1588v2 support for timing synchronizationOrdering Information:Products:Part Number Manufacturer Farnell P/N Newark P/NMPC8308-RDB FreescaleSemiconductor 1799644 64R6879 Associated Products:Part Number Manufacturer Description Farnell P/N Newark P/NMPC8308CVMAFDFreescaleSemiconductorPower QUICC II PRO,333MHz MPU in 473pinMAPBGA package1799646 64R6881MPC8308CVMADDFreescaleSemiconductorPower QUICC II PRO,266MHz MPU in 473pinMAPBGA package1799645 64R6880Similar Products:Part Number Manufacturer Description SupportDeviceFarnellP/NNewarkP/NMPC8349E-MITX-GPFreescaleSemiconductorMPC8349e-MITX-GP IndustrialReferencePlatformPOWERQUICC IIPRO1692095 14M6286MPC8377E-RDBAFreescaleSemiconductorMPC837x FamilyReferenceDesign PlatformMPC837xfamily1706252 40P5264MPC8349E-MITXE.FreescaleSemiconductorMPC8349EReferencePlatformPOWERQUICC IIPRONA 14M6287MPC8349E-MITX-GP .FreescaleSemiconductorMPC8349e-MITX-GP IndustrialReferencePlatformPOWERQUICC IIPRONA 14M6286Document List:Datasheets:Part Number Description SizeMPC8308RDBUG PowerQUICC™ MPC8308_RDB User’s Guide 542KB MPC8308EC MPC8308 PowerQUICC II Pro Processor Hardware Specification 2550KBMPC8308RM MPC8308 PowerQUICC II Pro Processor Reference Manual 8775KBMPC8308PB MPC8308 Product Brief PowerQUICC™ II Pro Processor 542KB Application Notes:File Name SizeMPC8308RDB Schematics 425 KBDesign Checklist for PowerQUICC II Pro MPC8308 Processor 672 KBMPC8308-RDB Reference Platform Fact Sheet 318 KBMPC8308 PowerQUICC® III Processor Fact Sheet 261 KBPowerQUICC III MPC8555E and MPC8541E Bring-Up Guidelines AN2805582 KBProgramming the PowerQUICC III/PowerQUICC II Pro DDR SDRAM Controller AN2583AN3781 Utilizing Extra FC Credits for PCI Express Inbound Posted Memory WriteTransactions in PowerQUICC III™ Devices447 KBHardware & Software:File Name SizeCodeWarrior Development Studio for Power Architecture Professional/Linux ApplicationEdition Release Service Pack 1 for P1020 and 8308 (WIN)5355 KBCodeWarrior Development Studio for Power Architecture Professional/Linux Application 26050 KBEdition Release Service Pack 1 for P1020 and 8308MPC8308-RDB BSP 1264916 KB Others Resources:File Name Size SG1007Q22009 Network and Communications Processors, SG1007 1001 KB SG1001 ARCHIVED - 32-Bit Embedded Processors SG1001Q12006 903 KB182 KB NANDFLASHWP How to Interface the PowerQUICC II Pro and PowerQUICC III Local BusController to NAND Flash。

JBL MRX525 音频系统说明书

JBL Incorporated, 8500 Balboa Boulevard, P .O.Box 2200, Northridge, California 91329 U.S.A.J B L M R X 525 R E V HPACKAGE WIRING DIAGRAM03-12T echnical ManualJBL MRX525SPECIFICATIONSACOUSTIC & ELECTRICAL SPECIFICATIONS:•Nominal Impedance: 4 Ohms •Power Capacity:800W / 1600W / 3200W, 2 hrs.(Cont/ Prog/Peak):700W / 1400W / 2800W, 100 hrs • Frequency Range:40 Hz - 20 kHz (-10 dB)•Frequency Response:57 Hz – 20 kHz (±3 dB) •Maximum SPL:129 dB SPL continuous (135 dB SPL peak)•System Sensitivity:100 dB SPL (1 watt @ 1 meter)•Crossover Frequency:1.8 kHzSYSTEM COMPONENTS:•Cabinet:Enclosure (Not for Sale)•Grille:362524-001•Low Frequency 265H-1, 380 mm (15 in) Differential Transducer:Drive woofer •DC Resistance: 5.0 ohm ±10%•High Frequency 2408H, 37.5 mm (1.5 in) annularTransducer:polymer diaphragm, neodymium compression driver•DC Resistance:4.8 ohm +/- 0.2 ohmSYSTEM COMPONENTS:(CONT’D) • Crossover Network:364969-001AURAL SWEEP TEST SPECIFICATIONS:A.System Aural Sweep T est:7.0V Input, 50 Hz to 20 kHzB.L.F .Aural Sweep Test:7.0V Input, 10 Hz to 300 HzC.H.F .Aural Sweep Test:0.75V Input, 200 Hz to 1.5 kHz PHYSICAL SPECIFICATIONS:•Enclosure Dimensions:1240 x 535 x 460 mm D (H x W x D)(48.75 x 21.0 x 18.0 in D)•Net Weight (ea):84.0 lb (38.2 kg)WARRANTY INFORMATION:•Refer to Warranty Statement packed with each product.Warranty 59660Manual362053-001Carton362293-001Fillers (2)362294-002Pkg, Microfoam (8) 49790PPop Sticker 362896-001NETWORK SCHEMATIC - (364969-001)Driver, High Freq 2408H(361549-001X) Driver Repl D8R2408Driver,Low Freq (2)265H(362048-001X)Cone Repl C8R265 265H-1 (2)(363837-003X)Cone Repl C8R265-1Network Assembly 364969-001YEL YEL/BLKGRN GRN/BLKWH/BLK WH NOTE:INDIVIDUAL PARTS FOR THE ABOVE CROSSOVER ARE NOT AVAILABLE.A COMPLETE REPLACEMENT ASSEMBL Y SHOULD BE ORDERED.JBL MRX525804-11110-1610-32 x 1, FLT, PH,BLK OXIDE, LCSNetwork, Input364969-001Screw (6)882-41110-106 x 5/8, PAN, PH,BLK ZINC, LCSNameplate 362051-001Grille Assembly w/ Screen362524-001 Screw (26)882-51110-12Foot (4)353445-001Screw (4)884-41110-1210 x 3/4, PAN, PH,PB, BLK ZINC, LCSDriver, Low Freq (2)265H(362048-001X)Cone ReplC8R265265H-1(363837-003X)Cone ReplC8R265-1Network, Input362292-001Screw (2)882-41110-106 x 5/8, PAN, PH,BLK ZINC, LCS。

3GPP TS 36.331 V13.2.0 (2016-06)

3GPP TS 36.331 V13.2.0 (2016-06)Technical Specification3rd Generation Partnership Project;Technical Specification Group Radio Access Network;Evolved Universal Terrestrial Radio Access (E-UTRA);Radio Resource Control (RRC);Protocol specification(Release 13)The present document has been developed within the 3rd Generation Partnership Project (3GPP TM) and may be further elaborated for the purposes of 3GPP. The present document has not been subject to any approval process by the 3GPP Organizational Partners and shall not be implemented.This Specification is provided for future development work within 3GPP only. The Organizational Partners accept no liability for any use of this Specification. Specifications and reports for implementation of the 3GPP TM system should be obtained via the 3GPP Organizational Partners' Publications Offices.KeywordsUMTS, radio3GPPPostal address3GPP support office address650 Route des Lucioles - Sophia AntipolisValbonne - FRANCETel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16InternetCopyright NotificationNo part may be reproduced except as authorized by written permission.The copyright and the foregoing restriction extend to reproduction in all media.© 2016, 3GPP Organizational Partners (ARIB, ATIS, CCSA, ETSI, TSDSI, TTA, TTC).All rights reserved.UMTS™ is a Trade Mark of ETSI registered for the benefit of its members3GPP™ is a Trade Mark of ETSI registered for the benefit of its Members and of the 3GPP Organizational PartnersLTE™ is a Trade Mark of ETSI currently being registered for the benefit of its Members and of the 3GPP Organizational Partners GSM® and the GSM logo are registered and owned by the GSM AssociationBluetooth® is a Trade Mark of the Bluetooth SIG registered for the benefit of its membersContentsForeword (18)1Scope (19)2References (19)3Definitions, symbols and abbreviations (22)3.1Definitions (22)3.2Abbreviations (24)4General (27)4.1Introduction (27)4.2Architecture (28)4.2.1UE states and state transitions including inter RAT (28)4.2.2Signalling radio bearers (29)4.3Services (30)4.3.1Services provided to upper layers (30)4.3.2Services expected from lower layers (30)4.4Functions (30)5Procedures (32)5.1General (32)5.1.1Introduction (32)5.1.2General requirements (32)5.2System information (33)5.2.1Introduction (33)5.2.1.1General (33)5.2.1.2Scheduling (34)5.2.1.2a Scheduling for NB-IoT (34)5.2.1.3System information validity and notification of changes (35)5.2.1.4Indication of ETWS notification (36)5.2.1.5Indication of CMAS notification (37)5.2.1.6Notification of EAB parameters change (37)5.2.1.7Access Barring parameters change in NB-IoT (37)5.2.2System information acquisition (38)5.2.2.1General (38)5.2.2.2Initiation (38)5.2.2.3System information required by the UE (38)5.2.2.4System information acquisition by the UE (39)5.2.2.5Essential system information missing (42)5.2.2.6Actions upon reception of the MasterInformationBlock message (42)5.2.2.7Actions upon reception of the SystemInformationBlockType1 message (42)5.2.2.8Actions upon reception of SystemInformation messages (44)5.2.2.9Actions upon reception of SystemInformationBlockType2 (44)5.2.2.10Actions upon reception of SystemInformationBlockType3 (45)5.2.2.11Actions upon reception of SystemInformationBlockType4 (45)5.2.2.12Actions upon reception of SystemInformationBlockType5 (45)5.2.2.13Actions upon reception of SystemInformationBlockType6 (45)5.2.2.14Actions upon reception of SystemInformationBlockType7 (45)5.2.2.15Actions upon reception of SystemInformationBlockType8 (45)5.2.2.16Actions upon reception of SystemInformationBlockType9 (46)5.2.2.17Actions upon reception of SystemInformationBlockType10 (46)5.2.2.18Actions upon reception of SystemInformationBlockType11 (46)5.2.2.19Actions upon reception of SystemInformationBlockType12 (47)5.2.2.20Actions upon reception of SystemInformationBlockType13 (48)5.2.2.21Actions upon reception of SystemInformationBlockType14 (48)5.2.2.22Actions upon reception of SystemInformationBlockType15 (48)5.2.2.23Actions upon reception of SystemInformationBlockType16 (48)5.2.2.24Actions upon reception of SystemInformationBlockType17 (48)5.2.2.25Actions upon reception of SystemInformationBlockType18 (48)5.2.2.26Actions upon reception of SystemInformationBlockType19 (49)5.2.3Acquisition of an SI message (49)5.2.3a Acquisition of an SI message by BL UE or UE in CE or a NB-IoT UE (50)5.3Connection control (50)5.3.1Introduction (50)5.3.1.1RRC connection control (50)5.3.1.2Security (52)5.3.1.2a RN security (53)5.3.1.3Connected mode mobility (53)5.3.1.4Connection control in NB-IoT (54)5.3.2Paging (55)5.3.2.1General (55)5.3.2.2Initiation (55)5.3.2.3Reception of the Paging message by the UE (55)5.3.3RRC connection establishment (56)5.3.3.1General (56)5.3.3.1a Conditions for establishing RRC Connection for sidelink communication/ discovery (58)5.3.3.2Initiation (59)5.3.3.3Actions related to transmission of RRCConnectionRequest message (63)5.3.3.3a Actions related to transmission of RRCConnectionResumeRequest message (64)5.3.3.4Reception of the RRCConnectionSetup by the UE (64)5.3.3.4a Reception of the RRCConnectionResume by the UE (66)5.3.3.5Cell re-selection while T300, T302, T303, T305, T306, or T308 is running (68)5.3.3.6T300 expiry (68)5.3.3.7T302, T303, T305, T306, or T308 expiry or stop (69)5.3.3.8Reception of the RRCConnectionReject by the UE (70)5.3.3.9Abortion of RRC connection establishment (71)5.3.3.10Handling of SSAC related parameters (71)5.3.3.11Access barring check (72)5.3.3.12EAB check (73)5.3.3.13Access barring check for ACDC (73)5.3.3.14Access Barring check for NB-IoT (74)5.3.4Initial security activation (75)5.3.4.1General (75)5.3.4.2Initiation (76)5.3.4.3Reception of the SecurityModeCommand by the UE (76)5.3.5RRC connection reconfiguration (77)5.3.5.1General (77)5.3.5.2Initiation (77)5.3.5.3Reception of an RRCConnectionReconfiguration not including the mobilityControlInfo by theUE (77)5.3.5.4Reception of an RRCConnectionReconfiguration including the mobilityControlInfo by the UE(handover) (79)5.3.5.5Reconfiguration failure (83)5.3.5.6T304 expiry (handover failure) (83)5.3.5.7Void (84)5.3.5.7a T307 expiry (SCG change failure) (84)5.3.5.8Radio Configuration involving full configuration option (84)5.3.6Counter check (86)5.3.6.1General (86)5.3.6.2Initiation (86)5.3.6.3Reception of the CounterCheck message by the UE (86)5.3.7RRC connection re-establishment (87)5.3.7.1General (87)5.3.7.2Initiation (87)5.3.7.3Actions following cell selection while T311 is running (88)5.3.7.4Actions related to transmission of RRCConnectionReestablishmentRequest message (89)5.3.7.5Reception of the RRCConnectionReestablishment by the UE (89)5.3.7.6T311 expiry (91)5.3.7.7T301 expiry or selected cell no longer suitable (91)5.3.7.8Reception of RRCConnectionReestablishmentReject by the UE (91)5.3.8RRC connection release (92)5.3.8.1General (92)5.3.8.2Initiation (92)5.3.8.3Reception of the RRCConnectionRelease by the UE (92)5.3.8.4T320 expiry (93)5.3.9RRC connection release requested by upper layers (93)5.3.9.1General (93)5.3.9.2Initiation (93)5.3.10Radio resource configuration (93)5.3.10.0General (93)5.3.10.1SRB addition/ modification (94)5.3.10.2DRB release (95)5.3.10.3DRB addition/ modification (95)5.3.10.3a1DC specific DRB addition or reconfiguration (96)5.3.10.3a2LWA specific DRB addition or reconfiguration (98)5.3.10.3a3LWIP specific DRB addition or reconfiguration (98)5.3.10.3a SCell release (99)5.3.10.3b SCell addition/ modification (99)5.3.10.3c PSCell addition or modification (99)5.3.10.4MAC main reconfiguration (99)5.3.10.5Semi-persistent scheduling reconfiguration (100)5.3.10.6Physical channel reconfiguration (100)5.3.10.7Radio Link Failure Timers and Constants reconfiguration (101)5.3.10.8Time domain measurement resource restriction for serving cell (101)5.3.10.9Other configuration (102)5.3.10.10SCG reconfiguration (103)5.3.10.11SCG dedicated resource configuration (104)5.3.10.12Reconfiguration SCG or split DRB by drb-ToAddModList (105)5.3.10.13Neighbour cell information reconfiguration (105)5.3.10.14Void (105)5.3.10.15Sidelink dedicated configuration (105)5.3.10.16T370 expiry (106)5.3.11Radio link failure related actions (107)5.3.11.1Detection of physical layer problems in RRC_CONNECTED (107)5.3.11.2Recovery of physical layer problems (107)5.3.11.3Detection of radio link failure (107)5.3.12UE actions upon leaving RRC_CONNECTED (109)5.3.13UE actions upon PUCCH/ SRS release request (110)5.3.14Proximity indication (110)5.3.14.1General (110)5.3.14.2Initiation (111)5.3.14.3Actions related to transmission of ProximityIndication message (111)5.3.15Void (111)5.4Inter-RAT mobility (111)5.4.1Introduction (111)5.4.2Handover to E-UTRA (112)5.4.2.1General (112)5.4.2.2Initiation (112)5.4.2.3Reception of the RRCConnectionReconfiguration by the UE (112)5.4.2.4Reconfiguration failure (114)5.4.2.5T304 expiry (handover to E-UTRA failure) (114)5.4.3Mobility from E-UTRA (114)5.4.3.1General (114)5.4.3.2Initiation (115)5.4.3.3Reception of the MobilityFromEUTRACommand by the UE (115)5.4.3.4Successful completion of the mobility from E-UTRA (116)5.4.3.5Mobility from E-UTRA failure (117)5.4.4Handover from E-UTRA preparation request (CDMA2000) (117)5.4.4.1General (117)5.4.4.2Initiation (118)5.4.4.3Reception of the HandoverFromEUTRAPreparationRequest by the UE (118)5.4.5UL handover preparation transfer (CDMA2000) (118)5.4.5.1General (118)5.4.5.2Initiation (118)5.4.5.3Actions related to transmission of the ULHandoverPreparationTransfer message (119)5.4.5.4Failure to deliver the ULHandoverPreparationTransfer message (119)5.4.6Inter-RAT cell change order to E-UTRAN (119)5.4.6.1General (119)5.4.6.2Initiation (119)5.4.6.3UE fails to complete an inter-RAT cell change order (119)5.5Measurements (120)5.5.1Introduction (120)5.5.2Measurement configuration (121)5.5.2.1General (121)5.5.2.2Measurement identity removal (122)5.5.2.2a Measurement identity autonomous removal (122)5.5.2.3Measurement identity addition/ modification (123)5.5.2.4Measurement object removal (124)5.5.2.5Measurement object addition/ modification (124)5.5.2.6Reporting configuration removal (126)5.5.2.7Reporting configuration addition/ modification (127)5.5.2.8Quantity configuration (127)5.5.2.9Measurement gap configuration (127)5.5.2.10Discovery signals measurement timing configuration (128)5.5.2.11RSSI measurement timing configuration (128)5.5.3Performing measurements (128)5.5.3.1General (128)5.5.3.2Layer 3 filtering (131)5.5.4Measurement report triggering (131)5.5.4.1General (131)5.5.4.2Event A1 (Serving becomes better than threshold) (135)5.5.4.3Event A2 (Serving becomes worse than threshold) (136)5.5.4.4Event A3 (Neighbour becomes offset better than PCell/ PSCell) (136)5.5.4.5Event A4 (Neighbour becomes better than threshold) (137)5.5.4.6Event A5 (PCell/ PSCell becomes worse than threshold1 and neighbour becomes better thanthreshold2) (138)5.5.4.6a Event A6 (Neighbour becomes offset better than SCell) (139)5.5.4.7Event B1 (Inter RAT neighbour becomes better than threshold) (139)5.5.4.8Event B2 (PCell becomes worse than threshold1 and inter RAT neighbour becomes better thanthreshold2) (140)5.5.4.9Event C1 (CSI-RS resource becomes better than threshold) (141)5.5.4.10Event C2 (CSI-RS resource becomes offset better than reference CSI-RS resource) (141)5.5.4.11Event W1 (WLAN becomes better than a threshold) (142)5.5.4.12Event W2 (All WLAN inside WLAN mobility set becomes worse than threshold1 and a WLANoutside WLAN mobility set becomes better than threshold2) (142)5.5.4.13Event W3 (All WLAN inside WLAN mobility set becomes worse than a threshold) (143)5.5.5Measurement reporting (144)5.5.6Measurement related actions (148)5.5.6.1Actions upon handover and re-establishment (148)5.5.6.2Speed dependant scaling of measurement related parameters (149)5.5.7Inter-frequency RSTD measurement indication (149)5.5.7.1General (149)5.5.7.2Initiation (150)5.5.7.3Actions related to transmission of InterFreqRSTDMeasurementIndication message (150)5.6Other (150)5.6.0General (150)5.6.1DL information transfer (151)5.6.1.1General (151)5.6.1.2Initiation (151)5.6.1.3Reception of the DLInformationTransfer by the UE (151)5.6.2UL information transfer (151)5.6.2.1General (151)5.6.2.2Initiation (151)5.6.2.3Actions related to transmission of ULInformationTransfer message (152)5.6.2.4Failure to deliver ULInformationTransfer message (152)5.6.3UE capability transfer (152)5.6.3.1General (152)5.6.3.2Initiation (153)5.6.3.3Reception of the UECapabilityEnquiry by the UE (153)5.6.4CSFB to 1x Parameter transfer (157)5.6.4.1General (157)5.6.4.2Initiation (157)5.6.4.3Actions related to transmission of CSFBParametersRequestCDMA2000 message (157)5.6.4.4Reception of the CSFBParametersResponseCDMA2000 message (157)5.6.5UE Information (158)5.6.5.1General (158)5.6.5.2Initiation (158)5.6.5.3Reception of the UEInformationRequest message (158)5.6.6 Logged Measurement Configuration (159)5.6.6.1General (159)5.6.6.2Initiation (160)5.6.6.3Reception of the LoggedMeasurementConfiguration by the UE (160)5.6.6.4T330 expiry (160)5.6.7 Release of Logged Measurement Configuration (160)5.6.7.1General (160)5.6.7.2Initiation (160)5.6.8 Measurements logging (161)5.6.8.1General (161)5.6.8.2Initiation (161)5.6.9In-device coexistence indication (163)5.6.9.1General (163)5.6.9.2Initiation (164)5.6.9.3Actions related to transmission of InDeviceCoexIndication message (164)5.6.10UE Assistance Information (165)5.6.10.1General (165)5.6.10.2Initiation (166)5.6.10.3Actions related to transmission of UEAssistanceInformation message (166)5.6.11 Mobility history information (166)5.6.11.1General (166)5.6.11.2Initiation (166)5.6.12RAN-assisted WLAN interworking (167)5.6.12.1General (167)5.6.12.2Dedicated WLAN offload configuration (167)5.6.12.3WLAN offload RAN evaluation (167)5.6.12.4T350 expiry or stop (167)5.6.12.5Cell selection/ re-selection while T350 is running (168)5.6.13SCG failure information (168)5.6.13.1General (168)5.6.13.2Initiation (168)5.6.13.3Actions related to transmission of SCGFailureInformation message (168)5.6.14LTE-WLAN Aggregation (169)5.6.14.1Introduction (169)5.6.14.2Reception of LWA configuration (169)5.6.14.3Release of LWA configuration (170)5.6.15WLAN connection management (170)5.6.15.1Introduction (170)5.6.15.2WLAN connection status reporting (170)5.6.15.2.1General (170)5.6.15.2.2Initiation (171)5.6.15.2.3Actions related to transmission of WLANConnectionStatusReport message (171)5.6.15.3T351 Expiry (WLAN connection attempt timeout) (171)5.6.15.4WLAN status monitoring (171)5.6.16RAN controlled LTE-WLAN interworking (172)5.6.16.1General (172)5.6.16.2WLAN traffic steering command (172)5.6.17LTE-WLAN aggregation with IPsec tunnel (173)5.6.17.1General (173)5.7Generic error handling (174)5.7.1General (174)5.7.2ASN.1 violation or encoding error (174)5.7.3Field set to a not comprehended value (174)5.7.4Mandatory field missing (174)5.7.5Not comprehended field (176)5.8MBMS (176)5.8.1Introduction (176)5.8.1.1General (176)5.8.1.2Scheduling (176)5.8.1.3MCCH information validity and notification of changes (176)5.8.2MCCH information acquisition (178)5.8.2.1General (178)5.8.2.2Initiation (178)5.8.2.3MCCH information acquisition by the UE (178)5.8.2.4Actions upon reception of the MBSFNAreaConfiguration message (178)5.8.2.5Actions upon reception of the MBMSCountingRequest message (179)5.8.3MBMS PTM radio bearer configuration (179)5.8.3.1General (179)5.8.3.2Initiation (179)5.8.3.3MRB establishment (179)5.8.3.4MRB release (179)5.8.4MBMS Counting Procedure (179)5.8.4.1General (179)5.8.4.2Initiation (180)5.8.4.3Reception of the MBMSCountingRequest message by the UE (180)5.8.5MBMS interest indication (181)5.8.5.1General (181)5.8.5.2Initiation (181)5.8.5.3Determine MBMS frequencies of interest (182)5.8.5.4Actions related to transmission of MBMSInterestIndication message (183)5.8a SC-PTM (183)5.8a.1Introduction (183)5.8a.1.1General (183)5.8a.1.2SC-MCCH scheduling (183)5.8a.1.3SC-MCCH information validity and notification of changes (183)5.8a.1.4Procedures (184)5.8a.2SC-MCCH information acquisition (184)5.8a.2.1General (184)5.8a.2.2Initiation (184)5.8a.2.3SC-MCCH information acquisition by the UE (184)5.8a.2.4Actions upon reception of the SCPTMConfiguration message (185)5.8a.3SC-PTM radio bearer configuration (185)5.8a.3.1General (185)5.8a.3.2Initiation (185)5.8a.3.3SC-MRB establishment (185)5.8a.3.4SC-MRB release (185)5.9RN procedures (186)5.9.1RN reconfiguration (186)5.9.1.1General (186)5.9.1.2Initiation (186)5.9.1.3Reception of the RNReconfiguration by the RN (186)5.10Sidelink (186)5.10.1Introduction (186)5.10.1a Conditions for sidelink communication operation (187)5.10.2Sidelink UE information (188)5.10.2.1General (188)5.10.2.2Initiation (189)5.10.2.3Actions related to transmission of SidelinkUEInformation message (193)5.10.3Sidelink communication monitoring (195)5.10.6Sidelink discovery announcement (198)5.10.6a Sidelink discovery announcement pool selection (201)5.10.6b Sidelink discovery announcement reference carrier selection (201)5.10.7Sidelink synchronisation information transmission (202)5.10.7.1General (202)5.10.7.2Initiation (203)5.10.7.3Transmission of SLSS (204)5.10.7.4Transmission of MasterInformationBlock-SL message (205)5.10.7.5Void (206)5.10.8Sidelink synchronisation reference (206)5.10.8.1General (206)5.10.8.2Selection and reselection of synchronisation reference UE (SyncRef UE) (206)5.10.9Sidelink common control information (207)5.10.9.1General (207)5.10.9.2Actions related to reception of MasterInformationBlock-SL message (207)5.10.10Sidelink relay UE operation (207)5.10.10.1General (207)5.10.10.2AS-conditions for relay related sidelink communication transmission by sidelink relay UE (207)5.10.10.3AS-conditions for relay PS related sidelink discovery transmission by sidelink relay UE (208)5.10.10.4Sidelink relay UE threshold conditions (208)5.10.11Sidelink remote UE operation (208)5.10.11.1General (208)5.10.11.2AS-conditions for relay related sidelink communication transmission by sidelink remote UE (208)5.10.11.3AS-conditions for relay PS related sidelink discovery transmission by sidelink remote UE (209)5.10.11.4Selection and reselection of sidelink relay UE (209)5.10.11.5Sidelink remote UE threshold conditions (210)6Protocol data units, formats and parameters (tabular & ASN.1) (210)6.1General (210)6.2RRC messages (212)6.2.1General message structure (212)–EUTRA-RRC-Definitions (212)–BCCH-BCH-Message (212)–BCCH-DL-SCH-Message (212)–BCCH-DL-SCH-Message-BR (213)–MCCH-Message (213)–PCCH-Message (213)–DL-CCCH-Message (214)–DL-DCCH-Message (214)–UL-CCCH-Message (214)–UL-DCCH-Message (215)–SC-MCCH-Message (215)6.2.2Message definitions (216)–CounterCheck (216)–CounterCheckResponse (217)–CSFBParametersRequestCDMA2000 (217)–CSFBParametersResponseCDMA2000 (218)–DLInformationTransfer (218)–HandoverFromEUTRAPreparationRequest (CDMA2000) (219)–InDeviceCoexIndication (220)–InterFreqRSTDMeasurementIndication (222)–LoggedMeasurementConfiguration (223)–MasterInformationBlock (225)–MBMSCountingRequest (226)–MBMSCountingResponse (226)–MBMSInterestIndication (227)–MBSFNAreaConfiguration (228)–MeasurementReport (228)–MobilityFromEUTRACommand (229)–Paging (232)–ProximityIndication (233)–RNReconfiguration (234)–RNReconfigurationComplete (234)–RRCConnectionReconfiguration (235)–RRCConnectionReconfigurationComplete (240)–RRCConnectionReestablishment (241)–RRCConnectionReestablishmentComplete (241)–RRCConnectionReestablishmentReject (242)–RRCConnectionReestablishmentRequest (243)–RRCConnectionReject (243)–RRCConnectionRelease (244)–RRCConnectionResume (248)–RRCConnectionResumeComplete (249)–RRCConnectionResumeRequest (250)–RRCConnectionRequest (250)–RRCConnectionSetup (251)–RRCConnectionSetupComplete (252)–SCGFailureInformation (253)–SCPTMConfiguration (254)–SecurityModeCommand (255)–SecurityModeComplete (255)–SecurityModeFailure (256)–SidelinkUEInformation (256)–SystemInformation (258)–SystemInformationBlockType1 (259)–UEAssistanceInformation (264)–UECapabilityEnquiry (265)–UECapabilityInformation (266)–UEInformationRequest (267)–UEInformationResponse (267)–ULHandoverPreparationTransfer (CDMA2000) (273)–ULInformationTransfer (274)–WLANConnectionStatusReport (274)6.3RRC information elements (275)6.3.1System information blocks (275)–SystemInformationBlockType2 (275)–SystemInformationBlockType3 (279)–SystemInformationBlockType4 (282)–SystemInformationBlockType5 (283)–SystemInformationBlockType6 (287)–SystemInformationBlockType7 (289)–SystemInformationBlockType8 (290)–SystemInformationBlockType9 (295)–SystemInformationBlockType10 (295)–SystemInformationBlockType11 (296)–SystemInformationBlockType12 (297)–SystemInformationBlockType13 (297)–SystemInformationBlockType14 (298)–SystemInformationBlockType15 (298)–SystemInformationBlockType16 (299)–SystemInformationBlockType17 (300)–SystemInformationBlockType18 (301)–SystemInformationBlockType19 (301)–SystemInformationBlockType20 (304)6.3.2Radio resource control information elements (304)–AntennaInfo (304)–AntennaInfoUL (306)–CQI-ReportConfig (307)–CQI-ReportPeriodicProcExtId (314)–CrossCarrierSchedulingConfig (314)–CSI-IM-Config (315)–CSI-IM-ConfigId (315)–CSI-RS-Config (317)–CSI-RS-ConfigEMIMO (318)–CSI-RS-ConfigNZP (319)–CSI-RS-ConfigNZPId (320)–CSI-RS-ConfigZP (321)–CSI-RS-ConfigZPId (321)–DMRS-Config (321)–DRB-Identity (322)–EPDCCH-Config (322)–EIMTA-MainConfig (324)–LogicalChannelConfig (325)–LWA-Configuration (326)–LWIP-Configuration (326)–RCLWI-Configuration (327)–MAC-MainConfig (327)–P-C-AndCBSR (332)–PDCCH-ConfigSCell (333)–PDCP-Config (334)–PDSCH-Config (337)–PDSCH-RE-MappingQCL-ConfigId (339)–PHICH-Config (339)–PhysicalConfigDedicated (339)–P-Max (344)–PRACH-Config (344)–PresenceAntennaPort1 (346)–PUCCH-Config (347)–PUSCH-Config (351)–RACH-ConfigCommon (355)–RACH-ConfigDedicated (357)–RadioResourceConfigCommon (358)–RadioResourceConfigDedicated (362)–RLC-Config (367)–RLF-TimersAndConstants (369)–RN-SubframeConfig (370)–SchedulingRequestConfig (371)–SoundingRS-UL-Config (372)–SPS-Config (375)–TDD-Config (376)–TimeAlignmentTimer (377)–TPC-PDCCH-Config (377)–TunnelConfigLWIP (378)–UplinkPowerControl (379)–WLAN-Id-List (382)–WLAN-MobilityConfig (382)6.3.3Security control information elements (382)–NextHopChainingCount (382)–SecurityAlgorithmConfig (383)–ShortMAC-I (383)6.3.4Mobility control information elements (383)–AdditionalSpectrumEmission (383)–ARFCN-ValueCDMA2000 (383)–ARFCN-ValueEUTRA (384)–ARFCN-ValueGERAN (384)–ARFCN-ValueUTRA (384)–BandclassCDMA2000 (384)–BandIndicatorGERAN (385)–CarrierFreqCDMA2000 (385)–CarrierFreqGERAN (385)–CellIndexList (387)–CellReselectionPriority (387)–CellSelectionInfoCE (387)–CellReselectionSubPriority (388)–CSFB-RegistrationParam1XRTT (388)–CellGlobalIdEUTRA (389)–CellGlobalIdUTRA (389)–CellGlobalIdGERAN (390)–CellGlobalIdCDMA2000 (390)–CellSelectionInfoNFreq (391)–CSG-Identity (391)–FreqBandIndicator (391)–MobilityControlInfo (391)–MobilityParametersCDMA2000 (1xRTT) (393)–MobilityStateParameters (394)–MultiBandInfoList (394)–NS-PmaxList (394)–PhysCellId (395)–PhysCellIdRange (395)–PhysCellIdRangeUTRA-FDDList (395)–PhysCellIdCDMA2000 (396)–PhysCellIdGERAN (396)–PhysCellIdUTRA-FDD (396)–PhysCellIdUTRA-TDD (396)–PLMN-Identity (397)–PLMN-IdentityList3 (397)–PreRegistrationInfoHRPD (397)–Q-QualMin (398)–Q-RxLevMin (398)–Q-OffsetRange (398)–Q-OffsetRangeInterRAT (399)–ReselectionThreshold (399)–ReselectionThresholdQ (399)–SCellIndex (399)–ServCellIndex (400)–SpeedStateScaleFactors (400)–SystemInfoListGERAN (400)–SystemTimeInfoCDMA2000 (401)–TrackingAreaCode (401)–T-Reselection (402)–T-ReselectionEUTRA-CE (402)6.3.5Measurement information elements (402)–AllowedMeasBandwidth (402)–CSI-RSRP-Range (402)–Hysteresis (402)–LocationInfo (403)–MBSFN-RSRQ-Range (403)–MeasConfig (404)–MeasDS-Config (405)–MeasGapConfig (406)–MeasId (407)–MeasIdToAddModList (407)–MeasObjectCDMA2000 (408)–MeasObjectEUTRA (408)–MeasObjectGERAN (412)–MeasObjectId (412)–MeasObjectToAddModList (412)–MeasObjectUTRA (413)–ReportConfigEUTRA (422)–ReportConfigId (425)–ReportConfigInterRAT (425)–ReportConfigToAddModList (428)–ReportInterval (429)–RSRP-Range (429)–RSRQ-Range (430)–RSRQ-Type (430)–RS-SINR-Range (430)–RSSI-Range-r13 (431)–TimeToTrigger (431)–UL-DelayConfig (431)–WLAN-CarrierInfo (431)–WLAN-RSSI-Range (432)–WLAN-Status (432)6.3.6Other information elements (433)–AbsoluteTimeInfo (433)–AreaConfiguration (433)–C-RNTI (433)–DedicatedInfoCDMA2000 (434)–DedicatedInfoNAS (434)–FilterCoefficient (434)–LoggingDuration (434)–LoggingInterval (435)–MeasSubframePattern (435)–MMEC (435)–NeighCellConfig (435)–OtherConfig (436)–RAND-CDMA2000 (1xRTT) (437)–RAT-Type (437)–ResumeIdentity (437)–RRC-TransactionIdentifier (438)–S-TMSI (438)–TraceReference (438)–UE-CapabilityRAT-ContainerList (438)–UE-EUTRA-Capability (439)–UE-RadioPagingInfo (469)–UE-TimersAndConstants (469)–VisitedCellInfoList (470)–WLAN-OffloadConfig (470)6.3.7MBMS information elements (472)–MBMS-NotificationConfig (472)–MBMS-ServiceList (473)–MBSFN-AreaId (473)–MBSFN-AreaInfoList (473)–MBSFN-SubframeConfig (474)–PMCH-InfoList (475)6.3.7a SC-PTM information elements (476)–SC-MTCH-InfoList (476)–SCPTM-NeighbourCellList (478)6.3.8Sidelink information elements (478)–SL-CommConfig (478)–SL-CommResourcePool (479)–SL-CP-Len (480)–SL-DiscConfig (481)–SL-DiscResourcePool (483)–SL-DiscTxPowerInfo (485)–SL-GapConfig (485)。

ALC887 音频芯片技术资料

2. FEATURES .........................................................................................................................................................................2

6. PIN DESCRIPTIONS.........................................................................................................................................................8

6.1. DIGITAL I/O PINS .........................................................................................................................................................8 6.2. ANALOG I/O PINS ........................................................................................................................................................8 6.3. FILTER/REFERENCE......................................................................................................................................................9 6.4. POWER/GROUND........................................................................................................................................................10

AX88796总结

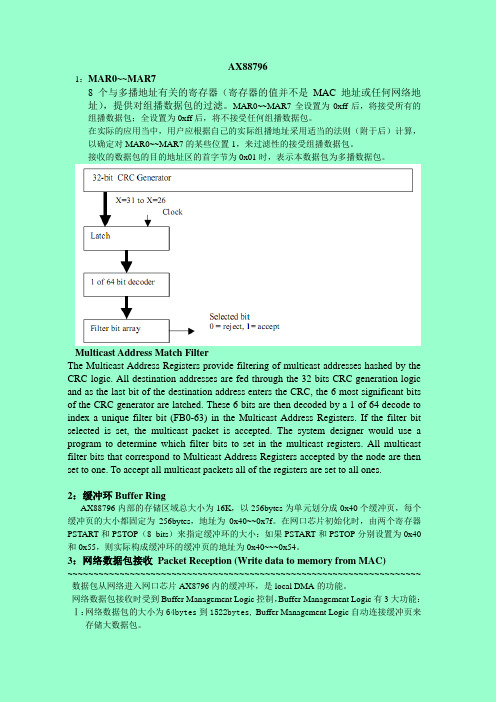

AX887961:MAR0~~MAR78个与多播地址有关的寄存器(寄存器的值并不是MAC地址或任何网络地址),提供对组播数据包的过滤。

MAR0~~MAR7全设置为0xff后,将接受所有的组播数据包;全设置为0xff后,将不接受任何组播数据包。

在实际的应用当中,用户应根据自己的实际组播地址采用适当的法则(附于后)计算,以确定对MAR0~~MAR7的某些位置1,来过滤性的接受组播数据包。

接收的数据包的目的地址区的首字节为0x01时,表示本数据包为多播数据包。

Multicast Address Match FilterThe Multicast Address Registers provide filtering of multicast addresses hashed by the CRC logic. All destination addresses are fed through the 32 bits CRC generation logic and as the last bit of the destination address enters the CRC, the 6 most significant bits of the CRC generator are latched. These 6 bits are then decoded by a 1 of 64 decode to index a unique filter bit (FB0-63) in the Multicast Address Registers. If the filter bit selected is set, the multicast packet is accepted. The system designer would use a program to determine which filter bits to set in the multicast registers. All multicast filter bits that correspond to Multicast Address Registers accepted by the node are then set to one. To accept all multicast packets all of the registers are set to all ones.2:缓冲环Buffer RingAX88796内部的存储区域总大小为16K,以256bytes为单元划分成0x40个缓冲页,每个缓冲页的大小都固定为256bytes,地址为0x40~~0x7f。

Cisco 880系列集成服务路由器数据册说明书