IO接口译码电路设计

微机原理CH5 IO接口电路的设计(ok)

键盘、鼠标、扫描仪是常用的输入设备;磁盘、 显示器、打印机、绘图仪是常用的输出设备。这些设 备统称为计算机的外部设备,简称外设或者是I/O设 备。计算机和外设之间的信息的交换称为通信。

2

第五章

由于外部设备的种类繁多,它们对所传输的信 息的要求也各不相同,这样就给计算机与外设之间 的信息交换带来了一些问题。 (1)速度不匹配 CPU的速度很高,而外设速度要低的多,一个快 速的设备和一个慢速的设备通信时应该要适应慢速 设备的要求,所以会降低CPU的工作效率。 (2)信号电平不匹配 CPU所使用的电平标准TTL电平,5V高电平表示1 ,0V低电平表示0;而外设的电平标准较复杂,不同 的外设有不同的电平标准。

3

第五章

(3)信号格式不匹配 CPU总线上传送的通常是8、16、32位的并行数 据,而各种外设使用的信息格式各不相同。 (4)时序不匹配 各种外设都有自己的定时和控制逻辑,与计算 机CPU时序不一致。 因此输入输出设备不能直接与计算机的系统总 线相连,必须在CPU与外设之间设置专门接口电路。

4

第五章

7

第五章

1、74LS244 8路单向数据总线缓冲器。

8

第五章

功能: 功能:内部包含了8个三态缓冲单元,分为两组, 每组4个单元,由两个控制信号进行控制。当1G 为 低电平时,输入端1A1~1A4的输入信号可以到达输出 端1Y1~1Y4;当 2G 为低电平时,输入端2A1~2A4的输 入信号可以到达输出端2Y1~2Y4;当1G 和 2G 为高电 ~ 平时,输出呈高阻态。此芯片常用来作为外设输入 数据的端口,是一种单向数据缓冲器,数据只能从A 传到Y 。

15

第五章

(3)命令端口(Command Port) 也称为控制端口(Control Port),它用来存放 CPU向接口发出的各种命令和控制字,以便控制接口 或设备的动作。 CPU通过接口和外设交换数据时,只有输入(IN) 和输出(OUT)两种指令,所以只能把状态信息和命令 信息也都当作数据信息来传送,且将状态信息作为 输入数据,控制信息作为输出数据。

第3章-IO端口地址译码技术

本章主要内容

➢ I/O 端口的基本概念 ➢ I/O 端口译码的基本原理 ➢ I/O 端口译码电路的设计

2020/5/11

计算机接口技术

1

一、接口信息与功能

1、接口信息 • 数据信号:

如:8位、16位、32位数据;

• 状态信号:

表示外设是否准备好信号。

CPU

地址 数据 控制

;将端口F4H和F5H的16位数据送AX ;将端口F4H、F5H、F6H和F7H的32位数据送 ;EAX ;从DX指出的端口输入32位数据到EAX

;EAX内容输出到DX指出的32位数据端口

2020/5/11

计算机接口技术

10

I/O指令表示,CPU从端口读数据或向端口写数据,

仅仅是指I/O端口与CPU的累加器之间的数据传输,

并未涉及数据是否传输到存储器的问题。若要将端口的数据 传输到存储器,还得用MOV指令进行传输。

例如:

MOV [DI],AL IN AL,DX

;将数据从AL→存储器 ;从端口读数据到AL

MOV [DI],AL ;将数据从AL→存储器

MOV DX,301H ;I/O端口

将端口的 数据传输 到存储器

MOV AL,[SI] ;从内存取数据到AL

信号转换功能:协调总线信号与I/O设备信号。转换包 括信号的逻辑关系、时序配合和电平转换。

可编程功能:增加接口的灵活性和智能性。

3.1 I/O 地址空间

如果忽略I/O地址空间的物理特征,仅从软件编程的角度来看,和 存储器地址空间一样,I/O地址空间也是一片连续的地址单元,可供 各种外设与CPU交换信息时,存放数据、状态和命令代码之用。

出程序段:接口电路硬件保护及操作系统中数据恢复。

第3章-IO地址译码

主要优点: (1) I/O端口地址不占用存储器空间; (2) I/O指令短,执行速度快;

FFFFH

(3) I/O操作和存储器操作层次清晰,程序的可读性强。

缺点:

I/O指令种类有限, I/O空间不易扩展

2、统一编址(存储器映象方式)

地址 0000H ... 0100H 00FFH ...

I/O空间 (256个) 整 个 地 址 空 间

四、DMA传送方式

工作原理 由外设与计算机内存直接进行数据交换,而不是通 过CPU; 在DMA传送期间,DMA控制器接管了总线控制权,而 CPU处在停机方式,即处于等待状态; 在DMA传送完成后,CPU再恢复对总线的控制权,进 入工作状态。 CPU 特点 数据的传送不经过CPU。 RAM 外设 要求 DMA 需要DMA控制器及相关逻辑支持。 控制器 应用 适用于高速度大量数据传送时。

2、C语言I/O语句

C语言有强大的I/O操作功能,利用c语言可方便地设计操作 界面,同时也可以对外设进行直接控制. 端口输出 outportb(port,value) //从port端口输出字节型数据 value outportw (port,value) //从port端口输出字型数据value

了解I/O端口地址分配 对接口设计者非常重要。 一、64K I/O地址映像图 I/O地址线:16位 I/O端口地址空间:64K 分为两部分。 ① 留给微机系统和ISA总线 地址固定 ② 留给PCI总线,主板功能和用户应用 地址动态分配

① 0000H~03FFH

② 0400H~FFFFH

3.3

I/O端口地址分配

第3章基本的I/O接口 ---来自I/O地址译码内容提要

接口技术作业2-地址译码

第3章I/O端口地址译码技术作业1、什么是I/O端口在一个接口电路中一般拥有几种端口2、I/O端口是I/O接口电路中能被CPU直接访问的寄存器。

在一个接口电路中一般拥有:命令端口、状态端口和数据端口。

2、图1是一个固定式I/O端口地址译码电路,试根据图中地址线的分配,写出输出端的地址。

图1 固定式I/O端口地址译码电路输出端低电平有效,根据图1有:地址线0 0 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0二进制 1 0 1 1 1 1 1 0 0 0十六进制 2 F 8所以,输出端的值:2F8H3、图2是某微机实验平台板的I/O端口地址译码电路。

若将DIP开关状态设置为:S0和S1合上(ON),S3和S4断开(OFF),试指出74LS138的输出端地址范围。

图2 使用比较器的可选式译码电路从图2中可以看出,当S0断开时,其值为1(高电平),A6必须为0,对应的异或门输出才会是1,;同样,当S1合上时,其值为0(高电平),A7必须为1,对应的异或门输出才会是1;类推,S2合上,S3断开时,A8,A9必须为1,0。

即当S2和S1合上,S3和S0断开时,译码电路输入地址线的值地址线0 0 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0二进制 0 1 1 0 片选片内端口寻址十六进制 0~7H 0~7H所以,CS0地址为:180H~187H共8个端口地址。

CS1地址为:188H~18FH共8个端口地址。

CS2地址为:190H~197H共8个端口地址。

CS3地址为:198H~19FH共8个端口地址。

CS4地址为:1A0H~1A7H共8个端口地址。

CS5地址为:1A8H~1AFH共8个端口地址。

CS6地址为:1B0H~1B7H共8个端口地址。

CS7地址为:1B8H~1BFH共8个端口地址。

第02章 IO端口地址译码技术

故不设状态口。

② 端口的数目设置:与接口电路的规模和功能有关。 (4)端口的共用技术 一般情况下,一个端口只允许接纳一种信息,但有些接口 芯片允许同一端口既作命令口用,有作状态口用,或允许向同

一命令口写多个命令字,这就产生了端口共用问题。

当多个命令字写到同一命令口时,命令寄存器采用以下办 法来识别不同的命令:

3

第2章 I/O端口地址译码技术

(1)在命令字中设置特征位或设置专门的访问位,根据特征位 来识别不同的命令(8255)。 (2)在编写初始化程序时,按先后顺序向同一端口写不同的命 令字,命令寄存器就根据这种先后顺序的约定来识别不同 的命令(8251)。 (3)有的是采用两种方法相结合的手段来解决端口的共用问题 (8259)。 2、端口的编址 (1)外设端口和存储器统一编址 ① 在这种编址方式中, 将存储器空间分出一部分给外设 端口,CPU对存储器的访问或对外设的访问使用同一个 操作指令。例如与存储器交换数据用MOV传送指令,与 外设交换数据也用MOV传送指令,是访问存储器还是访 问外设,用不同的地址加以区别。

指令加以区别。因此这种编址方式又称为覆盖编址方式。

5

第2章 I/O端口地址译码技术

② 优点:是不占用存储器地址,因而不会减少存储器容量,专门的 I/O指令比存储器指令执行速度快, 并且与存储器指令区 别明显,从而使程序中的I/O操作清晰,可读性强。 ③ 缺点:是这种方式只能传送数据而无算术或逻辑运算功能。 (3)独立编址方式的端口访问 单字节——当端口地址为单字节宽度时,采用直接寻址方式(AL,AX) 最多可访问256个端口,系统主板上接口芯片的端口。 例:IN AL,port; 将port端口内容送AL IN AX,port; 将port和port+1端口内容送AX OUT port,AL; 将AL内容输出到port端口 OUT port,AX; 将AX内容送port和port+1端口 双字节——当端口地址宽度为双字节宽度时采用间接寻址方式(DX) 最多可访问216,64K 个端口,I/O扩展槽的接口控制卡上 的端口。 例:MOV DX,port IN AL,DX ;将DX指向的端口中读一个字节送AL MOV DX,port IN AX,DX ;将DX和DX+1指向的2个端口组成一个字送AX

第5章 IO接口电路的设计

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0

0 1 1 1 0 0

1 0 1 1 1 0 1 1 1

x x x x x x

x x x x x x x x x

C018~C01F C020~C027

C028~C02F C030~C037 C038~C03F

1 1 1

1 1 1

0 0 0

0 0 0

0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 1 0 1 0

x x x x x x x x x

C000~C007 C008~C00F C010~C017

1 1

1 1 1

1 1

1 1 1

0 0

0 0 0

0 0

0 0 0

0 0 0 0

开始 初始化 读入状态

N

数据准备好

Y

输入数→CPU

数→内存缓冲区

N Y

传送完? 结束

9

例5-4

查询式输出方式的接口电路

输出 /ACK 设备

数 据 锁存器 (8位) R C

选通 信号 +5V

D7~D0 /WR(写数据) 2 /CS2 /CS1 1

I/O 译码

M//IO A15~A0

Q

D

D触发器

/RD(读状态) D1(数据总线)

10

设:状态口的地址为P_S2,输出口地址 为P_OUT,传送数据的总字节为C_2, 则查询方式输出数据的程序段为: MOV CX,C_2 READ_S2:IN AL,P_S2 TEST AL,02H JZ READ_S2 MOV AL,输出数据 OUT P_OUT,AL LOOP READ_S2 ……

I-O译码实验

I/O译码实验

实验目的: 掌握I/O端口的译码方法

实验设备: 数字逻辑实验箱

2

实验内容

已知并行接口芯片8255A有4个端口,片选信号 CS 为低电平有效。 试用组合逻辑电路实现一个译码电路,使该芯片的4个端口地址为 218H~21BH。

已知数/模转换芯片0832的端口地址为228H~22FH,片选信号CS为 低电平有效。试用集成器件74LS138实现。

3

实验步骤及说明

根据实验要求设计电路 根据设计电路进行连线,可利用实验箱上的开关控

制输入地址,并用发光二极管观测实验结果

4

微型计算机

接口多媒体第二章IO端口译码

第二章I/O端口地址译码技术对设备选择功能是接口电路应具备的基本功能之一,因此,作为进行设备端口选择的I/O端口地址译码电路是每个接口电路中不可缺少的部分。

为此,本章在讨论I/O端口基本概念和I/O端口译码基本原理、基本方法的基础上,着重讨论译码电路的设计。

第一节I/O端口的寻址方式I/O端口微型计算机系统在过程控制、信息处理、数据通信等方面得到了广泛的应用。

对于不同的需求,可选用不同型号的计算机,同时还需要配置不同的外部设备,以扩展系统的功能。

I/O端口:它是处理器与I/O设备直接通信的地址。

实际应用中,通常把I/O接口(Interface)电路中能被CPU直接访问的寄存器或某些特定器件称之为端口(Port)。

通过端口向接口电路中的寄存器发送命令,读取状态和传送数据,因此,一个接口可以有几个端口,如命令口、状态口和数据口,分别对应于命令寄存器、状态寄存器和数据寄存器。

有的接口包括的端口多(如8255A并行接口芯片有4个端口,8237A芯片有16个端口),有的接口包括的端口少(如825lA、8259A芯片只有两个端口)。

对端口的操作也有所不同,有的端口只能写或只能读,有的既可以写也可以读。

一般,一个端口只能写入或读出一种信息,但也有几种信息共用一个端口的,如8255A的一个命令口可接收两种不同的命令,8259A的一个命令口可接收4种不同的命令。

计算机给接口电路中的每个寄存器分配一个端口,因此,CPU在访问这些寄存器时,只需指明它们的端口,不需指出是什么寄存器。

这样,我们在输人/输出程序中,只看到端口,而看不到相应的具体寄存器。

也就是说,访问端口就是访问接口电路中的寄存器。

所谓I/O的操作指的是指对I/O端口的操作,而不是对I/O设备的操作,即CPU所访问访问的是与 I/O设备相关的端口,而不是 I /O设备本身。

端口地址编址方式如何对端口进行访问呢?这就是所谓的接口的寻址问题。

对上述端口有两种编址方式,一种是端口地址和存储器地址统一编址,即存储器映射方式;另一种是I/O端口地址和存储器地址分开独立编址,即I/O映射方式。

io接口电路设计

io接口电路设计io接口电路设计的目标是实现计算机与外设之间高效、稳定、可靠的数据传输。

在设计io接口电路时,需要考虑的因素非常多,包括数据传输速率、数据传输方式、数据传输协议等等。

在这篇文章中,我们将从以下几个方面来介绍io接口电路的设计。

io接口电路的设计需要考虑数据传输速率。

数据传输速率是指计算机与外设之间进行数据传输的速度。

不同的外设对数据传输速率的要求不同,因此在设计io接口电路时,需要根据外设的需求来确定合适的数据传输速率。

同时,还需要考虑计算机系统的处理能力,确保计算机能够及时处理外设传输过来的数据。

io接口电路的设计还需要考虑数据传输方式。

数据传输方式包括并行传输和串行传输两种。

并行传输是指同时传输多个数据位,传输速度快,但是对线路的要求较高;串行传输是指逐位传输数据,传输速度较慢,但是对线路的要求较低。

在设计io接口电路时,需要根据外设的特点以及系统的要求来选择合适的数据传输方式。

io接口电路的设计还需要考虑数据传输协议。

数据传输协议是指计算机与外设之间进行数据传输时所遵循的规则和约定。

不同的外设可能采用不同的数据传输协议,因此在设计io接口电路时,需要根据外设的需求来选择合适的数据传输协议。

同时,还需要考虑系统的兼容性,确保计算机能够与各种外设进行数据传输。

在设计io接口电路时,还需要考虑电路的稳定性和可靠性。

稳定性是指电路在工作过程中保持稳定的性能和特性;可靠性是指电路在长时间工作过程中不会出现故障。

在设计io接口电路时,需要选择合适的电子元器件,确保电路的稳定性和可靠性。

同时,还需要进行严格的测试和验证,确保电路能够正常工作。

io接口电路设计是计算机系统中非常重要的一部分。

在设计io接口电路时,需要考虑数据传输速率、数据传输方式、数据传输协议等因素,并确保电路的稳定性和可靠性。

通过合理的设计和测试,可以实现计算机与外设之间高效、稳定、可靠的数据传输。

相信随着科技的不断发展,io接口电路设计在未来会有更多的创新和突破。

2.第二章 IO端口地址译码技术

Y2

Y3 Y4

G2B G2A G1

Y5

Y6 Y7

IOW

逻辑门电路进行I/O地址译码

A9 A8 A7 A6 A5 A2 A4 A3 AEN A1 A0

74LS03

3E7H

1. 固定式端口地址译码

接口中用到的地址不能更改,分为单端口地址 译码和多个端口地址译码两种情况 例1. 使用74LS30/20/32和74LS04设计2F8的只读 译码电路 表2.3 译码电路输入地址线的值

A9 1

Y7

端口31 31F

A4~A0

A0 A1 A2 A3 A4

MOV DX,301H ( 31FH ) IN AL,DX D0~D7 IOR

300~31FH

端口0 300 端口1 301

IOW AEN CPU A9 A8

A7 1 1 0

A6 A5

0 0

端 口 译 码 电 路

端口1 302 Y0 CS

方法1:使用基本的逻辑门

304H ~ 307H

A0 A1 A2 CPU A3 A4 A5 A6 A7 A8 A9

D0-D7

A6 A7 A8 A9

1

A2 A3 A4

__ Y0 __ Y1

端口0 端口1 端口2 端口3

….

__ Y6 __

G1

Y7

31C~31FH

(扩展槽上接口卡的地址译码电路)

以Y0为例:

通过跳线控制其逻辑电平组合决定具体选中哪一个扩展卡

A9 1 1 1 1

A8 A7 A6 1 0 0 1 0 0 1 0 0 1 0 0

A5 0 0 0 0

介绍74LS245

8位双向缓冲器 • 控制端连接在一起, 低电平有效 • 可以双向导通 • 输出与输入同相

微机接口技术-第3章IO端口地址译码技术

内存 内存接口

系统总线:地址总线XA19-0,数据总线XD7-0,控制总线/XIOR ……

智能仪器接口 通信接口 过程控制接口 输入接口

输出接口

外存接口

数字化存储示 波器,数字化

万用表

终端 调制解调器 TTY 电传机

A/D转换器 开关量输入 D/A转换器 开关量输出

键盘 数字化仪 点阵打印 CRT 显示

么?

思考:在PC机上设计接口,你设计的接口IO地址必须不能与其他设备 接口IO地址冲突,你能想到用什么办法解决这个问题?

方案一:先查PC机硬件说明书,看那些IO 地址已经被占用。

缺点是麻烦,且非PC机器厂家生产的设备 (如扩展接口卡)地址,必须通过查该卡

说明书才能了解它占用的IO地址。

不可能!!你怎么知道你的卡被客户装在 哪台机器上?客户计算机上装了哪些其它 厂家的卡,你怎么能预先知道呢?客户买

Y X 9X A 8 X A 7 X A 6 X A 5 X A 4 X A 3X A 2 A X 1 X A 0 X AX I O A XA9 XA8 XA7 XA6 XA5 XA4 XA3 XA2

/+Y

例2。 使用74LS138设计一个系统板上IO端口地址译码电路,并且让每个接口芯片内部 可以有32个端口,非DMA期间可以访问接口芯片。

分析:输入 XA9-5,XAEN。因为低5位地址用来选中芯片内部端口,不作为外部译码器 的输入。一片138只能译码3位地址,这里用138对XA7-XA5译码。

输出 8个芯片选中信号/Y0-/Y7。 逻辑关系:XAEN=0,XA9XA8=00时,使译码器工作。 XA7-XA5=000时,输出/Y0=0, 其余全无效为1。 XA7-XA5=001时,输出/Y1=0, 其余全无效为1 XA7-XA5=010时,输出/Y2=0, 其余全无效为1 ……

第二章 IO端口地址译码技术

举例:

30h发送命令寄存器CPU31h 传送

数据寄存器

32h

读取

状态寄存器

CPU与I/O端口

二、端口地址编址方式

1.统一编址 端口地址和存储器地址统一编址,即存储器 映射方式。

优点:指令类型多、功能齐全; 端口有较大的编址空间。

缺点:端口占用地址空间,使存储器容量减少; 指令长度及执行时间较长。

二、I/O端口地址分配

1. PC微机I/O地址线有16根,对应的I/O端口编址可达 64K字节。

2. 端口地址译码是采用非完全译码方式,即只考虑了 低10位地址线A0~A9,而没 有考虑高6位地址线 A10~A15。

3. I/0端口地址范围是0000H~03FFH,总共只有1024个 端口。

三、I/O端口地址选用的原则

000~01FH

DMA控制器2

0C0~0DFH

DMA页面寄存器

080~09FH

中断控制器1

020~03FH

中断控制器2

0A0~0BFH

定时器

040~05FH

并行接口芯片(键盘接口) 060~06FH

RT/CMOS RAM

070~07FH

协处理器

0F0~0FFH

表2.2 扩展槽上接口控制卡的端口地址

凡是被系统配置占用了的地址一律不能使用; 对计算机厂家申明保留的地址,不要使用; 用户可使用300H--31FH地址,且最好使用地址开关。

2.3 I/O端口地址译码

一、I/O地址译码电路原理及作用

I/O地址译码电路的作用是把输入的地址和控制 信号进行逻辑组合,从而产生对接口芯片的选择 信号,低电平有效。

双字节地址指令格式:

MOV DX, × × × ×H

O地址译码一、实验目的掌握IO地...

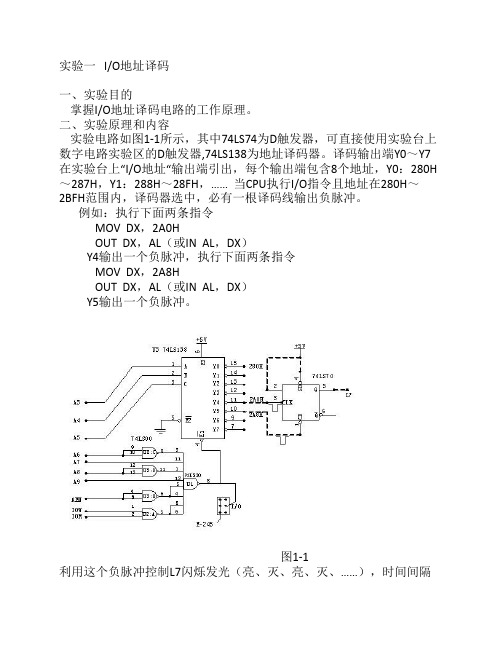

微机原理硬件实验报告实验一I/O地址译码一、实验目的掌握I/O地址译码电路的工作原理。

二、实验原理和内容1、实验电路如图1-1所示,其中74LS74为D触发器,可直接使用实验台上数字电路实验区的D触发器,74LS138为地址译码器。

译码输出端Y0~Y7在实验台上“I/O地址“输出端引出,每个输出端包含8个地址,Y0:280H~287H,Y1:288H~28FH,……当CPU执行I/O指令且地址在280H~2BFH范围内,译码器选中,必有一根译码线输出负脉冲。

利用这个负脉冲控制L7闪烁发光(亮、灭、亮、灭、……),时间间隔通过软件延时实现。

2、接线: Y4/IO地址接 CLK/D触发器Y5/IO地址接 CD/D触发器D/D触发器接 SD/D角发器接 +5VQ/D触发器接L7(LED灯)或逻辑笔三.硬件连线图四.软件流程图五.源程序CODE SEGMENTASSUME CS:CODESTART: MOV DX,2A0HOUT DX,ALCALL DELAYMOV DX,2A8HOUT DX,ALCALL DELAYJMP STARTMOV AX,4C00HINT 21HDELAY PROC NEAR --延时子程序MOV BX,200LOOP1:MOV CX,0FFFFHLOOP2:LOOP LOOP2DEC BXCMP BX,0JNZ LOOP1RETDELAY ENDPCODE ENDSEND START六.实验结果小灯L7出现亮灭交替的现象,通过改变延时子程序BX的值可以改变亮灭的时间间隔。

七.实验总结与心得体会本次实验主要是对延时子程序的编写,由于书上有范例所以比较简单。

实验二简单并行接口一、实验目的掌握简单并行接口的工作原理及使用方法。

二、实验原理和内容1、按下面图简单并行输出接口电路图连接线路(74LS273插通用插座,74LS32用实验台上的“或门”)。

74LS273为八D触发器,8个D输入端分别接数据总线D0~D7,8个Q输出端接LED显示电路L0~L7。

接口多媒体第二章IO端口译码

接口多媒体第二章IO端口译码第二章 I/O端口地址译码技术对设备选择功能是接口电路应具备的基本功能之一,因此,作为进行设备端口选择的I/O端口地址译码电路是每个接口电路中不可缺少的部分。

为此,本章在讨论I/O端口基本概念和I/O端口译码基本原理、基本方法的基础上,着重讨论译码电路的设计。

第一节 I/O端口的寻址方式I/O端口微型计算机系统在过程控制、信息处理、数据通信等方面得到了广泛的应用。

对于不同的需求,可选用不同型号的计算机,同时还需要配置不同的外部设备,以扩展系统的功能。

I/O端口:它是处理器与I/O设备直接通信的地址。

实际应用中,通常把I/O接口(Interface)电路中能被CPU直接访问的寄存器或某些特定器件称之为端口(Port)。

通过端口向接口电路中的寄存器发送命令,读取状态和传送数据,因此,一个接口可以有几个端口,如命令口、状态口和数据口,分别对应于命令寄存器、状态寄存器和数据寄存器。

有的接口包括的端口多(如8255A并行接口芯片有4个端口,8237A芯片有16个端口),有的接口包括的端口少(如825lA、8259A芯片只有两个端口)。

对端口的操作也有所不同,有的端口只能写或只能读,有的既可以写也可以读。

一般,一个端口只能写入或读出一种信息,但也有几种信息共用一个端口的,如8255A的一个命令口可接收两种不同的命令,8259A的一个命令口可接收4种不同的命令。

计算机给接口电路中的每个寄存器分配一个端口,因此,CPU在访问这些寄存器时,只需指明它们的端口,不需指出是什么寄存器。

这样,我们在输人/输出程序中,只看到端口,而看不到相应的具体寄存器。

也就是说,访问端口就是访问接口电路中的寄存器。

所谓I/O的操作指的是指对I/O端口的操作,而不是对I/O设备的操作,即CPU所访问访问的是与 I/O设备相关的端口,而不是 I/O设备本身。

端口地址编址方式如何对端口进行访问呢?这就是所谓的接口的寻址问题。

IO接口译码电路设计

17

A0 A1 A14 A15 IOR IOW AEN

译 码 电 路 译码电路示意图

18

A B C G1 G2A G2B

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

19

20

例 设计端口地址为218H的译码电路

分析 CPU执行IN/OUT指令时,发出端口的地址信号 MOV DX, 218H IN AL, DX 或 OUT DX, AL

6

译码电路的作用

将CPU执行IN/OUT指令发出的地址信号,“翻译”成欲操 作口的选通信号。

解决存储器、I/O设备与CPU连接时地址总线失配问题。 此信号常作为接口内三态门或锁存器的控制信号

接通或断开接口数据线与系统的连接。

7

例 一个输入设备的简单接口电路

PC总线

D7 ~ D0

数据 线

200H

三 态 缓冲器

12

A15~A0

D7~D0

0000 0110 0000 0000

IOW

D7 数据线 ~ 锁存器 PC D0 总 A15 地址线 地址 300H ~ 译码 A0 线 0 与 0 0 IOW 非

输出 设备

MOV DX, 300H

OUT DX, AL

输出设备接口电路,即硬件上保证: 只在CPU执行从300H端口输出数据时, 锁存器处于触发状态,其输出随输入变化, 而CPU执行其它指令时, 锁存器均处于锁存状态, 其输出不随输入变化,

该电路在CPU执行指令 MOV DX, 300H OUT DX, AL 将CPU内AL中的数据送至输出设备 11

PC总线 D7 数据线 ~ 锁存器 D0 A15 地址线 地址 300H ~ 译码 A0 0 与 0 0 IOW 非 CLK

微机原理课程IO地址译码设计报告

郑州科技学院微机原理与接口技术课程设计任务书专业计算机科学与技术班级计科一班学号201215017 姓名夏飞一、设计题目I/O地址译码二、设计任务与要求1、掌握I/O地址译码电路的工作原理。

2、实现走马灯产生8种彩灯(8位LED)的走马灯花样。

3、通过走马灯的设计与制作,深入了解与掌握利用可编程8255A。

三、参考文献(不少于5个)[1] 《微机原理与接口技术》,梁建武,中国水利水电出版社,2010;[2] 《微机原理与接口技术》,雷丽文,北京:电子工业出版社1997;[3] 《微机原理及应用》,周明德,北京:清华大学出版社,1998;[4] 《微机原理与接口技术》,倪继烈,电子科技大学出版社,2004;[5] 雷丽文《微机原理与接口技术》[M] 电子工业出版社,1997.2四、设计时间2015 年12 月5 日至2015 年1 月11 日指导教师签名:2015年 1 月 5日郑州科技学院《微机原理与接口技术》课程设计题目I/O地址译码学生姓名院(系)目录1 引言 (1)2 方案讨论 (3)2.1 方案1 (3)2.2 方案2 (4)2.3 方案3 (5)2.4 个人设计方案 (5)3 设计原理及功能 (7)3.1 设计原理应用芯片8255A介绍 (7)3.2 硬件电路设计 (7)3.2.1 硬件连线 (8)3.3软件电路设计 (10)4 测试与结果测试 (11)4.1 硬件检测 (11)4.2 调试运行 (11)4.3 实验现象与说明 (11)4.4 结果与分析 (11)5 总结 (12)参考文献 (14)附录1 (15)附录2 (16)1 引言经过了为期一周的紧张实训,我和我的搭档完成了微机原理实训的实验电路的搭载与调试。

与此同时开始完成本次课程设计的内容。

我的课程设计的题目的内容比较简单。

目的是掌握I/O 地址译码电路的工作原理,并在此基础上通过8255控制8位单色灯的开关状态,达到以下目的:产生8种彩灯(8位LED)的走马灯花样;通过设计调试较为复杂的汇编语言程序进一步熟练常用会变语言程序设计技术;掌握数码转码换类程序设计的基本方法。

实验01_IO地址译码.

实验一 I/O地址译码一、实验目的掌握I/O地址译码电路的工作原理。

二、实验原理和内容实验电路如图1-1所示,其中74LS74为D触发器,可直接使用实验台上数字电路实验区的D触发器,74LS138为地址译码器。

译码输出端Y0~Y7在实验台上“I/O地址“输出端引出,每个输出端包含8个地址,Y0:280H ~287H,Y1:288H~28FH,…… 当CPU执行I/O指令且地址在280H~2BFH范围内,译码器选中,必有一根译码线输出负脉冲。

例如:执行下面两条指令MOV DX,2A0HOUT DX,AL(或IN AL,DX)Y4输出一个负脉冲,执行下面两条指令MOV DX,2A8HOUT DX,AL(或IN AL,DX)Y5输出一个负脉冲。

图1-1利用这个负脉冲控制L7闪烁发光(亮、灭、亮、灭、……),时间间隔通过软件延时实现。

三、编程提示1、实验电路中D触发器CLK端输入脉冲时,上升沿使Q端输出高电平L7发光,CD端加低电平L7灭。

代码实现;*******************************;;* I/O地址译码 *;;*******************************;outport1 equ 2a0houtport2 equ 2a8hcode segmentassume cs:codestart:mov dx,outport1out dx,alcall delay ;调延时子程序mov dx,outport2out dx,alcall delay ;调延时子程序mov ah,1int 16hje startmov ah,4chint 21hdelay proc near ;延时子程序mov bx,200lll: mov cx,0ll: loop lldec bxjne lllretdelay endpcode endsend start。

第06章 IO接口数据传送及地址译码技术

采用间接寻址,则其指令格式为: 输入指令:IN AL,DX 输出指令:OUT DX,AL 这种间接寻址方式的端口地址为两个字节长, 由DX寄存器间接给出,可寻址64K个端口地址。

优点:

1. I/O口的地址空间独立,且不占用存储

器地址空间。 2.地址线较少,且寻址速度相对较快 。

3.专门I/O指令的使用,使编制的程序清

OUT PORT ,AX

OUT DX ,AX

2)I/O端口访问 设某输出设备的状态READY(高有效)可由端口PORTS中读 出(D7位),数据端口地址为PORTD,编写程序段,将内 存ND

DX ,PORTS AL ,DX AL ,80H ;读取状态字,判断READY=1?

通常有两种寻址方式:存储器映像的 I/O寻址方式和I/O端口单独寻址方式。

一、存储器映像的I/O寻址方式

端口地址与存储器地址统一编址

A15

WR RD

RD

CPU

WR

存储器映像的I/O端口寻址连接方式

优点:

1.端口寻址丰富,且不需要专门的I/O指令。

2.I/O寄存器数目与外设数目不受限制,而只 受总存储容量的限制。 3.读写控制逻辑比较简单。

I/O接口名称

游戏控制卡 并行口控制卡1 并行口控制卡2 串行口控制卡1 串行口控制卡2 原型插件板(用户可用) 同步通信卡1 同步通信卡2 单显MDA 彩显CGA 彩显EGA/VGA 硬驱控制卡 软驱控制卡 PC网卡

端口地址

200H~20FH 370H~37FH 270H~27FH 3F8H~3FFH 2F8H~2FFH 300H~31FH 3A0H~3AFH 380H~38FH 3B0H~3BFH 3D0H~3DFH 3C0H~3CFH 1F0H~1FFH 3F0H~3F7H 360H~36FH

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

该电路在CPU执行指令 MOV DX, 300H OUT DX, AL 将CPU内AL中的数据送至输出设备 11

PC总线 D7 数据线 ~ 锁存器 D0 A15 地址线 地址 300H ~ 译码 A0 0 与 0 0 IOW 非 CLK

输出 设备

OUT指令时序

T1

T2

T3 Tw

T4

执行:

MOV DX, 300H OUT DX, AL

C1 C2 C3 C4 C5 C6 C7 C8 C8 C10 C11 C12 C13 C14 C15 C16 C17 C18

SBHE LA23 LA22 LA21 LA20 LA19 LA18 LA17 MEMR MEMW SD08 SD09 SD10 SD11 SD12 SD13 SD14 SD15

Reset Drv IRQ2 DRQ2 D0 MEMW IOW DACK3 DACK1 DACK0 IRQ7 IRQ5 IRQ3 T/C OSC

2

B1

A1

I/OCHCK D7 D7~D0 8根数据线

B10 MEMR

IOR DRQ3 DRQ1 B20 IRQ6 IRQ4 DACK2 ALE B31

A10

输入 设备

A15 地址线 ~ A0 IOR

地址 译码

0

0

与 0 非

图中译码电路的作用:

只当A15~A0上出现200H时,

该电路在CPU执行指令 (即0000 0010 0000 0000B) MOV DX, 200H 输出0,其他输出1。 IN AL, DX 将输入设备的数据读入CPU内AL中

8

PC

B

A

线 总 线

D

C

36线

MEMCS16 I/OCS16 IRQ10 IRQ11 IRQ12 IRQ13 IRQ14 DACK0 DRQ0 DACK5 DRQ5 ISA DACK6 DRQ6 DACK7 DRQ7 +5V MASTER GND

D1 D2 D3 D4 D5 D6 D7 D8 D8 D10 D11 D12 D13 D14 D15 D16 D17 D18

12

A15~A0

D7~D0

0000 0110 0000 0000

IOW

D7 数据线 ~ 锁存器 PC D0 总 A15 地址线 地址 300H ~ 译码 A0 线 0 与 0 0 IOW 非

输出 设备

MOV DX, 300H

OUT DX, AL

输出设备接口电路,即硬件上保证: 只在CPU执行从300H端口输出数据时, 锁存器处于触发状态,其输出随输入变化, 而CPU执行其它指令时, 锁存器均处于锁存状态, 其输出不随输入变化,源自D7 ~ D0数据 线

三 态 缓冲器

输入 设备

A15 地址线 ~ A0 IOR

地址 200H 译码 0 与 0 0 非

MOV DX, 200H

IN

AL, DX

输入设备接口电路,即硬件上保证: 只在CPU执行从200H端口输入数据时, 三态门处于工作状态,使输入设备的数据送上总线侧, 而CPU执行其它指令时, 三态门均处于高阻状态, 使输入设备的数据线与总线侧断开

PC总线信号

IOR IOW MEMR MEMW

CPU最大模式信号 CPU最小模式信号

IORC IOWC MRDC MWTC RD,M/IO=0 WR,M/IO=0 RD,M/IO=1 WR,M/IO=1

5

I/O 端口的译码

1 2 3 4

译码电路的作用

译码电路的构成 译码电路的设计方法 片内译码和片选译码

总 线

D7 ~ D0

数据 线

三 态 缓冲器

输入 设备

A15 地址线 ~ A0 IOR

地址 200H 译码 0 与 0 0 非

T1 CLK

IN指令时序

T2

T3

Tw T4

执行:

MOV DX, 200H

IN AL, DX

9

A15~A0

D7~ D0 IOR

0000 0010 0000 0000

PC 总 线

10 思考:其他的指令为什么不可以?

例 一个输出设备的简单接口电路

PC总线

D7 数据线 ~ 锁存器 D0 A15 地址线 地址 300H ~ 译码 A0 0 与 0 0 IOW 非

输出 设备

图中译码电路的作用:

只当A15~A0上出现300H时,

(即0000 0011 0000 0000B) 输出0,其他输出1。

3

62 PC

AEN:地址允许信号 PC总线、ISA总线可由CPU或DMA控制器控制,当DMA控制 器控制总线时,它同时产生AEN信号,用于禁止CPU控制总线。 AEN=0,表示CPU控制总线。 AEN=1,表示DMA控制器控制总线

4

读写信号

有时于接口译 常用于接口译 由CPU或DMA 控制器产生,经总线控制器至总线,传送给总线 码电路设计 上的从设备 码电路设计

NUIST

I/O接口译码电路设计

PC 总线

PC总线是IBM PC及 PC/XT机上使 用的总线,又称XT总线或8位ISA 总线。 锁存器、8286发送接收器、8259 中断控制器、8237DMA控制器以 及其他逻辑的重新驱动和组合控 制而形成,又称I/O通道。 它共有62引脚,其中,数据线8 根、地址线20根、控制线21根、 状态线2根,还有时钟、电源、 地线 。

6

译码电路的作用

将CPU执行IN/OUT指令发出的地址信号,“翻译”成欲操 作口的选通信号。

解决存储器、I/O设备与CPU连接时地址总线失配问题。 此信号常作为接口内三态门或锁存器的控制信号

接通或断开接口数据线与系统的连接。

7

例 一个输入设备的简单接口电路

PC总线

D7 ~ D0

数据 线

200H

三 态 缓冲器

I/OCHRDY

AEN A19

A20

A11

A19~A0 20根数据线

A31

A0

见教材p171

ISA总线

ISA(Industry Standard Architecture,工业标准体 系结构)是IBM PC/AT( 80286)机上首先使用,故又 称为AT总线,后被国际标准 化组织确定为国际标准ISA。 它具有16位数据宽度,最高 工作频率位8MHz,数据传输 速率达到16MB/s,地址线24 条,可寻访16M字节地址单元 。ISA总线98芯插槽引脚分布

13 思考:其他的指令为什么不可以?

I/O 端口的译码

1 2 3 4

译码电路的作用

译码电路的构成 译码电路的设计方法 片内译码和片选译码

14

可用门电路、译码器或者两者的组合实现。 门电路: 与门、非门、或门、与非门、或非门等 译码器: 2-4线译码器 3-8线译码器 4-16线译码器