数字系统时序模拟器

fpga中的模拟时钟和数字时钟

fpga中的模拟时钟和数字时钟

在FPGA(现场可编程门阵列)中,模拟时钟和数字时钟是两

种不同的时钟信号。

1. 模拟时钟:

模拟时钟是连续变化的信号,它可以表示连续时间的变化。

在FPGA中,模拟时钟通常用于模拟信号处理(Analog Signal Processing)和模拟电路仿真。

模拟时钟通常以模拟时钟频率

定义,如100MHz或1GHz。

2. 数字时钟:

数字时钟是离散的信号,它用于同步数字电路操作。

在FPGA 中,数字时钟用于同步逻辑电路的操作和数据传输。

数字时钟通常以数字时钟频率定义,如50MHz或100MHz。

在FPGA设计中,模拟和数字时钟起到了不同的作用。

模拟

时钟主要用于处理和模拟连续信号,例如模拟滤波、混频等操作。

数字时钟用于同步FPGA中的数字逻辑电路,确保逻辑

电路按照预期的时序进行操作,并提供数据的正确传输和处理。

通常情况下,FPGA设计中会引入一个或多个数字时钟信号,

以确保系统的正确运行,并使用时钟分频器等技术来将数字时钟信号转换为模拟时钟信号供模拟电路使用。

总之,模拟时钟和数字时钟是FPGA设计中的两种不同的时

钟信号,用于处理连续信号和同步数字电路操作。

时序控制器的使用说明

时序控制器的使用说明时序控制器是一种用于调控电子设备或系统中不同操作的时间顺序的重要工具。

它可以精确地控制各个操作的时间点和持续时间,从而协调各部分之间的协作,并确保系统的正常运行。

本文将为您详细介绍时序控制器的基本原理和使用方法,以及如何利用这一工具实现各种实际应用。

一、什么是时序控制器?时序控制器是一种基于时钟信号的设备,通过计时器和触发器等内部电路,按照预定的时间序列来控制设备中的不同操作。

通过设置不同的参数和触发条件,可以精确地控制每个操作的开始、结束时间以及操作之间的相对顺序。

二、时序控制器的基本原理时序控制器主要由时钟信号、计时器和触发器组成。

时钟信号是时序控制器的基准信号,用来衡量时间的单位。

计时器用来记录经过的时间,当计时器的值达到设定的时间参数时,触发器会被触发,从而执行相应的操作。

三、时序控制器的使用方法1. 设置时钟信号在使用时序控制器之前,首先需要设置时钟信号。

时钟信号通常通过外部的时钟发生器提供,可以根据需要选择不同的时钟频率。

确保时钟信号的稳定性和准确性对于精确控制时间非常重要。

2. 设置计时器参数计时器参数的设置决定了每个操作的持续时间。

根据实际需要,可以设置不同的时间单位和时间周期。

通过调整计时器参数,可以实现对不同操作时间长度的精确控制。

3. 设置触发条件触发条件决定了每个操作何时触发。

可以设置不同的触发条件,如时间触发、外部信号触发等。

根据实际需求,选择适合的触发条件,并将其与计时器进行关联。

4. 编程和测试根据实际需求,编写相应的程序来控制时序控制器的操作。

在编程完成后,进行测试以验证是否实现了预期的时间顺序和操作。

五、时序控制器的应用领域时序控制器广泛应用于各个领域,如工业自动化、通信系统、医疗设备等。

它可以用来控制设备的启动、停止、复位等操作,确保各个操作的时间协调和正确执行。

同时,时序控制器也可以应用于各种实验室研究中,用于控制实验仪器的操作顺序和时间间隔。

FPGA仿真流程

FPGA仿真流程FPGA(Field Programmable Gate Array)是一种可编程的逻辑器件,能够根据用户的需求进行逻辑设计。

为了验证设计的正确性和性能,需要进行FPGA仿真。

FPGA仿真流程包括设计和验证两个主要阶段。

设计阶段:1.确定需求:首先,需要明确设计的功能和性能需求。

这包括功能要求、接口要求、时钟频率等。

2. 开发RTL代码:根据需求,开发RTL(Register Transfer Level)代码。

RTL是一种硬件描述语言,可用于表示各种逻辑电路的功能和行为。

3.进行功能仿真:使用功能仿真工具,对RTL代码进行仿真测试。

功能仿真能够验证设计的功能正确性,例如输入和输出的正确性、电路的数据通路等。

4.优化设计:根据仿真结果,对设计进行分析和优化。

可以通过调整电路结构、改进算法等方式,提高设计的性能和效率。

5.进行时序仿真:时序仿真是对电路的时序特性进行仿真测试,包括时钟频率、信号延迟等。

时序仿真能够验证设计在不同时钟频率下的工作稳定性,并发现可能存在的时序问题。

6.进行可综合性仿真:可综合性仿真是对设计的可综合性进行仿真测试。

可综合性是指RTL代码能否被综合工具转换成逻辑门级的网表文件,从而实现在FPGA中的可编程。

验证阶段:1.进行功能验证:功能验证是使用验证平台或模拟器,对设计进行全面的功能测试。

在验证平台中,可以模拟各种输入和环境条件,对设计进行全面的测试和验证。

2.进行时序验证:时序验证是对设计的时序特性进行验证。

使用时序验证工具,验证电路在不同频率、不同延迟条件下的工作稳定性和正确性。

3.进行电路板级仿真:在电路板级仿真中,将FPGA设计与外部电路、接口进行联合仿真。

通过电路板级仿真,可以验证设计在整个电路环境中的正确性和性能。

4.进行物理布局和布线仿真:通过物理布局和布线仿真,可以验证设计的物理约束和布局是否合理,能否满足时序要求。

5.进行系统级仿真:系统级仿真是对整个系统进行仿真测试。

时序预测_应用实验报告

一、实验背景时序预测(Time Series Forecasting)是机器学习领域的一个重要分支,旨在根据历史数据预测未来的趋势。

随着大数据时代的到来,时序预测在金融、气象、能源、交通等领域得到了广泛的应用。

本实验旨在通过Python编程实现时序预测,并应用于实际场景。

二、实验目的1. 了解时序预测的基本原理和方法。

2. 掌握Python中常用的时序预测库。

3. 应用时序预测方法解决实际问题。

三、实验环境1. 操作系统:Windows 102. 编程语言:Python3.73. 软件库:NumPy、Pandas、Matplotlib、Scikit-learn、Statsmodels四、实验内容1. 数据准备本次实验以某城市一周的气温数据为例,数据来源于国家气象局。

数据包括日期、最高气温、最低气温。

数据格式如下:```日期最高气温最低气温2021-01-01 5 -22021-01-02 6 -3...2021-01-07 4 -1```2. 数据预处理首先,将数据导入Pandas库,并进行数据清洗。

删除含有缺失值的行,并按照日期对数据进行排序。

```pythonimport pandas as pd# 读取数据data = pd.read_csv("temperature.csv")# 删除缺失值data.dropna(inplace=True)# 按日期排序data.sort_values(by="日期", inplace=True)```3. 时序分析方法本次实验采用以下时序分析方法:(1)自回归模型(AR)自回归模型假设当前值与过去若干个时间步的值之间存在线性关系。

通过训练自回归模型,可以预测未来的气温。

```pythonfrom statsmodels.tsa.ar_model import AutoReg# 构建自回归模型ar_model = AutoReg(data["最高气温"], lags=3)ar_result = ar_model.fit()# 预测未来一周的最高气温predicted_temperatures = ar_result.predict(start=len(data),end=len(data)+6)```(2)移动平均模型(MA)移动平均模型假设当前值与过去若干个时间步的移动平均值之间存在线性关系。

FPGA时序优化方法

FPGA时序优化方法FPGA(Field-Programmable Gate Array)是一种可编程逻辑设备,广泛应用于数字电路设计和嵌入式系统开发。

在FPGA设计中,时序优化是提高电路性能和可靠性的重要步骤之一、时序优化旨在减少电路中的时序违例(timing violations),以确保电路能够按照预期的时序要求正常工作。

以下是几种常用的FPGA时序优化方法:1. 约束优化(Constraint Optimization):约束是FPGA设计的重要部分,用于定义电路的时序约束和限制。

优化约束可以帮助FPGA工具准确地分析和优化电路时序。

在优化约束时,可以考虑以下几个方面:时钟约束、延迟约束、时序路径约束等。

2. 时钟优化(Clock Optimization):时钟是FPGA设计中的关键因素之一、时钟优化可以帮助提高电路的最大工作频率。

时钟优化的一些常见方法包括时钟缓冲器的优化、时钟树的优化、时钟路径的缩短等。

此外,使用时钟插入技术(Clock Insertion)可以帮助减少时序违例。

4. 时序分析与检查(Timing Analysis and Verification):时序分析是确保电路满足时序要求的关键步骤。

通过使用时序分析工具,可以检查电路中是否存在时序违例,并找出引起时序违例的原因。

时序分析的一些常见工具包括时序模拟器、时序分析器、时序约束检查工具等。

5. 管脚布局和时序拓扑规划(Pin Placement and Timing Topology Planning):管脚布局和时序拓扑规划是FPGA设计中的关键步骤。

正确的管脚布局和时序拓扑规划可以减少时序路径长度、避免信号交叉干扰等问题。

在进行管脚布局和时序拓扑规划时,可以考虑时钟信号的分布、信号路径的长度等因素。

6. 空间优化(Space Optimization):空间优化是指在有限的FPGA资源上实现尽可能多的功能。

通过合理的资源分配和优化,可以减少电路的面积并提高性能。

一篇很好的关于功能验证、时序验证、形式验证、时序建模的论文

FF-DX半定制/全定制混合设计流程中功能与时序验证摘要随着集成电路的规模和复杂度不断增大,验证的作用越来越重要。

要在较短的时间内保证芯片最终能正常工作,需要将各种验证方法相结合,全面充分地验证整个系统。

FF-DX是一款高性能定点DSP,为了在提升芯片性能的同时,缩短设计周期,降低开发成本,采用了半定制/全定制混合设计的方法,对RTL级代码进行优化改进,对处理器内核的执行单元采用全定制设计实现。

混合设计的复杂性,给验证工作带来了巨大的挑战。

本文针对半定制/全定制混合设计的特点,提出并实现了一套半定制/全定制混合设计流程中功能和时序验证的方法。

论文从模拟验证、等价性验证和全定制设计的功能验证三个方面对FF-DX的分支控制部件进行功能验证。

对于模拟验证中激励的产生,采用了手工生成和伪随机生成相结合的方法,并通过覆盖率评估,使设计的代码覆盖率达到98%。

对于全定制模块,采用了NC-Verilog模拟器和功能模型提取工具TranSpirit相结合的新方法,提高了验证效率。

论文还研究了运用形式验证的方法对RTL级和RTL级以及RTL级和门级网表进行等价性验证。

为了进一步保证RTL级设计和对应的全定制设计模块之间功能的等价性,设计了一个能同时考察两种设计的验证平台,以此来提高工作效率。

论文介绍了FF-DX地址计算部件的时序建模和静态时序分析方法。

在静态时序分析之后,将SDF文件中的延时信息反标到逻辑网表中,通过动态时序验证进一步保证设计的时序收敛。

论文还结合工程任务,设计实现了验证过程中使用的几种辅助工具,大大提高了验证的效率,减少了人工参与带来的失误。

运用上述验证方法对FF-DX功能部件进行验证,取得了较好的效果,缩短了验证周期,提高了验证效率。

主题词:半定制/全定制混合设计,功能验证,形式验证,时序验证,时序模型,静态时序分析,辅助工具ABSTRACTThe complexity and size of the modern VLSI has been increasing dramatically, which present a significant challenge for verification. In order to ensure proper function of the design, various methods need to be used to verify the entire system sufficiently.FF-DX, a high-performance fix-point DSP our group designed, has adopted several design methods to enhance performance, as well as cut down design cycle and lower the cost. The most featured one is what we called blended methodology which mixes semi-custom and full-custom design methods together. Nevertheless, this methodology has led to a huge challenge to verification because of the complexity it brings in. In this dissertation, based on the characteristics of the blended methodology, we propose a flow for functional and timing verification, with the novel idea of combining full-custom and semi-custom verification methods.We verify the branch control function unit in three aspects, simulation verification, equivalence verification, together with functional verification in the full-custom designs.A blended methodology is introduced to generate the testbench for functional verification, which combines both manual and pseudo-random methods, and after evaluation, the code coverage rate is 98%. We also adopt a new methodology of combining the NC-Verilog simulator with functional model extractor TranSpirit for full-custom block ,and it speed up verification efficiency. Besides, we studied equivalence verification, a formal verification methodology which is used for RTL-RTL and RTL-gate design. To guarantee the functional equivalence between RTL design and full-custom design further, we design a testbench which can verify the two designs at the same time and it can greatly improve efficiency.This paper introduces a methodology of timing modeling and STA in FF-DX core. After STA, we backanotate the delay info into the logical netlist, then the timing closure could be assured further by another dynamic timing analysis.To meet the requirement of out project, we design several tools which are used in verification. These tools greatly enhance the efficiency of verification, as well as reduce the man-made errors.We use the above methods to finish verification of the core module of FF-DX, which effectively shorten design cycle, and speed up verification efficiency.Key Words:Semi-custom/Full-custom Mixed Design, Functional Verification, Formal Verification, Timing Verification, Timing Model, Static Timing Analysis, Aiding Tool第一章绪论当今集成电路技术的高速发展以及所取得的巨大成就,使得集成电路系统的规模和复杂度日趋提高,以微处理器为代表的集成电路技术已经对整个社会产生了广泛地影响,成为信息社会的支柱产业之一。

时序实验报告总结

时序实验报告总结时序实验报告总结时序实验是计算机科学中的一项重要实验,旨在通过设计和实现时序电路,来加深对数字电路和时序逻辑的理解。

本文将对我在时序实验中的学习和总结进行分享。

实验一:时序电路设计在时序电路设计实验中,我通过学习时序逻辑的基本概念和设计原理,成功完成了一个简单的时序电路设计。

通过该实验,我深入理解了时钟信号、触发器和状态机的概念,并学会了使用Verilog语言进行时序电路的建模和仿真。

实验二:时序电路优化时序电路优化实验是进一步提高时序电路设计能力的关键一步。

在该实验中,我通过对已有电路的分析和优化,实现了电路的性能提升。

通过优化电路的关键路径,我成功降低了电路的延迟,并提高了电路的工作速度。

实验三:时序电路测试时序电路测试是保证电路正确性的重要环节。

在该实验中,我学会了使用测试向量和模拟器对时序电路进行测试。

通过设计全面的测试用例和检查电路的输出波形,我成功发现和解决了电路中的一些问题,并提高了电路的稳定性和可靠性。

实验四:时序电路综合时序电路综合是将逻辑电路转化为物理电路的过程。

在该实验中,我学会了使用综合工具将Verilog代码转化为门级电路,并通过对综合结果的分析和优化,提高了电路的面积效率和功耗性能。

实验五:时序电路布局与布线时序电路布局与布线是将逻辑电路映射到芯片上的过程。

在该实验中,我学会了使用布局与布线工具对电路进行布局和布线,并通过对布局和布线结果的分析和优化,提高了电路的可靠性和稳定性。

实验六:时序电路验证时序电路验证是验证电路设计的正确性和可靠性的重要环节。

在该实验中,我学会了使用仿真和验证工具对电路进行验证,并通过对验证结果的分析和优化,提高了电路的正确性和稳定性。

通过以上实验,我深入了解了时序电路的设计、优化、测试、综合、布局与布线以及验证等方面的知识和技能。

通过实践和总结,我不仅提高了对时序电路的理解和掌握,还培养了问题解决和创新能力。

时序实验的学习过程中,我还遇到了一些挑战和困惑。

数字序列发生器实训报告

一、引言数字序列发生器是一种能够产生周期性数字序列的电路,广泛应用于数字通信、数字信号处理等领域。

本次实训旨在通过设计和实现一个数字序列发生器,加深对数字电路设计原理和移位寄存器应用的理解,提高动手实践能力。

二、实训目的1. 理解数字序列发生器的工作原理;2. 掌握移位寄存器的应用方法;3. 提高数字电路设计能力;4. 培养团队合作精神。

三、实训内容1. 数字序列发生器原理分析;2. 电路设计;3. 电路仿真与测试;4. 电路板制作与调试。

四、实训过程1. 数字序列发生器原理分析数字序列发生器由移位寄存器、计数器、逻辑门电路等组成。

其基本原理是:通过移位寄存器存储一个数字序列,在移位脉冲的作用下,将序列逐位右移或左移,从而产生周期性数字序列。

2. 电路设计本次实训设计一个序列循环长度为16的数字序列发生器。

设计步骤如下:(1)确定输入序列:根据实际需求,自定义输入序列,如1010101010101010。

(2)选择移位寄存器:选用4个74LS194移位寄存器,实现并行输入、串行输出。

(3)设计计数器:使用一个74LS161计数器,实现计数功能。

(4)设计逻辑门电路:利用逻辑门电路实现序列的顺序与逆序输出。

(5)绘制电路原理图:根据以上设计,绘制数字序列发生器的电路原理图。

3. 电路仿真与测试(1)电路仿真:使用Multisim软件对电路原理图进行仿真,验证电路功能是否正常。

(2)电路测试:搭建实际电路,进行功能测试,观察输出序列是否符合预期。

4. 电路板制作与调试(1)制作电路板:根据电路原理图,制作电路板。

(2)焊接元件:将74LS194、74LS161、逻辑门电路等元件焊接在电路板上。

(3)调试电路:检查电路连接是否正确,进行功能调试,确保电路工作正常。

五、实训结果与分析1. 仿真结果通过Multisim软件仿真,验证了电路原理的正确性。

在移位脉冲的作用下,输出序列符合预期。

2. 实际电路测试结果搭建实际电路,进行功能测试,输出序列符合预期,验证了电路设计的正确性。

时钟模拟课件

总结词

未来时钟模拟技术的发展将更加注重精度、速度和效率, 同时也将不断探索新的应用领域和发展方向。

要点二

详细描述

随着电子系统的发展和对时钟信号要求的不断提高,未来 时钟模拟技术将不断进步和完善。同时,新的应用领域和 市场也将不断涌现,为时钟模拟技术的发展提供更多的机 会和挑战。

06 时钟模拟的实际案例分析

在实时操作系统中,调度和 任务管理是非常关键的要素 。通过时钟模拟,研究人员 可以验证实时操作系统的调 度算法和任务管理的正确性 和可靠性,确保系统在实时 任务处理中能够高效运行。

实时操作系统仿真的时钟模 拟案例主要采用实时操作系 统(如RTLinux或VxWorks )和仿真软件(如RTEMS或 Wind)进行模拟。

在实时操作系统(RTOS)仿真中,时钟模拟也是一项关键 技术。RTOS是实时应用程序的核心,需要精确控制任务调 度和时间管理。

通过时钟模拟,可以模拟RTOS在不同时钟条件下的行为 ,对RTOS进行测试和验证。这有助于确保RTOS的正确性 和可靠性,提高实时应用程序的性能和稳定性。

通信系统仿真

通信系统仿真中,时钟模拟同样发挥着重要作用。通信系统通常需要高度同步的时钟信号来确保数据 传输的可靠性和性能。

02

时钟模拟可以模拟各种类型的时 钟信号,如晶体振荡器、石英振 荡器等,以及各种时钟源的特性 ,如频率、占空比、偏置等。

时钟模拟的重要性

时钟模拟在电子系统设计和测试中具有重要意义,特别是在数字电路和数字信号处 理中。

通过时钟模拟,工程师可以预测和验证电路的行为,以及在不同时钟源和时钟配置 下的性能。

详细描述

开发人员使用嵌入式操作系 统进行时钟管理和任务调度 ,然后通过仿真软件进行时 钟模拟。仿真软件能够模拟 嵌入式系统的运行环境和行 为,帮助开发人员发现系统 中的问题并进行优化。

verilog delay语句

verilog delay语句Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

Verilog 中的延迟是指指定每个语句的执行时间。

延迟使用的单位是时间或时间精度。

在Verilog中,有几种不同类型的延迟,包括延迟模拟和延迟综合。

延迟模拟(Delay Simulation)是利用时钟周期和延迟来模拟数字系统的行为。

当模拟在仿真器中运行时,每个语句的执行时间由仿真器的时钟周期控制。

Verilog使用两种类型的延迟模拟:时间延迟(Time Delay)和时间精度延迟(Time Precision Delay)。

时间延迟是用时间单位指定的延迟,例如10ns,100ps等。

时间延迟指定了在模拟期间执行语句的时间数量。

例如,一个语句的延迟为10ns,意味着在模拟器中模拟的每个时钟周期,该语句将在10ns后执行。

时间延迟的单位通常是纳秒(ns)、皮秒(ps)、毫秒(ms)或微秒(us)等。

时间精度延迟是使用时间精度值和数字值来指定的。

时间精度是在模块、包含块或模拟期间指定的,它指定了数字表示的最小时间单位。

语句的延迟是以数字值表示的,乘以时间精度值。

例如,如果时间精度是10ns,语句的延迟是5,那么实际延迟为5乘以10ns,即50ns。

时间精度延迟允许更灵活地控制语句的执行时间,但需要根据时钟周期进行转换,因此会增加模拟器的复杂性。

延迟综合(Delay Synthesis)是指将Verilog代码转换为硬件电路的过程。

在延迟综合期间,延迟用于指定电路中不同组件之间的时间关系。

Verilog使用两种类型的延迟综合:传输延迟(Transport Delay)和嵌入延迟(Inertial Delay)。

传输延迟是指信号从一个逻辑门到另一个逻辑门的延迟。

在传输延迟模型中,延迟是在源信号的高或低转换到目标信号的高或低之间测量的。

传输延迟表示信号在电路中传播所需的时间。

嵌入延迟是指信号在一段时间内保持稳定状态所需的最小时间。

PLC调试工程师必备的个调试工具

PLC调试工程师必备的个调试工具PLC调试工程师必备的调试工具PLC(可编程逻辑控制器)调试工程师是负责开发和调试PLC系统的专业人员,他们在工作中需要使用各种调试工具来确保PLC系统的正常运行。

本文将介绍几种PLC调试工程师必备的调试工具,帮助他们更好地完成工作任务。

一、逻辑分析仪逻辑分析仪是PLC调试工程师必备的重要工具之一。

它能够对PLC系统的信号进行监测和分析,帮助工程师找出系统中可能存在的问题。

逻辑分析仪可以捕获和显示信号的时序图,使工程师能够清晰地了解信号的变化过程。

通过分析这些时序图,工程师可以判断PLC 系统是否正常工作,以及是否存在信号冲突或传输错误等问题。

二、模拟器模拟器是另一个PLC调试工程师必备的调试工具。

它能够模拟PLC系统中各个输入和输出设备的工作状态,使工程师能够在电脑上进行虚拟的调试和测试。

通过模拟器,工程师可以快速定位和解决PLC系统中的问题,而无需实际连接和操作硬件设备。

模拟器还能够提供实时的监测和反馈功能,帮助工程师更好地理解系统的运行原理和逻辑。

三、编程软件编程软件是PLC调试工程师必备的另一种调试工具。

不同厂家的PLC系统通常使用不同的编程语言和开发环境,因此工程师需要根据具体PLC系统的要求选择相应的编程软件。

编程软件具有编写、编辑和调试PLC程序的功能,能够帮助工程师更好地掌握系统的逻辑和功能。

通过编程软件,工程师可以对PLC程序进行修改和优化,并及时调试和测试程序的正确性和稳定性。

四、信号发生器信号发生器是PLC调试工程师常用的调试工具之一。

它能够产生各种不同的电信号和脉冲信号,用于模拟和测试PLC系统的输入和输出信号。

通过信号发生器,工程师可以模拟输入信号的变化和干扰,以及输出信号的响应和处理过程,从而检验PLC系统的稳定性和可靠性。

信号发生器通常配备有多种输出方式和参数调节功能,使工程师能够根据具体情况进行灵活的调试和测试。

五、测量仪器测量仪器是PLC调试工程师不可或缺的调试工具之一。

计算机硬件设计中的时序分析方法

计算机硬件设计中的时序分析方法时序分析是计算机硬件设计过程中非常重要的一环。

它可以帮助设计师确保系统中各个元件的工作时序满足预期的要求,从而保证系统的正确性和稳定性。

本文将介绍几种常见的时序分析方法,包括静态时序分析、动态时序分析以及时钟域分析。

一、静态时序分析静态时序分析是在不考虑信号传输延迟和时钟周期的情况下进行的时序分析。

它主要依赖于电路元件的逻辑关系和布局设计来进行分析。

在进行静态时序分析时,需要提供设计的电路原理图、信号路径以及逻辑关系等信息。

常用的静态时序分析工具包括VHDL等硬件描述语言,它们可以帮助设计师对电路进行建模、仿真和验证,从而找到潜在的时序问题。

静态时序分析可以帮助设计师发现电路中的时序冲突、时序违约和时序不确定性等问题。

通过对电路进行静态时序分析,设计师可以提前预测并解决可能出现的时序问题,从而减少后期测试的工作量和风险。

二、动态时序分析动态时序分析是指考虑信号传输延迟和时钟周期的情况下进行的时序分析。

它主要依赖于电路的时钟边沿和时钟周期等信息进行分析。

在进行动态时序分析时,需要提供设计的时钟频率、延迟模型以及电路中的时钟约束等信息。

常用的动态时序分析工具包括模拟器和时序分析器等。

动态时序分析可以帮助设计师检测电路中的时序故障、时序偏差和时序违规等问题。

通过对电路进行动态时序分析,设计师可以模拟真实的工作环境,准确评估电路的时序性能,从而提前发现并解决时序问题。

三、时钟域分析时钟域分析是指对电路中不同时钟域的信号传输进行分析。

在现代的计算机硬件设计中,通常存在多个时钟域,每个时钟域都有自己的时钟信号和时钟延迟特性。

时钟域之间的信号传输需要进行专门的时序分析,以保证信号的正确传递和同步。

时钟域分析可以帮助设计师解决时钟间的异步问题、时序冲突和时序不一致等。

通过对不同时钟域的信号传输进行分析,设计师可以确定时钟域之间的接口逻辑,优化时钟插入和同步方法,确保电路的正常工作。

电子设计自动化技术内容讲解

电子设计自动化技术内容讲解1. 引言电子设计自动化技术(Electronic Design Automation,简称EDA)是一种利用计算机技术辅助进行电子系统设计的技术。

它包括了电子设计自动化软件工具的开发、集成和应用。

EDA技术的发展,极大地提高了电子系统的设计效率和成功率。

本文将对EDA技术进行详细的讲解。

2. EDA技术的分类EDA技术可以根据其在电子系统设计中的应用领域进行分类,主要包括:2.1 电路设计自动化技术电路设计自动化技术是EDA技术中最重要的一个领域,其主要用于集成电路(Integrated Circuit,简称IC)的设计和验证。

这些工具包括原理图编辑器、电路模拟器、布局设计工具等。

电路设计自动化技术的发展,极大地提高了IC的设计效率和可靠性。

2.2 系统级设计自动化技术系统级设计自动化技术主要用于复杂电子系统的设计和验证。

这些工具可以从高层次的角度对电子系统进行建模、分析和仿真。

系统级设计自动化技术的应用使得电子系统的设计更加灵活、可靠和高效。

2.3 物理设计自动化技术物理设计自动化技术主要用于集成电路的物理设计和制造。

这些工具包括布局布线工具、印刷电路板设计工具等。

物理设计自动化技术的发展,使得集成电路的布局布线更加紧凑、稳定和可靠。

2.4 验证和测试技术验证和测试技术是EDA技术中非常重要的一个领域,它主要用于验证和测试电子系统和芯片的性能和可靠性。

这些工具包括功能模拟器、时序模拟器、测试生成器等。

3. EDA技术的应用EDA技术在电子系统设计中的应用十分广泛,主要包括以下几个方面:3.1 集成电路设计EDA技术在集成电路设计中的应用非常广泛。

通过使用EDA工具,设计工程师可以方便地进行电路的建模、仿真和验证,从而大大提高了集成电路的设计效率和可靠性。

3.2 PCB设计EDA技术在PCB设计中也有重要应用。

设计工程师可以使用EDA工具进行印刷电路板的布局布线,以及信号完整性的验证和仿真。

电力系统仿真软件介绍

电力系统仿真软件介绍电力系统仿真软件是一种可以模拟电力系统运行和故障情况的软件。

在电力系统工程中,电力系统仿真软件拥有广泛的应用,可以用于电力系统的规划、设计、运行和故障诊断等方面。

本文将介绍几种常见的电力系统仿真软件。

PSS/EPSS/E(Power System Simulator for Engineering)是一款由美国General Electric公司开发的电力系统仿真软件。

PSS/E提供了包括潮流、短路、稳定性和动态分析等在内的多种仿真模型,易于使用且具有可扩展性。

PSS/E的最新版本支持计算大电网的稳定性和控制。

ATPATP(Alternative Transients Program)是一款由美国Electric Power Research Institute公司开发的电力系统仿真软件。

ATP主要用于模拟电力系统的暂态过程,包括瞬态稳定性、过电压和电磁暂态等。

ATP的特点是承载能力强,可以处理大规模系统模型,适用于复杂的电力系统场景。

EMTPEMTP(Electromagnetic Transients Program)是一款由瑞士电力公司和瑞士联邦理工学院合作开发的电力系统仿真软件。

EMTP主要用于模拟电力系统的电磁瞬态过程,包括雷电、开关操作、过电压和电磁干扰等。

EMTP可处理数百个设备并同时运行故障模拟。

PSASPPSASP(Power System Analysis Software Package)是一款由美国Power Technologies公司开发的电力系统仿真软件。

PSASP是一个功能齐全的全功率电力系统分析软件,提供了多种电网模型和计算方式。

PSASP可以进行短路、潮流、稳定性和动态分析等多种电力系统仿真。

PSCADPSCAD(Power System Computer Aided Design)是一款由加拿大Manitoba Hydro公司开发的电力系统仿真软件。

数字系统时序关系

数字系统时序关系数字系统中的时序关系是指数字信号在不同时刻之间的相对顺序和时序关系。

在数字系统设计和分析中,时序关系是至关重要的,它直接影响到数字电路的功能和性能。

本文将探讨数字系统的时序关系及相关概念。

1. 时钟信号时序关系中,时钟信号起着重要的作用。

时钟信号是一个周期性的信号,用于同步数字电路中各个组件的操作。

时钟信号决定了数字系统中信号的采样、传输和处理的时间顺序。

2. 时钟周期与频率时钟信号具有一定的周期性,称为时钟周期。

时钟周期是一个完整时钟信号周期的持续时间。

频率表示单位时间内时钟信号的发生次数,它是时钟周期的倒数。

3. 时序约束在数字电路设计中,时序约束是指某些信号在特定的时间范围内满足一定的条件。

时序约束通常包括时钟到达时间、时钟占空比、时序延迟等。

通过合理的时序约束,可以保证数字系统的正确性和稳定性。

4. 时钟同步和异步时钟信号可以分为同步和异步两种不同的方式。

同步时钟是由系统内部的时钟发生器产生的,所有的组件都以相同的时钟信号为基准进行操作。

异步时钟则是通过各个组件自己的时钟发生器产生的,各个组件的操作相互不受限制。

5. 时序逻辑与组合逻辑时序逻辑和组合逻辑是数字系统中常见的两种逻辑电路。

组合逻辑是基于输入信号直接生成输出信号,不涉及时序关系。

而时序逻辑则要求在特定的时钟信号下进行状态更新和输出生成。

6. 时序分析与验证在数字系统设计中,时序分析和验证是确保系统正确性和性能的重要手段。

时序分析是通过对系统中各个信号的时序关系进行分析,评估电路的时序要求是否满足。

时序验证则是使用模拟器或验证工具对设计进行验证,确保电路在不同条件下都能正常运行。

总结:数字系统中的时序关系是设计和分析的关键要素,它直接影响着数字电路的功能和性能。

通过合理设置时钟信号、时序约束和采用适当的时序分析和验证方法,可以确保数字系统的正确性和稳定性。

在数字系统设计和分析过程中,时序关系的理解和应用是非常重要的。

时序控制器说明书

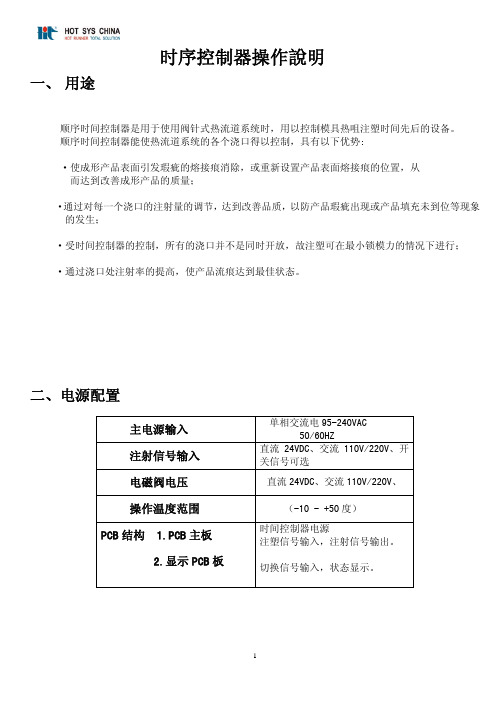

时序控制器操作說明一、 用途顺序时间控制器是用于使用阀针式热流道系统时,用以控制模具热咀注塑时间先后的设备。

顺序时间控制器能使热流道系统的各个浇口得以控制,具有以下优势:·使成形产品表面引发瑕疵的熔接痕消除,或重新设置产品表面熔接痕的位置,从而达到改善成形产品的质量;·通过对每一个浇口的注射量的调节,达到改善品质,以防产品瑕疵出现或产品填充未到位等现象的发生;·受时间控制器的控制,所有的浇口并不是同时开放,故注塑可在最小锁模力的情况下进行;·通过浇口处注射率的提高,使产品流痕达到最佳状态。

二、电源配置主电源输入单相交流电95-240VAC50/60HZ注射信号输入直流24VDC、交流110V/220V、开关信号可选电磁阀电压直流24VDC、交流110V/220V、操作温度范围(-10 - +50度)PCB结构 1.PCB主板 2.显示PCB板时间控制器电源注塑信号输入,注射信号输出。

切换信号输入,状态显示。

三、面板操作說明A —蜂鸣器B —A模式指示灯C —B模式指示灯D —显示关闭时间E —显示开启时间F —关闭指示灯G —打开指示灯H —待机指示灯J —设定值调节功能键(上)K —设定值调节功能键(下)I —手动键L —参数设置键M —电源开关键N —模式信息对照表二.时序控制器操作步骤。

1.按ON/OFF键打开时序控制卡电源,2.功能参数设置,1>A/B模式设置按住MODE SET键1秒进入参数设置,上端显示器会显示A-B,下端显示器显示模式A或B,通过按上键或下键可调整为B模式或A模式;按按住MODE SET 键1秒可退出参数设置。

2>0.1与0.01秒定时分辨率选择按住MODE SET键1秒进入参数设置,上端显示器会显示A-B,下端显示器显示模式A或B,然后再点击MODE SET键1次,此时上端显示器会显示dot, 下端显示器分辨率0.01或0.1,通过按上键或下键可调整分辨率为0.1或0.01;按住MODE SE T键1秒可退出参数设置。

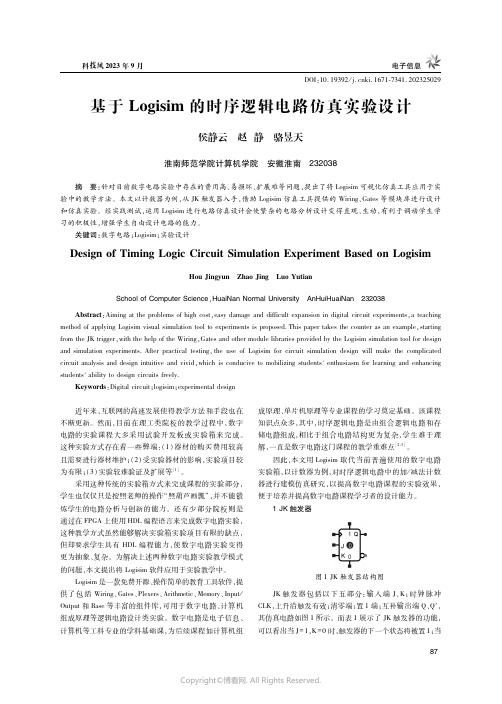

基于Logisim的时序逻辑电路仿真实验设计

电路的实验课程大多采用试验开发板或实验箱来完成# 储电路组成"相比于组合电路结构更为复杂"学生难于理

这种实验方式存在着一些弊端!&$'器材的购买费用较高 解"一直是数字电路这门课程的教学重难点,)2(-#

且需要进行器材维护%&)'受实验器材的影响"实验项目较 因此"本文用@V[/F/X取代当前普遍使用的数字电路

与经典理论之间的联系与区别"从而激发同学们夯实理论 知识体系和解决实际问题的创新性思维能力,4- #

&总结 本文对时序逻辑电路中的计数器进行探讨"先从功能 真值表$卡诺图$特征方程$状态转换图$驱动表等五个方 面将计数器结构分析清楚"然后借助@V[/F/X仿真软件中 的EH触发器和逻辑门等模块进行设计和仿真实验# 经实 践教学验证"采用@V[/F/X软件进行电路仿真不仅简单直 观"而且能够降低实验的成本"丰富教学方法和手段# 此 外"通过设计性实验"还可以帮助学生更好地理解电路设 计知识"提高学生的学习兴趣"改善教学质量#

组成原理等逻辑电路设计类实验# 数字电路是电子信息$ 其仿真电路如图$ 所示# 而表$ 展示了EH触发器的功能"

计算机等工科专业的学科基础课"为后续课程如计算机组 可以看出当Eh$"Hh% 时"触发器的下一个状态将被置$%当

*)

Copyright©博看网. All Rights Reserved.

电子信息

将保持输出不变"即保持% 不变%aa)

的时钟是J$

由于 "

J$

没有变化"所以J) 也保持% 不变"电路由%%%%%%%$# 再

数字系统时序测试

数字系统时序测试数字系统时序测试是一项关键的测试方法,用于验证数字电路的时序性能。

时序测试是保证数字系统正确运行的关键环节,因此合适的时序测试方案和测试方法对于确保系统的可靠性至关重要。

1. 时序测试的意义时序测试是验证数字系统中各个模块按照正确的时序进行工作的方法。

它通过测试输入和输出信号之间的时序关系,确认系统在不同时间点上的状态是否符合设计预期。

时序测试可以发现时钟抖动、冒险现象、编码错误等问题,从而提高系统的可靠性和稳定性。

2. 时序测试的基本原理在数字系统中,时序的正确性取决于时钟信号的稳定性和各个模块之间的信号传输时延。

时序测试通过一系列的测试模式和时钟信号,确保系统在各种条件下都能按照预期的时序进行工作。

常用的时序测试方法包括纯随机测试、伪随机测试和时钟缩放测试等。

3. 时序测试的方法3.1 纯随机测试纯随机测试是一种基于随机输入信号的测试方法,通过随机生成输入模式,检测系统在各种不确定的情况下的时序性能。

纯随机测试可以全面覆盖系统的各种操作模式,但测试时间较长且不能保证覆盖所有可能的故障。

3.2 伪随机测试伪随机测试是一种基于伪随机序列的测试方法,通过生成特定的伪随机序列来进行测试。

与纯随机测试相比,伪随机测试具有更好的覆盖率和测试效率,能够在较短的时间内发现潜在的时序问题。

3.3 时钟缩放测试时钟缩放测试是一种通过改变时钟信号的频率和占空比来测试时序性能的方法。

通过增加或减小时钟频率,可以测试系统在不同工作条件下的时序可靠性。

时钟缩放测试可以有效地发现时钟频率相关的问题,如时钟抖动、时钟偏移等。

4. 时序测试工具为了方便进行时序测试,现代数字系统设计中常常使用专业的时序测试工具。

这些工具可以自动生成不同的测试模式和测试序列,能够全面、快速地检测系统的时序性能,并生成详细的测试报告供分析使用。

5. 时序测试的实践应用时序测试在数字系统的设计和验证过程中起着重要的作用。

通过合理选择测试方法和工具,可以提高测试的效率和准确性,从而提高系统的可靠性和稳定性。

时序控制器

时序控制器

时序控制器是一种用于控制特定任务在特定时序下执行的装置。

它在各种工程

和科学领域中都被广泛应用,例如在交通信号灯系统、工业自动化设备、数字电子电路等方面都可以看到时序控制器的身影。

概述

时序控制器的主要功能是根据预先设定的时间顺序来控制各种设备或系统的操作。

它通常由时钟模块、计时器、逻辑控制器等组成。

时序控制器能够准确地控制每个步骤的执行时间,并且可以根据需要进行灵活的调整和修改。

工作原理

时序控制器通过接收外部信号或内部时钟模块产生的时序信号来执行控制任务。

它会根据预设的逻辑控制程序依次执行各个步骤,确保任务按照既定的时间序列进行。

时序控制器通常包含多个独立的定时器,可以同时控制多个任务的执行。

应用领域

时序控制器在各种领域中都有广泛的应用。

在工业自动化领域,时序控制器可

以用于控制生产线上各种设备的协调运行,提高生产效率和质量。

在交通领域,时序控制器被用来控制交通信号灯的变换,确保车辆和行人的安全通行。

未来发展

随着科技的不断发展,时序控制器也在不断创新和完善。

未来的时序控制器可

能会更加智能化,能够根据外部环境和需求进行自动调整和优化。

同时,时序控制器的精准度和可靠性也将得到进一步提升,以应对更加复杂和多样化的任务需求。

结论

时序控制器作为一种重要的控制装置,在现代工程和科学应用中发挥着关键作用。

它的准确性、稳定性和灵活性使其成为各种系统中不可或缺的组成部分。

随着技术的进步,时序控制器将不断演进和完善,为人类创造更多便利和效率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字系统时序模拟器

数字系统时序模拟器是一种可以模拟和分析数字系统中的时序电路

的工具。

它可以模拟时钟信号、寄存器、触发器等组成的电路,并且

能够准确地模拟电路中各个信号的时序行为。

数字系统时序模拟器在

数字电路设计和验证中起着重要的作用,能够帮助设计者更好地理解

和调试电路。

一、数字系统时序模拟器的工作原理

数字系统时序模拟器通过模拟时钟信号的变化和触发器的状态转换,来准确地模拟和分析数字系统中的时序行为。

它通过内部的逻辑运算

和状态转换机制来实现对时序电路的模拟,能够模拟电路运行过程中

各个信号的变化和相互之间的影响。

数字系统时序模拟器通常包括时钟发生器、寄存器、触发器等模块。

时钟发生器产生一个连续的时钟信号,用于控制电路中各个触发器和

寄存器的状态转换。

寄存器用于存储输入信号和中间计算结果,而触

发器则是存储和控制电路状态的关键元件。

二、数字系统时序模拟器的应用场景

数字系统时序模拟器广泛应用于数字电路设计和验证的各个阶段。

它可以用于电路设计的初步验证,帮助设计者快速评估和调试电路的

功能和性能。

同时,它也可以用于电路的仿真验证,通过模拟电路运

行过程,分析和检测电路中的故障和错误。

数字系统时序模拟器还可以用于教学和学术研究。

在数字系统课程中,学生可以通过使用时序模拟器,更好地理解和体验数字电路中的时序行为。

在学术研究中,研究人员可以利用时序模拟器进行实验和分析,探索新的电路设计和验证方法。

三、数字系统时序模拟器的特点与优势

1. 准确性:数字系统时序模拟器可以准确地模拟和分析电路中信号的时序行为,可以帮助设计者发现和解决电路中的时序问题。

2. 可视化:时序模拟器通常提供直观的图形界面,可以实时显示电路中信号的变化和状态的转换,方便设计者理解和调试电路。

3. 灵活性:时序模拟器支持多种模拟和分析方式,可以根据需要选择不同的仿真算法和参数设置,满足不同场景下的需求。

4. 效率性:时序模拟器可以快速模拟和分析大规模复杂电路,提高设计和验证效率,减少电路设计周期。

四、数字系统时序模拟器的发展和趋势

随着数字电路设计和验证需求的不断增加,数字系统时序模拟器也在不断发展和完善。

目前,已经有许多商业和开源的时序模拟器可供选择,提供了更加强大和智能的功能。

未来,数字系统时序模拟器有望在以下几个方面得到进一步发展:

1. 高性能:随着硬件技术的发展,数字系统时序模拟器将会越来越强大,能够模拟和分析更大规模复杂的电路。

2. 多领域应用:时序模拟器不仅仅在数字电路设计和验证领域有应用,还可以扩展到其他领域,如通信系统、嵌入式系统等。

3. 人工智能:借助人工智能技术,数字系统时序模拟器可以实现更高级的仿真和分析功能,提供更加智能化的设计和验证支持。

总结:

数字系统时序模拟器是一种重要的工具,在数字电路设计和验证中发挥着重要作用。

它通过模拟和分析电路中的时序行为,帮助设计者更好地理解和调试电路。

随着技术的不断发展,数字系统时序模拟器将会变得更加强大和智能,为电路设计和验证提供更好的支持。