基于FPGA的多核信号处理平台的实现

OFDM基带处理器芯片设计与FPGA实现

OFDM基带处理器芯片设计与FPGA实现OFDM(正交频分复用)技术是一种高效的多载波调制技术,常用于无线通信系统中,如Wi-Fi、4GLTE等。

OFDM技术通过将信号分割成多个不重叠的子载波,并在每个子载波上进行独立调制和解调,提高了传输效率和频谱利用率。

OFDM基带处理器芯片的设计与FPGA实现是实现OFDM系统的关键环节。

1.子载波生成和调制:OFDM系统中的信号由多个子载波组成,每个子载波上进行调制。

基带处理器芯片需要能够生成这些子载波,并进行调制。

通常使用快速傅里叶变换(FFT)来生成子载波,并在频域上进行调制,将数据映射到子载波上。

2.信道编码和解码:OFDM系统对信号进行差错控制,通常使用纠错编码技术,如卷积编码和RS编码。

基带处理器芯片需要实现这些编码和解码算法,以提高系统的可靠性和抗干扰性。

3.调制和解调算法:OFDM系统中使用的调制和解调算法有许多种,如QAM、PSK等。

基带处理器芯片需要实现这些算法,通过调制将数字信号转换为模拟信号,并通过解调将模拟信号转换为数字信号。

4.功率控制和均衡:OFDM系统中需进行功率控制,使各个子载波的功率尽可能平均。

此外,OFDM系统还需进行均衡处理,以消除信道带来的各种失真。

基带处理器芯片需要实现这些功能,保证系统的性能。

FPGA(现场可编程逻辑门阵列)是一种可编程数字逻辑电路的芯片,广泛应用于嵌入式系统领域。

FPGA可以通过编程来实现不同的数字逻辑电路,因此可用来实现OFDM基带处理器芯片。

使用FPGA实现OFDM基带处理器芯片有以下几个优势:1.灵活性:FPGA可以根据需要进行编程,可以实现不同的OFDM调制和解调算法。

与固定的硬件实现相比,FPGA具有更好的灵活性。

2.功耗低:FPGA芯片通常具有较低的功耗,可以满足OFDM系统对功耗的要求。

此外,FPGA也可以通过电源管理技术降低功耗。

3.高性能:FPGA具有较高的计算性能和数据处理能力,可以满足OFDM系统对实时性和吞吐量的要求。

基于FPGA的高效计算平台设计与优化

基于FPGA的高效计算平台设计与优化随着信息技术的不断发展,计算机的性能越来越强大,能够处理的数据量越来越大,但是在面对一些特殊的计算任务时,如人工智能、数据挖掘、图像处理等,传统的计算机结构已经不能满足需求,需要更加高效的计算平台来支持这些工作。

而基于FPGA的高效计算平台正是这方面的一个有力的解决方案。

FPGA是一种可编程逻辑门阵列,通过对其内部逻辑单元进行编程,可以实现不同的功能。

因此FPGA具有非常强的可扩展性和灵活性,能够满足各种不同的应用场景需求。

FPGA计算平台的优势在于它能够高效地处理并行计算任务,同时能够实现低功耗的计算过程。

在设计FPGA计算平台时,需要考虑各种因素,如计算任务的特点、可用资源的数量和功耗等。

从计算任务的特点来看,如果任务需要大量的并行计算,则可以采用多个FPGA设备进行计算,从而提高计算效率。

在设计时,需要考虑不同FPGA设备之间的数据传输,以及如何协调不同设备的工作,从而避免数据丢失和错误。

同时,还需要考虑具体任务使用的资源量,从而合理配置FPGA设备资源,避免浪费和不足。

除了任务的特点之外,FPGA计算平台设计还需要考虑功耗问题。

在设计时,需要考虑如何降低功耗,以避免过高的运行成本。

一种方法是通过切断不必要的点位或时钟资源来降低功耗。

同时,还可以采用低功耗的设计策略,这样能够使整个平台在运行时能够更加高效地使用能源。

在优化FPGA计算平台时,需要考虑的因素很多。

其中最重要的因素是将计算任务映射到FPGA硬件上。

由于FPGA计算平台是可编程的,因此可以对其进行定制化编程,将计算任务转换为适合FPGA硬件实现的形式。

当然,在实际应用中,可能需要对任务进行适当的修改和调整,以适应FPGA硬件的特点。

此外,还需要考虑FPGA编程语言的选择。

目前,常用的FPGA编程语言有Verilog和VHDL两种。

因为两者各有特点,在具体应用时需要结合实际需求选择不同的编程语言。

《基于FPGA的多核处理器系统的研究与设计》范文

《基于FPGA的多核处理器系统的研究与设计》篇一一、引言随着科技的快速发展,处理器性能的需求不断提升,传统单核处理器已经难以满足日益增长的计算需求。

因此,多核处理器系统成为了研究的热点。

本文以基于FPGA(现场可编程门阵列)的多核处理器系统为研究对象,对其进行了详细的研究与设计。

二、研究背景及意义FPGA作为一种可编程的硬件设备,具有高度的并行性、灵活性和可定制性,因此被广泛应用于高性能计算、信号处理等领域。

而多核处理器系统则通过集成多个处理器核心,实现了更高的计算性能和更快的处理速度。

将FPGA和多核处理器系统相结合,可以构建出高性能、高灵活性的多核处理器系统,对于提高计算性能、降低功耗、增强系统稳定性等方面具有重要的意义。

三、FPGA多核处理器系统的设计(一)系统架构设计基于FPGA的多核处理器系统主要由多个FPGA芯片组成,每个FPGA芯片上集成了多个处理器核心。

系统采用共享内存的方式,实现了各个处理器核心之间的数据交换和通信。

此外,系统还包含了控制模块、接口模块等部分,以实现系统的整体控制和外部接口的连接。

(二)处理器核心设计处理器核心是FPGA多核处理器系统的核心部分,其设计直接影响到整个系统的性能。

在处理器核心设计中,需要考虑指令集设计、数据通路设计、控制单元设计等方面。

指令集设计需要考虑到指令的兼容性、可扩展性和执行效率;数据通路设计需要考虑到数据的传输速度和带宽;控制单元设计则需要考虑到处理器的控制流程和时序。

(三)系统通信设计系统通信是FPGA多核处理器系统中非常重要的一部分,它涉及到各个处理器核心之间的数据交换和通信。

在系统通信设计中,需要考虑到通信协议的设计、通信接口的选择、通信速度和带宽等方面。

常用的通信协议包括总线协议、消息传递协议等,需要根据具体的应用场景进行选择和设计。

四、系统实现与测试(一)硬件实现在硬件实现阶段,需要根据设计要求选择合适的FPGA芯片和开发工具,完成电路设计和布局布线等工作。

基于FPGA+CPU的信号处理系统的设计与实现

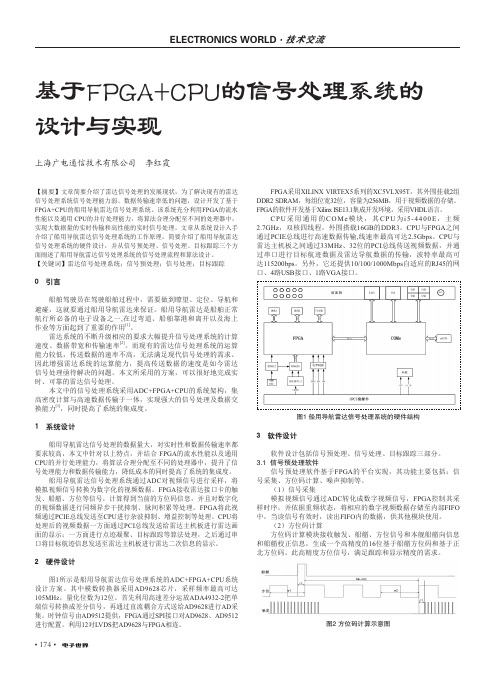

• 174•基于FPGA+CPU的信号处理系统的设计与实现上海广电通信技术有限公司 李红霞【摘要】文章简要介绍了雷达信号处理的发展现状,为了解决现有的雷达信号处理系统信号处理能力弱、数据传输速率低的问题,设计开发了基于FPGA+CPU 的船用导航雷达信号处理系统。

该系统充分利用FPGA 的流水性能以及通用 CPU 的并行处理能力,将算法合理分配至不同的处理器中,实现大数据量的实时传输和高性能的实时信号处理。

文章从系统设计入手介绍了船用导航雷达信号处理系统的工作原理,简要介绍了船用导航雷达信号处理系统的硬件设计,并从信号预处理、信号处理、目标跟踪三个方面阐述了船用导航雷达信号处理系统的信号处理流程和算法设计。

【关键词】雷达信号处理系统;信号预处理;信号处理;目标跟踪0 引言船舶驾驶员在驾驶船舶过程中,需要做到瞭望、定位、导航和避碰,这就要通过船用导航雷达来保证。

船用导航雷达是船舶正常航行所必备的电子设备之一,在过弯道、船舶靠港和离开以及海上作业等方面起到了重要的作用[1]。

雷达系统的不断升级相应的要求大幅提升信号处理系统的计算速度、数据带宽和传输速率[2]。

而现有的雷达信号处理系统的运算能力较低,传送数据的速率不高,无法满足现代信号处理的需求。

因此增强雷达系统的运算能力,提高传送数据的速度是如今雷达信号处理亟待解决的问题。

本文所采用的方案,可以很好地完成实时、可靠的雷达信号处理。

本文中的信号处理系统采用ADC+FPGA+CPU 的系统架构,集高密度计算与高速数据传输于一体,实现强大的信号处理及数据交换能力[1],同时提高了系统的集成度。

1 系统设计船用导航雷达信号处理的数据量大,对实时性和数据传输速率都要求较高,本文中针对以上特点,并结合 FPGA 的流水性能以及通用 CPU 的并行处理能力,将算法合理分配至不同的处理器中,提升了信号处理能力和数据传输能力,降低成本的同时提高了系统的集成度。

船用导航雷达信号处理系统通过ADC 对视频信号进行采样,将模拟视频信号转换为数字化的视频数据。

基于FPGA的数字信号处理算法实现与优化

基于FPGA的数字信号处理算法实现与优化数字信号处理(DSP)是一种通过数字计算器对模拟信号进行处理和转换的技术。

在现代通信、音频处理、图像处理、雷达与声呐等领域中,数字信号处理技术得到了广泛的应用。

为了实现高效的数字信号处理,采用FPGA(Field Programmable Gate Array)作为实现平台是一个不错的选择。

本文将探讨基于FPGA的数字信号处理算法的实现与优化。

一、FPGA概述FPGA是一种可编程的逻辑集成电路,由大量可编程逻辑单元(PLU)和大量的内部互联资源构成。

FPGA具有灵活性高、计算密度高、功耗低等优点,因此在数字信号处理领域中得到了广泛应用。

FPGA的可编程性使得它可以灵活地实现各种数字信号处理算法,并可以根据需求对算法进行优化。

二、数字信号处理算法数字信号处理算法包括一系列数学运算和数字滤波器的设计。

常见的数字信号处理算法包括傅里叶变换、滤波、降噪等。

在FPGA上实现数字信号处理算法需要考虑算法的复杂度、延迟和功耗等因素。

将算法转化为硬件描述语言(HDL)可以使得算法在FPGA上运行更高效,且可以通过优化来提高性能。

三、FPGA中数字信号处理算法的实现在FPGA中实现数字信号处理算法需要将算法转化为硬件描述语言,例如VHDL或Verilog。

首先需要对算法进行建模和仿真验证,然后根据算法的复杂度和性能需求进行优化。

通过对算法进行划分和并行化,可以提高算法在FPGA上的运行速度。

此外,还可以采用硬件加速器、数据存储优化等手段来提高算法的效率。

四、优化策略在FPGA中实现数字信号处理算法时,有一些常用的优化策略可以提高算法的性能。

首先是流水线技术,将算法划分为多个阶段并行执行,可以提高系统的运行速度。

其次是定点化运算,使用定点数表示浮点数可以节省资源和功耗。

另外,还可以采用复杂度折中的方法,通过减少部分计算以降低算法复杂度。

五、案例研究以图像处理为例,实现数字信号处理算法的优化。

多核SOC系统整合过程FPGA软处理器应用论文

多核SOC系统整合过程中的FPGA软处理器应用摘要:当代soc设计流程的核心环节逐步转向将成熟的ip整合为一个更大的芯片系统。

随着芯片系统规模越来越大,各种ip之间相互的影响也越来越复杂,甚至导致整个芯片系统无法协同工作。

本文提出了一种利用多核软处理器进行soc软硬件系统分析和动态调试的方法,大大加速了soc的开发质量和速度。

关键词:soc软硬件系统fpga软处理器芯片系统现代的soc芯片系统,典型的如手机芯片,不断变得越来越复杂,功能越来越强大——通讯,多媒体,网络,照相摄影设备等等不断丰富,使gtsoc芯片的设计难度不断上升。

除了外在的芯片规模在不断上升之外,我们发现,芯片的设计正在变得越来越“软”,这个“软”主要表现在以下方面:(1)soc芯片的主体已经从传统的硬逻辑电路,逐步演化为各种各样处理器相互通过片上总线系统相互连接。

这些处理器软件的编程逐步取代硬件逻辑设计成为soc设计中最耗费人力的环节。

(2)一个soc团队中,软件人员的数量超越硬件逻辑设计人员,目前,典型的比率是6:1(3)软件设计必须和芯片硬件设计几乎同时开始,而不是象以前那样拿到了芯片才开始软件开发(4)软件的功能划分,调试环境的能力,继承性和兼容性成为影响硬件ip选择的重要因素(5)软硬件协同后,各个ip模块之间的影响变得特别复杂,越发难以分析验证,也就越发难以选择各个ip模块在传统的芯片设计过程中,芯片的硬件行为是通过工作站上的软件来仿真的,但对soc而言,一方面各个处理器ip已经越来越复杂,精确仿真处理器模型的建立越来越费劲,甚至根本就没有;一方面系统规模膨胀速度指数级增长,越来越大,严重挑战了仿真软件的性能,目前主流的工作站,在当前规模的soc软件仿真条件下,系统的运行能力不到lhz是非常正常的,而由于应用的复杂,嵌入式操作系统的流行,使得soc系统光启动操作系统什么都没干,就至少需要数千万个时钟周期,在这样的运行性能下,进行软件调试也成了不可能的任务了。

基于FPGA的音频信号处理系统设计与实现

基于FPGA的音频信号处理系统设计与实现随着科技的发展和音频技术的不断进步,音频信号处理系统被广泛应用于各个领域。

本文将介绍基于FPGA的音频信号处理系统的设计与实现,并探讨其中的原理和关键技术。

一、引言随着数字音频技术的快速发展,音频信号处理系统的需求日益增长。

传统的音频信号处理方法往往通过软件实现,但其实时性和处理能力受到了限制。

而基于FPGA的音频信号处理系统具有高速运算、低延迟和灵活性强等优势,逐渐成为热门研究方向。

二、FPGA的基本原理FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,其内部由大量可编程的逻辑资源和存储器单元组成。

通过在FPGA上配置电路,可以实现各种不同的功能,包括音频信号处理。

三、音频信号处理系统的设计1. 模拟信号输入音频信号一般以模拟信号的形式输入到系统中,需要进行采样和模数转换。

采样率的选择应根据音频信号的特点和需求进行合理确定。

2. 数字信号处理在FPGA上设计并实现各种数字信号处理算法,如滤波、均衡、降噪等。

选择适合的算法和优化算法实现的技术,以提高系统的处理能力和性能。

3. 实时性要求由于音频信号的特性需保证处理系统的实时性。

FPGA的高并行性和硬件级别的实时性特点,使得其能够满足音频信号处理系统的实时性要求。

4. 数据存储与输出经过数字信号处理后的音频信号可以存储在FPGA内部的存储器中或外部的存储器中,也可以通过数字转模拟的方式输出到外部设备中。

四、关键技术与应用1. 快速算法优化为提高音频信号处理系统的处理速度,可以采用快速算法进行优化,如FFT(Fast Fourier Transform)等。

这些优化算法能够在保证处理结果准确性的前提下有效提高系统的运算速度。

2. 并行计算FPGA的并行计算能力是其强大的优势之一,可以将音频信号的处理任务进行拆分,同时进行多路处理,从而提高整个系统的处理能力。

3. 运算精度的选择在音频信号处理系统中,需要根据处理需求选择合适的运算精度。

基于FPGA的数字信号处理系统设计与实现

基于FPGA的数字信号处理系统设计与实现数字信号处理(DSP)是对数字信号进行处理和分析的技术方法,广泛应用于通信、音频、图像等领域。

其中,利用可编程逻辑器件进行数字信号处理的算法加速已成为一种重要的技术趋势。

本文主要讨论基于FPGA(Field Programmable Gate Array)的数字信号处理系统的设计与实现。

一、FPGA的基础知识及特点FPGA是一种具有可编程逻辑和可编程连接的硬件器件,能够实现用户自定义的数字电路功能。

与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA具有灵活性强、开发周期短、成本低等优势。

在数字信号处理系统中,FPGA可以作为一种高性能的实现平台。

二、数字信号处理系统的基本框架数字信号处理系统通常包括信号的采集、预处理、算法处理和结果输出等步骤。

在FPGA上实现数字信号处理系统时,通常将这些步骤划分为不同的模块,并将其设计成可并行执行的结构,以提高系统的吞吐量和性能。

1. 信号采集与预处理信号采集模块通常用于将模拟信号转换成数字信号,并对其进行采样和量化处理。

预处理模块则用于滤波、降噪、增益控制等处理,以准备信号供后续的算法处理模块使用。

2. 算法处理算法处理模块是数字信号处理系统的核心,其中包括常用的信号处理算法,例如快速傅里叶变换(FFT)、数字滤波器、自适应滤波器等。

这些算法通常采用并行处理的方式,以提高系统性能。

3. 结果输出结果输出模块将经过处理的数字信号转换成模拟信号,并通过数字至模拟转换器(DAC)输出。

此外,还可以添加显示设备或通信接口,以直观地观察处理结果或将结果传输到其他设备。

三、基于FPGA的数字信号处理系统的设计流程基于FPGA的数字信号处理系统设计一般包括硬件设计和软件设计两个层面。

1. 硬件设计硬件设计主要包括系统的功能分析与规划、模块的设计与实现以及系统的验证与测试。

利用FPGA进行数字信号处理

利用FPGA进行数字信号处理数字信号处理是现代通信、音视频等领域中不可或缺的技术,而FPGA(Field-Programmable Gate Array)则是数字信号处理的重要工具之一。

FPGA是一种可编程逻辑器件,可以实现任意逻辑功能,也可以用来加速数字信号处理算法。

下面,我们将探讨如何利用FPGA进行数字信号处理。

一、FPGA的基本原理FPGA是一种可在现场编程的数字逻辑芯片,具有可重构的物理结构。

它有一系列的可编程逻辑单元,通过编程可以实现任意的数字逻辑功能。

FPGA也可以包含大量的嵌入式模块,如时钟管理单元、DSP单元、片上存储器等。

FPGA可以实现数字信号处理算法的高效实现。

通常情况下,数字信号处理算法需要大量的乘法器和加法器,而FPGA中的DSP单元可以加速这些运算,同时FPGA中的片上存储器可以提高数据访问的效率。

因此,利用FPGA实现数字信号处理算法可以获得比利用通用处理器更高的性能和效率。

二、利用FPGA实现数字滤波器数字滤波器是数字信号处理中一种重要的技术,可以实现信号去噪、信号增强、信号分析等多种功能。

利用FPGA实现数字滤波器可以获得高效的实现。

数字滤波器可以分为FIR滤波器和IIR滤波器两种。

FPGA可以实现两种滤波器。

FIR滤波器可以用FPGA中的可编程逻辑单元和片上存储器实现。

IIR滤波器可以用FPGA中的DSP单元和可编程逻辑单元实现。

利用FPGA实现数字滤波器时,需要首先设计滤波器的算法。

然后,使用VHDL或Verilog语言将算法实现在FPGA中。

最后,通过仿真和验证确保滤波器的正确性和性能。

三、利用FPGA实现数字信号处理器数字信号处理器是一种专门的处理器,可以高效地处理数字信号。

FPGA可以作为数字信号处理器的实现方式之一。

利用FPGA实现数字信号处理器可以满足数字信号处理中的高性能要求。

数字信号处理器通常需要高效的处理器和存储器,而FPGA的可编程逻辑单元、DSP单元和片上存储器可以满足这些要求。

基于FPGA的高速数字信号处理系统设计与实现

基于FPGA的高速数字信号处理系统设计与实现随着时代的进步和科技的发展,数字信号处理(Digital Signal Processing,简称DSP)在各个领域中扮演着重要角色。

而FPGA (Field Programmable Gate Array)作为一种强大的可编程逻辑器件,已经被广泛应用于高速信号处理系统中。

本文将探讨基于FPGA的高速数字信号处理系统的设计与实现。

1. 引言高速数字信号处理系统在实时性和处理速度方面要求较高。

传统的通用处理器往往无法满足这些需求,而FPGA的并行处理能力和灵活性使其成为处理高速数字信号的理想选择。

本文将着重讨论FPGA系统的设计和实现。

2. FPGA基础知识2.1 FPGA原理FPGA是一种可编程逻辑器件,由大量的可编程逻辑单元和存储单元构成。

通过编程可以实现逻辑门、存储器和各种电路。

FPGA的可重构性使得其适用于不同的应用领域。

2.2 FPGA架构常见的FPGA架构包括查找表(Look-up Table,简称LUT)、寄存器和可编程互连网络。

LUT提供逻辑功能,寄存器用于数据存储,而可编程互连网络则实现不同逻辑单元之间的连接。

3. 高速数字信号处理系统设计3.1 系统需求分析在设计高速数字信号处理系统之前,需要明确系统的需求和目标。

这可能包括处理速度、资源利用率、功耗等方面的要求。

3.2 系统架构设计基于FPGA的高速数字信号处理系统的架构设计是关键步骤之一。

需要根据系统需求和目标来选择合适的算法和硬件结构。

可以采用流水线结构、并行处理结构等以提高处理速度。

3.3 硬件设计硬件设计包括选择FPGA器件、选择合适的外设、设计适配电路等。

通过合理的硬件设计可以实现信号处理系统的高速和稳定运行。

4. 实现与验证4.1 FPGA编程使用HDL(Hardware Description Language)进行FPGA编程。

常用的HDL语言包括VHDL和Verilog。

FPGA技术在信号处理中的应用研究

FPGA技术在信号处理中的应用研究随着现代通信技术的快速发展,对信号处理技术的需求越来越大。

传统的软件实现方式难以满足高要求的实时性、低功耗、低延时等要求。

而FPGA(Field Programmable Gate Array)的出现,为信号处理技术的应用带来了革命性的改变。

本文将从FPGA技术的基础和原理入手,探讨FPGA技术在信号处理领域的应用。

一、FPGA技术的基础与原理FPGA是一种可编程逻辑器件。

与通用处理器不同,FPGA的硬件可以随意配置,可以根据实际需要设计各种不同的硬件电路模块,从而适应各种具体的应用场景,并具有高度的可定制性和可重构性。

FPGA设备的逻辑单元是可以自由编程的,即可以通过开发工具来编写指令,将逻辑单元编程成任意所需的逻辑功能。

FPGA的硬件实现方式也是与ASIC(应用特定集成电路)相比较的一个优点。

ASIC的功能相对较为固定,而FPGA可以在设计完成后通过修改硬件的配置,改变其实现的功能模块,从而达到不同的应用需求。

这样就能够更好的解决市场需求、适应产品组合和品质变化等多种方面的需求。

二、FPGA技术在信号处理中的应用由于FPGA具有高速、并行、灵活等特性,在信号处理领域被广泛应用。

1、图像处理图像处理是FPGA的主要应用领域之一。

以数字相机为例,它的基本构成单元是CMOS或CCD传感器。

传感器对图像信息采样、缓存和传输,需要快速处理大量数据。

由于图像处理需要较强的实时性和高低延迟的特点,因此传统的软件处理方式难以满足要求。

而FPGA可编程逻辑器件由于可以以硬件电路的形式实现图像处理算法,因此可以大大加快数据处理速度。

同时,通过实现分组和流水线等技术来增加处理效率,以实现基于FPGA的快速图像处理系统。

2、视频处理和图像处理类似,FPGA技术也被广泛应用于视频处理领域。

视频处理系统需要快速地对大量数据进行处理和分析,以保证实时性和准确性。

由于视频处理算法的计算密集型、数据带宽要求高等特点,传统的处理器难以满足实时性需求。

基于FPGA_的Multi-h_CPM_高速解调系统设计与实现

doi:10.3969/j.issn.1003-3114.2023.05.017引用格式:刘誉楷,刘荣科,陈祺治.基于FPGA 的Multi-h CPM 高速解调系统设计与实现[J].无线电通信技术,2023,49(5):912-923.[LIU Yukai,LIU Rongke,CHEN Qizhi.Design and Implementation of High-speed Demodulation System for Multi-h CPM Signal Based on FPGA[J].Radio Communications Technology,2023,49(5):912-923.]基于FPGA 的Multi-h CPM 高速解调系统设计与实现刘誉楷1,刘荣科1,2∗,陈祺治1(1.北京航空航天大学电子信息工程学院,北京100191;2.深圳北航新兴产业技术研究院,广东深圳518063)摘㊀要:多指数连续相位调制(Multi-h Continuous Phase Modulation,Multi-h CPM )作为一种高效的调制方式,具有良好的频谱效率和抗干扰能力,在卫星通信领域有着广泛的应用价值㊂但是Multi-h CPM 的解调算法计算复杂度较高,为了实现高速数据传输能力,需要较高的硬件资源开销㊂因此基于现场可编程门阵列(Field Programmable Gate Ar-ray,FPGA)平台的高并行度数据处理能力,设计了一种Multi-h CPM 高速解调系统,采用了软输出维特比算法(Soft Output Viterbi Algorithm,SOVA)实现了Multi-h CPM 信号解调,并通过早迟门和升降频门实现了时频同步功能㊂为了降低算法的计算复杂度,本系统引入了倾斜相位(Tilted Phase,TP )算法和频率脉冲响应截断(Frequency Pulse Truncation,FPT)算法减少了Viterbi 过程的网格状态数,降低了系统的资源开销㊂通过仿真和实际测试,验证了所提出的解调系统的有效性,并表明该系统具有良好的解调性能和系统稳定性㊂关键词:多指数连续相位调制;软输出维特比算法;高速解调系统;现场可编程门阵列中图分类号:TN919.6㊀㊀㊀文献标志码:A㊀㊀㊀开放科学(资源服务)标识码(OSID):文章编号:1003-3114(2023)05-0912-12Design and Implementation of High-speed Demodulation System forMulti-h CPM Signal Based on FPGALIU Yukai 1,LIU Rongke 1,2∗,CHEN Qizhi 1(1.School of Electronic and Information Engineering,Beihang University,Beijing 100191,China;2.Shenzhen Institution of Beihang University,Shenzhen 518063,China)Abstract :Multi-h Continuous Phase Modulation (Multi-h CPM)is an efficient modulation technique with high spectrum efficiencyand anti-jamming ability,and has extensive applications in of satellite communications.However,the high computational complexity ofthe demodulation algorithm requires high resource consumption to ensure fluent data transmission with high speed.Therefore,a high-throughput Multi-h CPM demodulation system based on the Field Programmable Gate Array (FPGA)platform is designed,which uses a Soft Output Viterbi Algorithm (SOVA)to demodulate the Multi-h CPM signal,and early-late gates and up-down frequency gates are ap-plied to achieve time and frequency synchronization.To reduce the computational complexity of the algorithm,Tilted Phase (TP)and Frequency Pulse Truncation (FPT)technologies are introduced to reduce the number of Viterbi states and lower the computational costof the system.Through simulations and experiments,the effectiveness of the proposed demodulation system is verified,and it is shown that the system has good demodulation performance and stability.Keywords :Multi-h CPM;SOVA;high speed demodulation system;FPGA收稿日期:2023-05-21基金项目:北京市自然科学基金(L202003)Foundation Item :Beijing Municipal Natural Science Foundation of China(L202003)0㊀引言卫星互联网技术可以利用卫星信道连接全球范围内的用户,在现代通信系统中发挥了至关重要的作用㊂它不仅能够提供高速稳定的接入服务,且不受地理和地形的限制,可以满足各种应用需求,在电信㊁航天等各个领域都有着广泛的应用前景[1-3]㊂在卫星通信系统中,信号调制与解调是实现高速数据传输的关键技术之一[4]㊂连续相位调制(Continuous Phase Modulation,CPM)技术通过控制信号的相位变化来调制信号,相较于其他的数字调制技术,CPM可以在较低误码率下提供更高的频谱效率[5]㊂此外CPM具有恒包络的特点,可以有效降低高功率放大器非线性效应的影响[6],适合应用于卫星等功放受限的场景㊂多指数连续相位调制(Multi-h Continuous Phase Modulation,Multi-h CPM)是CPM的一种扩展形式㊂Multi-h CPM通过采用不同的调制指数,改变调制信号的相位偏移量㊂与传统的CPM技术相比,Multi-h CPM可以通过选择不同的调制指数来适应不同的信道环境,提高数据的传输效率,改善系统的容错性能[7]㊂目前Multi-h CPM接收机中最常采用的算法是最大似然序列检测(Maximum Likelihood Sequence Detection,MLSD)算法[8]㊂但是由于Multi-h CPM相比于CPM信号,其解调的复杂度较高,还需要采用一些简化算法来降低算法的复杂度㊂降低Multi-h CPM的解调复杂度有两个主要方向:降低匹配滤波器数量和减少网格状态数㊂降低匹配滤波器数量的简化算法主要包括脉冲幅度调制(Pulse Amplitude Modulation,PAM)分解[9-10]㊁Walsh分解[11]㊁奇异值分解(Singular Value Decomposition,SVD)[12]㊁状态空间分类(State Space Partitioning,SSP)算法[13]和虚拟指数集解调算法[14]等㊂降低网格状态数的简化算法主要包括倾斜相位(Tilted Phase,TP)算法[15]㊁频率脉冲截断(Frequency Pulse Truncation,FPT)算法[16]和减状态序列检测(Reduced State Sequence Detection,RSSD)算法[17]等㊂以上算法中,除了TP 算法之外,其他算法都会降低接收机的解调性能㊂在实际的系统设计时,通常将几种降低复杂度的算法联合应用,通过牺牲部分解调性能的方式,显著降低接收机系统的实现复杂度㊂为了实现高效的Multi-h CPM解调,保证接收机的高速数据处理能力,除了降低解调算法的计算复杂度之外,还需要在硬件架构设计时,通过高度并行化的数据处理方案,提高系统的吞吐率㊂现场可编程门阵列(Field Programmable Gate Array,FPGA)作为一种可编程的逻辑器件,具有可重构性强㊁高并发性能㊁高速运算能力㊁低功耗和灵活性等优点,可以支持多个逻辑电路并行计算,进行复杂的逻辑电路设计与实现,在信号处理和通信领域得到了广泛应用[18]㊂因此本文设计并实现了基于FPGA平台下的Multi-h CPM解调系统,完成了Multi-h CPM的软输出维特比算法(Soft Output Viterbi Algorithm,SO-VA)[19-20]㊁时频同步等功能,并且采用了TP算法和FPT算法,大幅度降低了系统的解调复杂度㊂通过仿真和实验验证,本文的Multi-h CPM接收机具有良好的系统性能,可有效满足实际应用需求㊂1㊀Multi-h CPM系统模型1.1㊀Multi-h CPMMulti-h CPM的复基带信号可以表示为:s(t;a)=2E STexp(jφ(t;a)),(1)式中:E S为信号能量,T为码元周期,φ(t;a)为信号相位,其可以进一步表示为:φ(t;a)=2πðɕi=0a i h i q(t-iT),(2)式中:a iɪ{ʃ1,ʃ3, ,ʃ(M-1)}为传输的M进制符号序列,h iɪ{h1,h2, ,h n}为调制指数集,q(t)为相位脉冲响应,可以表示为频率脉冲响应g(t)的积分,即:q(t)=ʏT0g(τ)dτ㊂(3)目前Multi-h CPM调制中最常用的脉冲函数为升余弦脉冲,其表达式为:g(t)=12LT1-cos2πtLT()[],(0ɤt<LT)q(t)=t2LT-14πsin2πt LT(),(0ɤt<LT)ìîíïïïï,(4)式中:L为关联长度㊂当L=1时,生成的Multi-h CPM信号为全响应信号;当L>1时,生成的信号为部分响应信号㊂1.2㊀Multi-h CPM相位网格状态Multi-h CPM信号在确定了调制参数的情况下,信号相位φ(t;a)仅与累加相位和关联长度内的传输符号有关,因此式(2)可以改写为:φ(t;a)=πðn-Li=-ɕa i h i+ðn i=n-L+1a i h i q(t-iT)=ϕn+ϕ(t;a),(5)式中:ϕn 为累加相位,ϕ(t ;a )为相关相位㊂考虑到调制指数h i 为有理数,因此Multi-hCPM 信号的累加相位状态是有限的㊂令h i =m /k ,其中m 和k 是互斥的两个质数,则累加相位的所有状态集合为:ϕn ɪ0,m πk,2m πk , ,(2k -1)m πk ,m 为奇数0,m πk ,2m πk , ,(k -1)m πk ,m 为偶数ìîíïïïï㊂(6)综合考虑累加相位和相关相位的影响,Multi-hCPM 信号的相位可以由下述状态序列决定:s n ={a n -L +1,a n -L +2, ,a n -1,ϕn -L }㊂(7)相位状态转移的表达式为:s n +1=s n a n ={a n -L +2,a n -L +3, ,a n ,ϕn -L +1}ϕn +1=ϕn +πh n a n -L +1{㊂(8)假设Multi-h CPM 的调制进制数M =2,关联长度L =1,调制指数h ={1/4,1/2},其相位状态转移如图1所示㊂从状态转移图中可以看到,Multi-hCPM 的信号相位具有周期性的网格结构,根据网格图的转移关系可以清楚地描述当前的信号状态和下一码元对输出信号的影响㊂图1㊀Multi-h CPM 相位状态转移图Fig.1㊀Phase state transition in Multi-h CPM system在Multi-h CPM 中,进制数M 将会影响到状态转移的复杂程度㊂当M =2时,每个状态有两条转移路径,而当M =4时,每个状态有4条转移路径㊂而进制数M ㊁关联长度L 和调制指数h 共同决定了网格状态数,随着Multi-h CPM 调制进制数的提升和关联长度的提升,都会导致整个系统的状态数呈指数增长,进而导致解调的复杂度上升㊂2㊀Multi-h CPM 解调算法2.1㊀Viterbi 解调算法假设信道为加性高斯白噪声信道(Additive white Gaussian Noise,AWGN),接收信号r (t )可以表示为:r (t )=s (t ;a )+n 0(t ),(9)式中:n 0(t )为零均值高斯白噪声㊂根据MLSD 准则,接收机在所有可能的结果中搜索距离接收信号的欧氏距离最近的一组序列值作为检测结果,该检测器可以表示为:λ(a -)=-ʏɕ-ɕ|r (t )-s (t ;a -)|2d t ㊂(10)MLSD 的目标是通过求解似然函数来在所有可能序列中寻找使式(10)最小的序列㊂考虑到Multi-h CPM 信号的恒包络特点,计算式(10)的最小值可以等价为计算式(11)的最大值㊂λ(a -)=Reʏɕ-ɕr (t )s ∗(t ;a -)d t ㊂(11)由于Multi-h CPM 信号具有相位网格特性,可以使用Viterbi 算法完成信号解调工作㊂Viterbi 算法中状态转移的度量值计算公式为:λ(n )=λ(n -1)+Reʏ(n +1)T nT r (t )s ∗(t ;a -)d t ㊂(12)整个Viterbi 算法包括了分支度量计算㊁路径度量值更新㊁路径选择和路径回溯等几个步骤㊂分支度量计算通过计算接收信号和每个不同的符号序列下的相关值,获得不同状态下的不同路径度量值㊂路径度量值更新是将计算得到的分支度量与上一时刻对应状态下的累计度量值进行累加,获得当前时刻下的所有路径的累计度量值㊂路径选择是对比每个状态下所有路径的累计度量值,选择最大路径的度量值结果作为新的累计度量值㊂重复上述步骤,从而完成整个序列的搜索过程㊂路径回溯是选择度量值最大的状态,沿着度量值更新的路径进行路径回溯,最终实现Multi-h CPM 的信号解调㊂2.2㊀软输出Viterbi 算法由于传统的Viterbi 算法在进行路径回溯后,只能获取符号序列的硬判决结果,而在通信系统中,解调器之后一般会级联译码器㊂考虑到译码器的纠错性能,译码器输入软信息相比于硬判决结果,可以获得更大的编码增益㊂在Multi-h CPM 接收机解调时,为了能够给后级的译码器提供软信息,因此采用了软输出Viterbi 算法㊂图2中实线为t -6~t时刻最大累计度量值的回溯路径,即幸存路径㊂虚线为t -6~t 时刻次大累计度量值的回溯路径,即竞争路径㊂节点S i 在t 时刻下的可靠性度量值Δt (S i )可以表示为幸存路径下的累计度量值和竞争路径下的累计度量值之差,即:Δt (S i )=|M S (S i ,t )-M C (S i ,t )|㊂(13)由图2可以看出,幸存路径和竞争路径在t -5时刻开始分离,并且幸存路径和竞争路径的比特判决结果并不是完全相同㊂在t -4和t -2时刻,幸存路径的比特判决结果是1,竞争路径的比特判决结果是0㊂因此仅通过t 时刻幸存路径和竞争路径下的度量值之差,不能完全表征可靠性度量值,还需要考虑幸存路径和竞争路径的比特判决结果,对可靠性度量值进行修正㊂图2㊀幸存路径和竞争路径网格图Fig.2㊀Trellis diagram of survivor path and competing path对于t 时刻下的状态节点S i ,可靠性度量值的更新算法计算过程如下:①存储节点S i 的可靠性度量值Δt (S i ),如果竞争路径不唯一,计算幸存路径和所有竞争路径的度量值之差,并将最小值存储到Δt (S i )㊂②将状态节点S i 的可靠性数值初始化为+ɕ㊂③比较状态节点S i 下的幸存路径与竞争路径的判决结果,并计算判决结果不同的时刻与节点所在时刻下的差值,将结果记录到MEM ㊂④在所有的MEM >0的时刻中,找到可靠性数值未更新过的最小的MEM ,记为MEM low ㊂⑤将MEM =0到MEM =MEM low 时刻之间,可靠性最小的数值更新为MEM low 的可靠性㊂通过可靠性更新算法之后,可以获得状态节点S i 的可靠性度量值㊂结合路径回溯的硬判决结果与状态节点的可靠性数值,就可以得到译码器所需要的软信息结果㊂2.3㊀Multi-h CPM 降复杂度算法2.3.1倾斜相位算法倾斜相位算法可以通过引入参考相位的手段将相位树从时变转化为非时变的形式,并且在无性能损失的前提下可以实现网格状态数减半㊂在式(2)中,φ(t ;a )的相位定义在实数域上,而考虑真实的物理相位,相位差为2π整数倍的相位是不能被区分的,所以对φ(t ;a )进行如下处理:φ-(t ;a )=φ(t ;a )-2π⌊φ(t ;a )2π」,(14)式中:φ-(t ;a )可以称为物理相位,其数据取值为0~2π㊂在Multi-h CPM 中,信号的相位转移既与传输的信息有关,也与当前时刻有关,增加了信号解调的复杂度㊂为了解决此问题,使用单极性符号U n 取代双极性符号a n ,其转换公式为:U n =12(a n +M -1)㊂(15)使用单极性符号后,令第n 个符号间隔内的时间t =τ+nT ,信号相位可以重新表示为:φ(t ;a )=2πðn -Li =0U i h i -(M -1)πðn -Li =0h i +2πðL -1j =0a n -j h n -j q (τ+jT )㊂(16)对式(16)的相位进行模2π,可以得到:ϕ-(τ+nT ;U )=R 2πR 2π[2πðn -Li =0U i h i ]+2πðL -1j =0a n -jh n -jq (τ+jT )éëêêùûúú,(17)式中:ϕ-(τ+nT ;U )为物理倾斜相位㊂式(17)中与时间相关的依赖项从t 变为τ+nT ,其相位转移是非时变的㊂此外,式中第一项为相位累计项,由于调制指数h i =K i /P ,式(17)的第一项可以改写为:R 2π[2πðn -Li =0U i h i ]=2πPR P [ðn -L i =0U i K i ]㊂(18)令v n =R P ðn -L i =0U i K i éëêêùûúú,可以得到v n 的递推关系为:v n =πP R P [v n -1+U n -L K n -L]㊂(19)没有进行符号映射前,Multi-h CPM 的信号相位是模2P ㊂通过TP 算法对信号的相位坐标系进行转换后,信号相位从模2P 变成了模P ㊂在进行Viterbi 解调时,相位状态数降低为原来的1/2,可以有效地降低Viterbi 解调的计算复杂度㊂由于TP 算法只是通过坐标系变换重新映射了信号相位,因此不会影响到Multi-h CPM 接收机的系统性能㊂2.3.2频率脉冲响应截断算法针对部分响应Multi-h CPM 信号,可以采用频率脉冲响应截断算法降低系统的计算复杂度㊂对于部分响应信号的CPM 信号,由于其频率脉冲两端的幅度较小,对信号相位的影响可以忽略,因此考虑对频率脉冲响应曲线进行截断,去掉低能量部分,等效的降低了信号的相关长度L ㊂假设Multi-h CPM 的调制参数M =4,L =3,h ={5/16,6/16},其FPT 算法截断方式如图3所示㊂Multi-h CPM 信号的频率脉冲响应函数在0T ~0.5T 和2.5T ~3T 这两个区间取值设置为0㊂由于其0.5T ~2.5T 区间内的能量占据了总能量的95%左右,因此通过截取频率脉冲响应,可以在仅损失少量信号能量的同时,有效降低响应长度㊂(a )频率脉冲响应(b )截断后的频率脉冲响应(c )相位脉冲响应(d )截断后的相位脉冲响应图3㊀频率脉冲响应截断算法示意图Fig.3㊀Frequency pulse truncation algorithm㊀㊀检测区间发生变化后,Multi-h CPM 的匹配滤波器构造如下:φ(t ,a )ʈπðn -Lᶄi =0a i h i +2πðLᶄ-1j =0a n -j h n -j q (t +jT +0.5T )㊂(20)使用了FPT 算法之后,由于降低了响应长度L ,Viterbi 解调的网格状态数也降低为原来的1/M ,从而有效降低了解调器的资源开销㊂但是不同于TP 算法,FPT 算法本质上是一个近似方法,会带来一定的串扰导致系统性能发生损失,不过其损失较小,对系统的影响可以忽略不计㊂2.4㊀Multi-h CPM 时频同步算法2.4.1定时同步算法式(9)中,接收信号仅考虑噪声的影响,但在实际系统中,接收信号存在链路衰减㊁链路延迟和多普勒频偏等,因此实际的接收信号重新写作:r (t )=A ej(2π(f c+Δf )(t -τ(t ))+ϕ(t -τ(t );a ))+n 0(t ),(21)式中:A 是信号幅度,f c 是中频频率,Δf 是多普勒频移,τ(t )是链路延迟㊂因此接收机在进行Multi-h CPM 信号解调时,需要保证接收机的本地信号和接收信号的时频同步㊂假设仅存在定时偏差而不存在频率偏差时,Viterbi 解调的累计度量值可以表示为:λ(Δt )=12T -14Δt ()cos πh -ΔtT ()+T 4πh k sin πh-Δt T (),0ɤΔt <T /214(T +Δt )cos πh-T -ΔtT ()+T 4πh ksin πh-T -Δt T (),T /2ɤΔt <Tìîíïïïïïïïïï,(22)式中:h -=TπΔt arccos 1N ðN k =0cos πh kΔt T()()㊂图4给出了Multi-h CPM 信号中定时误差对Viterbi 解调的累计度量值的影响㊂可以看出,当接收机存在定时偏差时,Viterbi 解调的累计度量值将会降低㊂利用该特点,可以采用超前-滞后门结构进行Multi-h CPM 的定时同步㊂图4㊀定时误差与累计度量值的关系图Fig.4㊀Effect of timing error on metric values超前支路信号r E 和滞后支路信号r L 可以表示为:r E (t )=r (t -δT )r L (t )=r (t +δT ){㊂(23)在[-0.5T,0.5T),超前支路累计度量值λE 及滞后支路累计度量值λL 相对于定时误差表现为凸函数,利用该特点可设计定时归一化度量值β来衡量超前支路累计度量值及滞后支路累计度量值的差值,其计算公式为:β(Δt )=λn ,L -λn ,E λn ,L +λn ,E㊂(24)当Multi-h CPM 的调制参数确定后,定时归一化度量值β相对归一化定时误差Δt /T 的曲线是固定的㊂从图5中可以看出,在[-0.5T ,0.5T ),定时归一化度量值β(Δt )与定时误差Δt 近似成线性关系,在设计中作为定时误差估计曲线使用㊂基于上述曲线,在计算获取了超前支路累计度量值λE 及滞后支路累计度量值λL 后,通过计算定时归一化度量值,对照定时误差曲线,即可获得Multi-h CPM 接收机的定时误差,修正定时误差即可完成定时同步㊂图5㊀归一化定时误差曲线图Fig.5㊀Normalized timing error curve2.4.2频率同步算法假设仅存在频率偏差而不存在定时偏差时,Viterbi 解调的度量值可以表示为:λ(Δf )=1Lʏ(k -1)T(k -L +1)Te j2πΔft d t㊂(25)频率误差与累计度量值的关系图如图6所示,可以看出,当接收机存在频率误差时,累计度量值将会降低㊂与定时同步类似,可以采用升降频门结构进行频率同步㊂图6㊀频率误差与累计度量值的关系图Fig.6㊀Effect of frequency error on metric values升频支路的信号r U 可以表示为:r U (t )=exp(j2πΔft +j2πðɕk =0a k h kq q (t -kT ))㊂(26)降频支路的信号r D 可以表示为:r D (t )=exp(-j2πΔft +j2πðɕk =0a k h kq q (t -kT ))㊂(27)对升频支路和降频支路的累计度量值进行归一化,可以得到频率归一化度量值:β(Δf )=λn ,U -λn ,D λn ,U +λn ,D㊂(28)当Multi-h CPM 的数据速率为50Mbit /s 时,接收机的载波频率误差Δf 对累计度量值的影响在[-80kHz,80kHz]呈现为凸函数,通过上述归一化设计后可以获取频率度量曲线,如图7所示㊂计算频率归一化度量值β(Δf ),可以通过其曲线获取接收机的频率误差,修正频率误差即可完成频率同步㊂图7㊀归一化频率误差曲线图Fig.7㊀Normalized frequency errorcurve3㊀FPGA 平台设计方案3.1㊀整体设计方案整个Multi-h CPM 接收机整体结构如图8所示㊂接收机主要包括了信号预处理模块㊁SOVA 解调模块㊁定时同步模块和频率同步模块㊂图8㊀Multi-h CPM 接收机整体框图Fig.8㊀System block diagram of the Multi-h CPM receiver信号预处理模块主要完成信号的预处理操作,包括对接收的中频信号进行去载波㊁为定时同步模块生成超前-滞后信号以及为频率同步模块生成升降频信号等操作㊂SOVA 解调模块主要完成Multi-h CPM 的解调并生成软信息㊂整个SOVA 过程中需要完成度量值计算㊁加比选以及路径回溯等操作㊂定时同步主要修正接收机的定时误差,需要计算超前支路和滞后支路的累计度量值并且获取定时同步的误差值㊂频率同步主要修正接收机的频率误差,需要计算升频支路和降频支路的累计度量值并且获取频率同步的误差值㊂3.2㊀信号预处理模块接收机从ADC 处获取到高速中频数据流之后,首先对信号进行去载波操作,将信号从中频信号转为基带信号㊂降频处理由DDS 载波生成器和FIR 低通滤波器构成,其中DDS 生成载波的具体数值由频率控制字决定,其计算公式为:FreqWord =⌊f IFf CLK ∗232」,(29)式中:f CLK 为接收机主频,f IF 为中频信号频率㊂为了保证DDS 生成的信号频率精度,采用了32bit 的频率控制字,可以保证接收机生成的正弦信号频率误差小于0.1Hz㊂同样,升频支路和降频支路的信号也是通过DDS 和FIR 滤波器生成,通过更改频率控制字即可生成所需的不同频率信号㊂对于超前支路和滞后支路的信号,通过对ADC的数据流进行延迟操作得到㊂未延迟的信号作为超前支路信号,延迟一次的信号作为正常的接收信号,而延迟两次的信号作为滞后支路信号㊂3.3㊀SOVA 解调模块如图9所示,SOVA 解调模块在接收到预处理模块的基带Multi-h CPM 信号后进行信号解调,并且根据整个解调算法的处理步骤,可以细分为分支度量值计算单元㊁加比选单元㊁路径回溯单元和控制单元㊂图9㊀SOVA 解调示意图Fig.9㊀SOVA demodulator控制单元为分支度量计算单元㊁加比选单元和路径回溯单元提供调制参数信息,并且对3个模块进行流程控制和协调,保证输入的基带信号可以以流水线形式完成数据处理㊂分支度量计算单元接收前级预处理模块输入的I㊁Q 两路基带信号与控制单元输入的调制参数信息㊂分支度量计算单元根据调制参数确定本地信号的生成,并且由内置的符号计时器计时确定当前的调制指数h ㊂在得到相关的信息之后生成接收机本地信号,然后通过矩阵乘法完成分支度量的计算,将分支度量矩阵的结果输入到加比选单元㊂加比选单元接收到分支度量计算单元不同状态下各个支路的分支度量值之后,通过控制单元输入调制指数信息,确定加比选的执行逻辑㊂加比选单元会在每个状态前一个符号周期存储的累计度量值的基础上,由当前的调制指数选择该状态所对应的分支度量值矩阵的分支,并将前一状态的累计度量值与对应的分支度量值相加,计算得到的新的分支度量值,并取度量值最大的路径作为幸存路径,次大的路径作为竞争路径,并将两个路径的信息输入到路径回溯单元㊂路径回溯单元根据幸存路径的路径编号回溯度量值矩阵,并且根据回溯过程的各个状态确定解调的硬判决结果㊂此外,路径回溯单元利用幸存路径和竞争路径的累计度量值和比特硬判决结果,更新内部可靠性度量矩阵㊂完成路径回溯后,获取当前时刻累计度量值最大的状态和状态对应的可靠性度量,计算其对数似然比并作为最终软信息结果㊂3.3.1分支度量计算单元分支度量计算单元的基本结构如图10所示㊂SOVA 解调控制单元输入的调制参数信息,一方面,输入到修正参数计算器中,控制倾斜相位修正ROM 地址,从本地存储的倾斜相位ROM 中读取对应的倾斜值,与输入的I㊁Q 两路信号进行复乘从而获取对应的经TP 处理后的I㊁Q 路信号㊂另一方面,调制参数输入到本地滤波器地址控制器中,经过地址控制器的计算后转换为本地滤波器地址,本地滤波器地址从本地滤波器ROM 阵列中读取形成所有匹配滤波器对应的接收机本地信号㊂本地信号与经过TP 处理的I㊁Q 基带信号进行并行相关,即可得到SOVA 解调的分支度量值㊂图10㊀分支度量计算单元示意图Fig.10㊀Branch metrics computing unit并行相关器是分支度量计算单元的核心㊂以Multi-h CPM 的调制参数M =4,L =3,h ={5/16,6/16}为例,为了提高解调器的数据处理能力,在进行分支度量计算时需要对所有状态下的所有分支进行并行计算㊂即使采用了TP 算法和FPT 算法,Multi-h CPM 依旧存在64个网格状态,256路分支路径,完全并行计算需要消耗大量的计算资源㊂为了简化并行相关器的计算复杂度,将整个相关运算拆解为接收信号复乘16组本地信号和对复乘结果进行两级相位旋转修正两个步骤完成㊂考虑到对于单一复数a +bi ,对其进行角度为π/2㊁π和3π/2的相位旋转后得到的结果分别为b -ai ㊁-a -bi 和-b +ai ㊂在256路分支路径计算过程中,存在周期为4的相位旋转角度为π/2整数倍的情况,因此通过计算其中64路的分支路径结果,就可以得到所有的256路分支度量值㊂而在进行64路分支度量值的计算过程中,可以再一次利用相位旋转的思想进一步简化计算量㊂假设所有本地信号的初相为0,64路本地信号就可以进一步被简化成16路信号,计算得到16路相关值后,对相关结果乘以π/8㊁π/4和3π/8的信号相位,可获得剩余的48路相关结果㊂整个并行相关器的硬件实现架构如图11所示㊂图11㊀并行相关器示意图Fig.11㊀Parallel correlator㊀㊀不利用分支度量的相位旋转,需要同时并行256路复数乘法器㊂采用了相位旋转之后,只需要消耗16个复数乘法器和48个CODIC 旋转器,就可以有效降低整体的资源消耗㊂同理,经过了分支度量单元之后,输入信号数率从采样速率降低到了符号速率,也降低了后级模块的数据处理压力㊂3.3.2加比选单元加比选单元主要完成对各个状态下所有分支路径的度量值累加㊁比较和选择㊂来自控制模块的调制参数输入映射表中,确定来自分支度量计算单元生成的分支度量结果的具体映射方案㊂整个加比选单元的硬件结构如图12所示㊂加比选单元中的状态分支度量映射实际是一个分选器,根据当前时刻每个状态的来源路径将所有的分支度量值映射至不同的状态中,即256路分支度量值每4个一组对应到Viterbi解调的64状态下㊂64个不同的状态都会从公用的累计度量值存储阵列中获取其对应的前一时刻累计度量值,随后利用其私有的加法器将分支度量值与前一时刻累计度量值相加得到4个累计度量值㊂4个累计度量值通过一个选择器,取其中最大的度量值作为当前时刻幸存路径的累计度量值,并将最大度量值所对应的路径记录为幸存路径,次大的累计度量值作为当前时刻竞争路径的累计度量值,其所对应的路径为竞争路径㊂图12㊀加比选单元示意图Fig.12㊀Add-compare-select unit㊀㊀在本单元的设计中,其所处理的数据速率远低于分支度量计算单元的数据速率,因此相比于分支度量计算单元需要全并行计算,加比选单元可以采用串并结合的方式完成计算,有效降低FPGA资源消耗㊂3.3.3路径回溯单元路径回溯单元中存储有每个状态对应的可靠性度量矩阵㊂取SOVA的回溯长度为10,则每个状态均需要存储大小为10ˑ4=40的可靠性度量矩阵㊂为了保证路径回溯的处理能力,10路路径回溯是并行处理㊂整个路径回溯单位的硬件架构如图13所示㊂输入的路径度量值会首先会通过缓存比较器选出累计度量值最大和次大的状态㊂之后根据幸存路径和竞争路径的编号值,控制回溯地址从缓存阵列中获取前一时刻的度量值进行路径回溯,并且在回溯的同时要计算当前状态下的可靠性,将可靠性数据存储在可靠性度量矩阵之中㊂在计算可靠性数据的同时还需要对幸存路径和竞争路径下的解调比特结果进行判决,当幸存路径和竞争路径的硬判决比特结果不同时,对可靠性数值进行更新㊂图13㊀路径回溯单元示意图Fig.13㊀Tracebackunit。

基于FPGA的高性能数字信号处理系统设计

基于FPGA的高性能数字信号处理系统设计随着数字信号处理技术的发展,数字信号处理系统在通信、雷达、生物医学、图像处理等领域中得到了广泛应用。

而FPGA技术则因其高性能、可编程性和可重构性成为数字信号处理系统中的重要组成部分。

本文将从以下几个方面阐述基于FPGA的高性能数字信号处理系统设计,包括FPGA架构、数字信号处理算法、系统级设计方法和应用案例。

FPGA架构FPGA(Field Programmable Gate Array)是一种基于现场可编程的硬件逻辑芯片。

FPGA内部由可编程逻辑单元(PL)、内存单元(BRAM)和数字信号处理单元(DSP)等模块组成,可以实现数字信号处理和数据通路等复杂的逻辑功能。

FPGA架构的选择对数字信号处理系统的性能和功耗有很大的影响。

通常选择的FPGA架构有两种:面向计算型的FPGA和面向通信型的FPGA。

其中,面向计算型的FPGA适用于高性能计算应用,提供高速的时钟频率和大量的计算资源;而面向通信型的FPGA适用于高速数据通信应用,能够提供高速的数据传输和处理效率。

数字信号处理算法数字信号处理算法是数字信号处理系统的核心部分,其主要任务是实现输入信号的特定操作,例如通信领域的调制、解调、信道编码和解码,图像处理领域的滤波、变换和分割等。

不同的数字信号处理算法对FPGA内部资源的需求也不同。

为了实现高性能的数字信号处理,使用一些常见的优化方法也是必不可少的。

如采用低复杂度算法、算法设计的并行化等方法,可以降低算法的时间和空间复杂度,从而提升系统的性能。

系统级设计方法在数字信号处理系统设计中,系统级设计方法是至关重要的。

系统级设计旨在将不同模块的功能组合起来,并通过优化系统架构、分配资源,以实现数字信号处理任务。

常用的系统级设计方法包括时序分析、时序优化、布局和布线等。

时序分析可帮助设计人员识别电路中的时序约束,从而避免电路时序问题。

时序优化则是通过合理的资源分配和时钟树设计来优化时序关系。

两种片上多核通讯结构的FPGA实现与性能评估

集溅 路 : 讯 薯 : 通 电:

j cHENGDl l ANL T U ONGXU N

Vol2 No |8 .1 M 8"2 0 1 01 .

两 种 片 上 多核 通 讯 结 构 的 F G 实 现 与 性 能 评 估 PA

刘 艳 王 少轩

3 N C原 型设 计 o

N C由一 组 路 由 器 ( o t ) 接 了不 同 的 o R ue 连 r

N C的互 连 和多核 的 系统 时 , 备足够 的能力 。 o 具

3 1 N C结 构 . o

核, 通过 中转 消息来 完成 其 问通信 , 就提 供 了潜 这

在 的高 带宽 , 延迟 和高 效 的片上互 连 , 为实 现 低 并

很难驾驭越来越庞大 的 电路规 模。传统 的 SC o

(yt Ss m—o e n—a—C i) 构 在 提 高 系统 整 体 性 hp 架

能上 已 出现一 些瓶 颈 , 核 系 统设 计 正 成 为 目前 多

实现 , 加载了 JE P G解码算法 , 并进行性能评估。

2 基 于分布 式共享总线的 MP0 SC

关键词 MP o ( l —PoesrSC) 总线 N C S C Mut rcso o i o

1 引 言

纳米时代 的到 来 , 集 成 电路 工 艺特 征 尺 寸 使 不断 缩小 , 电路规模 不断扩 大 , 颗芯 片上集 成 的 单

器件 数 目成指 数倍 增 长 , 一 处 理器 及 总 线结 构 单

外, 还会遇 到 一些无 法 预料 的问题 , 因此需 要开 发

N C原型 , 评估 在 实 际应 用 中 N C体 系结 构 的 o 并 o

DSP和FPGA的双核并行通信方法设计与应用

DSP和FPGA的双核并行通信方法设计与应用DSP(数字信号处理器)和FPGA(可编程逻辑器件)是当前数字信号处理和嵌入式系统设计领域中常用的处理器。

两者结合可以充分利用DSP和FPGA的优势,实现高性能数字信号处理和复杂算法的加速。

本文将讨论DSP和FPGA的双核并行通信方法的设计与应用。

1.双核处理器架构设计双核处理器架构设计是实现DSP和FPGA双核并行通信的第一步。

通常的双核处理器架构包括DSP和FPGA两个核心处理器,以及他们之间的集成总线。

DSP负责实现高性能数字信号处理算法,而FPGA负责实现复杂的逻辑和并行计算。

集成总线则起到了双核之间数据传输与通信的桥梁。

2.双核通信接口设计在双核处理器架构中,DSP和FPGA之间的通信是至关重要的。

为了实现高效的通信,需要设计适合DSP和FPGA的双核通信接口。

常见的接口方式有DMA(直接内存访问)、FIFO(先进先出缓冲区)和消息队列等。

DMA是一种高效的数据传输方式,可以实现DSP和FPGA之间的高速数据传输。

通过配置DMA控制器,可以直接将数据从DSP的内存传输到FPGA的输入缓冲区,或者将计算结果从FPGA的输出缓冲区传输到DSP的内存。

而FIFO则是一种缓冲区,用于平衡DSP和FPGA之间的数据传输速率。

当DSP处理速度较快时,可以将数据存储在FIFO中,等待FPGA处理。

当FPGA处理完成后,再通过FIFO将处理结果传输回DSP。

消息队列是一种基于事件驱动的通信方式,可以实现DSP和FPGA之间的异步通信。

通过向消息队列发送消息,DSP和FPGA可以相互通知对方需要进行数据传输或处理。

3.双核并行通信应用在音频和视频处理中,DSP可以负责音频和视频信号的解码和编码,而FPGA可以负责音频和视频信号的滤波和残差编解码。

通过双核并行通信,可以实现高质量、高效率的音频和视频信号处理。

在图像识别中,DSP可以负责图像的预处理和特征提取,而FPGA可以负责图像的分类和目标检测。

新一代DSP+FPGA高速数字信号处理方案

L … … 一 。

On l i n e S em i n ar Hi gh l i gh t s

占 用 一 定 的 时 钟 周 期 ,这 点 对 于 复 杂

的 算 法 是 可 以 接 受 的 ,但 是 ,如 果 数

据 量 大 ,任 务 重 复 的 时 候 , 会 造 成 很

合 众 科 技 有 限 公 司新 推 出 的 新 一 代 高

端F P GA + D S P应 用 方 案 。 该 平 台采 用 T l 公 司 主 频 最 高 可 达1 0 GH z的 多 核 心 定 浮 点 DS P芯 片

薹 I I 巷 I I l 薹 I I 彗 l 磊 l l 薹 叶 Q ∞ x

S E E D— HP S 6 6 7 8 ( A) 信号处理能达到什么水平 。

背景

现 在 比 较 热 门 的 行 业 , 比如 高 速 有 F P G A和 D S P。F P G A编程 灵活 ,

络控 制 等等 。所 以,F P GA 更 适 合 处

市场 上主要 用作高速 处理 的器 件 理 任 务 固 定 重 复 的 应 用 。

D S P 算 法 处 理 能 力 强 , 它 的 专 长

通信 系统 、 多媒体 系统 、 高级测量 系统 、 具 有 高 度 并 行 体 系 结 构 、处 理 时 间 可 是 计 算 ,可 以 用 来 实 现 多 条 件 操 作 和

S P 在 处 理 时 需 要 医 疗 系 统 和 高 清 图 像 处 理 , 他 们 都 涉 控 、高 数 据 率 等 特 点。但 是 ,F P GA 多算 法 复 杂任 务 。 D

图2 T MS 3 2 0 C 6 6 7 8 功 能框 图

T MS 3 2 0 C6 6 7 8 。此芯片凭 借多达 8 个核心的架构实现超高性能计算能力 。

基于数字信号处理的FPGA实现

基于数字信号处理的 FPGA实现摘要:高速通信接口设计FPGA可用于高速信号处理。

一般来说,在AD采样率较高并且数据速率也较高的情况下,就需要对数据、处理信号、发送信号、存储数据进行处理,例如处理数据、过滤数据、减少数据速率等。

数字信号处理包含图像处理、雷达信号处理、医疗信号处理等,其优点在于良好的实时性能。

通过面积换高速,可以获得比CPU更快、更大的并行度。

关键词:数字信号;数字信号处理;FPGA实现;前言:通过使用FPGA设计ASIC电路,可以在不进行芯片制造的情况下获得适当的芯片。

FPGA可以用作其他全色或半定制ASIC电路的中间采样芯片。

FPGA 有很多触发器和输入输出销,其中FPGA是具有最短设计周期、最低开发成本以及ASIC电路最低风险的设备之一,并且FPGA采用低功耗、高速chmos技术,与cmos和ttl电平兼容。

1.FPGA应用的三个主要方向1.1第一个方向第一个方向被用于以往通信装置的高速接口电路的设计。

设计者需要理解高速接口电路设计和高速数字电路板水平设计,在解决高速收发机过程中的信号完整性问题。

FPGA最初在通信领域被广泛使用,而且距离很远。

另一方面,通信领域需要高速的通信协议处理方法,但是通信协议总是被变更,不适合制作特殊芯片,因此能够灵活变更功能的FPGA是第一选择。

迄今为止,应用FPGA的一半以上也存在于通信行业。

1.2第二个方向第二个方向也可以被称为数字信号处理方向或数学计算方向,这是因为其自身大大超出了信号处理的范围。

例如,最早在2006年,报道美国使用FPGA分析财务数据,并且在此基础之上,FPGA设计者需要具备一个恒定的数学基础,并且可以理解和改进相对复杂的数学算法,并使用FPGA内部的各种资源将其转化为实际的运算电路。

然而,最近在欧洲和美国等地区,人们发现许多电子和计算机系统已经进入金融业,以更好地发展金融信号处理。

随着传输数量的增加,FPGA其他领域的数学计算功能将得到更好地展示。

FPGA在数字信号处理系统方面的应用PPT课件

这种算法使用了3次乘法、1次加法和2次减法, 其代价是多使用了一个表。由以上高效复数乘法器 原理,可以设计实现旋转因子复数乘法器。

第8页/共19页

课题各模块的实现

对应的硬件的输入输出框图如下图所示:

其中,旋转因子乘法器是由3个lpm_mult组 件实例和3个lpm_add_sub模块来实现的。

=(50+45j)(121+j39)/256

256=16+j28

=(4295+j7395)/

由于使用高效乘法器算法计算复数乘法,3个 第10页/共19页

课题各模块的实现 输入值为50+45j,旋转C因子jS 256 e j /9 121 j39

时的仿真波形如下图所示:

第11页/共19页

课题各模块的实现

FPGA在数字信号处理系统方面 的应用

第1页/共19页

1、课题简介 2、课题总体设计思想 3、课题各模块的实现

第2页/共19页

课题简介

本课题旨在研究用FPGA实现FFT算法,重点设计实现了 FFT算法中的蝶形处理单元,并采用高效乘法器算法设计实现了 蝶形处理单元中的旋转因子乘法器。

课题的实现方案采用基—2 FFT算法以及单元结构的设计思 路,用VHDL语言完成了系统设计描述,中间数据缓存单元采用 双口RAM,减少了访问RAM的时钟消耗。在Quartus Ⅱ这一 软件环境下,经过编译、综合和下载,给出了仿真测试的结果。 理论和仿真分析论证了该方案的有效性,从而证明了用FPGA实 现高速数字信号处理的可行性。

=(20+30j)+(16+28j)=36+58j

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

奉 设 汁在 追 求 整 个 系统 性 能 的基 础 上 ,兼 顾 系 统 的 使 用 寿 命 和 周 期 , l

僻脚 的岛度 灵活特性 , 实现数据的高速率传输 。同时利用 F P G A的可重构 性, : F P ( ; A I 土 = 】 部 构造 双 口 RA M来和 A R M 实 现 数据 交 换 。 下 图 所 示 为 系

通 过 接 u 资源 实现 处 理器 间 的全 互 连 , 实现多 C P U 商速 并 行处 理 系统 。与

接L 】 信 示 意 图 见 F陶, 中 D I S P的 H P I 逻辑信 号均直接与 F P GA的 H P 1

逻 辑 部 分相 连 接 , 相应的控制逻辑信号 由 F P GA提 供 。

结 构 简化 , 突 出 计算 能 力和 数 据 吞 吐 能 力 。 本 波 汁采 用蔓 个 独 立 的 子 系 统 互 连 形 成 一 个 整 体 架构 , 利用 F P GA 多

. . ●一 . . . l i D I 1 5 : O l

J

—

} 1 CN. r R【 ( ) ■ H} | Wl L J

科 学 论 坛

科 学 与财 富

基于 F P G A 的 多核 信 号 处 理 平 台 的实 现

娄 欣 欣

( 长安 大 学 电 控 学 院 陕 两 两 安 7 1 0 0 6 4 ) 摘 要: 虽 然 日 前 已经 存 在 D S P + A R M 的 烈核 处 理平 台 , 可 以处 理 一些 高频 的信 号, 仳 由于 二 者 的通 信 速 度 和 通 信 方 式 还 有 经 济 成 本 等 仔 在 ’ 定 的 不 足, 这 考虑 借 助 D s J 】 + F P ( 认+ A l M 三 饮 处 理 器 来 实 现 对 于信 号 处 理 的 高 效 率 和 高 频率 要 求 , 同时 利 用 F P GA的 可晕 构 性 也 便 于 系统 后 期 的 升 级 和 维 护 , 具有很强的通用性和可扩展性, 并 降低 了 系统 的成 本 。 关键词 : F I 】 G A; 重构; D S P; A R M

使F P GA用 做 协处 理 器 、 高速 数 据 处 理 器 或 高 速 数 据 传 输 接 口。 2 . 2 . 3 I ) S P端 [ _ 】 及 HP 1 b o o t 的 加 载 和 实现 D S P端 通 过 E MI F接 口外 扩 了 S D R A M 和 A S H俘 储 器 , 同时 E MI F 接口I j _ F P ( . A连 接 。 主机 通 过 D S P提 供 的 H P I 这 样 不 需 要 增 加 额 外 的 外 围 器件 , 便丁 二D S P程 序 的 更 新 和修 改 , 具有 更 好 的 灵活 性 和 方 便 性 。 为 此 ,

I + P( A D P

传统采 用々F H芯片的数字信 号处理机相 比, 通用算法 平台具有可重构性和 通用性 . 优 良 的 叮扩 展 性 、 开 发周 期 短 、 采 用 统 一 的硬 件 结 构 完 成 不 同的 信 号处 理 算法 : 通 用 的 并 行 计算 机 相 比 , 充 分 考 虑 了数 字 信 号 处 理 的 特 点 ,

2 . 系统 总 体 架构

2 . 1原理 分 析

这样 A R M D S P之 间 的通 信 就 很 灵活 : 既 町 以通 过 I ) S I , 的 HP I 接L _ 】 进 行

通信 , 也l J J ‘ 以在 F P G A 内部 构 造 一个 双 口 R A M 进 行通 信 。 这 种 设 计 带 来 的 好处是系统结构紧凑, F P G A可 以根 据 需 要 灵 活 配 置 , 通 用性更好 , 且更 经 济 。D S P通 过 E M1 F接 口与 F P GA相 连 , 通过对 F P G A进 行编 程 重构 , 可 以

理 和 语 凿处 理 等 领 域 , 对 于越 来越 复 杂 的二 维 、 三 维 甚 至 四 维 的 图像 处理 , 需要处理系统能够运 行复杂的算法。单核 D S P依 靠 工 艺 的 改 进 提 升 处 理 性能, 1 面单核 芯 片 的 集 成 度提 高 受 以 卜因素 的 制 约 : 物理极限的制约 、 按 几 何 级 数 递 增 的制 作 成 本 、 芯片处理 能力对功耗 、 散 热、 线延迟 的要求等 , 从 使 得 单 核 处 理 器 性 能提 高 产生 了瓶 颈 采 用 D s P + F P GA + A RM 的 多 C P U 处 器 , 打 破 了 传统 D S P处 理 速 度 有 限 的 约 束 , 可 以 大 大 提 高 平 台处 理 信 l j 的速 度 。在 F P GA端 采用 D D C数 字 下 变 频技 术对 信 号进 行 降频 , 扩 大 了 所 处理 信 号 的 频带 范 围 。借助 F P G A 的可 重 构性 , 降低 了 系统 成 本 , 便 于 系 统 的升 级 和维 护I ” 。

1 . 引 言 数 字 信 号处 理 技 术 己广 泛 应 用 于 通 信 、 雷达 、 声纳 、 遥感 、 图 形 图像 处

可 以 方 便进 行 系统 升 级 。

2 . 4 . 2 F P GA接 口 的设 计‘ 与实 现 AR M和 D S P各 相 关控 制 逻 辑 及 部 分 中 断 控 制 逻 辑 Байду номын сангаас 引 入 F P G A内。