Microblaze debug

ISE14.3开发microblaze实验教程

一:打开ISE集成开发环境,这里的版本是ISE14.3.进入ISE主界面,如下图二:在ISE中新建一个Project。

选择file 子菜单下的new project如下图进入新建工程导航New Project Wizard,新工程命名为TEST,工程位置自选,top—level source type 选HDL。

如下图Spartan 3E中的XC3S500E 。

package选FG320,speed选-4.开发语言选VHDL。

如下图点击next,会看到工程的总结Project Summary。

如下图点击Finish就创建好了一个新的工程。

这时ISE主界面会出现我们新建的TEST工程。

如下图。

不过这时我们的工程是空的。

三:为我们的工程添加一个microblaze软核了。

如下图右键TEST工程名。

选择new source。

进入新New Source wizard。

这里我们选择Embedded Processor(嵌入式处理器),文件名为SYS_CPU,即新建一个名为SYS_CPU的软核处理器。

Location选默认即可。

如下图点击next。

点击finish。

即创建好了一个名为SYS_CPU的软核处理器。

我们会在ISE主界面下看到我们新建的SYS_CPU处理器,文件格式为xmp格式,这是我们的软核处理器的顶层工程文件。

如下图同时系统会自动进入嵌入式开发套件EDK(Embedded Development Kit)。

包括硬件开发平台工具XPS(Xilinx Platform Studio)和软件开发套件SDK(Software Development Kit)。

这里我们看到的界面是硬件开发平台XPS,在这里我们可以操作我们的硬件资源。

如下图这时系统会提示我们是否使用BSB向导新建一个新的XPS工程,点击Yes。

AXI system最近刚开发的总线系统,PLB是较基础的,Spartan 3E开发板上我们选择PLB System。

microblaze实验总结

Microblaze实验报告实验目的:在venu3_mainboard嵌入microblaze软核处理器,检验一些基本接口的可行性及稳定性。

实验工具:硬件:venu3_mainboard,万用表,示波器,usb仿真器。

软件:XPS12.4,SDK12.4。

实验内容:1:plb总线挂载uart16c550模块系统的实现以及实现与PC之间实现简单的串口收发。

2:plb总线挂载generic_spi模块系统的实现以及实现spi模块主模式发数据。

3:plb总线挂载generic_iic模块系统的实现以及实现iic模块主模式发数据。

实验步骤:一:XPS环境下系统平台的搭建:1:采用BSB向导建立工程:2:选择保存路径:3:选择总线形式:4:创建新设计5:选择芯片种类和复位模式:6:选择单核模式:7:处理器配置:系统及总线时钟,内部RAM,不采用浮点形式.8:选择挂载设备:点击ADD DEVICE:9:挂载16C550:10:挂载GENERIC_SPI:11:挂载GENERIC_IIC:12:平台搭建完成:13:修改UCF文件与VENU3_MAINBOARD板硬件匹配:14:产生bitstream文件15:产生lib库文件:二:调试uart16c550接口1:建立应用工程:2:加载调试好的源代码:3:编译工程文件:4:将该工程设置为SRAM初始化文件:5:将工程文件加载到bitstream文件中:6:打开串口调试助手,设置如下图:7:板子上电下载程序:8:观察串口调试助手:可以看到有数据打印出来.9:发送一个字节数据观察接收到的结果:10:修改程序及串口调试助手的波特率19200,观察运行结果:运行结果:11:修改程序及串口调试助手的波特率57600,观察运行结果:运行结果:三:调试iic接口1:创建iic工程:2:添加工程源代码:3:将工程添加到sram文件下:4:编译该工程:5:升级bitstream文件:6:下载源文件:7:观察串口运行结果:系统通过iic接口发送了100个数据. 8:观察iic_sck波形:观察iic_sda波形:四:调试spi接口1:创建spi工程:2:添加工程源代码:3:编译该工程:4:将该工程加载到initial sram中5:将该工程加载到bitstream中6:下载bitstream文件7:观察运行结果:可以观察到系统通过spi接口向外设发送了128个数据。

MicroBlaze串口设计

MicroBlaze串口设计设计原理本系统中,Basys3的MicroBlaze模块调用基于AXI协议的(UART)IP核,通过AXI总线实现MicroBlaze-UART之间的(通信),完成串口打印。

操作步骤一、基于GUI界面创建工程1.创建新的工程项目1)双击桌面图标打开Viv(ad)o 2023.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2023.2>Vivado 2023.2;2)点击‘Create Project’,或者单击File>New Project创建工程文件;3)将新的工程项目命名为‘lab6’,选择工程保存路径,勾选‘Create project (sub)directory’,创建一个新的工程文件夹,点击Next继续;4)选择新建一个RTL工程,由于本工程无需创建源文件,故将Do not specify sources at this (ti)me(不指定添加源文件)勾选上。

点击Next继续;5)选择目标(FPGA)器件:xc7a35tcpg236-1或Basys3;6)最后在新工程总结中,检查工程创建是否有误。

没有问题,则点击Finish,完成新工程的创建。

2. 创建原理图,添加IP,进行原理图设计。

1)在Project Navigat(or)下,展开IP INTEGRATOR,选择‘Create Block Design’创建新的原理图设计;2)将新的设计命名为‘MB_UART’;3)添加一个clock IP,在原理图(Diag(ram))界面中鼠标右击,选择‘Add IP’。

在IP搜索框中输入‘clocking’,双击添加Clocking Wizard;4)双击Clocking Wizard模块进行自定义配置,选择Output Clocks 一栏,确定clk_out1频率为100(MHz),Reset Type为(Ac)tive High;5)鼠标右击‘clk_in1’,选择Make Ex(te)rnal添加引脚;6)完成后,如下图所示:7)同样的,在Diagram中添加MicroBlaze IP;8)添加完成后如下图所示,点击‘Run Block Automation’;9)在弹出窗口中,使用以下设置替换默认设置;Local Memory: 128KBLocal Memory ECC: NoneCache Configuration: NoneDebug Module: Debug OnlyPeripheral AXI Port:EnabledInterrupt Controller: 不勾选Clock Connection: /clk_wiz0/clk_out1(100 MHZ)10)完成之后,Vivado会基于之前的设置自动生成一些额外的IP,并且会自动连接完毕,此时不要点击‘Run Connection Automation’;11)在Diagram中添加AXI Uartlite IP,在搜索框输入‘uart’,选择相应的IP;12)鼠标右击Clocking Wizard的‘reset’,选择Make External添加引脚;13)使用连线工具将Processor System Reset的‘ext_reset_in’与‘reset’相连接。

MicroBlaze的使用方法(初学者)

建立一个ISE的工程,工程的顶层文件为schematic的。

然后根据实际需要添加自己的逻辑或处理部分。

Microblaze可以像一个IP一样同时应用到自己的设计中去。

具体方法如下:1、在工程中选择Add Source,在选择框中选择Embedded Processor,假设为该处理器起名为Microblaze_xxx。

2、此时ISE会自动启动XPS,在XPS中根据导向设置自己的Microblaze_xxx处理器的参数,并生成网表(注意必须在EDK中生成)。

3、选中Microblaze_xxx,双击View HDL Instantiation Template 生成例化文件。

如果要使得Microblaze的管脚既可以和FPGA的外部通用IO连又能和内部的用户逻辑连接,则要将例化文件中关于对Microblaze管脚加BUF类的语句删除。

4、由例化文件生成一个schematic symbol。

5、这个schematic symbol即为Microblaze处理器核。

用户可以像使用其他普通核一样使用它。

6、下面是生成mcs烧写文件。

具体步骤如下:7、/*将整个顶层的schematic生成schematic symbol并产生位流文件(.bit),然后将该位流文件改名为download.bit(因为后面用到的XPS中的批处理文件dow nload.cmd文件里的链接文件名为download.bit,当然也可以改把这个名字改成与前面一样。

两个名字改其中之一就行了)8、将download.bit文件拷入工程所在文件夹下Microblaze_xxx文件夹下的impl ementation文件夹。

*/9、在XPS中编写软件。

10、如果想要microblaze自举加载,则要在处理器设置的PARAMETERS中的C _NUMBER_OF_PC_BRK的参数改为1。

12、将edkBmmFile.bmm文件中的每一行第一个/ 删除,并将文件属性改成只读,改名microblaze1_stub.bmm文件为microblaze1_bd.bmm文件12、将Microblaze_xxx_bd.bmm文件里加上PLACED语句指定对应使用哪个Bl ock RAM。

软核之MicroBlaze接口说明

作用

Clocking Wizard

生成时钟

Processor system Reset

生成复位

Concat

将多个信号转换成一个多位的信号

AXI interrup以设置触发模式

AXI interconnect

AXI连接器,连接多个AXI总线的IP,管理数据的收发,仲裁

MicroBlaze

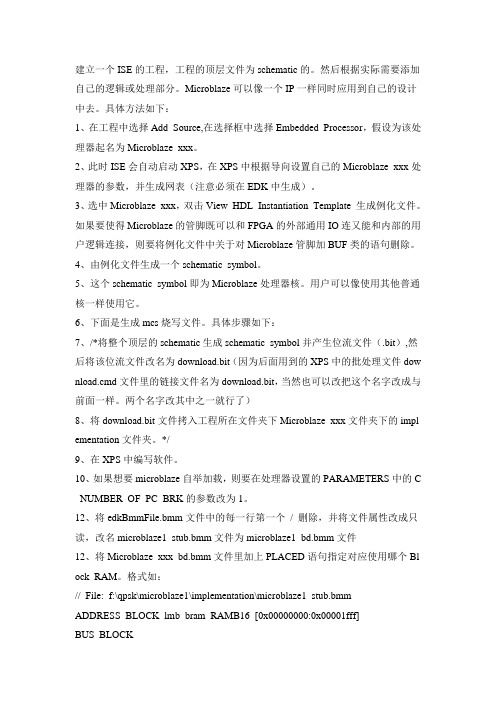

MicroBlaze接口中常见的有如下几种:

接口名

作用

INTERRUPT

中断控制器接口,用来连接中断控制器

DEBUG

DEBUG接口,用来连接MDM,方便开发中进行DEBUG

Clk

MicroBlaze系统运行时钟

Reset

系统复位,高有效

DLMB

处理器数据接口

ILMB

处理器指令接口

MicroBlaze Debug Module(MDM)

MB调试模块,方便进行调试。

Local memory

本地存储*

M_AXI_DP

MB外围数据接口,可以用来连接片内的BARM,AXI-Lite类型,非必选

M_AXI_IP

MB外围指令接口,用来挂载AXI总线形式的接口外设IP,AXI-Lite类型,必选

M_AXI_DC

外部存储器数据接口,AXI-FULL类型,非必选

M_AXI_IC

外部存储器指令接口,AXI-FULL类型,非必选

MicroBlaze的那些事儿1:MicroBlaze的体系架构

MicroBlaze的那些事儿1:MicroBlaze的体系架构前言:Nios II很多人都知道,是Altera的32位软核,但MicroBlaze知道的人不多,是对头公司Xilinx与Nios II大擂台的产品。

“blaze”是火焰的意思,可惜MicroBlaze不如它的名字一样,引起太大的关注。

一方面是Xilinx的推广不力,另一方面是资料太少。

也看过MicroBlaze和Nios II比较的文章,最后总是说其实两者难分伯仲,其实主要还是看你FPGA用哪家公司的,唉,我算倒霉,自学的是用Xilinx的芯片,也只好投入MicroBlaze的怀抱,下面就讲讲MicroBlaze的那些事儿Xilinx公司其实有三个核:Picobalze 8位软核(真的很难用,没有C编译器,编程用汇编,资料超少,具体见之前我blog文章)MicroBlaze 32位软核(下面文章的主角)PowerPC 32位硬核,只存在于Xilinx高端系列芯片上(Virtex-4和Virtex-5)。

当你见到人家叫PPC时候,千万不要以为是智能手机,其实PowerPC也简称PPC。

MicroBlaze的体系结构MicroBlaze V7.0核心框图要注意MicroBlaze核心框图,MicroBlaze V7.0已经有MMU了,意味着MicroBlaze可以运行依赖MMU的操作系统,像Linux、WindowCE等。

EDK6.2的MicroBlaze核心框图MicroBlaze的版本号是同EDK的版本号相联系的,我用的EDK 9.2i MicroBlaze版本是v7.0。

而从上面框图可以看到EDK6.2的MicroBlaze是没有MMU的,因此也不能运行Linux,只能运行ucLinux。

目前最新版本是MicroBlaze v7.20。

要使用相关应用,先更新一下EDK的版本(软件安装文件越来越大 )。

不同版本MicroBlaze的性能还要注意MicroBlaze支持的器件系列,当然首先是Xilinx的FPGA器件(这不废话!其实我也不知道NIOS II 能不能移植到Xilinx FPGA上来)Spartan-3E / Spartan-II / Spartan-3 / Spartan-IIE / Virtex-4 FX /Virtex-4 LX / Virtex-4 SX / Virtex-5 FX / Virtex-5 LX / Virtex-5 SX /Virtex-E / Virtex-II / Virtex-II Pro如果你手上只是CoolRunner-II的CPLD,我建议你尝试一下用Picobalze作控制。

32位软处理器MicroBlaze的体系结构及其应用 (图)

Xilinx公司的MicroBlaze32位软处理器核是业界最快的软处理解决方案。

支持CoreConnect总线的标准外设集合为MicroBlaze设计人员提供了兼容性和重复利用能力。

MicroBlaze处理器运行在150MHz 时钟下,可提供125 D-MIPS的性能,非常适合设计针对网络、电信、数据通信、嵌入式和消费市场的复杂系统。

MicroBlaze的体系结构MicroBlaze就是基于Xilinx公司FPGA的微处理器IP核,利用它和其他外设IP核一起,就可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze处理器是采用RISC架构和哈佛结构的独立32位指令和数据总线,可以全速度执行存储在片上存储器和外部存储器中的程序并访问其中的数据。

其内核结构如图1所示。

● 内部结构MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器——PC指针和MSR状态标志寄存器。

为了提高性能,MicroBlaze还具有指令和数据缓存。

所有的指令字长都是32位,有三个操作数和两种寻址模式。

指令按功能划分有逻辑运算、算术运算、分支、存储器读/写和特殊指令等。

指令执行的流水线是并行流水线,它分为3级流水:取指、译码和执行。

CoreConnect技术CoreConnect是由IBM开发的片上总线通信链,它使多个源的芯片核相互连接成为一个完整的新芯片成为可能。

CoreConnect技术使整合变得更为容易,而且在标准产品平台设计中处理器、系统以及外围的核可以重复使用,以达到更高的整体系统性能。

CoreConnect总线架构包括处理器本机总线(PLB)、片上外围总线(OPB)、一个总线桥、两个判优器,以及一个设备控制寄存器(DCR)总线,CoreConnect总线架构如图4所示。

Xilinx将为所有嵌入式处理器用户提供IBM CoreConnect许可,因为它是所有Xilinx嵌入式处理器设计的基础。

MicroBlaze简介很好很全面

第1章基于XILINX FPGA嵌入式系统片上系统开发概述XILINX是全球领先的可编程逻辑完整解决方案的供应商。

Xilinx公司成立于 1984年。

并首创了现场可编程逻辑阵列(FPGA)这一创新性的技术,并于1985年首次推出商业化产品。

随着FPGA技术的发展,FPGA的逻辑容量越来越大,成本越来越低。

在这种趋势下,FPGA可以代替系统中越来越多的器件,最后发展到FPGA片上系统。

第1节XILINX简介XILINX是全球领先的可编程逻辑完整解决方案的供应商。

Xilinx公司成立于 1984年。

并首创了现场可编程逻辑阵列(FPGA)这一创新性的技术,并于1985年首次推出商业化产品。

目前Xilinx满足了全世界对 FPGA产品一半以上的需求。

Xilinx可编程逻辑解决方案缩短了电子设备制造商开发产品的周期并加快了产品面市的速度,从而减小了制造商的风险。

Xilinx产品已经被广泛应用于从无线基站到DVD播放机的数字多媒体电子应用技术中。

传统的半导体公司只有几百个客户,而Xilinx在全世界有7,500多家客户与50,000多个设计开端。

其客户包括Alcatel,Cisco Systems,EMC,Ericsson,Fujitsu,Hewlett-Packard,IBM,Lucent Technologies,Motorola,NEC,Nokia,Nortel,Samsung,Siemens,Sony,Sun Microsystems以与Toshiba。

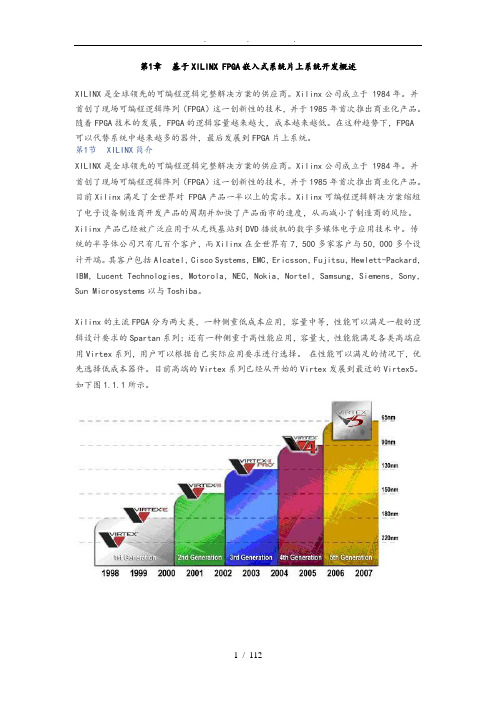

Xilinx的主流FPGA分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求的Spartan系列;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用Virtex系列,用户可以根据自己实际应用要求进行选择。

在性能可以满足的情况下,优先选择低成本器件。

目前高端的Virtex系列已经从开始的Virtex发展到最近的Virtex5。

Microblaze debug

MICROBLAZE的调试相关telantan MICROBLAZE是XILINX提供的采用大端存储系统、指令和数据采用哈佛结构的32位软核,可在SPARTAN2,3和VIRTEX系统上运行,现对其调试方法做一个简单介绍,希望对有兴趣这方面开发的人有所帮助。

XILINX提供的调试环境主要有GDB和SDK。

即在XPS环境下可通过调用GDB完成,也可将程序导入SDK环境下进行调试。

这两种方法都是通过XMD作为底层工具与目标进行通讯。

本文以XPS环境下的GDB调试为例。

调试的方法主要由4种:MDM,XMD-stub,ISS和Virtual Platform。

其中后两为仿真调试,不需要目标硬件支持,对于没有目标板的而又想预先程序开发的用户是个不错的选择。

下面对这4种方法逐一做一简要介绍。

1. MDM(Microprocessor Debug Module)这种方式是基于硬件的调试方法。

主机通过JTAG与FPGA中的MDM core相连,而MDM又与Microblaze的调试端口连接起来,从而完成调试信息的通讯。

一个MDM模块可以与一个和多个MicroBlaze处理器核相连,如下图1。

首先要加入opb_mdm模块并完成与microblaze调试接口的连接,并设置好相应的参数,如图2所示。

如果是通过BSB创建的项目,选择Use On-chip Debug Logic作为调试方式即可完成opb_mdm模块的加入。

相应的MHS文件为:BEGIN microblazePARAMETER INSTANCE = microblaze_0PARAMETER HW_VER = 4.00.aPARAMETER C_DEBUG_ENABLED = 1PARAMETER C_NUMBER_OF_PC_BRK = 2PARAMETER C_NUMBER_OF_RD_ADDR_BRK = 1PARAMETER C_NUMBER_OF_WR_ADDR_BRK = 1BUS_INTERFACE DLMB = dlmbBUS_INTERFACE ILMB = ilmbBUS_INTERFACE DOPB = mb_opbBUS_INTERFACE IOPB = mb_opbPORT CLK = sys_clk_sPORT DBG_CAPTURE = DBG_CAPTURE_sPORT DBG_CLK = DBG_CLK_sPORT DBG_REG_EN = DBG_REG_EN_sPORT DBG_TDI = DBG_TDI_sPORT DBG_TDO = DBG_TDO_sPORT DBG_UPDATE = DBG_UPDATE_sENDBEGIN opb_mdmPARAMETER INSTANCE = debug_modulePARAMETER HW_VER = 2.00.aPARAMETER C_MB_DBG_PORTS = 1PARAMETER C_USE_UART = 1PARAMETER C_UART_WIDTH = 8PARAMETER C_BASEADDR = 0x41400000PARAMETER C_HIGHADDR = 0x4140ffffBUS_INTERFACE SOPB = mb_opbPORT OPB_Clk = sys_clk_sPORT DBG_CAPTURE_0 = DBG_CAPTURE_sPORT DBG_CLK_0 = DBG_CLK_sPORT DBG_REG_EN_0 = DBG_REG_EN_sPORT DBG_TDI_0 = DBG_TDI_sPORT DBG_TDO_0 = DBG_TDO_sPORT DBG_UPDATE_0 = DBG_UPDATE_sEND其中PARAMETER C_USE_UART = 1是使能MDM中的UART功能,可通过它模拟UART从JTAG口传送数据。

Microblaze 应用程序固化 打开已有工程 microblaze

Microblaze应用程序固化

打开已有工程microblaze

在Flow Navigator侧边栏中选择Project Manager中Add Source.

在打开的对话框中,选择Add or Create Design Sources.

点击Next,选择Add Files…

在文档查看对话框中打开工程目录下sdk文件夹(此处文件夹名为microblaze.sdk),进而打开应用工程文件夹(此处文件夹名为helloworld),然后打开Debug文件夹。

此时可以看到SDK编译生成的可执行文件(后缀为.elf)。

选中helloworld.elf文件,点击OK。

在Add Sources文件夹中就可看到将要添加进工程的文件helloworld.elf。

点击Finish,完成添加。

此时在Source窗口下可以查看添加的ELF文件。

右击mb_subsystem.bd。

选择Associate ELF Files…

弹出关联ELF文件的对话框,其默认设置如下:

点击红色方框中选择ELF文件的按钮,弹出Select ELF Files…窗口。

选择刚刚添加的helloworld.elf文件。

点击OK,发现此时microblaze关联的ELF文件修改为helloworld.elf。

点击OK。

重新综合,实现设计,再进行编译生成可执行文件。

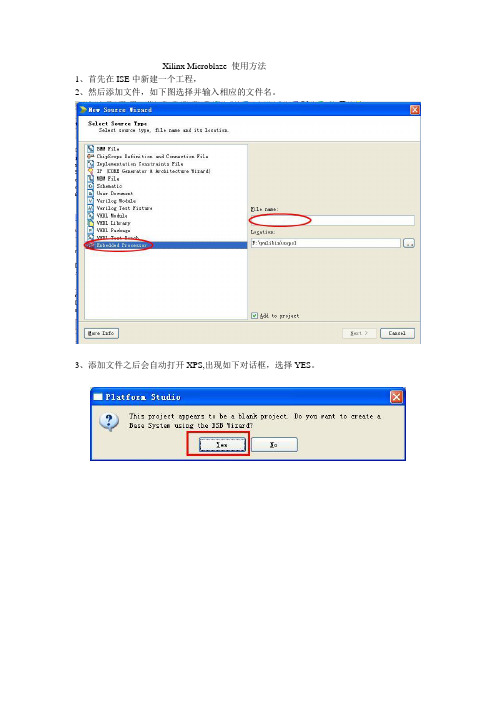

Xilinx Microblaze 使用方法

Xilinx Microblaze 使用方法1、首先在ISE中新建一个工程,2、然后添加文件,如下图选择并输入相应的文件名。

3、添加文件之后会自动打开XPS,出现如下对话框,选择YES。

4、如下图可以选择AXI4总线或者PLB总线,在此选择AXI4总线。

5、继续下一步如图选择时钟频率和复位的电平,然后点击下一步。

6、如下图点击可以添加需要的外设,包括GPIO、SPI、DDR控制器等。

7、选择需要添加的外设,选择好之后点击Apply即可。

然后选择完成。

8、在IP Catalog中可以继续添加需要的IP核。

9、添加完成之后会发现IP核已经自动的连接到了总线上。

10、在此可以继续对IP核进行相关配置。

11、配置界面如下。

12、如下图可以将需要的端口引出到片外。

13、当添加IP核完成之后,如下图打开时钟配置界面,对时钟进行配置。

14、时钟配置界面如下。

15、配置完成之后如下图点击,生成网表,如有错误则修改错误之后重新生成网表。

16、生成网表完成之后打开ISE,在顶层模块中对其进行实例化。

并生成BIT文件。

17、回到XPS中如下图点击,将硬件平台导入到SDK中。

18、选择导出到SDK并打开SDK.19、执行完上一步之后会弹出如下对话框,如图选择路径。

20、打开SDK之后会看到只有一个硬件平台。

我们需要再新建一个板级支持包和一个C工程。

21、如图新建板级支持包。

22、如图新建C工程。

23、如图输入工程名称并选择板级支持包。

24、写好相应的代码。

25、当代码写好之后,将BIT文件下载到FPGA中就可以进行调试了。

第二章_MicroBlaze处理器原理

MicroBlaze处理器的流水线及分支

需要注意的是,延迟隙不能使用下面的指令:IMM、 分支、断点。那些引起可恢复异常的指令是允许使用延迟 隙的。如果在延迟隙中产生异常,则异常句柄(异常服务 程序)负责转向执行分支目标(这个分支目标保存在BTR 寄存器内)。如果设置了ESR[DS]位,R17寄存器就不是 有效的,除非该寄存器保存着引起异常指令的下一条指令 的地址。

MicroBlaze处理器的浮点单元

1)算数操作:加,浮点加(fadd);减,浮点减 (fsub);乘,浮点乘(fmul);除,浮点除(fdiv); 平方根,浮点平方根(fsqrt); 2)比较:小于,浮点小于(fcmp.lt)、等于,浮点等于 (fcmp.eq);小于等于,浮点小于等于(fcmp.le);大 于,浮点大于(fcmp.gt);不等于,浮点不等于 (fcmp.ne);大于等于,浮点大于等于(fcmp.ge);无 序,浮点无序(fcmp.un,NaN使用); 3)转换:有符号整数到浮点(flt);浮点到有符号整 数(fint)

为了提高性能,使用下面的非标准的简化: 1)不支持亚正常操作数(这种操作树接近0,无法用完 整精度表示)。对亚正常操作数的操作将返回NaN,并且 在FSR中设置亚正常操作数错误标志; 2)亚正常操作数结果存为0,并且在FSR的寄存器中设 置下溢标志。这种方法通常称为清零(Flush-to-zero)模 式; 3)对NaN操作返回固定的NaN-0xFFC00000; 4)浮点操作的上溢总是返回∞。

MicroBlaze处理器的存储器结构

处理器的指令和数据缓存可以配置成4或8字的缓存行 (缓存最小结构单位)。缓存行越大,可存放的代码就越 长,执行效率也就越高。但是当程序中使用很多的随机访 问模式时,会降低缓存的命中率,因此给定大小的缓存行 反而会降低性能。

microblaze的固化方式

很高兴获得您的邀请,让我为您撰写一篇关于microblaze的固化方式的文章。

在这篇文章中,我将深入研究主题,提供全面的评估和深度的探讨,以便您能更深入地了解这个话题。

1. 什么是microblaze?Microblaze是由Xilinx公司开发的一款软核处理器,它是一种基于RISC架构的小型处理器,专门用于嵌入式系统。

作为一款可配置的处理器核,microblaze可以根据需求进行定制,使其在不同的应用环境中有更好的性能和功耗表现。

由于其灵活性和可定制性,microblaze在嵌入式系统领域得到了广泛的应用。

2. microblaze的固化方式分类在设计嵌入式系统时,如何将microblaze处理器核固化到FPGA芯片中是一个关键问题。

固化方式的选择会影响系统性能、功耗和开发成本。

一般来说,microblaze的固化方式可以分为硬固化和软固化两种。

2.1 硬固化硬固化是将microblaze处理器核的RTL(寄存器传输级)代码直接融入FPGA的逻辑单元中。

这种方式可以提高系统的性能和功耗效率,因为处理器核直接被实现在硬件中,可以快速执行指令并具有较低的功耗。

然而,硬固化的缺点是不够灵活,处理器核的配置和修改需要重新设计硬件电路,开发成本较高。

2.2 软固化软固化是将microblaze处理器核实现为FPGA中的可编程逻辑资源。

这种方式灵活性较强,可以根据需求对处理器核进行修改和重新配置,从而适应不同的应用需求。

软固化的缺点是性能和功耗较硬固化方式会有所下降,因为处理器核是通过逻辑资源实现的,执行指令需要经过逻辑门级的转换,速度和功耗会受到一定影响。

3. 选择固化方式的考量在选择microblaze的固化方式时,需要综合考虑系统的性能需求、功耗预算和开发成本。

如果系统对性能有较高要求,并且预算允许,可以选择硬固化的方式实现microblaze处理器核。

这样可以获得更好的性能和功耗表现。

如果系统对灵活性和可配置性有较高要求,或者预算有限,可以选择软固化的方式实现microblaze处理器核。

mircoblaze 汇编指令

mircoblaze 汇编指令

MicroBlaze是一种基于RISC架构的32位微处理器核,常用于嵌入式系统中。

MicroBlaze汇编指令集包括了各种用于执行特定操作的指令。

以下是一些常见的MicroBlaze汇编指令及其功能:

1. 加载和存储指令:

lw(Load Word),从内存中加载一个字(32位数据)到寄存器。

sw(Store Word),将寄存器中的字(32位数据)存储到内存中。

2. 算术运算指令:

add,将两个寄存器中的值相加,并将结果存储到目标寄存器中。

sub,从一个寄存器中的值中减去另一个寄存器中的值,并将结果存储到目标寄存器中。

3. 逻辑运算指令:

and,对两个寄存器中的值执行按位与操作,并将结果存储到目标寄存器中。

or,对两个寄存器中的值执行按位或操作,并将结果存储到目标寄存器中。

4. 分支和跳转指令:

beq(Branch if Equal),如果两个寄存器中的值相等,则跳转到目标地址。

j(Jump),无条件跳转到目标地址。

5. 控制指令:

nop(No Operation),什么也不做,用于插入空操作。

以上只是MicroBlaze汇编指令集中的一小部分,实际上还有许多其他指令用于执行各种不同的操作。

在编写MicroBlaze汇编程序

时,需要根据具体的需求选择合适的指令来完成相应的任务。

同时,还需要注意指令的执行顺序和寄存器的使用,以确保程序能够正确

地实现预期的功能。

microblaze 逻辑 -回复

microblaze 逻辑-回复microblaze 逻辑是什么?MicroBlaze逻辑是一种处理器设计的方法,它是Xilinx公司推出的一种32位快速硬件设计处理器核,主要用于嵌入式系统的设计。

MicroBlaze 处理器可以通过对其适应相关的硬件组件和软件平台来实现所需的定制功能。

它可以在FPGA(可编程逻辑器件)上实现,因此广泛用于嵌入式系统和数字信号处理等领域。

本文将以MicroBlaze逻辑为主题,详细介绍其特点、架构和应用。

第一部分:MicroBlaze的特点(500字)MicroBlaze是一种定制的32位核处理器,具有以下几个主要特点:(1) 可定制化:MicroBlaze处理器可以根据需要进行定制,可以添加或移除特定的硬件组件,以适应不同的应用场景。

这种定制化的能力使得MicroBlaze可以在不同嵌入式系统中满足灵活的要求。

(2) 快速设计:MicroBlaze处理器的设计流程相对简单,只需进行高级综合和门级综合等少量步骤,就可以快速地实现和验证其功能。

这使得MicroBlaze逻辑在硬件设计领域中具有很高的开发效率。

(3) 小型化:MicroBlaze处理器的核心组件相对较小,仅包括基本指令集和寄存器等,这使得其占用的硬件资源较少。

尽管如此,MicroBlaze仍然可以实现高性能和各种应用需求。

(4) 可扩展性:MicroBlaze处理器支持多种外设,包括存储器控制器、通信接口和数字信号处理单元等。

这些外设可以通过高级片上系统(MicroBlaze内部基于AXI总线的外设集成)或外部模块(通过AXI总线进行连接)进行扩展,以满足更多的应用需求。

第二部分:MicroBlaze的架构(600字)MicroBlaze处理器基于Harvard结构,具有五个主要部分:指令存储器、数据存储器、控制单元、运算单元和寄存器文件。

(1) 指令存储器:MicroBlaze使用32位存储器来存储指令,其中包括支持32位、16位和8位指令的指令解码器。

MicroBlaze软核处理器接口(行业研究)

I 主设备接口输入AXI4通道写准备

I 从设备接口输入AXI4通道写最后

Sn_AXIS_TDATA Sn_AXIS_TVALID Sn_AXIS_TREADY

M0_AXIS..M15_AXIS M0_AXIS..M15_AXIS M0_AXIS..M15_AXIS

I 从设备接口输入AXI4通道写数据 I 从设备接口输入AXI4通道写有效 O 从设备接口输出AXI4通道写准备

Mn_AXIS_TVALID M0_AXIS..M15_AXIS

Mn_AXIS_TREADY M0_AXIS..M15_AXIS

Sn_AXIS_TLAST

M0_AXIS..M15_AXIS

I/O

描述

O 主设备接口输出AXI4通道写最后

O 主设备接口输出AXI4通道写数据

O 主设备接口输出AXI4通道写有效

行写猝发访问。通过设置合适的字节选通,可以执行字、

半字和字节写操作。当读时,接口最多发出2个地址,而当

写时,最多发出32个地址。使能互斥访问用于LWX和SWX

指令。

谷风优质

7

AXI4接口 --存储器映射接口

M_AXI_DP、M_AXI_IP、M_AXI_DC和 M_AXI_IC接口信号功能一样,表4.1给出了M_AXI_DP 端口的信号及功能。更具体的功能可以参看第二章的 内容。

谷风优质

15

PLB接口

MicroBlaze处理的PLB接口用于字节使能的32位主 设备。表4.3给出了IPLB总线接口信号定义。表4.4给出 了DPLB总线接口定义。更详细的可以参考PLBV46互 连和接口资料。

谷风优质

16

PLB接口(IPLB)

信号

接口 I/O

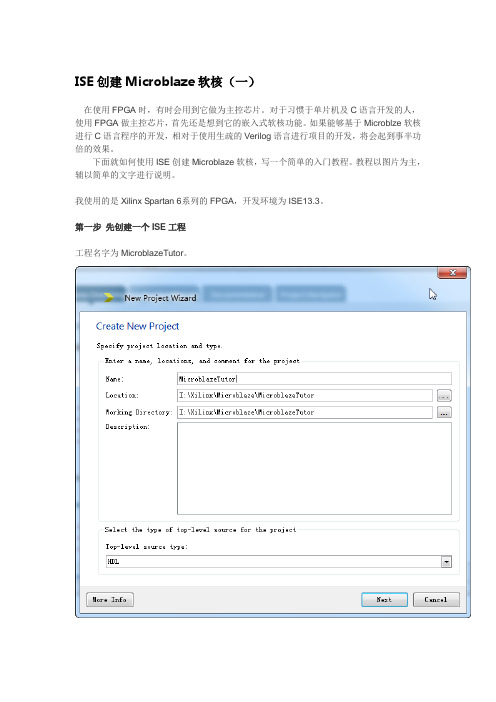

在ISE中调用microblaze软核

ISE创建Microblaze软核(一)在使用FPGA时,有时会用到它做为主控芯片。

对于习惯于单片机及C语言开发的人,使用FPGA做主控芯片,首先还是想到它的嵌入式软核功能。

如果能够基于Microblze软核进行C语言程序的开发,相对于使用生疏的Verilog语言进行项目的开发,将会起到事半功倍的效果。

下面就如何使用ISE创建Microblaze软核,写一个简单的入门教程。

教程以图片为主,辅以简单的文字进行说明。

我使用的是Xilinx Spartan 6系列的FPGA,开发环境为ISE13.3。

第一步先创建一个ISE工程工程名字为MicroblazeTutor。

在这里根据自己的硬件平台进行选择对应的FPGA型号。

根据自己开发习惯,选择是使用Verilog语言还是VHDL语言。

点击完成,完成工程的创建。

工程创建完成图。

第二步在工程中添加一个嵌入式软核如图,右键点击,选择New Source。

选择Embedded Processor(嵌入式软核),软核名字为mb_system。

点击完成。

第三步进入软核创建向导点击确认,进入软核创建向导。

选择PLB system。

PLB系统是旧版本的软核系统,相对操作更简单一些;AXI是新版的软核系统,有兴趣的话可以自己去研究。

按向导点击下一步。

这里会自动使用之前创建工程时设置的FPGA型号。

选择单核,下一步。

根据自己硬件平台的主时钟,选择对应的晶振频率。

注意,系统时钟要选择晶振倍频后能够达到的频率。

内存选择16KB。

这是系统默认最精简的内核。

通过Add Device选项添加如下图所示的外设:按键、LED、IIC、串口、定时器。

也可以不要选这么多外设,添加最简单的串口即可。

LED和按键只要选择1位数据位宽。

下一步。

系统内核的地址分配。

点击OK,完成创建。

第四步进入Platform Studio操作界面通过向导创建软核后,进入到PlatformStudio——内核开发环境。

使用MicroBlaze的指令集扩展(原文)

这是原文,译文在文档:使用MicroBlaze的指令集扩展(译文).docxINSTRUCTION SET EXTENSION USING MICROBLAZEPROCESSORABSTRACT:Instruction set extension is a common way to improve theperformance of embedded processors. During my work theMicroBlaze synthesizable processor was used. It has aspecial high-speed bus called Fast Simplex Link (FSL)enabling to develop multiprocessor systems and to integratecustomized IP cores into the design.In the Xilinx usage scenario the operands of the specialinstruction are transmitted through the FSL link. To achievehigher data transfer rate the FSL was used only to controlthe function of the custom IP while the operands requiredfor the operation read directly from the on-chip data memory.1. MICROBLAZE PROCESSOR USING FSL LINKMicroblaze is a 32 bit RISC, Harvard-style soft processordeveloped by Xilinx. It can be synthesized in FPGAs withthe maximum clock speed of 150 MHz. The processor haslarge variety of bus interfaces. For fast on chip memoryaccess it can use the Local Memory Bus (LMB) whichenables to use internal Block-RAM memory as bothinstruction and data storage. The peripherals can beconnected through theCoreConnectcompatible OnChipPeripheral Bus (OPB). [1]The processor core can have eight pair of dedicatedunidirectional Fast Simplex Link (FSL) channels to enablehigh speed point-to-point data transfer among multipleprocessor cores or in some other implementations theprocessor and peripherals. It has a dedicated bit todistinguish between data and control information. The FSLbus is FIFO based, enabling the implementation of basiccommunication primitives like: semaphores and pipes. Themaximum transfer speed is 300 million words/sec. The FSLconnection is highly-integrated into the processorarchitecture, and it can be programmed through dedicatedassembly and C language instructions. [2]We can use the FSL link to connect the processor corewith a custom IP block, described in [3]. In this case thecustom IP block is attached to the main CPU loosely. Thissolution has many advantages: We do not change theoptimized processor core while adding custom instruction,Fig. 1. System architecture proposed by Xilinxso we can fulfill the previously determined strict timingconstraints defined for the CPU. With the high levellanguage macros we can send data easily through the FSLlink superseding to rebuild the full tool-chain (assembler,linker, c-compiler, debugger etc.) for each systemseparately. Fig. 1.shows the system architecture proposedby Xilinx.In [3] the author presents a IDCT core, that multipliestogether the input samples with constants read from a table.The operands can be transferred to the IDCT core in 16clock cycles. Eight clock cycles are necessary to read fromthe internal data memory to the internal file registers, and 8more to transfer it thought the FSL. The multiplication isdone in 64 clock cycles. The data is written back in 16 morecycles resulting all together 96 clock cycles. During theIDCT process the processor can execute some other tasks,and read the data from the custom IDCT core only ifnecessary. In the described implementation the FSL has aFIFO capacity of 16 words, to compensate the speeddifference between the CPU and the IDCT core.If we could read the eight input samples directly fromthe memory through a Direct Memory Interface the IDCTinstruction would be 32 clock cycles less (33 percentimprovement). We could reduce the system size too,eliminating FSL FIFO.The described scenario of instruction set extension canbe powerful only detaching relatively large algorithms (likeIDCT) from the main CPU,however there is a significantoverhead caused by operand and result transfer between theCPU and the Custom IP core.Fig. 2. Proposed system architecture2. PROPOSED ARCHITECTUREWe can increase the speed of the above describedarchitecture, by eliminating the operand and result transferamong the CPU and the custom IP block through the FSL,and using it only to initialize the function.The Microblaze processor can use internal Block RAMas data memory. The scenario described in [2] fetches datafrom the BRAM, stores it in one of the 32 internal registers,and passes it to the custom IP block.If we connect our custom IP with the dual-ported datamemory directly, through a Dir ect Memory Interface wecan access the CPU‟s memory directly (as shown in Fig.2),eliminating the temporary internal register store and loadinstructions.By disabling the caching in the segment of the datamemory, where the operands and results are stored, we canmaintain data integrity through the whole system.3. TEST SCENARIOIn some application the custom instruction uses a bigamount data as operands and/or results. This can betransferred through the FSL or can be read directly from theData BRAM. During my tests I was using a ChemicalSimilarity Search [4] engine to evaluate the performance ofthe proposed scenario.Each molecule has a binary representation of 1024 bitlength. Two molecules A and B are identical if their binarydescription X A and X B is equal. The goal is to find alikemolecules, where similarity S is defined in the followingway:a: the number of binary …1‟-s in X Ab: the number of binary …1‟-s in X Bc: the number of binary …1‟-s in {X A (binary and) X B}We can download the binary representation of themolecules to the BRAM data memory through a systemconnection (like UART). Each molecule uses 32 memorywords. Calculus of the similarity constant S can be initiatedthrough transferring two memory pointers pointing to X A andX B through the FSL, afterwards the result is transferredthrough the same link.The proposed architecture has a significant benefit byeliminating the need to transfer all the operands (two times1024 bits) to the Similarity Search Engine. Otherimprovement is that the direct BRAM access works atmuch higher speed compared to the FSL which is limitedby the Microblaze processor.The only limitation of the recommended systemarchitecture is that, only one custom peripheral unit can beconnected directly to the data BRAM through the DirectMemory Interface.4. CONCLUSIONThe recommended system architecture enables to develop afast custom instruction interface for applications wherelarge amount of data is necessary for the auxiliary calculus.The custom instruction is interfaced to the Microblazeprocessor through a FSL interface, where commands aretransmitted; the numerous operands and results are directlyaccessed from the on-chip BRAM.In our test scenario we were using this architecture todevelop a chemical similarity check engine that calculatestwo molecules likeness, based on their 1024 bit long binaryrepresentation.The improvement of this system is significant comparedto the scheme where the custom instruction receives theoperands through theFSL.5. REFERENCES[1] MicroBlaze Processor Reference Guide, Xilinx, 2004[2] Fast Simplex Link Channel (FSL), Product specification,Xilinx,2004[3] Hans-Peter Rosinger: Connecting Customized IP totheMicroBlaze Soft Processor Using the Fast Simplex Link(FSL)Channel, Xilinx, 2004[4] Peter Willett, “Chemical Similarity Searching”, J. Chem.Inf.Comput. Sci., vol 38, pp. 983-996, 1998。

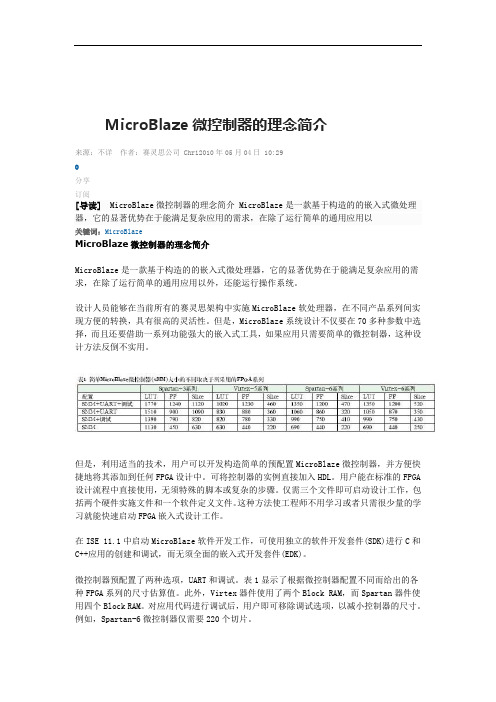

MicroBlaze微控制器的理念简介

MicroBlaze微控制器的理念简介来源:不详作者:赛灵思公司 Chri2010年05月04日 10:29分享订阅[导读] MicroBlaze微控制器的理念简介 MicroBlaze是一款基于构造的的嵌入式微处理器,它的显著优势在于能满足复杂应用的需求,在除了运行简单的通用应用以关键词:MicroBlazeMicroBlaze微控制器的理念简介MicroBlaze是一款基于构造的的嵌入式微处理器,它的显著优势在于能满足复杂应用的需求,在除了运行简单的通用应用以外,还能运行操作系统。

设计人员能够在当前所有的赛灵思架构中实施MicroBlaze软处理器,在不同产品系列间实现方便的转换,具有很高的灵活性。

但是,MicroBlaze系统设计不仅要在70多种参数中选择,而且还要借助一系列功能强大的嵌入式工具,如果应用只需要简单的微控制器,这种设计方法反倒不实用。

但是,利用适当的技术,用户可以开发构造简单的预配置MicroBlaze微控制器,并方便快捷地将其添加到任何FPGA设计中。

可将控制器的实例直接加入HDL。

用户能在标准的FPGA 设计流程中直接使用,无须特殊的脚本或复杂的步骤。

仅需三个文件即可启动设计工作,包括两个硬件实施文件和一个软件定义文件。

这种方法使工程师不用学习或者只需很少量的学习就能快速启动FPGA嵌入式设计工作。

在ISE 11.1中启动MicroBlaze软件开发工作,可使用独立的软件开发套件(SDK)进行C和C++应用的创建和调试,而无须全面的嵌入式开发套件(EDK)。

微控制器预配置了两种选项,UART和调试。

表1显示了根据微控制器配置不同而给出的各种FPGA系列的尺寸估算值。

此外,Virtex器件使用了两个Block RAM,而Spartan器件使用四个Block RAM。

对应用代码进行调试后,用户即可移除调试选项,以减小控制器的尺寸。

例如,Spartan-6微控制器仅需要220个切片。

MicroBlaze软核处理器简介

MicroBlaze 软核处理器简介

MicroBlaze™是Xilinx 嵌入式产品系列的重要组件。

MicroBlaze 是功能齐全的、更少指令集的FPGA 优化型32 位计算机(RISC) 软处理器,可充分满足各种应用需求,如工业、医疗、汽车、消费类以及通信基础设施市场等。

MicroBlaze 是一款高度可配置的易用型处理器,可在FPGA 以及全可编程(AP) SoC 产品系列中使用。

它免费配套提供Vivado®设计与系统版以及Vivado Webpack 版。

此外,它还可作为原有IDS 嵌入式版本的一部分提供,用于Spartan®-6 和Virtex®-6 等较早的FPGA 器件系列。

MicroBlaze 是高度可配置的IP 核,支持70 多种配置选项。

一些重要的配置选项为指令/数据高速缓存、浮点单元和存储器管理单元等。

用户可

使用高度灵活的可配置内核,实现几乎任何处理器使用案例,从极小型状态

机或微控制器到运行Linux 的高性能计算密集型微处理器系统,无所不能。

该IP 既可配置为在三级管线模式下工作(针对尺寸进行优化),也可配置为在五级管线模式下工作(针对速度进行优化),因而可提供比其它任何FPGA 软处理解决方案更快的DMIP 性能。

MicroBlaze 性能指标:基于Vivado 2017.3

注:因为Zynq-7000 器件,Zynq-7000 AP SoC 的性能值和Artix-7 及。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MICROBLAZE的调试相关

telantan MICROBLAZE是XILINX提供的采用大端存储系统、指令和数据采用哈佛结构的32位软核,可在SPARTAN2,3和VIRTEX系统上运行,现对其调试方法做一个简单介绍,希望对有兴趣这方面开发的人有所帮助。

XILINX提供的调试环境主要有GDB和SDK。

即在XPS环境下可通过调用GDB完成,也可将程序导入SDK环境下进行调试。

这两种方法都是通过XMD作为底层工具与目标进行通讯。

本文以XPS环境下的GDB调试为例。

调试的方法主要由4种:MDM,XMD-stub,ISS和Virtual Platform。

其中后两为仿真调试,不需要目标硬件支持,对于没有目标板的而又想预先程序开发的用户是个不错的选择。

下面对这4种方法逐一做一简要介绍。

1. MDM(Microprocessor Debug Module)

这种方式是基于硬件的调试方法。

主机通过JTAG与FPGA中的MDM core相连,而MDM又与Microblaze的调试端口连接起来,从而完成调试信息的通讯。

一个MDM模块可以与一个和多个MicroBlaze处理器核相连,如下图1。

首先要加入opb_mdm模块并完成与microblaze调试接口的连接,并设置好相应的参数,如图2所示。

如果是通过BSB创建的项目,选择Use On-chip Debug Logic作为调试方式即可完成opb_mdm模块的加入。

相应的MHS文件为:

BEGIN microblaze

PARAMETER INSTANCE = microblaze_0

PARAMETER HW_VER = 4.00.a

PARAMETER C_DEBUG_ENABLED = 1

PARAMETER C_NUMBER_OF_PC_BRK = 2

PARAMETER C_NUMBER_OF_RD_ADDR_BRK = 1

PARAMETER C_NUMBER_OF_WR_ADDR_BRK = 1

BUS_INTERFACE DLMB = dlmb

BUS_INTERFACE ILMB = ilmb

BUS_INTERFACE DOPB = mb_opb

BUS_INTERFACE IOPB = mb_opb

PORT CLK = sys_clk_s

PORT DBG_CAPTURE = DBG_CAPTURE_s

PORT DBG_CLK = DBG_CLK_s

PORT DBG_REG_EN = DBG_REG_EN_s

PORT DBG_TDI = DBG_TDI_s

PORT DBG_TDO = DBG_TDO_s

PORT DBG_UPDATE = DBG_UPDATE_s

END

BEGIN opb_mdm

PARAMETER INSTANCE = debug_module

PARAMETER HW_VER = 2.00.a

PARAMETER C_MB_DBG_PORTS = 1

PARAMETER C_USE_UART = 1

PARAMETER C_UART_WIDTH = 8

PARAMETER C_BASEADDR = 0x41400000

PARAMETER C_HIGHADDR = 0x4140ffff

BUS_INTERFACE SOPB = mb_opb

PORT OPB_Clk = sys_clk_s

PORT DBG_CAPTURE_0 = DBG_CAPTURE_s

PORT DBG_CLK_0 = DBG_CLK_s

PORT DBG_REG_EN_0 = DBG_REG_EN_s

PORT DBG_TDI_0 = DBG_TDI_s

PORT DBG_TDO_0 = DBG_TDO_s

PORT DBG_UPDATE_0 = DBG_UPDATE_s

END

其中PARAMETER C_USE_UART = 1是使能MDM中的UART功能,可通过它模拟UART从JTAG口传送数据。

在启动XMD与目标板连接之前,应用相应的设置如图3所示,选择HARDWARE,即选用MDM的调试方法。

如一切正常的话,则XMD窗口显示的信息如图4所示。

此时便可启动GNB进行软件调试了。

2XMDSTUB

这是一种基于软件的调试方法。

XMDSTUB是一段从0x0开始的监控程序(ROM MONITOR),它可通过JTAG-UART(在OPB-MDM中使能的UART,当然也可单独加入一JTAG-UART IP核)或UART口与XMD完成数据通讯,因此在MSS文件中必须有一个OPB-MDM或UARTLITE设计为XMDSTUB PERIPHERAL。

相应的MSS 文件如下所示:

BEGIN microblaze

PARAMETER INSTANCE = microblaze_0

PARAMETER HW_VER = 3.00.a

PARAMETER C_DEBUG_ENABLED = 0

BUS_INTERFACE DOPB = mb_opb

BUS_INTERFACE IOPB = mb_opb

BUS_INTERFACE DLMB = dlmb

BUS_INTERFACE ILMB = ilmb

PORT CLK = sys_clk_s

END

BEGIN opb_mdm

PARAMETER INSTANCE = debug_module

PARAMETER HW_VER = 2.00.a

PARAMETER C_MB_DBG_PORTS = 0

PARAMETER C_USE_UART = 1

PARAMETER C_UART_WIDTH = 8

PARAMETER C_BASEADDR = 0x80002000

PARAMETER C_HIGHADDR = 0x800020ff

BUS_INTERFACE SOPB = mb_opb

PORT OPB_Clk = sys_clk_s

END

.....

当然这也可通过GUI进行设置,PROJECT-SOFTWARE PLATFORME SETTING,如图5所示:

在Applications中完成如图6所示的设置,保证在编译时将XMDSTUB程序从0x0处开始放置。

另在XMD设置中,即图3中,应选择stub选项。

在advanced options 中,默认的是JTAG方式的连接,即采用JTAG-UART方式,用JTAG 口模拟UART功能。

如要选用UART方式,可勾上advanced options,选择serial,并设置好相应的串口参数,与IP CORE中选中的UARTLITE 参数保持一致,保证正确连接,如图7所示。

另外,有一个有意思的事,不知是不是我机子的问题,就是当我将advanced options中选为SERIAL之后,就没法再改回JTAG了,SA VE 时总是报错。

一个解决的办法就是先将CONNECTION TYPE改为其它类型SA VE,然后再改回STUB,此时就不要再选advanced options

了,因为默认的是JTAG方式。

上述设置完成后,便可DOWNLOAD程序,将XMDSTUB程序下载时FPGA 中,然后打开XMD进行连接和启动GDB的SEVER,最后用GDB完成应用程序的下载和调试。

3 ISS(Instruction Set Simulator)

这是一种基于指令集仿真的调试方法,只能支持处理器和内存模型,对其它的周边硬件不支持。

在图3中选用SIMULATOR,没有使用过这种方法,所以不多说。

4 Virtual Platform systems

虚拟平台是硬件系统指令周期级的仿真模型。

通过它可以在没有硬件的基础上,进行应用程序的调试和优化。

如果没有硬件平台,这是一种很好的选择。

在XPS中,选择Tools > Generate Virtual Platform创建虚拟平台。

然后在图3的XMD中便可选择virtual platform选项。

打开XMD,输入vpconnect命令,或前三个字母vpc,完成XMD与虚拟平台的连接,如图8所示。

最后便可运行

这4种调试方法先介绍到这里,具体可参考XILINX公司提供的文档。

文中错误在所难免,希望大家指正,telantan@。