专用集成电路设计大作业----多功能时钟设计

基于单片机的多功能电子钟的设计

数字电子钟实际上是一个对标准频率(1HZ)进行计数的计数电路。

它将“时”,“分”,“秒”显示于人的视觉器官的计时装置。

它的计时周期为24小时,显示满刻度为23时59分59秒,另外应有校时功能和报时等附加功能。

因此,一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器,校时电路、报时电路和振荡器组成。

干电路系统由秒信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路组成。

秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用振荡器加分频器来实现。

将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,译码显示电路将“时”、“分”、“秒”计数器的输出状态送到七段显示译码器译码,通过七位LED 七段显示器显示出来。

关键词:电子钟调试制作1 设计任务和要求 (4)1.1设计任务 (4)1.2设计要求 (4)2 系统设计 (4)2.1方案设计 (4)2.2系统工作原理 (5)3 单元电路设计 (5)3.1 直流电源 (5)3.1.1电路结构及工作原理 (5)3.2秒脉冲发生电路 (7)3.2.1电路结构及工作原理 (7)3.2.2电路仿真 (8)3.3计时秒计数(六十进制)电路 (8)3.3.1电路结构及工作原理 (8)3.4计时分计数(六十进制)电路 (12)3.4.1电路结构及工作原理 (12)3.5时计数(二十四进制)电路 (13)3.5.1电路结构及工作原理 (12)3.6报时电路 (14)电路结构及其工作原理 (14)3.7校时电路 (17)结构及其工作原理电路 (17)4 系统仿真 (19)5 电路安装、调试与测试 (19)5.1电路安装 (19)5.2电路调试 (19)5.3测试结果及分析 (20)6 结论 (20)7 参考文献 (21)8 总结、体会和建议 (22)元器件列表 (23)1.设计任务和要求1.1设计任务:设计一个多功能电子钟,且能实现基本功能。

毕业设计(论文)-基于单片机多功能电子时钟的设计与仿真(含程序仿真)[管理资料]

![毕业设计(论文)-基于单片机多功能电子时钟的设计与仿真(含程序仿真)[管理资料]](https://img.taocdn.com/s3/m/9ad55f3e0508763230121257.png)

程序仿真等全套设计,联系153893706第1章绪论二十一世纪的今天,最具代表性的计时产品就是电子万年历,它是近代世界钟表业界的第三次革命。

第一次是摆和摆轮游丝的发明,相对稳定的机械振荡频率源使钟表的走时差从分级缩小到秒级,代表性的产品就是带有摆或摆轮游丝的机械钟或表。

第二次革命是石英晶体振荡器的应用,发明了走时精度更高的石英电子钟表,使钟表的走时月差从分级缩小到秒级。

第三次革命就是单片机数码计时技术的应用(电子万年历),使计时产品的走时日差从分级缩小到1/600万秒,从原有传统指针计时的方式发展为人们日常更为熟悉的夜光数字显示方式,直观明了,并增加了全自动日期、星期、温度以及其他日常附属信息的显示功能,它更符合消费者的生活需求!因此,电子万年历的出现带来了钟表计时业界跨跃性的进步……我国生产的电子万年历有很多种,总体上来说以研究多功能电子万年历为主,使万年历除了原有的显示时间,日期等基本功能外,还具有闹铃,报警等功能。

商家生产的电子万年历更从质量,价格,实用上考虑,不断的改进电子万年历的设计,使其更加的具有市场。

本设计为软件,硬件相结合的一组设计。

在软件设计过程中,应对硬件部分有相关了解,这样有助于对设计题目的更深了解,有助于软件设计。

基本的要了解一些主要器件的基本功能和作用。

除了采用集成化的时钟芯片外,还有采用MCU的方案,利用AT89系列单片微机制成万年历电路,采用软件和硬件结合的方法,控制LED数码管输出,分别用来显示年、月、日、时、分、秒,其最大特点是:硬件电路简单,安装方便易于实现,软件设计独特,可靠。

AT89C52是由ATMEL公司推出的一种小型单片机。

95年出现在中国市场。

其主要特点为采用Flash存贮器技术,降低了制造成本,其软件、硬件与MCS-51完全兼容,可以很快被中国广大用户接受。

本文介绍了基于AT89C52单片机设计的电子万年历。

选题背景及研究的目的与意义设计的目的电子钟已成为人们日常生活中必不可少的物品,广泛用于个人家庭以及车站码头、剧院、办公室等公共场所,给人们的生活、学习、工作、娱乐带来了极大的方便。

多功能数字钟的设计报告

多功能数字钟的设计报告目录1.实验目的 (2)2.实验题目描述和要求 (2)3.设计报告内容 (2)3.1实验名称 (2)3.2实验目的 (2)3.3实验器材及主要器件 (2)3.4数字钟基本原理和电路设计 (3)3.5数字电子钟单元电路设计、参数计算和器件选择..............................3-8 3.6数字电子钟电路图 (9)3.7数字电子钟的组装与调试 (9)4.实验结论 (9)5.实验心得 (10)参考文献 (10)1.实验目的※掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法;※进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力;※提高电路布局﹑布线及检查和排除故障的能力;※培养书写综合实验报告的能力。

2. 实验题目描述和要求1、基本要求(1)能进行正常的时,分,秒计时的功能,分别由6个数码管显示24小时、60分钟、60秒钟的计数显示。

(2)、具有清零功能。

(3)、具有开、关功能。

2、发挥部分(1)能实现“校时”“校分”功能:当按下“SA”“校时”键时,计时器迅速递增,并按24小时循环,计满23小时后返回00;按下“SB”“校分”键时,计分器迅速递增,并按60分钟循环,计满59分钟后返回00;但不向“时”进位。

(2)能利用扬声器做整点报时:整点自动报时。

(参考:在离整点10s内,便自动发出鸣叫声,步长1s,每隔1s鸣叫一次,前四响是低音,最后一响为高音,最后一响结束为整点,报时频率可定为1KHz。

)能进行整点报时:当计时到达59分50秒后,每隔2秒钟发出一次低音“嘟”信号(其声音频率为500HZ),连续5次到达整点,发出一次高音“嘀”信号(其声音频率为1000HZ)3、对电路进行逻辑功能仿真。

3.设计报告内容3.1实验名称: 数字电子钟3.2实验目的·掌握数字电子钟的设计、组装与调试方法;·熟悉集成电路的使用方法。

多功能数字钟电路设计课程设计论文

电子技术课程设计报告——多功能数字钟电路设计目录一、任务及要求.......................................................... - 1 -(一)设计要求...................................................... - 1 - (二)设计指标...................................................... - 1 -二、数字钟的构成........................................................ - 1 -三、单元电路的设计...................................................... - 2 -(一)秒脉冲产生电路................................................ - 2 - (二)计数器电路.................................................... - 5 - (三)译码显示电路.................................................. - 7 - (四)校时、校分电路............................................... - 10 - (五)整点报时电路................................................. - 11 - (六)闹钟电路..................................................... - 11 -四、元器件清单......................................................... - 12 -五、总电路图........................................................... - 13 -六、电路仿真........................................................... - 14 -(一)开始状态..................................................... - 14 - (二)校时、校分功能............................................... - 14 - (三)满六十秒向分钟进位状态....................................... - 15 - (四)满六十分向小时进位........................................... - 15 - 七、个人小结........................................................... - 16 -一、任务及要求(一)设计要求(1)利用中规模数字集成器件设计、实现所需电路。

电子技术课程设计----多功能电子时钟的设计

电子技术(下)课程设计题目名称:多功能电子时钟的设计院系名称:电子信息学院班级:学号:学生姓名:指导教师:年月电子技术(下)课程设计任务书姓名学号学院电子信息学院班级题目多功能电子时钟的设计设计任务1、基本部分1)、由振荡电路产生秒脉冲信号;2)、经分频电路、计数电路、译码电路,由数码管显示;3)、秒和分电路为60进制,小时电路为24进制;2、发挥部分1)、可以增加校正电路,对秒、分、小时进行校对;2)、可以增加报时电路,整点前进行“四低一高”报时;时间进度总体时间为1周;星期一上午:讲解;星期一下午:理解电路原理;星期二上午:发放元器件和工具,设计电路和连线;星期四上午:验收电路;星期日之前:上交课程设计报告;主要参考文献[1]康华光。

电子技术基础数字部分(第五版)。

北京:高等教育出版社,2006;[2]康华光。

电子技术基础模拟部分(第五版)。

北京:高等教育出版社,2006;[3]电子技术(下)实验指导书,中原工学院电子技术课程组自编,2011;摘要设计一台可以准确计时,以十进制数显示“时”、“分”、“秒”的多功能电子时钟,小时为24进制,分和秒均为60进制。

多功能电子时钟实际是一个对标准频率(1HZ)进行计数的计数电路,是采用数字电路实现“时”、“分”、“秒”数字显示的计时装置。

通过本课程设计,巩固加强“数字电子技术”课程的理论知识;掌握电子电路的一般设计方法,并了解电子产品研制开发的过程;基本掌握电子电路安装和调试的方法;培养独立分析问题和解决问题的能力以及创新能力和创新思维。

关键词:电子时钟;计数器;AbstractDesign a can accurate timing, in decimal number shows "hour"," minute" and "seconds" multifunctional electronic clock, for 24 hours into the system, minutes and seconds are 60 into the system. Multifunctional electronic clock is actually a for standard frequency (1 HZ) to count count circuit, is the digital circuit implementation digital display timer device. Through this course design, make we strengthen "hour","minute" and "seconds" digital electronic technology" the curriculum theory knowledge; Grasp the electronic circuit of the general design method, and understand the electronic product development development process; Basic grasp the electronic circuit installation and debugging methods; To foster independent analysis and problem-solving ability and creative ability and creative thinking.Key words:Electronic clock; counter;目录中文摘要Abstract第一章绪论 (1)第二章总体方案设计 (1)2.1 设计内容 (1)2.1.1基本部分 (1)2.1.2发挥部分 (1)2.2 原理说明 (1)第三章单元模块设计 (3)3.1 振荡器 (3)3.2 分频器 (6)3.3 计数器 (7)3.4 译码显示电路 (10)3.5校时电路 (11)3.6 整点报时电路 (12)第四章系统的调试与功能 (13)4.1 系统的调试 (13)4.2 系统的功能 (14)第五章心得体会 (15)参考文献 (15)附录一:工具清单 (15)附录二:元器件清单 (16)附录三:主要元器件的引脚图和功能表 (17)第一章绪论随科技的发展,电子产品越来越多的走进人们的生活,工艺也是越来越精湛。

推荐-多功能计时电路的设计数字钟的实验设计 精品

实验1多功能计时电路的设计——数字钟1.1 实验目的1.通过实验掌握十进制加法计数、译码、显示电路的工作过程。

2.通过实验深入掌握电路的分频原理和数字信号的测量方法。

3.熟悉集成电路构成的计数、译码、显示器件的外部功能及其使用方法。

1.2 实验要求1.秒信号发生电路:为计时器提供秒信号2.计时电路:完成0分00秒~9分59秒的计时功能。

3.清零电路:具有开机自动清零功能;在任何时候,按动清零开关,可进行计时器手动清零。

4.译码显示电路:显示计时电路产生的数字信息。

5.系统级联调试:将以上电路进行级联完成计时器的所有功能。

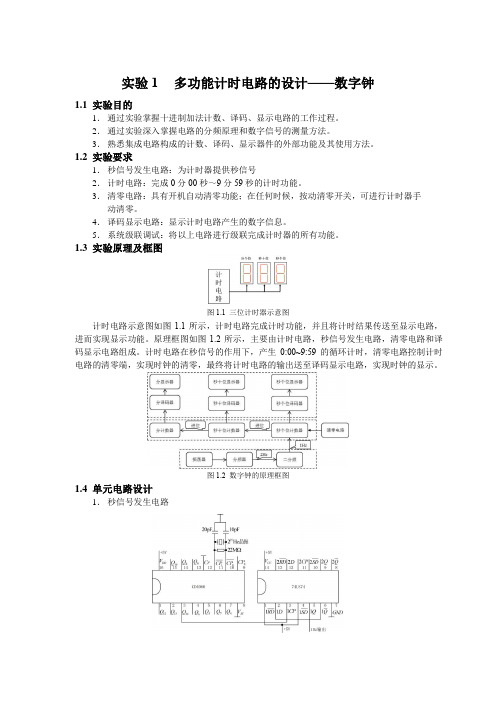

1.3 实验原理及框图图1.1 三位计时器示意图计时电路示意图如图1.1所示,计时电路完成计时功能,并且将计时结果传送至显示电路,进而实现显示功能。

原理框图如图1.2所示,主要由计时电路,秒信号发生电路,清零电路和译码显示电路组成。

计时电路在秒信号的作用下,产生0:00~9:59的循环计时,清零电路控制计时电路的清零端,实现时钟的清零,最终将计时电路的输出送至译码显示电路,实现时钟的显示。

图1.2 数字钟的原理框图1.4 单元电路设计1.秒信号发生电路图1.3 秒信号发生电路秒信号发生电路为计时电路提供驱动信号,电路原理如图1.3所示。

为提供较为精确的秒信号,本设计中振荡电路采用215Hz 的石英晶体管为主体的晶振电路,并作为电路的秒信号源。

由于振荡电路产生的源信号为215Hz ,而秒的基准信号频率为1Hz ,则需要对215Hz 信号进行分频,得到1Hz 信号。

分频器采用CD4060和74LS74来实现,CD4060为14位二进制串行计数器,各管脚功能如表1.1所示,功能表如表1.2所示。

虽然CD4060内部有14级由T 触发器构成的二分频器,但实际输出端只有10个:Q 4~Q 10、Q 12~Q 14。

Q 1~Q 3以及Q 11并不引出。

CP 1̅̅̅̅、CP 0̅̅̅̅̅、CP 0为晶振电路的引出端,需接外部石英晶体。

多功能数字钟的设计及制作

目录整点报时单元电路设计 (1)摘要数字钟被广泛用于个人家庭及公共场所,成为人们日常生活中的必需品。

诸如定时自动报警、按时自动打铃、定时广播、自动起闭路灯、定时开关烘箱、甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。

因此,研究数字钟及扩大其应用,有着非常现实的意。

数字电子钟,从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

数字电子钟有以下几部分组成:振荡器,分频器,60进制的秒、分计时器和12进制计时计数器,秒、分、时的译码显示部分及校正电路等。

关键词:数字钟 555多谐振荡器计数器 74LS390 74LS48数字电子时钟的设计及制作1数字钟的结构设计及方案选择数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。

主要由振荡器、分频器、计数器、译码器显示器和校时电路组成。

振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,通常使用石英晶体震荡器,然后经过分频器输出标准秒脉冲,或者由555构成的多谐振荡器来直接产生1HZ的脉冲信号。

秒计数器满60后向分计数器进位,分计数器满60后向小时计数器进位,小时计数器按照“12翻1”规律计数。

计数器的输出分别经译码器送显示器显示。

由于计数的起始时间不可能与标准时间一致,故需要在电路上加一个校时电路,当计时出现误差时,可以用校时电路校时、校分。

如图 1-1所示为数字钟电路系统的组成框图。

图1-1数字钟电路系统的组成框图方案一:首先构成一个NE555定时器产生震荡周期为秒的标准秒脉冲,在加一个74ls74分频电路。

由74LS390采用清零法分别组成六十进制的秒计数器、六十进制分计数器、十二进制时计数器。

使用74ls74d的输出作为秒记数器的CP脉冲,把秒记数器地进位输出作为分记数器地CP脉冲,分记数器的进位输出作为时记数器的CP脉冲。

使用74LS48为驱动器,共阴极数码管作为显示器,再以基本RS锁存器构成校时电路。

方案二:首先构成一个由石英晶体振荡器和由CD4060构成的分频器构成的产生震荡周期为一秒的标准秒脉冲,由CD4518采用清零法分别组成六十进制的秒计数器、六十进制分计数器、十二进制时计数器。

多功能电子钟设计实验报告

十二翻一模块

时间计数模块

图 4:“12 翻 1”小时计数器

第 8 页 共 17 页

多功能电子钟设计实验报告.doc

表 2:“12”翻一小时计数时序 思路:根据时序表,在 1~9 脉冲的作用下,正常加计数,用瞬时 1010 使触发器翻转, 在 10 号脉冲来到时 LS191 清零,在 12 号脉冲来到时,LS191 变成减法计数器,在 13 号 脉冲来到时,LS74 置 0。

OUTPUT PIN 12 ISTYPE 'COM';

COUNT1=[MG3,MG2,MG1,MG0];

第 11 页 共 17 页

多功能电子钟设计实验报告.doc

COUNT2=[MS2,MS1,MS0]; OUT=[MS2,MS1,MS0,MG3,MG2,MG1,MG0]; C,X=.C.,.X.;

OUTM

PIN 13 ISTYPE 'COM ISTYPE 'COM'; //时计数器的脉冲

"CONST DECLARATIONS

EQUATIONS OUTM=!(S2&CPSS # !S2&CP0); OUTH=!(S1&CPMS # !S1&CP0); 校时电路设计在 GAL3 中,详情请见附录的 GAL3 芯片报告。

仿电台报时电路:

仿电台报时即:在每个小时最后一分钟的 51,53,55,57 秒发出 500Hz 的叫声,在 59 秒发出 1KHz 的叫声。 其逻辑表达式为:OUT_COM=R4 & R6 & R0 & R3 & MS0 & MS2 & MG0 & MG3 & CP1K +

基于单片机的多功能数字时钟的设计课案

本科毕业设计基于单片机的多功能数字时钟负西弱201030580405指导教师XXX 讲师学院名称工程学院专业名称电子信息工程论文提交日期2014年4月30日论文答辩日期2014年5月10日摘要随着数字集成电路的发展和石英晶体与振荡器的广泛应用,数字时钟的精度远远超过了老式钟表,而且能够方便地扩展钟表原先的报时功能,满足人们日常应用的各种需求,数字时钟不管在性能还是功能上都远远超过了传统的钟表。

本设计中的多功能数字时钟采用基于ARM Cortex-M3核心的32 位微控制器STM32F103RCT6作为控制系统的核心,采用内置晶振、具有标准I2C接口的实时时钟芯片SD2403API计算当前的秒、分、时、日、月、年,可保证时钟精度为+5ppm(在25℃±1℃下),通过编程配合芯片内置的数字化时间精度调整电路还可以进一步提高时钟精度,通过2.2寸TFT液晶屏的友好人机界面将结果直观地呈现给用户。

为具有更高的实用价值,利用数字温湿度传感器DHT11获取温湿度,增加了温湿度显示功能;移植Fatfs文件系统读取SD卡的文件,增加了数码相框功能;通过阳历转阴历算法,实现了阴历显示;此外,还增加了红外遥控、闹钟、电子挂历、节日提醒、备忘录等功能。

关键词:Cortex-M3 STM32F103RCT6 数字时钟The Multifunctional Digital Clock Based On Single Chip MicrocomputerFu Dongqiang(College of Engineering, South China Agricultural University, Guangzhou 510642, China) Abstract: With the development and wide application of digital integrated circuits and quartz crystal oscillators , precision digital clock is far more than the old-fashioned clocks, watches and clocks, and can easily extend the original timekeeping features to meet the diverse needs of everyday applications , digital clock regardless of performance or features are far more than the traditional watches .The design of the multi-function digital clock based on ARM Cortex-M3 core, 32-bit microcontrollers STM32F103RCT6 as the core of the control system, with built-in crystal oscillator , with a standard I2C interface, real-time clock chip SD2403API calculate the current seconds , minutes, hours, day, month , year, can guarantee that the clock accuracy of +5 ppm ( at 25 ℃±1 ℃), adjustment circuit programmed with chip built-in digital time accuracy can be further improved clock accuracy , by 2.2 -inch TFT LCD screen and friendly people machine interface will result visually presented to the user . To have a higher practical value , the use of digital temperature and humidity sensor DHT11 get temperature, humidity, increased temperature and humidity display function; transplant Fatfs SD card file system reads files , increasing the digital photo frame function ; through Gregorian lunar transfer algorithm to achieve a lunar display ; addition , it has added an infrared remote control , alarm clock , electronic calendar, festival reminders, memos and other functions.Key words: Cortex-M3 STM32F103RCT6 digital clock目录1 前言 (1)1.1 设计意义 (1)1.2 设计内容 (1)2 总体方案确定 (2)2.1 主控芯片方案 (2)2.2 显示方案 (3)2.3 实时时钟方案 (3)2.4 温湿度传感器方案 (4)2.5 图片存储方案 (4)3 硬件电路设计 (5)3.1 系统总体框图 (5)3.2 STM32F103RCT6最小系统设计 (5)3.3 SD2403电路图设计 (6)3.4 DHT11电路图设计 (7)3.5 TFT显示电路设计 (8)3.6 SD存储卡电路设计 (8)3.7 红外接收电路设计 (9)4 程序设计 (9)4.1 系统初始化流程 (10)4.1.1 SD卡初始化介绍 (10)4.1.2 Fatfs文件系统介绍 (11)4.2 时间调整程序设计 (12)4.3 日期调整程序设计 (14)4.4 闹钟处理程序设计 (15)4.5 节日提醒程序设计 (16)5 调试与调试结果 (16)5.1 硬件调试 (16)5.2 调试结果 (17)6 结论 (17)参考文献 (18)附录 (19)附录A 设计主要电路图 (19)附录B 主要设计程序 (20)致谢 (77)华南农业大学本科生毕业设计成绩评定表1 前言1.1 设计意义自1975年美国德州仪器公司第一块微型计算机芯片TMS-1000问世以来,在短短的20年间,单片机技术已发展成为计算机领域一个非常有前途的分之,它有自己的技术特征、规范和应用领域。

二十四多功能数字钟的设计

实验二十四多功能数字钟的设计钟太绵(2012213696)一、设计框图如下:二、程序代码如下LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.std_logic_arith.all;entity CLOCK28 isport( Clk : in std_logic; --时钟输入1KHZRst : in std_logic; --复位输入S1,S2 : in std_logic; --SPK : out std_logic; --LED: out std_logic_VECTOR(3 DOWNTO 0);DISPLAY : out std_logic_vector(6 downto 0);SEG_SEL : OUT std_logic_vector(2 downto 0) );end CLOCK28;architecture behave of CLOCK28 isTYPE STATES IS(T0,T1,T2,T3);SIGNAL CT,NT:STA TES;SIGNAL CLK1HZ,CLK5HZ:STD_LOGIC;SIGNAL QM,QS:INTEGER RANGE 59 DOWNTO 0;SIGNAL QH:INTEGER RANGE 23 DOWNTO 0;SIGNAL DE:INTEGER RANGE 7 DOWNTO 0;SIGNAL M0,M1,M3,M4,M6,M7,MT,MD:std_logic_vector(3 downto 0); --V ARIABLE M0,M1:STD_LOGIC_VECTOR(3 DOWNTO 0 );SIGNAL FULL,FULL2:STD_LOGIC;SIGNAL BEE,FG:STD_LOGIC;BEGINPROCESS(CLK,FULL)V ARIABLE CNT:integer range 4999 downto 0;--10kHZ CHANGE TO 1HZV ARIABLE CNT1:STD_LOGIC;BEGINIF CLK'EVENT AND CLK='1' THENIF CNT=4999 THENCNT:=0;FULL<='1';ELSECNT:=CNT+1;FULL<='0';END IF;BEE<=NOT BEE;END IF;IF FULL'EVENT AND FULL='1' THENCNT1:=NOT CNT1;IF CNT1='1' THENCLK1HZ<='1';ELSECLK1HZ<='0';END IF;END IF;END PROCESS;PROCESS(CLK,FULL2)V ARIABLE CNT:integer range 2499 downto 0;--10kHZ CHANGE TO 5HZ V ARIABLE CNT1:STD_LOGIC;BEGINIF CLK'EVENT AND CLK='1' THENIF CNT=2499 THENCNT:=0;FULL2<='1';ELSECNT:=CNT+1;FULL2<='0';END IF;--BEE<=NOT BEE;END IF;IF FULL2'EVENT AND FULL2='1' THENCNT1:=NOT CNT1;IF CNT1='1' THENCLK5HZ<='1';ELSECLK5HZ<='0';END IF;END IF;END PROCESS;PROCESS(CLK)BEGINIF CLK'EVENT AND CLK='1' THENCT<=NT;END IF;END PROCESS;PROCESS(CLK,RST)BEGINIF(RST='0')THENNT<=T0;ELSIF CLK'EVENT AND CLK='1' THENCASE CT ISWHEN T0=>NT<=T1;WHEN T1=>IF(QS=50 and QM=59)THENNT<=T2;END IF;WHEN T2=>IF(QS=55 and QM=59)THENNT<=T3;END IF;WHEN T3=>IF(QS=0 and QM=0)THENNT<=T1;END IF;WHEN OTHERS=>NT<=T0;END CASE;END IF;END PROCESS;PROCESS(CLK)V ARIABLE S,M:INTEGER RANGE 59 DOWNTO 0;V ARIABLE H:INTEGER RANGE 23 DOWNTO 0;V ARIABLE F1,F2:INTEGER;BEGINIF(RST='0')THENS:=0;M:=0;H:=0;ELSIF CLK1HZ'EVENT AND CLK1HZ='1' THEN FG<=NOT FG;S:=S+1;IF(S>59) THEN-- OR S2='0' OR S1='0';S:=S REM 60;M:=M+1;END IF;IF(M>59) THENM:=M REM 60;H:=H+1;END IF;IF(H>23)THENH:=H REM 24;END IF;END IF;IF CLK5HZ'EVENT AND CLK5HZ='1' THENIF(S2='0') THENF2:=1;ELSEF2:=0;END IF;IF(S1='0') THENF1:=1;ELSEF1:=0;END IF;END IF;QS<=S;QM<=M+F2;QH<=H+F1;END PROCESS;PROCESS(CT,CLK1HZ)BEGINCASE CT ISWHEN T0=>SPK<=BEE;LED<="1111";--QS<=0;QM<=0;QH<=0;WHEN T1=>SPK<='0';LED<="0000";WHEN T2=>SPK<=BEE;LED<="0000";WHEN T3=>SPK<=BEE;IF FG='1' THENLED<="1111";ELSELED<="0000";END IF;WHEN OTHERS=>SPK<='0';LED<="0000";END CASE;END PROCESS;PROCESS(QS)V ARIABLE K0,K1:integer range 59 downto 0;BEGINK0:=QS;K1:=K0/10;M0<=CONV_STD_LOGIC_VECTOR(K0 REM 10,4);M1<=CONV_STD_LOGIC_VECTOR(K1 REM 10,4);END PROCESS;PROCESS(QM)V ARIABLE K0,K1:integer range 59 downto 0;BEGINK0:=QM;K1:=K0/10;M3<=CONV_STD_LOGIC_VECTOR(K0 REM 10,4);M4<=CONV_STD_LOGIC_VECTOR(K1 REM 10,4); END PROCESS;PROCESS(QH)V ARIABLE K0,K1:integer range 23 downto 0;BEGINK0:=QH;K1:=K0/10;M6<=CONV_STD_LOGIC_VECTOR(K0 REM 10,4);M7<=CONV_STD_LOGIC_VECTOR(K1 REM 10,4); END PROCESS;PROCESS(CLK)BEGINMT<="1111";IF CLK'EVENT AND CLK='1' THENDE<=DE+1;END IF;CASE DE ISWHEN 0=>MD<=M7;WHEN 1=>MD<=M6;WHEN 2=>MD<=MT;WHEN 3=>MD<=M4;WHEN 4=>MD<=M3;WHEN 5=>MD<=MT;WHEN 6=>MD<=M1;WHEN 7=>MD<=M0;WHEN OTHERS=>MD<="0000";END CASE;SEG_SEL<=CONV_STD_LOGIC_VECTOR(DE,3); END PROCESS;PROCESS(MD)BEGINCASE MD ISWHEN "0000"=>Display<="0111111";WHEN "0001"=>Display<="0000110";WHEN "0010"=>Display<="1011011";WHEN "0011"=>Display<="1001111";WHEN "0100"=>Display<="1100110";WHEN "0101"=>Display<="1101101";WHEN "0110"=>Display<="1111101";WHEN "0111"=>Display<="0000111";--7WHEN "1000"=>Display<="1111111";--8WHEN "1001"=>Display<="1101111";--9WHEN "1111"=>Display<="1000000";-- -WHEN OTHERS=>NULL;END CASE;END PROCESS;END BEHA VE;三、modelsim波形仿真如图。

集成电路设计中的时钟设计研究

集成电路设计中的时钟设计研究集成电路是现代电子技术中十分重要的一部分,在各种电子设备中都有广泛应用。

集成电路设计的核心问题之一是时钟设计。

时钟信号在数字电路中起着非常重要的作用。

本文将围绕集成电路设计中的时钟设计问题进行研究探索。

一、时钟设计的基本原理时钟信号是一个周期性的信号,周期性是指信号的波形能够在一定时间内重复出现。

时钟信号可以用一定的频率周期性地改变电路的状态,以便控制电路的运行。

在数字电路中,时钟信号的频率通常表现为高频,以便快速操纵电路的状态。

实际上,时钟信号的频率越高,则电路的响应时间越短,系统处理速度也就越快。

时钟设计的目标是使得时钟信号的稳定性和准确性可以满足电路运行的需求。

在集成电路中,时钟信号的稳定性和准确性是至关重要的,因为这直接关系到系统的运行效率和可靠性。

在设计时钟电路时,需要考虑以下几个方面。

1. 时钟信号的质量时钟信号的质量反映的是信号的稳定性和准确性。

时钟信号的稳定性主要指时钟信号的波形是否同步和稳定。

时钟信号的准确性主要体现在时钟信号的频率和相位是否准确。

如果时钟信号波形不同步或不稳定,会导致数字电路的错误操作,从而影响系统的运行。

如果时钟频率和相位不准确,则会导致电路发生误差,从而使系统输出结果产生偏差,这对系统可靠性和精度影响很大。

2. 噪声抑制在数字电路中,时钟信号的抖动(jitter)是十分常见的。

抖动是指时钟信号波形的不稳定性。

抖动可以分为周期性抖动和随机抖动两种类型,不同类型的抖动都会对电路产生一定的影响。

周期性抖动会导致电路产生不规则的振荡,从而影响系统的性能;随机抖动则会使信号产生噪声,从而降低系统的信噪比,影响系统的稳定性。

3. 稳定性时钟信号的稳定性是指时钟信号的波形以及频率和相位的稳定程度。

当时钟信号的波形稳定,时钟频率和相位准确时,电路的稳定性才能得到保障。

此外,在时钟设计中,需要考虑电路的温度漂移、电压漂移等因素的影响,以保证时钟信号的稳定性。

用集成电路LM8560的电子钟

IC2(CD4060)、JT、R2、C2 构成 50HZ 的时基电路,CD4060 内部 包含 14 为二分频器和一个振荡器,电路简洁,30720HZ 的信号经分 频后,得到 50HZ 信号送到 LM8560 的 25 脚,并作出秒信号经 YT2、 VT3 驱动显示屏的冒号闪动。

当调好定时间后并按下开关 K1(白色键),显示屏右下方有红 点指示,到定时时间有驱动信号经 R3 使 VT1 工作,即可定时报警输 出。

二 交流电源部分

电路需要直流供电,所以需要经过整流滤波电路得到稳定的直流电。 整流桥为全波整流得到脉动的直流电,电容充放电滤波之后电压趋于 稳定。变压器得到的为6V 电压,提供给整个电路。当交流电断电时, 由4节1.5V 电池组成的6V 电源继续供电,但显示屏只有交流电供给, 所以此时的功耗较低,电池组只是保障走时的准确,再次上电时,时 钟又会从准确的时刻走时。

120k、1M

7 电阻

6.8k

各一只

只

3

只

8

LED 显 FTTL-655

示器

G

9 蜂鸣器 Ǿ12×9

10 晶振 30.720k

11 电源变 220V/9V/2

压器

W

12 瓷片电 20P、103P 容

13 电解电 220UF、

容

1000UF

14 轻触开 6×6×17 关

15 自锁开 关

7×7

1

块

1

个只

只

4

个

1

个

五 芯片资料: LM8560 是一种大规模时钟集成电路它与双阴极显示屏组可以制

成数字钟钟控电路。作为时钟,它准确醒目;作为控制开关,它动作 无误;在 1 小时 59 分钟或 59 分钟内,能任意暂停,使用十分方便。

多功能电子钟的设计与实现课程设计说明

多功能电子钟的设计与实现课程设计说明多功能电子钟的设计与实现摘要电子时钟主要是利用电子技术将时钟电子化、数字化,拥有时钟精确、体积小、界面友好、可扩展性能强等特点,被广泛应用于生活和工作当中。

另外,在生活和体育赛场中,也常常需要跑秒,这就需要电子时钟具有多功能性。

本设计主要为实现一款可正常显示时钟,带有定时闹铃,跑秒的多功能电子时钟。

本文对当前电子钟开发手段进行了比较和分析,最终确定了采用单片机技术实现多功能电子时钟。

本设计应用AT89C51芯片作为核心,利用74LS164作为串入并出的寄存器,7位LED数码管显示,并且设置按键来对分秒小时闹铃等进行校对。

这种实现方法的优点是电路简单,性能可靠,实时性好,时间精度高,操作简单,编程容易。

该电子时钟可以应用于一般的生活和工作中,也可通过改装,提高性能,增加新功能,从而给人们的生活和工作带来更多的方便。

关键词:电子时钟;AT89C51;74LS164;LED;The Design with Investigation of the Multi-function Electron ClockAbstractElectronic clock is the use of electronic technology will be an electronic clock, digital, with the clock precision, small size and friendly interface, scalable performance, and other characteristics, are widely used to live and work. In addition, in the field of sports and life, often need to run second, which requires electronic clock with versatility.The main design for the realization of this can be a normal clock display, from time to time with alarm, running the second multi-function electronic clock.This article on the current development of the electronic clock means were compared and analyzed to determine the ultimate use of a single chip multifunctional electronic clock technology. AT89C51 chip design of this application as the core, to use as a 74LS164 and a string into the register, 7 LED digital display and button set up to every minute of the hour for alarm, and other proof-reading. This method has the advantage of a simple circuit, reliable and real-time, high-accuracy time, simple, easy to program.The electronic clock can be applied to general life and work, can also be modified to improve performance, add new functions to the people living and working more convenient.Key words: Electronic clock; AT89C51; 74LS164; LED;目录摘要 (I)Abstract .................................................................................................................................... I I 第一章引言 . (5)1.1 多功能电子时钟研究的背景和意义 (5)1.2 电子时钟的功能 (6)第二章电子时钟设计方案分析 (7)第三章基于单片机的电子时钟硬件设计 (8)3.1 主要IC芯片选择 (8)3.1.1微处理器的选择 (8)3.1.2寄存器的选择 (11)3.1.3显示器件的选择 (12)3.1.4看门狗器件的选择 (14)3.2 电子时钟硬件电路设计 (14)3.2.1 显示电路 (15)3.2.2 按键电路设计 (15)3.2.3 闹铃电路设计 (17)3.2.4 复位电路设计 (18)第四章电子时钟软件设计 (20)4.1 主程序设计 (20)4.2 子程序设计 (21)4.2.1 显示子程序设计 (21)4.2.2 键盘扫描子程序 (21)4.2.3闹铃子程序设计 (23)4.2.4跑秒子程序设计 (23)第五章系统调试 (24)5.1 硬件调试 (24)5.1.1 单片机基础电路调试 (24)5.1.2 显示电路调试 (25)5.2 软件调试 (27)结论 (28)参考文献 (29)附录A 程序............................................................................................................................... 附录B 多功能电子时钟硬件电路图......................................................................................... 致谢 .. (30)第一章引言时间是人类生活必不可少的重要元素,如果没有时间的概念,社会将不会有所发展和进步。

多功能电子时钟设计(汇编语言完美版)

多功能电⼦时钟设计(汇编语⾔完美版)电⼦时钟实验报告⼀,实验⽬的1. 学习8051定时器时间计时处理、按键扫描及LED数码管显⽰的设计⽅法。

2. 设计任务及要求利⽤实验平台上4个LED数码管,设计带有闹铃功能的数字时钟⼆,实验要求A.基本要求:1. 在4位数码管上显⽰当前时间。

显⽰格式“时时分分”2. 由LED闪动做秒显⽰。

3. 利⽤按键可对时间及闹玲进⾏设置,并可显⽰闹玲时间。

当闹玲时间到蜂鸣器发出声响,按停⽌键使可使闹玲声停⽌。

4.实现秒表功能(百分之⼀秒显⽰)B.扩展部分:1.⽇历功能(能对年,⽉,⽇,星期进⾏显⽰,分辨平年,闰年以及各⽉天数,并调整)2.⾳乐闹铃(铃⾳可选择,闹铃被停⽌后,闪烁显⽰当前时刻8秒后,或按键跳⼊正常时间显⽰状态)3.定时功能(设定⼀段时间长度,定时到后,闪烁提⽰)4.倒计时功能(设定⼀段时间长度,能实现倒计时显⽰,时间长减到0时,闪烁提⽰)5.闹铃重响功能(闹铃被停⽌后,以停⽌时刻开始,⼀段时间后闹铃重响,且重响时间的间隔可调)三,实验基本原理利⽤单⽚机定时器完成计时功能,定时器0计时中断程序每隔0.01s中断⼀次并当作⼀个计数,设定定时1秒的中断计数初值为100,每中断⼀次中断计数初值减1,当减到0时,则表⽰1s到了,秒变量加1,同理再判断是否1min钟到了,再判断是否1h到了。

为了将时间在LED数码管上显⽰,可采⽤静态显⽰法和动态显⽰法,由于静态显⽰法需要译码器,数据锁存器等较多硬件,可采⽤动态显⽰法实现LED显⽰,通过对每位数码管的依次扫描,使对应数码管亮,同时向该数码管送对应的字码,使其显⽰数字。

由于数码管扫描周期很短,由于⼈眼的视觉暂留效应,使数码管看起来总是亮的,从⽽实现了各种显⽰。

四,实验设计分析针对要实现的功能,采⽤AT89S51单⽚机进⾏设计,AT89S51 单⽚机是⼀款低功耗,⾼性能CMOS8位单⽚机,⽚内含4KB 在线可编程(ISP)的可反复擦写1000次的Flash只读程序存储器,器件采⽤⾼密度、⾮易失性存储技术制造,兼容标准MCS-51指令系统及80C51引脚结构。

多功能数字钟的设计及制作

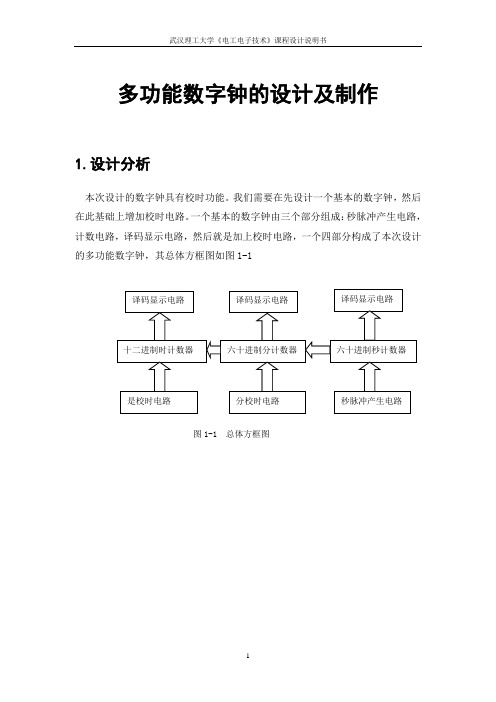

多功能数字钟的设计及制作1.设计分析本次设计的数字钟具有校时功能。

我们需要在先设计一个基本的数字钟,然后在此基础上增加校时电路。

一个基本的数字钟由三个部分组成:秒脉冲产生电路,计数电路,译码显示电路,然后就是加上校时电路,一个四部分构成了本次设计的多功能数字钟,其总体方框图如图1-1图1-1 总体方框图2.设计内容2.1秒脉冲产生部分本设计使用由555定时器构成的多谐振荡器来产生1HZ的信号。

虽然此振荡器没有石英晶体稳定度和精确度高,由于设计简单而成为了设计时的首选。

只要在555定时器电路外部配上两个电阻及两个电容元件,并将某些引脚相连,就可以方便地构成多谐振荡器。

555定时器是数字脉冲产生的核心芯片,所以在了解其原理之前,我们需了解555定时器。

555定时器逻辑符号如图2-1所示:图2-1 555定时器逻辑符号管脚功能如表2-1所示:图2-2 秒脉冲电路根据原理和元件图,结合一阶电路暂态过程的三要素法,可以计算出充放电的时间,两者相加即为脉冲周期,脉冲周期的倒数即为脉冲频率。

充电过程的方程式: 2/3Vcc=Vcc+(1/3Vcc-Vcc)e(t1/RC)t1=(R1+R2)C*㏑2=0.7(R1+R2)C放电过程的方程式: 1/3Vcc=0+(2/3Vcc-0)e(t1/RC)t2=R2*C㏑2=0.7R2*C脉冲周期为: t=t1+t2=0.7(R1+2R2)C脉冲频率为: f=1/t=1.43/(R1+2R2)C令R1=15k,R2=68k,C=0. 01F,(其中0.01F的电容的作用是防干扰的)代入数据,计算得,f=0.94HZ≈1HZ基本满足实验要求。

2.2计数部分计数部分的核心芯片是74LS9074LS90是二---五---十进制异步计数器。

它有两个时钟输入CKA和CKB,其中,CPA和Q0组成一位二进制计数器,CKB和Q1Q2Q3组成五进制计数器,若将Q0与CKB相连接,时钟脉冲从CKA输入,则构成了84212BCD码十进制计数器。

课程设计(论文)基于lcd液晶显示的多功能数字钟的设计(附pcb图及电路原理图)

目录1前言 (1)2总体方案设计 (2)2.1设计内容 (2)2.2设计内容 (2)2.3方案论证 (3)2.4方案选择 (4)3单元模块设计 (5)3.1各单元模块功能介绍及电路设计 (5)3.1.1 温度采集电路 (5)3.1.2 DS1302时钟电路 (5)3.1.3 串行通信接口电路 (6)3.1.4 USB连接电路 (6)3.1.5 按键电路 (7)3.1.6液晶显示显示电路 (7)3.2特殊器件介绍 (7)3.2.1 STC89C52单片机芯片 (7)3.2.2 DS1302介绍 (8)3.2.3 温度传感器DS18B20 (9)3.2.4 液晶显示LCD1602 (9)4软件设计 (10)4.1软件选择 (10)4.2软件设计流程 (10)4.2.1 温度采集流程 (11)4.2.2 日期数据处理流程 (12)5系统的仿真及调试 (13)5.1系统仿真 (13)5.2硬件调试 (13)5.3软件调试 (14)6结论 (16)7总结与体会 (17)7.1设计小结 (17)7.2设计收获及改进 (17)7.3致谢 (17)8参考文献 (18)附录: (19)1前言单片机是指一个集成在一块芯片上的完整计算机系统。

尽管他的大部分功能集成在一块小芯片上,但是它具有一个完整计算机所需要的大部分部件:CPU、内存、内部和外部总线系统,目前大部分还会具有外存。

同时集成诸如通讯接口、定时器,实时时钟等外围设备。

而现在最强大的单片机系统甚至可以将声音、图像、网络、复杂的输入输出系统集成在一块芯片上。

单片机也被称为微控制器(Microcontroller),它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上。

概括的讲:一块芯片就成了一台计算机。

它的体积小、质量轻、价格便宜、为学习、应用和开发提供了便利条件。

单片机诞生于20世纪70年代末,经历了SCM、MCU、SOC三大阶段。

STC单片机完全兼容51单片机,并有其独到之处,其抗干扰性强,加密性强,超低功耗,可以远程升级,内部有专用复位电路,价格也较便宜,由于这些特点使得 STC 系列单片机的应用日趋广泛。

单片机课程设计 多功能数字钟的设计

摘要电子钟在日常生活中最常见,应用也最广泛。

作为一种定时工具被广泛的使用在生产生活的各方面。

人类最初依靠太阳的角度来进行定时,所以受天气的影响比较大,为了克服依靠自然现象定时的缺点人们发明的机器钟表,电子钟表一系列的定时工具。

而电子钟表具有价格便宜,质量轻,定时误差小等优点,被广泛的应用在生产,生活的各个方面。

由于电子钟的能提供精确定时又被广泛的运用在测量之中。

此电子钟采用单片机进行设计,8 段数码通过单片机进行刷新显示。

其设计的产品除了单片机之外没有用到其他集成块,使其成本可以大大降低,而其便于维修。

成品可以被广泛的用于公共场所,匾额装饰,以及教案等方面。

本文主要就是设计一款数字钟, AT89C51 单片机为核心,以配备 LED 显示模块、键盘输入模块、等功能模块。

数字钟采用 24 小时制方式显示时间,定时信息以及年月日显示等功能。

文章的核心主要从硬件设计和软件编程两个大的方面。

1目录摘要...... 1 1 设计要求及方案确定...... 3 1.1 设计要求...... 3 1.2 方案确定...... 3 2 硬件电路设计及描述...... 3 2.1 确定元器件的型号及参数...... 3 2.1.1 单片机的选择...... 3 2.1.2 AT89C51 单片机的介绍...... 5 2.1.3 LED 数码管显示模块...... 7 2.1.4 键盘输入模块 (8)2.1.5 闹铃模块...... 8 2.1.6 电源电路...... 8 2.1.7 蜂鸣器的介绍...... 9 2.2 硬件电路图 (10)3 软件设计...... 10 3.1 程序结构设计...... 10 3.1.1 程序结构...... 10 3.1.2 主要程序模块清单...... 11 3.2 程序...... 14 4 参考文献...... 17 结束语 (18)211.1 设计要求设计要求及方案确定利用单片机设计制作具有下列功能的数字钟:①自动计时,由 6 位 LED 显示器显示时、分和秒②具备调整功能,可以直接由 0~9 数字键设置当前时间;③具备定时闹钟功能。

多功能数字钟电路设计

多功能数字钟电路设计

多功能数字钟电路可以用来显示时间、日期、闹钟和定时器等功能。

下面是一个简单的多功能数字钟电路设计,它基于CD4511七段译码器和CD4543 BCD-七段译码器。

1. 时间显示功能

为了显示时间,我们需要使用CD4543 BCD-七段译码器。

该译码器接收来自实时时钟(RTC)模块的BCD编码输出。

RTC模块可以用来跟踪时间和日期,它通常包括一个晶体振荡器、计数器和存储器。

BCD 编码输出通过CD4543译码器转换为七段LED显示。

2. 日期显示功能

类似于时间显示功能,日期显示也需要使用RTC模块。

RTC模块可以提供年份、月份和日期的BCD编码输出。

这些编码输出通过CD4543译码器转换为七段LED显示。

3. 闹钟功能

闹钟功能可以通过计时器和比较器实现。

我们可以使用555定时器作

为计时器,它可以生成一个固定的时间间隔。

然后,我们可以使用一个比较器来比较当前时间和闹钟时间。

如果它们匹配,闹钟就会响起。

4. 定时器功能

定时器功能可以通过555定时器来实现。

我们可以设置计时器的时间间隔,并使用CD4511七段译码器来显示剩余时间。

当定时器完成计时时,它可以触发一个报警器或执行其他操作。

总之,多功能数字钟电路可以实现时间、日期、闹钟和定时器等多种功能。

这些功能可以通过RTC模块、CD4511七段译码器、CD4543 BCD-七段译码器和555定时器等元件来实现。

多功能集成电路设计

多功能集成电路设计随着科技的不断发展,电子产品的功能和性能不断提升,而其核心——集成电路也在不断发展与创新。

多功能集成电路是一种集成了多种功能模块的电路,通常用于系统控制、数字信号处理、模拟信号处理等领域。

在本文中,我们将介绍多功能集成电路的设计流程、常见模块和优化技术。

设计流程多功能集成电路的设计流程可以分为以下几步:1.需求分析:明确电路的使用场景、功能需求和性能指标。

2.电路设计:根据需求,设计适合的电路结构和电路原理图。

3.电路验证:通过模拟仿真或实际试验验证电路的性能和可靠性。

4.布局和布线:将电路的元器件按照一定的布局方式排列,并进行电路布线。

5.制造和测试:通过CMOS制造工艺将电路印制在芯片上,然后通过测试确认电路性能和可靠性。

常见模块多功能集成电路包含了许多常见的模块,以下为其中一些典型的模块:1.时钟电路:提供时钟信号以统一各模块节拍和使系统同步。

2.存储器:存储微处理器所需程序代码和数据,以及各种中间结果。

3.数字信号处理器:用于数字信号处理,并能与其他模块实现数据互换。

4.模拟-数字转换器:将模拟电信号转换为数字信号,实现数字信号处理。

5.电源管理电路:负责电源管理、测量和监控电源电压、电流和温度。

优化技术多功能集成电路的优化技术包括以下方面:1.功耗优化:采用低功率设计技术,如电源监控技术、核间电压阀值等技术,降低功耗。

2.低噪声优化:透过缩小集成电路中线圈和电容,优化互相干扰。

3.时钟优化:采用多个电源和平衡布局等技术,使时钟信号更稳定与准确。

4.散热优化:针对高密度的设计板卡来进行优化,采用散热装置,降低电路温度,延长电路使用寿命。

结语多功能集成电路的应用越来越广泛,然而,其设计与制造难度也随之提高。

为了保证电路的性能和可靠性,需要采用科学的设计流程和优化技术,才能达到最佳的技术性价比和客户满意度。

多功能电子时钟的设计

4.1 多功能电子时钟的设计一、技术指标1.设计一台能准确计时,以十进制数形式显示“时”、“分”、“秒”的多功能电子时钟钟;2.小时为24进制,分和秒均为60进制;3.有校时功能,可以分别对“时”、“分”信号进行单独校对;4.能整点报时。

要求报时声为四低一高,最后一响为整点。

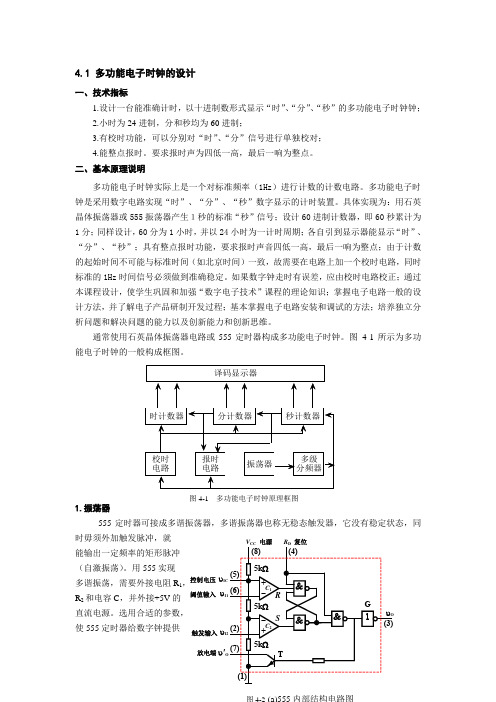

二、基本原理说明多功能电子时钟实际上是一个对标准频率(1Hz )进行计数的计数电路。

多功能电子时钟是采用数字电路实现“时”、“分”、“秒”数字显示的计时装置。

具体实现为:用石英晶体振荡器或555振荡器产生1秒的标准“秒”信号;设计60进制计数器,即60秒累计为1分;同样设计,60分为1小时,并以24小时为一计时周期;各自引到显示器能显示“时”、“分”、“秒”;具有整点报时功能,要求报时声音四低一高,最后一响为整点;由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1Hz 时间信号必须做到准确稳定。

如果数字钟走时有误差,应由校时电路校正;通过本课程设计,使学生巩固和加强“数字电子技术”课程的理论知识;掌握电子电路一般的设计方法,并了解电子产品研制开发过程;基本掌握电子电路安装和调试的方法;培养独立分析问题和解决问题的能力以及创新能力和创新思维。

通常使用石英晶体振荡器电路或555定时器构成多功能电子时钟。

图 4-1所示为多功能电子时钟的一般构成框图。

1.振荡器555定时器可接成多谐振荡器,多谐振荡器也称无稳态触发器,它没有稳定状态,同时毋须外加触发脉冲,就 能输出一定频率的矩形脉冲 (自激振荡)。

用555实现 多谐振荡,需要外接电阻R 1R 2和电容C ,并外接+5V 的 使555定时器给数字钟提供 图4-1 多功能电子时钟原理框图一个频率稳定准确的1k Hz 的方波信号,可保证数字钟 的走时准确及稳定。

555定 时器的内部结构电路图、外部接线图、c u 及o u 波形图,图4-2 (b) 555外部接线图图4-2 (c) c u 及o u 波形图 第一个暂稳状态的脉冲宽度PHt ,即c u 从CC V 1充电上升到CC U 32所需的时间: C R R t PH )(7.021+=第二个暂稳状态的脉冲宽度PL t ,即c u 从CC U 32放电下降到CC U 31所需的时间: C R t PL 27.0=振荡周期: C R R t t T PL PH )2(7.021+=+= 振荡频率: CR R T f )2(43.1121+==为得到1k Hz 的方波信号可选择:W =k R 1.51、W =k R 7.42、F C μ1.0=。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的多功能时钟设计报告目录摘要 (3)设计内容及要求 (3)设计(代码)分析 (4)实验过程及步骤 (5)实验结果的测试及仿真 (13)实验总结与感想 (16)参考文献 (17)附录(原代码) (17)1摘要在学习了专用集成电路和verilog语言及数电的相关知识后,运用所学知识及查阅资料完成对多功能时钟的设计,以巩固以前所学知识,提高解决和分析问题的能力以及掌握稍复杂逻辑电路的设计方法;深刻理解verilog语言的思路,并进一步掌握操作BASYS2板的使用;掌握计数器的设计方法,模块之间的协调方式,了解电路设计层次。

2 设计内容及要求多功能时钟设计分为基本电路部分和拓展功能部分和特色部分。

基本电路部分●以数字形式显示时、分、秒的时间;(要求可切换显示)●小时计数器为同步24进制;(同步计数器)●可精确手动校时,包括小时,分钟,秒;设有按钮,每按一次相应按钮可使对应的时间循环改变,以校时用手动校时时,长按按钮可加速校时速度。

拓展部分●可设定24小时任意时刻闹钟(精确到秒),设定按钮与校时按钮共用。

设有闹钟开关键●整点报时59分51秒59分53秒59分55秒59分57秒led[7:4]流水灯式依次点亮以模仿电台播音(频率为1HZ)59分59秒时 led灯led[3]点亮频率为10HZ 特色部分stopwatch可储存记忆10组59分59秒99内时间数据的秒表。

可显示记录的数据个数和对应顺序精确到1/100秒设有 swo(秒表模式开启键) ————K3swp(暂停键) ————————L3scrl(数据控制键)——————B4Ncr(清零复位键)—————— A7counter(记录数据键)———— M4- (数据加键) ———————— C11+ (数据减键)————————G12Switch (显示切换键)---------------P113代码分析top_clock总共分为顶层和底层●顶层top.v计时部分:调用底层模块10位计数器6位计数器3位计器4*6=24位寄存器cnt[23:0]Cnt[3:0] second0 cnt[7:4] second1Cnt[11:8] minute0 cnt[15:12] minute1Cnt[19:16] hour0 cnt[23:20] hour1校时部分:设计为信号选择器ad=1时为计时模式,信号为校时信号ad =0时为正常计时模式数据显示部分:设有切换switch端数码管扫描自动扫描1KHZ4*8=32位寄存器Temp[31:0]分为校时模式显示ad=1 set=0 swo=0 ------------ cnt闹钟设置模式显示ad=0 set=1 swo=0------------ cnt1秒表计时模式显示ad=0 set=0 swo=1------------ cnt2正常走时模式显示其余---------------------------------- cnt●底层部分计数器counter10.v counter6.v counter3.v// counter10.v(0~9)module counter10(en,ncr,clk,q);input en,ncr,clk;output [3:0] q;reg [3:0] q;always@(posedge clk )beginif(ncr) q<=4'd0;//ncr=0时,异步清零else if(~en) q<=q;// EN=0,暂停计数else if (q==4'b1001) q<=4'b0000;else q<=q+1;//计数器加1endendmodule闹钟设定模块bell.v cnt1 代码见附录仿电台报时radio.v 代码见附录秒表stopwatch.v cnt2 代码见附录4实验内容及步骤(1)创建工程命名为top_clock(2)选择BASYS2型号并完成创建(3)新建verilogmodule文件命名为top完整代码见附录(4)检查语法直至通过双击Synthesize—XST(5) 创建时钟信号约束即CLK(6) 创建管脚约束双击管脚设置为管脚分布a[0]-a[3]---------→K14 F12 J12 M13 数码管扫描信号adj[0]—adj[3]--→G12 C11 M4 A7 校时及闹钟设定及秒表按钮led[0]-----led[7]--→M5 M11 P7 P6 N5 N4 P4 G1 led灯segs[0]---segs[6]-→L14 H12 N14 N11 P12 L13 M12 数码管rcrl→F3 仿电台播报开关scrl--→B4 秒表显示切换开关bcrl→N3 闹铃开关set→E2 闹钟设定按钮ad→G3 校时按钮switch→P11 显示切换按钮swo→K3 秒表开关swp→L3 秒表暂停开关CLK→B8 时钟信号50MHz(7) 逻辑综合(8) 下载到BASYS2板上打开bit文件下载到板子上在板子上试验1。

正常走时模式Switch=1 时显示分分:秒秒Switch=0时显示时时:分分2。

手动校时模式ad=1 set=0 swo=03,闹钟设定和开关模式(brcl)N3 ->闹铃(led灯)开关闹铃响时M11 M5亮灯以10MHZ 闪烁闹铃设定ad=0 set=1 swo=0设置方法和校时方法共用键(A7 M4 C11 G12)方法相同4,秒表模式ad=0 set=0 swo=1(swp) 暂停键低电平有效A7 清零键(包括数据清零)M4 记录数据键每按一次记录一个时间数据(59分59秒99以内)可记录10组数据并可显示当前数据的序号Switch=0时[ ] [ ] [ ] [ ]^ ^ ^ ^显示C 数据序号分分Switch=1时[ ] [ ] [ ] [ ]^ ^ ^ ^秒秒0.1秒0.01秒(5) 实验结果的测试和仿真仿真波形如下:Counter10Counter6Counter3BellRadio实验结果及说明:(1)正常走时模式Switch=1 时显示分分:秒秒Switch=0时显示时时:分分;(2)手动校时模式ad=1 set=0 swo=0使ad=1,每按一下[ ] [ ] [ ] [ ] switch=1,每按一下循环加一(分分秒秒)A7 M4 C11 G12[ ] [ ] [ ] [ ] A7 M4 C11 G12switch=0,每按一下循环加一(时时分分)A7 M4 C11 G12例如设定为20:12:08(3)闹钟设定和开关模式(brcl)N3 ->闹铃(led灯)开关闹铃响时M11 M5亮灯以10MHZ 闪烁闹铃设定ad=0 set=1 swo=0设置方法和校时方法共用键(A7 M4 C11 G12)方法相同(4)秒表模式ad=0 set=0 swo=1(swp) 暂停键低电平有效A7 清零键(包括数据清零)M4 记录数据键每按一次记录一个时间数据(59分59秒99以内)可记录10组数据并可显示当前数据的序号Switch=0时[ ] [ ] [ ] [ ]^ ^ ^ ^显示C 数据序号分分Switch=1时[ ] [ ] [ ] [ ]^ ^ ^ ^秒秒0.1秒0.01秒C11 (—)数据减键序号循环减一最小为1G12(+)数据加键序号循环加一最大为9序号即为数据记录的顺序(5)其他按法皆为正常走时模式6实验总结与感想通过多功能时钟的设计过程,我深刻的感觉到复杂电路设计的思路和方法特别重要,好的方法不仅省时省力,也可使程序运行更稳定快速高效。

此次的多功能时钟分为好几个大的模块,怎样能恰当好处的连接这些模块是需要经验的,通过这次试验我也初步积累到了一些经验:端口尽量不要太多,能调用模块尽量调用,可省时省力,模块与模块之间尽量独立,但又要设置好端口之间的连接,中间变量不宜过多,但适当的中间变量省下不好麻烦。

例如我就设置啦显示的中间变量temp【31:0】通过不同的模式转换将不同的值赋给temp变量,这样显示的代码就可重复使用。

与此同时,在设计中也还有值得改进的地方,就是按钮使用过多,操作方法显得有些复杂,可以进一步优化改进。

遇到的最主要的问题:秒表设计模块中的1/100秒在数码管上无法正常快速显示(由于led灯的余辉效应造成)记录数据时的准确度也就下降,人们正常按键时间或大于0.01秒所以秒表的十分位为准确位百分位不准确7参考文献【1】《Verilog hdl与数字asic设计基础》8.4 和8.5(罗杰主编)(8)附录(源代码)module top(set,ad,swo,swp,switch,bcrl,rcrl,scrl,,clk,adj,segs,a,led);input ad,set,swo,bcrl,rcrl,scrl,swp,switch,clk;//定义输入端口input [3:0] adj;output [6:0] segs;//数码管output [3:0] a;//扫描输出output [7:0] led;//led灯reg [3:0] a;reg [6:0] segs;//shu ma guanreg [31:0] temp;wire [23:0] cnt;//走时模式和校时模式临时变量wire [23:0] cnt1;//闹钟模式临时变量wire [31:0] cnt2;// 秒表模式临时变量//使能信号initial begina=4'b1110;end //chu shi huawire eno,enp1,enp2,enp3,enp4,enp5;in50MHz_out1Hz u0(clk,cp1);//输出频率1HZin50MHz_out1kHz u7(clk,cp2);//输出频率1kHZ扫描信号in50MHz_out10Hz u8(clk,cp3); //输出频率10HZin50MHz_out100Hz u12(clk,cp4);//100Hzcounter10 u1(en0,0,cp,cnt[3:0]); //second个位计数counter6 u2(enp1,0,cp,cnt[7:4]);//second十位计数counter10 u3(enp2,0,cp,cnt[11:8]);//minutes个位计数counter6 u4(enp3,0,cp,cnt[15:12]);//minutes十位计数counter10 u5(enp4,0,cp,cnt[19:16]);//hours个位计数counter3 u6(enp5,0,cp,cnt[23:20]); //hours十位计数bell u9(switch,set,bcrl,adj,cp3,cnt,cnt1,led[1:0]);//闹钟模块radio u10(rcrl,cnt[15:0],cp1,cp3,led[7:3]);//仿真报时模块stopwatch u11(swo,scrl,swp,adj,cp4,cp3,cnt2);//秒表模块assign cp= ad?cp3:cp1,en0=(~ad)|(switch&adj[0]),enp1=~ad?(cnt[3:0]==4'h9):(adj[1]&switch),//产生second十位计数使能信号enp2=~ad?(cnt[7:4]==4'd5)&(cnt[3:0]==4'd9):(adj[0]&switch==0),//产生minutes个位计数使能信号enp3=~ad?(enp2&(cnt[11:8]==4'd9)):(adj[1]&switch==0),//产生minutes十位计数使能信号enp4=~ad?(enp3&(cnt[15:12]==4'd5)):(adj[2]&switch==0),//产生hours个位计数使能信号enp5=~ad?(enp4&cnt[19:16]==4'd9):(adj[3]&switch==0),//产生hours十位计数使能信号led[2]=0;always@(ad or set or swo) //显示模式选择if((~ad)&set&(~swo)) begin temp[15:0]<=cnt1[15:0];temp[31:16]<=cnt1[23:8];endelse if( (~ad)&(~set)&swo) temp<=cnt2;else begin temp[15:0]<=cnt;temp[31:16]<=cnt[23:8];endalways@(posedge cp2) // 扫描信号循环变化if(a==4'b1110) a<=4'b1101;//J12else if(a==4'b1101) a<=4'b1011;//M13else if(a==4'b1011) a<=4'b0111;//k14else a<=4'b1110;//F12always@(posedge cp2) //数码管显示译码if(switch==1'b0)beginif(a==4'b1110)begincase(temp[19:16])4'd0: segs <= 7'b1000000;4'd1: segs <= 7'b1111001;4'd2: segs <= 7'b0100100;4'd3: segs <= 7'b0110000;4'd5: segs <= 7'b0010010;4'd6: segs <= 7'b0000010;4'd7: segs <= 7'b1111000;4'd8: segs <= 7'b0000000;4'd9: segs <= 7'b0010000;default segs <= 7'b1111111;endcaseendelse if(a==4'b1101)begincase(temp[23:20])4'd0: segs <= 7'b1000000;4'd1: segs <= 7'b1111001;4'd2: segs <= 7'b0100100;4'd3: segs <= 7'b0110000;4'd4: segs <= 7'b0011001;4'd5: segs <= 7'b0010010;default segs <= 7'b1111111;endcaseendelse if(a==4'b1011)begincase(temp[27:24])//hours个位4'h0: segs <= 7'b1000000;4'h1: segs <= 7'b1111001;4'h2: segs <= 7'b0100100;4'h3: segs <= 7'b0110000;4'h4: segs <= 7'b0011001;4'h5: segs <= 7'b0010010;4'h6: segs <= 7'b0000010;4'h7: segs <= 7'b1111000;4'h8: segs <= 7'b0000000;4'h9: segs <= 7'b0010000;4'ha: segs <= 7'b0001000;default segs <= 7'b1111111; endcaseendelsebegincase(temp[31:28])//hours十位4'h0: segs <= 7'b1000000;4'h1: segs <= 7'b1111001;4'h2: segs <= 7'b0100100;4'h4: segs <= 7'b0011001;4'h5: segs <= 7'b0010010;4'h6: segs <= 7'b0000010;4'h7: segs <= 7'b1111000;4'h8: segs <= 7'b0000000;4'h9: segs <= 7'b0010000;4'ha: segs <= 7'b0001000;4'hb: segs <= 7'b0000011;4'hc: segs <= 7'b1000110;default segs <= 7'b1111111;endcaseendendelse if(switch==1)begin if(a==4'b1110)case(temp[3:0])4'd0: segs <= 7'b1000000;4'd1: segs <= 7'b1111001;4'd2: segs <= 7'b0100100;4'd3: segs <= 7'b0110000;4'd4: segs <= 7'b0011001;4'd5: segs <= 7'b0010010;4'd6: segs <= 7'b0000010;4'd7: segs <= 7'b1111000;4'd8: segs <= 7'b0000000;4'd9: segs <= 7'b0010000;default segs <= 7'b1111111;endcaseelse if(a==4'b1101)case(temp[7:4])4'd0: segs <= 7'b1000000;4'd1: segs <= 7'b1111001;4'd2: segs <= 7'b0100100;4'd3: segs <= 7'b0110000;4'd4: segs <= 7'b0011001;4'd5: segs <= 7'b0010010;4'd6: segs <= 7'b0000010;4'd7: segs <= 7'b1111000;4'd8: segs <= 7'b0000000;4'd9: segs <= 7'b0010000;default segs <= 7'b1111111;endcaseelse if(a==4'b1011)case(temp[11:8])4'd0: segs <= 7'b1000000;4'd1: segs <= 7'b1111001;4'd2: segs <= 7'b0100100;4'd3: segs <= 7'b0110000;4'd4: segs <= 7'b0011001;4'd5: segs <= 7'b0010010;4'd6: segs <= 7'b0000010;4'd7: segs <= 7'b1111000;4'd8: segs <= 7'b0000000;4'd9: segs <= 7'b0010000;default segs <= 7'b1111111;endcaseelsecase(temp[15:12])4'd0: segs <= 7'b1000000;4'd1: segs <= 7'b1111001;4'd2: segs <= 7'b0100100;4'd3: segs <= 7'b0110000;4'd4: segs <= 7'b0011001;4'd5: segs <= 7'b0010010;default segs <= 7'b1111111;endcaseendendmodule// counter10.v(0~9)module counter10(en,ncr,clk,q);input en,ncr,clk;output [3:0] q;reg [3:0] q;always@(posedge clk )beginif(ncr) q<=4'd0;//ncr=0时,同步清零else if(~en) q<=q;// EN=0,暂停计数else if (q==4'b1001) q<=4'b0000;else q<=q+1;//计数器加1endendmodule// counter6.v(0~5)module counter6(en,ncr,clk,q);input en,ncr,clk;output [3:0] q;reg [3:0] q;always@(posedge clk )beginif(ncr) q<=4'b0000;//NCR=0,同步清零else if(~en) q<=q;//EN=0,暂停计数else if(q==4'b0101) q<=4'b0000;else q<=q+1'b1;//计数器增1endendmodule//counter3.vmodule counter3(en,ncr,clk,q);input en,ncr,clk;output [3:0] q;reg [3:0] q;always@(posedge clk )beginif(ncr) q<=4'b0000;//NCR=0,同步清零else if(en==0) q<=q;//EN=0,暂停计数else if(q==4'd2) q<=4'b0000;else q<=q+1'b1;//计数器增1endendmodule//分频模块1Hzmodule in50MHz_out1Hz(in_50MHz,out_1Hz); input in_50MHz;output out_1Hz;reg out_1Hz;reg [31:0]cnt; //use cnt to countalways@(posedge in_50MHz)begin if(cnt < 32'd2*******)//计数到24999999 begincnt <= cnt + 1'B1;endelse begin cnt <= 32'b0;out_1Hz <= ~out_1Hz; //频率为1HZendendendmodule//分频模块1KHzmodule in50MHz_out1kHz(in_50MHz,out_1kHz); input in_50MHz;output out_1kHz;reg out_1kHz;reg [31:0]cnt; //use cnt to countalways@(posedge in_50MHz)begin if(cnt < 32'd24999)//计数到24999 begincnt <= cnt + 1'B1;endelse begin cnt <= 32'b0;out_1kHz <= ~out_1kHz; //频率为1kHZendendendmodulemodule in50MHz_out10Hz(in_50MHz,out_10Hz); input in_50MHz;output out_10Hz;reg out_10Hz;reg [31:0]cnt; //use cnt to countalways@(posedge in_50MHz)begin if(cnt < 32'd2499999)//计数到2499999 begincnt <= cnt + 1'B1;endelse begin cnt <= 32'b0;out_10Hz <= ~out_10Hz; //频率为10HZendendendmodulemodule in50MHz_out100Hz(in_50MHz,out_100Hz); input in_50MHz;output out_100Hz;reg out_100Hz;reg [31:0]cnt; //use cnt to countalways@(posedge in_50MHz)begin if(cnt < 32'd249999)//计数到249999 begincnt <= cnt + 1'B1;endelse begin cnt <= 32'b0;out_100Hz <= ~out_100Hz; //频率为100HZ endendendmodulemodule bell(switch,set,crl,p,clk,cnt,cnt1,led); //闹钟模块input switch,set,crl,clk;input [23:0] cnt;input [3:0] p;output [23:0] cnt1;output [1:0] led;reg led;reg cl;adjust f(clk,set,switch,p,cnt1);always@(negedge clk)if((cnt>=cnt1)&(cnt1+22'h59>=cnt)&crl)cl=1;else cl=0;always@(negedge clk)if (cl)led<=~led;else led<=2'b00;endmodulemodule adjust(clk,ad,switch,adj,cnt1); //闹钟里面的定时模块input switch,ad,clk;input [3:0] adj;output [23:0] cnt1;reg [23:0] cnt1;always@(posedge clk)if(switch==0&ad==1)case(adj)4'b0001:begin if(cnt1[11:8]==4'd9) cnt1[11:8]<=4'd0;else cnt1[11:8]<=cnt1[11:8]+1'd1;end4'b0010:begin if(cnt1[15:12]==4'd5) cnt1[15:12]<=4'd0;else cnt1[15:12]<=cnt1[15:12]+1'd1;end4'b0100:begin if(cnt1[19:16]==4'd9) cnt1[19:16]<=4'd0;else cnt1[19:16]<=cnt1[19:16]+1'd1;end4'b1000:begin if(cnt1[23:20]==4'd2) cnt1[23:20]<=4'd0;else cnt1[23:20]<=cnt1[23:20]+1'd1;enddefault cnt1<=cnt1;endcaseelse if(switch==1&ad==1) case(adj)4'b0001:begin if(cnt1[3:0]==4'd9) cnt1[3:0]<=4'd0;else cnt1[3:0]<=cnt1[3:0]+1'd1;end4'b0010:begin if(cnt1[7:4]==4'd5) cnt1[7:4]<=4'd0;else cnt1[7:4]<=cnt1[7:4]+1'd1;end4'b0100:begin if(cnt1[11:8]==4'd9) cnt1[11:8]<=4'd0;else cnt1[11:8]<=cnt1[11:8]+1'd1;end4'b1000:begin if(cnt1[15:12]==4'd5) cnt1[15:12]<=4'd0;else cnt1[15:12]<=cnt1[15:12]+1'd1;enddefault cnt1<=cnt1;endcaseelse cnt1<=cnt1;endmodule//radio.vmodule radio(rcrl,cnt,clk1,clk2,led); //仿真报时模块input rcrl,clk1,clk2;input [15:0] cnt;output [4:0] led;reg c;reg c2;reg led;always@(cnt)if(cnt[15:8]==8'h59)case(cnt[7:0])8'h50,8'h52,8'h54,8'h56: c<=1;8'h59: c2<=1;default :begin c<=0;c2<=0;endendcaseelse begin c<=0;c2<=0;endalways@(posedge clk1)if(c&~c2&rcrl)case(cnt[7:0])8'h50:led[4:1]<=4'b1000;8'h52:led[4:1]<=4'b0100;8'h54:led[4:1]<=4'b0010;8'h56:led[4:1]<=4'b0001;default: led[4:1]<=4'b0000;endcaseelse led[4:1]<=4'b0000;always@(posedge clk2)if(~c&c2&rcrl)led[0]<=1;else led[0]<=0;endmodule//stopwatch.v //秒表模块module stopwatch(start,crl,en,p,clk1,clk2,temp);input start,crl,en,clk1,clk2;input [3:0] p;output [31:0] temp;wire [23:0] cnt;wire enp0,enp1,enp2,enp3,enp4,enp5,cp1,cp2,cp3;reg [23:0] temp1,temp2,temp3,temp4,temp5,temp6,temp7,temp8,temp9;reg [31:0] temp;reg [3:0] i;counter10 f3(enp0,p[3],clk1,cnt[3:0]);counter10 f4(enp1,p[3],clk1,cnt[7:4]);counter10 f5(enp2,p[3],clk1,cnt[11:8]);counter6 f6(enp3,p[3],clk1,cnt[15:12]);counter10 f7(enp4,p[3],clk1,cnt[19:16]);counter6 f8(enp5,p[3],clk1,cnt[23:20]);assign enp0=start&en,enp1=(cnt[3:0]==4'd9),enp2=enp1&(cnt[7:4]==4'd9),enp3=enp2&(cnt[11:8]==4'd9),enp4=enp3&(cnt[15:12]==4'd5),enp5=enp4&(cnt[19:16]==4'd9);//always@(posedge clk2)if(~crl)begin temp[23:0]<=cnt;temp[27:24]<=i;temp[31:28]<=4'hc;endelsebegintemp[27:24]<=i;temp[31:28]<=4'hc;case(i)4'h1: temp[23:0]<=temp1;4'h2: temp[23:0]<=temp2;4'h3: temp[23:0]<=temp3;4'h4: temp[23:0]<=temp4;4'h5: temp[23:0]<=temp5;4'h6: temp[23:0]<=temp6;4'h7: temp[23:0]<=temp7;4'h8: temp[23:0]<=temp8;4'h9: temp[23:0]<=temp9;endcaseend//always@(posedge clk2 )if(crl)begincase(p[1:0])2'b10:begin if(i>4'd1) i<=i-1'd1;else i<=i;end2'b01:begin if(4'd9>i) i<=i+1'd1;else i<=i;enddefault i<=i;endcaseendelse if(enp0&p[3]&(~crl))i<=4'h0;else if(enp0&p[2]&i<=4'h9)begini<=i+4'd1;case(i)4'h0: temp1<=cnt;4'h1: temp2<=cnt;4'h2: temp3<=cnt;4'h3: temp4<=cnt;4'h4: temp5<=cnt;4'h5: temp6<=cnt;4'h6: temp7<=cnt;4'h7: temp8<=cnt;4'h8: temp9<=cnt;endcaseendelse i<=i;endmodule。