R106中文资料

常用放大器参数

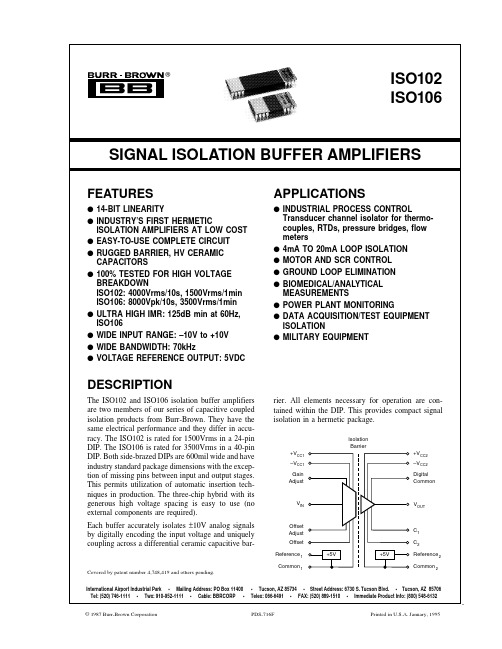

ISO106高压,隔离缓冲放大器ISO106同ISO102性能基本相同,主要区别要以下两点:①ISO106的连续隔离电压3500;②ISO106封装为40引脚DIP组件;主要引脚定义可参看ISO102。

LF147/347四JFET输入运算放大器输入失调电压1mV(LF147)、5mV(LF347);温度漂移10μV/℃;偏置电流50pA增益带宽4MHz;转换速率13V/μs;噪声20nV/(Hz^1/2)(1kHZ);消耗电流7.2mA。

±22V电源(LF147)、±18V电源(LF347);差模输入电压±38V(LF147)、±30V(LF347);共模输入电压±19V(LF147)、±15V(LF347);功耗500mW。

LF155/255/355JFET输入运算放大器输入失调电压1mV(LF155/355)、3mV(LF255);温度漂移3μV/℃(LF155/355)、5μV/℃(LF255);偏置电流30pA增益带宽GB=2.5MHz;转换速率5V/μs;噪声20nV/(Hz^1/2)(1kHZ);消耗电流2mA。

±40V电源(LF155/255)、±30V电源(LF355);共模输入电压±20V(LF155/255)、±16V(LF355);输入阻抗10^12Ω共模抑制比100dB;电压增益106dB。

LF353双JFET输入运算放大器输入失调电压5mV;温度漂移10μV/℃;偏置电流50pA;增益带宽GB=4MHz;转换速率13V/μs;噪声16nV/(Hz^1/2)(1kHZ);消耗电流1.8mA。

±18V电源;差模输入电压±30V;共模输入电压±15V;功耗500mW。

LF411/411A低失调、低漂移、JFET输入运算放大器输入失调电压800μV(LF411)、300μV(LF411A);温度漂移7μV/℃;偏置电流50pA;增益带宽GB=4MHz;转换速率15V/μs;噪声23nV/(Hz^1/2)(1kHZ);消耗电流1.8mA。

MPC106资料

Semiconductor Products SectorThis document contains information on a new product under development by Motorola.Motorola reserves the right to change or discontinue this product without notice.Technical DataMPC106 PCI Bridge/Memory Controller Hardware SpecificationsThe Motorola MPC106 PCI bridge/memory controller provides a PowerPC™ microprocessor common hardware reference platform (CHRP™) compliant bridge between the PowerPC microprocessor family and the Peripheral Component Interconnect (PCI) bus. In this document, the term ‘106’ is used as an abbreviation for the phrase ‘MPC106 PCI bridge/memory controller.’ This document contains pertinent physical characteristics of the 106. For functional characteristics, refer to the MPC106 PCI Bridge/Memory Controller User’s Manual .This document contains the following topics:TopicPageSection 1.1, “Overview”2Section 1.2, “Features”3Section 1.3, “General Parameters”5Section 1.4, “Electrical and Thermal Characteristics”5Section 1.5, “Pin Assignments”15Section 1.6, “Pinout Listings16Section 1.7, “Package Description”20Section 1.8, “System Design Information”22Section 1.9, “Document Revision History”27Section 1.10, “Ordering Information”27OverviewIn this document, the term ‘60x’ is used to denote a 32-bit microprocessor from the PowerPC architecture family that conforms to the bus interface of the PowerPC 601™, PowerPC 603™, or PowerPC 604™microprocessors. Note that this does not include the PowerPC 602™ microprocessor which has a multiplexed address/data bus. 60x processors implement the PowerPC architecture as it is specified for 32-bit addressing, which provides 32-bit effective (logical) addresses, integer data types of 8, 16, and 32 bits, and floating-point data types of 32 and 64 bits (single-precision and double-precision).To locate any published errata or updates for this document, refer to the website at /SPS/PowerPC/.1.1 OverviewThe MPC106 provides an integrated high-bandwidth, high-performance, TTL-compatible interface between a 60x processor, a secondary (L2) cache or additional (up to four total) 60x processors, the PCI bus, and main memory. This section provides a block diagram showing the major functional units of the 106 and describes briefly how those units interact.Figure 1 shows the major functional units within the 106. Note that this is a conceptual block diagram intended to show the basic features rather than how these features are physically implemented on the device.Figure 1. Block DiagramFeatures The 106 provides a PowerPC microprocessor CHRP-compliant bridge between the PowerPC microprocessor family and the PCI bus. CHRP documentation provides a set of specifications that define a unified personal computer architecture. PCI support allows the rapid design of systems using peripherals already designed for PCI and the other standard interfaces available in the personal computer hardware environment. The 106 integrates secondary cache control and a high-performance memory controller, uses an advanced, 3.3-V CMOS process technology, and is fully compatible with TTL devices.The 106 supports a programmable interface to a variety of PowerPC microprocessors operating at select bus speeds. The 60x address bus is 32 bits wide and the data bus is 64 bits wide. The 60x processor interface of the 106 uses a subset of the 60x bus protocol, supporting single-beat and burst data transfers. The address and data buses are decoupled to support pipelined transactions.The 106 provides support for the following configurations of 60x processors and L2 cache:•Up to four 60x processors with no L2 cache• A single 60x processor plus a direct-mapped, lookaside L2 cache using the internal L2 cache controller of the 106•Up to four 60x processors plus an externally controlled L2 cache (such as the Motorola MPC2605 integrated secondary cache)The memory interface controls processor and PCI interactions to main memory and is capable of supporting a variety of configurations using DRAM, EDO, SDRAM, ROM, or Flash ROM.The PCI interface of the 106 complies with the PCI Local Bus Specification, Revision 2.1, and follows the guidelines in the PCI System Design Guide, Revision 1.0,for host bridge architecture. The PCI interface connects the processor and memory buses to the PCI bus, to which I/O components are connected. The PCI bus uses a 32-bit multiplexed address/data bus, plus various control and error signals.The PCI interface of the 106 functions as both a master and target device. As a master, the 106 supports read and write operations to the PCI memory space, the PCI I/O space, and the PCI configuration space. The 106 also supports PCI special-cycle and interrupt-acknowledge commands. As a target, the 106 supports read and write operations to system memory.The 106 provides hardware support for four levels of power reduction: doze, nap, sleep, and suspend. The design of the MPC106 is fully static, allowing internal logic states to be preserved during all power-saving modes.1.2 FeaturesThis section summarizes the major features of the 106, as follows:•60x processor interface—Supports up to four 60x processors—Supports various operating frequencies and bus divider ratios—32-bit address bus, 64-bit data bus—Supports full memory coherency—Supports optional 60x local bus slave—Decoupled address and data buses for pipelining of 60x accesses—Store gathering on 60x-to-PCI writesFeatures•Secondary (L2) cache control—Configurable for write-through or write-back operation—Supports cache sizes of 256 Kbytes, 512 Kbytes, and 1 Mbyte—Up to 4 Gbytes of cacheable space—Direct-mapped—Supports byte parity—Supports partial update with external byte decode for write enables—Programmable interface timing—Supports pipelined burst, synchronous burst, or asynchronous SRAMs—Alternately supports an external L2 cache controller or integrated L2 cache module •Memory interface— 1 Gbyte of RAM space, 16 Mbytes of ROM space—Supports parity or error checking and correction (ECC)—High-bandwidth, 64-bit data bus (72 bits including parity or ECC)—Supports fast page mode DRAMs, extended data out (EDO) DRAMs, and synchronous DRAMs (SDRAMs)—Supports 1 to 8 banks of DRAM/EDO/SDRAM with sizes ranging from 2 Mbyte to 128 Mbytes per bank—ROM space may be split between the PCI bus and the 60x/memory bus (8 Mbytes each)—Supports 8-bit asynchronous ROM or 64-bit burst-mode ROM—Supports writing to Flash ROM—Configurable external buffer control logic—Programmable interface timing•PCI interface—Compliant with PCI Local Bus Specification, Revision 2.1—Supports PCI interlocked accesses to memory using LOCK signal and protocol—Supports accesses to all PCI address spaces—Selectable big- or little-endian operation—Store gathering on PCI writes to memory—Selectable memory prefetching of PCI read accesses—Only one external load presented by the MPC106 to the PCI bus—Interface operates at 20–33 MHz—Word parity supported— 3.3 V/5.0 V-compatible•Support for concurrent transactions on 60x and PCI buses•Power management—Fully-static 3.3-V CMOS design—Supports 60x nap, doze, and sleep power management modes and suspend mode •IEEE 1149.1-compliant, JTAG boundary-scan interface•304-pin ceramic ball grid array (CBGA) packageGeneral Parameters1.3 General ParametersThe following list provides a summary of the general parameters of the 106:Technology0.5 µm CMOS, four-layer metalDie size 5.8 mm x 7.2 mm (41.8 mm2)Transistor count250,000Logic design Fully-staticPackages Surface mount 304-lead C4 ceramic ball grid array (CBGA)Power supply 3.3 V ± 5% V DCMaximum input rating 5.0 V ± 10% V DC1.4 Electrical and Thermal CharacteristicsThis section provides both the AC and DC electrical specifications and thermal characteristics for the 106.1.4.1 DC Electrical CharacteristicsThe tables in this section describe the 106 DC electrical characteristics. Table 1 provides the absolute maximum ratings. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause it permanent damage.Table 1. Absolute Maximum RatingsCharacteristic Symbol Value Unit NotesSupply voltage Vdd–0.3 to 3.6V—PLL supply voltage AVdd–0.3 to 3.6V—Input voltage V in–0.3 to 5.5V1 Junction temperature T j0 to 105°C2 Storage temperature range T stg–55 to 150°C—Notes:1Caution: V in must not exceed Vdd by more than 2.5 V at all times including during power-on reset.2The extended temperature parts have die junction temperature of -40 to 105°C. See MPC106ARXTGPNS/D for more information.Table 2 provides the recommended operating conditions for the 106. Proper device operation outside of these recommended and tested conditions is not guaranteed.Electrical and Thermal CharacteristicsTable 3 provides the package thermal characteristics for the 106.Table 4 provides the DC electrical characteristics for the 106, assuming Vdd = A Vdd = 3.3 ± 5% V DC,GND = 0 V DC, and 0 ≤ T j ≤ 105 °C.Table 5 lists the power consumption of the 106.Table 2. Recommended Operating ConditionsCharacteristic Symbol Value Unit Notes Supply voltage Vdd 3.3 ± 165 mv V —PLL supply voltage AVdd 3.3 ± 165 mv V —Input voltageV in 0 to 5.5V —Die junction temperatureT j0 to 105°CThe extended temperature parts have die junction temperature of -40 to 105°CTable 3. Package Thermal CharacteristicsCharacteristicSymbol Value Rating CBGA package thermal resistance, junction-to-top of dieθ JC0.133°C/WNote : Refer to Section 1.8, “System Design Information,” for more details about thermal management.Table 4. DC Electrical SpecificationsCharacteristicSymbol Min Max Unit Input high voltage (all inputs except SYSCLK)V IH 2 5.5V Input low voltage (all inputs except SYSCLK)V IL GND 0.8V SYSCLK input high voltage CV IH 2.4 5.5V SYSCLK input low voltage CV IL GND 0.4V Input leakage current, V in =3.3 V 1I in —15.0µA Hi-Z (off-state) leakage current, V in = 3.3 V 1 I TSI —15.0µA Output high voltage, I OH = -7 mA 2 V OH 2.4—V Output low voltage, I OL = 7 mA 2V OL —0.5V PCI 3.3 V signaling output high voltage, I OH = -0.5 mA 2 V OH 2.7—V PCI 3.3 V signaling output low voltage, I OL = 1.5 mA 2 V OL —0.3V Capacitance, V in = 0 V , f = 1 MHz 3C in—7.0pFNotes:1 Excludes test signals (LSSD_MODE and JT AG signals).2 This value represents worst case 40-ohm drivers (default value for Processor/L2 control signals CI, WT , GBL, TBST , TSIZ[0–2], TT[0–4], TWE, and TV) only. Other signals have lower default driver impedance and will support larger I OH and I OL . All drivers may optionally be programmed to different driver strengths. 3Capacitance is periodically sampled rather than 100% tested.Electrical and Thermal Characteristics1.4.2 AC Electrical CharacteristicsThis section provides AC electrical characteristics for the 106. After fabrication, parts are sorted by maximum 60x processor bus frequency, as shown in Section 1.4.2.1, “Clock AC Specifications,” and tested for conformance to the AC specifications for that frequency. These specifications are for operation between 16.67 and 33.33 MHz PCI bus (SYSCLK) frequencies. The 60x processor bus frequency is determined by the PCI bus (SYSCLK) frequency and the settings of the PLL[0–3] signals. All timings are specified relative to the rising edge of SYSCLK.1.4.2.1 Clock AC SpecificationsTable 6 provides the clock AC timing specifications as shown in Figure 2, and assumes Vdd = A Vdd = 3.3± 5% V DC, GND = 0 V DC, and 0 ≤ T j ≤ 105 °C.Table 5. Power ConsumptionModeSYSCLK/Core 33/66 MHzSYSCLK/Core 33/83.3 MHzUnitFull-OnT ypical Maximum1.22.2W 1.42.4WDozeT ypical Maximum1.0 1.1W 1.21.4WNapT ypical Maximum1.0 1.1W 1.21.4WSleepT ypical Maximum260330mW 360450mWSuspendT ypical Maximum140220mW 190270mWNotes:•Power consumption for common system configurations assuming 50 pF loads •Suspend power-saving mode assumes SYSCLK off and PLL in bypass mode.•T ypical power is an average value measured at Vdd = AVdd = 3.30 V and T A = 25 °C. •Maximum power is measured at Vdd = AVdd = 3.45 V and T A= 25 °C.Electrical and Thermal CharacteristicsFigure 2 provides the SYSCLK input timing diagram.Figure 2. SYSCLK Input Timing Diagram1.4.2.2 Input AC SpecificationsTable 7 provides the input AC timing specifications for the 106 as defined in Figure 3 and Figure 4. These specifications are for operation between 16.67 and 33.33 MHz PCI bus clock (SYSCLK) frequencies.Assume Vdd = A Vdd = 3.3 ± 5% V DC, GND = 0 V DC, and 0 ≤ T j ≤ 105 °C.Table 6. Clock AC Timing SpecificationsNum Characteristic SYSCLK/Core 33/66 MHz SYSCLK/Core 33/83.3 MHz Unit NotesMinMax Min Max —60x processor bus (core) frequency 16.676616.6783.3MHz 1—VCO frequency 120200120200MHz 1, 2—SYSCLK frequency 16.6733.3316.6733.33MHz 11SYSCLK cycle time 30.060.030.060.0ns —2, 3SYSCLK rise and fall time— 2.0— 2.0ns 34SYSCLK duty cycle measured at 1.4 V 40604060%4—SYSCLK jitter—±200—±200ps 5—106 internal PLL relock time—100—100µ s4, 6Notes :1 Caution : The SYSCLK frequency and PLL[0–3] settings must be chosen such that the resulting SYSCLK (bus) frequency, CPU (core) frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL[0–3] signal description in Section 1.8, “System Design Information,” for valid PLL[0–3] settings, and to Section 1.9, “Document Revision History,” for available frequencies and part numbers.2 VCO operating range for extended temperature devices is different. Refer to MPC106ARXTGPNS/D for more information.3 Rise and fall times for the SYSCLK input are measured from 0.4 V to 2.4 V . 4 Timing is guaranteed by design and characterization and is not tested.5 The total input jitter (short-term and long-term combined) must be under ±200 ps.6PLL-relock time is the maximum time required for PLL lock after a stable Vdd, AVdd, and SYSCLK are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled andsubsequently re-enabled during the sleep and suspend power-saving modes. Also note that HRST must be held asserted for a minimum of 255 bus clocks after the PLL-relock time (100 µs) during the power-on reset sequence.Electrical and Thermal CharacteristicsFigure 3 provides the input timing diagram for the 106.Table 7. Input AC Timing SpecificationsNumCharacteristic66 MHz83.3 MHzUnitNotesMinMaxMin Max10a Group I input signals valid to 60x Bus Clock (input setup) 4.0 3.5ns 1,2,310a Group II input signals valid to 60x Bus Clock (input setup) 3.5 3.5ns 1,2,410a Group III input signals valid to 60x Bus Clock (input setup) 3.0 2.5ns 1,2,510a Group IV input signals valid to 60x Bus Clock (input setup) 5.0 4.0ns 1,2,610b Group V input signals valid to SYSCLK (input setup)7.07.0ns 7,810b Group VI input signals valid to SYSCLK (input setup)7.07.0ns 7,911a 60x Bus Clock to group I–IV inputs invalid (input hold)0—0—ns 3,4,5,611b SYSCLK to group V–VI inputs invalid (input hold)–0.5—–0.5—ns8,9HRST pulse width255 x t sysclk + 100 µs —255 x t sysclk + 100 µs ——10c Mode select inputs valid to HRST (input setup) 3 x t sysclk— 3 x t sysclk—ns 10, 11,1211c HRST to mode select input invalid (input hold)1.0—1.0—ns10, 12Notes:1Input specifications are measured from the TTL level (0.8 or 2.0 V) of the signal in question to the 1.4 V of the rising edge of SYSCLK. Both input and output timings are measured at the pin (see Figure 3).2Processor and memory interface signals are specified from the rising edge of the 60x bus clock (which is internally synchronized to SYSCLK).3Group I input signals include the following processor, L2, and memory interface signals: A[0–31], P AR[0–7]/AR[1–8], BR[0–4], BRL2, XA TS, LBCLAIM, ADS, BA0, TV and HIT (when configured for external L2)4Group II input signals include the following processor and memory interface signals: TBST , TT[0–4], TSIZ[0–2], WT , CI, GBL, AACK, and T A.5Group III input signals include the following processor and memory interface signals: DL[0–31] and DH[0–31].6Group IV input signals include the following processor and L2 interface signals: TS, ARTRY , DIRTY_IN, and HIT (when configured for internal L2 controller).7PCI 3.3 V signaling environment signals are measured from 1.65 V (Vdd ÷ 2) on the rising edge of SYSCLK to V OH = 3.0 V or V OL = 0.3 V . PCI 5 V signaling environment signals are measured from 1.65 V (Vdd ÷ 2) on the rising edge of SYSCLK to V OH = 2.4 V or V OL = 0.55 V .8Group V input signals include the following bussed PCI interface signals: FRAME, C/BE[0–3], AD[0–31], DEVSEL, IRDY , TRDY , STOP , P AR, PERR, SERR, LOCK, FLSHREQ, and ISA_MASTER.9Group VI input signal is the point-to-point PCI GNT input signal.10The setup and hold time is with respect to the rising edge of HRST (see Figure 4). Mode select inputs include the RCS0, FOE, and DBG0 configuration inputs.11 tsysclk is the period of the external clock (SYSCLK) in nanoseconds (ns). When the unit is given as t sysclk , the numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in nanoseconds) of the parameter in question.12These values are guaranteed by design and are not tested.Electrical and Thermal CharacteristicsFigure 3. Input Timing DiagramFigure 4 provides the mode select input timing diagram for the 106.Figure 4. Mode Select Input Timing Diagram1.4.2.3 Output AC SpecificationsTable 8 provides the output AC timing specifications for 106 (shown in Table 5). Assume Vdd = A Vdd =3.3 ± 5% V DC, GND = 0 V DC, CL = 50 pF, and 0 ≤ T j ≤ 105 °C. Processor and memory interface signals are specified from the rising edge of the 60x bus clock (which is internally synchronized to SYSCLK). All units are nanoseconds.VM = Midpoint Voltage (1.4 V)HRSTMODE PINSElectrical and Thermal Characteristics Table 8. Output AC Timing SpecificationsNum Characteristic66 MHz83.3 MHzNotes Min Max Min Max12SYSCLK to output driven (outputenable time)2.0— 2.0—113a SYSCLK to output valid for TS andARTRY—7.0— 6.02, 3, 413b SYSCLK to output valid for all non-PCIsignals except TS, ARTRY, RAS[0–7],CAS[0–7], and DWE[0-2]—7.0— 6.02, 3, 514a SYSCLK to output valid (for RAS[0–7]and CAS[0–7])—7.0— 6.02, 3 14b SYSCLK to output valid for PCI signals—11.0—11.03, 615a SYSCLK to output invalid for allnon-PCI signals (output hold)1.0— 1.0—7, 1015b SYSCLK to output invalid for PCIsignals (output hold)1.0— 1.0—718SYSCLK to ARTRY high impedancebefore precharge (output hold)—8.0—8.0119SYSCLK to ARTRY precharge enable (0.4 *t sysclk) + 2.0—(0.4 xt sysclk) + 2.0—8, 121SYSCLK to ARTRY high impedance after precharge —(1.5 *t sysclk) + 8.0—(1.5 xt sysclk) + 8.08, 1Notes:1These values are guaranteed by design and are not tested.2Output specifications are measured from 1.4 V on the rising edge of the appropriate clock to the TTL level (0.8 V or 2.0 V) of the signal in question. Both input and output timings are measured at the pin (see Figure 5).3The maximum timing specification assumes C L = 50 pF.4The shared outputs TS and ARTRY require pull-up resistors to hold them negated when there is no bus master driving them.5When the 106 is configured for asynchronous L2 cache SRAMs, the DWE[0–2] signals have a maximum SYSCLK to output valid time of (0.5 x t PROC) + 8.0 ns (where t PROC is the 60x bus clock cycle time).6PCI 3.3 V signaling environment signals are measured from 1.65 V (Vdd ÷ 2) on the rising edge of SYSCLK to V OH = 3.0 V or V OL = 0.3 V.7The minimum timing specification assumes C L = 0 pF.8tsysclk is the period of the external bus clock (SYSCLK) in nanoseconds (ns). When the unit is given as t sysclk the numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in nanoseconds) of the parameter in question.9PCI devices which require more than the PCI-specified hold time of Th = 0ns or systems where clock skewapproaches the PCI-specified allowance of 2ns may not work with the MPC106. For workarounds, see Motorola application note Designing PCI 2.1-Compliant MPC106 Systems (order number AN1727/D).Electrical and Thermal CharacteristicsFigure 5 provides the output timing diagram for the 106.Figure 5. Output Timing Diagram1.4.3 JTAG AC Timing SpecificationsTable 9 provides the JTAG AC timing specifications. Assume Vdd = A Vdd = 3.3 ± 5% V DC, GND = 0 V DC, CL = 50 pF, and 0 ≤ T j ≤ 105 °C.Table 9. JTAG AC Timing Specifications (Independent of SYSCLK)Num CharacteristicMin Max Unit Notes —TCK frequency of operation 025MHz —1TCK cycle time40—ns —2TCK clock pulse width measured at 1.4 V 20—ns —3TCK rise and fall times03ns 14TRST setup time to TCK rising edge 10—ns 25TRST assert time10—ns160x Bus ClockALL Non-PCI TSARTRYVM = Midpoint Voltage (1.4V)(Except TS andARTRY)SYSCLKALLOUTPUTS PCI OUTPUTSElectrical and Thermal CharacteristicsFigure 6 provides the JTAG clock input timing diagram.Figure 6. JTAG Clock Input Timing DiagramFigure 7 provides the TRST timing diagram.Figure 7. TRST Timing Diagram6Boundary-scan input data setup time 5—ns 37Boundary-scan input data hold time 15—ns 38TCK to output data valid 030ns 49TCK to output high impedance 030ns 410TMS, TDI data setup time 5—ns —11TMS, TDI data hold time 15—ns 112TCK to TDO data valid 015ns —13TCK to TDO high impedance15ns—Notes :1These values are guaranteed by design, and are not tested2TRST is an asynchronous signal. The setup time is for test purposes only.3Non-test signal input timing with respect to TCK.4Non-test signal output timing with respect to TCK.Table 9. JTAG AC Timing Specifications (Independent of SYSCLK) (Continued)Num CharacteristicMin Max Unit NotesTCKVM = Midpoint Voltage (1.4 V)TRSTTCKElectrical and Thermal CharacteristicsFigure 8 provides the boundary-scan timing diagram.Figure 9. Test Access Port Timing DiagramTCKData InputsData OutputsData OutputsData OutputsTCKTDI, TMSTDOTDOTDOPin Assignments1.5 Pin AssignmentsFigure 10 contains the pin assignments for the MPC106, and Figure 11 provides a key to the shading.Figure 11. Pin Assignments Shading Key16151413121110987654321WW V V U U TT R R P P N N M M L L K K J J H H G G F F E E D D C C B B AA16151413121110987654321Figure 10. Pin AssignmentsNo ConnectPower Supply GroundPower Supply PositiveAVddClock Power Supply Positive (K9)VIEWSignalsPinout Listings1.6 Pinout ListingsTable 10 provides the pinout listing for the MPC106. S ome signals have dual functions and are shown more than once.Table 10. Pinout ListingSignal Name Pin Number Active I/O60x Processor Interface SignalsHigh I/O A[0–31]R2, P2, N2, M2, L2, K2, J5, K4, K5, K6, J2, J6, J3, J4, H3,H4, H2, G2, F1, E1, E2, F4, E3, D1, C1, C2, B1, C3, B2, E4,D3, E5AACK D2Low I/OARTRY F2Low I/OBG0K3Low OutputBG1R4Low Output (DIRTY_OUT)R5Low Output BG2(TWE)T1Low Output BG3(DCS)BR0L3Low InputT3Low Input BR1(DIRTY_IN)T6Low Input BR2(TV)T5Low Input BR3(BA0)CI N3Low I/ODBG0L5Low OutputU4Low Output DBG1(TOE)DBG2P3Low Output (DWE0)H11Low Output DBG3(DWE1)DBGLBJ10Low Output (CKE)DH[0–31]T14, R13, R14, P13, P14, N13, U3, W1, V2, W2, V3, W3, V4,High I/OW4, V5, W5, V6, W6, V7, W7, V8, W8, N8, W9, V9, W10, V10,W11, V11, W12, V12, W13High I/O DL[0–31]U6, T7, U7, T8, U8, R8, P8, N9, P9, R9, U9, T9, U10, T10,U13, T13, R12, N14, M13, T2, U1, U2, V1, U15, V16, U14,W16, V15, W15, V14, W14, V13GBL M3Low I/OPinout ListingsLBCLAIM N4Low InputMCP J11Low OutputT A N1Low I/OTBST L4Low I/OTEA J1Low OutputTS R1Low I/O TSIZ[0–2]G3, G4, F3High I/OTT[0–4]G1, H1, K1, L1, M1High I/OWT M4Low I/OXA TS(SDMA1)P1Low InputL2 Cache Interface SignalsADS/DALE/BRL2R3Low I/O BA0(BR3)T5Low Output BA1/BAA/BGL2P4Low Output DBGL2/DOE U5Low Output DCS(BG3)T1Low OutputDIRTY_IN(BR1)T3Low InputDIRTY_OUT(BG1)R4Low OutputDWE0(DBG2)P3Low OutputDWE1(DBG3)H11Low OutputDWE2(CKO)L11Low Output HIT T4Low InputTOE(DBG1)U4Low OutputTV(BR2)T6High I/OTWE(BG2)R5Low Output Memory Interface SignalsBCTL[0–1]F16, F15Low OutputBERR (ISA_MASTER)B3Low Input Table 10. Pinout Listing (Continued)Signal Name Pin Number Active I/OPinout ListingsCAS/DQM[0–7]J15, H15, G16, E16, G14, G13, F14, E14Low Output CKE/DBGLBJ10High Output FOED13Low Output MA0/SDBA1/SDMA0/AR0N15High Output SDMA1(XA TS)P1High Output MA1/SDBA0/AR9U16High Output MA[2–12]/SDMA[2–12]/AR [10–20]T16, R16, P15, P16, N16, M15, M16, L15, K15, K16, J16High Output MDLE/SDCAS E13Low Output P AR[0–7]/AR[1–8]D16, D15, C16, C15, B16, C14, A16, B15High I/O PPEN J14Low Output RAS/CS[0–7]M14, L13, K13, K14, K12, L10, J12, K11Low Output RCS0R15Low I/O RCS1J13Low Output RTC G15High Input SDRAS (PIRQ)H10Low Output WET15LowOutputPCI Interface Signals1AD[31–0]A4, C13, B5, D12, A5, C12, B6, D11, C11, B7, D10, A7, C10, B8, D9, A8, B10, D8, A11, C7, B11, D7, A12, C6, B12, C5, A13, D5, A14, C4, B14, D4High I/OC/BE[3–0]A6, C9, C8, D6Low I/O DEVSEL F8Low I/O FLSHREQ A3Low Input FRAME A10Low I/O GNT A15Low Input IRDY E8Low I/O ISA_MASTER (BERR)B3Low Input LOCK G8Low Input MEMACK A2Low Output P AR G9High I/O PERR F9Low I/O PIRQ (SDRAS)H10Low Output REQB4LowOutputTable 10. Pinout Listing (Continued)Signal Name Pin NumberActive I/OPinout ListingsSERR E9Low I/O STOP A9Low I/O TRDYB9LowI/OInterrupt, Clock, and Power Management SignalsCKO (DWE2)L11High Output HRST L16Low Input NMI E15High Input QACK L14Low Output QREQ H16Low Input SYSCLK L6Clock Input SUSPENDH14LowInputTest/Configuration SignalsPLL[0–3]U11, T11, U12, T12High Input TCK F13Clock Input TDI B13High Input TDO E12High Output TMS D14High Input TRSTH13LowInputPower and Ground SignalsAVdd K9High Clock Power LSSD_MODE 2G11Low Input Vdd E10, E6, F11, F5, F7, G10, G12, G6, H5, H7, K10, K7, L12, M11, M5, M7, N10, N12, N6, P11, P5, P7, R10, R6, J8, L8High Power Vss E11, E7, F10, F12, F6, G5, G7, H12, H6, J7, L7, M10, M12, M6, N11, N5, N7, P10, P12, P6, R11, R7, K8, J9, L9Low Ground NCH8, H9, M8, M9——Note:1All PCI signals are in little-endian bit order.2This test signal is for factory use only. It must be pulled up to Vdd for normal device operation.Table 10. Pinout Listing (Continued)Signal NamePin NumberActive I/O。

kohl's defect list 中文翻译

主要疵点分类表——家纺主要疵点1..疵点影响了产品的外观,使用和质量以至于:客人看到疵点不会购买商品初次使用后因质量问题引起不满疵点造成的拒付通常要求供货商在装运之前仔细的检查和重新审计。

2. 产品必须达到一定的性能标准或测试要求1主要疵点=1分布料和颜色F01洞孔——纱线的断点(包括两头或经纬纱上的极小断点)漏针——编织上的缝纫故障会造成脱针断头——经纱断裂后并经过修补的地方,特别是可以看见织到织物当中的明显断头。

F02条花疵——由弯针造成的垂直裂缝硬折痕疵——由于在缩水率控制和稳定过程中采用起皱织物而造成的坚硬折痕。

横裆疵——物横列或在织物横向上通常会出现一些不均匀的花纹图案。

原因是纱线不均匀、纱线张力不均匀以及纱线具有不同的染料亲和力。

粗经疵——有一根经纱的直径要明显大于织物正常经纱的直径。

起毛不匀在一组套件中出现不同绒面,例如毛巾F03 切断纱向——不按经纱、条纹方向剪裁影响美观,造成缩水。

F04 影响美观的结、斑块或纱头F05彩色飞花织入疵,影响产品美观F06缺纬——编织纹由于缺纬而破坏F07影响美观的泥点、油斑、污点F08 织布水洗洗、织物整理不均,例如:存在过渡磨损、明显的水洗差异,或者与要求不符。

F09 乳胶衬里破损,能明显看到喷射在毯子前的乳胶衬里F10 影响美观的不均匀印染或色斑F11 违背已经认可的员工、加工标准F12 扭曲、压弯或严重起皱零件&装饰T01 未经允许的零件装饰影响了产品性能,例如:不正确的内衬、劣等松紧带、相对于经线包边的斜纹包边T02 指定的零件装饰没有按照指定要求意外的丢失、破损、瑕疵、损耗线向不正,影响产品外观和品质型号、尺寸、颜色、位置与要求不符不符合要求的不配套的色线或配件内衬/衬料内衬必须与布料合适;例如不合适的易熔化配件如果有衬里,在完成包边后,衬里不可露出。

在产品表面不可出见衬里、衬头掉线粘衬不可穿透纽扣:丢失;破损、瑕疵、定反的纽扣;与要求(例,式样)不符的纽扣;配件爱你与要求不符;纽扣小于14莱茵必须有4个孔拉链:失灵;不可使用爪型定位停止梢;使用铝制拉链;拉链部件未按指定要求,影响产品品质美观(例如,拉链齿、拉链牌、拉链带、拉链颜色、尺寸、长度);拉链带边缘露出,易扎手;所有拉链滑动必须是锁式的,也可是自动锁、半自动锁、针锁式。

H3C_S5130EI_E-CMW710-R3116_版本说明书

3 软件特性及命令行变更说明 ······························································································ 10 4 MIB变更说明 ················································································································· 10 5 操作方式变更说明··········································································································· 12

1.1 版本号 ························································································································1 1.2 历史版本信息···········································································ቤተ መጻሕፍቲ ባይዱ····································1 1.3 版本配套表···················································································································5 1.4 版本升级注意事项··········································································································7

ISO106中文资料

SIGNAL ISOLATION BUFFER AMPLIFIERSAPPLICATIONSq INDUSTRIAL PROCESS CONTROLTransducer channel isolator for thermo-couples, RTDs, pressure bridges, flowISOLATION AMPLIFIERS AT LOW COST2®ISO102/106SPECIFICATIONSELECTRICALAt T A = +25°C and V CC1 = V CC2 = ±15V unless otherwise noted.ISO102, ISO106, ISO102B, ISO106BPARAMETERCONDITIONSMINTYPMAXUNITSISOLATION VoltageRated Continuous (1)ISO102:AC, 60HzT MIN to T MAX 1500Vrms DCT MIN to T MAX 2121VDC ISO106:AC, 60HzT MIN to T MAX 3500Vrms DCT MIN to T MAX4950VDC Test Breakdown, AC, 60Hz ISO10210s 4000Vrms ISO10610s8000Vpk Isolation-Mode Rejection (2)V ISO = Rated Continuous, 60HzAC:ISO102115120dB 12µVrms/V ISO106125130dB 0.30.6µVrms/V DC140160dB 0.010.10µVDC/V Barrier Resistance 1014ΩBarrier Capacitance 6pF Leakage Current V ISO = 240Vrms, 60Hz 0.51µArms INPUTVoltage Range Rated Operation–10+10V Resistance 75100k ΩCapacitance 5pF OUTPUTVoltage RangeRated Operation –10+10V Derated Operation–12+12V Current Drive±5mA Short Circuit Current 92050mA Ripple Voltage (6) f = 0.5MHz to 1.5MHz3mVp-p Resistance0.31ΩCapacitive Load Drive Capability 10,000pF Overload Recovery Time, 0.1%|V O | > 12V30µs OUTPUT VOLTAGE NOISE Voltage:f = 0.1Hz to 10Hz300µVp-p f = 0.1Hz to 70kHz16µV/ Hz Dynamic Range (7):f = 0.1Hz to 70kHz12-Bit Resolution, 1LSB, 20V FS 74dB f = 0.1Hz to 280Hz 16-Bit Resolution, 1LSB, 20V FS96dB FREQUENCY RESPONSE Small Signal Bandwidth70kHz Full Power Bandwidth, 0.1% THD V O = ±10V 5kHz Slew RateV O = ±10V 0.5V/µs Settling Time, 0.1%V O = –10V to +10V100µs Overshoot, Small Signal (8)C 1 = C 2 = 040%VOLTAGE REFERENCES Voltage Output, Ref 1, Ref 2No Load +4.975+5+5.025VDC B GradeNo Load+4.995+5+5.005VDC vs Temperature ±520ppm/°C vs Supplies 10µV/V vs Load4001000µV/mA Current Output–0.1+5mA Short Circuit Current 61430mA POWER SUPPLIESRated Voltage, ±V CC1, ±V CC2Rated Performance±15V Voltage Range±10±20V Quiescent Current:+V CC1No Load+11+15mA –V CC1–9–12mA +V CC2+25+33mA –V CC2–15–20mA Dissipation:±V CC1300400mW ±V CC2600800mW TEMPERATURE RANGE Specification –25+85°C Operating (9)–25+85°C Storage–65+150°C Thermal Resistance, θJA40°C/W θJC12°C/W3®ISO102/106ELECTRICAL (CONT)ISO102ISO102B PARAMETER CONDITIONSMINTYP MAXMINTYP MAXUNITS GAINNominal Gain 1*V/V Initial Error (3)±0.1±0.250.070.13% FSR Gain vs Temperature ±20±50±12±25ppm FSR/°C Nonlinearity (4)V O = –10V to +10V±0.007±0.012±0.002±0.003% FSRINPUT OFFSET VOLTAGE Initial OffsetV IN = 0V±25±70±15±25mV vs Temperature ±250±500±150±250µV/°C vs Power Supplies (5)Input Stage, V CC1 = ±10V to ±20V 0 1.4 4.0***mV/V Output Stage, V CC2 = ±10V to ±20V–4–1.4***mV/VThe information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.ISO106ISO106B PARAMETER CONDITIONSMINTYP MAXMINTYP MAXUNITS GAINNominal Gain 1*V/V Initial Error (3)±0.1±0.250.07*% FSR Gain vs Temperature ±20±50±12±25ppm FSR/°C Nonlinearity (4)V O = –10V to +10V±0.04±0.075±0.007±0.025% FSRINPUT OFFSET VOLTAGE Initial OffsetV IN = 0V±25±70**mV vs Temperature ±250±500±150±250µV/°C vs Power Supplies (5)Input Stage, V CC1 = ±10V to ±20V 3.7*mV/V Output Stage, V CC2 = ±10V to ±20V–3.7*mV/V* Specification same as model to the left.NOTES: (1) 100% tested at rated continuous for one minute. (2) Isolation-mode rejection is the ratio of the change in output voltage to a change in isolation barrier voltage.It is a function of frequency as shown in the Typical Performance Curves. This is specified for barrier voltage slew rates not exceeding 100V/µs. (3) Adjustable to zero.FSR = Full Scale Range = 20V. (4) Nonlinearity is the peak deviation of the output voltage from the best fit straight line. It is expressed as the ratio of deviation to FSR.(5) Power supply rejection = change in V OS /20V supply change. (6) Ripple is the residual component of the barrier carrier frequency generated internally. (7) Dynamic range = FSR/(voltage spectral noise density x square root of user bandwidth). (8) Overshoot can be eliminated by band-limiting. (9) See “Power Dissipation vs Temperature” performance curve for limitations. (10) Band limited to 10Hz, bypass capacitors located less than 0.25" from supply pins.NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.4®ISO102/106PIN CONFIGURATION–V V Gain Adjust Common C Common Reference +V +V Offset Adjust Offset Reference Digital Common C V –V 1 2 3 4 9 10 11 1224 23 22 21 16 15 14 13CC1CC2CC1ISO1021OUT CC22 IsolationBarrierIN112 2–V V Gain Adjust Common C Common Reference +V +V Offset Adjust Offset Reference Digital Common C V –V 1 2 3 4 17 18 19 2040 39 38 37 24 23 22 21CC1CC2 CC1ISO1061OUT CC22 IsolationBarrierIN112 2PIN DESCRIPTIONS±V CC1,Positive and negative power supply voltages and common (or ground) for the input stage. Common 1 is the analog reference voltage for input Common 1signals. The voltage between Common 1 and Common 2 is the isolation voltage and appears across the internal high voltage barrier.±V CC2,Positive and negative power supply voltages and common (or ground) for the output stage. Common 2 is the analog reference voltage for output Common 2signals. The voltage between Common 1 and Common 2 is the isolation voltage and appears across the internal high voltage barrier.V IN Signal input pin. Input impedance is typically 100k Ω. The input range is rated for ±10V. The input level can actually exceed the input stage supplies. Output signal swing is limited only by the output supply voltages.Gain This pin is an optional signal input. A series 5k Ω potentiometer between this pin and the input signal allows a guaranteed ±1.5% gain adjustment Adjust range. When gain adjustment is not required, the Gain Adjust should be left open. Figure 4 illustrates the gain adjustment connection.Reference 1+5V reference output. This low-drift zener voltage reference is necessary for setting the bipolar offset point of the input stage. This pin must be strapped to either Offset or Offset Adjust to allow the isolation amplifier to function. The reference is often useful for input signal conditioning circuits. See “Effect of Reference Loading on Offset” performance curve for the effect of offset voltage change with reference loading.Reference 1 is identical to, but independent of, Reference 2. This output is short circuit protected.Reference 2+5V reference output. This reference circuit is identical to, but independent of, Reference 1. It controls the bipolar offset of the output stage through an internal connection. This output is short-circuit protected.Offset Offset input. This input must be strapped to Reference 1 unless user adjustment of bipolar offset is required.Offset This pin is for optional offset control. When connected to the Reference 1 pin through a 1k Ω potentiometer, ±150mV of adjustment range is Adjust guaranteed. Under this condition, the Offset pin should be connected to the Offset Adjust pin. When offset adjustment is not required, the Offset Adjust pin is left open. See Figure 4.Digital Digital common or ground. This separate ground carries currents from the digital portions of the output stage circuit. The best grounding practi-Common ces require that digital common current does not flow in analog common connections. Both pins can be tied directly to a ground plane if available.Difference in potentials between the Common 2 and Digital Common pins can be ±1V. See Figure 2.V OUTSignal output. Because the isolation amplifier has unity gain, the output signal is ideally identical to the input signal. The output is low impedance and is short-circuit protected. This signal is referenced to Common 2; subsequent circuitry should have a separate “sense” connection to Common 1as well as V OUT .C 1, C 2Capacitors for small signal bandwidth control. These pins connect to the internal rolloff frequency controlling nodes of the output low-pass filter.Additional capacitance added to these pins will modify the bandwidth of the buffer. C 2 is always twice the value of C 1. See “Bandwidth Control”performance curve for the relationship between bandwidth and C 1 and C 2. When no connections are made to these pins, the full small-signal bandwidth is maintained. Be sure to shield C 1 and C 2 pins from high electric fields on the PC board. This preserves AC isolation-mode rejection by reducing capacitive coupling effects.5®ISO102/106TYPICAL PERFORMANCE CURVEST A = +25°C, V CC = ±15VDC unless otherwise noted.ISOLATION-MODE REJECTION vs ISOLATION VOLTAGE FREQUENCYIsolation Voltage Frequency (Hz)I s o l a t i o n -M o d e R e j e c t i o n (d B )1601401201008060 101M1001k10k100kDYNAMIC RANGE vs BANDWIDTHSmall Signal Bandwidth (Hz)Bandwidth Control Capacitors (F)D y n a m i c R a n g e (d B )120110100908070 110 100 1k 10k 100k 3µ300n30n3nF300p30pBW — C — 1ISOLATION LEAKAGE CURRENT vs ISOLATION VOLTAGE FREQUENCYIsolation Voltage Frequency (Hz)I s o l a t i o n L e a k a g e C u r r e n t (A )101M10m1m100µ10µ1µ100n1001k10k100kIsolation Voltage (V)Rated10.5–0.5–1210 –1 –2 GainOffsetT = T to T MIN MAX∆ GAIN ERROR AND ∆ OFFSET VOLTAGEvs ISOLATION VOLTAGEG a i n E r r o r (%)∆ ∆ O f f s e t V o l t a g e (m V )BANDWIDTH CONTROLC 1 (F)S m a l l S i g n a l B a n d w i d t h (H z )1M100k10k 1k 10010 13p30p300p3n 30n300n 3µPOWER DISSIPATION vs TEMPERATUREAmbient Temperature (°C)M a x i m u m P o w e r D i s s i p a t i o n (W )1.61.41.210.80M a x i m u m P o w e r S u p p l i e s (V )±20±15±106®ISO102/106TYPICAL PERFORMANCE CURVES (CONT)T A = +25°C, V CC = ±15VDC unless otherwise noted.LARGE SIGNAL TRANSIENT RESPONSETime (µs)100200 30040015 105 0 –5 –10 –15O u t p u t V o l t a g e (V )TOTAL HARMONIC DISTORTIONFrequency (Hz)1001k 10k100kT H D + N o i s e (%)1010.10 RECOMMENDED RANGE OF ISOLATION VOLTAGEIsolation Voltage Frequency (Hz)1k10k100k1M10k M a x i m u m I s o l a t i o n V o l t a g e (V p k )1k10010 2k 5kGAIN/PHASE vs FREQUENCY101001k10k100kFrequency (Hz)S m a l l S i g n a l G a i n (d B )6–6–12–1890–90–180–270P h a s e S h i f t (d e g r e e s )OUTPUT SPECTRAL NOISE DENSITY40 35 30 25 20 15 10 5 0 S p e c t r a l N o i s e D e n s i t y (d B H z )10µV / H z 01020 30 40 50 Frequency (kHz) N: 128 : 125Hz FS: –47dBVβ GAIN FLATNESS vs FREQUENCY0 1 2 3 4 5 6 7 8Frequency (kHz)L a r g e S i g n a l G a i n (d B )0.030.02 0.01 0 –0.01 –0.02 –0.037®ISO102/106TYPICAL PERFORMANCE CURVES (CONT)T A = +25°C, V CC = ±15VDC unless otherwise noted.FIGURE 1. Simplified Diagram of ISO102 and ISO106.THEORY OF OPERATIONThe ISO102 and ISO106 have no galvanic connection be-tween the input and output. The analog input signal refer-enced to the input common is accurately duplicated at the output referenced to the output common. Because the barrier information is digital, potentials between the two commons can assume a wide range of voltages and frequencies with-out influencing the output signal. Signal information re-mains undisturbed until the slew rate of the barrier voltage exceeds 100V/µs. The isolation amplifier’s ability to reject fast dV/dt changes between the two grounds is specified as transient immunity. The amplifier is protected from damage for slew rates up to 100,000V/µs.A simplified diagram of the ISO102 and ISO106 is shown in Figure 1. The design consists of an input voltage-controlled oscillator (VCO) also known as a voltage-to-frequency con-verter (VFC), differential capacitors, and output phase lock loop (PLL). The input VCO drives digital levels directly into the two 3pF barrier capacitors. The digital signal is fre-quency modulated and appears differentially across the bar-rier, while the externally applied isolation voltage appears common-mode.EFFECT OF REFERENCE LOADING ON OFFSETVoltage Reference Load (mA)1250–50O u t p u t O f f s e t (m V )0.010.005–0.005–0.01ISO102B TYPICAL LINEARITY–100 10V OUT = V IN (V)N o n l i n e a r i t y (%)5–58®ISO102/106A sense amplifier detects only the differential information.The output stage decodes the frequency modulated signal by the means of a PLL. The feedback of the PLL employs a second VCO that is identical to the encoder VCO. The PLL forces the second VCO to operate at the same frequency (and phase) as the encoder VCO; therefore, the two VCOs have the same input voltage. The input voltage of the decoder VCO serves as the isolation buffer’s output signal after passing through a 100kHz second-order active filter.For a more detailed description of the internal operation of the ISO102 and ISO106, refer to Proceedings of the 1987International Symposium on Microelectronics, pages 202-206.ABOUT THE BARRIERFor any isolation product, barrier composition is of para-mount importance in achieving high reliability. Both the ISO102 and ISO106 utilize two 3pF high voltage ceramic coupling capacitors. They are constructed of tungsten thick film deposited in a spiral pattern on a ceramic substrate.Capacitor plates are buried in the package, making the barrier very rugged and hermetically sealed. Capacitance results from the fringing electric fields of adjacent metal runs. Dielectric strength exceeds 10kV and resistance is typically 1014Ω. Input and output circuitry are contained in separate solder-sealed cavities, resulting in the industry’s first fully hermetic hybrid isolation amplifier.FIGURE 3. Technique for Wiring Analog and Digital Com-mons Together.FIGURE 2. Power Supply and Signal Connection.The ISO102 and ISO106 are designed to be free from partial discharge at rated voltages. Partial discharge is a form of localized breakdown that degrades the barrier over time.Since it does not bridge the space across the barrier, it is difficult to detect. Both isolation amplifiers have been exten-sively evaluated at high temperature and high voltage.POWER SUPPLY AND SIGNAL CONNECTIONS Figure 2 shows the proper power supply and signal connec-tions. Each supply should be AC-bypassed to Analog Com-mon with 0.1µF ceramic capacitors as close to the amplifier as possible. Short leads will minimize lead inductance. A ground plane will also reduce noise problems. Signal com-mon lines should tie directly to the common pin even if a low impedance ground plane is used. Refer to Digital Com-mon in the Pin Descriptions table.To avoid gain and isolation-mode rejection (IMR) errors introduced by the external circuit, connect grounds as indi-cated, being sure to minimize ground resistance. Any ca-pacitance across the barrier will increase AC leakage current and may degrade high frequency IMR. The schematic in Figure 3 shows the proper technique for wiring analog and digital commons together.DISCUSSION OF SPECIFICATIONSThe IS0102 and IS0106 are unity gain buffer isolation amplifiers primarily intended for high level input voltages on the order of 1V to 10V. They may be preceded by operational, differential, or instrumentation amplifiers that precondition a low level signal on the order of millivolts and translate it to a high level.9®ISO102/106noise power varies with the square root of the bandwidth ofthe buffer. It is recommended that the bandwidth be reduced to about twice the maximum signal bandwidth for optimum dynamic range as shown in the “Dynamic Range vs Band-width” performance curve. The output spectral noise density measurement is displayed in the “Output Spectral Noise Density” performance curve. The noise is flat to within 5dB Hz between 0.1Hz to 70kHz.The overall AC gain of the buffer amplifiers is shown in two performance curves: “Gain Flatness vs Frequency” and “Gain/Phase vs Frequency.” Note that with C 1 = 100pF and C 2 = 200pF, the AC gain remains flat within ±0.01dB up to 7kHz. The total harmonic distortion for large-signal sine wave outputs is plotted in the “Total Harmonic Distortion”performance curve. The phase-lock-loop displays slightly nonuniform rise and fall edges under maximum slew condi-tions. Reducing the output filter bandwidth to below 70kHz smoothes the output signal and eliminates any overshoot.See the “Large Signal Transient Response” performance curve.OPTIONAL OFFSET AND GAIN ADJUSTMENT In many applications the factory-trimmed offset is adequate.For situations where reduced or modified gain and offset are required, adjustment of each is easy. The addition of two potentiometers as shown in Figure 4 provides for a two step calibration.Offset should be adjusted first. Gain adjustment does not interfere with offset. The potentiometer’s TCR adds only 2% to overall temperature drift. The offset and gain adjust-ment procedures are as follows:1. Set V IN to 0V and adjust R 1 to desired offset at the output.2. Set V IN to full scale (not zero). Adjust R 2 for desired gain.ISOLATION-MODE REJECTIONThe IS0102 and IS0106 provide exceptionally high isola-tion-mode rejection over a wide range of isolation-mode voltages and frequencies. The typical performance curves should be used to insure operation within the recommended range. The maximum barrier voltage allowed decreases as the frequency of the voltage increases. As with all isolation amplifiers, a change of voltage across the barrier will induce leakage current across the barrier. In the case of the IS0102and IS0106, there exists a threshold of leakage current through the signal capacitors that can cause over-drive of the decoder’s sense amplifier. This occurs when the slew rate of the isolation voltage reaches 100V/µs. The output will recover in about 50µs from transients exceeding 100V/µs.The first two performance curves indicate the expected isolation-mode rejection over a wide range of isolation voltage frequencies. Also plotted is the typical leakage current across the barrier at 240Vrms. The majority of the leakage current is between the input common pin and the output digital ground pin.The IS0102 and IS0106 are intended to be continuously operated with fully rated isolation voltage and temperature without significant drift of gain and offset. See the “Gain Error/Offset Isolation Voltage” performance curve for changes in gain and offset with isolation voltage.SUPPLY AND TEMPERATURE RANGEThe IS0102 and IS0106 are rated for +15V supplies; how-ever, they are guaranteed to operate from ±10V to ±20V.Performance is also rated for an ambient temperature range of –25°C to +85°C. For operation outside this temperature range, refer to the “Power Dissipation vs Temperature”performance curve to establish the maximum allowed sup-ply voltage. Supply currents are fairly insensitive to changes in supply voltage or temperature. Therefore, the maximum current limits can be used in computing the maximum junction temperature under nonrated conditions.OPTIONAL BANDWIDTH CONTROLThe following discussion relates optimum dynamic range performance to bandwidth, noise, and settling time.The outputs of the IS0102 and IS0106 are the outputs of a second-order low-pass Butterworth filter. Its low impedance output is rated for ±5mA drive and ±12V range with 10,000pF loads. The closed-loop bandwidth of the PLL is 70kHz,while the output filter is internally set at 100kHz. The output filter lowers the residual voltage of the barrier FM signal to below the noise floor of the output signal.Two pins are available for optional modification of the filter’s bandwidth. Only two capacitors are required. The “Bandwidth Control” performance curve gives the value of C 1 (C 2 is equal to twice C 1) for the desired bandwidth. Figure 4 illustrates the optional connection of both capacitors.A tradeoff can be achieved between the required signal bandwidth and system dynamic range. The noise floor of the output limits the dynamic range of the output signal. TheFIGURE 4. Optional Gain Adjust, Offset Adjust, and Band-width Control.10®ISO102/106PRINTED CIRCUIT BOARD LAYOUTThe distance across the isolation barrier, between external components, and conductor patterns, should be maximized to reduce leakage and arcing at high voltages. Good layout techniques that reduce stray capacitance will assure low leakage current and high AC IMR. For some applications,applying conformal coating compound such as urethane is useful in maintaining good performance. This is especially true where dirt, grease or moisture can collect on the PC board surface, component surface, or component pins. Fol-lowing this industry-accepted practice will give best results,particularly when circuits are operated or tested in a mois-ture-condensing environment. Optimum coating can be achieved by administering urethane under vacuum condi-tions. This allows complete coverage of all areas. Grounded rings around the C l and C 2 contacts on the board greatly reduce high voltage electric fields at these pins.APPLICATIONSThe ISO102 and ISO106 isolation amplifiers are used inthree categories of applications:1.accurate isolation of signals from high voltage ground potentials,2.accurate isolation of signals from severe ground noise,and3.fault protection from high voltages in analog measure-ment systems.Figures 5 through 15 show a variety of application circuits.Additional discussion of applications can be found in the December 11, 1986 issue of Electronic Design, pages 91-96.FIGURE 5. Isolated Power Current Monitor for Motor Cir-cuit. (The ISO102 allows reliable, safe measure-ment at high voltages.)FIGURE 6. Isolated Power Line Monitor (0.5µA leakagecurrent at 120Vrms).FIGURE 7. Battery Monitor for High Voltage ChargingCircuit.FIGURE 8. Isolated RTD Temperature Amplifier.FIGURE 10. Isolation Amplifier with Isolated Bipolar InputReference.FIGURE 9. Programmable-Gain Isolation Channel with Gainsof 1, 10, and 100.FIGURE 11. Low Cost Eight-Channel Isolation Amplifier Block with Channel-to-Channel Isolation.FIGURE 12. Thermocouple Amplifier with Ground Loop Elimination, Cold Junction Compensation, and Upscale Burn-out.FIGURE 13. Remote Isolated Thermocouple Transmitter with Cold Junction Compensation.FIGURE 14. Isolated Instrumentation Amplifier for 300Ω Bridge. (Reference voltage from isolation amplifier is used to excite bridge.)FIGURE 15. Right-Leg-Driven ECG Amplifier (with defibrillator protection and calibrator).AN ERROR ANALYSIS OF THE IS0102 IN A SMALL SIGNAL MEASURING APPLICATIONHigh accuracy measurements of low-level signals in the presence of high isolation mode voltages can be difficult due to the errors of the isolation amplifiers themselves.This error analysis shows that when a low drift operational amplifier is used to preamplify the low-level source signal, a low cost, simple and accurate solution is possible.In the circuit shown in Figure 16, a 50mV shunt is used to measure the current in a 500VDC motor. The OPA27 amplifies the 50mV by 200 x to 10V full scale. The output of the OPA27 is fed to the input of the IS0102, which is a unity-gain isolation amplifier. The 5kΩ and 1kΩ potentiom-eters connected to the IS0102 are used to adjust the gain and offset errors to zero as described in Discussion of Specifica-tions.Some ObservationsThe total errors of the op amp and the ISO amp combined are approximately 0.11% of full-scale range (see Figure 17). If the op amp had not been used to preamplify the signal, the errors would have been 2.6% of FSR. Clearly, the small cost of adding the op amp buys a large performance improve-ment. Optimum performance, therefore, is obtained when the full ±10V range of the IS0102/106 is utilized.The rms noise of the IS0102 with a 120Hz bandwidth is only 0.18mVrms, which is only 0.0018% of the 10V full scale output. Therefore, even though the 16µV/ √Hz noise spectral density specification may appear large compared to other isolation amplifiers, it does not turn out to be a significant error term. It is worth noting that even if the bandwidth is increased to 10kHz, the noise of the iso amp would only contribute 0.016%FSR error.FIGURE 16. 50mV Shunt Measures Current in a 500VDC Motor.The Errors of the Op Amp at 25°C (Referred to Input, RTI)V E (OPA) = V D1 – 1 + 1 + V OS (1 + R 1/R F ) + I B R 1 + P.S.R. + NoiseV E (OPA) = Total Op Amp Error (RTI)V D = Differential Voltage (Full Scale) Across Shunt1 – 1 + 1 = Gain Error Due to Finite Open Loop Gainβ = Feedback FactorA VOL = Open Loop Gain at Signal Frequency V OS = Input Offset Voltage IB = Input Bias CurrentP.S.R. = Power Supply Rejection (µV/V) [Assuming a 5% change with ±15V supplies. Total error is twice that due to one supply.]Noise = 5nV/ Hz (for 1k Ω source resistance and 1kHz bandwidth)ERROR (OPA) (RTI)GAIN ERROR OFFSETP.S.R.NOISE V E (OPA)=50mV 1 – 1 + 1{0.025mV (1 + 1/200) + 40 x 10–9 x 103}(20µV/V x 0.75V x 2){5nV √120 (nVrms)}=0.01mV (0.0251mV + 0.04mV)+0.03mV +0.055 x 10–3mVrms Error as % of FSR =0.02%+(0.05% + 0.08%)+0.06%+0.00011%After Nulling=0.01mV +(0mV + 0mV)+0.03mV+0.055 x 10–3mVrms=0.10mV Error as % of FSR*=0.02%+(0% + 0%)+0.06%+0.00011%=0.08% of 50mV*FSR = Full-Scale Range. 50mV at input to op amp, or 10V at input (and output) of ISO amp.The Errors of the Iso Amp at 25°C (RTI)V E (ISO) = 1/200 (V ISO /IMR + V OS + G.E. + Nonlinearity + P.S.R. + Noise)V E (ISO) = Total ISO Amp Error IMR = Isolation Mode Rejection V OS = Input Offset VoltageV ISO = V IMV = Isolation Voltage = Isolation Mode Voltage G.E. = Gain Error (% of FSR)Nonlinearity = Peak-to-peak deviation of output voltage from best-fit straight line. It is expressed as ratio based on full-scale range.P.S.R. = Change in V OS /10V x Supply ChangeNoise = Spectral noise density x √bandwidth. It is recommended that bandwidth be limited to twice maximum signal bandwidth for optimum dynamic range.ERROR (ISO) (RTI)IMRV OS G.E.NONLINEARITYP.S.R.NOISE V E (ISO)=1/200 { 500VDC/140dB+70mV +20V x 0.25/100+0.003/100 x 20V1.4mV x 0.75V x 2+16µV √120 (rms) }=1/200 { 0.05mV+70mV +50mV +0.6mV + 2.1mV +0.175mVrms }Error as % of FSR =0.0005%+0.7%+0.5%+0.006%+0.021%+0.00175%After Nulling V E (ISO)=1/200 { 0.05mV +0mV+0mV+0.6mV+2.1mV+0.175mVrms }=1/200 (3.0mV)=0.03mV Error as % of FSR =0.0005%+0%+0%+0.006%+0.021%+0.00175%=0.03% of 50mVTotal Error=V E (OPA)+V E (ISO)=0.10mV +0.03mV =0.08% of 50mV +0.03% of 50mV=0.11% of 50mV{}β A VOL{}β A VOL{ }106/200FIGURE 17. Op Amp and Iso Amp Error Analysis.111。

第五章 信源编码LVRH1010

解:将信源通过一个二元信道传输,就必须把信源符号si变换 成由0,1符号组成的码符号序列,即进行编码。可以用不同 的二元码符号序列与信源符号 一一对应,就得到不同的码。

信源符号 P(si) s1 s2 s3 s4 P(s1) P(s2) P(s3) P(s4) 码1 00 01 10 11 码2 0 01 001 111 5.1 编码的定义 定长码 变长码 二次扩展信源符号 二次扩展码字 S1=S1S1 s2=S1S2 …… s4=S4S4 00 001 …… 111111

l ≥ log r q = 5

分析:考虑到符号出现的概率以及符号之间的相关性后,实际平均每 分析 个英文电报符号所提供的信息量约1.4bit,远小于5bit,因此定长编码 后,每个码字只载1.5bit信息,5个二进制符号最大能载5bit信息 ,因 此,定长编码的信息传输效率低。 解决方案: 解决方案 (1)对于不会出现的符号序列不予编码,这样不会造成误差; (2)对于概率非常小的信源符号序列不予编码,这样可能会造成一 定误差,但当信源符号序列N足够大,误差概率非常小

第五章 信源编码 五

问题

• 对信源有两个重要问题 1. 信源输出的信息量的度量问题 度量问题; 度量问题 2. 如何更有效地 有效地表示信源输出的问题 输出的问题; 有效地 输出的问题

信源输出的符号序列,经过信源编码,变换成 适合信道传输的符号序列,同时,在不失真或允许 一定失真的条件下,用尽可能少的码符号来传递信 源消息,提高信息传输的效率。

i =1 8

a7 0.05

a8 , 0.04

HL (X ) 2 .55 得K = = 2.83bit / 符号 90 % K 即每个符号用 2.83bit 进行定长二元编码,共 有 2 2.83 = 7.11种可能性 若取 L = 1,据 η = 根据 η = H( X ) = 0.9 ⇒ ε = 0 .28 H (X ) + ε

西门子(Siemens)S7-1500R H 冗余系统的 PROFINET说明书

SIMATICPROFINET使用 STEP 7 组态 PROFINET功能手册11/2022A5E03444491-AMSiemens AGDigital Industries Postfach 48 48A5E03444491-AMⓅ 10/2022 本公司保留更改的权利Copyright © Siemens AG 2013 - 2022.保留所有权利法律资讯警告提示系统为了您的人身安全以及避免财产损失,必须注意本手册中的提示。

人身安全的提示用一个警告三角表示,仅与财产损失有关的提示不带警告三角。

警告提示根据危险等级由高到低如下表示。

危险表示如果不采取相应的小心措施,将会导致死亡或者严重的人身伤害。

警告表示如果不采取相应的小心措施,可能导致死亡或者严重的人身伤害。

小心表示如果不采取相应的小心措施,可能导致轻微的人身伤害。

注意表示如果不采取相应的小心措施,可能导致财产损失。

当出现多个危险等级的情况下,每次总是使用最高等级的警告提示。

如果在某个警告提示中带有警告可能导致人身伤害的警告三角,则可能在该警告提示中另外还附带有可能导致财产损失的警告。

合格的专业人员本文件所属的产品/系统只允许由符合各项工作要求的合格人员进行操作。

其操作必须遵照各自附带的文件说明,特别是其中的安全及警告提示。

由于具备相关培训及经验,合格人员可以察觉本产品/系统的风险,并避免可能的危险。

按规定使用 Siemens 产品请注意下列说明:警告Siemens 产品只允许用于目录和相关技术文件中规定的使用情况。

如果要使用其他公司的产品和组件,必须得到Siemens 推荐和允许。

正确的运输、储存、组装、装配、安装、调试、操作和维护是产品安全、正常运行的前提。

必须保证允许的环境条件。

必须注意相关文件中的提示。

商标所有带有标记符号 ® 的都是 Siemens AG 的注册商标。

本印刷品中的其他符号可能是一些其他商标。

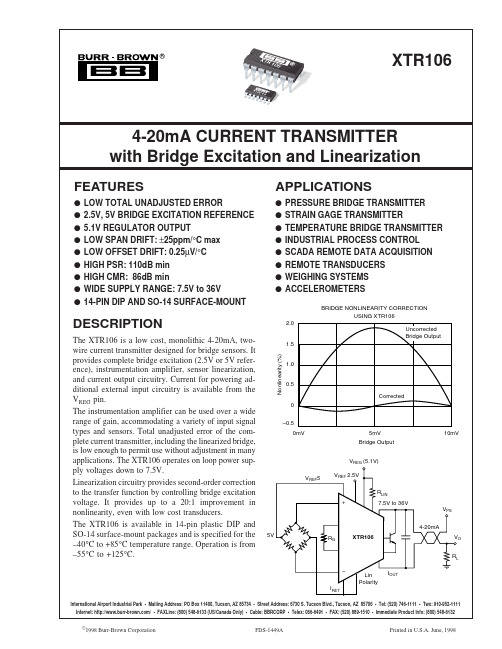

XTR106U中文资料

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: / • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©

1998 Burr-Brown Corporation

PDS-1449A

Printed in U.S.A. June, 1998

元器件交易网

SPECIFICATIONS

At TA = +25°C, V+ = 24V, and TIP29C external transistor, unless otherwise noted. XTR106P, U PARAMETER OUTPUT Output Current Equation Output Current, Specified Range Over-Scale Limit Under-Scale Limit ZERO OUTPUT(1) Initial Error vs Temperature vs Supply Voltage, V+ vs Common-Mode Voltage (CMRR) vs VREG (IO) Noise: 0.1Hz to 10Hz SPAN Span Equation (Transconductance) Untrimmed Error vs Temperature(2) Nonlinearity: Ideal Input (3) INPUT(4) Offset Voltage vs Temperature vs Supply Voltage, V+ vs Common-Mode Voltage, RTI Common-Mode Range(5) Input Bias Current vs Temperature Input Offset Current vs Temperature Impedance: Differential Common-Mode Noise: 0.1Hz to 10Hz VOLTAGE REFERENCES(5) Initial: 2.5V Reference 5V Reference Accuracy vs Temperature vs Supply Voltage, V+ vs Load Noise: 0.1Hz to 10Hz VREG(5) Accuracy vs Temperature vs Supply Voltage, V+ Output Current Output Impedance LINEARIZATION(6) RLIN (external) Equation KLIN Linearization Factor Accuracy vs Temperature Max Correctable Sensor Nonlinearity POWER SUPPLY Specified Voltage Range TEMPERATURE RANGE Specification Operating Storage Thermal Resistance 14-Pin DIP SO-14 Surface Mount VREF2.5 VREF5 VREF = 2.5V or 5V TA = –40°C to +85°C V+ = 7.5V to 36V IREF = 0mA to 2.5mA VREG TA = –40°C to +85°C V+ = 7.5V to 36V IREG I REG = 0mA to 2.5mA RLIN KLIN VREF = 5V VREF = 2.5V TA = –40°C to +85°C VREF = 5V VREF = 2.5V IO IOVER I UNDER IZERO CONDITIONS MIN IO = VIN 4 24 1 2.9 TYP MAX MIN XTR106PA, UA TYP MAX UNITS A mA mA mA mA mA µA µA/°C µA/V µA/V µA/mA µAp-p A/V % ppm/°C % µV µV/°C µV/V µV/V V nA pA/°C nA pA/°C GΩ || pF GΩ || pF µVp-p

lte中文协议下载

竭诚为您提供优质文档/双击可除lte中文协议下载篇一:td-lte协议简介--中文lte基站-终端空中接口标准1范围本部分规定了ltetdd数字蜂窝移动通信网中用户设备(ue)与演进基站(enb)之间,即uu接口的无线资源管理(RRc)部分。

本部分适用于lteFdd数字蜂窝移动通信网。

2术语、定义和缩略语3规范性引用文件[1]3gppts36.201V.9.1.0:“evolveduniversalterrestrialRadioaccess(e-utRa);longtermevolution(lte)physicallayer;generaldescription”.[2]3gppts36.211V.9.1.0:“evolveduniversalterrestrialRadioaccess(e-utRa);physicalchannelsandmodution”.[3]3gppts36.212V.9.4.0:“evolveduniversalterrestrialRadioaccess(e-utRa);multiplexingandchannelcoding”.[4]3gppts36.213V.9.3.0:“evolveduniversalterrestrialRadioaccess(e-utRa);physicallayerprocedures”.[5]3gppts36.321V.9.6.0:“evolveduniversalterrestrialRadioaccess(e-utRa);mediumaccesscontrol(mac)protocolspecification”.[6]3gppts36.322V.9.3.0:“evolveduniversalterrestrialRadioaccess(e-utRa);Radiolinkcontrol(Rlc)protocolspecification”.[7]3gppts36.323V.9.0.0:“evolveduniversalterrestrialRadioaccess(e-utRa);packetdataconvergenceprotocol(pdcp)specification”.[8]3gppts36.331V.9.13.0:“evolveduniversalterrestrialRadioaccess(e-utRa);RadioResourcecontrol(RRc);protocolspecification”.4概述lte接入网协议可以分为3个层次的结构,由下至上依次为:物理层(层1)、数据链路层(层2)和网络层(层3),如图3-1所示。

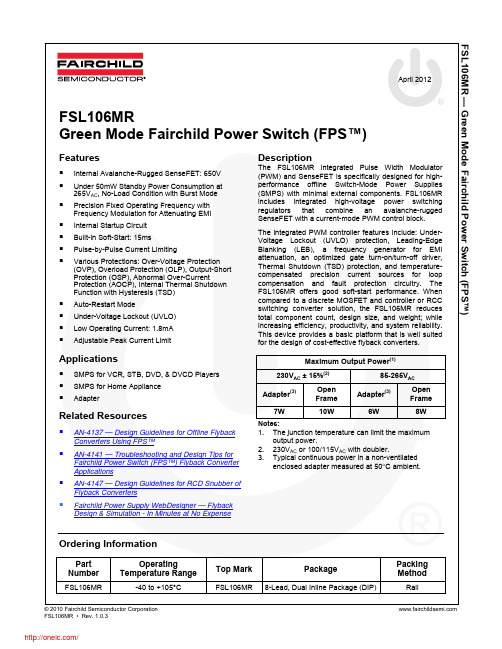

FSL106MR;中文规格书,Datasheet资料

Description

The FSL106MR integrated Pulse Width Modulator (PWM) and SenseFET is specifically designed for highperformance offline Switch-Mode Power Supplies (SMPS) with minimal external components. FSL106MR includes integrated high-voltage power switching regulators that combine an avalanche-rugged SenseFET with a current-mode PWM control block. The integrated PWM controller features include: UnderVoltage Lockout (UVLO) protection, Leading-Edge Blanking (LEB), a frequency generator for EMI attenuation, an optimized gate turn-on/turn-off driver, Thermal Shutdown (TSD) protection, and temperaturecompensated precision current sources for loop compensation and fault protection circuitry. The FSL106MR offers good soft-start performance. When compared to a discrete MOSFET and controller or RCC switching converter solution, the FSL106MR reduces total component count, design size, and weight; while increasing efficiency, productivity, and system reliability. This device provides a basic platform that is well suited for the design of cost-effective flyback converters. Maximum Output Power(1) 230VAC ± 15%(2) Adapter(3) 7W

16.附件9:货车、卡车常用协议SAE_J1939-71协议解析

前言

本文档也已经按照 SAE 技术标准公告版格式作了修改。定义改为第 3 部分,而缩写改 为第 4 部分。其他所有部分的编号也做相应改变。 本系列 SAE 推荐操作规程是由卡车及客车电子电气委员会所属的卡车及客车控制及通 信小组委员会制定的。该小组委员会的目标是针对电控单元的需求、设计和使用,提交消息 报告、制定推荐操作规程。这些电控单元在汽车部件之间传递着电子信号和控制信息。本规 程的使用不限于卡车和客车应用, 其对于其他的应用也可以提供直接的支持, 正如已在建筑 及农业设备和固定式的动力系统。 本推荐操作规程的最终目标是形成工业标准, 因此可能为适应实际应用和技术进步作出 经常性的调整。 目 录 前言 .................................................................................................................................................. 1 1 目标 .......................................................................................................................................... 6 2 参考 .......................................................................................................................................... 6 2.1 相关文档 ................................................................................................................... 6 2.1.1 SAE 出版物 ...................................................................................................... 6 2.1.2 ISO 出版物 ....................................................................................................... 6 3 定义 .......................................................................................................................................... 6 4 缩写 .......................................................................................................................................... 6 5 技术规定................................................................................................................................... 7 5.1 常规原则 ................................................................................................................... 7 5.1.1 信号特征描述 ................................................................................................... 7 5.1.2 消息格式 ........................................................................................................... 7 5.1.3 ISO 拉丁语-1 字母组 ....................................................................................... 7 5.1.4 参数数值范围 ................................................................................................... 8 5.1.5 新参数的数值范围分配 ................................................................................... 9 5.1.6 在参数群中添加参数 ..................................................................................... 12 5.1.7 传输重复速度(更新速度) ......................................................................... 12 5.1.8 发动机参数的命名惯例 ................................................................................. 13 5.2 参数定义 ................................................................................................................. 13 5.2.1 控制参数 ......................................................................................................... 14 5.2.2 驱动系统状态参数 ......................................................................................... 37 5.2.3 驱动系统控制参数 ......................................................................................... 53 5.2.4 动力系统状态设置参数 ................................................................................. 61

Intel Arria 10 内核架构和通用 I O 手册说明书

Intel® Arria® 10内核架构和通用I/O手册本翻译版本仅供参考,如果本翻译版本与其英文版本存在差异,则以英文版本为准。

某些翻译版本尚未更新对应到最新的英文版本,请参考英文版本以获取最新信息。

在线版本发送反馈A10-HANDBOOKID: 683461版本: 2017.05.08内容内容1. Arria® 10器件中的逻辑阵列模块与自适应逻辑模块 (7)1.1. LAB (7)1.1.1. MLAB (8)1.1.2. 本地和直链(Direct Link)互联 (9)1.1.3. 共享算术链和进位链互联 (10)1.1.4. LAB控制信号 (11)1.1.5. ALM资源 (12)1.1.6. ALM输出 (13)1.2. ALM操作模式 (14)1.2.1. 正常模式 (14)1.2.2. 扩展LUT模式 (17)1.2.3. 算术模式 (18)1.2.4. 共享算术模式 (20)1.3. LAB功耗管理技术 (21)1.4. 文档修订历史 (21)2. Arria 10器件中的嵌入式存储器模块 (22)2.1. 嵌入式存储器类型 (22)2.1.1. Arria 10器件中的嵌入式存储器性能 (23)2.2. Arria 10器件的嵌入式存储器设计指南 (23)2.2.1. 考虑存储器模块选择 (23)2.2.2. 指南:实现外部冲突消解 (24)2.2.3. 指南:定制Read-During-Write行为 (24)2.2.4. 指南:考虑上电状态和存储器初始化 (27)2.2.5. 指南:控制时钟来降低功耗 (28)2.3. 嵌入式存储器特性 (28)2.4. 嵌入式存储器模式 (29)2.4.1. 单端口模式的嵌入式存储器配置 (30)2.4.2. 双端口模式的嵌入式存储器配置 (30)2.5. 嵌入式存储器时钟模式 (32)2.5.1. 每种存储器模式的时钟模式 (32)2.5.2. 时钟模式中的异步清零 (32)2.5.3. 同步读/写中的输出读数据 (33)2.5.4. 时钟模式的独立时钟使能 (33)2.6. 嵌入式存储器模块中的奇偶校验位 (33)2.7. 嵌入式存储器模块中的字节使能 (33)2.7.1. 存储器模块中的字节使能控制 (34)2.7.2. 数据字节输出 (34)2.7.3. RAM模块操作 (34)2.8. 存储器模块Packed模式支持 (35)2.9. 存储器模块地址时钟使能支持 (35)2.10. 存储器模块异步清零 (36)2.11. 存储器模块纠错码支持 (37)2.11.1. 纠错码真值表 (38)Intel® Arria® 10内核架构和通用I/O手册发送反馈22.12. 文档修订历史 (38)3. Arria 10器件中的精度可调DSP 模块 (40)3.1. Arria 10器件中支持的操作模式 (40)3.1.1. 特性 (41)3.2. 资源 (42)3.3. 设计考量 (43)3.3.1. 操作模式 (44)3.3.2. 用于定点运算的内部系数和预加器 (45)3.3.3. 用于定点运算的累加器 (45)3.3.4. Chainout 加法器 (45)3.4. 模块体系结构 (45)3.4.1. 输入寄存器组(Input Register Bank) (47)3.4.2. 流水线寄存器 (49)3.4.3. 定点运算的预加器 (49)3.4.4. 定点运算的内部系数 (50)3.4.5. 乘法器 (50)3.4.6. 加法器 (50)3.4.7. 用于定点运算的累加器和Chainout 加法器 (50)3.4.8. 用于定点运算的脉动寄存器 (51)3.4.9. 用于定点运算的双倍累加寄存器 (51)3.4.10. 输出寄存器组(Output Register Bank) (51)3.5. 操作模式说明 (52)3.5.1. 定点运算的操作模式 (53)3.5.2. 浮点运算的操作模式 (59)3.6. 文档修订历史 (66)4. Arria 10器件中的时钟网络和PLL (68)4.1. 时钟网络 (68)4.1.1. Arria 10器件中的时钟资源 (69)4.1.2. 层次化时钟网络 (71)4.1.3. 时钟网络类型 (72)4.1.4. 时钟网络源 (76)4.1.5. 时钟控制模块 (77)4.1.6. 时钟断电 (80)4.1.7. 时钟使能信号 (80)4.2. Arria 10 PLL (81)4.2.1. PLL 使用 (82)4.2.2. PLL 体系结构 (83)4.2.3. PLL 控制信号 (83)4.2.4. 时钟反馈模式 (84)4.2.5. 时钟倍频与分频 (85)4.2.6. 可编程相移 (85)4.2.7. 可编程占空比 (86)4.2.8. PLL 级联 (86)4.2.9. 参考时钟源 (86)4.2.10. 时钟切换 (87)4.2.11. PLL 重配置和动态相移 (91)内容发送反馈Intel ® Arria ® 10内核架构和通用I/O 手册3内容4.3. 文档修订历史 (91)5. Arria 10 器件的I/O和高速I/O (94)5.1. Arria 10 器件中的I/O和差分I/O缓冲 (95)5.2. Arria 10器件中的I/O标准和电平 (96)5.2.1. Arria 10 器件的FPGA I/O所支持的I/O标准 (96)5.2.2. Arria 10 器件的HPS I/O所支持的I/O标准 (97)5.2.3. Arria 10 器件中的I/O标准电平 (98)5.2.4. Arria 10器件中的MultiVolt I/O接口 (99)5.3. Arria 10 器件的Intel FPGA I/O IP内核 (99)5.4. Arria 10 器件的I/O资源 (99)5.4.1. Arria 10 器件的GPIO Bank、SERDES和DPA位置 (100)5.4.2. Arria 10 器件的GPIO缓冲和LVDS通道 (105)5.4.3. Arria 10 器件的I/0 Bank组 (108)5.4.4. Arria 10器件的I/O纵向移植 (114)5.5. Arria 10 器件的体系结构和I/O的一般功能 (115)5.5.1. Arria 10 器件中的I/O单元结构 (115)5.5.2. Arria 10 器件的I/O管脚特性 (117)5.5.3. Arria 10 器件的可编程IOE的特性 (118)5.5.4. Arria 10 器件的片上I/O匹配 (123)5.5.5. Arria 10 器件的外部I/O匹配 (132)5.6. Arria 10 器件的高速源同步SERDES和DPA (140)5.6.1. SERDES电路 (141)5.6.2. Arria 10 器件中支持的SERDES I/O标准 (142)5.6.3. Arria 10 器件的差分发送器 (144)5.6.4. Arria 10 器件中的差分接收器 (145)5.6.5. Arria 10 器件的PLL和时钟 (152)5.6.6. Arria 10 器件的时序和优化 (163)5.7. 在 Arria 10 器件中使用I/O和高速I/O (168)5.7.1. Arria 10 器件的I/O和高速I/O通用指南 (168)5.7.2. 混合电压参考和非电压参考I/O标准 (170)5.7.3. 指南:上电顺序期间不可驱动I/O管脚 (171)5.7.4. 指南:在HPS共享的I/O Bank中使用I/O管脚 (171)5.7.5. 指南:最大化DC电流限制 (172)5.7.6. 指南:Altera LVDS SERDES IP内核实例 (172)5.7.7. 指南:Soft-CDR模式的LVDS SERDES管脚对 (172)5.7.8. 指南:Arria 10 GPIO性能的最小化高抖动的影响 (173)5.7.9. 指南:外部存储器接口I/O Bank 2A的使用 (173)5.8. 文档修订历史 (174)6. Arria 10 器件的外部存储器接口 (178)6.1. Arria 10 外部存储器接口解决方案的关键特性 (178)6.2. Arria 10 器件支持的存储器标准 (178)6.3. Arria 10 器件的外部存储器接口宽度 (180)6.4. Arria 10 器件的外部存储器接口I/O管脚 (180)6.4.1. 指南:外部存储器接口I/O Bank 2A的使用 (181)6.5. Arria 10 器件封装支持的存储器接口 (182)6.5.1. 含有ECC的DDR3 x40在 Arria 10 中的封装支持 (183)Intel® Arria® 10内核架构和通用I/O手册发送反馈46.5.2. Single 和Dual-Rank 的DDR3 x72(含有ECC)在 Arria 10 中的封装支持 (185)6.5.3. 含有ECC 的DDR4 x40在 Arria 10 中的封装支持 (187)6.5.4. Single-Rank 含有ECC 的DDR4 x72在 Arria 10 中封装支持 (189)6.5.5. Dual-Rank 含有ECC 的DDR4 x72在 Arria 10 中的封装支持 (191)6.5.6. Arria 10的HPS 外部存储器接口连接 (192)6.6. Arria 10 器件支持的外部存储器接口IP (196)6.6.1. Ping Pong PHY IP (197)6.7. Arria 10 器件的外部存储器接口体系结构 (197)6.7.1. I/O Bank (198)6.7.2. I/O AUX (206)6.8. 文档修订历史 (208)7. Arria 10器件中的配置、 设计安全和远程系统更新 (210)7.1. 增强配置和通过协议配置(Configuration via Protocol) (210)7.2. 配置方案 (211)7.2.1. 主动串行配置 (211)7.2.2. 被动串行配置 (220)7.2.3. 快速被动并行配置 (224)7.2.4. JTAG 配置 (228)7.3. 配置详细信息 (231)7.3.1. MSEL 管脚设置 (231)7.3.2. CLKUSR (232)7.3.3. 配置序列 (233)7.3.4. 配置时序波形 (236)7.3.5. 估算配置时间 (239)7.3.6. 器件配置管脚 (240)7.3.7. 配置数据压缩 (242)7.4. 使用主动串行方案升级远程系统 (243)7.4.1. 配置映像 (244)7.4.2. 远程更新模式中的配置序列 (245)7.4.3. 远程系统更新电路 (247)7.4.4. 使能远程系统更新电路 (247)7.4.5. 远程系统更新寄存器 (247)7.4.6. 远程系统更新状态机 (249)7.4.7. 用户看门狗定时器(User Watchdog Timer ) (249)7.5. 设计安全 (250)7.5.1. 安全密钥类型 (251)7.5.2. 安全模式 (251)7.5.3. Arria 10 Qcrypt 安全工具 (253)7.5.4. 设计安全实现步骤 (253)7.6. 文档修订历史 (254)8. Arria 10器件的SEU 缓解 (256)8.1. SEU 缓解概述 (256)8.1.1. SEU 缓解应用 (256)8.1.2. 配置RAM (256)8.1.3. 嵌入式存储器 (257)8.2. Arria 10缓解技术 (257)内容发送反馈Intel ® Arria ® 10内核架构和通用I/O 手册5内容8.2.1. 存储器模块纠错码支持 (257)8.2.2. CRAM的错误检测和纠正 (258)8.3. 规范 (265)8.3.1. 错误检测频率 (265)8.3.2. 错误检测时间 (266)8.3.3. EMR更新间隔 (266)8.3.4. 纠错时间 (268)8.4. 文档修订历史 (268)9. Arria 10器件中的JTAG边界扫描测试 (270)9.1. BST操作控制 (270)9.1.1. IDCODE (270)9.1.2. 所支持的JTAG指令 (271)9.1.3. JTAG安全模式 (272)9.1.4. JTAG专用指令 (273)9.2. JTAG操作的I/O电压 (273)9.3. 执行BST (273)9.4. 使能和禁用IEEE Std. 1149.1 BST电路 (274)9.5. IEEE Std. 1149.1边界扫描测试指南 (275)9.6. IEEE Std. 1149.1边界扫描寄存器 (275)9.6.1. Arria 10器件I/O管脚的边界扫描单元 (276)9.6.2. IEEE Std. 1149.6边界扫描寄存器 (278)9.7. 文档修订历史 (279)10. Arria 10器件中的电源管理 (280)10.1. 功耗 (280)10.1.1. 动态功耗公式 (280)10.2. 功耗降低技术 (281)10.2.1. SmartVID (281)10.2.2. 可编程电源技术 (281)10.2.3. 低静态功耗器件等级 (282)10.2.4. SmartVID功能实现 (282)10.3. 电源感应线(Power Sense Line) (284)10.4. 电压传感器 (284)10.4.1. 外部模拟信号的输入信号范围 (286)10.4.2. 在Arria 10器件中使用电压传感器 (286)10.5. 温度感应二极管 (290)10.5.1. 内部温度感应二极管 (290)10.5.2. 外部温度感应二极管 (291)10.6. 上电复位电路 (292)10.6.1. POR电路监控和未监控电源 (294)10.7. 上电和断电序列 (294)10.8. 电源设计 (297)10.9. 文档修订历史 (298)Intel® Arria® 10内核架构和通用I/O手册发送反馈61. Arria ® 10器件中的逻辑阵列模块与自适应逻辑模块逻辑阵列模块(LAB )由称作自适应逻辑模块(ALM )的基本构造模块组成,通过配置这些模块,能够实现逻辑功能、算术功能以及寄存器功能。

手机维修资料

WT-WT-E003 手机分析维修手册手机分析维修手册拟日制期示例机型页数WT-WT-E003 目录一 DL 工位: 1.DL 没反应--------------------------3 2. DL 下载变红-----------------------7 二三 SN 工位------------------------------------8 CFT 工位: 1.AFC 不良------------------------------9 2.EGSM APC 不良------------------------11 3.EGSM AGC 不良------------------------11 4.CALL 不良----------------------------11 5.EGSM TXP 不良------------------------11 6.EGSM B E R不良------------------------11四C I T工位: 1.不开机-----------------------------11 2. 显示不良---------------------------11 3. 触摸屏无效-------------------------12 4. 开机声音不良 ----------------------13 5. 不识S I M卡-------------------------146.不识T卡---------------------------14 7. 键盘灯不亮-------------------------15 W T-W T-E0038.按键无效--------------------------169.无振动--------------------------16 10. 无回音---------------------------17 11. 耳机不良-------------------------18 12. 摄像不良-------------------------19 13. 蓝牙不良-------------------------20 14. FM 调频收音机不良-----------------22 15. 七彩灯不良-----------------------23 16. 充电不良-------------------------25 17. 不能识别 USB---------------------26 18. 附录----------------------------27 工位:一 DL 工位:没反应: 1.DL 没反应:没电流: 1.1 DL 没电流:、现所用多为 USB 下载,故应先从电池连接器供电,按 POWER 键看开机电流是否正常,若开机电流正常一般为20~30MA 则说明是 USB 接口 J501 有问题 US,SS 或 CD ; WT-WT-E003 若从电池连接器供电开机电流仍为零,则应先检查 VBAT 是否经过 L201 供给电源管理芯片,再检查电源部分是否正常工作,加焊或更换电源管理芯片展讯平台都为 PMIC 和 CPU 集成,故要加焊或更换 BBIC U101 。

Polaroid L104 L106数码相机 说明书

关于本手册

本手册介绍如何使用您的数码相机。 plawa-feinwerktechnik GmbH & Co. KG已尽最大努力 确保本手册内容的准确性,但保留变更的权利,恕不另 行通知。

本手册中使用的符号 在本手册中,使用下列符号来帮助您方便快捷地找到所 需的信息。

表示应了解的有用信息。

表示在使用相机时应采取的预防措施。

ii

前言

感谢您购买本数码相机。请仔细阅读本手册,并妥善保 管以备日后参考。

版权 版權所有,此產品之授權生產,分銷及銷售為 plawa-feinwerktechnik GmbH & Co. KG, Bleichereistrasse 18, 73066 Uhingen, Germany。 未经plawa-feinwerktechnik GmbH & Co. KG事先书面 许可,不得以任何形式和任何方式复制、传播、转录本 发行物的任何部分,也不得将其存储到检索系统中或者 翻译成任何语言或计算机语言。

前言.................................................................................... 1 版权............................................................................ 1 商标............................................................................ 1

尺寸..........................................................................21 影像品质.................................................................21 白平衡......................................................................22 色彩效果.................................................................22 ISO...........................................................................23 EV.............................................................................23

MOTOROLA MCR106 Series 数据手册

Silicon Controlled RectifiersReverse Blocking Triode ThyristorsPNPN devices designed for high volume consumer applications such as temperature, light and speed control; process and remote control, and warning systems where reliability of operation is important.•Glass-Passivated Surface for Reliability and Uniformity •Power Rated at Economical Prices•Practical Level Triggering and Holding Characteristics•Flat, Rugged, Thermopad Construction for Low Thermal Resistance, High Heat Dissipation and DurabilityMAXIMUM RATINGS (T = 25°C unless otherwise noted.)1.V DRM and V RRM for all types can be applied on a continuous basis. Ratings apply for zero or negative gate voltage;(cont.)however, positive gate voltage shall not be applied concurrent with negative potential on the anode. Blocking voltages shall not be tested with a constant current source such that the voltage ratings of the devices are exceeded.Order this documentby MCR106/DMOTOROLA SEMICONDUCTOR TECHNICAL DATA查询MCR106供应商MCR106 SeriesMAXIMUM RATINGS — continuedRating Symbol Value Unit Storage Temperature Range T stg–40 to +150°C Mounting T orque(1)—6in. lb. THERMAL CHARACTERISTICSCharacteristic Symbol Max Unit Thermal Resistance, Junction to Case RθJC3°C/W Thermal Resistance, Junction to Ambient RθJA75°C/W ELECTRICAL CHARACTERISTICS (T C = 25°C and R GK = 1000 Ohms unless otherwise noted.)Characteristic Symbol Min Typ Max UnitPeak Forward or Reverse Blocking Current(V AK = Rated V DRM or V RRM)T J = 25°CT J = 110°C I DRM, I RRM————10200µAµAForward “On” Voltage(I TM = 4 A Peak)V TM——2VoltsGate Trigger Current (Continuous dc)(2)(V AK = 7 Vdc, R L = 100 Ohms)(V AK = 7 Vdc, R L = 100 Ohms, T C = –40°C)I GT————200500µAGate Trigger Voltage (Continuous dc)(V AK = 7 Vdc, R L = 100 Ohms, T C = 25°C)V GT——1VoltsGate Non-Trigger Voltage(V AK = Rated V DRM, R L = 100 Ohms, T J = 110°C)V GD0.2——VoltsHolding Current(V AK = 7 Vdc, T C = 25°C)I H——5mAForward Voltage Application Rate(T J = 110°C)dv/dt—10—V/µs1.Torque rating applies with use of compression washer (B52200-F006 or equivalent). Mounting torque in excess of 6 in. lb. does notappreciably lower case-to-sink thermal resistance. Anode lead and heatsink contact pad are common. (See AN209B).For soldering purposes (either terminal connection or device mounting), soldering temperatures shall not exceed +200°C. For optimum results, an activated flux (oxide removing) is recommended.2.R GK current is not included in measurement.MCR106 SeriesI T(AV), AVERAGE FORWARD CURRENT (AMP)5070901100.10.20.30.40.50.60.70.8α00.40.81.2 1.62.0 2.4 2.83.23.64.08230πf = 60 Hzdcα = 30°60°90°180°f = 60 Hzα11010610298949086I T(AV), AVERAGE FORWARD CURRENT (AMP)90°60°α = 30°T , M A X I M U M A L L O W A B L E A M B I E N T A °T E M P E R A T U R E ( C )dc180°120°πT , M A X I M U M A L L O W A B L E C A S E T E M P E R A T U R E ( C )°C FIGURE 1 – MAXIMUM CASE TEMPERATUREFIGURE 2 – MAXIMUM AMBIENT TEMPERATURECURRENT DERATING。

药厂房间名称中英文