LC72131.M中文版.pdf

国际电子股份有限公司IC-3121工业控制器技术参数手册说明书

DEVICE SPECIFICATIONSIC-3121Industrial ControllerThis document provides the specifications for the IC-3121. Specifications are subject to change without notice. Refer to the National Instruments Product Manuals Library at / manuals for the most recent versions of product documentation.Characteristics/Nominal Specifications describe basic functions and attributes of the device established by design.Physical CharacteristicsCaution You can impair the protection provided by the IC-3121 if you use it in amanner not described in this document.To clean the IC-3121, wipe it with a dry towel.Dimensions10.8 cm × 6.1 cm × 13.0 cm (4.3 in × 2.4 in ×5.1 in)Weight911 g (2.01 lb)ProcessorType Quad Core Intel Atom Processor E3845 Frequency 1.91 GHzOn-die L2 cache 2 MBOperating SystemSupported Operating Systems NI Linux Real-Time 64-bitWindows Embedded Standard 7 64-bitMemorySystem RAMCapacity 4 GBType DDR3LSpeed1333 MT/sNonvolatile storageCapacity 2 GBPower RequirementsNote Supply voltages are measured at the IC-3121 power connectors.System Power (V)Supply voltage10.8 to 26.4 VDCMaximum power input24 WIsolated Output Power (V ISO)Supply voltage 4.5 to 30 VDCReconfigurable FPGAType Spartan-6 LX25Number of flip-flops30,064Number of 6-input LUTs15,03238Number of DSP48E1 slices(18 × 25 multipliers)Embedded block RAM52 (936 Kbits)Number of DMA channels32Number of logical interrupts322| | IC-3121 SpecificationsNetwork PortStandard IEEE 802.3 Ethernet, 10BASE-T, 100BASE-TX, 1000BASE-TInterface RJ45Speed10, 100, 1000 MbpsUSB 3.0 PortsNumber of ports2Type USB 3.0, SuperSpeedSpeed 5 Gbit/sMaximum current900 mA, per portUSB 2.0 PortsNumber of ports2Type USB 2.0, Hi-SpeedSpeed480 Mbit/sMaximum current 1 A, shared across both portsVGA PortMaximum resolution1920 × 1200 at 60 HzTTL Inputs/OutputsNumber of channels8Type BidirectionalOutput voltage range0 V to 5 VMaximum pulse rate 2 MHzMinimum pulse detected500 nsPower-on state Input (high-impedance), 10 kΩ pull-up to 5 VIC-3121 Specifications| © National Instruments| 3Logic levelsInput low voltage0.59 V maximumInput high voltage 2.57 V minimumOutput low voltage0.38 V maximum at 1.5 mAOutput high voltage 4.12 V minimum at 1.5 mADifferential Inputs/OutputsNumber of channels2Types Bidirectional RS-422/RS-485 or single-endedinputMaximum pulse rate 5 MHz, differentialDifferential input threshold±200 mVDifferential output voltage 2.0 V min (R LOAD = 100 Ω, RS-422)Input voltage range0 V to 5.5 VTTL-compatible single-ended logic levelsInput low voltage0.8 VInput high voltage 2.0 VIsolated InputsType Current sinkingNumber of channels8Input voltageInput voltage range0 V to 24 VInput OFF voltage0 V to 2.0 VInput ON voltage 3.3 V to 24 VTurn-on current 2.5 mAMaximum pulse rate100 kHzMinimum pulse detected10 µsInput protectionReverse polarity protection Yes, -30 VInput voltage (channel to C ISO)30 V maximumInput current 3.3 mA, internally limited4| | IC-3121 SpecificationsIsolated OutputsType Current sourcingNumber of channels8Supply voltage (V ISO)Supply voltage range (V ISO) 4.5 to 30 VDCReverse polarity protection Yes, -30 VMaximum output voltage dropV ISO = 5 V 1.08 V at 35 mAV ISO = 24 V 1.18 V at 80 mAMaximum output currentV ISO = 5 V35 mAV ISO = 24 V80 mAMaximum current limit345 mAMinimum pulse rate 2.5 kHz (load of 100 kΩ, 300 pF)Maximum pulse rate20 kHz (load of 10 kΩ, 300 pF)Minimum pulse generated400 µsNote The isolated outputs have a current limit which will turn off the outputs incase the limit is exceeded. The circuit resets when the output is turned off. Do notdraw more than 100 mA from any 24 V isolated output. Do not draw more than50 mA from any 5 V isolated output. Do not draw more than 640 mA combinedfrom the V ISO pins on the 44-pin D-SUB connector.EnvironmentalIndoor use only.Ingress protection (IEC 60529)IP40Temperature (IEC 60068-2-1 and IEC 60068-2-2)Operating0 °C to 55 °CStorage-20 °C to 85 °COperating humidity (IEC 60068-2-56)10% RH to 90% RH, noncondensing Storage humidity (IEC 60068-2-56)5% RH to 95% RH, noncondensing Pollution degree (IEC 60664)2IC-3121 Specifications| © National Instruments| 5Maximum Altitude2,000 mOperating shock (IEC 60068-2-27)50 g, 3 ms half sine, 3 shocks per side 30 g, 11ms half sine, 3 shocks per sideOperating vibrationRandom (IEC 60068-2-64)10 to 500 Hz, 5 g rmsSwept Sine (IEC 60068-2-6)10 to 500 Hz, 5 gSafetyThis product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control, and laboratory use:•IEC 61010-1, EN 61010-1•UL 61010-1, CSA C22.2 No. 61010-1Note For UL and other safety certifications, refer to the product label or the OnlineProduct Certification section.Electromagnetic CompatibilityThis product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:•EN 61326-1 (IEC 61326-1): Class A emissions; Industrial immunity•EN 55011 (CISPR 11): Group 1, Class A emissions•AS/NZS CISPR 11: Group 1, Class A emissions•FCC 47 CFR Part 15B: Class A emissions•ICES-001: Class A emissionsNote In the United States (per FCC 47 CFR), Class A equipment is intended foruse in commercial, light-industrial, and heavy-industrial locations. In Europe,Canada, Australia and New Zealand (per CISPR 11) Class A equipment is intendedfor use only in heavy-industrial locations.Note Group 1 equipment (per CISPR 11) is any industrial, scientific, or medicalequipment that does not intentionally generate radio frequency energy for thetreatment of material or inspection/analysis purposes.Note For EMC declarations and certifications, and additional information, refer tothe Online Product Certification section.6| | IC-3121 SpecificationsCE ComplianceThis product meets the essential requirements of applicable European Directives, as follows:•2014/35/EU; Low-V oltage Directive (safety)•2014/30/EU; Electromagnetic Compatibility Directive (EMC)Online Product CertificationRefer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for this product, visit / certification, search by model number or product line, and click the appropriate link in the Certification column.Environmental ManagementNI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.For additional environmental information, refer to the Minimize Our Environmental Impact web page at /environment. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.Waste Electrical and Electronic Equipment (WEEE)EU Customers At the end of the product life cycle, all NI products must bedisposed of according to local laws and regulations. For more information abouthow to recycle NI products in your region, visit /environment/weee.Battery Replacement and DisposalBattery Directive This device contains a long-life coin cell battery. If you need toreplace it, use the Return Material Authorization (RMA) process or contact anauthorized National Instruments service representative. For more information aboutcompliance with the EU Battery Directive 2006/66/EC about Batteries andAccumulators and Waste Batteries and Accumulators, visit /environment/batterydirective.IC-3121 Specifications| © National Instruments| 7电子信息产品污染控制管理办法(中国RoHS)中国客户National Instruments符合中国电子信息产品中限制使用某些有害物质指令(RoHS)。

Eaton P721 产品数据手册说明书

Eaton P721Eaton Moeller series Weatherproof range (PREMERA PROOF) - Wiring Devices. Switch, 16A, 1G, 2W, neon, IP66General specificationsEaton Moeller series Weatherproof range (PREMERA PROOF) - Wiring Devices P721P721501082613268263 mm103 mm 82 mm0.212 kg RoHS conformIEC 60669-1Product Name Catalog NumberModel CodeEAN Product Length/DepthProduct Height Product WidthProduct Weight CompliancesCertificationsNot included16 Ampere AC/DCTwo-way switch21 mmBasic element with full cover plateMattFlush mounted (plaster)16 ADuroplast0 mmThermoplasticRocker/button1.5 mm² (4x) or2.5 mm² (3x) or 4 mm² (1x) or 6 mm² (1x) Screw terminalNoGray250 V AC eaton-us-power-defense-flyer-br013004en-en-us.pdf eaton-circuit-breakers-bzm-catalog-w1230-7594-gb-int.pdf eaton-xchargein-installation-manual-v1.01-en-us.pdfLighting typeSwitching current of fluorescent lamps Wiring systemFront plate depthAssembly arrangementSurface finishingMounting methodAmperage RatingMaterial qualityBuilt-in installation box depth - min Front plate materialMethod of operationTerminal capacity (LN and E) Connection typeIlluminationRocker colorVoltage ratingHead style BrochuresCatalogsInstallation instructionsCombination headDegree of protectionIP66Special featuresZinc Coated Steel with clear PassivationSwitch type2 wayFront plate/module dimensions82 mm x 102.5 mm x 62.5 mmNominal voltage - max240 VColorWhiteBuilt-in depth25 mmFeaturesPush button switchHalogen freeMaterialThermoplasticPlasticFront plate color/finishingGrayFunction lightingIlluminated (on)Base colorGrayNumber of gangs1Contact materialNickelSilverNumber of modules (module system)TypeOther Accessories Premera ProofFastening typeScrew mountingEaton Corporation plcEaton House30 Pembroke RoadDublin 4, Ireland © 2023 Eaton. All Rights Reserved. Eaton is a registered trademark.All other trademarks areproperty of their respectiveowners./socialmedia 0UntreatedThermoplasticNo1BrassRAL-number (Akin)Surface protectionBase materialLabel space/information surfaceNumber of rockersTerminal material。

BL0972 交 直流电能计量芯片 数据手册 V1.0说明书

BL0972交/直流电能计量芯片数据手册V1.0目录1、产品简述 (5)2、基本特征 (6)2.1主要特点 (6)2.2系统框图 (7)2.3管脚排列(TSSOP20) (7)2.4性能指标 (8)2.4.1电参数性能指标 (8)2.4.2极限范围 (9)3、工作原理 (10)3.1电流电压波形产生原理 (10)3.1.1PGA增益调整 (10)3.1.2相位补偿 (11)3.1.3通道偏置校正 (11)3.1.4通道增益校正 (12)3.1.5电流电压波形输出 (12)3.2有功功率计算原理 (13)3.2.1有功波形的选择 (14)3.2.2有功功率输出 (14)3.2.3有功功率校准 (14)3.2.4有功功率的防潜动 (15)3.2.5有功功率小信号补偿 (15)3.3有功能量计量原理 (16)3.3.1有功能量输出 (16)3.3.2有功能量输出选择 (16)3.3.3有功能量输出比例 (17)3.4电流电压有效值计算原理 (17)3.4.1有效值输出 (18)3.4.2有效值输入信号的设置 (18)3.4.3有效值刷新率的设置 (18)3.4.4电流电压有效值校准 (19)3.4.5有效值的防潜动 (19)3.5快速有效值检测原理 (20)3.5.1快速有效值输出 (20)3.5.2快速有效值输入选择 (21)3.5.3快速有效值累计时间和阈值 (21)3.5.4电网频率选择 (21)3.5.5快速有效值超限数据保存 (22)3.5.6过流指示 (22)3.5.7继电器控制 (22)3.6温度计量 (23)3.7.1线周期计量 (23)3.7.2线频率计量 (23)3.7.3相角计算 (24)3.7.4功率符号位 (24)3.8故障检测 (25)3.8.1过零检测 (25)3.8.2峰值超限 (25)3.8.3线电压跌落 (26)3.8.4过零超时 (27)3.8.5电源供电指示 (28)4、内部寄存器 (30)4.1电参量寄存器(只读) (30)4.2校表寄存器(外部写) (30)4.3OTP寄存器 (32)4.4模式寄存器 (33)4.4.1 MODE1寄存器 (33)4.4.2 MODE2寄存器 (33)4.4.3 MODE3寄存器 (34)4.5中断状态寄存器 (34)4.5.1 STATUS1寄存器 (34)4.5.2 STATUS3寄存器 (34)4.6校表寄存器详细说明 (34)4.6.1 通道PGA增益调整寄存器 (34)4.6.2 相位校正寄存器 (35)4.6.3 有效值增益调整寄存器 (35)4.6.4 有效值偏置校正寄存器 (36)4.6.5 有功小信号补偿寄存器 (36)4.6.7 防潜动阈值寄存器 (36)4.6.8 快速有效值相关设置寄存器 (37)4.6.9 过流报警及控制 (38)4.6.11 能量读后清零设置寄存器 (39)4.6.12 用户写保护设置寄存器 (39)4.6.13 软复位寄存器 (39)4.6.14 通道增益调整寄存器 (40)4.6.15 通道偏置调整寄存器 (40)4.6.16 有功功率增益调整寄存器 (40)4.6.17 有功功率偏置调整寄存器 (41)4.6.20 CF缩放比例寄存器 (41)4.7电参数寄存器详细说明 (42)4.7.1 波形寄存器 (42)4.7.2 有效值寄存器 (42)4.7.3 快速有效值寄存器 (42)4.7.7 电能脉冲计数寄存器 (43)4.7.8 波形夹角寄存器 (44)4.7.9 快速有效值保持寄存器 (44)4.7.11 线电压频率寄存器 (44)5、SPI通讯接口 (45)5.1概述 (45)5.2工作模式 (45)5.3帧结构 (45)5.4读出操作时序 (46)5.5写入操作时序 (47)5.6SPI接口的容错机制 (48)6、典型应用图 (49)7、封装信息 (50)1、产品简述BL0972是一颗内置时钟的单相交/直流电能计量芯片。

CGS3312M中文资料

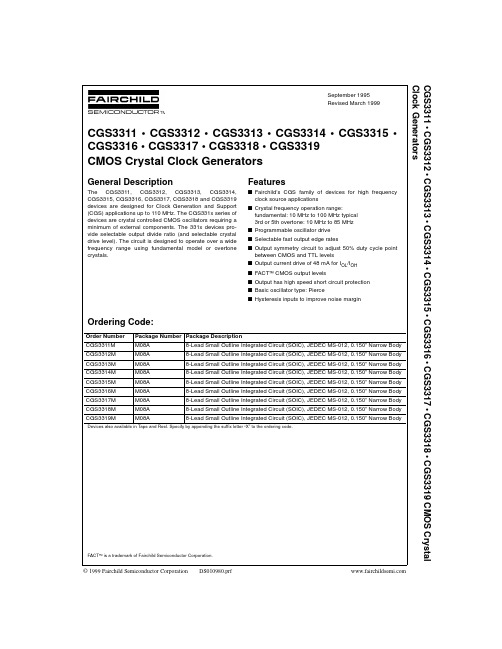

September 1995Revised March 1999CGS3311 • CGS3312 • CGS3313 • CGS3314 • CGS3315 • CGS3316 • CGS3317 • CGS3318 • CGS3319 CMOS Crystal Clock Generators© 1999 Fairchild Semiconductor Corporation DS010980.prf CGS3311 • CGS3312 • CGS3313 • CGS3314 • CGS3315 •CGS3316 • CGS3317 • CGS3318 • CGS3319CMOS Crystal Clock GeneratorsGeneral DescriptionThe CGS3311, CGS3312, CGS3313, CGS3314,CGS3315, CGS3316, CGS3317, CGS3318 and CGS3319devices are designed for Clock Generation and Support (CGS) applications up to 110 MHz. The CGS331x series of devices are crystal controlled CMOS oscillators requiring a minimum of external components. The 331x devices pro-vide selectable output divide ratio (and selectable crystal drive level). The circuit is designed to operate over a wide frequency range using fundamental model or overtone crystals.Featuress Fairchild’s CGS family of devices for high frequency clock source applications s Crystal frequency operation range:fundamental: 10 MHz to 100 MHz typical 3rd or 5th overtone: 10 MHz to 85 MHz s Programmable oscillator drive s Selectable fast output edge ratess Output symmetry circuit to adjust 50% duty cycle point between CMOS and TTL levels s Output current drive of 48 mA for I OL /I OH s FACT ™ CMOS output levelss Output has high speed short circuit protection s Basic oscillator type: Pierces Hysteresis inputs to improve noise marginOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.FACT ™ is a trademark of Fairchild Semiconductor Corporation.Order Number Package Number Package Description CGS3311M M08A 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body CGS3312M M08A 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body CGS3313M M08A 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body CGS3314M M08A 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body CGS3315M M08A 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body CGS3316M M08A 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body CGS3317M M08A 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body CGS3318M M08A 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body CGS3319MM08A8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body 2C G S 3311 • C G S 3312 • C G S 3313 • C G S 3314 • C G S 3315 • C G S 3316 • C G S 3317 • C G S 3318 • C G S 3319Connection Diagrams(A) 3311(B)3312(C) 3313(D) 3314(E) 3315(F) 3316(G) 3317(H) 3318(I) 3319CGS3311 • CGS3312 • CGS3313 • CGS3314 • CGS3315 • CGS3316 • CGS3317 • CGS3318 • CGS3319 Truth Tables Division Selection Note: Actual value of the floating OSC_DR and DIVB input is V CC/2Rise and Fall Time Selection Drive Selection Note: Where “F” indicates floating the input.Pin Descriptions Functional Table Summary of Device Options Each drive has one output with the choices of selecting frequency divide,output enable, crystal drive and output rise and fall time. Crystal drive options are:L = LOW Drive M = MEDIUM Drive H = HIGH Drive DIVB DIVA OEL OEH Divider Output F0/F X X Divide-by 110/F01Divide-by 200/F01Divide-by 4F101Divide-by 81101Divide-by 160101Divide-by 32X X1X Output Reset HIGH at Re-enable X X X0Output Reset HIGH at Re-enable OSC_DR DIV TRF Rise/Fall Time (ns)F N0/F2F N1less than 2F Y0/F4F Y120,1X0/F40,1X12OSC_DR Drive0Low1Medium F High Note: Pin out varies for each device.OSC_IN Input to Oscillator Inverter. The output of the crystal would be connected here.OEL Active LOW 3-STATE enable pin. This pin pulls to a low value when left floating and 3-STATE the output when forced HIGH. This pin has TTL compatible input levels.OSC_OUT Resistive Buffered Output of the Oscillator Inverter TRF Rise and Fall time override pin. Available only for die form.OSC_DR 3 Level input pin that selects Oscillator Drive Level OUT This pin is the main clock output on the device.DIVA Input used to select Binary Divide-by Option. This pin has CMOS compatible input levels.OSCLO_1The Oscillator LOW pin is the ground for the Oscillator.OEH Active HIGH 3-STATE enable pin. This pin pulls to a high value when left floating and 3-STATEs the output when forced low. This pin has TTL compatible input levels.OSCLO_2This pin is the same signal as OSCLO_1. It has been provided as an alternate connection for OSCLO_1 for hybrid assemblies.V CC The power pin for the chip.GND The ground pin for all sections of the circuitry except the oscillator and oscillator related circuitry.Device Divide Enable Drive Output Rise/ Fall Time (ns)33111, 2, 4OEH L, M, H2, 433121, 2, 4OEH H2, 433138, 16, 32OEH H433148, 16, 32OEH L, M, H433151, 2, 4OEL H1, 233164OEH H4331732OEH H433181, 2, 4OEH H1, 233191, 2, 4OEL L, M, H2, 4 4C G S 3311 • C G S 3312 • C G S 3313 • C G S 3314 • C G S 3315 • C G S 3316 • C G S 3317 • C G S 3318 • C G S 3319Block DiagramsNote: Pin numbers vary for each deviceOscillator StageOutput StageCGS3311 • CGS3312 • CGS3313 • CGS3314 • CGS3315 • CGS3316 • CGS3317 • CGS3318 • CGS3319 Absolute Maximum Ratings(Note 1)Recommended Operating Conditions Note 1: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the DC and AC Electrical Characteristics tables are not guaranteed at the absolute maxi-mum ratings. The Recommended Operating Conditions will define the con-ditions for actual device operation.DC Electrical Characteristics Supply Voltage (V CC)−0.5V to 7.0V DC Input Voltage Diode Current (I IK)±9 mA DC Input Voltage (V I)−0.5V to 7.0V DC Output Diode Current (I OK)±20 mA DC Output Voltage (V O)-0.5V to V CC+ 0.5V DC Output Source or Sink Current (I O)±70 mA Storage Temperature (T STG)−55°C to 150°C Junction Temperature (T J)SOIC140°C/W Supply Voltage (V CC) 4.5V to 5.5V Input Voltage (V I)0V to5.5V Output Voltage (V O)0V to V CC V Operating Temperature (T A)−40° to +85°C Symbol Parameter T A=+25°C T A=−40° C to +85°C Units Conditions V CC Typ Guaranteed Limits(V)Min Max Min Max V IHTTL Minimum HIGH Level Input Voltage, TTL Level Inputs (OEH, OEL) 4.5 2.0 2.0V5.5 2.0 2.0V ILTTL Maximum LOW Level Input Voltage, TTL Level Inputs (OEH, OEL) 4.50.80.8V5.50.80.8V IHCMOS Minimum HIGH Level Input Voltage. CMOS Level Inputs (DIVA) 4.5 3.15 3.15V5.5 3.85 3.85V ILCMOS Maximum LOW Level Input voltage. CMOS Level Inputs (DIVA) 4.5 1.35 1.35V5.5 1.65 1.65V IN3L_H Minimum Logic 1 Input for Three Level Input(DIVB, OSC_DR) 4.5 4.05 4.05V5.5 4.95 4.95V IN3L_1/2Minimum Logic 1/2 Input for Three Level Input(DIVB, OSC_DR) 4.5 1.8 2.7 1.8 2.7V5.5 2.2 3.3 2.2 3.3V IN3L_L Maximum Logic 0 Input Level Three Level Input(DIVB, OSC_DR) 4.50.450.45V5.50.450.45V OH Minimum HIGH Level Output Voltage 4.5 4.49 4.40 4.40V I OUT=−50µA5.5 5.49 5.40 5.404.5 3.86 3.76I OH=−48 mA5.5 4.86 4.76V IN= V IH or V IH V OL Minimum LOW Level Output Voltage 4.50.0010.10.1V I OUT= 50µA5.50.0010.10.14.50.440.44I OL=+48mA5.50.440.44V IN= V IL or V IH I IHRES Input Current for Pins DIVB, OSC_DR, and DIVA (Input is Logic HIGH) 5.5220360200380µA V IN= 5.5V I ILRES Input Current for Pins DIVB, OSC_DR, and DIVA (Input is Logic LOW) 5.5−220−360−200−380µA VIN = 0.0V I IHENAB Input Current for Enable Pin OEL 5.59016085175µA V IN= 5.5V I ILENAB Input Current for5.5−90−160−85−175µA V IN= 0.0VEnable Pin OEH5.52010020125µA V IN = 5.5VI IHOSC Input Current for OSC_IN Pin(Indicates Bias Resistance)I ILOSC Input Current for OSC_IN Pin5.5−20−100−20−125µA V IN= 0.0V(Indicates Bias Resistance)I OZH Output Disabled Current 4.5 3.0 5.0µA V OUT= V CC(Output HIGH) 5.5 3.0 5.0 6C G S 3311 • C G S 3312 • C G S 3313 • C G S 3314 • C G S 3315 • C G S 3316 • C G S 3317 • C G S 3318 • C G S 3319DC Electrical Characteristics (Continued)AC Electrical CharacteristicsOver recommended operating free air temperature range. All typical values are measured at V CC = 5V, T A = 25°C.Note 2: Voltage Range 5.0 is 5.0V ± 0.5VSymbol ParameterT A = +25°CT A = −40° C to +85°CUnits Conditions V CCTypGuaranteed Limits (V)MinMax MinMax I OZL Output Disabled Current 4.5−140−150µAV OUT = 0.0V(Output LOW) 5.5−170−180I OLD Minimum Dynamic Output Current 5.57575mA V OLD = 1.65v I OHD Minimum Dynamic Output Current5.5−75−75mA V OHD = 3.85V I CCOSC_L Additional I CC with OSC_IN 4.50.60.6mAOSC_IN = FloatFloating. LOW Drive Mode 5.5 6.56.5I CCOSC_M Additional I CC with OSC_IN 4.5 1.71.7mAOSC_IN = FloatFloating. LOW Drive Mode 5.512.412.4I CCOSC_H Additional I CC with OSC_IN 4.5 5.55.5mAOSC_IN = FloatFloating. LOW Drive Mode 5.531.531.5I CCTAdditional Maximum I CC per Input(OEH, OEL Pins) 5.51.51.5mAV IN = V CC − 2.1VI CC3LAdditional Maximum I CC per Input(DIVB, OSC_DR Inputs)5.5 1.5 1.5mADIVB, OSC_DRInputs Equal to V CC/2Symbol ParameterV CC T A = −40°C to + 85°C Units (V)C L = 50 pF (Note 2)Min TypeMaxf MAX Frequency Maximum 5.0100ns t PZH Output HIGH Enable Time 5.0 1.031.5ns t PZL Output LOW Enable Time 5.0 1.028.0ns t PHZ Output HIGH Disable Time 5.0 1.021.5ns t PLZ Output LOW Disable Time 5.0 1.016.0ns t RISE Rise/Fall Time 5.04.0nst FALL30 pF (20% to 80%)Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.CGS3311 • CGS3312 • CGS3313 • CGS3314 • CGS3315 • CGS3316 • CGS3317 • CGS3318 • CGS3319 CMOS Crystal Clock GeneratorsLIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into thebody, or (b) support or sustain life, and (c) whose failureto perform when properly used in accordance withinstructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or Physical Dimensions inches (millimeters) unless otherwise noted8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow BodyPackage Number M08A。

Si721x 霍尔效应磁性位置传感器产品系列说明书

Si721x 场输出霍尔效应磁性位置传感器数据表Silicon Labs 提供的 Si7211/2/3/4/5/6/7 霍尔效应磁性传感器产品系列结合了斩波稳定型霍尔元件以及低噪声模拟放大器、13 位 AD 转换器。

模数转换后,磁场数据可以以模拟、脉冲宽度调制 (PWM)或单边缘渐进传输 (SENT)格式提供(视部件编号而定)。

借助 Silicon Labs 成熟的 CMOS 设计技术,Si721x 产品系列融入数字信号处理,为温度和失调漂移提供精密补偿。

与现有霍尔效应传感器相比,Si721x 产品系列具有行业领先的灵敏度和低噪声,使传感器能够在较大气隙和较小磁体条件下使用。

在最简单的情况下,Si721x 设备以 3 引脚 SOT23 或 TO92 形式封装,提供电源、接地和单输出引脚,该单输出引脚可用于输出对应模拟格式、PWM 或 SENT 格式的磁场信号。

Si721x 设备还提供 5 引脚 SOT23 和 8 引脚 DFN(即将推出)封装形式,除上述引脚外,其他引脚可以用于睡眠模式 (DIS) 或用于启动片上线圈内置自检 (BISTb) 功能。

应用特性:•高灵敏度霍尔效应传感器•与磁场相对应的低噪声输出•为温度和失调漂移提供补偿的集成数字信号处理•睡眠电流消耗低至 50 nA(典型值)•可配置灵敏度、输出极性和采样率•随温度变化,灵敏度漂移幅度 < ±3%•电源电压范围广•1.7 至 5.5 V•3.3 至 26.5 V•可配置输出选项•模拟•PWM•SENT•行业标准封装•表面安装式 SOT-23(3 引脚或 5 引脚)封装•TO92 封装•DFN 封装(即将推出)•消费、工业和汽车应用中的机械位置传感器•相机影像稳定、放大和自动聚焦•液位感应•控制旋钮和选择器开关DIS (Optional)VOUTVDD VDDTable of Contents1.Electrical Specifications (3)2.Functional Description (9)3.Analog Output (10)4.PWM Output Description (11)5.SENT Output (12)5.1 tSENT Status Nibble (12)5.2 SENT Data Nibbles (13)5.3 CRC Calculation (13)5.4 SENT Pause Pulse (13)5.5 SENT Frame Rate (13)5.6 BIST Activation During SENT Operation (13)6.Pin Description (14)7.Ordering Guide (16)8.Package Outline (18)8.1 SOT23 3-Pin Package (18)8.2 SOT23-5 5-Pin Package (20)8.3 TO92S 3-Pin Package (22)nd Patterns (23)9.1 SOT23 3-Pin PCB Land Pattern (23)9.2 SOT23-5 5-Pin PCB Land Pattern (24)10.Top Marking (25)10.1 SOT23 3-Pin Top Marking (25)10.2 SOT23-5 5-Pin Top Marking (26)10.3 TO92 Top Marking (26)11.Revision History (27)1.Electrical SpecificationsUnless otherwise specified, all min/max specifications apply over the recommended operating conditions.Table 1.1. Recommended Operating ConditionsTable 1.2. General Specification1Table 1.3. Output Pin SpecificationsTable 1.4. Magnetic SensorTable 1.5. Temperature CompensationTable 1.6. Thermal CharacteristicsTable 1.7. Absolute Maximum Ratings1Functional Description 2. Functional DescriptionThe Si7211/2/3/4/5/7 family of Hall Effect magnetic sensors digitize the component of the magnetic field in the z axis of the device (pos-itive field is defined as pointing into the device from the bottom). The digitized field is then converted to an output format of analog, PWM or SENT and presented on the output pin.Table 2.1. Part DescriptionRefer to the Magnetic Sensors Selector Guide for the two digit number after the die revision which gives more details about output, sampling frequency and other details.Data output is always unsigned. That is, half scale (V DD/2 for analog out parts, 50% duty cycle for PWM output parts and 2048 (0x800) for SENT output parts) corresponds to zero field.The parts are preconfigured for the magnetic field measurement range, idle time, temperature compensation and digital filtering and will wake into this mode when first powered. The specific configuration output type (open collector or push pull) are determined by the part number.Analog Output 3. Analog OutputFor the Si7211, the analog output is V DD/2 at zero field and goes from nearly zero at large negative field to nearly V DD at large positive field.B(mT)=(20.47or204.7)×(2×Vout Vdd−1)4- and 5-pin packages also have the option of a BISTb pin. When configured and detected low, the internal coil is turned on until the pin is detected high again. Each subsequent BISTb activation flips the polarity of the coil during BIST.For high voltage parts (Si7216), the output is ratiometric to an internally derived V DD of 5V (± 5%) so long as the input V DD is > 6 V.B(mT)=(20.47or204.7)×(2×Vout5−1)For V DD < 6 V the internally derived reference drops 1 V for each 1 V drop in V DD to the minimum recommended working voltage of 4.0 V.PWM Output Description 4. PWM Output DescriptionThe PWM output can be configured as open drain or push pull. High voltage parts can only be configured as open drain. The PWM duty cycle is factory configured and is normally set to in the range of 10 Hz to 1 KHz and is ±5%. See ordering guide for specific part num-bers..As each measurement completes, the next PWM cycle will be updated to reflect the last measurement result. The duty cycle varies from 0 to 100% where 50% duty cycle means zero field, 0 % duty cycle generally means maximum negative field (-20.47 mT or -204.7 mT) and 100% duty cycle generally means maximum positive field (+20.47 or +204.7 mT). The high portion of the PWM is output first so thatB(mT)=(20.47or204.7)×(2×Thigh−1)Thigh+TlowThe host processor should look for a variation in the magnetic field to determine the entire system is working properly.4- and 5-pin packages also have the option of a BISTb pin. When configured and detected low the internal coil is turned on until the pin is detected high again. Each subsequent BISTb activation flips the polarity of the coil during BIST.5. SENT OutputThe Si7213 and Si7215 output data in SENT (Single Edge Nibble transmission) format conforming to J2716 January 2010. All SENT output parts are configured as open collector.SENT protocol messages consist of:• A calibration/synchronization period consisting of 56 clock ticks• A status and serial communication 4-bit nibble• A sequence of up to six data nibbles• A one nibble checksum•Each nibble is 12 to 27 clock ticks•An optional delay pause pulseFigure 5.1. SENT Timing DiagramAs can be seen, each part of the sequence is determined by the timing between falling edges of the open drain sent output. First, a time of 56 clock ticks is produced so that the receiver can calibrate itself to the Si7213/5 speed. Then a total of 8 nibbles (4 bits per nibble) is produced. The edge to edge time of each nibble is 12 clock ticks for a data nibble of 0000b 13 ticks for a data value of 0001b and so on up to 27 ticks for a data value of 1111b.The nominal tick time has been standardized at 5 μsec (±5%) however this is configurable.5.1 tSENT Status NibbleIn the Si721x the four bit status nibble is defined as follows:•Bit 3 and Bit 2 always transmitted as zeroes (No serial message support)•Bit 1 and Bit 0•00 Normal; No error condition•01 Error condition•10 Positive field BIST active•11 Negative field BIST active5.2 SENT Data NibblesThe Si7213 and Si7215 are configurable to support a variety of options. The standard option follows J2716 A.3 where:For magnetic field, 3 nibbles are put together for a total 12 bit data word with values that can range from 0 to 4095. For magnetic field data, 2048 corresponds to zero field. The Si7213 can be configured for ± 20.47 mT full scale or ± 204.7 mT full scale. On the 20.47 mT full scale 1 LSB is 0.01 mT and on the 204.7 mT full scale 1 LSB is 0.1 mT.5.3 CRC CalculationThe CRC is calculated based on the 6 data nibble according to x4 +x3 + x2 + 1 with a seed value of 0101 as per the recommendations in J7216 section 5.4.2.2. The legacy CRC calculation is not supported.5.4 SENT Pause PulseThe Si7213 and Si7215 are configurable for a pause pulse that is 12 ticks low, 256 ticks wide. However, the standard offering is no pause pulse.5.5 SENT Frame RateFor the standard offering with no pause pulse, each message will be 154 to 270 ticks in length. At a tick time of 5 μsec this is 770 to 1350 μsec. This gives an average frame rate of approximately 1 msec for the standard tick time of 5 μsec. Conversion start is synchronized to the start of the synch pulse and is normally completed before the synch pulse completes so the data that is reported is the data obtained during the synch pulse time.5.6 BIST Activation During SENT OperationFor 3-pin packages BIST can be activated by holding the output pin low for the entire message.Once BIST is activated SENT messages resume 12 ticks after the SENT IO pin is detected high. Eight positive field BIST messages are followed by eight negative field BIST messages followed by a return to normal messages.The nominal magnetic field output of the on-chip generator varies with coil current. The coil current varies with the coil resistance and power supply voltage, so the nominal magnetic field output varies according to:Bout = BperVnom x VDDBperVnom is 1.6 mT/VThis can be used to calculate the expected magnetic field from the test coil for a given V DD. This is somewhat temperature dependent, so the actual measured field will vary according to the accuracy of the part as well as temperature. Generally, as the coil is turned on and off the measured variation in field should be within ±25% of expectation based on the calculated field generation.The host processor should look for a variation in the magnetic field output to determine the entire system is working properly.The 4- and 5-pin packages also have the option of a BISTb pin. When configured and detected low, the internal coil is turned on until the pin is detected high again. Each subsequent BISTb activation flips the polarity of the coil during BIST.6. Pin Description123TO-92, 3-PinFront ViewSOT-23, 5-PinTop ViewSOT-23, 3-Pin Top View Figure 6.1. Si721x Pin AssignmentsNote:The 3-pin option includes part numbers: Si7211/12/13/14/15/16.The SOT-23 5 pin option include part numbers: Si7217.Table 6.1. Si7211/12/13/14/15/16 (SOT23 3-pin Package)Table 6.2. Si7217 (SOT23 5-pin Package)Table 6.3. Si7211 (TO-92 Package)7. Ordering GuideSi721B F V Rxx Silicon Labs Magnetic Sensor Family Output TypeRevision Feature Set MinorTemperature GradePackageTape and Reel (Optional)See Selector Guide for breakdown of feature setV = SOT23, B = TO92, M = DFN8xFeature Set Major1, 6, 7 = Analog 2, 4 = PWM F = (0 to +70)I = (-40 to +125)3, 5 = SENTFigure 7.1. Si721x Part NumberingTable 7.1. Product Selection GuideAdditional InformationFor information on the below specifications of each OPN refer to the Magnetic Sensors Selector Guide:•Current consumption•Built in self test if applicableAll Si721x parts periodically measure the field and output the data in PWM, SENT, or analog format.The Si721x parts are factory configurable for:•The type of output analog, SENT, or PWM•The amount of digital filtering applied to the samples•The time between measurements•The output pin can be open drain or push pull (SENT and PWM parts)•Full scale can be programmed as 20mT or 200mT• A temperature compensation can be applied to the field data to adjust for the variation in field with temperature for common magnet typesNote: North pole of a magnet at the bottom of a SOT23 package, top of a DFN 8 package(coming soon), or front of a TO92 pack-age(coming soon) is defined as positive field.8. Package Outline 8.1 SOT23 3-Pin PackageTable 8.1. SOT23 3-Pin Package Dimensions8.2 SOT23-5 5-Pin PackageTable 8.2. SOT23-5 5-Pin Package Dimensions8.3 TO92S 3-Pin PackageTable 8.3. TO92S 3-Pin Package Dimensions9. Land Patterns9.1 SOT23 3-Pin PCB Land Pattern9.2 SOT23-5 5-Pin PCB Land Pattern10. Top Marking10.1 SOT23 3-Pin Top MarkingNote: TTTT is a manufacturing code.10.2 SOT23-5 5-Pin Top MarkingNote: TTTT is a manufacturing code.10.3 TO92 Top MarkingNote: TTTT is a manufacturing code. PPPP is 72xx.Revision History 11. Revision HistoryRevision 1.3May, 2020•Added EOL note for Si7214/15/16 in the Ordering Guide (200324717 End of Life Notification for High Voltage Si72xx Devices). Revision 1.2March, 2019•Removed all mention of AEC-Q100 qualification in product description and feature list.Revision 1.1October 11th, 2018•Added Si7211 TO92 part number.•Added details on Si7217 part number.•Added specifications for Si7217.Revision 1.0January 4, 2018•Updated power numbers to be consistent with production test limits.•Moved detailed ordering guide to a separate selection guide.•Updated detailed description to be clearer and more accurate.Revision 0.9June 30, 2017•Updated 1. Electrical Specifications.•Updated 7. Ordering Guide.•Minor typo corrections.Revision 0.1February 1, 2016•Initial release.Smart. Connected. Energy-Friendly.Products /productsQuality/qualitySupport and CommunitySilicon Laboratories Inc.400 West Cesar ChavezAustin, TX 78701USADisclaimerSilicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice to the product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Without prior notification, Silicon Labs may update product firmware during the manufacturing process for security or reliability reasons. Such changes will not alter the specifications or the performance of the product. Silicon Labs shall have no liability for the consequences of use of the information supplied in this document. This document does not imply or expressly grant any license to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any FDA Class III devices, applications for which FDA premarket approval is required, or Life Support Systems without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Silicon Labs disclaims all express and implied warranties and shall not be responsible or liable for any injuries or damages related to use of a Silicon Labs product in such unauthorized applications.Trademark InformationSilicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clock B uilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, Gecko OS, Gecko OS Studio, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® , Zentri, the Zentri logo and Zentri DMS, Z-Wave®, and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. Wi-Fi is a registered trademark of the Wi-Fi Alliance. All other products or brand names mentioned herein are trademarks of their respective holders.。

LC72131.M中文版.pdf

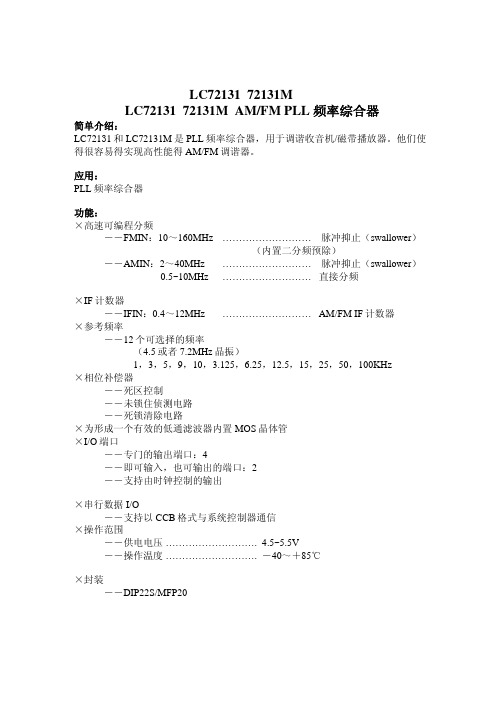

LC72131 72131MLC72131 72131M AM/FM PLL 频率综合器简单介绍:LC72131和LC72131M是PLL频率综合器,用于调谐收音机/磁带播放器。

他们使得很容易得实现高性能得AM/FM调谐器。

应用:PLL频率综合器功能:×高速可编程分频――FMIN:10~160MHz ……………………… 脉冲抑止(swallower)(内置二分频预除)――AMIN:2~40MHz ……………………… 脉冲抑止(swallower)0.5~10MHz ……………………… 直接分频×IF计数器――IFIN:0.4~12MHz ……………………… AM/FM IF计数器×参考频率――12个可选择的频率(4.5或者7.2MHz晶振)1,3,5,9,10,3.125,6.25,12.5,15,25,50,100KHz×相位补偿器――死区控制――未锁住侦测电路――死锁清除电路×为形成一个有效的低通滤波器内置MOS晶体管×I/O端口――专门的输出端口:4――即可输入,也可输出的端口:2――支持由时钟控制的输出×串行数据I/O――支持以CCB格式与系统控制器通信×操作范围――供电电压 ………………………. 4.5~5.5V――操作温度 ………………………. -40~+85℃×封装――DIP22S/MFP20管腿图:框图:说明:绝对最大值范围()允许操作范围()注释:推荐晶振振荡器CI值:<采样振荡电路>晶振振荡器:HC-49/U(Kinseki制造),CL=12pFC1=C2=15pF这个电路对于晶振确定,印刷电路板确定,其他确定的晶体振荡器电路是不变的。

为了可评估和稳定性,因此我们推荐晶振制造厂家。

在允许的操作范围内的电子特性()XIN XOUT 1(1) 22(20)Xtal OSC ×晶振共鸣连接(4.5/7/2MHz )FMIN16(14) 本地振荡信号输入 ×当串行数据输入DVS 位设置成1是,选择FMIN×输入频率范围是10~160MHz×输入信号通过内置的二分频预除器,并且输入到抑止计数器AMIN15(13) 本地振荡信号输入 ×当串行数据输入DVS 设置为0时,选择AMIN×当串行数据输入SNS 设置成1时:-输入频率范围是2~40MHz-信号直接输入到抑止(swallow )计数器-除数范围是272~65535,并且使用的除数将是一个估计设置×当串行数据输入SNS 位设置为0时:-输入频率范围时0.5~10MHz-信号直接输入到一个12位的可编程除法器-除数范围是4~4095,并且使用的除数将是一个估计设置CE3(2) 片选使能 当输入(DI )或者输出(DO )串行数据时,设置这个PIN 为高DI 4(3)数据输入 ×输入串行数据,从控制器到LC72131DO6(5) 数据输出 ×输出串行数据,从LC72131到控制器输出数据的内容是由串行数据DOC0到DOC2决定的。

LC723732资料

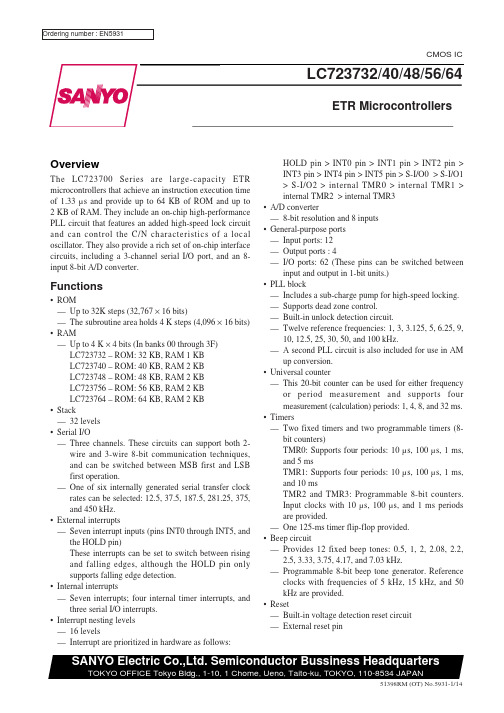

OverviewThe LC723700 Series are large-capacity ETR microcontrollers that achieve an instruction execution time of 1.33 µs and provide up to 64 KB of ROM and up to 2 KB of RAM. They include an on-chip high-performance PLL circuit that features an added high-speed lock circuit and can control the C/N characteristics of a local oscillator. They also provide a rich set of on-chip interface circuits, including a 3-channel serial I/O port, and an 8-input 8-bit A/D converter.Functions•ROM—Up to 32K steps (32,767 ×16 bits)—The subroutine area holds 4 K steps (4,096 ×16 bits)•RAM—Up to 4 K ×4 bits (In banks 00 through 3F)LC723732 – ROM: 32 KB, RAM 1 KB LC723740 – ROM: 40 KB, RAM 2 KB LC723748 – ROM: 48 KB, RAM 2 KB LC723756 – ROM: 56 KB, RAM 2 KB LC723764 – ROM: 64 KB, RAM 2 KB •Stack—32 levels •Serial I/O—Three channels. These circuits can support both 2-wire and 3-wire 8-bit communication techniques,and can be switched between MSB first and LSB first operation.—One of six internally generated serial transfer clock rates can be selected: 12.5, 37.5, 187.5, 281.25, 375,and 450 kHz.•External interrupts—Seven interrupt inputs (pins INT0 through INT5, and the HOLD pin)These interrupts can be set to switch between rising and falling edges, although the HOLD pin only supports falling edge detection.•Internal interrupts—Seven interrupts; four internal timer interrupts, and three serial I/O interrupts.•Interrupt nesting levels —16 levels—Interrupt are prioritized in hardware as follows:HOLD pin > INT0 pin > INT1 pin > INT2 pin >INT3 pin > INT4 pin > INT5 pin > S-I/O0 > S-I/O1> S-I/O2 > internal TMR0 > internal TMR1 >internal TMR2 > internal TMR3•A/D converter—8-bit resolution and 8 inputs •General-purpose ports —Input ports: 12—Output ports : 4—I/O ports: 62 (These pins can be switched between input and output in 1-bit units.)•PLL block—Includes a sub-charge pump for high-speed locking.—Supports dead zone control.—Built-in unlock detection circuit.—Twelve reference frequencies: 1, 3, 3.125, 5, 6.25, 9,10, 12.5, 25, 30, 50, and 100 kHz.—A second PLL circuit is also included for use in AM up conversion.•Universal counter—This 20-bit counter can be used for either frequency or period measurement and supports four measurement (calculation) periods: 1, 4, 8, and 32 ms.•Timers—Two fixed timers and two programmable timers (8-bit counters)TMR0: Supports four periods: 10 µs, 100 µs, 1 ms,and 5 msTMR1: Supports four periods: 10 µs, 100 µs, 1 ms,and 10 msTMR2 and TMR3: Programmable 8-bit counters.Input clocks with 10 µs, 100 µs, and 1 ms periods are provided.—One 125-ms timer flip-flop provided.•Beep circuit—Provides 12 fixed beep tones: 0.5, 1, 2, 2.08, 2.2,2.5, 3.33, 3.75, 4.17, and 7.03 kHz.—Programmable 8-bit beep tone generator. Reference clocks with frequencies of 5 kHz, 15 kHz, and 50kHz are provided.•Reset—Built-in voltage detection reset circuit —External reset pinCMOS ICSANYO Electric Co.,Ltd. Semiconductor Bussiness HeadquartersTOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPANOrdering number : EN5931•Cycle time—1.33 µs (All instructions are one word.)•Halt mode—The microcontroller operating clock is stopped in halt mode.There are four conditions that can clear halt mode: an interrupt request, a timer flip-flop overflow, a PA port input, or a HOLD pin input.•Operating supply voltage—4.5 to 5.5 V (Microcontroller block only: 3.5 to 5.5 V)•Package—QIP100E•OTP version—LC72P3700•Development tools—Emulator :RE32N—Evaluation chip: LC72EV3700—Evaluation chip board: EB-72EV3700Package Dimensions unit: mm3151-QFP100ELC723732/40/48/56/64SANYO: QFP100EPin AssignmentBlock DiagramParameterSymbol ConditionsRatings Unit Maximum supply voltage V DD max –0.3 to +6.5V Input voltage V IN 1PC-PORT–0.3 to +15V V IN 2All input pins other than V IN 1–0.3 to V DD + 0.3V Output voltageV OUT 1PC, PJ-PORT–0.3 to +15V V OUT 2All output pins other than V OUT 1–0.3 to V DD + 0.3V I OUT 1PC, PJ-PORT0 to +5mA Output currentI OUT 2PB, PD, PE, PF, PG, PK, PL, PM, PN, PO, PP, PQ, PR, 0 to +3mA PS, PT, PT-PORT, EO1, EO2, EO3, SUBPD Allowable power dissipation Pd max Ta = –40 to +85°C400mW Operating temperature Topg –40 to +85°C Storage temperatureTstg–45 to +125°CSpecificationsElectrical CharacteristicsAbsolute Maximum Ratings at Ta = 25°C, V SS = 0 VParameterSymbol ConditionsRatingsUnit min typ max V DD 1CPU and PLL operating 4.5 5.05.5V Supply voltageV DD 2CPU operating 3.5 5.5V V DD 3Memory retention1.3 5.5V PB, PC, PH, PI, PL, PM, PN, PO, PP, PQ, PR, V IH 1PS, PT-PORT, HCTR, LCTR, E03, SUBPD 0.7 V DD V DD V(with the I/O ports set to input mode.)Input high-level voltageV IH 2PD, PE, PF, PG, PK-PORT, LCTR,0.8 V DDV DD V (in period measurement mode), HOLD, RESET V IH 3SNS 2.5V DD V V IH 4PA-PORT0.6 V DDV DD V PB, PC, PH, PI, PL, PM, PN, PO, PP, PQ, PR, V IL 1PS, PT-PORT, HCTR, LCTR, E03, SUBPD 00.3 V DD V(with the I/O ports set to input mode.)Input low-level voltageV IL 2PA, PD, PE, PF, PG, PK-PORT, LCTR 00.2 V DDV (in period measurement mode), RESET V IL 3SNS 0 1.3V V IL 4HOLD 00.4 V DDV f IN 1XIN4.0 4.55.0MHz f IN 2FMIN V IN 2, V DD 110150MHz f IN 3FMIN V IN 3, V DD 110130MHz f IN 4AMIN(H) V IN 3, V DD 1 2.040MHz Input frequencyf IN 5AMIN(L) V IN 3, V DD 10.510MHz f IN 6HCTR V IN 3, V DD 10.412MHz f IN 7LCTR V IN 3, V DD 1100500kHz f IN 8LCTR(period measurement)120 ×103Hz V IH 2, V IL 2, V DD 1V IN 1XIN 0.5 1.5Vrms Input amplitude V IN 2FMIN0.07 1.5Vrms V IN 3FMIN, AMIN, HCTR, LCTR 0.04 1.5Vrms Input voltage rangeV IN 4ADI0 to ADI7V DDVAllowable Operating Ranges at Ta = –40 to +85°C, V DD = 3.5 to 5.5 VParameterSymbol ConditionsRatingsUnit min typ maxI IH 1XIN: V I = V DD = 5.0 V2.0 5.015µA I IH 2FMIN, AMIN, HCTR, LCTR: V I = V DD = 5.0 V 4.01030µAPA, PB, PC, PD, PE, PF, PG, PH, PI, PK, PL, PM, PN, PO, PP, PQ, PR, PS, PT-PORT, SNS, HOLD, RESET, HCTR, LCTR, E03, Input high-level currentI IH 3SUBPD: V I = V DD = 5.0 V3.0µA(With the port PA pull-down resistors disabled, and PB, PC, PD, PE, PF, PG, PK, PL, PM, PN, PP, PO, PQ, PR, PS, and PT ports set to input mode.)I IH 4Port PA (pull-down resistors enabled): 50µA V I = V DD = 5.0 V I IL 1XIN: V I = V SS2.0 5.015µA I IL 2FMIN, AMIN, HCTR, LCTR: V I = V SS4.01030µAPA, PB, PC, PD, PE, PF, PG, PH, PI, PK, PL, PM, PN, PO, PP, PQ, PR, PS, PT-PORT, Input low-level currentSNS, HOLD, RESET, HCTR, LCTR, E03, I IL 3SUBPD: V I = V SS3.0µA(With the port PA pull-down resistors disabled, and PB, PC, PD, PE, PF, PG, PK, PL, PM, PN, PP, PO, PQ, PR, PS, and PT ports set to input mode.)Input floating voltage V IF Port PA (pull-down resistors enabled)0.05 V DDV HysteresisV H PD, PE, PF, PG, PK-PORT, RESET,0.1 V DD 0.2 V DDV LCTR(in period measurement mode)V OH 1PB, PD, PE, PF, PG, PK, PL, PM, PN, PO, V DD – 1.0V Output high-level voltagePP, PQ, PR, PS, PT-PORT: I O = –1 mA V OH 2EO1, EO2, EO3, SUBPD: I O = –500 µA V DD – 1.0V V OH 3XOUT: I O = –200 µAV DD – 1.0V V OL 1PB, PD, PE, PF, PG, PK, PL, PM, PN, PO, 1.0V PP, PQ, PR, PS, PT-PORT: I O = 1 mA Output low-level voltageV OL 2E01, E02, E03, SUBPD: I O = 500 µA 1.0V V OL 3XOUT: I O = 200 µA 1.5V V OL 4PC, PJ-PORT: I O = 5 mA2.0V I OFF 1PB, PD, PE, PF, PG, PK, PL, PM, PN, PO, –3.0 3.0µA Output off leakage currentPP, PQ, PR, PS, PT-PORT I OFF 2E01, E02, E03, SUBPD –100100nA I OFF 3PC, PJ-PORT –5.0 5.0µA A/D conversion error ADI0 to ADI7 V DD 1–1.5 1.5LSB Rejected pulse widthP REJ SNS50µsec Power down detection voltage V DET 2.6 3.0 3.4V R PD 1Port PA (pull-down resistors enabled): 75100200k ΩPull-down resistanceV DD = 5 V R PD 2TEST1, TEST210k ΩI DD 1During normal operation (PLL operating)2030mAV DD 1, f IN 2 = 130 MHz Ta = 25°CHalt mode (CPU operation stopped, crystal I DD 2oscillator operating) (See figure 1.)0.45mACurrent drainV DD 2, Ta = 25°C *I DD 3Backup mode (crystal oscillator stopped)5µA (See figure 2.) V DD = 5.5 V, Ta = 25°C I DD 4Backup mode (crystal oscillator stopped)1µA(See figure 2.) V DD = 2.5 V, Ta = 25°C Electrical Characteristics in the allowable operating rangesNote *: Twenty instruction steps are executed every millisecond. The PLL, universal counter, and other functions are stopped.Test CircuitsNote: Ports PB through PG, and PJ through PT are all left open.However, ports PB through PG, PK through PT, EO3, and SUBPD are left open in output mode.Note: Ports PA through PT are all left open.Figure 1 IDD2 in Halt ModeFigure 2 IDD3 and IDD4 in Backup ModePin DescriptionsPin No.SymbolI/OFunctionEquivalent circuitDedicated input ports.These ports are designed with a low threshold voltage.The pull-down resistors for all four pins are set up together with an IOS1 instruction.The pull-down resistors cannot be set individually.Input is disabled in backup mode.32313029PA0PA1PA2PA3I General-purpose I/O portsThe mode (input or output) is set using the IOS2 instruction.Input is disabled and the pins go to the high-impedance state in backup mode.These ports are set up as general-purpose input ports after a power on reset.28272625PB0PB1PB2PB3I/OGeneral-purpose I/O ports (high-voltage input and output)The mode (input or output) is set using the IOS2 instruction.External pull-up resistors are required since the output circuits are open drain circuits.Input is disabled and the pins go to the high-impedance state in backup mode.These ports are set up as general-purpose input ports after a power on reset.24232221PC0PC1PC2PC3I/OGeneral-purpose I/O and external interrupt shared function ports The input formats are Schmitt inputs.The external interrupt function is enabled when the external interrupt enable flag is set.•When used as general-purpose I/O ports:The mode (input or output) is set in 1-bit units using the IOS2 instruction.•When used as external interrupt pins:The external interrupt functions are enabled by setting the corresponding external interrupt enable flag (INT4EN or INT5EN). Here, the pins must be set to input mode in advance.Input is disabled and the pins go to the high-impedance state in backup mode.These ports are set up as general-purpose input ports after a power on reset.20191817PD0/INT4PD1/INT5PD2PD3I/OContinued on next page.Pin No.SymbolI/OFunctionEquivalent circuitGeneral-purpose I/O ports with shared functions as serial I/O portsThe input formats are Schmitt inputs. The PE1/SCK2 and PE2/SO2 pins can be switched to function as open drain outputs.The IOS1 instruction is used to switch between the general-purpose I/O port and serial I/O port functions.•When used as general-purpose I/O ports:The pins are set to the general-purpose I/O port function using the IOS1instruction.The mode (input or output) is set in 1-bit units using the IOS1 instruction.•When used as serial I/O ports:The pins are set to the serial I/O port function using the IOS1 instruction.[Pin states when set to the serial I/O port function]PE0, PF0, PG0 ... General-purpose I/O PE1, PF1, PG1 ... SCK input or output PE2, PF2, PG2 ... SO output PE3, PF3, PG3 ... SI inputThe PE1/SCK2 and PE2/SO2 pins can be switched to function as open drain outputs with the IOS2 instruction. When using this circuit type, the external pull-up resistors must be connected to the same power supply as that used by the IC.Input is disabled and the pins go to the high-impedance state in backup mode.These ports are set up as general-purpose input ports after a power on reset.1615141312111098765PE0PE1/SCK2PE2/S02PE3/SI2PF0PF1/SCK1PF2/S01PF3/SI1PG0PG1/SCK0PG2/S00PG3/SI0I/OConnections for a 4.5-MHz crystal oscillator element1100XIN XOUTI OMain charge pump outputsThese pins output a high level when the frequency of the local oscillator divided by n is higher than that of the reference frequency, and they output a low level when that frequency is lower. They go to the high-impedance state when the frequencies match.These pins go to the high-impedance state in backup mode, after a power on reset,and in the PLL stopped state.9897E01E02OPower supply connectionsThe V DD PORT and V SS PORT pins mainly supply power for the peripheral I/O blocks and the regulator.The V DD PLL and V SS PLL pins mainly for the PLL circuits.The V SS CPU pin is mainly used by the CPU block.The V SS ADC pin is mainly used by the A/D converter block.Since all the V DD and V SS pins are independent, all must be connected to the same power supply.39934408196V DD PORT V DD PLL V SS CPU V SS PORT V SS ADC V SS PLL —Internal low voltage outputConnect a bypass capacitor to this pin.3V REGO FM VCO (local oscillator) inputThis pin is selected with CW1 in the PLL instruction.The signal input to this pin must be capacitor coupled.Input is disabled in backup mode, after a power on reset, and in the PLL stopped state.95FM IN IAM VCO (local oscillator) inputThis pin is selected and the band set with CW1 (b1, b0) in the PLL instruction.The signal input to this pin must be capacitor coupled.Input is disabled in backup mode, after a power on reset, and in the PLL stopped state.94AM IN Ib1b0Band 10 2 to 40 MHz (SW)110.5 to 10 MHz (MW, LW)Continued on next page.Pin No.SymbolI/OFunctionEquivalent circuitSub-charge pump output and general-purpose input shared function portThe IOS2 instruction is used for switching between the sub-charge pump output and general-purpose input functions.•When used as the sub-charge pump output:The sub-charge pump output function is set up with the IOS2 instruction.A high-speed locking circuit can be formed by using this pin in conjunction with the main charge pump.The sub-charge pump is controlled using the DZC instruction.•When used as a general-purpose input:The general-purpose input function is set up with the IOS2 instruction.Data is read from the port using the INR instruction.This pin goes to the high-impedance state in backup mode, after a power on reset,and in the PLL stopped state.92SUBPDI/OSecond PLL charge pump output and general-purpose input shared function port The IOS2 instruction is used for switching between the second PLL charge pump output and general-purpose input functions.•When used as a charge pump output:The charge pump output function is set up with the IOS2 instruction.This pin outputs a low level when the frequency of the local oscillator divided by n is higher than that of the reference frequency, and it outputs a high level when that frequency is lower. It goes to the high-impedance state when the frequencies match. (Note that the logic of this pin is inverted from that of the EO1 and EO2pins.)•When used as a general-purpose input:The general-purpose input function is set up with the IOS2 instruction.Data is read from the port using the INR instruction.This pin goes to the high-impedance state in backup mode, after a power on reset,and in the PLL stopped state.91E03I/OUniversal counter and general-purpose input shared function input portThe IOS1 instruction is used for switching between the universal counter and general-purpose input functions.•When used for frequency measurement:The universal counter function is set up with the IOS1 instruction.The counter is controlled using the UCS and UCC instructions.Since this pin functions as an AC amplifier in this mode, the input signal must be input with capacitor coupling.•When used as a general-purpose input pin:The general-purpose input function is set up with the IOS1 instruction.Data is read from the port using the INR (b0) instruction.Input is disabled in backup mode. (The input pin will be pulled down.) The universal counter function is selected after a power on reset.90HCTR IUniversal counter (frequency or period measurement) and general-purpose input shared function input portThe IOS1 instruction is used for switching between the universal counter and general-purpose input functions.•When used for frequency measurement:The universal counter function is set up with the IOS1 instruction.Set up LCTR frequency measurement mode with the UCS instruction, and control operation with the UCC instruction. Since this pin functions as an AC amplifier in this mode, the input signal must be input with capacitor coupling.•When used for period measurement:The universal counter function is set up with the IOS1 instruction.Set up LCTR frequency measurement mode with the UCS instruction, and control operation with the UCC instruction. Since the bias feedback resistor is disconnected in this mode, the input signal must be input with DC coupling.•When used as a general-purpose input pin:The general-purpose input port function is set up with the IOS1 instruction.Data is read from the port using the INR (b1) instruction.Input is disabled in backup mode. (The input pin will be pulled down.)The universal counter function (HCTR frequency measurement mode) is selected after a power on reset.89LCTR Ib3b2Operation00High impedance01Only operates when the PLL is unlocked (450 kHz)10Only operates when the PLL is unlocked (900 kHz)11Normal operationPin No.SymbolI/OFunctionEquivalent circuitVoltage sense and general-purpose input shared function port This input circuit is designed with a low input threshold voltage.•When used as a voltage sense input:This pin is used to test for power failures on the return from backup mode.Application can test this condition using the internal SNS flip-flop. The SNS flip-flop can be tested with the TST instruction.(This usage requires external components (capacitors and resistors). See the sample application circuit in the user's manual.)•When used as a general-purpose input port:When used as a general-purpose input port the pin state can be tested with the TST instruction.Unlike the other input ports, input to this pin is not disabled in backup mode and after a power on reset. As a result, through currents must be taken into account when designing applications that use this pin as a general-purpose input.88SNS IPower supply monitor (with interrupt function)This pin is designed with a high input threshold voltage.This pin is normally connected to the ACC line and used for power off detection.When a power off state is detected, the HOLDON flag and the hold interrupt request flag will be set. To enter backup mode, execute a CKSTP instruction when the HOLD pin is low. Set this pin high to clear backup mode.87HOLD ISystem reset pinWhen the CPU is operating or in halt mode, the system is reset when this pin is held low for at least one machine cycle. Execution starts with the PC pointing to location 0. At this time the SNS flip-flop is set. A low level must be applied for at least 50 ms when power is first applied.86RESET IGeneral-purpose input and A/D converter input shared function portsThe IOS1 instruction is used to switch between the general-purpose input and the A/D converter input functions.•When used as a general-purpose input ports:The general-purpose input port function is set up with the IOS1 instruction. (In bit units)•When used as A/D converter input pins:The A/D converter input port function is set up with the IOS1 instruction. (In bit units)The pin whose voltage is to be converted is specified with the IOS1 instruction, and the conversion is started with the UCC instruction.Note: Since input is disabled for ports specified for the ADI function, executing aninput instruction for such a port will always return a low level.Input is disabled in backup mode.These ports are set up as general-purpose input ports after a power on reset.8584838281807978PH0/ADI0PH1/ADI1PH2/ADI2PH3/ADI3PI0/ADI4PI1/ADI5PI2/ADI6PI3/ADI7IGeneral-purpose output portsSince these are open-drain output circuits, external pull-up resistors are required.The internal transistors are turned off (resulting in a high-level output) in backup mode and after a power on reset.76757473PJ0PJ1PJ2PJ3OGeneral-purpose I/O and external interrupt shared function ports The input formats are Schmitt inputs.The external interrupt function is enabled when the external interrupt enable flag is set.• When used as general-purpose I/O ports:The mode (input or output) is set in 1-bit units using the IOS1 instruction.• When used as external interrupt pins:The external interrupt functions are enabled by setting the corresponding external interrupt enable flag (INT0EN through INT3EN). Here, the pins must be set to input mode in advance.Input is disabled and the pins go to the high-impedance state in backup mode.These ports are set up as general-purpose input ports after a power on reset.72717069PK0/INT0PK1/INT1PK2/INT2PK3/INT3I/OContinued on next page.Continued from preceding page.Pin No.Symbol I/OFunctionEquivalent circuitGeneral-purpose I/O portsThe mode is switched between input and output with the IOS instruction.Input is disabled and the pins go to the high-impedance state in backup mode.These ports are set up as general-purpose input ports after a power on reset.68 to 61PL0 to 3PN0 to 3I/OGeneral-purpose I/O port and beep tone output shared function portsThe IOS2 instruction is used to switch between the general-purpose I/O port and the beep tone output functions.•When used as a general-purpose input ports:The general-purpose I/O port function is set up with the IOS2 instruction.(Pins PN1 through PN3 are general-purpose I/O pins.)•When used as the beep tone output pin:The beep tone output function is set up with the IOS2 instruction.The frequency is set with the BEEP instruction.When this pin is used as the beep tone output pin, executing an output instruction for this pin only sets the internal latch and has no influence on the output.Input is disabled and the pins go to the high-impedance state in backup mode.These ports are set up as general-purpose input ports after a power on reset.60595857PN0/BEEP PN1PN2PN3I/OGeneral-purpose I/O portsThe mode is switched between input and output with the IOS instruction.Input is disabled and the pins go to the high-impedance state in backup mode.These ports are set up as general-purpose input ports after a power on reset.56 to 49P00 to 3PP0 to 3I/OGeneral-purpose I/O portsThe mode is switched between input and output with the IOS instruction, and data is input with the INR instruction and output with the OUTR instruction.The SPB, RPB, TPT, and TPF instruction cannot be used with these ports.Input is disabled and the pins go to the high-impedance state in backup mode.These ports are set up as general-purpose input ports after a power on reset.48 to 4138 to 33PQ0 to 3PR0 to 3PS0 to 3PT0 to 1I/OIC test pinsThese pins must be tied to ground.992TEST1TEST2LC723700 Instruction Set Abbreviations ADDR:Program memory address b:Borrow c:CarryDH:Data memory address High (Row address) [2 bits]DL:Data memory address Low(Column address) [4 bits]I:Immediate data [4 bits]M:Data memory address N:Bit position [4 bits]M ADR :M specified by address registerROM ADR :Program memory data specified by address register P1n, P2n:Port number [4 bits]PW1n, PW2n:Port control word number [4 bits]PEn:Peripheral register number [4 bits]SR:ADR/DTRADR:Address register DTR:Data registerr:General register (One of the address from 00H to 0FH of BANK0)SWR:Status write register SRR:Status read register( ), [ ]:Contents of register or memory M(DH, DL):Data memory specified by DH, DLMnemonicOperand FunctionOperations function Instruction format1st 2nd ADr M Add M to rr ←(r) + (M)010000DH DL r ADS r M ADD M to r, then skip if carry r ←(r) + (M), skip carry 010001DH DL r AC r M Add M to r with carryr ←(r) + (M) + C010010DH DL r ACS r M Add M to r with carry, then skip if carry r ←(r) + (M) + C skip if carry 010011DH DL r AI M I Add I to MM ←(M) + I010100DH DL I AIS M I Add I to M, then skip if carry M ←(M) + I, skip if carry 010101DH DL I AIC M I Add I to M with carryM ←(M) + I + C010110DH DL I AICS M I Add I to M with carry, then skip if carry M ←(M) + I + C, skip if carry 010111DH DL I SUr M Subtract M from rr ←(r) – (M)011000DH DL r SUS r M Subtract M from r, then skip if borrow r ←(r) – (M), skip if borrow 011001DH DL r SB r M Subtract M from r with borrow r ←(r) – (M) – b011010DHDL r SBS r M Subtract M from r with borrow, r ←(r) – (M) –b, skip if borrow 011011DH DL r then skip if borrow SI M I Subtract I from MM ←(M) – I011100DH DL I SIS M I Subtract I from M, then skip if borrow M ←(M) – I, skip if borrow 011101DH DL I SIB M I Subtract I from M with borrow M ←(M) – I – b011110DHDL I SIBSM I Subtract I from M with borrow, M ←(M) – I –b, skip if borrow 011111DH DL I then skip if borrw SEQ r M Skip if r equal to M (r) – (M), skip if zero 000100DH DL r SEQI M I Skip if M equal to I (M) – I, skip if zero 000101DH DL I SNEI M I Skip if M not equal to I(M) – I, skip if not zero 000001DH DL I SGE r M Skip if r is greater than or equal to M (r) – (M), skip if not borrow 000110DH DL r SLE r M Skip if r is less than M(r) – M, skip if borrow 000010DH DL r SGEI M I Skip if M is greater than or equal to I (M) – I, skip if not borrow 000111DH DL I SLEIMISkip if M is less than I(M) – I, skip if borrow000011DHDLIS u b t r a c t i o n i n s t r u c t i o n sC o m p a r i s o n i n s t r u c t i o n sA d d i t i o n i n s t r u c t i o n sI n s t r u c t i o n g r o u pf e d c b a 9876543210Continued on next page.Continued on next page.This catalog provides information as of June, 1998. Specifications and information herein are subject to change without notice.s No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.s Anyone purchasing any products described or contained herein for an above-mentioned use shall:Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.s Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.MnemonicOperand FunctionOperations function Instruction format1st 2nd IN M P1n Input port1 data to MM ←(P1n)111010DH DL P1n OUTM P1n Output contents of M to port 1P1n ←M 111011DH DL P1n INR M P2n Input port 2 data to M M ←(P2n)001110DH DL P2n OUTR M P2n Output contents of M to port 2P2n ←(M)001111DH DL P2n SPB P1n N Set port 1 bits (P1n)N ←100000010P1n N RPB P1n N Reset port 1 bits(P1n)N ←000000011P1n N TPT P1n N Test port 1 bits, then skip if all bitsif (P1n)N = all 1, then skip 11111100P1n N specified are trueTPFP1nNTest port 1 bits, then skip if all bits if (P1n)N = all 0, then skip11111101P1nNspecified are falseBANK I Select Bank BANK ←I 1111100100IMVTLMove program memory data specified by DTR ←(ROM ADR )000000000011ADR to DTRPUSH SR Move ADR/DTR to stack Stack ←(ADR/DTR)111110011000SR POP SR Move stack to ADR/DTR ADR/DTR ←Stack 111110011001SR PAGEI Set page flag PAGE flag ←I 000000000111I HALT IHalt mode control HALT reg ←I,000000000100Ithen CPU clock stop CKSTP Clock stop Stop xtal OSC if HOLD = 0000000000101NOPNo operationNo operation000000000000I /O i n s t r u c t i o n sB a n k s w i t c h i n g i n s t r u c t i o n sT a b l e r e f e r e n c e i n s t r u c t i o n s S t a c k m a n i p u l a t i o n i n s t r u c t i o n sO t h e r i n s t r u c t i o n sI n s t r u c t i o n g r o u pf e d c b a 9876543210。

Icom721(725)短波电台中文使用说明书

Icom 721/725短波电台中文使用说明书BH1MME整理2011-6-21 一前面板1-3(略)4、可变频率振荡器开关[VFO]选择VFO A或VFO B。

本机中具有两个可变频率振荡器,分别叫做VFOA和VFOB,均可进行接收和发射。

两套系统为机器的使用提供了很大的灵活性。

按一下[VFO]即可选择VFOA或VFOB。

5、异频开关[SPLIT]选择异频操作功能。

6、存储频道选择开关[UP][DOWN]选择存储频道。

7、存储器写入开关[MW]将显示屏上所显示的频率和工作模式写入所显示的存储频道中。

8、存储器读出开关[MEMO]选定存储频道工作模式。

9、接收增量调谐开关[RIT]开启或关断接收增量调谐电路,该电路的作用是微调接收频率,以补偿发射台频率的频率漂移,当不改变本机的发射(即显示的)频率时,可将显示屏上的频率移动+—1KHz(但不显示),以获得满意的接收效果。

10、接收增量调谐旋钮当接收增量调谐电路起作用时,用此移动(微调)接收频率。

11、功能转换开关[FUNC]本机的一些开关具有两种功能,按此开关后,再按相应的开关,即可选择第二功能,见下表:—1KHz(但不显示),以获得满意的接收效果。

10、接收增量调谐旋钮当接收增量调谐电路起作用时,用此移动(微调)接收频率。

11、功能转换开关[FUNC]本机的一些开关具有两种功能,按此开关后,再按相应的开关,即可选择第二功能,见下表:12、天线调谐器开关[TUNER]控制AH-3型高频全自动天线调谐器(选购件)。

13、频段开关[BAND]使调谐旋钮的作用仅仅是选择(改变)频段而不是频率。

14、调谐旋钮锁定开关[LOCK]使调谐旋钮失效,以及当工作于FM模式时,发射一个亚音频信号。

15、M赫兹调谐步进级开关[MHz]选择1MHz的调谐步级。

即调谐旋钮转动时,以MHz步级改变频率。

16、K赫兹调谐步进级开关[MHz]选择1KHz的调谐步级。

即调谐旋钮转动时,以KHz步级改变频率。

LC72131.M中文版

等于除数设置

的值

注释:当 P4 是 LSB 时,忽略 P0~P3

×选择信号输入管脚(AMIN 或者 FMIN)给可编程除

法器,选择输入频率范围(*表示不需要关心)

DVS SNS 输入脚 输入频率范围

1 * FMIN 10~160MHz

0 1 AMIN 2~40MHz

0 0 AMIN 0.5~10MHz

LC72131

6(5) 数据输出 ×输出串行数据,从 LC72131

到控制器

输出数据的内容是由串行数据

DOC0 到 DOC2 决定的。

17(15) 电源供电 ×LC72131 供电电源管腿

(VDD=4.5 到 5.5V)

×当电源第一次上电时,复位

电路电源工作

21(19) 地

×LC72131 地

-

7(6)

在允许的操作范围内的电子特性(

)

XIN 1(1) XOUT 22(20)

Xtal OSC ×晶振共鸣连接 (4.5/7/2MHz)

FMIN AMIN

CE

16(14) 15(13)

3(2)

本地振荡 信号输入 本地振荡 信号输入

片选使能

×当串行数据输入 DVS 位设 置成 1 是,选择 FMIN ×输入频率范围是 10~ 160MHz ×输入信号通过内置的二分频 预除器,并且输入到抑止计数 器

行数据输入)

×24 位数据输入

×详细内容请见“DI 控制

数据(串行数据输入)”

结构

3 OUT(A2) 0 1 0 1 0 1 0 0 ×数据输出模式(串行数

据输出)

1、DI 控制数据(串行数据输入)结构 ×IN1 模式

2、DI 控制数据功能 NO. 控制块/数据 功能

PC7312C-12C1中文资料

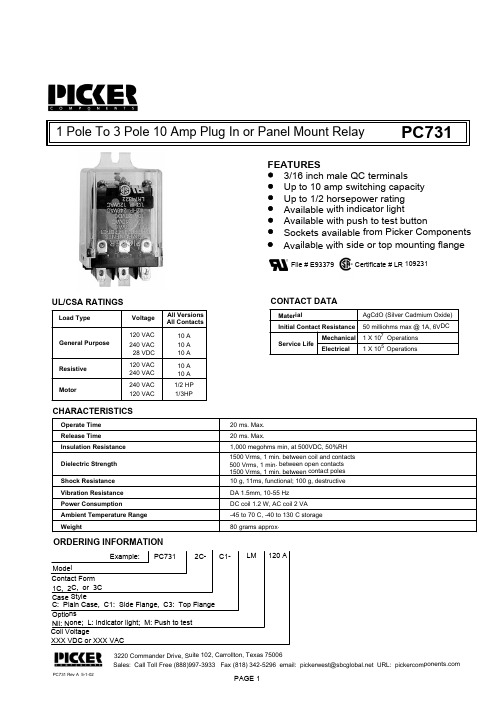

1 Pole To 3 Pole 10 Am p Plug In or Panel Mount R elayFEATURES3/16 inch male QC terminals Up to 10 amp switching capaci ty Available with indicator lightUp to 1/2 horsepower rating Available with push to test butt onSockets available from Picker C omponents PC731Load TypeGeneral PurposeResistive MotorVoltage 120 VAC 240 VAC 28 VDC 240 VAC 120 VACAll Versions 10 A 10 A 10 A 1/2 HP 1/3HPUL/CSA RATINGSCONTACT DATAMaterialInitial Contact Resistance Service LifeMechanical ElectricalAgCdO (Silver Cadmium Oxide)50 milliohms max @ 1A, 6VDC 1 X 1071 X 105CHARACTERISTICSOperate Time 20 ms. Max.Release Time Insulation Resistance 20 ms. Max.1,000 megohms min, at 500VDC, 50%RH Dielectric Strength 1500 Vrms, 1 min. between coil and contacts 500 Vrms, 1 min. between open contacts Shock Resistance 10 g, 11ms, functional; 100 g, destructive Vibration Resistance DA 1.5mm, 10-55 Hz Power Consumption DC coil 1.2 W, AC coil 2 VA Ambient Temperature Range -45 to 70 C, -40 to 130 C storage Weight80 grams approx.120 VAC 240 VAC 10 A 10 A Operations OperationsSales: Call Toll Free (888)997-3933 Fax (818) 342-5296 email: pickerwest@ URL: 3220 Commander Drive, Suite 102, Carrollton, T exas 75006All ContactsPC731 Rev A 5-1-021500 Vrms, 1 min. between contact poles PAGE 1File # E93379Certificate # LR 109231ORDERING INFORMATIONExample:PC731ModelLMCoil Voltage2C-Contact Form 1C, 2C, or 3C 120 AXXX VDC or XXX VACCase StyleC: Plain Case, C1: Side Flange, C3: To p Flange Available with side or top moun ting flangeOptionsNil: None; L: Indicator light; M: Push to te st C1-PC731PC731PAGE 2Sales: Call Toll Free (888) 997-3933 Fa x (818) 342-5296 email: pickerwest@sbcg 3220 Commander Drive, Suite 102, Car rollton, Texas 75006Tolerances +.010 unless otherwise noted(11.0)(11.0)(5.6)(8.4)(7.6).44.44.22.33.301.870(47.5)1.37(34.8)1.50(38.0)2.50(63.5)2.750(69.9).500(12.7).140 Dia.(3.55)1C2C3CWiring Diagrams2.150(54.61)Plain CaseSide Flange2.53(64.26)Top Flange.187 Typ.(4.75)Dimensions in Inches (Millimeters)。

收音头规格书

不计权 A 计权 不计权 A 计权

SPEC 规格

MIN 最小 55 75 53 71

TYP 正常 57 76 54 73

MAX 最高 58 77 55 74

19KHz LPF OFF 98.1MHz

0.6 1.0

MONO

19KHz LPF ON 98.1MHz

1.5 2.5

STEREO

L and R

Antenna for measurement

PILOT

7.5KHz

RF Input Level: 94dB EMF

Antenna Input 75

RF Input Level 60dB

测试调制度

FM MONO 1KHz

75.0KHz 频偏 AM 1KHz 30%调制度

STEREO 1KHz L+R 67.5KHz 频偏

19KHz 90.1MHz LPF 98.1MHz ON 106.1MHz

9

15

dB V

7

15

7

15

ITEM 项目

MONO S/N Ratio 98.1MHz

STEREO S/N Ratio

98.0MHz Distortion

失真率

Audio Output Level

调频输出电平 Stereo Separation

AGC From 自动增益控制特性

Audio Frequency at 3kHz

频率特性 3kHz

Auto Stop Level 自动停台电平

Tuned Level 调谐电平指示 Mute Attenuation 静噪衰减量

TEST Condition 试验条件

999KHz 以 1KHz 为基准 999KHz

ICP DAS GPS-721-MRTU GPS接收器快速入门指南说明书

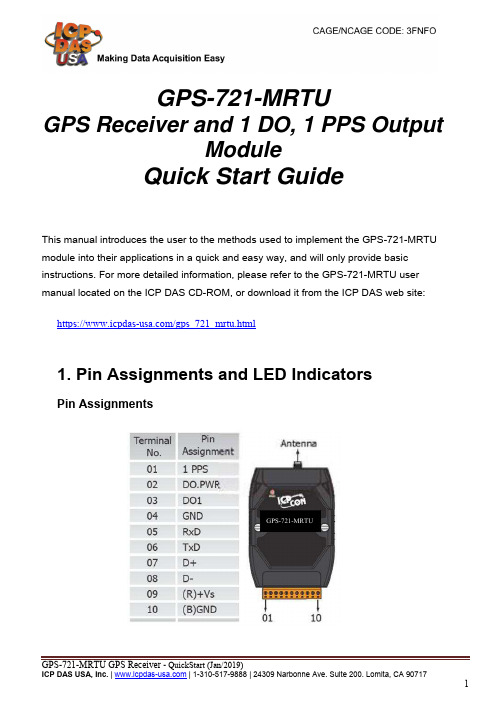

GPS-721-MRTUGPS Receiver and 1 DO, 1 PPS OutputModuleQuick Start GuideThis manual introduces the user to the methods used to implement the GPS-721-MRTU module into their applications in a quick and easy way, and will only provide basic instructions. For more detailed information, please refer to the GPS-721-MRTU user manual located on the ICP DAS CD-ROM, or download it from the ICP DAS web site:https:///gps_721_mrtu.html1. Pin Assignments and LED IndicatorsPin AssignmentsLED Indicators2. Operation ModesThe back panel of the GPS-721-MRTU contains the frame groundand the INIT/Normal Switch. Themodule has two operation modes(INIT and Normal modes), whichcan be determined via the switchmechanism on the chassis. Thedescription and figure are asfollows.3. Wiring Digital Output WiringPPS WiringMountingThe GPS-721-MRTU can be mounted on either a DIN-Rail or a wall, or it can be piggybacked to other modules using the bottom of the chassis.DIN-Rail MountingThe GPS-721-MRTU includes simple rail clips that allow for for reliable mounting on a standard 35 mm DIN rail.Three new DIN-Rail models are available, and each is made of stainless steel, which is stronger than those made of aluminum. There is a screw at one end, and a ring terminal is included so that it can be easilyconnected to the earth ground.Note: It is recommended that a 16 – 14 AWG wire is used to connect the DIN rail to the earth ground.Piggyback MountingThe GPS-721-MRTU has two holes on either side of the module to enable piggyback mounting. Refer to the figure below for an illustration of how to piggyback the modules.4. Using the ModuleThis section describes the installation of the GPS-721-MRTU, and provides details of how to begin using the module.1. Refer to Section 1 for details of the pin assignments.2. Connect the module to the RS-485 network using the DATA+ and DATA-pins. See Section 1 for details of the pin assignments. If the Host is only equipped with an RS-232 interface, then an RS-232 to RS-485 converter will be required. The GPS-721-MRTU supports RS-232 connections.Refer to the “I-7000 Bus Converter User Manual” for more information.Configure the module by sending the %AANNTTCCFF command. See Section 2.1 of the “GPS-721-MRTU User Manual” for details.ICP DAS provides two free tools that allow the GPS-721-MRTU to beeasily configured, the DCON Utility and the Send232 application, both of which can be downloaded from/pub/cd/8000cd/napdos/driver/dcon_utility/3. All module functions can be implemented using the DCON commandsdescribed in Section 2.4. If the Host is a PC with a Windows operating system installed, the DCONUtility can be used to allow easy configuration and reading of data. The DCON Utility can be downloaded from the ICP DAS website(), and documentation for the DCON Utility can be found in the ”Getting Started For I-7000 Series Modules” manual.Note 1: The DCON Utility is provided to enable commands to be sent to the GPS-721-MRTU. The graphic settings of the GPS-721-MRTU arenot supported by the DCON Utility.Note 2: If GPS-721-MRTU is unable to receive a GPS signal, check the position of the antenna and if the problem persists, try relocating theGPS antenna outside.。

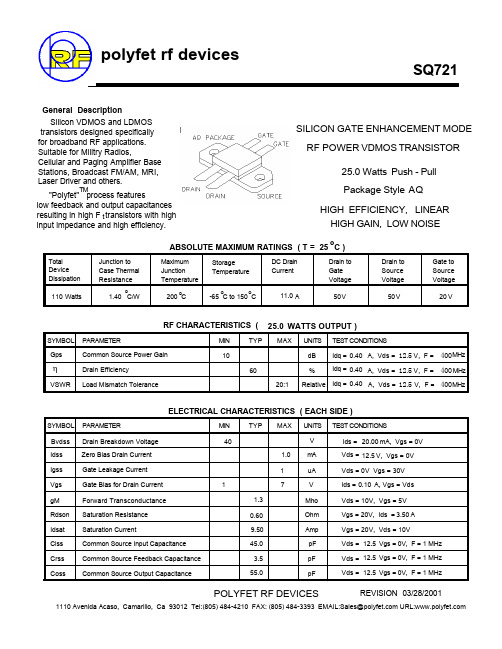

SQ721资料

400 MHz 400 MHz

η

VSWR

Relative Idq = 0.40 A, Vds = 12.5 V, F = 400 MHz

ELECTRICAL CHARACTERISTICS ( EACH SIDE )

SYMBOL Bvdss Idss Igss Vgs gM Rdson Idsat Ciss Crss Coss PARAMETER Drain Breakdown Voltage Zero Bias Drain Current Gate Leakage Current Gate Bias for Drain Current Forward Transconductance Saturation Resistance Saturation Current Common Source Input Capacitance Common Source Feedback Capacitance Common Source Output Capacitance 1 1.3 0.60 9.50 45.0 3.5 55.0 MIN 40 1.0 1 7 TYP MAX UNITS V mA uA V Mho Ohm Amp pF pF pF TEST CONDITIONS Ids = 20.00 mA, Vgs = 0V Vds = 12.5 V, Vgs = 0V Vds = 0V Vgs = 30V Ids = 0.10 A, Vgs = Vds Vds = 10V, Vgs = 5V Vgs = 20V, Ids = 3.50 A Vgs = 20V, Vds = 10V Vds = 12.5 Vgs = 0V, F = 1 MHz Vds = 12.5 Vgs = 0V, F = 1 MHz Vds = 12.5 Vgs = 0V, F = 1 MHz

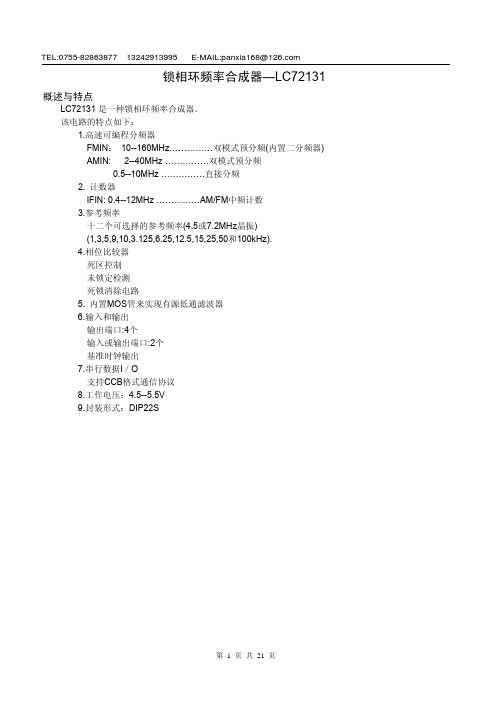

锁相环频率合成器—LC72131

TEL:0755-8286387713242913995E-MAIL:*****************锁相环频率合成器—LC72131概述与特点LC72131是一种锁相环频率合成器。

该电路的特点如下:1.高速可编程分频器FMIN: 10--160MHz……………双模式预分频(内置二分频器)AMIN: 2--40MHz ……………双模式预分频0.5--10MHz ……………直接分频2. 计数器IFIN: 0.4--12MHz ……………AM/FM中频计数3.参考频率十二个可选择的参考频率(4.5或7.2MHz晶振)(1,3,5,9,10,3.125,6.25,12.5,15,25,50和100kHz).4.相位比较器死区控制未锁定检测死锁清除电路5. 内置MOS管来实现有源低通滤波器6.输入和输出输出端口:4个输入或输出端口:2个基准时钟输出7.串行数据I/O支持CCB格式通信协议8.工作电压:4.5--5.5V9.封装形式:DIP22S方框图与引出端功能最大额定值(Tamb=25℃)参数名称符号引脚额定单位最大电源电压Vdd max Vdd –0.3~+7.0V Vin1max CE,CL,DI,AIN –0.3~+7.0VVin2max XIN,FMIN,AMIN,IFIN –0.3~VDD + 0.3V最大输入电压Vin3max IO1,IO2 –0.3~+15VVo1max DO –0.3~+7.0VVo2max XOUT,PD –0.3~VDD + 0.3V最大输出电压Vo3max BO1~BO4,IO1,IO2,AOUT –0.3~+15VLo1max BO1 0~3.0mALo2max DO,AOUT 0~6.0mA 最大输出电流Lo3max BO2~BO4,IO1,IO2 0~10.0mA最大功耗Pd max Ta≦85℃DIP22S: 350MFP20: 180mW工作温度Topr –40~+85°C存储温度Tstg –55~+125°C电特性(Tamb=25℃)参数名称符号引脚测试条件最小最大单位电源电压Vdd Vdd 4.5 5.5 VVih1 CE,CL,DL 0.7Vdd 6.5 V 输入高电平 Vih2 IO1, IO20.7Vdd 13 V 输入低电平 Vil CE,CL,DI,IO1,IO2 0 0.3Vdd V Vo1 DO0 6.5 V 输出电压 Vo2 BO1---BO4,IO1,IO2,AOUT 013 VFin1 XIN Vin1 1 8 MHz Fin2 FMIN Vin210 160 MHzFin3 AMIN Vin3,SNS = 1 2 40 MHzFin4 AMIN Vin4,SNS =0 0.5 10 MHz输入频率Fin5 IFINVin5 0.4 12 MHz Vin1 XIN Fin1400 1500 mVrmsVin2-1 FMIN F =10~130MHz 40 1500 mVrms Vin2-2 FMIN F =130~160MHz 701500 mVrmsVin3 AMIN Fin3, SNS = 1 40 1500 mVrms Vin4 AMIN Fin4, SNS =0 40 1500 mVrms Vin5 IFIN Fin5,IFS = 1 40 1500 mVrms 输入振幅 Vin6 IFINFin6,IFS =0 70 1500 mVrms 晶体振荡器 Xtal XIN,XOUT*4.0 8.0 MHz注:允许工作范围:Ta=-40-----+85℃,Vss=0V 。

TPI 721可燃气泄漏探测器说明书