PCB增加网络,编辑网络

PCB布线设计规范精选全文

可编辑修改精选全文完整版印制电路板设计规范一、适用范围该设计规范适用于常用的各种数字和模拟电路设计。

对于特殊要求的,尤其射频和特殊模拟电路设计的需量行考虑。

应用设计软件为Protel99SE。

也适用于DXP Design软件或其他设计软件。

二、参考标准GB 4588.3—88 印制电路板设计和使用Q/DKBA—Y004—1999 华为公司内部印制电路板CAD工艺设计规范三、专业术语1.PCB(Print circuit Board): 印制电路板2.原理图(SCH图):电路原理图,用来设计绘制,表达硬件电路之间各种器件之间的连接关系图。

3.网络表(NetList表):由原理图自动生成的,用来表达器件电气连接的关系文件。

四、规范目的1.规范规定了公司PCB的设计流程和设计原则,为后续PCB设计提供了设计参考依据。

2.提高PCB设计质量和设计效率,减小调试中出现的各种问题,增加电路设计的稳定性。

3.提高了PCB设计的管理系统性,增加了设计的可读性,以及后续维护的便捷性。

4.公司正在整体系统设计变革中,后续需要自主研发大量电路板,合理的PCB设计流程和规范对于后续工作的开展具有十分重要的意义。

五、SCH图设计5.1 命名工作命名工作按照下表进行统一命名,以方便后续设计文档构成和网络表的生成。

有些特殊器件,没有归类的,可以根据需求选择其英文首字母作为统一命名。

对于元器件的功能具体描述,可以在Lib Ref中进行描述。

例如:元器件为按键,命名为U100,在Lib Ref中描述为KEY。

这样使得整个原理图更加清晰,功能明确。

5.2 封装确定元器件封装选择的宗旨是1. 常用性。

选择常用封装类型,不要选择同一款不常用封装类型,方便元器件购买,价格也较有优势。

2. 确定性。

封装的确定应该根据原理图上所标示的封装尺寸检查确认,最好是购买实物后确认封装。

3. 需要性。

封装的确定是根据实际需要确定的。

总体来说,贴片器件占空间小,但是价格贵,制板相同面积成本高,某些场合下不适用。

PCB布线的Net Class功能

PCB软件不为人知的技巧2010-03-03 17:20:48| 分类:电路设计 | 标签: |字号大中小订阅2007-08-07作者:王玮PCB布线软件的书籍和资料大家应该都看得不少了,网上有很多布线技巧的文章,大都是教人如何避免干扰,如何走地线等等,其实这些软件里面还有一个功能,也很好用的,只是绝大部分的书籍都没有介绍。

这就是Net Class功能。

Pcb文件首次加载网络表的时候,没有对其进行分类。

这个功能可以人工将无数的网络连接分门别类,比如分成Power、data_bus、Address_bus、Hi_volta等类别。

这样分类后可以分别对不同的类别施加不同的布线策略。

好了,现在让我们尝试一下这个功能(以protel为例):首先打开一个PCB图;选择菜单“Design-->Classes..”跳出图 1的画面。

这里我已经预先定好了几个C ,其中“All Nets”是protel 默认的类别,这个类别包含了所有的网络。

如果定义了布线规则,默认就是针对这个类别的。

现在我要为这个pcb增加一个表示CPU地址总线的类别“Address_bus”,按下图 1画面中的“Add”按键,在图 2的画面中输选择“A0~A19”,然后选择“>”把这些网络放置到右边的子窗口中。

如图 3。

这样就建立好了一个新的pcb 网络类别。

用同样的办法,再建立“power”、“data_bus”等网络类别。

好了,我们为这些网络类别分别指定布线策略吧,首先我们为电源类指定布线策略。

按下图 4画面中的“Add”按键,增加一个策略。

如图 5所示,“Filter Kind”选择“Net Class”, “Net Class”选择“POWER”,然后可以分别设定它的线宽等参数,你还可以为POWER类增加一个靠近限制的规则(由于我这个电路板是4层板,我这个工程就不设置靠近规则了)。

由于我的这个电路板是一个高速的嵌入式系统,CPU外部总线频率大约200MHz。

PADS2007使用手记

PADS2007使用手记从昨天开始正式使用PADS2007的,感觉还是很不错,改掉了以前的几个BUG了,如2005中POWERLOGIC的出BOM会有问题。

到SP2 POWERLOGIC中的相同网络不能用黑体字来显示出来,都给使用带来了很大的不便,看了2007的这个版本已经处理了这两个BUG,又重新回到稳定的状态!目前正在使用中看有没有什么新的问题。

已经用这个软件做了几个PCB了,现将所遇到的情况与大家交流一下!新增的功能:1、当你在非正常模式下操作,会弹出框蚋闾崾荆幌笠郧埃缭谧呦咦刺≡ 挥蟹从Γ衷诰陀辛颂崾究颍梢匀米约褐雷约捍砦笤谀睦铮?/p>2、POWERPCB中增加PIN显示功能,这一点和PROTEL差不多了,便于方便查询。

3、双击位号,可以对其进行修改了,这在2004以前的时候是有的,但是以后就没有了,现在又恢复了!不好的功能及退步的功能“1、在同步的时候,如果对POWRERPCB进行多次铺铜处理会出现退出的现象。

经过又多次测试,有时候不同步的时候,进行铺铜,也会出现错误;2、在同步的时候在PCB中进行了选择,然后连带进主LOGIC后会出现错误退出现象;3、在LAYOUT的时候,如果想对元件进行重新编排脚的时候,RENAME NUMBER显示灰色,要你去对元件进行修改才可以的!这一点极其不方便;4、现在版本的LIB文件,在PADS2007中不支持直接打开,必须通过导入导出才能库的使用,很不方便!5、这一次又多了个2013的问题,这是以前很少遇到的问题,提示说数据库有问题,主要出现在两个PCB文件拷贝封装的时候。

6、前些天又发现了一个致命的问题,竟然出现用PAGE UP和PAGE DOWN出现不能放大和缩小的问题,真是晕呀,但是用放大缩小键却可以的!到目前还没有找到解决的办法!7、也是个很严重的问题,就是你制定的走线规则会发生变化,不知道在什么情况下,他就会回到原来默认的状态下。

真是太奇怪了!8、从这个版本的PCB再导回到原来的版本通过ASC文件,有可能会出现错误的情况!经过这一系列的问题,最终我还是选择回到2005SP2的版本上去,虽然这个POWERLOGIC有点缺陷,但两者相比还是没有这么多的问题!所以最终还是没有选择PADS2007!不过还算好这个软件和以前的还是可以同时并存的,我现在装有三个版本的软件在电脑上,主要还是使用PADS2005SP2.这一点还是很不错的!前些日子一朋友出现安癙ADS的时候出现DEMO的现象,但是他的安装过程也是正确的,但是就是不行,于是我就分析了可能存在问题1、没有正确的生成LIENCE,2、可能出现了更换网卡等设备哪怕更换插口也不行。

制作印制电路板PPT课件

2、电源/接地线加宽 3、文字标注的调整 4、增加电源和接地

为了获得完整的PCB电路图,必须加上电源和接地。 ✓添加电源和接地焊盘 ✓手动连接导线

6.6.4 补泪滴的应用

课堂演示

6.1.7 放置标注信息

✓字符串:String ✓坐标:Coordinate ✓尺寸标注:Dimension ✓圆弧:Arc

6.2 规划电路板和电气定义

所谓规划规划电路板和电气定义,就是根据电路 的规模以及公司或制造商的要求,具体确定所需制作 电路板的物理外形尺寸和电气边界。电路板规划的原 则是在满足公司或制造商的要求的前提下,尽量美观 且便于后面的布线工作。

1、拆线:Tool/Un-Route

ALL 拆除所有布线,进行手工调整。 Net 拆除所选布线网络,进行手动调整。 Component 拆除与所选的元件相连的线,进行手动调整。 Connection 拆除所选的一条布线,进行手工调整。

下面以 Un-Route /Connection 命令为例来介绍调整布线的 操作步骤。如:将U3-2和L1-2之间、U3-4和L2-2之间的连线 进行手工调整。

图标,手动走线

课堂演示

6.8 PCB板的3D显示

执行View—Board in 3D

3D显示可以 清晰显示PCB 板的3维效果

当3D显示PCB板不尽理想时,可以对布局和布线做微调 以达到设计者的要求。

6.9 生成PCB网络报表

打开网络表管理器—生成PCB网络表—比较原理图 网络表和PCB网络表

6.1.2 放置焊盘

执行菜单命令【Place】/【Pad】

印刷电路板(PCB)供电网络 (PDN)设计方法

2009 Altera Corporation

AN 574

稳压器模块 (VRM) 就一级分析而言,您可以将 VRM 建模为一个串联电阻和电感,如图 5 所示。图 5 还绘制了其仿真 频率响应情况。 在约为 50KHz 的低频下,VRM 具有较低的阻抗并且能够对 FPGA 的瞬时电流要求响应。在更高频 率下,VRM 阻抗主要为电感,从而使其不能满足瞬时电流要求。您可以从 VRM 厂商那里获得等效 串联电阻 (ESR) 和等效串联电感 (ESL) 的值。 图 5、稳压器模块 (VRM) 示意图及频率响应

图 12 显示了三种情况的仿真波形: “理想 PCB”的 Z 曲线—谐振频率 F1 的紫色波形(A) “低 PCB 寄生”的 Z 曲线—谐振频率 F2 的绿色波形(B) “高 PCB 寄生”的 Z 曲线—谐振频率 F2 的橙色波形(C) 随着 PCB 电感的增加,首个谐振峰值的位置转移至左边(更低频率),同时峰值振幅也增加。 使用方程式 5,可以大致计算出这种频率变化。 方程式 5

AN 574

层电容 电源/接地夹层的分布电容大小取决于下列几个因素: 层长度 层宽度 介电常量 介电厚度 利用一个平板电容器方程式,您可以近似计算电容的大小,如方程式 3 所示。图 8 显示了电源/接地 夹层之间层电容的等价表征。 方程式 3

Protel99SE重要功能说明

原理图#把原理图部分内容复制成图片放EXCELE等软件编辑在电路图里选中要复制的部分,在EXCELE直接粘贴#快速查找元件Edit/Text Find或者Ctrl+F#原理图模板文件添加T ools/Preferences/schematic中Default Template File文件扩展名tab在Design Explorer 99 SE /System/Templates里面,把文件放里面就可以#自动放电气节点Tools/Preferences/schematic/options中auto-junction#原理图的光标形状栅格形状,移动长度等设置T ools/ Preferences/Graphical editing#原理图的栅格设置Design/Options/Grids选项中snap元件移动栅格visible可视栅格enable电气节电自动搜索#原理图标题栏Design/Options/Title block里面有两种图纸标题选项,取消选中将不显示标题栏。

#原理图更新PCB错误检查Design/Update PCB选Preview change/勾上Only show errors点Report,在生成的错误表里检查错误。

ToolS/Reset Error Markers可以清除错误#PCB里设定网格大小Design/Options/Sheet Options里#给元件自动编号Tools/Annotate.../Options/Annottate Options(All Psrts 对所有元件编号)/Advanced Options(设置自动编号数字范围)/Options/Annottate Options(Reset Designators取消元件标号,标号前先取消就从1开始标起)#设计图纸运行习惯参数设定Tools/Preferences.../Schematic/Options/Auto Junction (选中系统自动在T形加电气接点) /Enable In-Place Editing(选中鼠标可以在原理图中双击左键进行元件标识文本等修改)#常用绘图工具View/T oolbars/#图纸参数设定Design/或者双击图纸边缘#打印图纸File/Setup Printe...#打印原理图颜色加深File/Setup Printe/Color选Monochrome #电路图电气性能检查Tools/ERC/Setup(各种电气检查)/Options/Create repot file(检查后生成报告文件)/Add error markers(检查后在电路图放置错误标示)/Sheets to Netlist(检查范围/Active project(当前打开的工程)/Active sheet(当前打开的图纸)/Active sheet plus sub sheets(当前打开的图纸和子图)#生成元件库清单Reports/Bill of Material/BOM Wizard/Sheet/选Footprint和Description#生成网络表Design/Creat Netlist.../选输出文件类型Protel 选网络标识范围Sheet Symbol/Port Connections#打开绘图工具栏View/T oolbars/Customize在选项前勾上相应项就可以打开,双击可以设置单一图标工具显示#显示或者隐藏栅格View/Visible Grid#禁止琐定栅格,绘图任意移动View/Snap Grid#Protel99 SE电气规则检查步骤步骤1:设置电气规则检查选项。

计算机辅助设计(Protel平台)绘图员级考试大纲及操作细则

[放置]

[零件]

;完成元件放置及属性编辑

注:有关元件 Protel 名称见下表。

元件中文名

PROTEL 名

器件库

元件中文名 PROTEL 名

电阻

RES1

d_device.lib

三极管

NPN

可变电阻

PNP

电容

CAP

场效应管

JFET-P

电解电容

ELECTRO2

JFET-N

可变电容

CAPVAR

电感

AIRIND2

[文件 Files]

[新建 New]

[另存为] ; 路径选择考生文件夹下

[命名] ; 正确的文件名

;自动执行“元器件库编辑 Libedit”

2、在库文件中新元件的建立

方法一:利用绘图工具创建新零件

1)【元件】 【新建元件】 【重命名】; 2)绘制边框:

(1)【编辑】 【跳至】 【原点】 (2)【放置】 【矩形及相关图形】 3)放管脚

C:\Protel2004 简体中文版

目录中有 Sch(电路原理图设计)、 Pfw(印制板图设计)、 Libedit(元器件库编辑),分

别执行这三个文件即可。

目录中包含以下 3 个文件夹:

GB:国标。

Library :该文件夹下有原理图元件库文件、PCB 元件封装库文件等。

PCB-Exam:Protel2002 自带设计实例。

二极管

DIODE

磁芯电感

INDUCTOR2

发光二极管

LED

变压器

TRANS1

稳压二极管

ZENER2

晶体振荡器 CRYSTAL

整流桥

BRIDGE1

指示灯

PCB版图设计(Ultiboard)

PCB版图设计任何电子设计的最终物理实现都必须有PCB板,它既是各类电路元器件的承载体,又起到保障电气连接的作用,现代电子设计人员学习PCB板制意义十分重大。

Ultiboard 9的功能与应用第一节Ultiboard 9概论一、Ultiboard 9的特点电路设计的主要物理实现形式之一就是印制电路板(PCB:Printed Circuit Board),它既是各类电路元器件的承载体,又起到保障电气连接的作用。

对于研发电子设备或电子电路系统的设计者而言,无论使用集成度多么高的IC器件,总是不能回避PCB 设计环节。

对比较复杂的电路系统进行PCB设计时,如果采用纯粹的手工布线,需要投入比其电气原理图设计更多的精力和时间,而且难以做到设计无误,不但浪费了时间,还会增加研制开发费用。

显然,设计者只有具备和掌握出色的PCB设计工具,才能适应日益激烈的电子技术市场竞争的需要。

EDA开发软件Electronics Workbench是加拿大公司Interactive Image Technologies Ltd.于1988推出的一个很有特色的EDA工具,自发布以来,已经有35个国家、10种语言的人在使用这种工具。

它(Electronics Workbench)与其他同类工具相比,不但设计功能比较完善,而且操作界面十分友好、形象,易于使用掌握。

电子设计工具平台Electronics Workbench主要包括Multisim和Ultiboard两个基本工具模块。

Ultiboard是Electronics Workbench中用于PCB设计的后端工具模块,它可以直接接收来自Multisim模块输出的前端设计信息,并按照确定的设计规则进行PCB 的自动化设计。

为了达到良好的PCB自动布线效果,通常还在系统中附带一个称为Ultiroute的自动布线模块,并采用基于网格的“拆线—重试”布线算法进行自动布线。

Ultiboard的设计结果可以生成光绘机需要的Gerber格式板图设计文件。

AltiumDesigner10(AD10)的使用要点总结

AltiumDesigner10(AD10)的使⽤要点总结AD10使⽤要点1.板框画在机械层(放置-⾛线),先设置原点(编辑-原点-设置)。

但是⾏业内很多是放置在Keep OutLayer,多数板⼚也是把Keep Out Layer作为边框直接裁掉。

2.布线外围框画在Keep Out Layer(放置-⾛线)。

画完板把它删掉,以免做板被裁掉。

3.固定孔画在机械层(放置-圆环)。

但是和板框⼀样,⾏业内很多是放置在Keep Out Layer。

但⽤3D看时看不到孔,做出板时是有孔的。

----软件缺陷如需3D效果下看到孔,直接放置⼀个焊盘,层为Multi,如外形尺⼨为,把通孔尺⼨改成更⼤如。

4.固定孔也可以在顶层放置⼀个过孔,将孔尺⼨和孔直径都改成⼀样⼤⼩,改属性始层为Top Layer,改属性末层为Bottom Layer。

这样3D下可以看见孔,但是孔为⾦属过孔。

5.在PCB编辑模式下,按3键转换为3D预览模式,按2键转换为2D预览模式。

3D预览模式下按住Ctrl然后滚动滚轮可以缩放;3D预览模式下按住Shift然后按住右键拖动⿏标可以旋转。

6.画PCB封装,先放置⼀个焊盘,然后编辑-设置参考-定位,可以将焊盘的坐标都归零,然后再放第⼆个焊盘并调整其坐标值,就可以准确定位焊盘距离。

7.画PCB封装,放置焊盘—双击焊盘,可设置焊盘形状(外形),孔⼤⼩(贴⽚就将通孔尺⼨改为0),标识,层(贴⽚就设置层为Top Layer,插件就设置层为Multi Layer,单层板插件也设置层为Multi Layer)。

顶层圆底层⽅的焊盘,将尺⼨和外形由选项(简单)改为(顶层-中间层-底层),并修改顶层或底层的外形。

按3键进⾏3D预览。

8.PCB板⼦按1:1⽐例打出来。

⽂件-页⾯设计9.放置⽹络标号必须要有电⽓连接,也就是放置时必须要出现红叉。

10. 覆铜需要与焊盘完全融合的设置⽅法,将覆铜时候焊盘设置成全部连接,⽽⾮热焊盘连接,规则设置如下所⽰:设计---规则---plane---polygon connect style---polygonconnect 关联类型选择下图11.对于⼀些可以忽略的错误,可以点击⼯具--复位错误标志,就可以消除了,但是当你再动这两个元件时⼜会显⽰绿⾊,所以最好等元件布局OK了再进⾏此操作。

pcb网络表转换器

pcb网络表转换器(Omninet for Windows)使用方法1.打开PCB图,选择菜单File-Report,文件类型选PowerPCB V3.0 Format Netlist ,将文件另存为Pwrdemoa.ASC。

2.启动程序Omninet for Windows,输入文件类型(Type)选Pads-PowerPCB,Input File 1里用Browse指定网络表文件的位置。

输出文件类型(Type)选EDIF。

Output File 1指定输出文件的文件名和路径。

然后点击Run(跑动的小人)。

系统弹出一个输出窗口,点击Accept Data。

完成后点击“确定”,再点击“Done”关闭输出窗口。

退出Omninet for Windows。

3.修改EDIF网表文件,非常麻烦且容易出错的部分。

下面是网络表的一部分;(edif (rename C_COLON_BSLTEMP_BSLPWRDEMOA_DOTEDF"C:\TEMP\PWRDEMOA.EDF")(edifVersion 2 0 0)(edifLevel 0)(keywordMap (keywordLevel 0))(library MAIN_LIB(edifLevel 0)(technology(numberDefinition(scale 1 (e 1 -6)(unit distance))))(cell &6167 (cellType generic)(view NetlistView (viewType netlist)(interface)))(cell &6167 (cellType generic)(view NetlistView (viewType netlist)(interface(port &1 )(port &2 )(port &3 )(port &4 )(port &5 )(port &6 )(port &7 )(port &10 )(port &13 )(port &14 )(port &15 )(port &16 )(port &17 )(port &18 )(port &19 )(port &20 ))))(cell &68HC68R2 (cellType generic)(view NetlistView (viewType netlist)(interface(port &1 )(port &2 )(port &3 )(port &4 )(port &5 )(port &6 )(port &7 )(port &8 ))))(cell &68HC68R2 (cellType generic)(view NetlistView (viewType netlist)(interface)))(cell (rename NE555_MINUSSO "NE555-SO") (cellType generic)(view NetlistView (viewType netlist)(interface)))(cell (rename R1_FSL4W "R1/4W") (cellType generic)(view NetlistView (viewType netlist)(interface)))(cell (rename R1_FSL4W "R1/4W") (cellType generic)(view NetlistView (viewType netlist)(interface(port &1 )(port &2 ))))检查一下有(cell…..标记的行,特别要注意红色字体部分,其Interface部分为空,在这个cell标记的前面或后面又有一个cell行,其Interface部分包含有(port &1)(port & 2)...等内容。

Altium Designer-使用总结

一、软件优化设置1.打开PCB,使用快捷键T+P,如下图设置:2.取消HTM文件3.禁止检查4.单层显示无阴影5.笔记本布线换层台式机有小键盘,可以*-+来换层,笔记本该如何换层呢,有两种方法。

第一种方法:CTRL+SHIFT+鼠标滑轮第二种方法:如,将*快捷键改为=首先打开一个PCB文档,之后依次选择DXP>>Customize,在Command中修改以下几个命令的快捷方式:Next Layer:切换到下一层。

默认快捷方式是小键盘的+号(Plus)Next Signal Layer:切换到下一可布线的层。

默认快捷方式是小键盘的*号(Multiply)Prev Layer:切换到上一层。

默认快捷方式是小键盘的-号(Minus)6、自动删除重复走线7、添加美式键盘我用的是win10系统,按shift+space键切换布线模式总是切换不了,是因为搜狗输入法全角和半角切换快捷键冲突了所以需要安装美式键盘。

添加流程很简单:控制面板->>添加语言->>添加语言选择英语->>英语(美国),双击,添加完成。

当布线的时候切换成美式键盘输入法即可。

需要注意的地方:当切换布线模式的时候,可能可能遇到无法画弧线的情况,看看你是否选择了Restrict to90/458、设置中文DXP->>Preferences->>System->>General->>如下图选中三个选项,点击Apply,重启AD,显示中文。

不过不建议使用中文,如果连这点英文都不懂,英文芯片手册看不了,不适合做硬件了。

OK,软件优化设置基本完成!、认识AD16,熟悉各个常用选项推荐一篇文章:Altium_Designer(protel_DXP)英文菜单汉化对应表表介绍的不错,我下面只介绍常用的几个。

1、Place放置2、选择网络信号3、设置参考点4、显示或隐藏信号线网络连接5、布线P+T时,按~快捷键V+S可将该界面隐藏/显示各个界面的介绍6.1、Libraries 介绍元件库目录6.2、Projects介绍PCB工程目录6.3、PCB介绍画差分线时用到PCB网络6.4、PCB Filter介绍选中Object的类,可将该类在PCB中选中,使用F11可以多元件操作DRC时,显示PCB违反规则目录PCB Inspector可以弹出设置过孔、信号线、器件、丝印等属性的界面使用方法:A、单器件:选中一个器件,按F11弹出B、多器件:通过快捷键SHIFT+F,选中一个器件,出现Find Similar Objects界面该界面有很多选项,如所在层、封装、锁定、显示名等,可根据这些选项刷选到你需要的器件。

PCB设计仿真工具-HyperLynx入门指南

HyperLynx入门指南目录使用叠层编辑器进行阻抗计算使用LineSim进行布线前仿真LineSim串扰分析BoardSim的交互式仿真BoardSim端接向导BoardSim串扰分析BoardSim板级分析BoardSim差分和GHz仿真直观的IBIS编辑器建立一个Databook模型使用叠层编辑器进行阻抗计算在BoardSim和 LineSim中均包括一个功能强大的叠层编辑器,使用它可以很简单地对您的PCB进行叠层设计和修改,以及对每个信号层进行特性阻抗的计算,以便您对信号反射和信号完整性的控制。

特性阻抗传输线和负载阻抗的匹配,以及选择合适的端接器件的值对信号完整性是很重要的。

BoardSim和LineSim的叠层编辑器正是对其控制的开始。

首先请记住特性阻抗Z0的计算等式:Z0 = √(L/C)增大电容可以通过一下方式:加宽走线减小信号层和参考层的距离增加介电常数这样就使等式的分母变大,也就降低的特性阻抗Z0。

当然,减小电容就使Z0增大。

而反射系数的计算等式如下:Refl. % = (ZL - Z0) / (ZL + Z0)当我们进行PCB设计时,对那些驱动端上升或下降时间小于等于5ns的单端信号线必须进行端接。

这个功能能够帮助我们选择合适的端接值,以便我们知道这个端接值ZL(例如:终端端接),以便我们可以控制信号反射和信号完整性,或者为了达到理想的目标特性阻抗值,调整优化我们的叠层结构。

建立一个新的LineSim原理图点击工具条上的图标“New LineSim Schematic”,便可以建立一个新的LineSim原理图,或者通过菜单选择File -> New LineSim File…。

选择工具条上绿色的叠层图标“Edit PCB Stackup”,或者通过菜单的Edit -> Stackup…选项,您将看到一个6层板的叠层结构图以及各层和介质层的参数。

双击您需要编辑的项目表格,例如介质层厚度、线宽等等,根据需要编辑顶层、底层和各个走线层、参考层以及介质层的参数,您可以分别选择Basic、Dielectric、Metal、Z0 Planning、Custom View进行各个项目的编辑。

PADS常用设置方法

二. PCB LAYOUT规则设置

Options参数设置-Design

1.一原点为参考点移动 2.以光标位置为参考点移动 3.以中心点为参考点移动 推荐:选择’3’. 1.移动过程中执行鼠线最短 2.移动结束后执行鼠线最短 3.不进行最短计算 也可以使用Ctrl+m执行最短 化操作 元件在布局时: Automatic:自动分 开不会重叠. Prompt:元件重叠 时提示 Off: 关闭排挤功能 1.保持信号线和元 件名称;2.包含没 有连接的走线;3. 在拐角处添加倒角 Diagonal:45度倒角 Arc:圆弧倒角 Auto Miter:画线过 程中自动添加倒角

1.线宽 2.最少连接线数目 3.Pad 形状选择 Round圆形/Square方形 /Rectangle长方形/Ooal 椭圆

正交连接 对角连接 填满连接 不连接

使走线元件的焊盘成热焊盘 显示平面层/分割的花孔指示标志 自动移除孤立的铜皮 自动移除违背规则的花孔连接线

二. PCB LAYOUT规则设置

一.PADS LAYOUT的使用

常用快捷键

Ctrl+A Ctrl+B Ctrl+C Ctrl+D Ctrl+E Ctrl+F Ctrl+G Ctrl+I Ctrl+K Ctrl+L Ctrl+M Ctrl+Q Ctrl+R Ctrl+S Ctrl+V Ctrl+X Ctrl+Y Ctrl+Z Ctrl+Alt+C Ctrl+Alt+D 置窗口 Ctrl+Alt+G 置窗口 Ctrl+Alt+J 选择全部 以板框为界整体显示当前设计 复制 刷新 移动 翻转 建立结合 任意角度旋转 建立组 排列元件 长度最短化 查询与修改 以45°角为单位旋转 存盘 粘贴 剪切 扩展 取消操作 显示颜色设置 打开Setup/Preference下的Design设 打开Setup/Preference下的Global 设 增加跳线 F1 F2 F3 F4 F5 F6 F7 F8 F9 F10 打开在线帮助 增加走线 动态走线模式 锁定层对 选择管肢对 选择网络 选择半自动走线 打开或关闭鼠标移动压缩 锁定绝对与相对协调 结束记录

Altium Designer 15 常用快捷键

Altium Designer 15 常用快捷键1.Altium Designer 15P+N 添加netC+C 项目编译P+L 布线快捷键U+选NET,点布线删除NET之间的布线L 调出BORDLAYERSP+D+L 量尺寸Ctrl+拖拽S CH下连线跟着器件走Shift+拖拽SCH下复制元器件Shift +A 调用蛇形走线,再按1和2改变转角,按3和4改变间距,按,和。

改变宽窄Ctrl+M 测量快捷,Q是公尺和英尺切换空格键在交互布线的过程中,切换布线方向。

这很常用主键盘上的1 在交互布线的过程中,切换布线方法(设定每次单击鼠标布1段线还是2段线)。

主键盘上的2 在交互布线的过程中,添加一个过孔,但不换层。

Shift+S 切换单层显示和多层显示Q 在公制和英制之间切换。

Shift+空格键在交互布线的过程中,切换布线形状J,L 定位到指定的坐标的位置。

这时要注意确认左下角的坐标值,如果定位不准,可以放大视图并重新定位,如果还是不准,则需要修改栅格吸附尺寸。

(定位坐标应该为吸附尺寸的整数倍)J,C 定位到指定的元件处。

在弹出的对话框内输入该元件的编号。

R,M 测量任意两点间的距离R,P 测量两个元素之间的距离。

G,G 设定栅格吸附尺寸O,B 设置PCB属性O,P 设置PCB相关参数O,M 设置PCB层的显示与否D,K 打开PCB层管理器E,O,S 设置PCB原点E,F,L 设置PCB元件(封装)的元件参考点。

(仅用于PCB元件库)元件参考点的作用:假设将某元件放置到PCB中,该元件在PCB中的位置(X、Y坐标)就是该元件的参考点的位置,当在PCB中放置或移动该元件时,鼠标指针将与元件参考点对齐。

如果在制作元件时元件参考点设置得离元件主体太远,则在PCB中移动该元件时,鼠标指针也离该元件太远,不利于操作。

一般可以将元件的中心或某个焊盘的中心设置为元件参考点。

E,F,C 将PCB元件的中心设置为元件参考点。

PCB布板

电源布板步骤一、电路版设计的先期工作1、利用原理图设计工具绘制原理图,并且生成对应的网络表.当然,有些特殊情况下,如电路版比较简单,已经有了网络表等情况下也可以不进行原理图的设计,直接进入PCB设计系统,在PCB设计系统中,可以直接取用零件封装,人工生成网络表.2、手工更改网络表将一些元件的固定引脚等原理图上没有的焊盘定义到与它相通的网络上,没任何物理连接的可定义到地或保护地等.将一些原理图和PCB封装库中引脚名称不一致的器件引脚名称改成和PCB封装库中的一致,特别是二、三极管等.二、画出自己定义的非标准器件的封装库建议将自己所画的器件都放入一个自己建立的PCB 库专用设计文件.三、设置PCB设计环境和绘制印刷电路的版框含中间的镂空等1、进入PCB系统后的第一步就是设置PCB设计环境,包括设置格点大小和类型,光标类型,版层参数,布线参数等等.大多数参数都可以用系统默认值,而且这些参数经过设置之后,符合个人的习惯,以后无须再去修改.2、规划电路版,主要是确定电路版的边框,包括电路版的尺寸大小等等.在需要放置固定孔的地方放上适当大小的焊盘.对于3mm 的螺丝可用6.5~8mm 的外径和3.2~3.5mm 内径的焊盘对于标准板可从其它板或PCB izard 中调入.注意:在绘制电路版地边框前,一定要将当前层设置成Keep Out层,即禁止布线层.四、打开所有要用到的PCB 库文件后,调入网络表文件和修改零件封装这一步是非常重要的一个环节,网络表是PCB自动布线的灵魂,也是原理图设计与印象电路版设计的接口,只有将网络表装入后,才能进行电路版的布线.在原理图设计的过程中,ERC检查不会涉及到零件的封装问题.因此,原理图设计时,零件的封装可能被遗忘,在引进网络表时可以根据设计情况来修改或补充零件的封装.当然,可以直接在PCB内人工生成网络表,并且指定零件封装.五、布置零件封装的位置,也称零件布局Protel99可以进行自动布局,也可以进行手动布局.如果进行自动布局,运行"Tools"下面的"Auto Place",用这个命令,你需要有足够的耐心.布线的关键是布局,多数设计者采用手动布局的形式.用鼠标选中一个元件,按住鼠标左键不放,拖住这个元件到达目的地,放开左键,将该元件固定.Protel99在布局方面新增加了一些技巧.新的交互式布局选项包含自动选择和自动对齐.使用自动选择方式可以很快地收集相似封装的元件,然后旋转、展开和整理成组,就可以移动到板上所需位置上了.当简易的布局完成后,使用自动对齐方式整齐地展开或缩紧一组封装相似的元件.提示:在自动选择时,使用Shift+X或Y和Ctrl+X或Y可展开和缩紧选定组件的X、Y方向. 注意:零件布局,应当从机械结构散热、电磁干扰、将来布线的方便性等方面综合考虑.先布置与机械尺寸有关的器件,并锁定这些器件,然后是大的占位置的器件和电路的核心元件,再是外围的小元件.六、根据情况再作适当调整然后将全部器件锁定假如板上空间允许则可在板上放上一些类似于实验板的布线区.对于大板子,应在中间多加固定螺丝孔.板上有重的器件或较大的接插件等受力器件边上也应加固定螺丝孔,有需要的话可在适当位置放上一些测试用焊盘,最好在原理图中就加上.将过小的焊盘过孔改大,将所有固定螺丝孔焊盘的网络定义到地或保护地等.放好后用VIEW3D 功能察看一下实际效果,存盘.七、布线规则设置布线规则是设置布线的各个规范(象使用层面、各组线宽、过孔间距、布线的拓朴结构等部分规则,可通过Design-Rules 的Menu 处从其它板导出后,再导入这块板)这个步骤不必每次都要设置,按个人的习惯,设定一次就可以.选Design-Rules 一般需要重新设置以下几点:1、安全间距(Routing标签的Clearance Constraint)它规定了板上不同网络的走线焊盘过孔等之间必须保持的距离.一般板子可设为0.254mm,较空的板子可设为0.3mm,较密的贴片板子可设为0.2-0.22mm,极少数印板加工厂家的生产能力在0.1-0.15mm,假如能征得他们同意你就能设成此值.0.1mm 以下是绝对禁止的.2、走线层面和方向(Routing标签的Routing Layers)此处可设置使用的走线层和每层的主要走线方向.请注意贴片的单面板只用顶层,直插型的单面板只用底层,但是多层板的电源层不是在这里设置的(可以在Design-Layer Stack Manager 中,点顶层或底层后,用Add Plane 添加,用鼠标左键双击后设置,点中本层后用Delete 删除),机械层也不是在这里设置的(可以在Design-Mechanical Layer 中选择所要用到的机械层,并选择是否可视和是否同时在单层显示模式下显示).机械层1 一般用于画板子的边框;机械层3 一般用于画板子上的挡条等机械结构件;机械层4 一般用于画标尺和注释等,具体可自己用PCB Wizard 中导出一个PCAT结构的板子看一下3、过孔形状(Routing标签的Routing Via Style)它规定了手工和自动布线时自动产生的过孔的内、外径,均分为最小、最大和首选值,其中首选值是最重要的,下同.4、走线线宽(Routing标签的Width Constraint)它规定了手工和自动布线时走线的宽度.整个板范围的首选项一般取0.2-0.6mm,另添加一些网络或网络组(Net Class)的线宽设置,如地线、+5 伏电源线、交流电源输入线、功率输出线和电源组等.网络组可以事先在Design-Netlist Manager中定义好,地线一般可选1mm 宽度,各种电源线一般可选0.5-1mm 宽度,印板上线宽和电流的关系大约是每毫米线宽允许通过1安培的电流,具体可参看有关资料.当线径首选值太大使得SMD 焊盘在自动布线无法走通时,它会在进入到SMD 焊盘处自动缩小成最小宽度和焊盘的宽度之间的一段走线,其中Board 为对整个板的线宽约束,它的优先级最低,即布线时首先满足网络和网络组等的线宽约束条件.下图为一个实例5、敷铜连接形状的设置(Manufacturing标签的Polygon Connect Style)建议用Relief Connect 方式导线宽度Conductor Width 取0.3-0.5mm 4 根导线45 或90 度. 其余各项一般可用它原先的缺省值,而象布线的拓朴结构、电源层的间距和连接形状匹配的网络长度等项可根据需要设置.选Tools-Preferences,其中Options 栏的Interactive Routing 处选Push Obstacle (遇到不同网络的走线时推挤其它的走线,Ignore Obstacle为穿过,Avoid Obstacle 为拦断)模式并选中Automatically Remove (自动删除多余的走线).Defaults 栏的Track 和Via 等也可改一下,一般不必去动它们.在不希望有走线的区域内放置FILL 填充层,如散热器和卧放的两脚晶振下方所在布线层,要上锡的在Top 或Bottom Solder 相应处放FILL.布线规则设置也是印刷电路版设计的关键之一,需要丰富的实践经验.八、自动布线和手工调整1、点击菜单命令Auto Route/Setup 对自动布线功能进行设置选中除了Add Testpoints 以外的所有项,特别是选中其中的Lock All Pre-Route 选项,Routing Grid 可选1mil 等.自动布线开始前PROTEL 会给你一个推荐值可不去理它或改为它的推荐值,此值越小板越容易100%布通,但布线难度和所花时间越大.2、点击菜单命令Auto Route/All 开始自动布线假如不能完全布通则可手工继续完成或UNDO 一次(千万不要用撤消全部布线功能,它会删除所有的预布线和自由焊盘、过孔)后调整一下布局或布线规则,再重新布线.完成后做一次DRC,有错则改正.布局和布线过程中,若发现原理图有错则应及时更新原理图和网络表,手工更改网络表(同第一步),并重装网络表后再布.3、对布线进行手工初步调整需加粗的地线、电源线、功率输出线等加粗,某几根绕得太多的线重布一下,消除部分不必要的过孔,再次用VIEW3D 功能察看实际效果.手工调整中可选Tools-Density Map 查看布线密度,红色为最密,黄色次之,绿色为较松,看完后可按键盘上的End 键刷新屏幕.红色部分一般应将走线调整得松一些,直到变成黄色或绿色.九、切换到单层显示模式下(点击菜单命令Tools/Preferences,选中对话框中Display栏的Single Layer Mode)将每个布线层的线拉整齐和美观.手工调整时应经常做DRC,因为有时候有些线会断开而你可能会从它断开处中间走上好几根线,快完成时可将每个布线层单独打印出来,以方便改线时参考,其间也要经常用3D显示和密度图功能查看.最后取消单层显示模式,存盘.十、如果器件需要重新标注可点击菜单命令Tools/Re-Annotate 并选择好方向后,按OK钮. 并回原理图中选Tools-Back Annotate 并选择好新生成的那个*.WAS 文件后,按OK 钮.原理图中有些标号应重新拖放以求美观,全部调完并DRC 通过后,拖放所有丝印层的字符到合适位置.注意字符尽量不要放在元件下面或过孔焊盘上面.对于过大的字符可适当缩小,DrillDrawing 层可按需放上一些坐标(Place-Coordinate)和尺寸((Place-Dimension).最后再放上印板名称、设计版本号、公司名称、文件首次加工日期、印板文件名、文件加工编号等信息(请参见第五步图中所示).并可用第三方提供的程序来加上图形和中文注释如BMP2PCB.EXE 和宏势公司ROTEL99 和PROTEL99SE 专用PCB 汉字输入程序包中的FONT.EXE 等.十一、对所有过孔和焊盘补泪滴补泪滴可增加它们的牢度,但会使板上的线变得较难看.顺序按下键盘的S 和A 键(全选),再选择Tools-Teardrops,选中General 栏的前三个,并选Add 和Track 模式,如果你不需要把最终文件转为PROTEL 的DOS 版格式文件的话也可用其它模式,后按OK 钮.完成后顺序按下键盘的X 和A 键(全部不选中).对于贴片和单面板一定要加.十二、放置覆铜区将设计规则里的安全间距暂时改为0.5-1mm 并清除错误标记,选Place-Polygon Plane 在各布线层放置地线网络的覆铜(尽量用八角形,而不是用圆弧来包裹焊盘.最终要转成DOS 格式文件的话,一定要选择用八角形).下图即为一个在顶层放置覆铜的设置举例:设置完成后,再按OK 扭,画出需覆铜区域的边框,最后一条边可不画,直接按鼠标右键就可开始覆铜.它缺省认为你的起点和终点之间始终用一条直线相连,电路频率较高时可选Grid Size 比Track Width 大,覆出网格线.相应放置其余几个布线层的覆铜,观察某一层上较大面积没有覆铜的地方,在其它层有覆铜处放一个过孔,双击覆铜区域内任一点并选择一个覆铜后,直接点OK,再点Yes 便可更新这个覆铜.几个覆铜多次反复几次直到每个覆铜层都较满为止.将设计规则里的安全间距改回原值. 十三、最后再做一次DRC选择其中Clearance Constraints Max/Min Width Constraints Short Circuit Constraints 和Un-Routed Nets Constraints 这几项,按Run DRC 钮,有错则改正.全部正确后存盘.十四、对于支持PROTEL99SE 格式(PCB4.0)加工的厂家可在观看文档目录情况下,将这个文件导出为一个*.PCB 文件;对于支持PROTEL99 格式(PCB3.0)加工的厂家,可将文件另存为PCB 3.0 二进制文件,做DRC.通过后不存盘退出.在观看文档目录情况下,将这个文件导出为一个*.PCB 文件.由于目前很大一部分厂家只能做DOS 下的PROTEL AUTOTRAX 画的板子,所以以下这几步是产生一个DOS 版PCB 文件必不可少的:1、将所有机械层内容改到机械层1,在观看文档目录情况下,将网络表导出为*.NET 文件,在打开本PCB 文件观看的情况下,将PCB 导出为PROTEL PCB 2.8 ASCII FILE 格式的*.PCB 文件.2 、用PROTEL FOR WINDOWS PCB 2.8 打开PCB 文件,选择文件菜单中的另存为,并选择Autotrax 格式存成一个DOS 下可打开的文件.3、用DOS 下的PROTEL AUTOTRAX 打开这个文件.个别字符串可能要重新拖放或调整大小.上下放的全部两脚贴片元件可能会产生焊盘X-Y大小互换的情况,一个一个调整它们.大的四列贴片IC 也会全部焊盘X-Y 互换,只能自动调整一半后,手工一个一个改,请随时存盘,这个过程中很容易产生人为错误.PROTEL DOS 版可是没有UNDO 功能的.假如你先前布了覆铜并选择了用圆弧来包裹焊盘,那么现在所有的网络基本上都已相连了,手工一个一个删除和修改这些圆弧是非常累的,所以前面推荐大家一定要用八角形来包裹焊盘.这些都完成后,用前面导出的网络表作DRC Route 中的Separation Setup ,各项值应比WINDOWS 版下小一些,有错则改正,直到DRC 全部通过为止.也可直接生成GERBER 和钻孔文件交给厂家选File-CAM Manager 按Next>钮出来六个选项,Bom 为元器件清单表,DRC 为设计规则检查报告,Gerber 为光绘文件,NC Drill 为钻孔文件,Pick Place 为自动拾放文件,Test Points 为测试点报告.选择Gerber 后按提示一步步往下做.其中有些与生产工艺能力有关的参数需印板生产厂家提供.直到按下Finish 为止.在生成的Gerber Output 1 上按鼠标右键,选Insert NC Drill 加入钻孔文件,再按鼠标右键选Generate CAM Files 生成真正的输出文件,光绘文件可导出后用CAM350 打开并校验.注意电源层是负片输出的.十五、发Email 或拷盘给加工厂家,注明板材料和厚度(做一般板子时,厚度为1.6mm,特大型板可用2mm,射频用微带板等一般在0.8-1mm 左右,并应该给出板子的介电常数等指标)、数量、加工时需特别注意之处等.Email发出后两小时内打电话给厂家确认收到与否.十六、产生BOM 文件并导出后编辑成符合公司内部规定的格式.十七、将边框螺丝孔接插件等与机箱机械加工有关的部分(即先把其它不相关的部分选中后删除),导出为公制尺寸的AutoCAD R14 的DWG 格式文件给机械设计人员.二十一、整理和打印各种文档.如元器件清单、器件装配图(并应注上打印比例)、安装和接线说明等.技术过程PCB抄板的技术实现过程简单来说,就是先将要抄板的电路板进行扫描,记录详细的元器件位置,然后将元器件拆下来做成物料清单(BOM)并安排物料采购,空板则扫描成图片经抄板软件处理还原成pcb板图文件,然后再将PCB文件送制版厂制板,板子制成后将采购到的元器件焊接到制成的PCB板上,然后经过电路板测试和调试即可。

AltiumDesigner手动添加的测试点覆盖率查算-查检及添加

Altium Designer中手动添加的测试点覆盖率查算/查检/添加主要内容:1、手动添加测试点 1.1、新板设计直接添加;1.2、通过【PCB】面板逐个网络添加。

2、查算测试点的覆盖率 2.1、通过【PCB】+【PCB Filter】->【PCB List】面板查算覆盖率。

3、三步查漏补缺测试点 3.1、通过【PCB Filter】->【PCB List】->【PCB Filter】三步查检补添测试点。

1、手动添加测试点1.1、新板设计直接添加——在Bottomlayer中直接添加附带如图示【Testpoint Setting】:Fbrication☑/Assenbly☑属性的测试点,比较简捷。

注:单面板测试点加在底层可选择Bottomlayer或Multilayer(便于查看,双面板一般只加在底层),但在<Solder Mask Expansion>属性设置中应保留(默认值4mil)开窗,不能勾选“Force tenting”盖油处理:2.2、通过【PCB】面板逐个网络添加——打开【PCB】面板,筛选“Nets”类型左击<All Nets>在面板下拉表框中会出现当前项目PCB 所有网络列表/数量及当前选定网络的节点列表,新版设计是通过PCB面板网络列表逐个添加测试点速度慢但比较可靠,可以清楚无法添加测试点的网络:2、测试点的覆盖率查算①先在【PCB】面板中筛选“Nets”查看当前PCB文件所有网络:②在【PCB Filter】面板中选出测试点:③通过【PCB List】面板下的说明即可算出测试点的覆盖率为96%。

3、三步查检补添单面板测试点①在【PCB Filter】面板筛选窗输入筛选对象条件:“testpoint bottom”,左击【▶Apply】即可选出所有底层有效测试点,注意在查找前先确认【PCB List】面板标题栏下显示条件为“View all objects或selected objects Include all types objects”,如图选定测试点后切到【PCB List】面板。

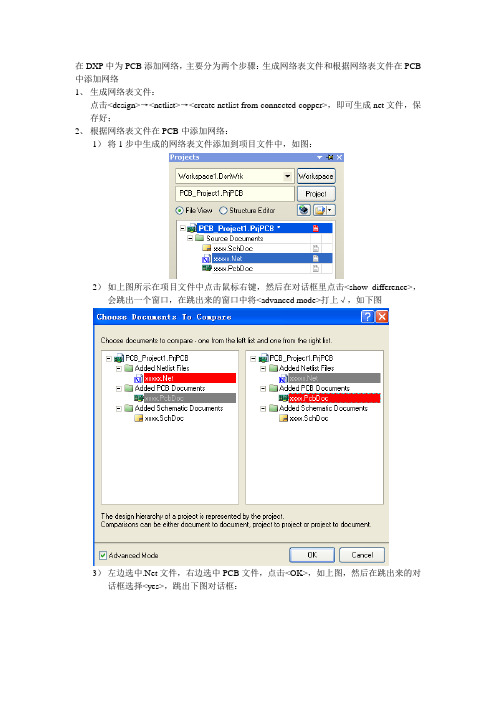

DXP中给PCB添加网络

在DXP中为PCB添加网络,主要分为两个步骤:生成网络表文件和根据网络表文件在PCB 中添加网络

1、生成网络表文件:

点击<design>→<netlist>→<create netlist from connected copper>,即可生成net文件,保存好;

2、根据网络表文件在PCB中添加网络:

1)将1步中生成的网络表文件添加到项目文件中,如图:

2)如上图所示在项目文件中点击鼠标右键,然后在对话框里点击<show difference>,会跳出一个窗口,在跳出来的窗口中将<advanced mode>打上√,如下图

3)左边选中.Net文件,右边选中PCB文件,点击<OK>,如上图,然后在跳出来的对话框选择<yes>,跳出下图对话框:

4)上图中可以看到左下角的按钮是灰色的,在上图空白处点击右键,选择< update all in>>PCB document >,左下角的按钮变为黑色,然后点击左下角的按钮,跳出如

下对话框:

5)点击<validate changes>,然后再点击<execute changes>,即可看到PCB中中出现了飞线;

6)最后一步<design>→<netlist>→<update free primitves from component pads>,飞线消

失了,网络添加成功,恭喜你。

PADS常用设置方法

Ctrl+A Ctrl+B Ctrl+C Ctrl+D Ctrl+E Ctrl+F Ctrl+G Ctrl+I Ctrl+K Ctrl+L Ctrl+M Ctrl+Q Ctrl+R Ctrl+S Ctrl+V Ctrl+X Ctrl+Y Ctrl+Z Ctrl+Alt+C Ctrl+Alt+D

置窗口 Ctrl+Alt+G

置窗口 Ctrl+Alt+J

选择全部 以板框为界整体显示当前设计 复制 刷新 移动 翻转 建立结合 任意角度旋转 建立组 排列元件 长度最短化 查询与修改 以45°角为单位旋转 存盘 粘贴 剪切 扩展 取消操作 显示颜色设置 打开Setup/Preference下的Design设

Options参数设置-Dimensioning(标注)

标注字符 所在层 标注线 所在层

(优先级比PCB工作环境中的当前活动 层设置高,所以必须在此设置标注层)

二. PCB LAYOUT规则设置

Options参数设置-Drafting(默认设置)

Normal:显示影线(显示为填 充后的整块铜皮). No hatch:不显示影线(显示 为填充区的轮廓框) See thr:显示所有影线的中 心线

显示状态

刷新页面

间距,会弹出[View Clearance]对话框, 可查找两个对象间

的最小间距

一.PADS LAYOUT的使用

[Setup](设置)菜单

Pad stacks(焊盘定义):打开[Query/Modify Pad Stacks]对 话框,建立,修改焊盘堆.

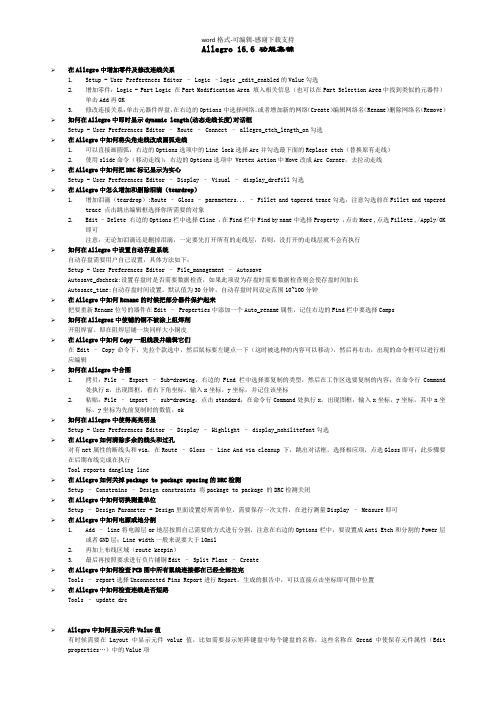

Allegro-16.6-功能集锦

Allegro 16.6 功能集锦➢在Allegro中增加零件及修改连线关系1.Setup - User Preferences Editor – Logic –logic _edit_enabled的Value勾选2.增加零件:Logic - Part Logic 在Part Modification Area 填入相关信息(也可以在Part Selection Area中找到类似的元器件)单击Add再OK3.修改连接关系:单击元器件焊盘,在右边的Options中选择网络。

或者增加新的网络(Create)编辑网络名(Rename)删除网络名(Remove)➢如何在Allegro中即时显示dynamic length(动态走线长度)对话框Setup - User Preferences Editor – Route – Connect – allegro_etch_length_on勾选➢在Allegro中如何将尖角走线改成圆弧走线1.可以直接画圆弧:右边的Options选项中的Line lock选择Arc并勾选最下面的Replace etch(替换原有走线)2.使用slide命令(移动走线):右边的Options选项中 Vertex Action中Move改成Arc Corner,去拉动走线➢在Allegro中如何把DRC标记显示为实心Setup - User Preferences Editor – Display – Visual – display_drcfill勾选➢在Allegro中怎么增加和删除泪滴(teardrop)1.增加泪滴(teardrop):Route – Gloss – parameters... – Fillet and tapered trace勾选,注意勾选前在Fillet and taperedtrace 点击跳出编辑框选择你所需要的对象2.Edit –Delete 右边的Options栏中选择Cline ,在Find栏中Find by name中选择Property ,点击More ,点选Fillet= ,/Apply/OK即可注意:无论加泪滴还是删掉泪滴,一定要先打开所有的走线层,否则,没打开的走线层就不会有执行➢如何在Allegro中设置自动存盘系统自动存盘需要用户自己设置,具体方法如下:Setup - User Preferences Editor – File_management – AutosaveAutosave_dbcheck:设置存盘时是否需要数据检查,如果此项设为存盘时需要数据检查则会使存盘时间加长Autosace_time:自动存盘时间设置。