C27E331_PLB_64B_8M中文资料

27C64资料

PACKAGE TYPES

DIP/SOIC

VPP • 1 A12 2

A7 3 A6 4 A5 5 A4 6 A3 7 A2 8 A1 9 A0 10 O0 11 O1 12 O2 13 VSS 14

27C64

28 VCC 27 PGM 26 NC 25 A8 24 A9 23 A11 22 OE 21 A10 20 CE 19 O7 18 O6 17 O5 16 O4 15 O3

Conditions

Input Voltages

all Logic "1"

VIH

2.0 VCC+1 V

Logic "0"

VIL

-0.5 0.8 V

Input Leakage

all

—

ILI

-10

10 µA VIN = 0 to VCC

Output Voltages

all Logic "1"

VOH

2.4

1.1 Maximum Ratings*

VCC and input voltages w.r.t. VSS ....... -0.6V to + 7.25V VPP voltage w.r.t. VSS during programming .......................................... -0.6V to +14V Voltage on A9 w.r.t. VSS ...................... -0.6V to +13.5V Output voltage w.r.t. VSS ............... -0.6V to VCC +1.0V Storage temperature .......................... -65˚C to +150˚C Ambient temp. with power applied ..... -65˚C to +125˚C

AT88SC0808C Atmel 密码型存储器数据手册说明书

AT88SC0808CAtmel CryptoMemory, 8-KbitSUMMARY DATASHEETFeatures • One of a family of nine devices with user memories from 1-Kbit to 256-Kbit •8-Kbit (1-Kbyte) EEPROM user memory• Eight 128-byte (1-Kbit) zones • Self-timed write cycle• Single byte or 16-byte page write mode • Programmable access rights for each zone• 2-Kbit configuration zone• 37-byte OTP area for user-defined codes• 160-byte area for user-defined keys and passwords •High security features• 64-bit mutual authentication protocol (under license of ELVA) • Encrypted checksum • Stream encryption• Four key sets for authentication and encryption • Eight sets of two 24-bit passwords • Anti-tearing function• Voltage and frequency monitor•Smart card features• ISO 7816 Class A (5V) or Class B (3V) operation• ISO 7816-3 asynchronous T = 0 protocol (Gemplus ®patent) * • Multiple zones, key sets and passwords for multi-application use • Synchronous 2-wire serial interface for faster device initialization * • Programmable 8-byte answer-to-reset register •ISO 7816-2 compliant modules•Embedded application features• Low voltage operation: 2.7V to 5.5V• Secure nonvolatile storage for sensitive system or user information • 2-wire serial interface• 1.0MHz compatibility for fast operation• Standard 8-lead plastic packages, green compliant (exceeds RoHS) •Same pinout as 2-wire Serial EEPROMs•High reliability• Endurance: 100,000 cycles • Data retention: 10 years • ESD protection: 4,000V min* Note: Modules available with either T=0 / 2-wire modes or 2-wire mode onlyThis is a summary document. The complete document is available on the Atmel website at .AT88SC0808C [SUMMARY DATASHEET]Atmel-2024MS-CryptoMem-AT88SC0808C-Datasheet-Summary_1220132Table 1. Pin AssignmentFigure 1.Pin Configuration1. DescriptionThe Atmel ®AT88SC0808C member of the Atmel CryptoMemory ®family is a high-performance secure memory providing 8-Kbits of user memory with advanced security and cryptographic features built in. The user memory is divided into eight 128-byte zones, each of which may be individually set with different security access rights or effectively combined together to provide space for one to eight data files.1.1 Smart Card ApplicationsThe AT88SC0808C provides high security, low cost, and ease of implementation without the need for a microprocessor operating system. The embedded cryptographic engine provides for dynamic and symmetric mutual authentication between the device and host, as well as performing stream encryption for all data and passwords exchanged between the device and host. Up to four unique key sets may be used for these operations. The AT88SC0808C offers the ability to communicate with virtually any smart card reader using the asynchronous T = 0 protocol (Gemplus Patent) defined in ISO 7816-3.1.2 Embedded ApplicationsThrough dynamic and symmetric mutual authentication, data encryption, and the use of encrypted checksums, theAT88SC0808C provides a secure place for storage of sensitive information within a system. With its tamper detection circuits, this information remains safe even under attack. A 2-wire serial interface running at 1.0MHz is used for fast and efficientcommunications with up to 15 devices that may be individually addressed. The AT88SC0808C is available in industry standard 8-lead packages with the same familiar pinout as 2-wire Serial EEPROMs.V CC =C1RST=C2SCL/CLK=C3NC=C4ISO Smart Card ModuleC5=GND C6=NC C7=SDA/IO C8=NCNC NC NC GND123487658-lead SOIC, PDIP V CC NC SCL SDAV CC =C1NC=C2SCL/CLK=C3NC=C4TWI Smart Card ModuleC5=GND C6=NC C7=SDA/IO C8=NCAT88SC0808C [SUMMARY DATASHEET]Atmel-2024MS-CryptoMem-AT88SC0808C-Datasheet-Summary_1220133Figure 1-1. Block Diagram2.Pin Descriptions2.1Supply Voltage (V CC )The V CC input is a 2.7V to 5.5V positive voltage supplied by the host.2.2 Clock (SCL/CLK)In the asynchronous T = 0 protocol, the SCL/CLK input is used to provide the device with a carrier frequency f . The nominal length of one bit emitted on I/O is defined as an “elementary time unit” (ETU) and is equal to 372/f. When the synchronous protocol is used, the SCL/CLK input is used to positive edge clock data into the device and negative edge clock data out of the device.2.3 Reset (RST)The AT88SC0808C provides an ISO 7816-3 compliant asynchronous answer to reset sequence. When the reset sequence is activated, the device will output the data programmed into the 64-bit answer-to-reset register. An internal pull-up on the RST input pad allows the device to be used in synchronous mode without bonding RST. The AT88SC0808C does not support the synchronous answer-to-reset sequence2.4 Serial Data (SDA/IO)The SDA pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wired with any number of other open drain or open collector devices. An external pull-up resistor should be connected between SDA and V CC . The value of this resistor and the system capacitance loading the SDA bus will determine the rise time of SDA. This rise time will determine the maximum frequency during read operations. Low value pull-up resistors will allow higher frequency operations while drawing higher average power. SDA/IO information applies to both asynchronous and synchronous protocols.When the synchronous protocol is used, the SCL/CLK input is used to positive edge clock data into the device and negative edge clock data out of the device.V CCAT88SC0808C [SUMMARY DATASHEET]Atmel-2024MS-CryptoMem-AT88SC0808C-Datasheet-Summary_12201343.*NOTICE: Stresses beyond those listed under “AbsoluteMaximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.Table 3-1.DC CharacteristicsNote:1. V IL min and V IH max are reference only and are not tested2. To prevent latch up conditions from occurring during power up of the AT88SCxxxxC, V CC must be turned onbefore applying V IH . For powering down, V IH must be removed before turning V CC offAT88SC0808C [SUMMARY DATASHEET]Atmel-2024MS-CryptoMem-AT88SC0808C-Datasheet-Summary_1220135Table 3-2.AC CharacteristicsApplicable over recommended operating range from V CC = +2.7 to 5.5V,4. Device Operation for Synchronous ProtocolsClock and Data Transitions:The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (see Figure 4-3 on page 7). Data changes during SCL high periods will indicate a start or stop condition as defined below.Start Condition:A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 4-4 on page 7).Stop Condition:A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (see Figure 4-4 on page 7).Acknowledge:All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero to acknowledge that it has received each word. This happens during the ninth clock cycle (see Figure 4-5 on page 7). Memory Reset:After an interruption in protocol, power loss or system reset, any 2-wire part can be reset by following these steps: 1. Clock up to nine cycles2. Look for SDA high in each cycle while SCL is high3. Create a start conditionAT88SC0808C [SUMMARY DATASHEET] Atmel-2024MS-CryptoMem-AT88SC0808C-Datasheet-Summary_1220136 Figure 4-1. Bus Timing for 2-wire Communications:SCL: Serial Clock, SDA – Serial Data I/OFigure 4-2. Write Cycle Timing:SCL: Serial Clock, SDA – Serial Data I/ONote: The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internalclear/write cycleSCLSDA INSDA OUTSTOPCONDITIONSTARTCONDITIONSCLSDAAT88SC0808C [SUMMARY DATASHEET]Atmel-2024MS-CryptoMem-AT88SC0808C-Datasheet-Summary_1220137Figure 4-3. Data ValidityFigure 4-4. Start and Stop DefinitionsFigure 4-5. Output AcknowledgeDATA CHANGE ALLOWEDDATA STABLEDATA STABLESDASCLSDASCLSTART STOPSCLDAT A INDAT A OUTEG D E L W O N K C A T R A T S 981AT88SC0808C [SUMMARY DATASHEET]Atmel-2024MS-CryptoMem-AT88SC0808C-Datasheet-Summary_12201385.Device Architecture5.1User ZonesThe EEPROM user memory is divided into eight zones of 1024 bits each. Multiple zones allow for different types of data or files to be stored in different zones. Access to the user zones is allowed only after security requirements have been met. These security requirements are defined by the user during the personalization of the device in the configuration memory. If the same security requirements are selected for multiple zones, then these zones may effectively be accessed as one larger zone.6. Control LogicAccess to the user zones occurs only through the control logic built into the device. This logic is configurable through access registers, key registers and keys programmed into the configuration memory during device personalization. Also implemented in the control logic is a cryptographic engine for performing the various higher-level security functions of the device.AT88SC0808C [SUMMARY DATASHEET]Atmel-2024MS-CryptoMem-AT88SC0808C-Datasheet-Summary_12201397. Configuration MemoryThe configuration memory consists of 2048 bits of EEPROM memory used for storing passwords, keys and codes and defining security levels to be used for each user zone. Access rights to the configuration memory are defined in the control logic and may not be altered by the user.AT88SC0808C [SUMMARY DATASHEET]Atmel-2024MS-CryptoMem-AT88SC0808C-Datasheet-Summary_122013108. Security FusesThere are three fuses on the device that must be blown during the device personalization process. Each fuse locks certain portions of the configuration memory as OTP memory. Fuses are designed for the module manufacturer, card manufacturer and card issuer and should be blown in sequence, although all programming of the device and blowing of the fuses may be performed at one final step.9. Protocol selectionThe AT88SC0808C supports two different communication protocols.• Smart Card Applications:The asynchronous T = 0 protocol defined by ISO 7816-3 is used for compatibility with the industry’s standard smart card readers• Embedded Applications:A 2-wire serial interface is used for fast and efficient communication with logic or controllersThe power-up sequence determines which of the two communication protocols will be used.9.1 Asynchronous T = 0 ProtocolThis power-up sequence complies with ISO 7816-3 for a cold reset in smart card applications.• V CC goes high; RST, I/O-SDA and CLK-SCL are low • Set I/O-SDA in receive mode • Provide a clock signal to CLK-SCL •RST goes high after 400 clock cyclesThe device will respond with a 64-bit ATR code, including historical bytes to indicate the memory density within theCryptoMemory family. Once the asynchronous mode has been selected, it is not possible to switch to the synchronous mode without powering off the device.Figure 9-1. Asynchronous T = 0 Protocol (Gemplus Patent)V cc I/O-SDARSTCLK-SCL9.2 Synchronous 2-wire Serial InterfaceThe synchronous mode is the default after powering up V CC due to an internal pull-up on RST. For embedded applications using CryptoMemory in standard plastic packages, this is the only communication protocol.• Power-up V CC , RST goes high also• After stable V CC , CLK-SCL and I/O-SDA may be drivenFigure 9-2. Synchronous 2-wire ProtocolNote:Five clock pulses must be sent before the first command is issued10. Communication Security ModesCommunications between the device and host operate in three basic modes. Standard mode is the default mode for the device after power-up. Authentication mode is activated by a successful authentication sequence. Encryption mode is activated by a successful encryption activation following a successful authentication. Table 10-1. Communication Security Modes (1)Note:1. Configuration data include viewable areas of the configuration zone except the passwords:• MDC: Modification Detection Code •MAC: Message Authentication CodeV cc I/O-SDARST CLK-SCL1234511. Security Options11.1 Anti-tearingIn the event of a power loss during a write cycle, the integrity of the device’s stored data may be recovered. This function is optional: the host may choose to activate the anti-tearing function, depending on application requirements. When anti-tearing is active, write commands take longer to execute, since more write cycles are required to complete them, and data are limited to eight bytes.Data are written first to a buffer zone in EEPROM instead of the intended destination address, but with the same accessconditions. The data are then written in the required location. If this second write cycle is interrupted due to a power loss, the device will automatically recover the data from the system buffer zone at the next power-up.In 2-wire mode, the host is required to perform ACK polling for up to 8mS after write commands when anti-tearing is active. At power-up, the host is required to perform ACK polling, in some cases for up to 2mS, in the event that the device needs to carry out the data recovery process.11.2 Write LockIf a user zone is configured in the write lock mode, the lowest address byte of an 8-byte page constitutes a write access byte for the bytes of that page.Example: The write lock byte at $080 controls the bytes from $080 to $087The write lock byte may also be locked by writing its least significant (rightmost) bit to “0”. Moreover, when write lock mode is activated, the write lock byte can only be programmed — that is, bits written to “0” cannot return to “1”.In the write lock configuration, only one byte can be written at a time. Even if several bytes are received, only the first byte will be taken into account by the device.12. Password VerificationPasswords may be used to protect read and/or write access of any user zone. When a valid password is presented, it ismemorized and active until power is turned off, unless a new password is presented or RST becomes active. There are eight password sets that may be used to protect any user zone. Only one password is active at a time, but write passwords give read access also..12.1 Authentication ProtocolThe access to a user zone may be protected by an authentication protocol. Any one of four keys may be selected to use with a user zone.The authentication success is memorized and active as long as the chip is powered, unless a new authentication is initialized or RST becomes active. If the new authentication request is not validated, the card loses its previous authentication and itshould be presented again. Only the last request is memorized.Note: Password and authentication may be presented at any time and in any order. If the trials limit has been reached (after four consecutive incorrect attempts), the password verification or authentication process will not be takeninto accountFigure 12-1. Password and Authentication OperationsREAD ACCESS12.2 ChecksumThe AT88SC0808C implements a data validity check function in the form of a checksum, which may function in standard,authentication or encryption modes.In the standard mode, the checksum is implemented as a Modification Detection Code (MDC), in which the host may read an MDC from the device in order to verify that the data sent was received correctly.In the authentication and encryption modes, the checksum becomes more powerful since it provides a bidirectional dataintegrity check and data origin authentication capability in the form of a Message Authentication Code (MAC). Only thehost/device that carried out a valid authentication is capable of computing a valid MAC. While operating in the authentication or encryption modes, the use of a MAC is required. For an ingoing command, if the device calculates a MAC different from the MAC transmitted by the host, not only is the command abandoned but the mode is also reset. A new authentication and/or encryption activation will be required to reactivate the MAC.12.3 EncryptionThe data exchanged between the device and the host during read, write and verify password commands may be encrypted to ensure data confidentiality.The issuer may choose to require encryption for a user zone by settings made in the configuration memory. Any one of four keys may be selected for use with a user zone. In this case, activation of the encryption mode is required in order to read/write data in the zone and only encrypted data will be transmitted. Even if not required, the host may elect to activate encryption provided the proper keys are known.12.4 Supervisor ModeEnabling this feature allows the holder of one specific password to gain full access to all eight password sets, including the ability to change passwords.12.5 Modify ForbiddenNo write access is allowed in a user zone protected with this feature at any time. The user zone must be written during device personalization prior to blowing the security fuses.12.6 Program OnlyFor a user zone protected by this feature, data within the zone may be changed from a “1” to a “0”, but never from a “0” to a “1”.13. Initial Device ProgrammingTo enable the security features of CryptoMemory, the device must first be personalized to set up several registers and load in the appropriate passwords and keys. This is accomplished through programming the configuration memory of CryptoMemory using simple write and read commands. To gain access to the configuration memory, the secure code must first besuccessfully presented. For the AT88SC0808C device, the secure code is $22 E8 3F. After writing and verifying data in the configuration memory, the security fuses must be blown to lock this information in the device. For additional information on personalizing CryptoMemory, please see the application notes Programming CryptoMemory for Embedded Applications and Initializing CryptoMemory for Smart Card Applications (at ).14.Note: 1. Formal drawings may be obtained from an Atmel sales office2. Both the J and P module packages are used for either ISO (T=0 / 2-wire mode) or TWI (2-wire mode only)15. Packaging InformationOrdering Code: MJ or MJTG Ordering Code: MP or MPTGModule Size: M2Dimension*: 12.6 x 11.4 [mm] Glob Top: Round - ∅ 8.5 [mm] Thickness: 0.58 [mm]Pitch: 14.25mm Module Size: M2Dimension*: 12.6 x 11.4 [mm]Glob Top: Square - 8.8 x 8.8 [mm] Thickness: 0.58 [mm]Pitch: 14.25mmNote: *The module dimensions listed refer to the dimensions of the exposed metal contact area. The actual dimensions of the module after excise or punching from the carrier tape are generally 0.4mm greater in both directions (i.e., apunched M2 module will yield 13.0 x 11.8mm)15.1 Atmel AT88SC0808C Package Marking Information15.2 Ordering Code: SH8S1 – 8-lead JEDEC SOIC15.3 Ordering Code: PU8P3 – 8-lead PDIP16. Revision History。

Atmel AT25128B 256B 131K 16K 电池电源 EEPROM 数据手册说明书

AT25128B and AT25256BSPI Serial EEPROM128K (16,384 x 8), 256K (32,768 x 8)DATASHEET Features●Serial Peripheral Interface (SPI) Compatible●Supports SPI Modes 0 (0,0) and 3 (1,1)Data Sheet Describes Mode 0 Operation●Low-voltage and Standard-voltage OperationV CC = 1.8V to 5.5V●20MHz Clock Rate (5V)●64-byte Page Mode and Byte Write Operation●Block Write ProtectionProtect 1/4, 1/2, or Entire Array●Write Protect (WP) Pin and Write Disable Instructions for Both Hardware andSoftware Data Protection●Self-timed Write Cycle (5ms max)●High ReliabilityEndurance: 1,000,000 Write CyclesData Retention: 100 Years●Green (Pb/Halogen-free/RoHS Compliant) Packaging Options●Die Sales: Wafer Form, Waffle Pack, and Bumped WafersDescriptionThe Atmel® AT25128B/256B provides 131,072/262,144 bits of Serial Electrically Erasable Programmable Read-Only Memory (EEPROM) organized as16,384/32,768 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. The AT25128B/256B is available in space saving JEDEC SOIC, TSSOP, UDFN, and VFBGA packages.The AT25128B/256B is enabled through the Chip Select pin (CS) and accessed via a 3-Wire interface consisting of Serial Data Input (SI), Serial Data Output (SO), and Serial Clock (SCK). All programming cycles are completely self-timed, and no separate erase cycle is required before write.Block Write protection is enabled by programming the status register with one of four blocks of Write Protection. Separate Program Enable and Program Disable instructions are provided for additional data protection. Hardware Data Protection is provided via the WP pin to protect against inadvertent write attempts. The HOLD pin may be used to suspend any serial communication without resetting the serial sequence.AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_01201521.Pin ConfigurationsTable 1-1.Pin Configurations 2.Absolute Maximum Ratings*Operating Temperature . . . . . . . . . . .-55︒C to +125︒C Storage Temperature. . . . . . . . . . . . .-65︒C to +150︒C Voltage on any pinwith respect to ground . . . . . . . . . . . . . -1.0V to +7.0V Maximum Operating Voltage . . . . . . . . . . . . . . . 6.25V DC Output Current. . . . . . . . . . . . . . . . . . . . . . .5.0mA*Notice:Stresses beyond those listed under “AbsoluteMaximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions forextended periods may affect device reliability.Note: Drawings are not to scale.8-lead SOICCS SO WP GNDV CC HOLD SCK SI12348765Top ViewTop View8-lead TSSOP12348765CS SO WP GNDV CC HOLD SCK SIV CC HOLD SCK SICS SO WP GND123487658-ball VFBGABottom View8-pad UDFNBottom ViewV CC HOLD SCK SI CS SO WP GND123487653AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_0120153.Block DiagramFigure 3-1.Block DiagramV CCAT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_01201544.Electrical Characteristics4.1Pin Capacitance (1)Table 4-1.Pin CapacitanceNote:1.This parameter is characterized and is not 100% tested.4.2DC CharacteristicsTable 4-2.DC CharacteristicsNote:1.V IL min and V IH max are reference only and are not tested.Applicable over recommended operating range from T A = 25°C, f = 1MHz, V CC = +5V (unless otherwise noted).Applicable over recommended operating range from: T AI = -40︒C to +85︒C, V CC = +1.8V to +5.5V, (unless otherwise noted).5AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_0120154.3AC CharacteristicsTable 4-3.AC CharacteristicsApplicable over recommended operating range from T AI = -40 to +85°C, V CC = As Specified, CL = 1 TTL Gate and 30pF (unless otherwise noted).AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_0120156Note:1.This parameter is characterized and is not 100% tested.5.Serial Interface DescriptionMaster: The device that generates the serial clock.Slave: Because the Serial Clock pin (SCK) is always an input, the AT25128B/256B always operates as a slave.Transmitter/Receiver: The AT25128B/256B has separate pins designated for data transmission (SO) and reception (SI).MSB: The Most Significant Bit (MSB) is the first bit transmitted and received.Serial Opcode: After the device is selected with CS going low, the first byte will be received. This byte contains the opcode which defines the operations to be performed.Invalid Opcode: If an invalid opcode is received, no data will be shifted into the AT25128B/256B, and the serial output pin (SO) will remain in a high-impedance state until the falling edge of CS is detected again. This will reinitialize the serial communication.Chip Select: The AT25128B/256B is selected when the CS pin is low. When the device is not selected, data will not be accepted via the SI pin, and the SO pin will remain in a high-impedance state.Hold: The HOLD pin is used in conjunction with the CS pin to select the AT25128B/256B. When the device is selected and a serial sequence is underway, HOLD can be used to pause the serial communication with the master device without resetting the serial sequence. To pause, the HOLD pin must be brought low while the SCK pin is low. To resume serial communication, the HOLD pin is brought high while the SCK pin is low (SCK may still toggle during HOLD). Inputs to the SI pin will be ignored while the SO pin is in the high-impedance state.Write Protect: The Write Protect pin (WP) will allow normal read/write operations when held high. When the WP pin is brought low and WPEN bit is one, all write operations to the status register are inhibited. WP going low while CS is still low will interrupt a write to the status register. If the internal write cycle has already been initiated, WP going low will have no effect on any write operation to the status register. The WP pin function is blocked when the WPEN bit in the status register is zero. This will allow the user to install the AT25128B/256B in a system with the WP pin tied to ground and still be able to write to the status register. All WP pin functions are enabled when the WPEN bit is set to one.Table 4-3.AC Characteristics (Continued)Applicable over recommended operating range from T AI = -40 to +85°C, V CC = As Specified, CL = 1 TTL Gate and 30pF (unless otherwise noted).7AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_012015Figure 5-1.SPI Serial InterfaceMaster :MicrocontrollerSlave :AT25128B/256BAT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_01201586.Functional DescriptionThe AT25128B/256B is designed to interface directly with the synchronous Serial Peripheral Interface (SPI) of the 6800 series of microcontrollers.The AT25128B/256B utilizes an 8-bit instruction register. The list of instructions and their operation codes are contained in Figure 6-1. All instructions, addresses, and data are transferred with the MSB first and start with a high-to-low CS transition.Table 6-1.Instruction Set for the AT25010B/020B/040BWrite Enable (WREN): The device will power-up in the Write Disable state when V CC is applied. Allprogramming instructions must therefore be preceded by a Write Enable instruction. The WP pin must be held high during a WREN instruction.Write Disable (WRDI): To protect the device against inadvertent writes, the Write Disable instruction disables all programming modes. The WRDI instruction is independent of the status of the WP pin.Read Status Register (RDSR): The Read Status Register instruction provides access to the status register. The Read/Busy and Write Enable status of the device can be determined by the RDSR instruction. Similarly, the Block Write Protection bits indicate the extent of protection employed. These bits are set by using the WRSR instruction.Table 6-2.Status Register FormatTable 6-3.Read Status Register Bit Definition9AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_012015Write Status Register (WRSR): The WRSR instruction allows the user to select one of four levels of protection. The AT25128B/256B is divided into four array segments. None, one-quarter (¼), one-half (½), or all of the memory segments can be protected. Any of the data within any selected segment will therefore be read-only. The block write protection levels and corresponding status register control bits are shown in Table 6-4.Bits BP1, BP0, and WPEN are nonvolatile cells that have the same properties and functions as the regular memory cells (e.g., WREN, t WC , RDSR).Table 6-4.Block Write Protect BitsThe WRSR instruction also allows the user to enable or disable the write protect (WP) pin through the use of the Write Protect Enable (WPEN) bit. Hardware write protection is enabled when the WP pin is low and the WPEN bit is one. The hardware write protection is disabled when either the WP pin is high or the WPEN bit is zero. When the device is hardware write protected, writes to the Status Register including the Block Protect bits, the WPEN bit, and the block protected sections in the memory array are disabled. Writes are only allowed to sections of the memory which are not block-protected.Note:When the WPEN bit is hardware write protected, it cannot be changed back to zero as long as the WP pin is held low.Table 6-5.WPEN Operation Read Sequence (READ): Reading the AT25128B/256B via the SO pin requires the following sequence. After the CS line is pulled low to select a device, the Read opcode is transmitted via the SI line followed by the byte address to be read (Table 6-6). Upon completion, any data on the SI line will be ignored. The data (D7 – D0) at the specified address is then shifted out onto the SO line. If only one byte is to be read, the CS line should be driven high after the data comes out. The Read Sequence can be continued since the byte address isautomatically incremented and data will continue to be shifted out. When the highest address is reached, the address counter will roll-over to the lowest address allowing the entire memory to be read in one continuous read cycle.AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_01201510Write Sequence (WRITE): In order to program the AT25128B/256B, the Write Protect pin (WP) must be held high and two separate instructions must be executed. First, the device must be write enabled via the WREN instruction. Then a Write (WRITE) instruction may be executed. Also, the address of the memory location(s) to be programmed must be outside the protected address field location selected by the Block Write Protection level. During an internal write cycle, all commands will be ignored except the RDSR instruction.A Write instruction requires the following sequence. After the CS line is pulled low to select the device, the Write opcode is transmitted via the SI line followed by the byte address and the data (D7 D0) to be programmed (see Table 6-6 for the address key). Programming will start after the CS pin is brought high. The low-to-hightransition of the CS pin must occur during the SCK low time immediately after clocking in the D0 (LSB) data bit.The Ready/Busy status of the device can be determined by initiating a Read Status Register (RDSR)instruction. If Bit 0 is one, the write cycle is still in progress. If Bit 0 is zero, the write cycle has ended. Only the RDSR instruction is enabled during the write programming cycle.The AT25128B/256B is capable of an 64-byte Page Write operation. After each byte of data is received, the six low-order address bits are internally incremented by one; the high-order bits of the address will remain constant. If more than 64 bytes of data are transmitted, the address counter will roll-over, and the previously written data will be overwritten. The AT25128B/256B is automatically returned to the Write Disable state at the completion of a write cycle.Note:If the WP pin is brought low or if the device is not Write Enabled (WREN), the device will ignore the Write instruction and will return to the standby state, when CS is brought high. A new CS falling edge is required to reinitiate the serial communication.Table 6-6.Address Key7.Timing Diagrams — SPI Mode 0 (0,0)Figure 7-1.Synchronous Data Timing (for Mode 0)Figure 7-2.WREN TimingFigure 7-3.WRDI TimingSOSISCKCSV V ILV V ILV V ILV V SOSISCK CSWREN OpcodeHI-ZSOSISCK CSWRDI OpcodeHI-ZAT25128B/256B [DATASHEET]12Figure 7-5.WRSR TimingFigure 7-6.READ TimingSOSISCKCSSOSISCKCSInstruction76543210Data InHigh-impedanceMSBSOSI SCKCSFigure 7-8.HOLD TimingSOSISCKCSInstructionByte AddressData InHigh-impedance7654321015 14 13 (3)210HOLDSOSCKCSt HDAT25128B/256B [DATASHEET]148.Ordering Code DetailAtmel DesignatorProduct FamilyDevice DensityDevice RevisionShipping Carrier OptionOperating Voltage128 = 128 kilobit 256 = 256 kilobit25 = Standard SPI Serial EPPROMB or Blank = Bulk (Tubes)T = Tape and Reel, Standard Quantity Option E = Tape and Reel, Expanded Quantity OptionL = 1.8V to 5.5VPackage Device Grade or Wafer/Die ThicknessH = Green, NiPdAu Lead Finish, Industrial Temperature Range (-40°C to +85°C)U = Green, Matte Sn Lead Finish, Industrial Temperature Range (-40°C to +85°C)11 = 11mil Wafer ThicknessPackage OptionSS = JEDEC SOIC X = TSSOP MA = UDFN C = VFBGAWWU = Wafer UnsawnWDT = Die in Tape and ReelA T 25128B -S S H L -B9.Part MarkingsNote: 1.Contact Atmel Sales for Wafer sales.AT25128B/256B [DATASHEET]1611.18S1 — 8-lead JEDEC SOICAT25128B/256B [DATASHEET]1811.28X — 8-lead TSSOP11.38MA2 — 8-pad UDFNAT25128B/256B [DATASHEET]2011.48U2-1 — 8-ball VFBGA21AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_01201512.Revision HistoryX X X X X XAtmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311F: (+1)(408) 436.4200| © 2015 Atmel Corporation. / Rev.: Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_012015.Atmel ®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities ®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended,authorized, or warranted for use as components in applications intended to support or sustain life.SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (“Safety-Critical Applications”) without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems.Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.。

AT28HC64B高性能电擦可编程只读存储器(EEPROM)说明书

Features Array•Fast Read Access Time – 70 ns•Automatic Page Write Operation–Internal Address and Data Latches for 64 Bytes•Fast Write Cycle Times–Page Write Cycle Time: 10 ms Maximum (Standard)2 ms Maximum (Option – Ref. AT28HC64BF Datasheet)–1 to 64-byte Page Write Operation•Low Power Dissipation–40 mA Active Current–100µA CMOS Standby Current•Hardware and Software Data Protection•DATA Polling and Toggle Bit for End of Write Detection•High Reliability CMOS Technology–Endurance: 100,000 Cycles–Data Retention: 10 Years•Single 5 V ±10% Supply•CMOS and TTL Compatible Inputs and Outputs•JEDEC Approved Byte-wide Pinout•Industrial Temperature Ranges•Green (Pb/Halide-free) Packaging Option Only1.DescriptionThe AT28HC64B is a high-performance electrically-erasable and programmable read-only memory (EEPROM). Its 64K of memory is organized as 8,192 words by 8 bits. Manufactured with Atmel’s advanced nonvolatile CMOS technology, the device offers access times to 55 ns with power dissipation of just 220 mW. When the device is deselected, the CMOS standby current is less than 100µA.The AT28HC64B is accessed like a Static RAM for the read or write cycle without the need for external components. The device contains a 64-byte page register to allow writing of up to 64 bytes simultaneously. During a write cycle, the addresses and 1 to 64 bytes of data are internally latched, freeing the address and data bus for other operations. Following the initiation of a write cycle, the device will automatically write the latched data using an internal control timer. The end of a write cycle can be detected by DATA polling of I/O7. Once the end of a write cycle has been detected, a new access for a read or write can begin.Atmel’s AT28HC64B has additional features to ensure high quality and manufactura-bility. The device utilizes internal error correction for extended endurance and improved data retention characteristics. An optional software data protection mecha-nism is available to guard against inadvertent writes. The device also includes anextra 64 bytes of EEPROM for device identification or tracking.20274L–PEEPR–2/3/09AT28HC64B2.Pin Configurations2.128-lead SOIC Top ViewPin Name Function A0 - A12Addresses CE Chip Enable OE Output Enable WE Write Enable I/O0 - I/O7Data Inputs/Outputs NC No Connect DCDon’t Connect2.232-lead PLCC Top ViewNote:PLCC package pins 1 and 17 are Don’t Connect.2.328-lead TSOP Top View30274L–PEEPR–2/3/09AT28HC64B3.Block Diagram4.Device Operation4.1ReadThe AT28HC64B is accessed like a Static RAM. When CE and OE are low and WE is high, the data stored at the memory location determined by the address pins is asserted on the out-puts. The outputs are put in the high-impedance state when either CE or OE is high. This dual line control gives designers flexibility in preventing bus contention in their systems.4.2Byte WriteA low pulse on the WE or CE input with CE or WE low (respectively) and OE high initiates a write cycle. The address is latched on the falling edge of CE or WE, whichever occurs last. The data is latched by the first rising edge of CE or WE. Once a byte write has been started, it will automatically time itself to completion. Once a programming operation has been initiated and for the duration of t WC , a read operation will effectively be a polling operation.4.3Page WriteThe page write operation of the AT28HC64B allows 1 to 64 bytes of data to be written into the device during a single internal programming period. A page write operation is initiated in the same manner as a byte write; after the first byte is written, it can then be followed by 1 to 63 additional bytes. Each successive byte must be loaded within 150 µs (t BLC ) of the previous byte. If the t BLC limit is exceeded, the AT28HC64B will cease accepting data and commence the internal programming operation. All bytes during a page write operation must reside on the same page as defined by the state of the A6 to A12 inputs. For each WE high-to-low transition during the page write operation, A6 to A12 must be the same.The A0 to A5 inputs specify which bytes within the page are to be written. The bytes may be loaded in any order and may be altered within the same load period. Only bytes which are specified for writing will be written; unnecessary cycling of other bytes within the page does not occur.4.4DATA PollingThe AT28HC64B features DATA Polling to indicate the end of a write cycle. During a byte or page write cycle, an attempted read of the last byte written will result in the complement of the written data to be presented on I/O7. Once the write cycle has been completed, true data is valid on all outputs, and the next write cycle may begin. DATA Polling may begin at any time during the write cycle.40274L–PEEPR–2/3/09AT28HC64B4.5Toggle BitIn addition to DATA Polling, the AT28HC64B provides another method for determining the end of a write cycle. During the write operation, successive attempts to read data from the device will result in I/O6 toggling between one and zero. Once the write has completed, I/O6 will stop toggling, and valid data will be read. Toggle bit reading may begin at any time during the write cycle.4.6Data ProtectionIf precautions are not taken, inadvertent writes may occur during transitions of the host system power supply. Atmel ® has incorporated both hardware and software features that will protect the memory against inadvertent writes.4.6.1Hardware ProtectionHardware features protect against inadvertent writes to the AT28HC64B in the following ways: (a) V CC sense – if V CC is below 3.8 V (typical), the write function is inhibited; (b) V CC power-on delay – once V CC has reached 3.8 V, the device will automatically time out 5 ms (typical) before allowing a write; (c) write inhibit – holding any one of OE low, CE high or WE high inhib-its write cycles; and (d) noise filter – pulses of less than 15 ns (typical) on the WE or CE inputs will not initiate a write cycle.4.6.2Software Data ProtectionA software-controlled data protection feature has been implemented on the AT28HC64B. When enabled, the software data protection (SDP), will prevent inadvertent writes. The SDP feature may be enabled or disabled by the user; the AT28HC64B is shipped from Atmel with SDP disabled.SDP is enabled by the user issuing a series of three write commands in which three specific bytes of data are written to three specific addresses (refer to the “Software Data Protection Algorithm” diagram on page 10). After writing the 3-byte command sequence and waiting t WC , the entire AT28HC64B will be protected against inadvertent writes. It should be noted that even after SDP is enabled, the user may still perform a byte or page write to the AT28HC64B. This is done by preceding the data to be written by the same 3-byte command sequence used to enable SDP.Once set, SDP remains active unless the disable command sequence is issued. Power transi-tions do not disable SDP, and SDP protects the AT28HC64B during power-up and power-down conditions. All command sequences must conform to the page write timing specifica-tions. The data in the enable and disable command sequences is not actually written into the device; their addresses may still be written with user data in either a byte or page write operation.After setting SDP, any attempt to write to the device without the 3-byte command sequence will start the internal write timers. No data will be written to the device, however. For the dura-tion of t WC , read operations will effectively be polling operations.4.7Device IdentificationAn extra 64 bytes of EEPROM memory are available to the user for device identification. By raising A9 to 12 V ±0.5 V and using address locations 1FC0H to 1FFFH, the additional bytes may be written to or read from in the same manner as the regular memory array.50274L–PEEPR–2/3/09AT28HC64BNotes:1.X can be VIL or VIH.2.See “AC Write Waveforms” on page 8.3.VH = 12.0 V ±0.5 V.Note:1.I SB1 and I SB2 for the 55 ns part is 40 mA maximum.5.DC and AC Operating RangeAT28HC64B-70AT28HC64B-90AT28HC64B-120Operating Temperature (Case)-40°C - 85°C -40°C - 85°C -40°C - 85°C V CC Power Supply5 V ±10%5 V ±10%5 V ±10%6.Operating ModesMode CE OE WE I/O Read V IL V IL V IH D OUT Write (2)V IL V IH V IL D IN Standby/Write Inhibit V IH X (1)X High ZWrite Inhibit X X V IH Write Inhibit X V IL X Output Disable X V IH XHigh ZChip Erase V ILV H (3)V IL High Z7.Absolute Maximum Ratings*Temperature Under Bias................................-55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliabilityStorage Temperature.....................................-65°C to +150°C All Input Voltages(including NC Pins)with Respect to Ground.................................-0.6 V to +6.25 V All Output Voltageswith Respect to Ground...........................-0.6 V to V CC + 0.6 V Voltage on OE and A9with Respect to Ground..................................-0.6 V to +13.5V8.DC CharacteristicsSymbol Parameter ConditionMinMax Units I LI Input Load Current V IN = 0 V to V CC + 1 V 10µA I LO Output Leakage Current V I/O = 0 V to V CC10µA I SB1V CC Standby Current CMOS CE = V CC - 0.3 V to V CC + 1 V 100(1)µA I SB2V CC Standby Current TTL CE = 2.0 V to V CC + 1 V 2(1)mA I CC V CC Active Current f = 5 MHz; I OUT = 0 mA40mA V IL Input Low Voltage 0.8V V IH Input High Voltage 2.0V V OL Output Low Voltage I OL = 2.1 mA 0.40V V OH Output High VoltageI OH = -400 µA2.4V60274L–PEEPR–2/3/09AT28HC64B10.AC Read Waveforms (1)(2)(3)(4)Notes:1.CE may be delayed up to t ACC - t CE after the address transition without impact on t ACC .2.OE may be delayed up to t CE - t OE after the falling edge of CE without impact on t CE or by t ACC - t OE after an address changewithout impact on t ACC .3.t DF is specified from OE or CE whichever occurs first (C L = 5 pF).4.This parameter is characterized and is not 100% tested.9.AC Read CharacteristicsSymbol ParameterAT28HC64B-70AT28HC64B-90AT28HC64B-120Units MinMax MinMax MinMax t ACC Address to Output Delay 7090120ns t CE (1)CE to Output Delay 7090120ns t OE (2)OE to Output Delay 035040050ns t DF (3)(4)OE to Output Float 035040050ns t OHOutput Hold00ns70274L–PEEPR–2/3/09AT28HC64B11.Input Test Waveforms and Measurement Level12.Output Test LoadNote:1.This parameter is characterized and is not 100% tested.R F 13.Pin Capacitancef = 1 MHz, T = 25°C (1)Symbol Typ Max Units Conditions C IN 46pF V IN = 0 V C OUT 812pFV OUT = 0 V815.AC Write Waveforms15.1WE Controlled15.2CE Controlled14.AC Write CharacteristicsSymbol ParameterMin MaxUnits t AS , t OES Address, OE Setup Time 0ns t AH Address Hold Time 50ns t CS Chip Select Setup Time 0ns t CH Chip Select Hold Time 0ns t WP Write Pulse Width (WE or CE)100ns t DS Data Setup Time 50ns t DH , t OEHData, OE Hold Timens90274L–PEEPR–2/3/09AT28HC64B17.Page Mode Write Waveforms (1)(2)Notes: 1.A6 through A12 must specify the same page address during each high to low transition of WE (or CE).2.OE must be high only when WE and CE are both low.18.Chip Erase Waveformst S = t H = 5 µs (min.)t W = 10 ms (min.)V H = 12.0 V ±0.5 V16.Page Mode CharacteristicsSymbol Parameter MinMax Units t WC Write Cycle Time10ms t WC Write Cycle Time (Use AT28HC64BF))2ms t AS Address Setup Time 0ns t AH Address Hold Time 50ns t DS Data Setup Time 50ns t DH Data Hold Time 0ns t WP Write Pulse Width 100ns t BLC Byte Load Cycle Time 150µs t WPHWrite Pulse Width High50ns100274L–PEEPR–2/3/09AT28HC64B19.Software Data Protection EnableAlgorithm (1)Notes:1.Data Format: I/O7 - I/O0 (Hex);Address Format: A12 - A0 (Hex).2.Write Protect state will be activated at end of writeeven if no other data is loaded.3.Write Protect state will be deactivated at end of writeperiod even if no other data is loaded.4.1 to 64 bytes of data are loaded.20.Software Data Protection DisableAlgorithm (1)Notes:1.Data Format: I/O7 - I/O0 (Hex);Address Format: A12 - A0 (Hex).2.Write Protect state will be activated at end of writeeven if no other data is loaded.3.Write Protect state will be deactivated at end of writeperiod even if no other data is loaded.4. 1 to 64 bytes of data are loaded.21.Software Protected Write Cycle Waveforms (1)(2)Notes:1.A6 through A12 must specify the same page address during each high to low transition of WE (or CE) after the softwarecode has been entered.2.OE must be high only when WE and CE are both low.11AT28HC64BNote:1.These parameters are characterized and not 100% tested. See “AC Read Characteristics” on page 6.23.Data Polling WaveformsNotes:1.These parameters are characterized and not 100% tested.2.See “AC Read Characteristics” on page 6.25.Toggle Bit Waveforms (1)(2)(3)Notes: 1.Toggling either OE or CE or both OE and CE will operate toggle bit.2.Beginning and ending state of I/O6 will vary.3.Any address location may be used, but the address should not vary.22.Data Polling Characteristics (1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 0ns t OEH OE Hold Time 0ns t OE OE to Output Delay (1)ns t WR Write Recovery Timens24.Toggle Bit Characteristics (1)Symbol Parameter Min TypMaxUnits t DH Data Hold Time 10ns t OEH OE Hold Time 10ns t OE OE to Output Delay (2)ns t OEHP OE High Pulse 150ns t WR Write Recovery Timens12AT28HC64B26.Normalized I CCGraphs13AT28HC64B27.Ordering Information27.1Green Package Option (Pb/Halide-free)t ACC (ns)I CC (mA)Ordering Code Package Operation RangeActive Standby 70400.1AT28HC64B-70TU 28T Industrial (-40°C to 85°C)AT28HC64B-70JU 32J AT28HC64B-70SU 28S 90400.1AT28HC64B-90JU 32J AT28HC64B-90SU 28S AT28HC64B-90TU 28T 120400.1AT28HC64B-12JU 32J AT28HC64B-12SU28SPackage Type32J 32-lead, Plastic J-leaded Chip Carrier (PLCC)28S 28-lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC)28T28-lead, Plastic Thin Small Outline Package (TSOP)27.2Die ProductsContact Atmel Sales for die sales options.28.Packaging Information 28.132J – PLCC14AT28HC64BAT28HC64B 28.228S – SOIC1528.328T – TSOP16AT28HC64BHeadquarters InternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USATel: 1(408) 441-0311 Fax: 1(408) 487-2600Atmel AsiaUnit 1-5 & 16, 19/FBEA Tower, Millennium City 5418 Kwun Tong RoadKwun Tong, KowloonHong KongTel: (852) 2245-6100Fax: (852) 2722-1369Atmel EuropeLe Krebs8, Rue Jean-Pierre TimbaudBP 30978054 Saint-Quentin-en-Yvelines CedexFranceTel: (33) 1-30-60-70-00Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb SiteTechnical Support******************Sales Contact/contactsLiterature Requests/literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2009 Atmel Corporation. All rights reserved. Atmel®, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

SL2.2S规格书,usb HUB大全,替换FE1.1S,GL850,GL852,PL2586

USB2.0 HUB控制器集成电路USB 2.0 HIGH SPEED 4-PORT HUB CONTROLLERSL2.2s数据手册Data Sheet内容目录第一章管脚分配 (3)1.1 SL2.2S管脚图 (3)1.2 SL2.2S管脚定义 (3)第二章 功能叙述 (5)2.1综述 (5)2.2指示灯 (5)2.2.1单灯方案 (5)2.2.2多灯方案 (6)2.2.3 LED指示定义 (6)2.3过流保护 (6)2.4充电支持 (6)2.5I2C接口 (7)2.6EEPROM设置 (7)第三章电气特性 (8)3.1极限工作条件 (8)3.2工作范围 (8)3.3直流电特性 (8)3.4HS/FS/LS电气特性 (8)3.5ESD特性 (8)附录一封装 (9)表格目录表格1: 端口LED定义 (6)表格 2 : ACTIVE LED定义 (6)表格3:EEPROM数据结构定义 (7)表格4: 最大额定值 (8)表格5: 工作范围 (8)表格6: 直流电特性 (8)插图目录图1:SSOP28 管脚图 (3)图2:单灯方案配置 (5)图3: 5灯方案配置 ............................................................................... (6)图 4:附录 封装图 ................................................................................... .9第一章管脚分配1.1SL2.2s管脚图图1:SSOP28 管脚图1.2SL2.2s管脚定义管脚名称28Die IO类型定义Pin#VSS 1 P 芯片地XOUT 2 O晶振PAD XIN 3 IDM4 4 B下行口4的USB信号DP4 5 BDM3 6 B下行口3的USB信号DP3 7 BDM2 8 B下行口2的USB信号DP2 9 BDM1 10 B下行口1的USB信号DP1 11 BVDD18 12 P 模拟1.8vVDD33 13 P 模拟3.3v - 14 NCUDM 15 B上行口的USB信号UDP 16 BRESET_N 17 I,Pu 芯片外部复位输入- 18 NCPSELF 19 I,Pu 高为自供电,低为总线供电VDD5 20 P 5v输入VDD33 21 P 3.3v输出DRV 22 B,Pu 点灯驱动信号LED1 23 B,Pu 点灯驱动信号LED2 24 B,Pu 点灯驱动信号PWRN 25 B,Pu 下行口电源输出控制,低有效OVCRN/SDA 26 B,PuI2C SDA数据线,内部上拉;芯片初始化完成后作为过流保护输入脚,低有效SCL 27 B,Pu I2C SCL时钟输出VDD18 28 P 数字1.8v注释:O,输出;I 输入;B 双向;P 电源/接地;Pu 上拉;Pd 下拉;NC 悬空;第二章 功能叙述2.1综述SL2.2s 是一颗高集成度,高性能,低功耗的USB2.0集线器主控芯片;该芯片采用STT 技术,单电源供电方式,芯片供电电压为5v , 内部集成5V 转3.3V,只需在外部电源添加滤波电容;芯片自带复位电路,低功耗技术让他更加出众。

Proteus电子元件符号大全及汉英对照表.

插座 XS 端子板 XT电线,电缆,母线 W 直流母线 WB插接式(馈电)母线 WIB 电力分支线 WP 照明分支线 WL 应急照明分支线 WE 电力干线 WPM 照明干线 WLM应急照明干线 WEM 滑触线 WT合闸小母线 WCL 控制小母线 WC信号小母线 WS 闪光小母线 WF事故音响小母线 WFS 预告音响小母线 WPS电压小母线 WV 事故照明小母线 WELM避雷器 F 熔断器 FU快速熔断器 FTF 跌落式熔断器 FF限压保护器件 FV 电容器 C电力电容器 CE 正转按钮 SBF反转按钮 SBR 停止按钮 SBS紧急按钮 SBE 试验按钮 SBT复位按钮 SR 限位开关 SQ 接近开关 SQP手动控制开关 SH 时间控制开关 SK液位控制开关 SL 湿度控制开关 SM压力控制开关 SP 速度控制开关 SS温度控制开关,辅助开关 ST电压表切换开关 SV 电流表切换开关 SA整流器 U 可控硅整流器 UR 控制电路有电源的整流器 VC变频器 UF 变流器 UC 逆变器 UI 电动机 M异步电动机 MA 同步电动机 MS 直流电动机 MD绕线转子感应电动机 MW 鼠笼型电动机 MC电动阀 YM 电磁阀 YV 防火阀 YF 排烟阀 YS 电磁锁 YL 跳闸线圈 YT 合闸线圈YC 气动执行器 YPA,YA 电动执行器 YE 发热器件(电加热) FH 照明灯(发光器件) EL 空气调节器 EV电加热器加热元件 EE 感应线圈,电抗器 L励磁线圈 LF 消弧线圈 LA 滤波电容器 LL电阻器,变阻器 R 电位器 RP热敏电阻 RT 光敏电阻 RL 压敏电阻 RPS 接地电阻 RG放电电阻 RD 启动变阻器 RS 频敏变阻器 RF 限流电阻器 RC光电池,热电传感器 B 压力变换器 BP 温度变换器 BT 速度变换器 BV 时间测量传感器 BT1、BK 液位测量传感器 BL 温度测量传感器 BH、BM电子元件符号及字母表示电流表 PA 电压表 PV有功电度表 PJ 无功电度表 PJR频率表 PF 相位表 PPA 最大需量表(负荷监控仪) PM功率因数表 PPF 有功功率表 PW 无功功率表 PR 无功电流表 PAR 声信号 HA 光信号 HS 指示灯 HL绿色灯 HG蓝色灯 HB连接片 XB插座 XS电线,电缆,母线 W插接式(馈电)母线 WIB照明分支线 WL电力干线 WPM应急照明干线 WEM合闸小母线 WCL信号小母线 WS事故音响小母线 WFS电压小母线 WV避雷器 F快速熔断器 FTF限压保护器件 FV红色灯 HR 黄色灯 HY 白色灯 HW 插头 XP 端子板 XT 直流母线 WB 电力分支线WP 应急照明分支线 WE 照明干线 WLM 滑触线 WT 控制小母线 WC 闪光小母线WF 预告音响小母线 WPS 事故照明小母线 WELM 熔断器 FU 跌落式熔断器 FF 电容器 C电力电容器 CE 正转按钮 SBF反转按钮 SBR 停止按钮 SBS紧急按钮 SBE 试验按钮 SBT复位按钮 SR 限位开关 SQ 接近开关 SQP手动控制开关 SH 时间控制开关 SK液位控制开关 SL 湿度控制开关 SM压力控制开关 SP 速度控制开关 SS温度控制开关,辅助开关 ST电压表切换开关 SV 电流表切换开关 SA整流器 U 可控硅整流器 UR 控制电路有电源的整流器 VC变频器 UF 变流器 UC 逆变器 UI 电动机 M异步电动机 MA 同步电动机 MS 直流电动机 MD绕线转子感应电动机 MW 鼠笼型电动机 MC电动阀 YM 电磁阀 YV 防火阀 YF 排烟阀 YS 电磁锁 YL跳闸线圈 YT 合闸线圈 YC 气动执行器 YPA,YA 电动执行器 YE 发热器件(电加热) FH 照明灯(发光器件) EL 空气调节器 EV 电加热器加热元件 EE 感应线圈,电抗器L励磁线圈 LF 消弧线圈 LA 滤波电容器 LL电阻器,变阻器 R 电位器 RP热敏电阻 RT 光敏电阻 RL 压敏电阻 RPS 接地电阻 RG放电电阻 RD 启动变阻器 RS 频敏变阻器 RF 限流电阻器 RC光电池,热电传感器 B 压力变换器 BP 温度变换器 BT 速度变换器 BV 时间测量传感器 BT1、BK 液位测量传感器 BL 温度测量传感器 BH、BMproteus元器件中英文对照表AD芯片-----TECHWELL TW6805A仿真软件里的AD0809有问题,用0808代替定时/计数器的使用方法:CLK:计数和测频状态时,数字波的输入端。

ISIS_7_Professional元件库列表

模拟芯片(Analog ICs )放大器(Amplifiers)比较器(Comparators)显示驱动器(Display Drivers)过滤器(Filters)数据选择器(Multiplexers)稳压器(Regulators)定时器(Timers)基准电压(Voltage Referenee) 杂类(Miseellananeous)电容(Capaeitors)可动态显示充放电电容(An imated)音响专用轴线电容(Audio Grade Axial)轴线聚苯烯电容(Axial Lead Polyprope ne)轴线聚苯烯电容(Axial Lead Polystyre ne)陶瓷圆片电容(Ceramic Disc)去耦片状电容(Deeoupling Disc)普通电容(Generic)高温径线电容(High Temp Radial)高温径线电解电容(High Temperature Axial Electrolytic)金属化聚酯膜电容(Metallised Polyester Film) 金属化聚烯电容(Metallised Polypropene)金属化聚烯膜电容( Metallised Polyprope ne Film)小型电解电容(Miniture Electrolytic)多层金属化聚酯膜电容( Multilayer Metallised Polyestern Film) 聚脂膜电容(Mylar Film)镍栅电容(Nickel Barrier)无极性电容(Non Polarised)聚脂层电容(Polyester Layer)径线电解电容(Radial Electrolytic)树脂蚀刻电容(Resin Dipped)钽珠电容(Tantalum Bead)可变电容(Variable)VX 轴线电解电容(VX Axial Electolytic)连接器(Connectors)音频接口( Audio)D 型接口( D-Type)双排插座(DIL)插头(Header Blocks)PCB 转接器(PCB Transfer)带线(Ribbon Cable)单排插座(SIL)连线端子(Terminal Blocks)杂类(Miscellananeous) 数据转换器(Data Converter) 模/数转换器(A/D converters) 数/模转换器(D/A converters) 采样保持器(Sample & Hold) 温度传感器(Temperature Sen sore) 调试工具(Debugging Tools) 断点触发器(Breakpoint Triggers) 逻辑探针(Logic Probes) 逻辑激励源(Logic Stimuli) 二极管(Diode) 整流桥(Bridge Rectifiers) 普通二极管(Generic) 整流管(Rectifiers) 肖特基二极管(Schottky) 开关管(Switching) 隧道二极管(Tunnel) 变容二极管(Varicap) 齐纳击穿二极管(Zener)ECL 10000 系列(ECL 10000 Series) 各种常用集成电路机电(Electromechanical)各种直流和步进电机电感(Inductors) 普通电感(Generic) 贴片式电感(SMT In ductors) 变压器(Transformers) 拉普拉斯变换(Laplace Primitives) 一阶模型(1st Order) 二阶模型(2st Order) 控制器(Controllers) 非线性模式(Non-Linear) 算子(Operators) 极点/零点(Poles/Zones) 符号(Symbols) 存储芯片(Memory Ics) 动态数据存储器(Dynamic RAM) 电可擦除可编程存储器(EEPROM) 可擦除可编程存储器(EPROM) I2C 总线存储器(I2C Memories) SPI 总线存储器(SPI Memories) 存储卡(Memory Cards) 静态数据存储器(Static Memories) 微处理器芯片(Microprocess ICs)6800 系列(6800 Family)8051 系列(8051 Family)ARM 系列(ARM Family)AVR 系列(AVR Family)Parallax 公司微处理器(BASIC Stamp Modules)HCF11 系列(HCF11 Family)PIC10 系列(PIC10 Family )PIC12 系列(PIC12 Family)PIC16 系列(PIC16 Family)PIC18 系列(PIC18 Family)Z80 系列(Z80 Family)CPU 外设(Peripherals)杂项(Miscellaneous)含天线、ATA/IDE硬盘驱动模型、单节与多节电池、串行物理接口模型、晶振、动态与通用保险、模拟电压与流符号、交通信号灯建模源(Modelling Primitives)模拟(仿真分析)(Analogy-SPICE)数字(缓冲器与门电路)(Digital-Buffers&Gates)数字(杂类)(Digital--Miscellaneous)数字(组合电路)(Digital--Combinational)数字(时序电路)(Digital--Sequential)混合模式(Mixed Mode)可编程逻辑器件单元(PLD Eleme nts)实时激励源(Realtime Actuators)实时指示器(Realtime Indictors)运算放大器(Operational Amplifiers)单路运放(Single)二路运放(Dual)三路运放(Triple)四路运放(Quad)八路运放(Octal)理想运放(Ideal)大量使用的运放(Macromodel)光电子类器件(Optoelectronics)七段数码管(7-Segment Displays)英文字符与数字符号液晶显示器(Alpha nu meric LCDs) 条形显示器(Bargraph Displays)点阵显示屏(Dot Matrix Display)图形液晶(Grphical LCDs)灯泡(Lamp)液晶控制器(LCD Controllers)液晶面板显示(LCD Pan els Displays)发光二极管(LEDs)光耦元件(Optocouplers)串行液晶(Serial LCDs)可编程逻辑电路与现场可编程门阵列(PLD&FPGA)无子类电阻(Resistors)0.6W 金属膜电阻(0.6W Metal Film)10W 绕线电阻(10W Wirewound)2W 金属膜电阻(2W Metal Film)3W 金属膜电阻(3W Metal Film)7W 金属膜电阻(7W Metal Film)通用电阻符号(Generic)高压电阻(High Voltage)负温度系数热敏电阻(NTC)排阻(Resisters Packs)滑动变阻器(Variable)可变电阻(Varistors)仿真源(Simulator Primitives)触发器(Flip-Flop)门电路(Gates)电源(Sources)扬声器与音响设备(Speaker&Sou nders)无子分类开关与继电器(Switch&Relays)键盘(Keypads)普通继电器(Generic Relays)专用继电器(Specific Relays)按键与拨码(Switchs)开关器件(Switching Devices)双端交流开关元件(DIACs)普通开关元件(Generic)可控硅(SCRs)三端可控硅(TRIACs)热阴极电子管(Thermionic Valves)二极真空管(Diodes)三极真空管(Triodes)四极真空管(Tetrodes)五极真空管(Pentodes)转换器(Transducers)压力传感器(Pressures)温度传感器(Temperature)晶体管(Transistors)双极性晶体管(Bipolar)普通晶体管(Generic)绝缘栅场效应管(IGBY/Insulated Gate Bipolar Transistors 结型场效应晶体管(JFET)金属-氧化物半导体场效应晶体管(MOSFET)射频功率LDMOS晶体管(RF Power LDMOS) 射频功率VDMOS晶体管(RF Power VDMOS) 单结晶体管(Unijunction)CMOS 4000 系列(CMOS 4000 seriesTTL 74 系列(TTL 74 series)TTL 74增强型低功耗肖特基系列(TTL 74ALS Series)TTL 74增强型肖特基系列(TTL 74AS Series)TTL 74 高速系列(TTL 74F Series)TTL 74HC 系列/CMOS 工作电平(TTL 74HC Series)TTL 74HCT 系歹U /TTL 工作电平(TTL 74HCT Series)TTL 74低功耗肖特基系列(TTL 74LS Series)TTL 74 肖特基系列(TTL 74S Series)加法器(Adders)缓冲器/驱动器(Bufers&Drivers)比较器(Comparators)计数器(Counters)解码器(Decoders)编码器(Encoders)存储器(Memory)触发器/锁存器(Flip-Flop&Latches)分频器/定时器(Frequency Dividers & Timers)门电路/反相器(Gates&lnverters)数据选择器(Multiplexers)多谐振荡器(Multivibrators)振荡器(Oscillators)锁相环(Phrase-Locked-Loop,PLL)寄存器(Registers)信号开关(Signal Switches) 收发器(Tranxceivers)杂类逻辑芯片(Misc.Logic)Proteus isis 的元件库中英对照Proteus元件名称对照1元件名称屮文名说明7407 驱动门1N914 二极管74Ls00 与非门74LS04 非门74LS08 与门74LS390 TTL 双十进制计数器7SEG 4 针BCD-LED俞出从0-9对应于4根线的BCD码7SEG 3-8 译码器电路BCD-7SEG[size=+0]转换电路ALTERNATOR 交流发电机AMMETER-MILLI m安培计AND 与门BATTERY 电池/电池组BUS 总线CAP 电容CAPACITOR 电容器CLOCK 时钟信号源CRYSTAL 晶振D-FLIPFLOP D 触发器FUSE 保险丝GROUND 地LAMP 灯LED-RED 红色发光二极管LM016L 2 行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7, RS R/W EN三个控制端口(共14线),工作电压为5V。

MB85RC64中文

铁电存储器MB85RC64(8K×8)1.概述MB85RC64了FRAM(铁电随机存取记忆体)独立芯片配置了8192×8位,形成铁电工艺和硅栅CMOS工艺技术非易失性内存中的细胞。

MB85RC64采用两线串行接口(与世界标准的I2C总线兼容)。

与SRAM不同的MB85RC64是无需使用数据备份电池,能够保留数据。

MB85RC64的读写次数10亿次,与EPROM和FLASH相比,有显著的改善。

而且不在向写完存储器后,不需要查询序列。

2.特性●位操作:8192×8位●工作电压:2.7V—3.3V●工作频率:400KHz●两串行总线:I2C总线2.1标准版,支持标准模式和快速模式,由SCL和SDA控制。

●工作温度范围:-40℃—85℃●数据保持:10年(55℃)●读写寿命:至少每位10亿次●封装:Plastic / SOP, 8-pin (FPT-8P-M02)●低电压消耗:工作电流0.15mA,待机电流5uA3.管脚分配3.管脚功能描述管教编号管脚名功能描述1—3 A0/A1/A2 器件地址一个I2C总线可以连接8个和MB85RC64类似的器件。

通过将A0/A1/A2与VDD和VSS连接,确定每个器件的地址。

如果A0/A1/A2未连接,默认为0。

CPU通过SDA线输出一个地址与器件进行匹配。

4 VSS 数字地5 SDA 数据IO串口这是双向通信的数据IO口,用来读写铁电存储器的阵列数据,这是开漏极输出,可能是与其它漏极开路(或者集电极开路信号总线)进行线或运算,因此需要一个上拉电阻连接到外部电路。

6 SCL 时钟串口这是时钟输入口,时钟上升沿进行数据采样,下降沿进行数据输出。

7 WP 写保护WP是H电平,禁止写入。

WP是L电平,可进行写数据,如果WP没有置位,默认为L电平。

而读数据操作,不受WP 管脚的限制。

8 VDD 电源电压4.模块框图5.I2C电路MB85RC64有两线串行接口,支持I2C总线,并作为从器件工作。

LM331中文资料_中文手册_芯片中文资料_芯片中文手册

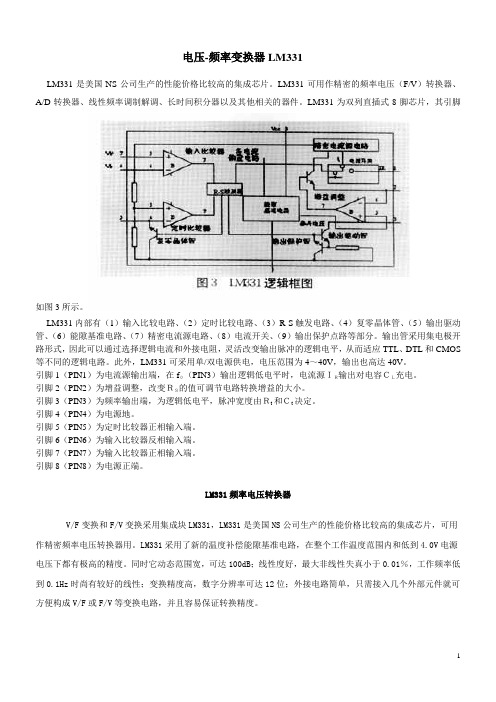

电压-频率变换器LM331LM331是美国NS公司生产的性能价格比较高的集成芯片。

LM331可用作精密的频率电压(F/V)转换器、A/D转换器、线性频率调制解调、长时间积分器以及其他相关的器件。

LM331为双列直插式8脚芯片,其引脚如图3所示。

LM331内部有(1)输入比较电路、(2)定时比较电路、(3)R-S触发电路、(4)复零晶体管、(5)输出驱动管、(6)能隙基准电路、(7)精密电流源电路、(8)电流开关、(9)输出保护点路等部分。

输出管采用集电极开路形式,因此可以通过选择逻辑电流和外接电阻,灵活改变输出脉冲的逻辑电平,从而适应TTL、DTL和CMOS 等不同的逻辑电路。

此外,LM331可采用单/双电源供电,电压范围为4~40V,输出也高达40V。

引脚1(PIN1)为电流源输出端,在f0(PIN3)输出逻辑低电平时,电流源IR输出对电容CL充电。

引脚2(PIN2)为增益调整,改变RS的值可调节电路转换增益的大小。

引脚3(PIN3)为频率输出端,为逻辑低电平,脉冲宽度由Rt和Ct决定。

引脚4(PIN4)为电源地。

引脚5(PIN5)为定时比较器正相输入端。

引脚6(PIN6)为输入比较器反相输入端。

引脚7(PIN7)为输入比较器正相输入端。

引脚8(PIN8)为电源正端。

LM331频率电压转换器V/F变换和F/V变换采用集成块LM331,LM331是美国NS公司生产的性能价格比较高的集成芯片,可用作精密频率电压转换器用。

LM331采用了新的温度补偿能隙基准电路,在整个工作温度范围内和低到4.0V电源电压下都有极高的精度。

同时它动态范围宽,可达100dB;线性度好,最大非线性失真小于0.01%,工作频率低到0.1Hz时尚有较好的线性;变换精度高,数字分辨率可达12位;外接电路简单,只需接入几个外部元件就可方便构成V/F或F/V等变换电路,并且容易保证转换精度。

图2是由LM331组成的电压频率变换电路,LM331内部由输入比较器、定时比较器、R-S触发器、输出驱动、复零晶体管、能隙基准电路和电流开关等部分组成。

2741S资料

FAR EAST

Bel Fuse Ltd. 8F / 8 Luk Hop Street San Po Kong Kowloon, Hong Kong Tel 852-2328-5515 Fax 852-2352-3706

EUROPE

Bel Fuse Europe Ltd. Preston Technology Management Centre Marsh Lane, Suite G7, Preston Lancashire, PR1 8UD, U.K. Tel 44-1772-556601 Fax 44-1772-888366

Bel Fuse Inc. 198 Van Vorst Street, Jersey City, NJ 07302 • Tel 201-432-0463 • Fax 201-432-9542 • T1-57

元器件交易网

HIGH FREQUENCY MAGNETICS

TM00114

•

•

•

ELECTRICAL SPECIFICATIONS AT 25° C

Turns Ratio ± 2% Part Number Pri : Sec DCR Ω max Pri Sec Inductance Unbalance5 of CT windings Winding % max

SCHEMATICS

2741S 2741T

5

S

S

4

3 6 CT 2

4

CT 6

3 CT

5

7

2

1 PRIMARY SECONDARY

7 1 PRIMARY SECONDARY

©2000 Bel Fuse Inc. Specifications subject to change without notice. 09.00

VAR-SOM-MX8M-PLUS based on NXP i.MX 8M Plus Evalua

VAR-SOM-MX8M-PLUS based on NXP i.MX 8M PlusEvaluation Kit Quick Start GuideFeatures:1. Power ON Switch (SW7)2. 12V DC In Jack (J24)3. USB Debug (J29)4. micro SD Card slot (J28)5. USB 3.0 OTG (J26)6. USB 2.0 Host (J23)7. Gigabit Ethernet #0 (J21) 8. Gigabit Ethernet #1 (J20)9. MIPI-CSI #1 Camera connector [optional] (J19) 10. Miscellaneous Header #1 (J17)11. HDMI/ MIPI-CSI #2 Camera connector[optional] (J13)12. Mini PCI Express Connector (J15) 13. Miscellaneous Header #2 (J3) 14. SOM Connector (J1) 15. LVDS#B Header (J5)16. LVDS#A/ DSI Header (J7) 17. Fan Power Connector (J9) 18. Digital Microphone (U1) 19. Resistive Touch (J10) 20. Capacitive Touch (J11)21. User Buttons (SW1, SW2, SW4) 22. Line-In Connector (J12)23. Headphones Connector (J14) 24. Boot Select Switch (SW3)25. SAI/I2C/SPI/CAN Header (J16) 26. Reset Button (SW5)27. PWR Select Switch (SW6) 28. UART/PWM Header (J18) 29. RTC Battery Holder (JBT1)Evaluation kit initial Setup1. Carefully remove the 7” LCD and Symphony-Board from the package.2. Connect the 7” LCD Display and Touch cablesto the Evaluation Kit connectors J7, J11 respectively.Note:connect the display cable with the red wire on pin 1. Connect the touch cable with the metal contacts facing down.3. Plug the USB type A to micro B cable betweenthe USB debug connector (J29) and a PC USB port.4. For heatsink assembly instructions, pleasefollow the VHP-VS8M documentation .Please note that the heatsink is mainly used for CPU/GPU intensive applications and may be required per your specific use case.P/N VSS0177AVAR-SOM-MX8M-PLUS based on NXP i.MX 8M PlusEvaluation Kit Quick Start GuideSetting the host PC for debug1. Download any PC terminal software (e.g. Putty ).2. Set the PC terminal software parameters as follows:- Baud Rate: 115200 - Data bits: 8 - Stop bits: 1 - Parity: None- Flow Control: NoneBooting from eMMC1. Set Boot select switch (SW3) to “Internal” position to boot from the VAR-SOM-MX8M-PLUS internal storage.2. Plug the wall adapter into the 12V power jack (J24) and to a 120VAC~240VAC power source.3. Set Power ON switch (SW7) to ON state.4. Boot messages are printed within the PC terminal window.Booting from a micro SD cardThe microSD card is supplied within the package. Updated SD card images can also be downloaded from the Variscite FTP server.See more details in the recovery SD card section in the Variscite Wiki pages.1. Set Power ON switch (SW7) to off state.2. Set Boot select switch (SW3) to “SD ” positionin order to boot from SD Card.3. Push microSD card into the microSD cardslot (J28) of the Symphony-Board.4. Set Power ON switch (SW7) to ON state.5. Boot messages are print ed within PC’sterminal window.(Re-)Installing the file system to eMMCPlease refer to the recovery SD card section in the Variscite Wiki pages.Linkso Wiki page:https:///index.php?title=VAR-SOM-MX8M-PLUSo VAR-SOM-MX8M-PLUS Evaluation kits:https:///product/evaluation-kits/var-som-mx8m-plus-evaluation-kits/o VAR-SOM-MX8M-PLUS System on Module:https:///product/system-on-module-som/cortex-a53-krait/var-som-mx8m-plus-nxp-i-mx-8m-plus/o Symphony carrier board:https:///product/single-board-computers/symphony-board/o Customer portal:https:///loginThank you for purchasing Variscite’s product.For additional assistance please contact: *******************。

海凌科电子 HLK-7688A 硬件手册说明书

深圳市海凌科电子有限公司HLK-7688A硬件手册版本:V1.2修改日期:2017-2-27版权所有@深圳市海凌科电子有限公司目录1.产品简介 (1)1.1.基本参数 (1)2.方框图 (2)2.1.典型应用 (3)2.2.规格 (4)2.3.接口数量 (4)3.电气特性 (5)3.1.供电要求 (5)3.2.射频特性 (5)3.2.1.802.11B11M (5)3.2.2.802.11G54M (5)3.2.3.802.11N MCS7(HT20) (6)3.2.4.802.11N_MCS7(HT40) (6)4.模块引脚定义 (7)4.1.引脚图定义图 (7)4.2.默认引脚图定义 (8)5.模块尺寸图 (10)6.回流焊温度曲线 (11)硬件手册1.产品简介海凌科电子出品的HLK-7688A模块是一款基于联发科MT7688AN为核心的低成本低功耗的物联网模块。

该模块引出了MT7688AN的所有接口,支持Linux和OpenWrt操作系统及自定义开发,具有丰富的接口和强大的处理器,可以广泛的应用于智能设备或云服务应用等,并可以自由进行二次开发。

1.1.基本参数⏹超强数据处理能力,MCU主频达580MHz⏹150M的无线速率⏹支持802.11b/g/n模式⏹20/40信道带宽⏹支持802.11v⏹支持AP,STA及AP,STA混合模式⏹5个10/100M自适应网口⏹1个USB2.0主机接口⏹多种接口SPI/SD-XC/eMMC⏹丰富的外设接口,SPI,I2C,I2S,PCM,UART,JTAG,GPIO⏹广泛应用于物联网⏹内置强大的PMU⏹支持16个Multiple BSSID⏹支持多种加密方式WEP64/128,TKIP,AES,WPA,WPA2,WAPI⏹支持QoS,WMM,WMM-PS⏹支持多种系统,Linux2.6.36SDK,OpenWrt3.10硬件手册2.方框图HLK-7688模块架构图EINT Ethernet UART GPIO PWM USB_HOSTSPI SPIS I 2C I 2S JTAG SDXCMT7688AN3.3V40MHzDDR2(128MB)SPI Flash(32MB)IPEX Connector硬件手册2.1.典型应用HLK-7688A典型外设接口图硬件手册2.2.规格项目参数备注模块型号HLK-7688A版本V1.2主芯片MT7688AN内核MIPS24KEc主频580MHz内存DDR2128MB可定制DDR264M/32MB Flash32MB可定制16MB/8MB 温度环境温度:-40℃~85℃湿度使用:10~95%(不凝结)存储:5~95%(不凝结)尺寸18mm×32.8mm×2.8mm2.3.接口数量接口模块具备的接口出厂默认固件支持的接口WiFi标准IEEE802.11b/g/n支持Ethernet接口5个10M/100M自适应1个WAN、4个LAN UART3路2路UART具备透传功能SDIO1路不支持SPI1路不支持I2C1路不支持I2S1路不支持PWM1路不支持GPIO8路以上已定义功能说明:1,模块出厂默认烧写的为我司基于Linux开发的固件;该固件的Ethernet、WiFi、UART0和UART1具有透传功能。

Embest Product List of 2010_V40191

V40191Embest Products List 2010 - ARM Tools DivisionOrder#Product Name Part Number IntroductionUnitPriceSortByPicture StatusSTR1STM32F103R100ARM-CM3 Board MCBSTM32CPU:ST STM32F103RB,ARM Cortex-M3 core, up to 72MHz,inner 128KBFlash and 20KB SRAM.Features: One serial interface, analog input (via potentiometer), one CANinterface, LCD, USB, and eight LEDs etc.62ST AvailableSTV2STM32F103V100ARM-CM3 Board EMSTM32V100CPU:STM32F103VBT6,72MHz,ARM Cortex-M3 core, up to 72MHz,inner128KB Flash and 20KB SRAM.Features: This board is the latest generation of full function evaluationboard produced by Embest for STMicroelectronic ARM Cortex-M3 core-based processors, helpful for users to evaluate the powerful capability ofSTM32 with an extensive range of peripherals, such as USB, MotorControl,CAN,SD card,Smart card,UART etc.136ST AvailableSZE1STM32F103ZEARM-CM3 Board EM-STM3210E CPU:STM32F103ZE,ARM Cortex-M3 core, up to 72MHz,inner 512KBFlash and 64KB SRAM.Features: One serial interface, analog input (via potentiometer), analogoutput (to speaker), one CAN interface, QVGA LCD, joystick, USB,MicroSD Card interface, and eight LEDs etc.136ST AvailableP368NXP LPC2368ARM7S Board LPCEB2300-68CPU: NXP LPC2368, ARM7S core, up to 72 MHz, inner 512KB Flash and32KB SRAM.Features: 1 ADC input, 1Audio ouput, 1 16x2 character LCD (TS1620-1) ,1 USB2.0 Device,2 UART, 1 RJ45, 2 CAN Bus interface, SD card interfaceetc.191NXP AvailableP378NXP LPC2378ARM7S Board LPCEB2300-78CPU: NXP LPC2378, ARM7S core, up to 72 MHz,inner 512KB Flash and58KB SRAM.Features: 1 ADC input, 1Audio ouput, 1 16x2 character LCD (TS1620-1) ,1 USB2.0 Device,2 UART, 1 RJ45, 2 CAN Bus interface, SD cardinterface.212NXPAvailable6LEKK LM-EKK8962 ARM-CM3 Kit LM3S8962-EB CPU: Stellaris LM3S8962, ARM Cortex-M3 core, with fully-integrated10/100 Ethernet controller and CAN MAC.Features: USB cable provides serial communication, debugging, andpower, OLED graphics display, microSD card slot.144LUMINARY AvailableEBH1Emlink for DSP EMLINK-BH Memory downloading and debugging speed upto 120KB/S(1.2Mbps),support Blackfin BF531,BF532,BF533,BF534,BF536,BF537 underVDSP++ 3.5,4.0,4.5,5.0. support Flash programmer of VDSP++.297EMBEST AvailableEAH1Emlink for ARM EMLINK-AH USB to JTAG adapter, support Keil MDK-ARM and IAR EWARM, memorydownloading and debugging speed up to 115KB/S, smart size (smallerthan name card).168EMBEST AvailableP758NXP LPC1758ARM-CM3 Board EM-LPC1700-58CPU: NXP LPC1758, Cortex-CM3, up to 100MHz, 512KB Flash, 64KB SRAMFeatures: Color QVGA TFT LCD, 10/100 Ethernet Port, USB 2.0 FullSpeed - USB, USB-OTG & USB Host2 CAN Interfaces, 2 Serial Ports, SD/MMC Card Interface5-position Joystick and push-button, 52 GPIO pins 191NXP AvailableP768NXP LPC1768ARM-CM3 Board EM-LPC1700-CPU: NXP LPC1768, Cortex-CM3, up to 100MHz, 512KB Flash,64KB SRAMFeatures: Color QVGA TFT LCD, 10/100 Ethernet Port, USB 2.0Full Speed - USB, USB-OTG & USB Host2 CAN Interfaces, 2 Serial Ports, SD/MMC Card Interface5-position Joystick and push-button, 70 GPIO pins191NXP Available P68L NXP LPC1768Starter Kit LPC1768-SK This is the low cost development kit for NXP LPC1766 (100MHz, the very fast Cortex-M3 processor), including the LPC1766 evaluationboard(P766) and Emlink for ARM(EAH1)JTAG adapter, so thedevelopers can easy start to learn and test all the relevantapplications on it, or evaluate your new project design through thisentire system.293NXPAvailableSZEL ST STM32F103ZEStarter Kit STM3210E-SK The development kit for STM32F103ZE (72MHz, the very popular ARMCortex-M3 processor), including the STM32F103ZE evaluationboard(SZE1) and Emlink for ARM(EAH1) JTAG adapter, so the developerscan easy start to learn and test all the relevant applications on it, orevaluate your new project design through this entire system.293ST AvailableLICA Emlink for ARMLicenseSW_LICA Windows Node Lock license for 2 seats each EAH1 hardware.32EMBEST AvailableSTRL STM32F103R100Starter Kit MCBSTM32-SK The development kit for STM32F103RB (72MHz, the very popular ARMCortex-M3 processor), including the STM32F103V100 evaluationboard(STR1) and Emlink for ARM(EAH1) JTAG adapter, so the developerscan easy start to learn and test all the relevant applications on it, orevaluate your new project design through this entire system.187ST AvailableSTVL STM32F103V100Starter Kit STM32V100-SK This is the low cost development kit for STM32F103VBT6 (72MHz, the verypopular ARM Cortex-M3 processor), including the STM32F103V100evaluation board(STV2) and Emlink for ARM(EAH1) JTAG adapter, so thedevelopers can easy start to learn and test all the relevant applications onit, or evaluate your new project design through this entire system.248ST AvailableAT3U AT91SAM3U ARM-CM3 Board EM-AT91SAM3U CPU: ATMEL AT91SAM3U4E, 96 MHz Cortex M3 Flash MCU with High-Speed USB Atmel introduces SAM3U series which is the world's first 32-bitARM Cortex M3 Flash microcontroller with high-speed 480 Mbps USB +Phy.187ATMEL AvailableP766NXP LPC1766ARM-CM3 Board EM-LPC1700-66CPU: NXP LPC1766, Cortex-CM3, up to 100MHz, 256KB Flash, 64KBSRAMFeatures: Color QVGA TFT LCD, 10/100 Ethernet Port, USB 2.0 FullSpeed - USB, USB-OTG & USB Host2 CAN Interfaces, 2 Serial Ports, SD/MMC Card Interface5-position Joystick and push-butt191NXPAvailableP76L NXP LPC1766Starter Kit LPC1766-SK This is the low cost development kit for NXP LPC1766 (100MHz, the very fast Cortex-M3 processor), including the LPC1766 evaluation board(P766)and Emlink for ARM(EAH1)JTAG adapter, so the developers can easy startto learn and test all the relevant applications on it, or evaluate your newproject design through this entire system.293NXP AvailableP47B NXP LPC2478ARM7S Board EM-LPC2478B CPU: NXP LPC2478, ARM7S core, up to 72 MHz, 512KB Flash, 98KB SRAM; 1 ADC input, 1Audio ouput, 1 16x2 character LCD (TS1620-1) , 1USB2.0 Device, 2 UART, 1 RJ45, 2 CAN Bus interface, SD card interfaceetc.297NXP AvailableIDEL Embest IDE forARM License SW_IDEL Windows Node Lock Licese for 1 seat. Embest IDE for ARM is a complete solution for embedded arm development, integrated GNUGCC for ARM compiler, linker and GCC library, supported text/hexfile editor, debugger, flash programmer.59EMBEST AvailableECEP PowerICE forARM POWERICE an ARM7, ARM9 JTAG emulator, connects PC parallel port to ARM JTAG interface to download and debug program both in RAM orFlash memory space, supports online flash programming.180EMBEST AvailableECEU UNetICE for ARM UNETICE an ARM7, ARM9 JTAG emulator, connects PC USB or Ethernetport to ARM JTAG interface to download and debug program both inRAM or Flash memory space, supports online flash programming.419EMBEST AvailableP7BL P47B + 1piece LCDpanel LPC2478B-LM LPC2748 evaluation board standard configuration plus TFT LCD Panel,320x240329NXP AvailableAT3L ATMELAT91SAM3UStarter Kit AT91SAM3U-SK The development kit for AT91SAM3U (96MHz, the ARM Cortex-M3processor built-in High Speed USB controller), including the AT91SAM3U evaluation board(AT3U) and Emlink for ARM(EAH1)JTAG adapter, so thedevelopers can easy start to learn and test all the relevant applications onit, or evaluate your new project design through this entire system.288ATMEL AvailableLM35TFT LCD Panel forP47B LCD3500LCD ADAPTER,320x240,with touch panel 66EMBEST AvailableP75L NXP LPC1758Starter Kit LPC1758-SK The development kit for NXP LPC1758 (100MHz, the very fast Cortex-M3processor), including the LPC1758 evaluation board(P758) and Emlink forARM(EAH1)JTAG adapter, so the developers can easy start to learn andtest all the relevant applications on it, or evaluate your new project designthrough this entire system.293NXP AvailableS364Samsung S3C6410 ARM11Board MPC6410This board is based on Samsung S3C6410 ARM11 processor,which is specifically designed for mobile phones, notebook,industrial navigation system and general applications. The boardprovides a wide range of peripherals, supports Windows EmbeddedCE 6.0, Linux2.6, Android and Ubuntu operating system.535SAMSUNG Available A9G4ATMEL SAM9G45 ARM9Board MPC9G45This board supports application development on the company's 400MHz ARM926 -based embedded microprocessor (MPU) with DDR2memory. Onboard flash memory includes 2 Gigabytes (GB) ofNAND flash and 32 Mb (2M x 16) flash memory, and the peripheralsinclude a high-speed (HS) USB host/device port, a second HS USBhost port, an Ethernet 10/100 interface, two high-speed TBD ATMEL AvailableSTMC ST STM32F107ARM-CM3 Board EM-STM32C Built in the STMicroelectronic's ARM Cortex-M3 core basedSTM32F107VCT microcontroller, operating at up to 72MHzfrequency, integrates a wide rang of peripherals, such as USB OTG,USB Host, Ethernet, two CAN interfaces, microSD card andsmartcard interface, TFT LCD interface, three JTAG Debuginterfaces, etc.198ST AvailableP130NXP LPC1300ARM-CM3 Board EM-LPC1300This board is a brand new, cost-effective but high-performanceevaluation tool of the ARM Cortex-M3 based LPC1300 controllerfamily from NXP.49NXP AvailableS4CF S3C2440 CoreBoard I HY2440-F This Core Board is based on the Samsung S3C2440 ARM920T processor which works at up to 400MHz. The board has 64MBSDRAM and 64MB NAND Flash, provides various power supplymethods and supports WindowsCE4.2/5.0, 6.0 and Linux2.6.141SAMSUNG AvailableS4CG S3C2440 CoreBoard II HY2440-G This Core Board is based on the Samsung S3C2440 ARM920T processor which works at up to 400MHz. The board has 64MBSDRAM and 64MB NAND Flash, provides various power supplymethods and supports WindowsCE4.2/5.0, 6.0 and Linux2.6.124SAMSUNG AvailableB80C UART to WifiModel EMB-380-C A UART/Wi-Fi converter embedded with TCP/IP protocol to access local area network or internet through wireless, support the TCP/IPprotocol, IEEE 802.11 b/g protocol, and DATA converting firmwarebetween UART and Wi-Fi.85EMBEST AvailableIDEU Embest IDE forARM Kits U IDEKIT-U EmbestIDE+UNetICE: an entire embedded development enironment for ARM.1320EMBEST AvailableIDEP Embest IDE forARM kits P IDEKIT-P EmbestIDE+PowerICE: an entire embedded development enironment for ARM.1080EMBEST AvailableEFPA FlashProgrammer forARM SW_EFP Embest Flash Programmer is used for flash chip programming in theembedded system developing based on ARM series processors,especially good for programming surface mounted flash chip.169EMBEST AvailableEIDE Embest IDE forARM SW_IDE Embest IDE for ARM is a complete solution for embedded armdevelopment, fully supports microcontrollers based on ARM7 orARM9 Core, offering source-level and in-circuit debugging.950EMBEST Available2010 Copyright (c) 2010-2011 All right reserved.* All prices are in US dollar. The international price does not include the shipping and handling fee.For more product information please search by Order#, Name or Keyword on our website: /en。

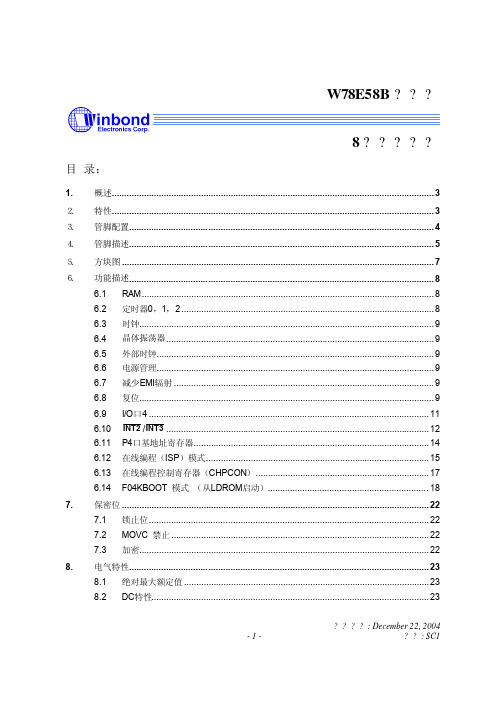

W78E58B中文资料