OCP8166 最新资料(2014版)

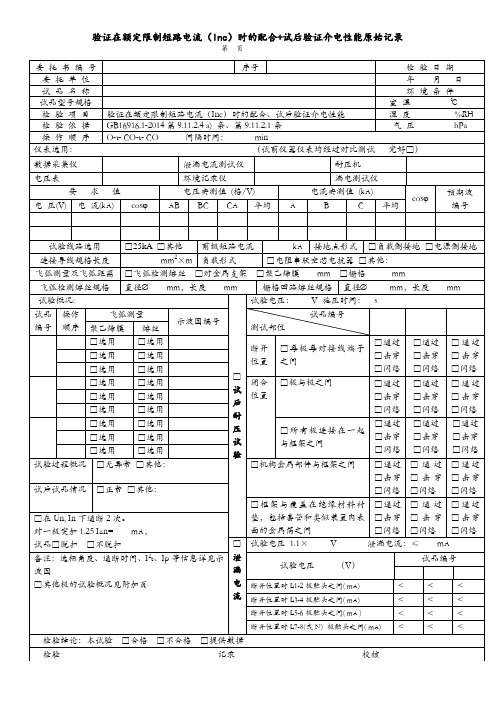

GB16916.1验证在额定限制短路电流(Inc)时的配合+试后验证介电性能原始记录模板

泄漏电流测试仪

耐压机

电压表

环境记录仪

漏电测试仪

要求值

电压实测值(格/V)

电流实测值(kA)

cos

预期波

编号

电压(V)

电流(kA)

cos

AB

BC

CA

平均

A

B

C平均试验线路选用源自□25kA□其他前级短路电流

kA

接地点形式

□负载侧接地□电源侧接地

连接导线规格长度

mm2×m

负载形式

□电阻串联空芯电抗器 □其他:

飞弧测量及飞弧距离

□飞弧检测熔丝□对金属支架□聚乙烯膜mm□栅格mm

飞弧检测熔丝规格

直径mm,长度mm

栅格回路熔丝规格

直径mm,长度mm

试验概况:

□试后耐压试验

试验电压: V 施压时间: s

试品编号

操作顺序

飞弧测量

示波图编号

试品编号

测试部位

聚乙烯膜

熔丝

□选用

□选用

断开

位置

□每极每对接线端子之间

□通过□击穿□闪烙

□通过□击穿□闪烙

□通过□击穿□闪烙

□选用

□选用

□选用

□选用

□选用

□选用

闭合

位置

□极与极之间

□通过□击穿□闪烙

□通过□击穿□闪烙

□通过□击穿□闪烙

□选用

□选用

□选用

□选用

□选用

□选用

□所有极连接在一起与框架之间

□通过□击穿□闪烙

□通过□击穿□闪烙

□通过□击穿□闪烙

□选用

□选用

□选用

□选用

试验过程概况

861分类 - 2014本稿

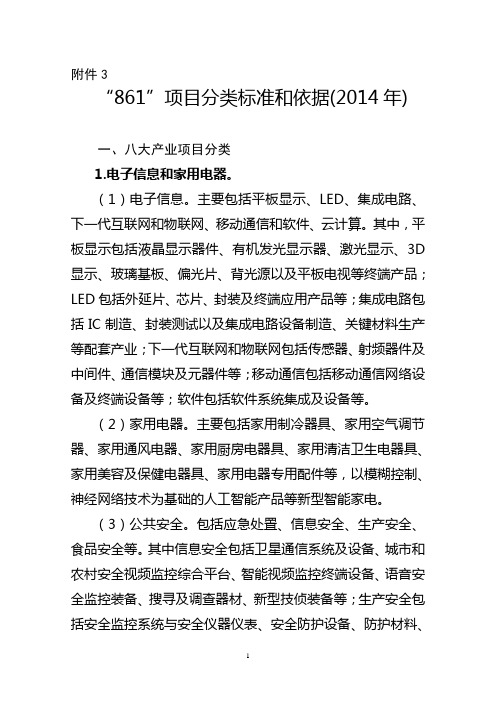

附件3“861”项目分类标准和依据(2014年)一、八大产业项目分类1.电子信息和家用电器。

(1)电子信息。

主要包括平板显示、LED、集成电路、下一代互联网和物联网、移动通信和软件、云计算。

其中,平板显示包括液晶显示器件、有机发光显示器、激光显示、3D显示、玻璃基板、偏光片、背光源以及平板电视等终端产品;LED 包括外延片、芯片、封装及终端应用产品等;集成电路包括IC制造、封装测试以及集成电路设备制造、关键材料生产等配套产业;下一代互联网和物联网包括传感器、射频器件及中间件、通信模块及元器件等;移动通信包括移动通信网络设备及终端设备等;软件包括软件系统集成及设备等。

(2)家用电器。

主要包括家用制冷器具、家用空气调节器、家用通风电器、家用厨房电器具、家用清洁卫生电器具、家用美容及保健电器具、家用电器专用配件等,以模糊控制、神经网络技术为基础的人工智能产品等新型智能家电。

(3)公共安全。

包括应急处置、信息安全、生产安全、食品安全等。

其中信息安全包括卫星通信系统及设备、城市和农村安全视频监控综合平台、智能视频监控终端设备、语音安全监控装备、搜寻及调查器材、新型技侦装备等;生产安全包括安全监控系统与安全仪器仪表、安全防护设备、防护材料、个体防护用品等;食品安全包括食品安全快速检测设备、果蔬农药残留去除专用设备、数字化X光异物检测机、数字化广泛用途色选机、食品辐照加速器等。

(4)节能产业。

包括节能电机、节能变压器、节能电器、绿色照明产品等。

2.汽车和装备制造。

(1)汽车及关键零部件。

主要包括乘用车、商务车、改装车、专用车和新能源汽车等,以及上下游配套的汽车零部件生产,还包括提升核心零部件(动力总成、电子控制等)的研发和制造等。

(2)新能源汽车。

包括纯电动汽车、燃料电池汽车、混合动力汽车、动力电池、电机及驱动模块等。

其中,纯电动汽车包括蓄电池电动汽车、蓄电池+超级电容电动汽车;混合动力汽车包括内燃机+蓄电池混合动力汽车,内燃机+超级电容混合电动汽车、内燃机+液压节能器混合动力汽车等;电机及驱动模块包括电动机、功率转换器、控制器、各种检测传感器等。

OCS LED照明解决方案 - 2016

隔离式 Triac

OCP8359 20W-50W OCP8358 12W-18W OCP8357 7W-12W

◆ 灿瑞科技LED照明电源驱动IC

隔离式AC-DC

Part No. OCP8150 OCP8151 OCP8152 OCP8153 OCP8155 OCP8153D OCP8155D OCP8156A OCP8157A OCP8158A OCP8159A 控制方式 PSR PSR PSR PSR PSR PSR PSR APFC APFC APFC APFC 输出功率 50W 7W 7W 18W 24W 18W 24W 12W 18W 30W 50W MOS管 外置 内置 内置 内置 内置 内置 内置 内置 内置 外置 外置 恒流精度 ± 3% ± 3% ± 3% ± 3% ± 3% ± 3% ± 3% ± 3% ± 3% ± 3% ± 3% 典型效率 88% 83% 83% 88% 88% 88% 88% 88% 90% 90% 90% 备注 SOT23-5封装 SOP8-1A/650V SOP8-1A/650V DIP8-2A/650V DIP8-4A/650V DIP8-2A/650V DIP8-4A/650V DIP8-2A/650V DIP8-4A/650V SOT23-6封装 SOP8封装

◆ 灿瑞科技LED照明电源驱动IC

非隔离AC-DC

Part No. 控制方式 输出功率 MOS管 恒流精度 典型效率 备注

OCP8161A

OCP8162A OCP8164A OCP8164B OCP8165A OCP8190 OCP8191

Buck+CC

Buck+CC Buck+CC Buck+CC Buck+CC Buck+CC Buck+CC

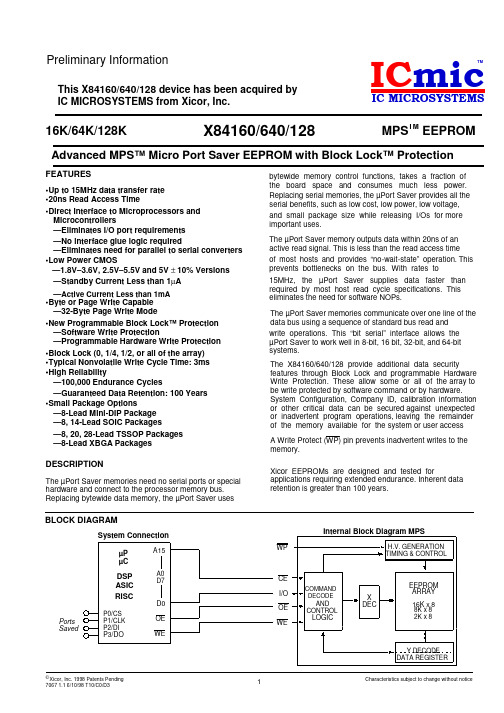

X84640-1.8资料

元器件交易网Preliminary InformationThis X84160/640/128 device has been acquired by IC MICROSYSTEMS from Xicor, Inc.ICmicTMIC MICROSYSTEMS16K/64K/128KX84160/640/128MPSTM EEPROMAdvanced MPS™ Micro Port Saver EEPROM with Block Lock™ ProtectionFEATURES•Up to 15MHz data transfer rate •20ns Read Access Time •Direct Interface to Microprocessors and Microcontrollers —Eliminates I/O port requirements —No interface glue logic required —Eliminates need for parallel to serial converters •Low Power CMOS —1.8V–3.6V, 2.5V–5.5V and 5V ± 10% Versions —Standby Current Less than 1µA —Active Current Less than 1mA •Byte or Page Write Capable —32-Byte Page Write Mode •New Programmable Block Lock™ Protection —Software Write Protection —Programmable Hardware Write Protection •Block Lock (0, 1/4, 1/2, or all of the array) •Typical Nonvolatile Write Cycle Time: 3ms •High Reliability —100,000 Endurance Cycles —Guaranteed Data Retention: 100 Years •Small Package Options —8-Lead Mini-DIP Package —8, 14-Lead SOIC Packages —8, 20, 28-Lead TSSOP Packages —8-Lead XBGA Packagesbytewide memory control functions, takes a fraction of the board space and consumes much less power. Replacing serial memories, the µPort Saver provides all the serial benefits, such as low cost, low power, low voltage, and small package size while releasing I/Os for more important uses. The µPort Saver memory outputs data within 20ns of an active read signal. This is less than the read access time of most hosts and provides “no-wait-state” operation. This prevents bottlenecks on the bus. With rates to 15MHz, the µPort Saver supplies data faster than required by most host read cycle specifications. This eliminates the need for software NOPs. The µPort Saver memories communicate over one line of the data bus using a sequence of standard bus read and write operations. This “bit serial” interface allows the µPort Saver to work well in 8-bit, 16 bit, 32-bit, and 64-bit systems. The X84160/640/128 provide additional data security features through Block Lock and programmable Hardware Write Protection. These allow some or all of the array to be write protected by software command or by hardware. System Configuration, Company ID, calibration information, or other critical data can be secured against unexpected or inadvertent program operations, leaving the remainder of the memory available for the system or user access A Write Protect (WP) pin prevents inadvertent writes to the memory. Xicor EEPROMs are designed and tested for applications requiring extended endurance. Inherent data retention is greater than 100 years.DESCRIPTIONThe µPort Saver memories need no serial ports or special hardware and connect to the processor memory bus. Replacing bytewide data memory, the µPort Saver usesBLOCK DIAGRAMSystem ConnectionµP µCA15 WPInternal Block Diagram MPSH.V. GENERATION TIMING & CONTROLDSP ASIC RISCPorts SavedP0/CS P1/CLK P2/DIA0 D7CE I/OCOMMAND DECODED0 OE WEOE WEAND CONTROLX DECEEPROM ARRAY 16K x 88K x 8 2K x 8LOGICP3/DOY DECODE DATA REGISTER© Xicor, Inc. 1998 Patents Pending7067 1.1 6/10/98 T10/C0/D31Characteristics subject to change without notice元器件交易网X84160/640/128PIN CONFIGURATIONS: Drawings are to the same scale, actual package sizes are shown in inches:8-LEAD PDIP 8-LEAD SOIC CE I/O WP V SS 1 2 X84160 3 X84640 4 .230 in. 8 7 6 5 V CC NC OE WE .190 in. NC VCC CE I/O 8-LEAD TSSOP 1 2 3 4 8 7 6 5 OE WE WP VSSPIN NAMES.114 in.X84160I/O CE OE WE WPData Input/Output Chip Enable Input Write Enable Input Supply Voltage Ground Output Enable Input Write Protect Input14-LEAD SOIC CE I/O NC NC NC WP V SS 1 2 3 4 5 6 7 .230 in. X84128 14 13 12 11 10 9 8 V CC NC NC NC NC OE WE .390 in.NC NC CE I/O NC NC NC WP VSS NC1 2 3 4 5 6 7 8 9 10X8464020 19 18 17 16 15 14 13 12 11NC NC VCC NC NC NC NC OE WE NC.250 in.roNC NC NC NC VCC NC NC .394 in. NC NC OE WE NC NC NC.252 in. 28-LEAD TSSOP NC NC CE CE CE I/O NC NC NC WP VSS NC NC NC 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 158-LEAD XBGA: Top View VCC 1 8 I/O .238 in. NC WE OE 2 7 CE 3 6 VSS 4 5 WPP2X84128e. 252 in..078 in.PIN DESCRIPTIONS Chip Enable (CE)ol etThe Chip Enable input must be LOW to enable all read/ write operations. When CE is HIGH, the chip is deselected, the I/O pin is in the high impedance state, and unless a nonvolatile write operation is underway, the device is in the standby power mode. Output Enable (OE) The Output Enable input must be LOW to enable the output buffer and to read data from the device on the I/O line.bsWrite Protect (WP) The Write Protect input controls the Hardware Write Protect feature. When WP is LOW and the nonvoltaile bit WPEN is “1”, nonvolatile writes of the X84160/640/128 control register is disabled, but the part otherwise functions normally. When WP is held HIGH, all functions, including nonvolatile write operate normally. WP going LOW while CS is still LOW will interrupt a write to the X84160/640/128 control register. If the internal Write cycle has already been initiated, WP going LOW will have no effect on write. The WP pin function is blocked when the WPEN bit in the control register is “0”. This allows the user to install the X84160/640/128 in a system with WP pin grounded and still be able to write to the control register. The WP pin functions will be enabled when the WPEN bit is set “1”.OWrite Enable (WE) The Write Enable input must be LOW to write either data or command sequences to the device. Data In/Data Out (I/O) Data and command sequences are serially written to or serially read from the device through the I/O pin.du cVCC VSS NC No Connect20-LEAD TSSOPPACKAGE SELECTION GUIDE841608-Lead PDIP 8-Lead SOIC 8-Lead TSSOP 8-Lead CSP/BGA 8-Lead PDIP 8-Lead SOIC 20-Lead TSSOP 8-Lead CSP/BGA 8-Lead PDIP 14-Lead SOIC 28-Lead TSSOP8464084128t.252 in.元器件交易网X84160/640/128DEVICE OPERATION The X84160/640/128 are serial EEPROMs designed to interface directly with most microprocessor buses. Standard CE, OE, and WE signals control the read and write operations, and a single l/O line is used to send and receive data and commands serially. Data Timing Data input on the l/O line is latched on the rising edge of either WE or CE, whichever occurs first. Data output on the l/O line is active whenever both OE and CE are LOW. Care should be taken to ensure that WE and OE are never both LOW while CE is LOW. Read Sequence A read sequence consists of sending a 16-bit address followed by the reading of data serially. The address is written by issuing 16 separate write cycles (WE and CE LOW, OE HIGH) to the part without a read cycle between the write cycles. The address is sent serially, most significant bit first, over the I/O line. Note that this sequence is fully static, with no special timing restrictions, and the processor is free to perform other tasks on the bus whenever the device CE pin is HIGH. Once the 16 address bits are sent, a byte of data can be read on the I/O line by issuing 8 separate read cycles (OE and CE LOW, WE HIGH). At this point, writing a ‘1’ will terminate the read sequence and enter the low power standby state, otherwise the device will await further reads in the sequential read mode. Sequential Read The byte address is automatically incremented to the next higher address after each byte of data is read. The data stored in the memory at the next address can be read sequentially by continuing to issue read cycles. When the highest address in the array is reached, the address counter rolls over to address 0000h and reading may be continued indefinitely. Reset Sequence The reset sequence resets the device and sets an internal write enable latch. A reset sequence can be sent at any time by performing a read/write “0”/read operation (see Figs. 1 and 2). This breaks the multiple read or write cycle sequences that are normally used to read from or write to the part. The reset sequence can be used at any time to interrupt or end a sequential read or page load. As soon as the write “0” cycle is complete, the part is reset (unless a nonvolatile write cycle is in progress). The second read cycle in this sequence, and any further read cycles, will read a HIGH on the l/O pin until a valid read sequence (which includes the address) is issued. The reset sequence must be issued at the beginning of both read and write sequences to be sure the device initiates these operations properly.Figure 1. Read SequenceCEObsOEWEol etI/O (IN)"0"A15 A14 A13 A12 A11 A10 A9 A8eP3A7 A6 A5 A4 A3 A2I/O (OUT) RESETWHEN ACCESSING: X84160 ARRAY: A15–A11=0 X84640 ARRAY: A15–A13=0 X84128 ARRAY: A15–A14=0LOAD ADDRESSroA1 A0du cD7 D6 D5 D4 D3 D2 D1 D0READ DATAt7008 FRM F04.1元器件交易网X84160/640/128Figure 2: Write SequenceCEOEWEI/O (IN)"0"A15 A14 A13 A12 A11 A10 A9 A8A7 A6 A5 A4 A3 A2 A1 A0du cD7 D6 D5 D4 D3 D2 D1 D0RESETWHEN ACCESSING: X84160 ARRAY: A15–A11=0 X84640 ARRAY: A15–A13=0 X84128 ARRAY: A15–A14=0LOAD ADDRESSroI/O (OUT)LOAD DATAP4ol etWrite Sequence A nonvolatile write sequence consists of sending a reset sequence, a 16-bit address, up to 32 bytes of data, and then a special “start nonvolatile write cycle” command sequence.epage, where data loading can continue. For this reason, sending more than 256 consecutive data bits will result in overwriting previous data. A nonvolatile write cycle will not start if a partial or incomplete write sequence is issued. The internal write enable latch is reset when the nonvolatile write cycle is completed and after an invalid write to prevent inadvertent writes. Note that this sequence is fully static, with no special timing restrictions. The processor is free to perform other tasks on the bus whenever the chip enable pin (CE) is HIGH. Nonvolatile Write Status The status of a nonvolatile write cycle can be determined at any time by simply reading the state of the l/O pin on the device. This pin is read when OE and CE are LOW and WE is HIGH. During a nonvolatile write cycle the l/O pin is LOW. When the nonvolatile write cycle is complete, the l/O pin goes HIGH. A reset sequence can also be issued during a nonvolatile write cycle with the same result: I/O is LOW as long as a nonvolatile write cycle is in progress, and l/O is HIGH when the nonvolatile write cycle is done.The nonvolatile write cycle is initiated by issuing a special read/write “1”/read sequence. The first read cycle ends the page load, then the write “1” followed by a read starts the nonvolatile write cycle. The device recognizes 32byte pages (e.g., beginning at addresses XXXXXX00000 for X84160). When sending data to the part, attempts to exceed the upper address of the page will result in the address counter “wrapping-around” to the first address on theObsThe reset sequence is issued first (as described in the Reset Sequence section) to set an internal write enable latch. The address is written serially by issuing 16 separate write cycles (WE and CE LOW, OE HIGH) to the part without any read cycles between the writes. The address is sent serially, most significant bit first, on the l/O pin. Up to 32 bytes of data are written by issuing a multiple of 8 write cycles. Again, no read cycles are allowed between writes.t"1" "0" START NONVOLATILE WRITE7008 FRM F05.1元器件交易网X84160/640/128CONTROL REGISTER The X84160/640/128 has one register that contains control bits for the devices. The control bits, WPEN, BP1, and BP0, are shown in Table 1. To read or change the contents of this register requires a one byte operation to address FFFFh. A read from FFFFh returns the one byte contents of the control register unused bits return 0. Continued reads return undefined data. A write to address FFFFh changes the value of the bits. Unused bits are written as “0”. Writing more than one byte to the control register is a violation and the operation will be aborted. After sending one byte to the control register, a start nonvolatile write cycle will latch in the new state. Table 1 7 WPEN 6 0 5 0 4 0 3 BP1 2 BP0 1 0 0 0 The Write Protect (WP) pin and the nonvolatile Write Protect Enable (WPEN) bit in the Status Register control the programmable hardware write protect feature. Hardware write protection is enabled when WP pin is LOW, and the WPEN bit is “1”. Hardware write protection is disabled when either the WP pin is HIGH or the WPEN bit is “0”. When the chip is hardware write protected, nonvolatile write is disabled to the Control Register, including the Block Protect bits and the WPEN bit itself, as well as the block-protected sections in the memory array. Only the sections of the memory array that are not block-protected can be written.Note: When the WP pin is tied to VSS and the WPEN bit is HIGH, the WPEN bit is write protected. It cannot be changed back to a “0”, as long as the WP pin is held LOW.WPEN 0 1 XWP X LOW HIGHProtected Blocks Protected ProtectedUnprotected Blocks Writable WritableProtectedTable 3. Block Lock ProtectionbsControl Register Bits BP1 0 0 1 1 BP0 0 1 0 1ol etWritableeWPEN: Write Protect Enable Bit The Write-Protect-Enable (WPEN) bit is an enable bit for the WP pin. Table 2Status Register WritableBP1, BP0: Block Protect Bits The Block Protect (BP0 and BP1) bits are nonvolatile and allow the user to select one of four levels of protection. The X84160/640/128 is divided into four segments. One, two, or all four of the segments may be protected. That is, the user may read the segments but will be unable to alter (write) data within the selected segments. The partitioning is controlled as illustrated in table 3 below.Protected WritableX84160 None 0600h–07FFh 0400h–07FFh 0000–07FFhPX84640 None5Array Address Protected X84128 None 3000h–3FFFh 2000h–3FFFh 0000h–3FFFh upper 1/4 upper 1/2 Full Array (Not including the control register.) Array1800h–1FFFh 1000h–1FFFh 0000–1FFFhOrodu ct元器件交易网X84160/640/128Low Power Operation The device enters an idle state, which draws minimal current when: —an illegal sequence is entered. The following are the more common illegal sequences: • Read/Write/Write—any time • Read/Write ‘1’—When writing the address or writing data. • Write ‘1’—when reading data • Read/Read/Write ‘1’—after data is written to device, but before entering the NV write sequence. —the device powers-up; —a nonvolatile write operation completes. While a sequential read is in progress, the device remains in an active state. This state draws more current than the idle state, but not as much as during a read itself. To go back to the lowest power condition, an invalid condition is created by writing a ‘1’ after the last bit of a read operation. Write Protection The following circuitry has been included to prevent inadvertent nonvolatile writes: —The internal Write Enable latch is reset upon power-up. —A reset sequence must be issued to set the internal write enable latch before starting a write sequence. —A special “start nonvolatile write” command sequence is required to start a nonvolatile write cycle.—The internal Write Enable latch is reset and remains reset as long as the WP pin is LOW, which blocks all nonvolatile write cycles. —The internal Write Enable latch resets on an invalid write operation. SYMBOL TABLEroWAVEFORM 6PeObsol etdu cINPUTS Must be steady May change from LOW to HIGH May change from HIGH to LOW Don’t Care: Changes Allowed N/A Will be steadyOUTPUTSWill change from LOW to HIGH Will change from HIGH to LOW Changing: State Not Known Center Line is High Impedancet—The internal Write Enable latch is reset automatically at the end of a nonvolatile write cycle.元器件交易网X84160/640/128ABSOLUTE MAXIMUM RATINGS* Temperature under Bias ...................... –65°C to +135°C Storage Temperature ........................... –65°C to +150°C Terminal Voltage with Respect to VSS .......................................–1V to +7V DC Output Current................................................... 5mA Lead Temperature (Soldering, 10 seconds)..........300°C RECOMMENDED OPERATING CONDITIONS Temperature Commercial Industrial Min. 0°C –40°C Max. +70°C +85°C +125°C *COMMENT Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Supply Voltage X84160/640/128X84160/640/128 – 2.5 X84160/640/128 – 1.8D.C. OPERATING CHARACTERISTICS (VCC = 5V ±10%) (Over the recommended operating conditions, unless otherwise specified.) Symbol ICC1 Parameter VCC Supply Current (Read) Min.PMax. 12 1 10 10 VCC x 0.3 VCC + 0.5 0.47LimitsroUnits mA Test Conditions OE = VIL, WE = VIH, I/O = Open, CE clocking = VCC x 0.1/VCC x 0.9 @ 10 MHzICC During Nonvolatile Write Cycle All Inputs at CMOS Levels CE = VCC, Other Inputs = VCC or VSS VIN = VSS to VCC VOUT = VSS to VCC mA µA µA µA V V V V IOL = 2.1mA IOH = –1mAMilitary† –55°C Notes: † Contact factory for Military availabilityISB1 ILI ILO VlL (1) VIH(1)VCC Standby CurrentInput Leakage CurrentOutput Leakage Current Input LOW VoltageInput HIGH VoltagebsVOLOutput LOW Voltage Output HIGH Voltage VCC – 0.8VOHNotes: (1) VIL Min. and VIH Max. are for reference only and are not tested.Ool etICC2VCC Supply Current (Write)e–0.5VCC x 0.7du ctLimits 4.5V to 5.5V 2.5V to 5.5V 1.8V to 3.6V元器件交易网X84160/640/128D.C. OPERATING CHARACTERISTICS (VCC = 2.5V to 5.5V) (Over the recommended operating conditions, unless otherwise specified.) Symbol Parameter Limits Min. Max. 300 Units Test Conditions OE = VIL, WE = VIH, I/O = Open, CE clocking = VCC x 0.1/VCC x 0.9 @ VCC = 2.5, 5 MHz ICC During Nonvolatile Write Cycle All Inputs at CMOS Levels CE = VCC, Other Inputs = VCC or VSS VIN = VSS to VCC VOUT = VSS to VCCICC1VCC Supply Current (Read)µAICC2 ISB1 ILI ILO VlL(1) VIH(1) VOL VOHVCC Supply Current (Write) VCC Standby Current Input Leakage Current Output Leakage Current Input LOW Voltage Input HIGH Voltage Output LOW Voltage Output HIGH Voltage VCC – 0.4 –0.5 VCC x 0.72 1 10 10 VCC x 0.3mA µA µA µA VVCC + 0.5 0.4PMax. 200 1 1 10 10 VCC x 0.3 VCC + 0.5 0.48ol etSymbolParametereD.C. OPERATING CHARACTERISTICS (VCC = 1.8V to 3.6V) (Over the recommended operating conditions, unless otherwise specified.) Limits Min. Units Test Conditions OE = VIL, WE = VIH, I/O = Open, CE clocking = VCC x 0.1/VCC x 0.9 @ VCC = 1.8V, 4 MHz ICC During Nonvolatile Write Cycle All Inputs at CMOS Levels CE = VCC, Other Inputs = VCC or VSS VIN = VSS to VCC VOUT = VSS to VCCICC1VCC Supply Current (Read)ICC2 ISB1 ILI ILOVCC Supply Current (Write) VCC Standby CurrentbsInput Leakage Current Output Leakage Current Input LOW Voltage Input HIGH Voltage Output LOW Voltage Output HIGH Voltage VCC – 0.2 –0.5 VCC x 0.7VlL(1)OVIH(1) VOL VOHNotes: (1) VIL Min. and VIH Max. are for reference only and are not tested.roV V V µA mA µA µA µA V V V Vdu cIOL = 1mA, VCC = 3V IOH = –400µA, VCC = 3V IOL = 0.5mA, VCC = 2V IOH = –250µA, VCC = 2Vt元器件交易网X84160/640/128CAPACITANCE Symbol CI/O(2) CIN(2) TA = +25°C, f = 1MHz, VCC = 5V Parameter Input/Output Capacitance Input Capacitance Max. 8 6 Units pF pF Test Conditions VI/O = 0V VIN = 0VPOWER-UP TIMING Symbol tPUR(3) tPUW(3) Parameter Power-up to Read Operation Power-up to Write OperationA.C. CONDITIONS OF TEST Input Pulse Levels Input Rise and Fall Times Input and Output Timing Levels5nsVCC x 0.5EQUIVALENT A.C. LOAD CIRCUITS5V 2.06KΩ OUTPUT 3.03KΩol eteP3V 2.8K Ω OUTPUT 30pF 5.6K Ω 30pF 2V9VCC x 0.1 to VCC x 0.92.39KΩOUTPUT30pF4.58KΩObsroNotes: (3) Time delays required from the time the VCC is stable until the specific operation can be initiated. Periodically sampled, but not 100% tested.du cMax. 2 5Notes: (2) Periodically sampled, but not 100% tested.tUnits ms ms元器件交易网X84160/640/128A.C. CHARACTERISTICS (Over the recommended operating conditions, unless otherwise specified.) Read Cycle Limits – X84160/640/128 VCC = 4.5V – 5.5V VCC = 2.5V – 5.5V VCC = 1.8V – 3.6V SymboltRC tCE tOE tOEL tOEH tLOW tHIGH tLZ(4)ParameterRead Cycle Time CE Access Time OE Access Time OE Pulse Width OE High Recovery Time CE LOW Time CE HIGH Time CE LOW to Output In Low Z CE HIGH to Output In High Z OE LOW to Output In Low Z OE HIGH to Output In High Z Output Hold from CE or OE HIGH WE HIGH Setup Time WE HIGH Hold TimeMin.70MaxMin.125Max.Min.25020 20 20 50 20 50 0 0 0 0 0 25 15 35 90 35 90 0du c25 70 25 70 70 180 70 180 0 0 0 25 0 0 25 25 30 30 25t OEH t OHZ HIGH Z t HZro0 0 0 0 25 25tHIGH tWEH tOHtHZ(4) tOLZ(4) tOHZ tOH tWES tWEH(4)P15e25Notes: (4) Periodically sampled, but not 100% tested. tHZ and tOHZ are measured from the point where CE or OE goes HIGH (whichever occurs first) to the time when I/O is no longer being driven into a 5pF load.ol ettRC tLOWtCECEbsWEtWES tOEt OELOEOI/Ot OLZ t LZDATA10tMax.Unitsns ns ns ns ns ns ns ns ns ns ns ns ns nsOb so l et ePr od u ctX84160/640/128Write Cycle Limits – X84160/640/128Notes:(5)t NVWC sequence until the self-timed, internal nonvolatile write cycle is completed.(6)Data is latched into the X84160/640/128 on the rising edge of CE or WE, whichever occurs first.(7)Periodically sampled, but not 100% tested.Symbol ParameterV CC = 4.5V – 5.5V V CC = 2.5V – 5.5V V CC = 1.8V – 3.6VUnits Min.Max.Min.Max.Min.Max.t NVWC (5)Nonvolatile Write Cycle Time 555ms t WCWrite Cycle Time70125250nst WP WE Pulse Width203550ns t WPH WE HIGH Recovery Time 5090180ns t CS Write Setup Time 000ns t CH Write Hold Time 000ns t CP CE Pulse Width203570ns t CPH CE HIGH Recovery Time 5090180ns t OES OE HIGH Setup Time 252550ns t OEH OE HIGH Hold Time 252550ns t DS (6)Data Setup Time 122030ns t DH (6)Data Hold Time 555ns t WPSU (7)WP HIGH Setup 100100150ns t WPHD (7)WP HIGH Hold100100150nsX84160/640/128CE Controlled Write CycleWE Controlled Write CycleOb soctX84160/640/1288-LEAD XBGA TYPE430±20X84640Z: Bottom ViewNOTE: ALL DIMENSIONS IN µMALL DIMENSIONS ARE TYPICAL VALUES20Ob soctX84160/640/1288-LEAD XBGA TYPEX84128: Bottom ViewNOTE: ALL DIMENSIONS IN µMALL DIMENSIONS ARE TYPICAL VALUES20Ob s octX84160/640/128NO TE:1.ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)2.PACKAGE DIMENSIONS EXCLUDE MOLDING FLASHTYP .8-LEAD PLASTIC DUAL IN-LINE P ACKAGE TYPE PHALF SHOULDER ALL MAX.X84160/640/1288-LEAD PLASTIC SMALL OUTLINE GULL WING P ACKAGE TYPE SNOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)X84160/640/128PACKAGING INFORMATION14-LEAD PLASTIC SMALL OUTLINE GULL WING P ACKAGE TYPE SNOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)Ob sou ctX84160/640/128PACKAGING INFORMATIONNOTE:ALL DIMENSIONS IN INCHES (IN P ARENTHESES IN MILLIMETERS)8-LEAD PLASTIC, TSSOP , PACKAGE TYPE V0° – 8°Ob so lt u ctX84160/640/128PACKAGING INFORMATIONNOTE:ALL DIMENSIONS IN INCHES (IN P ARENTHESES IN MILLIMETERS)20-LEAD PLASTIC, TSSOP PACKAGE TYPE V0° – 8Gage Plane Seating PlaneOb so lu ctX84160/640/128PACKAGING INFORMATIONNOTE:ALL DIMENSIONS IN INCHES (IN P ARENTHESES IN MILLIMETERS)28-LEAD PLASTIC, TSSOP PACKAGE TYPE V0° – 8Gage Plane Seating PlaneX84160/640/128LIMITED WARRANTYDevices sold by Xicor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Xicor, Inc. makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Xicor, Inc. makes no warranty of merchantability or fitness for any purpose. Xicor, Inc. reserves the right to discontinue production and change specifications and prices at any time and without notice.Xicor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Xicor, Inc. product. No other circuits, patents, licenses are implied.U.S. PATENTSXicor products are covered by one or more of the following U.S. Patents: 4,263,664; 4,274,012; 4,300,212; 4,314,265; 4,326,134; 4,393,481; 4,404,475;4,450,402; 4,486,769; 4,488,060; 4,520,461; 4,533,846; 4,599,706; 4,617,652; 4,668,932; 4,752,912; 4,829, 482; 4,874, 967; 4,883, 976. Foreignpatents and additional patents pending.LIFE RELATED POLICYIn situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurence.Xicor's products are not authorized for use in critical components in life support devices or systems.1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustainlife, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failureof the life support device or system, or to affect its safety or effectiveness.22。

特征库升级技术白皮书V11

特征库升级说明文档 ConplatConplat 特征库升级说明文档Prepared byDate2014-5-5杨兴博拟制日期Reviewed byDate评审人日期DateAuthorized by日期签发2014-5-5 页10页,共1第 Page 1 , Total 10 版权所有,侵权必究 All rights reserved特征库升级说明文档 Conplat Revision Recor修订记录修订版本作者日期Revision 描述Description Date Author version2014-3-20杨兴博初稿完成2014-5-5杨兴博按照文档规范进行修改2014-6-9杨兴博修订最新病毒特征库规格页10页,共22014-5-5 第 Page 2 , Total 10 版权所有,侵权必究 All rights reserved特征库升级说明文档 Conplat目录未定义书签。

错误!特征库简介一、...............................................未定义书签。

错误!特征库升级说明 ........................................... 二、未定义书签。

错误!设备初次启动 ................................................ 1.未定义书签。

! ................................................ 错误软件版本更换2.Conplat主线V100R003B00D013P02、神州一号V100R002B01D083之前版本及其他分支 ......................................................错误!未定义书签。

Conplat主线V100R003B00D013P02、神州一号V100R002B01D083及之后版本错误!未定义书签。

中国信息安全测评中心

中国信息安全测评中心测评公告(2019年第5号)中国信息安全测评中心是经中央批准成立的国家信息安全权威测评机构,主要职能包括:为信息技术安全性提供测评服务;信息安全漏洞分析和信息安全风险评估;信息技术产品、信息系统和工程安全测试与评估;信息安全服务和信息安全人员资质测评;信息安全技术咨询、工程监理与开发服务等。

根据国家职能授权,测评结果定期向社会公布。

特此公告。

中国信息安全测评中心二〇一九年十月附表:通过国家信息安全测评/注册信息安全工程师(CISE)的人员序号姓名证书编号发证日期有效期备注1.李辉CNITSEC2002CISE00029 2019-9-23 2022-9-22 维持2.谭述纲CNITSEC2002CISE00045 2019-9-232022-9-22维持3.杨力CNITSEC2004CISE00280 2019-9-232022-9-22维持4.黄春CNITSEC2004CISE00281 2019-9-232022-9-22维持5.沈勇CNITSEC2004CISE00285 2019-9-232022-9-22维持6.郑毅强CNITSEC2005CISE00388 2019-9-232022-9-22维持7.韩瑜CNITSEC2005CISE00728 2019-9-232022-9-22维持8.冀传坤CNITSEC2007CISE01225 2019-9-232022-9-22维持9.甘洋CNITSEC2007CISE01231 2019-9-232022-9-22维持10.金建新CNITSEC2008CISE01275 2019-9-232022-9-22维持11.颜喜宏CNITSEC2009CISE00174 2019-9-232022-9-22维持12.王喆CNITSEC2009CISE00309 2019-9-232022-9-22维持13.张鹏CNITSEC2009CISE00363 2019-9-232022-9-22维持14.熊文丹CNITSEC2009CISE00379 2019-9-232022-9-22维持15.刘志欣CNITSEC2009CISE00537 2019-9-232022-9-22维持16.冯晓冬CNITSEC2010CISE00014 2019-9-232022-9-22维持17.罗希CNITSEC2010CISE00047 2019-9-232022-9-22维持18.陈森CNITSEC2010CISE00248 2019-9-232022-9-22维持19.张腾标CNITSEC2010CISE00360 2019-9-232022-9-22维持20.赵兆CNITSEC2010CISE00369 2019-9-232022-9-22维持21.杨威CNITSEC2010CISE00424 2019-9-232022-9-22维持22.楼晓CNITSEC2010CISE00479 2019-9-232022-9-22维持23.王旭CNITSEC2010CISE00535 2019-9-232022-9-22维持24.卫威CNITSEC2011CISE00131 2019-9-232022-9-22维持25.凌晨CNITSEC2011CISE00348 2019-9-232022-9-22维持26.石磊CNITSEC2011CISE01033 2019-9-232022-9-22维持27.万京平CNITSEC2012CISE00203 2019-9-232022-9-22维持28.陈游生CNITSEC2012CISE01080 2019-9-232022-9-22维持29.邢振华CNITSEC2012CISE01052 2019-9-232022-9-22维持30.肖伟CNITSEC2012CISE01150 2019-9-232022-9-22维持31.李愿军CNITSEC2012CISE01258 2019-9-232022-9-22维持32.战莹CNITSEC2012CISE01330 2019-9-232022-9-22维持33.颜清华CNITSEC2012CISE01404 2019-9-232022-9-22维持34.韩国峰CNITSEC2012CISE01373 2019-9-232022-9-22维持35.王永琦CNITSEC2012CISE01374 2019-9-232022-9-22维持36.赵春CNITSEC2012CISE01386 2019-9-232022-9-22维持37.唐立忠CNITSEC2012CISE01437 2019-9-232022-9-22维持38.陆晨晖CNITSEC2012CISE01472 2019-9-232022-9-22维持39.杨凯利CNITSEC2013CISE00065 2019-9-232022-9-22维持40.廖谦CNITSEC2013CISE00067 2019-9-232022-9-22维持41.陈烁文CNITSEC2013CISE00119 2019-9-232022-9-22维持42.纪德伟CNITSEC2013CISE00121 2019-9-232022-9-22维持43.梁庆姿CNITSEC2013CISE00122 2019-9-232022-9-22维持44.刘冰琼CNITSEC2013CISE00123 2019-9-232022-9-22维持45.岳志鹏CNITSEC2013CISE00126 2019-9-232022-9-22维持46.张信庆CNITSEC2013CISE00127 2019-9-232022-9-22维持47.韦红金CNITSEC2013CISE00152 2019-9-232022-9-22维持48.常茜茜CNITSEC2013CISE00177 2019-9-232022-9-22维持49.王鹏CNITSEC2013CISE00178 2019-9-232022-9-22维持50.林丰洲CNITSEC2013CISE00192 2019-9-232022-9-22维持51.吴占玉CNITSEC2013CISE00193 2019-9-232022-9-22维持52.段卫东CNITSEC2013CISE00196 2019-9-232022-9-22维持53.张华云CNITSEC2013CISE00200 2019-9-232022-9-22维持54.张亚合CNITSEC2013CISE00251 2019-9-232022-9-22维持55.陈志伟CNITSEC2013CISE00295 2019-9-232022-9-22维持56.王立民CNITSEC2013CISE00313 2019-9-232022-9-22维持57.罗乐CNITSEC2013CISE00529 2019-9-232022-9-22维持58.屈闯CNITSEC2013CISE00496 2019-9-232022-9-22维持59.刘伟CNITSEC2013CISE00513 2019-9-232022-9-22维持60.庄严CNITSEC2013CISE00526 2019-9-232022-9-22维持64.钟振帆CNITSEC2013CISE00675 2019-9-232022-9-22维持65.徐逸飞CNITSEC2013CISE00613 2019-9-232022-9-22维持66.徐志元CNITSEC2013CISE00614 2019-9-232022-9-22维持67.陈曙光CNITSEC2013CISE00624 2019-9-232022-9-22维持68.李烁CNITSEC2013CISE00688 2019-9-232022-9-22维持69.冯伟CNITSEC2013CISE00702 2019-9-232022-9-22维持70.金蕊CNITSEC2013CISE00796 2019-9-232022-9-22维持71.黄海CNITSEC2013CISE00862 2019-9-232022-9-22维持72.霍立磊CNITSEC2013CISE00839 2019-9-232022-9-22维持73.陈仙住CNITSEC2013CISE00891 2019-9-232022-9-22维持74.陈永泉CNITSEC2013CISE00892 2019-9-232022-9-22维持75.黄丽荣CNITSEC2013CISE00895 2019-9-232022-9-22维持76.黄骁婷CNITSEC2013CISE00896 2019-9-232022-9-22维持77.张玮CNITSEC2013CISE00903 2019-9-232022-9-22维持78.郑晓伟CNITSEC2013CISE00904 2019-9-232022-9-22维持79.朱亮CNITSEC2013CISE01141 2019-9-232022-9-22维持80.姚磊CNITSEC2013CISE00931 2019-9-232022-9-22维持81.王蓓CNITSEC2013CISE00968 2019-9-232022-9-22维持82.魏建新CNITSEC2013CISE00972 2019-9-232022-9-22维持83.桑月秋CNITSEC2013CISE01069 2019-9-232022-9-22维持84.刘阳CNITSEC2013CISE01085 2019-9-232022-9-22维持85.马悦CNITSEC2014CISE00900 2019-9-232022-9-22维持86.李平CNITSEC2014CISE00945 2019-9-232022-9-22维持87.陈立治CNITSEC2014CISE00990 2019-9-232022-9-22维持88.罗浪涛CNITSEC2014CISE01150 2019-9-232022-9-22维持89.杨铮CNITSEC2014CISE01243 2019-9-232022-9-22维持90.蔡春景CNITSEC2014CISE01509 2019-9-232022-9-22维持91.郑太海CNITSEC2014CISE01595 2019-9-232022-9-22维持92.邢懿CNITSEC2015CISE00632 2019-9-232022-9-22维持93.余希CNITSEC2015CISE00643 2019-9-232022-9-22维持96.王东CNITSEC2015CISE00939 2019-9-232022-9-22维持97.潘善民CNITSEC2015CISE01053 2019-9-232022-9-22维持98.王陈诚CNITSEC2015CISE01288 2019-9-232022-9-22维持99.张剑峰CNITSEC2015CISE01491 2019-9-232022-9-22维持100.程璋CNITSEC2015CISE01611 2019-9-232022-9-22维持101.王立江CNITSEC2015CISE01678 2019-9-232022-9-22维持102.蒋梦凌CNITSEC2016CISE00016 2019-9-232022-9-22维持103.辜轶峰CNITSEC2016CISE00126 2019-9-232022-9-22维持104.曹渝CNITSEC2016CISE00128 2019-9-232022-9-22维持105.曹宇龙CNITSEC2016CISE00241 2019-9-232022-9-22维持106.皇甫张棣CNITSEC2016CISE00800 2019-9-232022-9-22维持107.李秉CNITSEC2016CISE00251 2019-9-232022-9-22维持108.刘玲丽CNITSEC2016CISE00402 2019-9-232022-9-22维持109.王烜CNITSEC2016CISE00404 2019-9-232022-9-22维持110.陶彦CNITSEC2016CISE00405 2019-9-232022-9-22维持111.王唐林CNITSEC2016CISE00289 2019-9-232022-9-22维持112.段正杰CNITSEC2016CISE00444 2019-9-232022-9-22维持113.黄强CNITSEC2016CISE00446 2019-9-232022-9-22维持114.江明CNITSEC2016CISE00447 2019-9-232022-9-22维持115.李坤CNITSEC2016CISE00448 2019-9-232022-9-22维持116.吕柯露CNITSEC2016CISE00449 2019-9-232022-9-22维持117.张亚珍CNITSEC2016CISE00453 2019-9-232022-9-22维持118.章其星CNITSEC2016CISE00454 2019-9-232022-9-22维持119.张亚强CNITSEC2016CISE00465 2019-9-232022-9-22维持120.蔡翔宇CNITSEC2016CISE00473 2019-9-232022-9-22维持121.文远CNITSEC2016CISE00479 2019-9-232022-9-22维持122.余基飞CNITSEC2016CISE00487 2019-9-232022-9-22维持123.陈远鹏CNITSEC2016CISE00530 2019-9-232022-9-22维持124.方武仪CNITSEC2016CISE00664 2019-9-232022-9-22维持125.孙星CNITSEC2016CISE00679 2019-9-232022-9-22维持129.朱阳阳CNITSEC2016CISE00926 2019-9-232022-9-22维持130.陈滢竹CNITSEC2016CISE00129 2019-9-232022-9-22维持131.王宁CNITSEC2016CISE00898 2019-9-232022-9-22维持132.钟慧CNITSEC2016CISE00936 2019-9-232022-9-22维持133.梁曦CNITSEC2016CISE00938 2019-9-232022-9-22维持134.林麓CNITSEC2016CISE01032 2019-9-232022-9-22维持135.刘晶晶CNITSEC2016CISE01138 2019-9-232022-9-22维持136.董玉君CNITSEC2016CISE01144 2019-9-232022-9-22维持137.孙宣CNITSEC2016CISE01149 2019-9-232022-9-22维持138.孟二飞CNITSEC2016CISE00450 2019-9-232022-9-22维持139.郝尚印CNITSEC2016CISE01222 2019-9-232022-9-22维持140.黄辉CNITSEC2016CISE01238 2019-9-232022-9-22维持141.于亚坤CNITSEC2016CISE01292 2019-9-232022-9-22维持142.刘雪梅CNITSEC2016CISE01293 2019-9-232022-9-22维持143.汤敏杰CNITSEC2016CISE01294 2019-9-232022-9-22维持144.姚梦薇CNITSEC2016CISE01295 2019-9-232022-9-22维持145.江楠CNITSEC2016CISE01297 2019-9-232022-9-22维持146.张琪CNITSEC2016CISE01298 2019-9-232022-9-22维持147.韦震CNITSEC2016CISE01268 2019-9-232022-9-22维持148.邵晋光CNITSEC2016CISE01277 2019-9-232022-9-22维持149.苏彦CNITSEC2016CISE01278 2019-9-232022-9-22维持150.黄维CNITSEC2016CISE01283 2019-9-232022-9-22维持151.林锴CNITSEC2016CISE01342 2019-9-232022-9-22维持152.魏明春CNITSEC2016CISE01320 2019-9-232022-9-22维持153.李辉CNITSEC2016CISE01440 2019-9-232022-9-22维持154.余玲CNITSEC2016CISE01450 2019-9-232022-9-22维持155.黄德俊CNITSEC2016CISE01453 2019-9-232022-9-22维持156.王泽政CNITSEC2016CISE01360 2019-9-232022-9-22维持157.姚克民CNITSEC2016CISE01375 2019-9-232022-9-22维持158.刘昉CNITSEC2016CISE01382 2019-9-232022-9-22维持161.何帆CNITSEC2016CISE01417 2019-9-232022-9-22维持162.牛晨CNITSEC2016CISE01469 2019-9-232022-9-22维持163.耿焰CNITSEC2016CISE01494 2019-9-232022-9-22维持164.张筝CNITSEC2016CISE01500 2019-9-232022-9-22维持165.周志强CNITSEC2016CISE01501 2019-9-232022-9-22维持166.魏凤CNITSEC2016CISE01506 2019-9-232022-9-22维持167.陈之华CNITSEC2016CISE01540 2019-9-232022-9-22维持168.许颖媚CNITSEC2016CISE01545 2019-9-232022-9-22维持169.高云CNITSEC2016CISE01699 2019-9-232022-9-22维持170.吴秋玫CNITSEC2016CISE01566 2019-9-232022-9-22维持171.孙佰明CNITSEC2016CISE01588 2019-9-232022-9-22维持172.李秀芬CNITSEC2016CISE01605 2019-9-232022-9-22维持173.王鹏CNITSEC2016CISE01609 2019-9-232022-9-22维持174.周昕CNITSEC2016CISE01615 2019-9-232022-9-22维持175.房浩CNITSEC2016CISE01616 2019-9-232022-9-22维持176.李伟CNITSEC2016CISE01632 2019-9-232022-9-22维持177.叶延磊CNITSEC2016CISE01710 2019-9-232022-9-22维持178.王思尧CNITSEC2016CISE01715 2019-9-232022-9-22维持179.崔岩松CNITSEC2016CISE01676 2019-9-232022-9-22维持180.葛军CNITSEC2016CISE01721 2019-9-232022-9-22维持181.章富强CNITSEC2016CISE01787 2019-9-232022-9-22维持182.胡宇辉CNITSEC2016CISE01837 2019-9-232022-9-22维持183.李军CNITSEC2016CISE01838 2019-9-232022-9-22维持184.田洋CNITSEC2016CISE01967 2019-9-232022-9-22维持185.田晶CNITSEC2016CISE01970 2019-9-232022-9-22维持186.王鹏CNITSEC2016CISE01975 2019-9-232022-9-22维持187.李景清CNITSEC2016CISE01981 2019-9-232022-9-22维持188.吕志鹏CNITSEC2016CISE01869 2019-9-232022-9-22维持189.覃岩岩CNITSEC2016CISE01872 2019-9-232022-9-22维持190.胡培军CNITSEC2016CISE01878 2019-9-232022-9-22维持191.唐振宇CNITSEC2016CISE01900 2019-9-232022-9-22维持195.寇志寅CNITSEC2016CISE02040 2019-9-232022-9-22维持196.杨翔CNITSEC2016CISE02041 2019-9-232022-9-22维持197.韩哲CNITSEC2016CISE02104 2019-9-232022-9-22维持198.肖洁CNITSEC2016CISE01950 2019-9-232022-9-22维持199.林彬CNITSEC2016CISE01951 2019-9-232022-9-22维持200.袁胜CNITSEC2016CISE02140 2019-9-232022-9-22维持201.吴志强CNITSEC2016CISE02192 2019-9-232022-9-22维持202.黄亚龙CNITSEC2016CISE02223 2019-9-232022-9-22维持203.刘海波CNITSEC2016CISE02268 2019-9-232022-9-22维持204.葛荣兴CNITSEC2016CISE02276 2019-9-232022-9-22维持205.张瑞峰CNITSEC2016CISE02416 2019-9-232022-9-22维持206.张伟琦CNITSEC2016CISE02420 2019-9-232022-9-22维持207.张雄胜CNITSEC2016CISE02421 2019-9-232022-9-22维持208.冯开CNITSEC2016CISE02423 2019-9-232022-9-22维持209.乔金玉CNITSEC2016CISE02424 2019-9-232022-9-22维持210.卢志远CNITSEC2016CISE02425 2019-9-232022-9-22维持211.任广平CNITSEC2016CISE02433 2019-9-232022-9-22维持212.任思诗CNITSEC2017CISE00016 2019-9-232022-9-22维持通过国家信息安全测评/注册信息安全管理人员(CISO)的人员序号姓名证书编号发证日期有效期备注1.杜鸿晖CNITESC2007CISO00455 2019-9-232022-9-22维持2.卢星宇CNITSEC2007CISO00449 2019-9-232022-9-22维持3.龙颂潜CNITSEC2008CISO00502 2019-9-232022-9-22维持4.邱建民CNITSEC2009CISO00191 2019-9-232022-9-22维持5.卓鹏程CNITSEC2009CISO00195 2019-9-232022-9-22维持6.张文豪CNITSEC2009CISO00197 2019-9-232022-9-22维持7.黄代安CNITSEC2009CISO00202 2019-9-232022-9-22维持8.吴兰CNITSEC2010CISO00149 2019-9-232022-9-22维持11.和正刚CNITSEC2013CISO00092 2019-9-232022-9-22维持12.刘智刚CNITSEC2013CISO00159 2019-9-232022-9-22维持13.张平CNITSEC2013CISO00161 2019-9-232022-9-22维持14.赵勇CNITSEC2013CISO00398 2019-9-232022-9-22维持15.朱严CNITSEC2013CISO00399 2019-9-232022-9-22维持16.郑茂林CNITSEC2013CISO00400 2019-9-232022-9-22维持17.张景明CNITSEC2013CISO00520 2019-9-232022-9-22维持18.陈非CNITSEC2013CISO00525 2019-9-232022-9-22维持19.闫利CNITSEC2013CISO00536 2019-9-232022-9-22维持20.陆高斌CNITSEC2014CISO00228 2019-9-232022-9-22维持21.宋燕伟CNITSEC2014CISO00317 2019-9-232022-9-22维持22.周源CNITSEC2015CISO00103 2019-9-232022-9-22维持23.张寒坤CNITSEC2015CISO00421 2019-9-232022-9-22维持24.张盛有CNITSEC2016CISO00002 2019-9-232022-9-22维持25.陈兴艳CNITSEC2016CISO00012 2019-9-232022-9-22维持26.康政辉CNITSEC2016CISO00034 2019-9-232022-9-22维持27.成首玺CNITSEC2016CISO00069 2019-9-232022-9-22维持28.吴寒平CNITSEC2016CISO00153 2019-9-232022-9-22维持29.刘超CNITSEC2016CISO00185 2019-9-232022-9-22维持30.马骎CNITSEC2016CISO00144 2019-9-232022-9-22维持31.苏晓春CNITSEC2016CISO00320 2019-9-232022-9-22维持32.贾明CNITSEC2016CISO00321 2019-9-232022-9-22维持33.于敏CNITSEC2016CISO00322 2019-9-232022-9-22维持34.佘智勇CNITSEC2016CISO00323 2019-9-232022-9-22维持35.闫振CNITSEC2016CISO00328 2019-9-232022-9-22维持36.孔祥龙CNITSEC2016CISO00340 2019-9-232022-9-22维持37.申斌CNITSEC2016CISO00352 2019-9-232022-9-22维持38.陈茜CNITSEC2016CISO00357 2019-9-232022-9-22维持39.张五一CNITSEC2016CISO00358 2019-9-232022-9-22维持40.邢昕CNITSEC2016CISO00360 2019-9-232022-9-22维持44.张明春CNITSEC2016CISO00495 2019-9-232022-9-22维持45.陈绍武CNITSEC2016CISO00519 2019-9-232022-9-22维持46.陈光敏CNITSEC2016CISO00522 2019-9-232022-9-22维持47.朱雯君CNITSEC2016CISO00563 2019-9-232022-9-22维持48.刘栋CNITSEC2016CISO00577 2019-9-232022-9-22维持49.肖华英CNITSEC2016CISO00597 2019-9-232022-9-22维持50.史晓辉CNITSEC2016CISO00715 2019-9-232022-9-22维持51.宋斌CNITSEC2016CISO00819 2019-9-232022-9-22维持通过国家信息安全测评/注册信息系统审计师(CISP-A)的人员序号姓名证书编号发证日期有效期备注1.李建军CNITSEC2013CISP-A00023 2019-9-232022-9-22维持2.韩文科CNITSEC2013CISP-A00027 2019-9-232022-9-22维持3.曹树仁CNITSEC2014CISP-A00005 2019-9-232022-9-22维持通过国家信息安全测评/注册信息安全员(CISM)的人员序号姓名证书编号发证日期有效期备注1.袁华刚CNITSEC2013CISM00476 2019-9-232022-9-22维持2.胡华锋CNITSEC2013CISM00555 2019-9-232022-9-22维持3.马家嘉CNITSEC2013CISM00701 2019-9-232022-9-22维持4.张鹏CNITSEC2014CISM00605 2019-9-232022-9-22维持5.石林晓CNITSEC2016CISM00323 2019-9-232022-9-22维持6.张权CNITSEC2016CISM00324 2019-9-232022-9-22维持。

p13 Wessa 2014

Restorative Neurology and Neuroscience32(2014)51–62DOI10.3233/RNN-139007IOS Press51 Bipolar disorder:A neural network perspective on a disorder of emotion and motivationMich`e le Wessa b,∗,Philipp Kanske c and Julia Linke aa Section for Experimental Psychopathology and Neuroimaging,Department of General Psychiatry,University Hospital Heidelberg,Heidelberg,Germanyb Department of Clinical Psychology and Neuropsychology,Institute of Psychology,Johannes Gutenberg-University Mainz,Mainz,Germanyc Department of Social Neuroscience,Max Planck Institute for Human Cognitive and Brain Sciences,Leipzig,GermanyAbstract.Bipolar disorder(BD)is a severe,chronic disease with a heritability of60–80%.BD is frequently misdiagnosed due to phenomenological overlap with other psychopathologies,an important issue that calls for the identification of biological and psychological vulnerability and disease markers.Altered structural and functional connectivity,mainly between limbic and prefrontal brain areas,have been proposed to underlie emotional and motivational dysregulation in BD and might represent relevant vulnerability and disease markers.In the present laboratory review we discuss functional and structural neuroimaging findings on emotional and motivational dysregulation from our research group in BD patients and healthy individuals at risk to develop BD.As a main result of our studies,we observed altered orbitofrontal and limbic activity and reduced connectivity between dorsal prefrontal and limbic brain regions,as well as reduced integrity offiber tracts connecting prefrontal and subcortical brain structures in BD patients and high-risk individuals.Our results provide novel insights into pathophysiological mechanisms of bipolar disorder.The current laboratory review provides a specific view of our group on altered brain connectivity and underlying psychological processes in bipolar disorder based on our own work,integrating relevantfindings from others. Thereby we attempt to advance neuropsychobiological models of BD.Keywords:Vulnerability,behavioral activation system,emotion regulation,amygdala,orbitofrontal cortex,reward,connectivity1.IntroductionBipolar disorder is a severe and chronic mental dis-order that is one of the leading causes of disability worldwide,whose lifetime costs were estimated to be in excess of$45billion in the US alone(Wyatt& Henter,1995).Among the several subtypes of bipolar spectrum disorders,bipolar I disorder is character-ized by recurrent prominent mood swings that lead ∗Corresponding author:Mich`e le Wessa,Ph.D.,Department of Clinical Psychology and Neuropsychology,Institute of Psychology, Johannes Gutenberg-University Mainz,Wallstraße3,55122Mainz, Germany.Tel.:+4961313939259;E-mail:wessa@uni-mainz.de.to alternating phases of mania and depression with interspersed periods of euthymia.Key symptoms of mania include euphoric or irritable mood,flight of ideas,pressure of speech,increased energy,and hyper-activity with an emphasis on pleasurable activities, even if they lead to negative consequences.In contrast, during depressive episodes patients report depressed mood,lack of energy and loss of interests,pessimistic thoughts,and reduced perception of and response to positive stimuli.To date,the diagnosis of bipolar disorder is based on the description of behavioral manifestations.However, due to its overlap with other psychopathological con-ditions,such as unipolar depression,schizophrenia or0922-6028/14/$27.50©2014–IOS Press and the authors.All rights reservedThis article is published online with Open Access and distributed under the terms of the Creative Commons Attribution Non-Commercial License.52M.Wessa et al./Bipolar disorder:A neural network perspectiveimpulse control disorders(Matza et al.,2005;Meyer& Meyer,2009;Mitchell et al.,2010),initial misdiagno-sis is common.This often leads to detrimental effects on the course of this disease(Findling,2009;Stens-land et al.,2008;Stensland et al.,2010)with a more severe and chronic progression in patients with late or misleading diagnosis.Therefore,research aiming at the identification of vulnerability markers of bipo-lar disorder that allow an early and valid diagnosis is particularly important.An even more serious con-dition is that in neither of the previously mentioned psychopathologies causal therapy is available.As an ultimate goal it appears therefore essential to determine biological and psychological markers that are common to different pathologies or specific for a certain illness in order to develop tailored treatments.Further,mark-ers that change during the course of the disease might show potential for improvement under treatment and are therefore important to be identified.As family and twin studies showed a high heritabil-ity of bipolar disorder of60–80%(McGuffin et al., 2003),biological vulnerability factors seem to be of special importance for this disease.The diathesis-stress model,therefore,poses a good framework to develop etiological models that incorporate biological and psy-chological factors associated with the development and maintenance of bipolar disorder.In general,such mod-els assume that the interplay of biological vulnerability factors(Greek:diathesis)with environmental factors (stress)determines the onset and course of the disorder (Jones,2004).In bipolar disorder,neurobiological abnormalities on different levels have been identified,using various methods ranging from techniques examining intracel-lular and molecular mechanisms to neuroimaging of neural networks(Langan&McDonald,2009).Neu-robiological models of bipolar disorder(Phillips et al., 2008)generally assume a hypoactive dorsal neural sys-tem including the dorsolateral prefrontal,ventrolateral prefrontal,and dorsal anterior cingulate cortex as well as the hippocampus.This dorsal system is relevant for selective attention,planning,performance mon-itoring and voluntary regulation of emotional states in bipolar disorder.It has been hypothesized that the hypoactive dorsal system interacts with a hyperac-tive ventral brain system comprising amygdala,insula, ventral striatum,ventral anterior cingulate cortex and medial orbitofrontal cortex implicated in the detection of emotionally salient stimuli,mediation of autonomic responses to emotional stimuli and the generation of an emotional state(Keener&Phillips,2007).It is assumed that an imbalance and decreased connectivity between these two systems,particularly the ventrolat-eral prefrontal cortex and the amygdala,accounts for mood instability,motivational dysregulation and cog-nitive deficits observed in patients with bipolar disorder (Cahill et al.,2009;Kurtz&Gerraty,2009;Strakowski et al.,2012;Wessa&Linke,2009).Most recently,it has been proposed that impaired white matter development in early life might pre-cede the onset of bipolar disorder.In more detail,it has been hypothesized that the impaired development of white matter results in impaired prefrontal-limbic modulation in two networks:(1)a network originat-ing in the ventrolateral prefrontal cortex and(2)a network starting from ventromedial prefrontal cor-tex.Both networks are similarly organized building iterative feedback loops that process information and modulate activity of the amygdala,the ventral striatum and the thalamus.Whereas thefirst network is assumed to be involved in the modulation of external emotional cues such as emotional faces,the second network sup-posedly regulates internal emotional states(Schneider et al.,2012;Strakowski et al.,2012).Although,the simplicity of this hypothesis is rather intriguing,we would like to point out that it neglects motivational aspects of bipolar symptomatol-ogy despite the fact that both emotion and motivation are related.Whereas the focus on emotion implies a certain state of feeling,the emphasis of motiva-tion relates to a certain state of goal pursuit like the achievement of pleasant and the avoidance of unpleas-ant feelings.Yet,to date,most of the existing studies in patients with bipolar disorder have focused on the neural correlates of aberrant emotion processing,mainly operationalized by paradigms that use emotionally evocative stimuli(e.g.,words,faces)during pas-sive viewing,implicit and explicit labeling tasks and response inhibition tasks(Houenou et al.,2011).How-ever,although tightly linked to emotion processing, the investigation of motivational processes,such as the anticipation of positive(reward)and negative con-sequences(punishment)and the response to their delivery has received little attention in thefield.Yet, the evaluation of stimuli as appetitive(reward)or aver-sive(punishment)facilitates approach or avoidance motivation and behavior(Alloy&Abramson,2010). Indeed,motivational dysregulation and altered reward processing have been hypothesized as importantM.Wessa et al./Bipolar disorder:A neural network perspective53mechanisms of the alternating phases of mania and depression and as an endophenotype of bipolar disor-der(Hasler et al.,2006).In the present laboratory review we will provide a specific view of our group on the structural and func-tional neural mechanisms underlying emotional and motivational dysregulation in bipolar disorder based on our own work.By additionally integrating relevant findings from other group we attempt to contribute to a further development of neurobiological models of bipolar disorder.2.Motivational processesMost of the structures comprised in neurobiolog-ical models of bipolar disorder are innervated by dopaminergic projections ascending from the ventral tegmental area to the mesolimbic system,includ-ing ventral striatum,amygdala and hippocampus and to the mesocortical system comprising,among oth-ers,the dorsolateral prefrontal,anterior cingulate and orbitofrontal cortex(Depue&Iacono,1989).These dopamine-irrigated structures represent the neural cor-relate of the behavioral activation system that mediates individual differences in the sensitivity and reactivity to appetitive stimuli.High sensitivity of the behavioral activation system is associated with enhanced appet-itive stimulus processing and approach-motivation as well as the diminished processing of aversive stimuli. However,the behavioral activation system might also facilitate active avoidance responses,when safety is perceived as reward,and aggressive behavior,when reward acquisition is blocked(Gray,1987).In the con-text of bipolar disorder,dysregulation model of the behavioral activation system suggests a hypersensi-tive behavioral activation system as vulnerability factor (Alloy&Abramson,2010;Depue&Iacono,1989; Uros´e vic et al.,2008).Extremefluctuations in acti-vation and deactivation of the behavioral activation system might be reflected in bipolar symptoms like “excessive involvement in pleasurable activities that have a high potential for painful consequences”dur-ing mania and“markedly diminished...pleasure in all, or almost all,activities”during depression(American Psychiatric Association,2000).On a behavioral level, reduced and delayed responses to more frequently rewarded stimuli(Pizzagalli et al.,2008)as well as longer reaction times for decisions that lead to reward or punishment(Gorrindo et al.,2005;McClure et al.,2005;Rich et al.,2005)were reported,suggesting a general deficit in responding to motivationally relevant stimuli in bipolar disorder patients.However,our own results show a more differenti-ated pattern of reward and punishment processing in bipolar disorder.In euthymic bipolar disorder patients, we observed differential learning from positive and negative consequences depending on the last illness phase of the patients(Linke et al.,2011).Interest-ingly,currently euthymic bipolar patients who last experienced a manic episode showed a bias towards positive consequences,whereas bipolar patients who last experienced a depressive episode showed a bias towards negative consequences.This effect occurred even though patients had been euthymic for up to sixty months.To explain this carry-over effect from symptomatic to euthymic phases,we proposed that affective episodes might represent learning experi-ences during which patients perceive and experience outcomes(failure vs.success)and consequences (reward vs.punishment)mostly in a mood-congruent manner which shapes their perception of self-efficacy as well as their action-outcome expectancies and outcome-consequence expectancies persisting beyond the symptomatic phases.The influence of action-outcome and outcome-consequence expectancies on personality constructs of generalized self-referential cognitions like control orientations and subjective knowledge(Krampen,1988)further explains the endurance of these biases,which might only be changed by very powerful learning experiences like the next affective episode or psychotherapy.These results correspond to the theoretical framework of the dysregulation model of the behavioral activation sys-tem(Uros´e vic et al.,2008)suggesting that altered expectancies and beliefs influence the appraisal as well as the creation and selection of events relevant for the behavioral activation system and thus interact with the dysregulation of that system.Furthermore,there is some evidence on brain func-tion and structure underlying this motivational bias. Altered activity of and changed connectivity between brain regions like the orbitofrontal cortex,rostral cin-gulate cortex,amygdala and striatum that are involved in motivation(Diekhof et al.,2008;Ernst et al.,2004) have been reported in patients with bipolar disor-der(for reviews see Blond et al.,2012;Strakowski et al.,2012)and might constitute the neuronal corre-late of differential responses to positive and negative feedback.54M.Wessa et al./Bipolar disorder:A neural network perspectiveIndeed,in a recent study,we observed decreased deactivation in the medial orbitofrontal cortex and greater activation of the amygdala in response to rever-sal of reward contingencies in euthymic patients with bipolar-I disorder and unaffectedfirst-degree relatives of bipolar I disorder patients(Linke et al.,2012a see Fig.1).Further,patients and relatives showed greater activation of the medial orbitofrontal cortex in response to reward delivery,whereas only in unaffectedfirst-degree relatives of bipolar patients(Linke et al.,2012a) and in healthy individuals carrying a genetic risk vari-ant(CACNA1C rs1006737)for bipolar disorder(Wessa et al.,2010)the amygdala appeared hyperactive in response to reward.However,in euthymic patients with bipolar-I disorder,hyper-activation of amygdala was normalized by psychotropic medication as indi-cated by a significant negative correlation between medication load and amygdala activation to reward delivery.Differential activation patterns in medial orbitofrontal cortex during reward delivery and reversal of reward contingencies in BD patients and first-degree relatives of bipolar disorder patients might represent different underlying mechanisms:whereas heightened activation of the medial orbitofrontal cor-tex(and amygdala)in response to reward is interpreted as heightened reward sensitivity,reduced deactivation of the medial orbitofrontal cortex and hyper-activation of the amygdala during reversal of reward contingen-cies,observed in both patients with bipolar disorder and healthy relatives of bipolar disorder patients represents an attenuated prediction error signal.Such an attenuated prediction error signal was particularly prominent in unaffected relatives when negative feedback was not followed by a behavioral change, which reminds of clinical symptoms in manic bipolar patients,who continue to pursue immediate rewards despite negative consequences(American Psychiatric Association2000).Interestingly,in a very recent neuropsychological study(Wessa et al.,unpublished manuscript)we observed increased delay aversion scores in healthyfirst-degree relatives of bipolar disorder patients,which reflect an impulsive behavior, i.e.,the inability to delay and inhibit responses in the context of reward-related decision-making.However, no such effect was present in bipolar disorder patients themselves.This even higher sensitivity to immediate rewards and impulsive behavior in healthy individuals at risk to develop bipolar disorder compared to bipolar patients might be related to medication effects.However,with respect to the prediction error signal and delay aversion we did not observe significant correlations with medication load,which of course does not rule out that medication has some effect or that it has a more specific effect than we were able to detect with a rather global measure like the composite medication load score.Another explanation refers to the fact that bipolar disorder patients in our study were chronic patients with a history of multiple manic and depressive episodes and ideally,during psychotherapy, they already acquired some strategies to regulate their initially increased sensitivity to immediate reward and impulsivity.The convergent results in patients with bipolar dis-order,unaffectedfirst-degree relatives of patients with bipolar disorder(Linke et al.,2012a)and carriers of a genome-wide supported genetic risk variant for bipolar disorder(CACNA1C rs1006737,Wessa et al., 2010)strongly suggest that alterations in the medial orbitofrontal cortex and amygdala represent a trait marker for bipolar disorder.On a cautious note,these abnormalities might also contribute to increased ill-ness vulnerability,a proposition that is in line with the above-mentioned dysregulation theory of the behav-ioral activation system(Alloy&Abramson,2010). This theory suggests that a hypersensitive behavioral activation system,which regulates approach motiva-tion and goal-directed behavior and depends(amongst other structures)on the orbitofrontal cortex(Depue and Iacono,1989),mediates vulnerability for bipo-lar disorder.Indeed,further analyses of our data revealed moderate and significantly positive correla-tions between the score on the behavioral activation system scale(Carver&White,1994)and neural acti-vation in the medial orbitofrontal cortex in response to reward and reversal of reward contingencies in bipo-lar disorder patients and their relatives.The behavior activation system scale measures dispositional sensi-tivity to the behavioral activation system(Carver& White,1994)and is calculated from questionnaire items loading high on the dimensions‘Drive’,‘Reward Responsiveness’and‘Fun Seeking’.Despite the evidence from our studies,the question whether alterations in the medial orbitofrontal cortex and amygdala in response to reward delivery and rever-sal of reward contingencies represent a vulnerability marker for bipolar disorder has to be further evaluated in longitudinal studies considering conversion rates in high-risk individuals,particularly at young age,to bipolar disorder or other psychopathologies.M.Wessa et al./Bipolar disorder:A neural network perspective55In addition to these potential vulnerability mark-ers for bipolar disorder,we also identified increased activity in the ventral putamen and lateral orbitofrontal cortex during reversal of reward contingencies.As described earlier,these structures have been subsumed under an external emotional control network in a recently published neurobiological consensus model of bipolar disorder(Strakowski et al.,2012).Further-more,increased activity in lateral orbitofrontal cortex seems to signal punishment and could thus repre-sent a compensatory mechanism in bipolar patients that aides to suppress previously rewarded responses (Cools et al.,2002)and potentially enables adequate performance during euthymia.Such compensatory recruitment of orbitofrontal structures was previously reported by our group for euthymic bipolar disorder patients during the inhibition of responses to emotional compared to neutral faces(Wessa et al.,2007). Taken as a whole,our results support neurobiolog-ical models of bipolar disorder,highlighting the role of the ventral prefrontal cortex and the amygdala as key structures in the development and maintenance of bipolar disorder(Blond et al.,2012;Strakowski et al.,2012).Ourfindings add to the existing models in identifying abnormal amygdala and ventral pre-frontal cortex functioning in response to reward as potential vulnerability marker for bipolar disorder.Fur-thermore,our data extend previous results by showing that heightened emotional reactivity in bipolar disorder is not limited to primary emotional cues but also occurs for positive and negative feedback probably leading to motivational dysregulation.3.Emotional processingAs pointed out,the majority of neuroimaging studies in bipolar disorder investigated the recog-nition of or reaction to emotional stimuli,such as emotional faces or words.In line with the clinical observation of an emotional instability and emotional hyper-reactivity in patients with bipolar disorder,an emotion-specific hyperactivity of ventral-limbic brain structures such as the amygdala,the insula,the anterior cingulate cortex and the orbitofrontal cortex has been repeatedly reported in adult depressed and euthymic bipolar disorder patients(Altshuler et al.,2005; Lawrence et al.,2004;Malhi et al.,2004;Wessa et al.,2007;Yurgelun-Todd et al.,2000).During mania, results are more conflicting with a number of studies reporting decreased rather than increased amygdala activity(Chen et al.,2010;Hulvershorn et al.,2012; Lennox,2004).In general,hyper-activation in ventral-limbic brain areas in bipolar disorder patients has been related to diminished top-down control,which is supported by studies showing reduced negative or even increased functional connectivity between the ventrolateral prefrontal cortex/anterior cingulate cortex and the amygdala in manic(Cerullo et al.,2012;Foland et al., 2008),euthymic(Wang et al.,2009)and depressed patients(Versace et al.,2010b).In addition to these task-related abnormal connectivity patterns,a rela-tively reduced negative correlation and decreased low frequency BOLDfluctuations between ventral pre-frontal/anterior cingulate cortex and amygdala activity at rest was reported in bipolar disorder patients as compared to healthy controls(Anand et al.,2009; Chepenik et al.,2010).Among other regions(e.g. medial prefrontal cortex,parietal cortex),the dorsal, anterior cingulate and ventrolateral prefrontal cortices have been found to underlie voluntary emotion reg-ulation through attentional control(e.g.distraction) or cognitive change(e.g.reappraisal)(Kanske et al., 2011;McRae et al.,2010).In bipolar disorder patients, hypo-activation of prefrontal structures and reduced negative functional connectivity between ventral pre-frontal and limbic brain areas might therefore lead to a deficit in voluntarily down-regulating exaggerated emotional responses.Until now,however,very few studies have investi-gated neural correlates of voluntary emotion regulation in bipolar disorder although theoretical models,empir-ical data and clinical observations strongly suggest such regulation deficits(Phillips et al.,2008).One major problem in emotion regulation research in bipolar disorder is a very heterogeneous conceptualiza-tion of emotion regulation,and consequently diverse operationalization in experimental research.Emotion regulation is part of a broader concept of emotional processing,including a pre-attentive stage,attention allocation,sensory perception,transient and automatic emotional responses,experience and expression of emotion,higher-level appraisal of emotional stim-uli,andfinally the regulation of emotions(Wessa &Linke,2009).From an experimental and clinical neuroscience perspective it is important to make a dis-tinction between these sub-processes in order to be able to validly characterize disturbed or maladaptive processes in psychopathology.56M.Wessa et al./Bipolar disorder:A neural network perspectiveAccording to Gross&Thompson(2007)regula-tion of emotions refers to the process of increasing or decreasing current affect.Such a process may occur consciously or unconsciously on a continuum from effortless and automatic(unconscious)to effort-ful and controlled regulation(conscious).Within their model of emotion regulation,Gross&Thompson (2007),differentiatefive types of emotion regula-tion strategies which can be broadly divided into (1)antecedent-focused strategies,occurring before full-blown emotional responses are elicited(situation selection,situation modification,attentional deploy-ment,and cognitive change),and(2)response-focused strategies,occurring after emotional responses are gen-erated(response modulation).In experimental emotion regulation research,a focus has been placed on the investigation of a few strategies,particularly on dis-traction as an example for attentional deployment, reappraisal as an example for cognitive change and suppression as an example for response modulation. Whereas distraction refers to directing attention away from the emotional features of the situation to differ-ent,potentially non-emotional aspects of the situation, reappraisal means to change the connotation of a situ-ation or how we think about a situation in order to alter its emotional significance.Previous studies in bipolar disorder employed exper-imental paradigms that included cognitive tasks(e.g., response inhibition,n-back task)with concurrently presented emotional stimuli(e.g.,Bertocci et al.,2012; Deckersbach et al.,2008;Elliott et al.,2004;Wessa et al.,2007).To assure successful task performance, study participants had to direct their attention away from the concurrently presented emotional stimulus and to focus on the cognitive task.Likewise,these studies might also be seen as investigating atten-tional deployment as one emotion regulation strategy. However,in their analyses the authors mainly investi-gated the distracting influence of emotion on cognitive processes,for example by contrasting brain activity associated with the task during the presentation of dis-tracting emotional stimuli versus neutral stimuli.Yet, to determine the neural correlates of the influence of cognitive task performance on emotional responses, and thus emotion regulation,a comparison between the ‘task+emotion’condition and‘emotion-only’condi-tion would be necessary.Previously,two studies investigated the impact of disturbing emotional information on response inhibition in manic and euthymic bipolar disorder patients,revealing increased ventral prefrontal activ-ity in bipolar patients when trying to inhibit responses to emotional faces compared to the inhibition of responses to neutral faces(Elliott et al.,2004;Wessa et al.,2007).Two more recent studies investigated working memory performance during either mood induction(Deckersbach et al.,2008)or concurrently presented emotional faces(Bertocci et al.,2012).In depressed bipolar disorder patients,Deckersbach et al.(2008)reported increased activation in dorsal ante-rior cingulate and dorsolateral prefrontal cortices while performing the working memory task under sad mood as compared to no mood induction.This might be interpreted as a greater demand for executive control to perform the cognitive task when being in a sad mood.Whereas Bertocci et al.(2012)did notfind such compensatory activity in bipolar disorder patients, but reported elevated activity in the dorsal anterior cingulate cortex during high working memory-load and concurrently presented neutral faces in depressed patients with unipolar depression,suggesting compen-sational recruitment of brain regions belonging to the attentional control network.Interestingly,our group could show a similar effect in patients with unipolar depression not only for dis-traction but also for reappraisal(Kanske et al.,2012). Activity in the regulating control-network includ-ing anterior cingulate cortex and lateral orbitofrontal cortex was increased during both distraction and reap-praisal.In contrast,patients with unipolar depression showed a selective deficit in down-regulating amyg-dala responses to negative emotional stimuli using reappraisal.This down-regulation of amygdala activ-ity was strongest in participants with high habitual use of reappraisal measured with the Cognitive Emo-tion Regulation Questionnaire(CERQ;Garnefski& Kraaij,2007)that assesses the regular use of reap-praisal or suppression as emotion regulation strategy during every-day life.These data are in line with previ-ous studies on cognitive control of emotions in patients with unipolar depression,suggesting a deficit in the ability to down-regulate amygdala activity to negative emotional stimuli(Beauregard et al.,2006),and altered connectivity between the amygdala and prefrontal con-trol regions(Erk et al.,2010;Johnstone et al.,2007). To overcome the described gap in voluntary emo-tion regulation research in bipolar disorder patients, we recently completed a study on the neural correlates of two different voluntary emotion regulation strate-gies,i.e.,distraction and reappraisal,in patients with。

Schaeffler AG Coupa电子竞价系统供应商快速参考指南说明书

Coupa Quick Reference Guide for Suppliers | eAuctionsCoupa电子竞价系统供应商快速参考指南Welcome 欢迎Supplier Quick Reference Guide for Coupa | ContentCoupa 供应商快速参考指南| 内容Getting yourself set-up让你自己准备好Read more about how login to Coupa 阅读更多关于如何登录CoupaParticipating in the eAuction 参加电子竞价Get familiar how to participate in an eAuction熟悉如何参加一个电子竞价Get familiar with our Coupa project and eAuction types熟悉我们的coupa 项目和电子竞价类型Getting you on the road 带你上路English Reverse Auction 英式反向竞价Find more information on how you can enter bids in a English Reverse Auction 找到更多信息关于如何参加一个英式方向竞价Click here 点击这里Dutch Reverse Auction 荷兰式反向竞价Find more information on how you can enter bids in a Dutch Reverse Auction 找到更多信息关于如何参加一个荷兰式方向竞价Japanese Reverse Auction 日式反向竞价Find more information on how you can enter bids in a Japanese Reverse Auction 找到更多信息关于如何参加一个日式方向竞价Starting November 4th Schaeffler will launch a new NPM Purchasing Platform (Coupa) with the aim for Purchasing to become more customer centric and user friendly in line with efficiently working together with their business counterparts. We strive for:为加强以客户为中心,让使用者更友好,业务对应方工作更有效,11月4日开始舍弗勒将上线新的NPM 采购平台(Coupa ).我们努力:•Intuitive and state-of-the-art system for requestor and purchaser 使用者及采购者直观及最先进的系统•High potential for self-service 潜力大的自助服务•Real-time tracking of supplier activities in Coupa 在Coupa 里实时跟踪供应商活动•Global standards and aligned processes 全球标准及协调一致的流程•Efficiency and effectiveness in decisions based on transparency & data•决策的效率和有效性基于数据且透明At a glance 快速摘要Getting you on the road 带你上路Exciting news for NPM Purchasing*NPM 采购部激动人心的新闻Coupa –working on one global platform Coupa-在一个全球平台上工作As a supplier you will find all the relevant information and access all necessary documents within one place. This will enable you to bid and interact with Schaeffler more effectively.作为一个供应商,你可以在同一个地方找到所有相关信息并可以进入所有必要的文件。

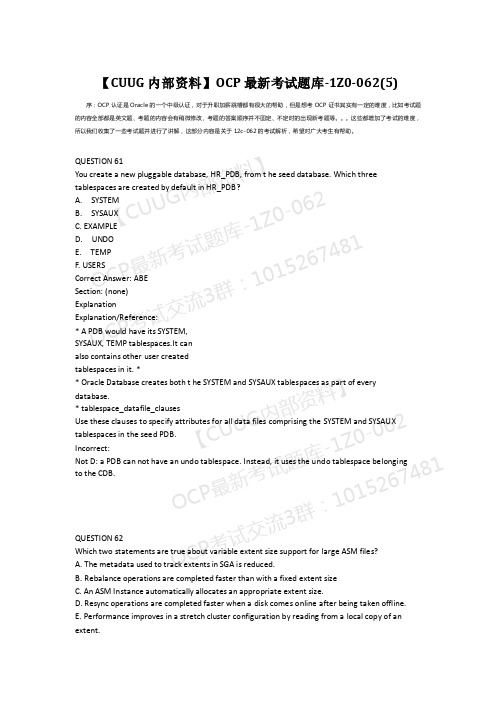

【CUUG内部资料】OCP最新考试题库-1Z0-062(5)

AUTHID CURRENT_USER AS BEGIN

OCP最新考试题库 1015267481 INSERT INTO departments VALUES (v_deptno, v_dname, v_mgr, v_loc);

END; 2、 调用该存储过程: CALL create_dept(44, 'Information Technology', 200, 1700);

】 E. Execute FLASHBACK TABLE OCA.EXAM_RESULTS TO BEFORE DROP RENAME TO 料 EXAM_RESULTS; connected as the OCP user. 部资 Correct Answer: C 【CUUG内 -1Z0-062 Section: (none)

能够执行这个存储过程,所以如果是 definer's rights 的话,执行就会出错,因为该模式下只 能对 HR.DEPARTMENTS 的表进行操作;可能的情况下是这些用户自己有跟 HR 用户相同的

OCP最新考试题库 1015267481 表名字也叫 DEPARTMENTS,所以当执行这个存储过程的时候,修改的是自己的表,可以实

Explanation(验证过) (解析:因为是删除了用户,而且数据库版本是 11g,没有表恢复功能,但是从恢复工作量

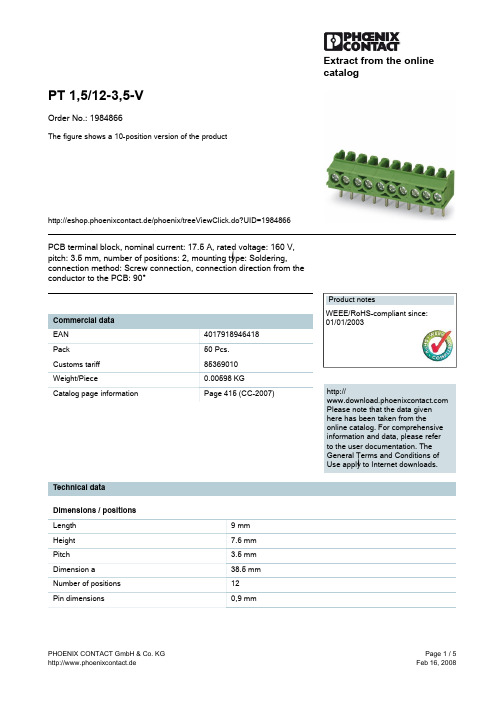

1984866资料

Extract from the onlinecatalogPT 1,5/12-3,5-VOrder No.: 1984866The figure shows a 10-position version of the producthttp://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1984866PCB terminal block, nominal current: 17.5 A, rated voltage: 160 V, pitch: 3.5 mm, number of positions: 2, mounting type: Soldering, connection method: Screw connection, connection direction from the conductor to the PCB: 90°http://Please note that the data givenhere has been taken from theonline catalog. For comprehensiveinformation and data, please referto the user documentation. TheGeneral Terms and Conditions ofUse apply to Internet downloads. Technical dataDimensions / positionsLength9 mmHeight7.6 mmPitch 3.5 mmDimension a38.5 mmNumber of positions12Pin dimensions0,9 mmPin spacing 3.5 mm Hole diameter 1.2 mm Screw thread M 2 Tightening torque, min0.25 NmTechnical dataInsulating material group IRated surge voltage (III/3) 2.5 kV Rated surge voltage (III/2) 2.5 kV Rated surge voltage (II/2) 2.5 kV Rated voltage (III/2)200 V Rated voltage (II/2)400 V Connection in acc. with standard EN-VDE Nominal current I N17.5 A Nominal voltage U N160 V Nominal cross section 1.5 mm2 Maximum load current17.5 A Insulating material PA Inflammability class acc. to UL 94V0 Stripping length 5 mmConnection dataConductor cross section solid min.0.2 mm2 Conductor cross section solid max. 1.5 mm2 Conductor cross section stranded min.0.2 mm2 Conductor cross section stranded max. 1.5 mm2 Conductor cross section stranded, with ferrule0.25 mm2 with plastic sleeve min.Conductor cross section stranded, with ferrule0.75 mm2 with plastic sleeve max.Conductor cross section AWG/kcmil min.26 Conductor cross section AWG/kcmil max162 conductors with same cross section, solid min.0.2 mm2 2 conductors with same cross section, solid max.0.34 mm2 2 conductors with same cross section, stranded0.2 mm2 min.2 conductors with same cross section, stranded0.5 mm2max.Certificates / ApprovalsApproval logoCULNominal voltage U N300 VNominal current I N10 AAWG/kcmil26-16ULNominal voltage U N300 VNominal current I N10 AAWG/kcmil26-16Certification CCA, CUL, SEV, ULAccessoriesItem Designation DescriptionMarking1051993B-STIFT Marker pen, for manual labeling of unprinted Zack strips,smear-proof and waterproof, line thickness 0.5 mm0804073SK 3,5/2,8:FORTL.ZAHLEN Marker card, printed horizontally, self-adhesive, 10-section markerstrip, 14 identical decades marked 1-10, 11-20 etc. up to 91-100,sufficient for 140 terminal blocks0805030SK 3,5/2,8:SO Marker card, special printing, self-adhesive, labeled acc. tocustomer requirements, 14 identical marker strips per card, max.25-position labeling per strip, color: White0803883SK U/2,8 WH:UNBEDRUCKT Unprinted marker cards, DIN A4 format, pitch as desired,self-adhesive, with 50 stamped marker strips, 185 mm strip length,can be labeled with the CMS system or manually with the M-PEN 0811228X-PEN 0,35Marker pen without ink cartridge, for manual labeling of markers,labeling extremely wipe-proof, line thickness 0.35 mmTools1205037SZS 0,4X2,5Screwdriver, bladed, matches all screw terminal blocks up to 1.5mm² connection cross section, blade: 0.4 x 2.5 mmDrawingsDrilling diagramDimensioned drawingAddressPHOENIX CONTACT GmbH & Co. KGFlachsmarktstr. 832825 Blomberg,GermanyPhone +49 5235 3 00Fax +49 5235 3 41200http://www.phoenixcontact.de© 2008 Phoenix ContactTechnical modifications reserved;。

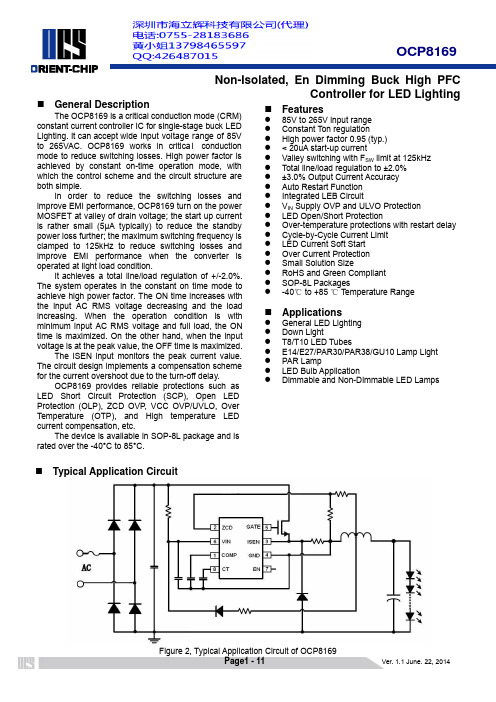

OCP8169 datasheet ver 1.1_20140622