M25P16-VME6TG

Micron 产品数据手册说明书

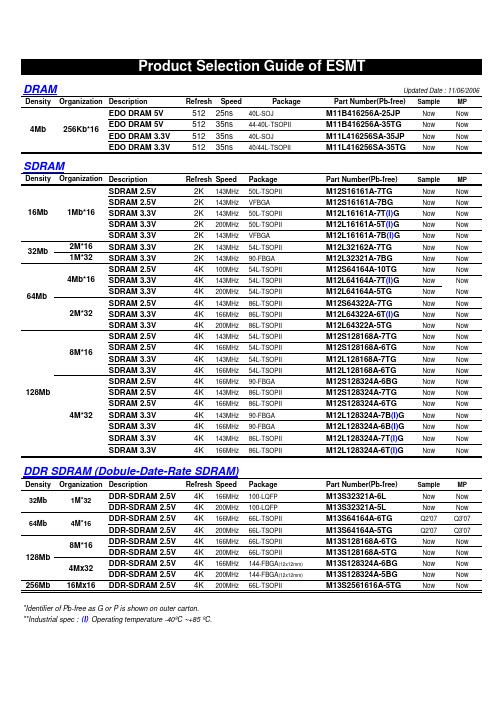

DRAMUpdated Date : 11/06/2006DensityOrganization DescriptionRefreshSpeedPackagePart Number(Pb-free)Sample MP EDO DRAM 5V 51225ns 40L-SOJ M11B416256A-25JP Now Now EDO DRAM 5V 51235ns 44-40L-TSOPII M11B416256A-35TG Now Now EDO DRAM 3.3V 51235ns 40L-SOJ M11L416256SA-35JP Now Now EDO DRAM 3.3V 51235ns 40/44L-TSOPIIM11L416256SA-35TGNowNowSDRAMDensityOrganization DescriptionRefresh SpeedPackagePart Number(Pb-free)Sample MP SDRAM 2.5V 2K 143MHz 50L-TSOPII M12S16161A-7TG Now Now SDRAM 2.5V 2K 143MHz VFBGA M12S16161A-7BG Now Now SDRAM 3.3V 2K 143MHz 50L-TSOPII M12L16161A-7T (I)G Now Now SDRAM 3.3V 2K 200MHz 50L-TSOPII M12L16161A-5T (I)G Now Now SDRAM 3.3V 2K 143MHz VFBGA M12L16161A-7B (I)G Now Now 2M*16SDRAM 3.3V 2K 143MHz 54L-TSOPII M12L32162A-7TG Now Now 1M*32SDRAM 3.3V 2K 143MHz 90-FBGA M12L32321A-7BG Now Now SDRAM 2.5V 4K 100MHz 54L-TSOPII M12S64164A-10TG Now Now SDRAM 3.3V 4K 143MHz 54L-TSOPII M12L64164A-7T (I)G Now Now SDRAM 3.3V 4K 200MHz 54L-TSOPII M12L64164A-5TG Now Now SDRAM 2.5V 4K 143MHz 86L-TSOPII M12S64322A-7TG Now Now SDRAM 3.3V 4K 166MHz 86L-TSOPII M12L64322A-6T (I)G Now Now SDRAM 3.3V 4K 200MHz 86L-TSOPII M12L64322A-5TG Now Now SDRAM 2.5V 4K 143MHz 54L-TSOPII M12S128168A-7TG Now Now SDRAM 2.5V 4K 166MHz 54L-TSOPII M12S128168A-6TG Now Now SDRAM 3.3V 4K 143MHz 54L-TSOPII M12L128168A-7TG Now Now SDRAM 3.3V 4K 166MHz 54L-TSOPII M12L128168A-6TG Now Now SDRAM 2.5V 4K 166MHz 90-FBGA M12S128324A-6BG Now Now SDRAM 2.5V 4K 143MHz 86L-TSOPII M12S128324A-7TG Now Now SDRAM 2.5V 4K 166MHz 86L-TSOPII M12S128324A-6TG Now Now SDRAM 3.3V 4K 143MHz 90-FBGA M12L128324A-7B (I)G Now Now SDRAM 3.3V 4K 166MHz 90-FBGA M12L128324A-6B (I)G Now Now SDRAM 3.3V 4K 143MHz 86L-TSOPII M12L128324A-7T (I)G Now Now SDRAM 3.3V4K166MHz86L-TSOPIIM12L128324A-6T (I)GNowNowDDR SDRAM (Dobule-Date-Rate SDRAM)Density Organization DescriptionRefresh SpeedPackagePart Number(Pb-free)Sample MP DDR-SDRAM 2.5V 4K 166MHz 100-LQFP M13S32321A-6L Now Now DDR-SDRAM 2.5V 4K 200MHz 100-LQFP M13S32321A-5L Now Now DDR-SDRAM 2.5V 4K 166MHz 66L-TSOPII M13S64164A-6TG Q2'07Q3'07DDR-SDRAM 2.5V 4K 200MHz 66L-TSOPII M13S64164A-5TG Q2'07Q3'07DDR-SDRAM 2.5V 4K 166MHz 66L-TSOPII M13S128168A-6TG Now Now DDR-SDRAM 2.5V 4K 200MHz 66L-TSOPII M13S128168A-5TG Now Now DDR-SDRAM 2.5V 4K 166MHz 144-FBGA (12x12mm)M13S128324A-6BG Now Now DDR-SDRAM 2.5V 4K 200MHz 144-FBGA (12x12mm)M13S128324A-5BG Now Now 256Mb16Mx16DDR-SDRAM 2.5V 4K200MHz66L-TSOPIIM13S2561616A-5TGNowNow*Identifier of Pb-free as G or P is shown on outer carton.**Industrial spec : (I) Operating temperature -40ºC ~+85 ºC.2M*3264Mb4Mb*1632Mb4Mb 256Kb*161Mb*1616Mb 128Mb8M*164Mx324M*32128Mb8M*1632Mb 64Mb1M*324M*16Mobile SDRAMDensityOrganizationDescriptionRefresh Speed Package & MCPPart Number(Pb-free)Sample MP Mobile SDRAM 2.5V4K 100MHz 50L-TSOPII M52S16161A-10T (I)G Now Now Mobile SDRAM 2.5V 4K 125MHz 50L-TSOPII M52S16161A-8T (I)G Now Now Mobile SDRAM 1.8V4K 100MHz50L-TSOPIIM52D16161A-10T (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 54L-TSOPII M52S32162A-10T (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 54-FBGA M52S32162A-10B (I)G Now Now Mobile SDRAM 2.5V 4K 133MHz 54L-TSOPII M52S32162A-7.5T (I)G Now Now Mobile SDRAM 2.5V 4K 133MHz 54-FBGA M52S32162A-7.5B (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D32162A-10T (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 54-FBGA M52D32162A-10B (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D32162A-7.5T (I)G Now Now Mobile SDRAM 1.8V 4K 133MHz 54-FBGA M52D32162A-7.5B (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 90-FBGA M52S32321A-10B (I)G Now Now Mobile SDRAM 2.5V 4K 133MHz 90-FBGA M52S32321A-7.5B (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 90-FBGA M52D32321A-10B (I)G Now Now Mobile SDRAM 1.8V 4K 133MHz 90-FBGA M52D32321A-7.5B (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 54L-TSOPII M52S64164A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 100MHz 54-FBGA M52S64164A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 54L-TSOPII M52S64164A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 54-FBGA M52S64164A-7.5B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D64164A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 54-FBGA M52D64164A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D64164A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 133MHz 54-FBGA M52D64164A-7.5B (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 100MHz 86L-TSOPII M52S64322A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 100MHz 90-FBGA M52S64322A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 86L-TSOPII M52S64322A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 90-FBGA M52S64322A-7.5B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 86L-TSOPII M52D64322A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 90-FBGA M52D64322A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 86L-TSOPII M52D64322A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V4K133MHz 90-FBGAM52D64322A-7.5B (I)GQ2 '07Q3 '07*Identifier of Pb-free as G or P is shown on outer carton.**Industrial spec : (I) Operating temperature -40ºC ~+85 ºC.64Mb4Mx162Mx32(1)All Mobile functions are included : PASR,TCSR,DS,Deep power down mode.(2)Max. Icc6 : Self-refresh current with full bank in 70 ºC .1Mx16Max. Icc6= 75uA (1.8V)16Mb32Mb2Mx161Mx32。

液晶屏型号屏定义大全

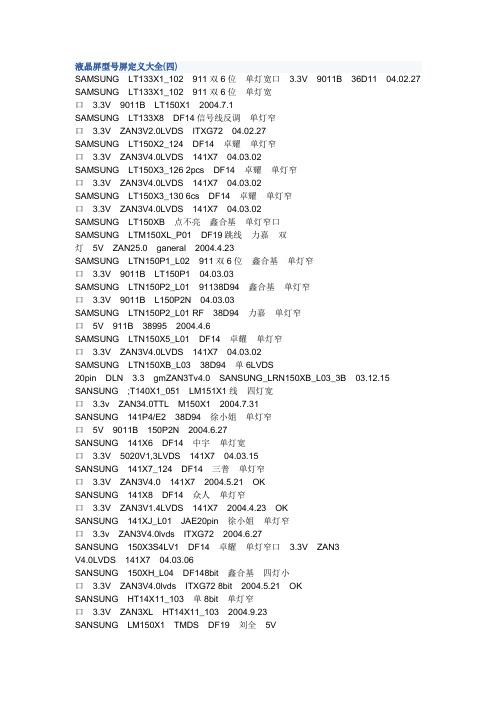

液晶屏型号屏定义大全(四)SAMSUNG LT133X1_102 911双6位单灯宽口 3.3V 9011B 36D11 04.02.27 SAMSUNG LT133X1_102 911双6位单灯宽口 3.3V 9011B LT150X1 2004.7.1SAMSUNG LT133X8 DF14信号线反调单灯窄口 3.3V ZAN3V2.0LVDS ITXG72 04.02.27SAMSUNG LT150X2_124 DF14 卓耀单灯窄口 3.3V ZAN3V4.0LVDS 141X7 04.03.02SAMSUNG LT150X3_126 2pcs DF14 卓耀单灯窄口 3.3V ZAN3V4.0LVDS 141X7 04.03.02SAMSUNG LT150X3_130 6cs DF14 卓耀单灯窄口 3.3V ZAN3V4.0LVDS 141X7 04.03.02SAMSUNG LT150XB 点不亮鑫合基单灯窄口SAMSUNG LTM150XL_P01 DF19跳线力嘉双灯5V ZAN25.0 ganeral 2004.4.23SAMSUNG LTN150P1_L02 911双6位鑫合基单灯窄口 3.3V 9011B LT150P1 04.03.03SAMSUNG LTN150P2_L01 91138D94 鑫合基单灯窄口 3.3V 9011B L150P2N 04.03.03SAMSUNG LTN150P2_L01 RF 38D94 力嘉单灯窄口5V 911B 38995 2004.4.6SAMSUNG LTN150X5_L01 DF14 卓耀单灯窄口 3.3V ZAN3V4.0LVDS 141X7 04.03.02SAMSUNG LTN150XB_L03 38D94 单6LVDS20pin DLN 3.3 gmZAN3Tv4.0 SANSUNG_LRN150XB_L03_3B 03.12.15 SANSUNG ;T140X1_051 LM151X1线四灯宽口 3.3v ZAN34.0TTL M150X1 2004.7.31SANSUNG 141P4/E2 38D94 徐小姐单灯窄口5V 9011B 150P2N 2004.6.27SANSUNG 141X6 DF14 中宇单灯宽口 3.3V 5020V1,3LVDS 141X7 04.03.15SANSUNG 141X7_124 DF14 三普单灯窄口 3.3V ZAN3V4.0 141X7 2004.5.21 OKSANSUNG 141X8 DF14 众人单灯窄口 3.3V ZAN3V1.4LVDS 141X7 2004.4.23 OKSANSUNG 141XJ_L01 JAE20pin 徐小姐单灯窄口 3.3v ZAN3V4.0lvds ITXG72 2004.6.27SANSUNG 150X3S4LV1 DF14 卓耀单灯窄口 3.3V ZAN3V4.0LVDS 141X7 04.03.06SANSUNG 150XH_L04 DF148bit 鑫合基四灯小口 3.3V ZAN3V4.0lvds ITXG72 8bit 2004.5.21 OKSANSUNG HT14X11_103 单8bit 单灯窄口 3.3V ZAN3XL HT14X11_103 2004.9.23SANSUNG LM150X1 TMDS DF19 刘全5VSANSUNG LM151X2 41A 芃峰双灯 3.3V ZAN3V4.0TTL LM151X2 2004.5.26 OKSANSUNG LNM150XS_T01 151X1 力嘉双灯 3.3V ZAN32.0TTL M150X1 2004.4.19 OKSANSUNG LT094V3_10T SHARP 4bit 单灯宽口5v ZAN34.0TTL pvi6448 2004.9.7 okSANSUNG LT104S1-102 41A 单灯宽口5V ZAN3V4.0TTL LP121S1 2004.10.18SANSUNG LT104S4_151 41B 单灯宽口5V ZAN34.0TTL 121S1 2004.7.26 SANSUNG lt1133x7_124 DF1914pin 鑫合基单灯窄口 3.3V ZAN3V4.0 lt1133x7_124 2004.5.6 OKSANSUNG LT121S1_153 41A 丰华单灯宽口5V ZAN34.0TTL 121S1 2004.6.8SANSUNG LT121S1_153 41A 金太星单灯宽口 3.3V 5020V1,3LVDS 141X7 04.03.16SANSUNG LT121S1153 41A 芃峰单灯宽口 3.3v ZAN34.0TTL 121S1 2004.6.19SANSUNG LT121SS_105 41A 晶捷单灯宽口 3.3v ZAN34.0TTL 121S1 2004.6.10SANSUNG LT121SS_123 2004.10.7SANSUNG LT121SU_121 DF14 单灯窄口 3.3v ZAN2V4.0lvds 800X600LVDS 2004.6.19SANSUNG LT121SU_121 DF14反插芃峰单灯窄口 3.3V ZAN34.0LVDS 800X600LVDS 2004.8.29 OK 此屏为笔记本屏SANSUNG LT121SU_121 DF1920pin SL 科星单灯宽口 3.3V ZAN3XL LT121SU_121 2004.10.7SANSUNG LT121SU_121 molxe20pin 徐小姐单灯窄口 3.3v ZAN3V4.0lvds HSD800X600 LVDS 2004.6.27SANSUNG LT133X1_101SANSUNG LT133X1_101 911双6位单灯宽口5V 9011B LT150X1M 2004.7.27SANSUNG LT133X1_104 38D94 单灯宽口5V ZAN3SL LT133X1 2004.10.21SANSUNG LT133X1_106 9011B双6bit 单灯宽口5V GM2211 LT133X1_106 2004.10.11SANSUNG LT133X1104 911双6位王玉高单灯宽口5V 9011B LT150X1 2004.8.22SANSUNG LT133X2_154 DF14 王玉高单灯窄口 3.3V ZAN34.0LVDS 141X7 2004.8.22SANSUNG LT133X2_154 DF14 新元单灯窄口 3.3V ZAN3V4.0LVDS ITXG72 2004.7.26SANSUNG LT133X4_122 MOLXE20 V.V.G.G.0-.0+.G.G.1-.1+.G.G.2-.2+.G.G.CLK-.CLK+.G 单灯宽口 3.3V ZAN3 4.0LVDS ITXG72 2004.9.2 OKSANSUNG LT133X8_122 DF14 V.V.NC.NC.G.G.0-0G+1-1+G2-2+GC-C+.G 佳显单灯窄口 3.3V ZAN3V4.0LVDS ITXG72 2004.8.4SANSUNG LT133X8_122 DF14 三盟单灯窄口 3.3V 5020 13INCH 2004.7.30SANSUNG LT133XB_122 133X1线芃峰单灯窄口 3.3V ZAN2V4.0lvds ITXG72 2004.5.25SANSUNG LT141E2 DF14 三盟单灯窄口 3.3v 5020v1.4lvds 13INCH 2004.6.24SANSUNG LT141X2_152 单8bit 单灯窄口 3.3V ZAN3XL 141X7 2004.9.26 SANSUNG LT141X6_122 DF14 王玉高单灯宽口 3.3V ZAN34.0LVDS 141X7 2004.8.22SANSUNG lt141x7 DF14 中宇单灯宽口 3.3V 5020V1.3单lvds 141X7 04.03.17SANSUNG LT141X8_L02 单8bit 惠日单灯窄口 3.3V ZAN3XL LT141X8_L02 2004.10.20SANSUNG LT141XC_L01 DF14 单灯窄口 3.3v ZAN2V4.0lvds ITXG72 2004.6.20SANSUNG LT141XF DF14 三盟单灯窄口 3.3v 5020v1.4lvds 13INCH 2004.6.24SANSUNG LT141XU_L01 JAE20PIN 单灯窄口 3.3v ZAN2V4.0lvds ITXG72 2004.6.20SANSUNG LT150P1_L01 911双6位单灯窄口5V 9011B LP150P1 2004.9.2 OKSANSUNG LT150X1_102 911双6位单灯宽口 3.3V 2004.9.5 SANSUNG LT150X1_131 DF14改TMDS 四灯宽口5V ZAN25.0TMDS JANLR 2004.8.29 OK 此屏厚宽SANSUNG LT150X1_302 12VSANSUNG LT150X1_302 911双6位鑫合基四灯宽口12V 9011B LT150X1 2004.6.20SANSUNG LT150X1_302 911双6位鑫合基四灯宽口12V 9011B LT150X1 2004.6.27SANSUNG LT150X2_124 DF14 单灯窄口 3.3V ZAN3V4.0LVDS 147X7 04.03.12SANSUNG LT150X3_126 2PCS 华精SANSUNG LT150X3_126 2pcs DF14 卓耀单灯窄口 3.3V ZAN3V4.0LVDS 141X7 04.03.06SANSUNG LT150X3_126 2PCS DF14 卓耀单灯窄口 3.3V ZAN3LVDS LP150X1_1 04.03.06SANSUNG LT150X3_130 单8bit 单灯窄口 3.3V GM2221 141X7 2004.9.23 SANSUNG LT150X3_130 6PCS DF14 卓耀单灯窄口 3.3V ZAN3V4.0LVDS 141X7 04.03.06SANSUNG LT152W1_L01 JAE20pin 徐小姐单灯窄口 3.3v ZAN3V4.0lvds 2004.6.27SANSUNG LTM141X4_L01 DF14 芃峰单灯宽口 3.3Vnbsp; ZAN2V4.0lvds 141X7 2004.5.24 OKSANSUNG LTM150XBS4L 38D94 单灯窄口 3.3V ZAN3XL LT141X2_153 2004.10.21SANSUNG LTM150XH_L01 DF148bit 技博四灯小口 3.3V ZAN3V4.0单lvds ITXG72 04.03.17 8bitokSANSUNG LTM150XH_L01 DF148bit 宇田四灯小口 3.3V ZAN3V4.0单lvds ITXG72 8bit 2004.4.21 OKSANSUNG LTM150XH_L06 单8bit 四灯小口 3.3V ZAN3XL LTM150XH_L06 2004.10.21SANSUNG LTM150XL_P01 跳DF19 双灯5V TMDS LTM150XL_P01 2004.10.24SANSUNG LTM150XP DF14 8bit 葛光华双灯 3.3v ZAN3V4. ITXG728bit 04.07.26SANSUNG LTM150XS_T01 LM151X1线微硕双灯5V ZAN34.0TTL LTM150XS_T01 2004.7.26SANSUNG LTM170E4_L01 170EH D8B LVDS 30Pin 四灯小口5V ZAN3SL L170EH 2004.9.21SANSUNG LTM170EH_L01 170EH D8B LVDS 30Pin 金泽兴宇四灯小口5V 9011B M170EH 2004.7.30SANSUNG LTM170EU_L01 170EH D8B LVDS 30Pin 微硕四灯小口5V 9011B M170E0 2004.7.26SANSUNG LTM170W01 df14 易唯四灯宽口 3.3 5020 LTM170W01 2004.7.24SANSUNG LTM170W1_L02 DF148pit 徐小姐四灯宽口 3.3v ZAN3V4.0lvds ltm170w1 2004.6.27SANSUNG LTN104S2_L01 DF19 14pin 芃峰单灯窄口 3.3V ZAN3V4.0LVDS LTN104S2_L01 2004.9.14 okSANSUNG LTN121X1_L01 DF19 华精单灯窄口 3.3V ZAN34.0LVDS ITXG72 2004.8.29 OKSANSUNG LTN121X1_L01 DF19 华精单灯窄口 3.3V ZAN34.0LVDS ITXG72 2004.8.29 OKSANSUNG LTN121XF_L01 DF19 2004.8.11SANSUNG LTN141P2_L01 38D94 单灯窄口 3.3V ZAN3SL LTN150P1_L01 2004.9.23SANSUNG LTN141P4_L01 DF14 冯小姐单灯窄口 3.3V 5020V1.3 13INTCH 2004.8.29SANSUNG LTN141X2_126 DF14 福星达单灯窄口 3.3 ZAN3V4.0lvds ITXG72 2004.7.20SANSUNG LTN141X7 单8bit 单灯窄口 3.3V ZAN3XL 141X7 2004.9.26 SANSUNG LTN141X7_124 DF14 海钲单灯窄口 3.3V ZAN3V4.0LVDS 141x7 2004.7.24SANSUNG LTN141X8_L00 DF14 易唯单灯窄口 3.3V ZAN3V4.0LVDS 141X7 2004.9.10 okSANSUNG LTN141X8_L02 DF14 4B066 单灯窄口 3.3v ZAN2V4.0lvds ITXG72 2004.6.19SANSUNG ltn141x8_l02 DF14 葛光华单灯窄口 3.3v ZAN3V4. 141X7 04.03.19SANSUNG LTN141XA_L01 ZAN3 38D94 芃峰单灯窄口 3.3v ZAN3V4.0lvds ITXG72 2004.6.27SANSUNG LTN141XA_L01 ZAN3 38D94 鑫合基单灯窄口 3.3V ZAN34.0LVDS LP150X1_1 2004.9.2 OKSANSUNG LTN141XE_L01 911DF19 单灯窄口 3.3V ZAN3XL LT 2004.9.23 SANSUNG LTN141XF_L02 DF14 微硕单灯窄口 3.3V ZAN3V4.0LVDS ITXG72 2004.9.17SANSUNG LTN141XU_L01 JEA ZAN2LVDS 万信单灯窄口 3.3V 50201.3LVDS 13INCH 2004.4.23 OKSANSUNG LTN141XU_L01 JEA ZAN2LVDS 鑫合基单灯窄口 3.3V ZAN3V4.0 LTN141XU_L01 2004.5.7 OKSANSUNG LTN150P1_L01 38D94 单灯窄口 3.3V ZAN3SL LTN150P1_L01 2004.9.23SANSUNG LTN150P4_L01 38D94 新锐博单灯窄口 3.3 9011B 150P2N 2004.7.24SANSUNG LTN150PE_L01 38D94 单灯窄口 3.3v 9011B LP150P2N 2004.7.18SANSUNG LTN150U2_L02 38D94 单灯窄口 3.3V ZAN3SL LTN150U2_L02 2004.9.29SANSUNG LTN150XB_L01 ZAN338D94 晶捷单灯窄口 3.3v ZAN2V4.0lvds ITXG72 2004.6.10SANSUNG LTN150XB_L03 ZAN338D94 单灯窄口 3.3v ZAN3V4.0lvds LP150X1_1 2004.6.30SANSUNG LTN150XB_l03 zan338d94 改1 到11均为空C+.C-.G.2+.2-G.1+.1-.G.0+.0-.NC.NC.NC.V.V.G. 单灯窄口 3.3V 2004.8.16 SANSUNG LTN150XD_L01 单8bit 单灯窄口 3.3V ZAN3XL LT141X2_153 2004.10.24SANSUNG LTN150XD_L02 DF14 单灯窄口 3.3V ZAN3V4.0LVDS ITXG72 2004.7.27SANSUNG LTN150XD_L02 DF14 8bit 单灯窄口 3.3V ZAN3 4.0LVDS ITXG72 8bit 2004.8.29SANSUNG LTN150XH_L01 DF14 8bit 四灯小口 3.3V ZAN3V4.0LVDS ITXG72 8bit 2004.7.29SANSUNG LTN154P1_L01 38D94 单灯窄口5v 9011B TX38D97(1900X1280) 2004.12.13SANSUNG LTN154U1_L01 38D94 徐小姐单灯窄口 3.3V 9011B LTN154U1_L01 2004.8.3SANSUNG LTN154X1_L01 ZAN3 38D94 单灯窄口 3.3V ZAN3V4.0LVDS LTN154X1_L01 2004.8.3SANSUNG LTN154X1_L01 zan3 38d94 晶捷单灯窄口 3.3v ZAN2V4.0lvds LTN154X1_L01 2004.6.24SANSUNG LTN154X1_L02 ZAN3 38D94 单灯窄口 3.3V ZAN3V4.0LVDS LTN154X1_L02 2004.8.3SAUHSUNG LT121S1-101 单8bit 新力通单灯窄口 3.3V ZAN3XL LT121SS800X600 2004.10.12SAUHSUNG LT150X1_302 LT150X1线四灯宽口5V ZAN3V4.0TTL m150x1 2004.10.12SAUNSUNG LT121S1_105A 41A 晶明单灯窄口 3.3V ZAN3V2.0TTL LP121S1 2004.8.4SAUNSUNG LT133X5_122 2004.8.3SAUNSUNG LT141X2_124 单8bit 新力通单灯窄口 3.3V ZAN3XL UB141X01 2004.10.12SAUNSUNG LTN150PG_L02 38D94 单灯窄口 3.3V 9011B LTN150P2N 2004.8.7SAUNSUNG LTN150PK_L01 38D94 单灯窄口 3.3V 9011B LTN150P2N 2004.8.7SAYO TM121SV_22L11A 41A 芃峰双灯 3.3V ZAN3V4.0TTL 121S1 2004.7.31SAYO TM150XG_02L11 ZAN3 38D94 鑫合基单灯窄口 3.3V ZAN34.0LVDS LP150X1_1 4.0LVDS LP150X1_1 2004.9.2 OKSAYO TM150XG_22L02A 15X16线芃峰双灯5V ZAN3V4.0TTL LQ14X042 2004.7.22SAYO TM150XG_52L11A 38D94 芃峰单灯窄口 3.3V 9011B TM150XG_52L11A 2004.8.22SAYO TM150XG_52L11A ZAN3 38D94 芃峰单灯窄口 3.3 ZAN3V4.0lvds LP150X1_1 2004.7.22SAYO TM150XG04_2 芃峰双灯2004.7.22SHARP 2004.9.21SHARP ;Q150F1LW14C 38D94 单灯窄口5V 9011B LTN150P2N 2004.8.16 SHARP 9D345 31A 单灯宽口 3.3V ZAN34.0TTL PV6448 2004.8.22 SHARP K3123TP DF14 S6B LVDS 20Pin SLN 3.3 gmZAN3L V4.0 ITXG72 SHARP L09D024 SHARP 4bit 单灯宽口5v ZAN34.0TTL pvi6448 2004.9.7 okSHARP LQ104S1LH11 molxe20pin 芃峰单灯宽口 3.3v ZAN2V4.0lvds lq121s1 2004.6.10SHARP LQ104S1LH11 molxe20pinNC.NC.NC.NC.V.V.G.0-.0+.G.1-.1+.G.2-.2+.G.C-.C+ 芃峰单灯窄口 3.3V ZAN3V4.0LVDS SHARP_121SH1LH11 2004.8.6SHARP LQ10D32A 31A 鑫合基单灯宽口5V ZAN3V4.0TTL PVI6448 2004.4.19 OKSHARP LQ10D341 31A 样品双灯SHARP LQ10DS01 41B 坤龙单灯宽口5V ZAN34.0TTL 121S1 2004.6.3 SHARP LQ11DS03 41B 坤龙单灯宽口5V ZAN3V4.0TTL 121S1 2004.7.20SHARP LQ11DS03 41B 芃峰单灯宽口 3.3V ZAN3V4.0TTL 121S1 2004.6.1SHARP LQ11S33 41A 单灯宽口 3.3V ZAN3V2.0TTL LN8060BC26_17 SHARP LQ11S452 41A 芃峰单灯宽口 3.3v ZAN34.0TTL LQ11S53 2004.6.19SHARP LQ11S46 41A 芃峰单灯宽口5V ZAN34.0TTL LQ121S1 2004.6.10 SHARP LQ11S53 41B 晶明单灯宽口 3.3V ZAN3V2.0TTL LQ11S53 2004.8.4SHARP LQ11S63 MOLXE14 V.V.G.G.0-.0+.1-.1+.2-.2+.C-.C+ 九深单灯窄口 3.3V ZAN3XL LQ11S63 2004.10.10SHARP LQ121S1DDG11 41A 蓝焰双灯 3.3 ZAN3V2.0TTL LP121S1 2004.8.2SHARP LQ121S1DDG11 41A 蓝焰双灯 3.3 ZAN3V2.0TTL LQ121S1 2004.5.11 OKSHARP LQ121S1DG11; 41A 力嘉双灯 3.3V ZAN34.0TTL 121S1 2004.7.3SHARP LQ121S1LG41 OK OK 双灯 3.3 2221 LTA104S1_L01_SVGA_LVDS 2006.2.12SHARP LQ121S1LH02 DF14 单灯宽口 3.3v 5020 121S1SHARP LQ121S1LH02 S6B LVDS20Pin SLW 3.3 gmZAN3 V2.0 NOSHARP LQ121S1LH13 DF14 20PIN 跳两信号两地排列单灯宽口 3.3V ZAN3V4.0LVDS ITXG72 2004.7.27SHARP LQ121S1LH33 DF14 跳两信号两地排列黄先生单灯小口 3.3V . Zan3_lq12s53_OK 2005.11.30SHARP LQ12DX02 LVDS双6位芃峰单灯宽口5V ZAN2V4.0lvds NL10276BC26_09 2004.5.22 推想没有试验SHARP LQ12DX03 911双6位福星达单灯窄口 3.3v 9011B LQ12DX03 2004.6.29SHARP LQ12S05_03C 41A 芃峰单灯宽口 3.3v ZAN34.0TTL LQ11S53 2004.6.19SHARP LQ12S11 41A35_0 单灯宽口 3.3V ZAN3V4.0TTL 121S1 2005.01.04 SHARP lq12s56 41A 福星达单灯宽口 3.3V ZAN34.0TTL lq12s56 2004.8.21SHARP LQ12X022 2004.4.6SHARP LQ12X022 ZAN2双6BIT 天之骄单灯宽口5V 5020双LVDS LQ14X02 2004.4.15 OKSHARP LQ12X43 911双6位单灯宽口5V 9011B LT150X1M 2004.7.27 SHARP LQ12X54 MOLXE 20pin 单灯宽口 3.3 ZAN3SL LQ12X54 2006.2.17 SHARP LQ133X02A 9011B双6bit 单灯窄口 3.3V ZAN3SLSHARP LQ133X1LH05 DF14 双灯 3.3V ZAN34.0LVDS LQ150X1LH82 2004.9.2 OKSHARP LQ133X1TH71 MOLXE 14PIN V.V.G.G.0-.0+.1-.1+.2-.2+.C-.C+.G.G G05电脑双灯 3.3V ZAN3V4.0 TMDS TM150XG_060 2004.9.17SHARP LQ133X1TH71 TMDS GG2+2-G1+1-G0+0-GC+C-GVV 芃峰双灯 3.3V ZAN2V5.0TMDS CLNERL 2004.6.3SHARP LQ133X1TH71 TMDS GG2+2-G1+1-G0+0-GC+C-GVV 芃峰双灯 3.3V ZAN3 4.0TMDS CLNERL 2004.9.2 OKSHARP LQ13X21 DF14 微硕单灯宽口 3.3V ZAN34.0LVDS LQ150X1LH82 2004.8.25SHARP LQ13X25 DF14 单灯窄口 3.3V ZAN3V4.0LVDSSHARP LQ141F1LH52 38D94 单灯窄口2004.9.21SHARP LQ14X03E SHARPDG51 徐小姐双灯 3.3v ZAN34.0TTL LQ14X042 2004.6.27SHARP LQ150F1LH22 38D94 D6B LVDS SLN 3.3 MST9011BV1.1 SXGA_38D95SHARP LQ150F1LH22 91138D94 卓耀单灯窄口 3.3V 9011B 38D95 04.03.03SHARP LQ150F1LH32EF 38D94 D6B LVDS SLN 3.3 MST9011BV1.1 SXGA_38D95SHARP LQ150U1LW22 38D94 单灯窄口 3.3V ZAN3SL ITUX97H 2004.10.11SHARP LQ150U1LW22 不能点鑫合基SHARP LQ150X1DG01 DG51FFC 柯荣双灯5V ZAN3V4.0TTLFFC SHARPDG51FFC 2004.11.03SHARP LQ150X1DG10 DG51FFC 柯荣双灯5V ZAN3V4.0TFFC SHARPDG51 2004.10.24SHARP LQ150X1DG11 SHARPDG51 双灯5V ZAN3V4.0双TTL LQ150X1DG11 04.03.05SHARP LQ150X1DG28 15X16线柯荣双灯5V ZAN3V4.0TTL LQ14X042 2004.11.03SHARP LQ150X1DH10 DG51FFC 柯荣双灯5V ZAN3V4.0TFFC SHARPDG51 2004.10.24SHARP LQ150X1LBE1 38D94 D6B LVDS 30Pin SLN 3.3 gmZAN3L V4.0 ITXG72SHARP LQ150X3DG51 DG51 塞维5V ZAN32.0TTLSHARP LQ15X01W SHARPDG51 伊麦双灯5V ZAN3V2.0TTL LQ14X02 2004.8.3SHARP LQ15X01W SHARPDG51 伊麦双灯5V ZAN3V4.0TTL LQ14X02 2004.7.30SHARP LQ15X05 DG51FFC 旭森双灯5V ZAN3V4.0TTLFFC SHARPDG51FFC 2004.11.03SHARP LQ15X11 15X16线柯荣双灯5V ZAN3V4.0TTL LQ14X042 2004.11.03SHARP LQ15X11 15X16线柯荣双灯5V ZAN3V4.0TTL LQ14X042 2004.11.03SHARP LQ15X14 DG51FFC 柯荣双灯5V ZAN3V4.0TTL SHARPDG51FFC 2004.11.03SHARP LQ15X14 TTL 60pin DLW 5 gmZAN3T V4.0SHARP LQ15X16 15X16线双灯 3.3V 5020v1.3TTL LQ14X02 2004.9.2 OKSHARP LQ15X16 15X16线柯荣双灯5V ZAN3V4.0TTL LQ14X042 2004.11.03SHARP LQ15X21 DF14 技博双灯 3.3v ZAN32.0LVDS LQ15X21 2004.8.13SHARP LQ170M1LA04 38D94 双灯小口 3.3 ZAN3SL 154P1-L04(1920X1200)2006.02.26SHARP LQ184V1DG21 31A 单灯宽口 3.3 ZAN3LVDS LQ104V3DG51_640X480 2006.02.23SHARP LQ1S353 41B 芃峰单灯宽口5V ZAN34.0TTL LQ121S1 2004.6.10 SHARP LQ64D343 31A 双灯5V ZAN3V4.0TTL TX33_18 2004.10.11 SHARP QD17ER01 50=35FFC 四灯宽口J133V.J212V ZAN3S QD17ER01 2005.01.14SHIMEI N141X201 DF14 福星达单灯窄口 3.3 ZAN3V4.0lvds ITXG72 2004.7.20shrap LQ150F1LW04 91138D94 单灯窄口 3.3V 9011B 38D95 04.03.11 SHRAP LQ150X1LH82 DF14 卓耀单灯窄口 3.3V ZAN3LVDS LQ150X1LH82 04.03.08SINYO TM150XG_26L04C TMDS 利嘉双灯5V 2004.4.2SINYO TM150XG_26L04C TMDS 三普双灯5V 5020 TM150XG_26L04C 2004.7.18SOYA TM150XG_26L10c DF14 8bit 四灯宽口 3.3V ZAN2V4.0lvds ITXG728bit 2004.7.27TODHBA LTM14C421F DF19 14PIN 袁立灿单灯窄口 3.3V ZAN3V2.0LVDS 141X7 04.03.13TODSHIBA LTM12C278P DF19 金鼎络单灯窄口 3.3V ZAN3V4.0LVDS 2004.4.1 没点亮TOPPOIY TD141TGCD1 38D94 OK 单灯小口 3.3 ZAN3SL BL150XH6 2006.2.12TORISAN LS170E01 50=35FFC 四灯宽口J133V.J212V ZAN3S LS170E01 2005.01.14TORISAN LTM10C021 31B 单灯宽口TORISAN LTM11C011 41B 单灯宽口5v ZAN3V4.0TTL 121S1 2004.12.10 TORISAN LTM12C263 151X1A 单灯宽口5v ZAN3V4.0TTL 121S1 2004.12.10TORISAN TM100SV_02L02 DF1914pin跳V.V.0-.0+.G.1-.1+.G.2-.2+.G.C-.C+.G 和兴单灯宽口 3.3V ZAN3LVDS HSD11SR800X600 2004.11.03TORISAN TM121SV_02L01 41A 单灯宽口 3.3V ZAN34.0TTL 121S1 2004.6.3TORISAN TM121SV_02L01D 41A 芃峰单灯宽口 3.3v ZAN34.0TTL 121S1 2004.6.19TORISAN TM121SV_02L07A DF14 跳两信号两地排列单灯宽口 3.3V ZAN2V4.0lvds 800X600LVDS 2004.6.6 屏有问题TORISAN TM121SV_02L07B DF14 芃峰单灯窄口 3.3 ZAN3V4.0lvds TM121SV_02L07B 2004.7.24TOSHBA LTM09C031A 31B 易唯单灯宽口5v ZAN34.0TTL pvi6448 2004.9.O9 okTOSHIBA 41A ZAN3V2.0 袁立灿单灯窄口 3.3V ZAN3V2.0LVDS 141X7 04.03.16 无信号时闪DCLK改为20TOSHIBA LM10C272S MOLXE 14PIN V.V.G.G.0-.0+.1-.1+.2-.2+.C-.C+.G.G 芃峰单灯东自5V ZAN3V4.0LVDS HSD11SR800X600 2004.9.14 okTOSHIBA LT10C286S MOLXE 14PIN V.V.G.G.0-.0+.1-.1+.2-.2+.C-.C+.G.G 芃峰单灯宽口 3.3V ZAN3V4.0LVDS HSD11SR800X600 2004.9.14 ok TOSHIBA LTM08C351 DF19 30pin 技博单边双灯 3.3V ZAN34.0TTL LP121S1 2004.8.25 TTL pintoshiba ltm09c012 10+15J(没有屏线)风杨单灯宽口没点亮2004.6.6 TOSHIBA LTM10C029 31A 三盟单灯宽口5v ZAN3V4.0TTL PVI6448 2004.11.03TOSHIBA LTM10C272 MOLXE14 V.V.G.G.0-.0+.1-.1+.2-.2+.C-.C+ 单灯窄口5V ZAN3V4.0LVDS 800X600LVDS 2004.8.3TOSHIBA LTM11C011STOSHIBA LTM11C016 41B 芃峰单灯宽口5v ZAN3V4.0TTL LTM11C016 2004.5.15 排阻220toshiba LTM12C025S 911双6位芃峰单灯宽口2004.7.11TOSHIBA LTM12C268E 41A 单灯宽口 3.3V ZAN3V4.0TTL LP121S1 2004.10.16toshiba LTM12C268F 41A 华晶单灯宽口3。

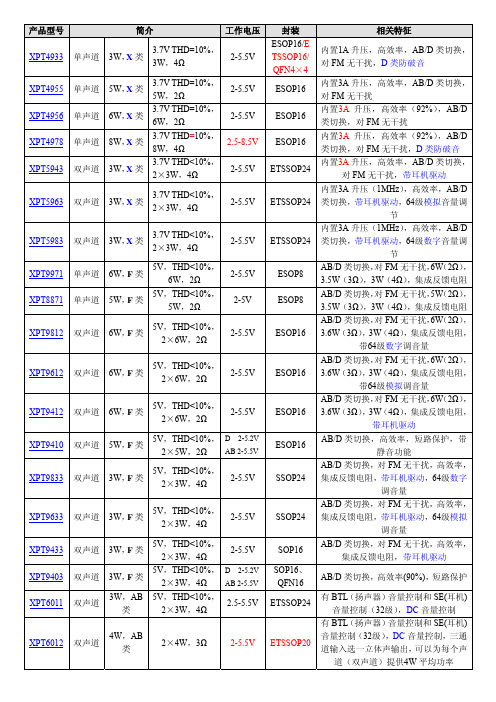

矽普特产品简介

XPT5983 XPT9971 XPT8871 XPT9812

XPT9612

XPT9412 XPT9410 XPT9833

XPT9633 XPT9433 XPT9403 XPT6011

XPT6012

道(双声道)提供4W 平均功率

产品型号 XPT6013 XPT6871 XPT6875 XPT4809

XPT9863

XPT8863

XPT2008

XPT2069

XPT2068 C

XPT4098 XPT4871

F XPT4890 XPT4990 XPT0030 XPT4066 XPT4088 XPT4068 XPT6872

4 SOP18/SS OP24/SOP

16

SOP16/QF N16/DIP16 MSOP8/SO P8/ESOP8/

DFN8 MSOP8/SO

P8/DFN

WCSP9

MSOP8/ES OP8/SOP8/

DFN

WCSP

备注 单端模式,5V,THD+N≤0.5%,75mW (32Ω)。XPT4963的 SD 是高电平工作,

封装

ETSSOP20

SOP8

ESOP8

MSOP8/SO P8

SOP16/DIP 16/ETSSO P16/ETSS OP20 SOP16/ET SSOP20/DI P16

SOP8/ ESOP8

SOP16/DIP 16/ESOP16

SOP16/ES OP16/DIP1

6

QFN16/SO P16/DIP16

完全兼容 LM4861/8002 ,XPT4871H

MEMORY存储芯片M25P64-VME6TG中文规格书

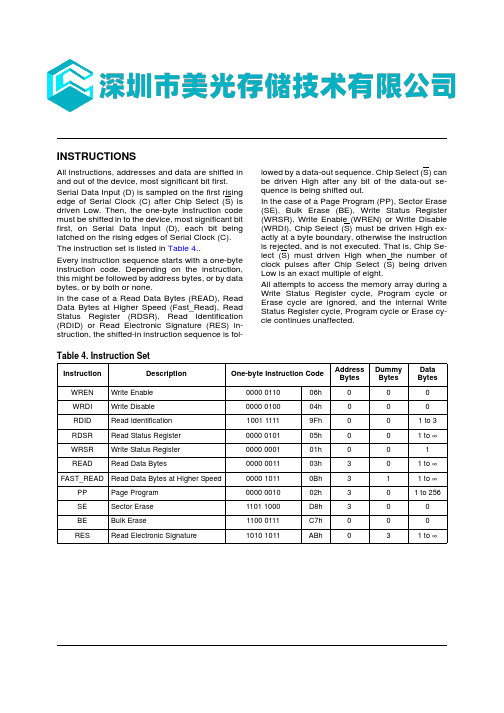

INSTRUCTIONSAll instructions, addresses and data are shifted in and out of the device, most significant bit first.Serial Data Input (D) is sampled on the first rising edge of Serial Clock (C) after Chip Select (S) is driven Low. Then, the one-byte instruction code must be shifted in to the device, most significant bit first, on Serial Data Input (D), each bit being latched on the rising edges of Serial Clock (C).The instruction set is listed in Table 4..Every instruction sequence starts with a one-byte instruction code. Depending on the instruction,this might be followed by address bytes, or by data bytes, or by both or none.In the case of a Read Data Bytes (READ), Read Data Bytes at Higher Speed (Fast_Read), Read Status Register (RDSR), Read Identification (RDID) or Read Electronic Signature (RES) in-struction, the shifted-in instruction sequence is fol-lowed by a data-out sequence. Chip Select (S) can be driven High after any bit of the data-out se-quence is being shifted out.In the case of a Page Program (PP), Sector Erase (SE), Bulk Erase (BE), Write Status Register (WRSR), Write Enable (WREN) or Write Disable (WRDI), Chip Select (S) must be driven High ex-actly at a byte boundary, otherwise the instruction is rejected, and is not executed. That is, Chip Se-lect (S) must driven High when the number of clock pulses after Chip Select (S) being driven Low is an exact multiple of eight.All attempts to access the memory array during a Write Status Register cycle, Program cycle or Erase cycle are ignored, and the internal Write Status Register cycle, Program cycle or Erase cy-cle continues unaffected.Table 4. Instruction SetInstructionDescriptionOne-byte Instruction CodeAddressBytesDummyBytesData Bytes WREN Write Enable 0000 011006h 000WRDI Write Disable 0000 010004h 000RDID Read Identification 1001 11119Fh 0 0 1 to 3RDSR Read Status Register 0000 010105h 0 0 1 to ∞WRSR Write Status Register 0000 000101h 0 0 1 READRead Data Bytes0000 001103h 30 1 to ∞FAST_READ Read Data Bytes at Higher Speed0000 10110Bh 31 1 to ∞PP Page Program 0000 001002h 30 1 to 256SESector Erase1101 1000D8h 3 0 0 BE Bulk Erase 1100 0111C7h 000RESRead Electronic Signature1010 1011ABh31 to ∞Write Enable (WREN)The Write Enable (WREN) instruction (Figure 9.) sets the Write Enable Latch (WEL) bit.The Write Enable Latch (WEL) bit must be set pri-or to every Page Program (PP), Sector Erase (SE), Bulk Erase (BE) and Write Status Register (WRSR) instruction.The Write Enable (WREN) instruction is entered by driving Chip Select (S) Low, sending the in-struction code, and then driving Chip Select (S) High.Write Disable (WRDI)The Write Disable (WRDI) instruction (Figure 10.) resets the Write Enable Latch (WEL) bit.The Write Disable (WRDI) instruction is entered by driving Chip Select (S) Low, sending the instruc-tion code, and then driving Chip Select (S) High. The Write Enable Latch (WEL) bit is reset under the following conditions: –Power-up–Write Disable (WRDI) instruction completion –Write Status Register (WRSR) instruction completion–Page Program (PP) instruction completion –Sector Erase (SE) instruction completion–Bulk Erase (BE) instruction completionRead Data Bytes at Higher Speed(FAST_READ)The device is first selected by driving Chip Select (S)Low. The instruction code for the Read Data Bytes at Higher Speed (FAST_READ) instruction is followed by a 3-byte address (A23-A0) and a dummy byte, each bit being latched-in during the rising edge of Serial Clock (C). Then the memory contents, at that address, is shifted out on Serial Data Output (Q), each bit being shifted out, at a maximum frequency f C, during the falling edge of Serial Clock (C).The instruction sequence is shown in Figure 15.. The first byte addressed can be at any location. The address is automatically incremented to the next higher address after each byte of data is shift-ed out. The whole memory can, therefore, be read with a single Read Data Bytes at Higher Speed (FAST_READ) instruction. When the highest ad-dress is reached, the address counter rolls over to 000000h, allowing the read sequence to be contin-ued indefinitely.The Read Data Bytes at Higher Speed (FAST_READ) instruction is terminated by driving Chip Select (S) High. Chip Select (S) can be driv-en High at any time during data output. Any Read Data Bytes at Higher Speed (FAST_READ) in-struction, while an Erase, Program or Write cycle is in progress, is rejected without having any ef-fects on the cycle that is in progress.M25P64Page Program (PP)The Page Program (PP) instruction allows bytes to be programmed in the memory (changing bits from 1 to 0). Before it can be accepted, a Write Enable (WREN) instruction must previously have been ex-ecuted. After the Write Enable (WREN) instruction has been decoded, the device sets the Write En-able Latch (WEL).The Page Program (PP) instruction is entered by driving Chip Select (S) Low, followed by the in-struction code, three address bytes and at least one data byte on Serial Data Input (D). If the 8 least significant address bits (A7-A0) are not all zero, all transmitted data that goes beyond the end of the current page are programmed from the start address of the same page (from the address whose 8 least significant bits (A7-A0) are all zero). Chip Select (S) must be driven Low for the entire duration of the sequence.The instruction sequence is shown in Figure 16.. If more than 256 bytes are sent to the device, pre-viously latched data are discarded and the last 256 data bytes are guaranteed to be programmed cor-rectly within the same page. If less than 256 Data bytes are sent to device, they are correctly pro-grammed at the requested addresses without hav-ing any effects on the other bytes of the same page.Chip Select (S) must be driven High after the eighth bit of the last data byte has been latched in, otherwise the Page Program (PP) instruction is not executed.As soon as Chip Select (S) is driven High, the self-timed Page Program cycle (whose duration is t PP) is initiated. While the Page Program cycle is in progress, the Status Register may be read to check the value of the Write In Progress (WIP) bit. The Write In Progress (WIP) bit is 1 during the self-timed Page Program cycle, and is 0 when it is completed. At some unspecified time before the cycle is completed, the Write Enable Latch (WEL) bit is reset.A Page Program (PP) instruction applied to a page which is protected by the Block Protect (BP2, BP1, BP0) bits (see Table 2. and Table 3.) is not execut-ed.M25P64。

MEMORY存储芯片M25PE16-VMW6TG中文规格书

DATA BRIEFOctober 2004For further information contact your local ST sales office.512 Kbit to 32 Mbit, Low Voltage, Serial Flash MemoryWith 40 MHz or 50 MHz SPI Bus InterfaceFEATURES SUMMARY■512Kbit to 32Mbit of Flash Memory■Page Program (up to 256 Bytes) in 1.4ms (typical)■Sector Erase (256 Kbit or 512Kbit)■Bulk Erase (512Kbit to 32Mbit)■ 2.7 to 3.6V Single Supply Voltage ■SPI Bus Compatible Serial Interface■40MHz to 50MHz Clock Rate (maximum)■Deep Power-down Mode 1µA (typical)■Electronic Signatures–JEDEC Standard Two-Byte Signature(20xxh)–RES Instruction, One-Byte, Signature, forbackward compatibility■More than 100000 Erase/Program Cycles per Sector■More than 20 Year Data RetentionTable 1. Product ListReferencePart NumberM25PxxM25P32M25P16M25P80M25P40M25P20M25P10-A M25P05-AM25PXXSUMMARY DESCRIPTIONThe M25Pxx is a 512Kbit to 32Mbit (2M x 8) Serial Flash Memory, with advanced write protection mechanisms, accessed by a high speed SPI-com-patible bus.The memory can be programmed 1 to 256 bytes at a time, using the Page Program instruction.The memory is organized as a number of sectors, each containing 256 or 128 pages. Each page is 256 bytes wide.The whole memory can be erased using the Bulk Erase instruction, or a sector at a time, using the Sector Erase instruction.Table 2. Signal NamesNote: 1.There is an exposed die paddle on the underside of the MLP8 package. This is pulled, internally, to V SS, andmust not be allowed to be connected to any other voltageor signal line on the PCB.Note: 1.DU = Don’t UseC SerialClockD Serial Data InputQ Serial Data Output S Chip SelectW WriteProtect HOLD HoldV CC Supply VoltageV SS GroundM25PXXTable 3. Instruction SetTable 4. Status Register FormatInstruction DescriptionOne-byte Instruction CodeAddressBytesDummy BytesData Bytes WREN Write Enable 0000 011006h 0 0 0 WRDI Write Disable 0000 010004h 0 0 0 RDID Read Identification 1001 11119Fh 0 0 1 to 3RDSR Read Status Register 0000 010105h 0 0 1 to ∞WRSR Write Status Register 0000 000101h 0 0 1 READRead Data Bytes0000 001103h 30 1 to ∞FAST_READ Read Data Bytes at Higher Speed0000 10110Bh 31 1 to ∞PPPage Program0000 001002h 30 1 to 256SE Sector Erase 1101 1000D8h 300BE Bulk Erase 1100 0111C7h 0 0 0 DP Deep Power-down1011 1001B9h 0 0RESRelease from Deep Power-down,and Read Electronic Signature 1010 1011ABh0 3 1 to ∞Release from Deep Power-downb7b0SRWD0 BP2 BP1 BP0 WEL WIPStatus RegisterWrite ProtectBlock Protect Bits Write Enable Latch BitWrite In Progress Bit。

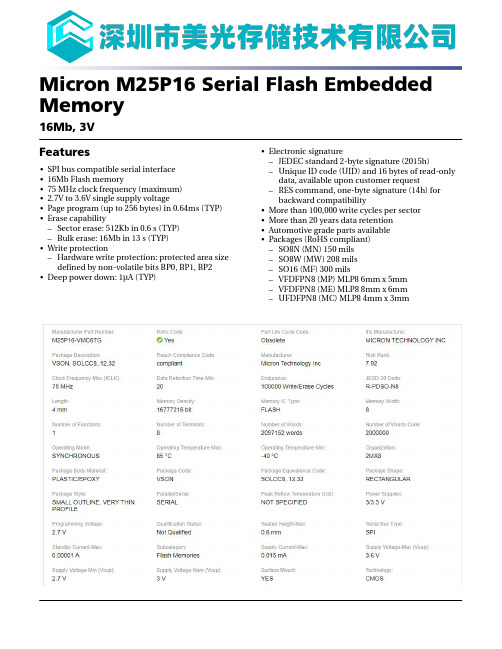

MEMORY存储芯片M25P16-VMC6TG中文规格书

Micron M25P16 Serial Flash Embedded Memory16Mb, 3V Features•SPI bus compatible serial interface •16Mb Flash memory•75 MHz clock frequency (maximum)•2.7V to 3.6V single supply voltage•Page program (up to 256 bytes) in 0.64ms (TYP)•Erase capability–Sector erase: 512Kb in 0.6 s (TYP)–Bulk erase: 16Mb in 13 s (TYP)•Write protection–Hardware write protection: protected area size defined by non-volatile bits BP0, BP1, BP2•Deep power down: 1µA (TYP)•Electronic signature–JEDEC standard 2-byte signature (2015h)–Unique ID code (UID) and 16 bytes of read-only data, available upon customer request–RES command, one-byte signature (14h) for backward compatibility•More than 100,000 write cycles per sector •More than 20 years data retention •Automotive grade parts available •Packages (RoHS compliant)–SO8N (MN) 150 mils –SO8W (MW) 208 mils –SO16 (MF) 300 mils–VFDFPN8 (MP) MLP8 6mm x 5mm –VFDFPN8 (ME) MLP8 8mm x 6mm –UFDFPN8 (MC) MLP8 4mm x 3mmMicron M25P16 Serial Flash Embedded MemoryImportant Notes and WarningsFunctional DescriptionThe M25P16 is an 16Mb (2Mb x 8) serial Flash memory device with advanced write pro-tection mechanisms accessed by a high speed SPI-compatible bus. The device supports high-performance commands for clock frequency up to 75MHz.The memory can be programmed 1 to 256 bytes at a time using the PAGE PROGRAM command. It is organized as 32 sectors, each containing 256 pages. Each page is 256bytes wide. Memory can be viewed either as 8,192 pages or as 2,097,152 bytes. The en-tire memory can be erased using the BULK ERASE command, or it can be erased one sector at a time using the SECTOR ERASE command.This datasheet details the functionality of the M25P16 device based on 110nm process.Figure 1: Logic DiagramS#V CCHOLD#V SSDQ1C DQ0W#Table 1: Signal NamesMicron M25P16 Serial Flash Embedded MemoryFunctional DescriptionFigure 5: Bus Master and Memory Devices on the SPI BusSS2.Resistors (R) ensure that the memory device is not selected if the bus master leaves theS# line High-Z.3.The bus master may enter a state where all I/O are High-Z at the same time; for exam-ple, when the bus master is reset. Therefore, C must be connected to an external pull-down resistor so that when all I/O are High-Z, S# is pulled HIGH while C is pulled LOW.This ensures that S# and C do not go HIGH at the same time and that the t SHCH require-ment is met.4.The typical value of R is 100kΩ, assuming that the time constant R × C p (C p = parasiticcapacitance of the bus line) is shorter than the time during which the bus master leavesthe SPI bus High-Z.5.Example: Given that C p = 50pF (R × C p= 5μs), the application must ensure that the busmaster never leaves the SPI bus High-Z for a time period shorter than 5μs.质量等级领域:宇航级IC、特军级IC、超军级IC、普军级IC、禁运IC、工业级IC,军级二三极管,功率管等;应用领域:航空航天、船舶、汽车电子、军用计算机、铁路、医疗电子、通信网络、电力工业以及大型工业设备祝您:工作顺利,生活愉快!以深圳市美光存储技术有限公司提供的参数为例,以下为M25P16-VMC6TG的详细参数,仅供参考。

迈普语音产品配置说明

MyPower VG M6500 VM6500-FANH PCR01-48/20

1 1 2

保号用户,保留208 个电信号码

保号用户,保留208 个电信号码 VM6000-MPUH VM-2DSP VM-16S16OH

主控卡:不带E1,支持两个100M以太口,一个 配置口,支持热拔插。 DSP卡,支持160路并发 业务卡:支持16路FXS模拟接入和16路FXO模拟 中继,支持热拔插。 主机机框。包括主机结构、背板,直流供电, 机框不包括风扇,提供16个槽位。 风扇 电源 主控卡:不带E1,支持两个100M以太口,一个 配置口,支持热拔插。 DSP卡,支持160路并发 业务卡:支持16路FXS模拟接入和16路FXO模拟 中继,支持热拔插。

1 2 1 1 2 覆盖32个保号需求,语音设备配置清单(VG M6000)

覆盖48个保号需求,语音设备配置清单(VG M6000)

MyPower VG M6000 AD150-1S007W1 保号用户,保留48 个电信号码 VM6000-MPUH VM-1DSP VM-16S16OH

1 2 1 1 3

覆盖64个保号需求,语音设备配置清单(VG M6500)

MyPower VG M6500 VM6500-FANH PCR01-48/20

1 1 2 1 1 4

保号用户,保留64 个电信号码 VM6000-MPUH VM-2DSP VM-16S16OH

覆盖80个保号需求,语音设备配置清单(VG M6500)

主控卡:不带E1,支持两个100M以太口,一个 配置口,支持热拔插。 DSP卡,支持160路并发 业务卡:支持16路FXS模拟接入和16路FXO模拟 中继,支持热拔插。 主机机框。包括主机结构、背板,直流供电, 机框不包括风扇,提供16个槽位。 风扇 电源 主控卡:不带E1,支持两个100M以太口,一个 配置口,支持热拔插。 DSP卡,支持160路并发 业务卡:支持16路FXS模拟接入和16路FXO模拟 中继,支持热拔插。 主机机框。包括主机结构、背板,直流供电, 机框不包括风扇,提供16个槽位。 风扇 电源 主控卡:不带E1,支持两个100M以太口,一个 配置口,支持热拔插。 DSP卡,支持160路并发 业务卡:支持16路FXS模拟接入和16路FXO模拟 中继,支持热拔插。 主机机框。包括主机结构、背板,直流供电, 机框不包括风扇,提供16个槽位。 风扇 电源 主控卡:不带E1,支持两个100M以太口,一个 配置口,支持热拔插。 DSP卡,支持160路并发 业务卡:支持16路FXS模拟接入和16路FXO模拟 中继,支持热拔插。 主机机框。包括主机结构、背板,直流供电, 机框不包括风扇,提供16个槽位。 风扇 电源 主控卡:不带E1,支持两个100M以太口,一个 配置口,支持热拔插。 DSP卡,支持160路并发 业务卡:支持16路FXS模拟接入和16路FXO模拟 中继,支持热拔插。 主机机框。包括主机结构、背板,直流供电, 机框不包括风扇,提供16个槽位。 风扇 电源 主控卡:不带E1,支持两个100M以太口,一个 配置口,支持热拔插。 DSP卡,支持160路并发 业务卡:支持16路FXS模拟接入和16路FXO模拟 中继,支持热拔插。 主机机框。包括主机结构、背板,直流供电, 机框不包括风扇,提供16个槽位。 风扇 电源

MEMORY存储芯片M25P16-VMP6TG中文规格书

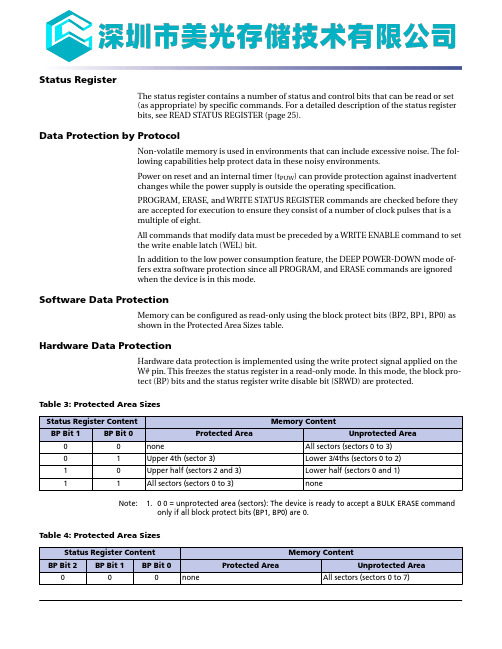

Status RegisterThe status register contains a number of status and control bits that can be read or set(as appropriate) by specific commands. For a detailed description of the status registerbits, see READ STATUS REGISTER (page 25).Data Protection by ProtocolNon-volatile memory is used in environments that can include excessive noise. The fol-lowing capabilities help protect data in these noisy environments.Power on reset and an internal timer (t PUW) can provide protection against inadvertentchanges while the power supply is outside the operating specification.PROGRAM, ERASE, and WRITE STATUS REGISTER commands are checked before theyare accepted for execution to ensure they consist of a number of clock pulses that is amultiple of eight.All commands that modify data must be preceded by a WRITE ENABLE command to setthe write enable latch (WEL) bit.In addition to the low power consumption feature, the DEEP POWER-DOWN mode of-fers extra software protection since all PROGRAM, and ERASE commands are ignoredwhen the device is in this mode.Software Data ProtectionMemory can be configured as read-only using the block protect bits (BP2, BP1, BP0) asshown in the Protected Area Sizes table.Hardware Data ProtectionHardware data protection is implemented using the write protect signal applied on theW# pin. This freezes the status register in a read-only mode. In this mode, the block pro-tect (BP) bits and the status register write disable bit (SRWD) are protected.Table 3: Protected Area SizesNote: 1.0 0 = unprotected area (sectors): The device is ready to accept a BULK ERASE commandonly if all block protect bits (BP1, BP0) are 0.Table 4: Protected Area SizesNote: 1.0 0 0 = unprotected area (sectors): The device is ready to accept a BULK ERASE command only if all block protect bits (BP2, BP1, BP0) are 0.质量等级领域:宇航级IC、特军级IC、超军级IC、普军级IC、禁运IC、工业级IC,军级二三极管,功率管等;应用领域:航空航天、船舶、汽车电子、军用计算机、铁路、医疗电子、通信网络、电力工业以及大型工业设备祝您:工作顺利,生活愉快!以深圳市美光存储技术有限公司提供的参数为例,以下为M25P16-VMP6TG的详细参数,仅供参考Table 10: Command Set Codes。

MAXHUB产品深度技术培训

型号

B02C SRI.SUSB.01B SRC.Camera Trans.01A SRS.HTJ41.01B

CN.SR.01A

适用机型

旗舰版 增强版/旗舰版

增强版 旗舰版 增强版/旗舰版 增强版/旗舰版 增强版/旗舰版

关键器件-MT21

关键点: 1.连接安卓转接板 2.连接PC转接板

1

2

作用: 增强PC模块到安卓模 块的信号

关键器件-VBO小板

CN.HDMI_SW.01

关键点: 1.连接TCON 2.连接HDMIOUT小板 3.连接TV主板 4.12V供电输入接口 5.PVCC 作用: 把TV板卡或者HDMI OUT 的信号传递到TCON

关键器件-MT21

关键器件-MT21

关键点: 1.无蓝牙WIFI模块 2.无天线座子 3.128G/256G SSD 4.核显 5.I5/I7 6.MD机型可选I3

PC 电源

CPU SSD

内存

关键器件-SA05

关键器件-TV板 (T.HV510.73C)

T.HV510.73

关键点: 1.连接USB HUB板 2.连接安卓转接板 3.连接VBO小板 4.连接TV电源板 5.连接USB小板,遥控头,按键板 6.连接喇叭 7.连接触摸框

问题: PC/安卓模块无信号,模块能启动

思路: ①若从开机开始就检测不到模块,有可能是安卓转接板缺陷,需要更换转接板 ②若整机静置一段时间后才检测不到模块,有可能是整机进入休眠状态。进入PC 的电源设置,把所有会导致息屏的设置都设为从不

近期案例

问题: 电磁笔书写出现跳线、无法双笔书写等与电磁笔相关的一切故障

HP Color LaserJet Pro M252 用户指南说明书

此处包含的信息如有更改,恕不另行通 知。

HP 产品及服务的保修仅以随该产品及 服务提供的书面保修声明为准。本文所 述任何内容不应被视为附加保修。对任 何技术或编辑错误或者本文所述内容的 遗漏,HP 不承担任何责任。

Edition 3, 8/2019

2 纸盘 .......................................................................................................................................................................................................... 15 将纸张装入单页进纸槽(纸盘 1) ................................................................................................................................ 16 简介 ..................................................................................................................................................................... 16 将纸张装入单页优先进纸槽 ........................................................................................................................ 16 在单页优先进纸槽中装入信封(纸盘 1) .............................................................................................. 17 纸盘 1 纸张方向 ............................................................................................................................................... 19 在纸盘 2 中装入纸张 .......................................................................................................................................................... 20 简介 ..................................................................................................................................................................... 20 在纸盘 2 中装入纸张 ...................................................................................................................................... 20 在纸盘 2 中装入信封 ...................................................................................................................................... 22 纸盘 2 纸张方向 ............................................................................................................................................... 25

M25P16

Micron M25P16 Serial Flash Embedded Memory16 Mb, 3VFeatures•SPI bus compatible serial interface•16Mb Flash memory•75 MHz clock frequency (maximum)•2.7V to 3.6V single supply voltage•Page program (up to 256 bytes) in 0.64ms (TYP)•Erase capability–Sector erase: 512Kb in 0.6 s (TYP)–Bulk erase: 16Mb in 13 s (TYP)•Write protection–Hardware write protection: protected area size defined by non-volatile bits BP0, BP1, BP2•Deep power down: 1µA (TYP)•Electronic signature–JEDEC standard 2-byte signature (2015h)–Unique ID code (UID) and 16 bytes of read-only data, available upon customer request–RES command, one-byte signature (14h) for backward compatibility•More than 100,000 write cycles per sector•More than 20 years data retention•Automotive grade parts available•Packages (RoHS compliant)–SO8N (MN) 150 mils–SO8W (MW) 208 mils–SO16 (MF) 300 mils–VFDFPN8 (MP) MLP8 6mm x 5mm–VFDFPN8 (ME) MLP8 8mm x 6mm–UFDFPN8 (MC) MLP8 4mm x 3mmContentsFunctional Description (6)Signal Descriptions (8)SPI Modes (9)Operating Features (11)Page Programming (11)Sector Erase, Bulk Erase (11)Polling during a Write, Program, or Erase Cycle (11)Active Power, Standby Power, and Deep Power-Down (11)Status Register (12)Data Protection by Protocol (12)Software Data Protection (12)Hardware Data Protection (12)Hold Condition (13)Configuration and Memory Map (14)Memory Configuration and Block Diagram (14)Memory Map – 16Mb Density (15)Command Set Overview (16)WRITE ENABLE (18)WRITE DISABLE (19)READ IDENTIFICATION (20)READ STATUS REGISTER (21)WIP Bit (22)WEL Bit (22)Block Protect Bits (22)SRWD Bit (22)SRWD Bit (22)WRITE STATUS REGISTER (23)READ DATA BYTES (25)READ DATA BYTES at HIGHER SPEED (26)PAGE PROGRAM (27)SECTOR ERASE (28)BULK ERASE (29)DEEP POWER-DOWN (30)RELEASE from DEEP POWER-DOWN (31)READ ELECTRONIC SIGNATURE (32)Power-Up/Down and Supply Line Decoupling (33)Power-Up Timing and Write Inhibit Voltage Threshold Specifications (35)Maximum Ratings and Operating Conditions (36)Electrical Characteristics (37)AC Characteristics (38)Package Information (44)Device Ordering Information (50)Standard Parts (50)Automotive Parts (51)Revision History (53)Rev. H – 1/14 (53)Rev. G – 1/13 (53)Rev. F – 10/12 (53)Rev. E – 8/12 (53)Rev. D – 05/12 (53)Rev. C – 3/12 (53)Rev. B – 3/12 (53)Rev. A – 09/2011 (53)List of FiguresFigure 1: Logic Diagram (6)Figure 2: Pin Connections: SO8, VFQFPN , VDFPN (7)Figure 3: Pin Connections: SO16 (7)Figure 4: SPI Modes Supported (9)Figure 5: Bus Master and Memory Devices on the SPI Bus (10)Figure 6: Hold Condition Activation (13)Figure 7: Block Diagram (14)Figure 8: WRITE ENABLE Command Sequence (18)Figure 9: WRITE DISABLE Command Sequence (19)Figure 10: READ IDENTIFICATION Command Sequence (20)Figure 11: READ STATUS REGISTER Command Sequence (21)Figure 12: Status Register Format (21)Figure 13: WRITE STATUS REGISTER Command Sequence (23)Figure 14: READ DATA BYTES Command Sequence (25)Figure 15: READ DATA BYTES at HIGHER SPEED Command Sequence (26)Figure 16: PAGE PROGRAM Command Sequence (27)Figure 17: SECTOR ERASE Command Sequence (28)Figure 18: BULK ERASE Command Sequence (29)Figure 19: DEEP POWER-DOWN Command Sequence (30)Figure 20: RELEASE from DEEP POWER-DOWN Command Sequence (31)Figure 21: READ ELECTRONIC SIGNATURE Command Sequence (32)Figure 22: Power-Up Timing (34)Figure 23: AC Measurement I/O Waveform (38)Figure 24: Serial Input Timing (42)Figure 25: Write Protect Setup and Hold during WRSR when SRWD=1 Timing (42)Figure 26: Hold Timing (43)Figure 27: Output Timing (43)Figure 28: SO8N 150 mils Body Width (44)Figure 29: SO8W 208 mils Body Width (45)Figure 30: SO16W 300 mils Body Width (46)Figure 31: VFDFPN8 (MLP8) 6mm x 5mm (47)Figure 32: VFDFPN8 (MLP8) 8mm x 6mm (48)Figure 33: UFDFPN8 (MLP8) 4mm x 3mm (49)List of TablesTable 1: Signal Names (6)Table 2: Signal Descriptions (8)Table 3: Protected Area Sizes (12)Table 4: Sectors 31:0 (15)Table 5: Command Set Codes (17)Table 6: READ IDENTIFICATION Data Out Sequence (20)Table 7: Status Register Protection Modes (24)Table 8: Power-Up Timing and V WI Threshold (35)Table 9: Absolute Maximum Ratings (36)Table 10: Operating Conditions (36)Table 11: Data Retention and Endurance (36)Table 12: DC Current Specifications (37)Table 13: DC Voltage Specifications (37)Table 14: AC Measurement Conditions (38)Table 15: Capacitance (38)Table 16: AC Specifications (25 MHz, Device Grade 3, V CC[min]=2.7V) (38)Table 17: Instruction Times (25 MHz, Device Grade 3, V CC[min]=2.7V) (39)Table 18: AC Specifications (75 MHz, Device Grade 3 and 6, V CC[min]=2.7V) (40)Table 19: Instruction Times (75 MHz, Device Grade 3 and 6, V CC[min]=2.7V) (41)Table 20: Part Number Example (50)Table 21: Part Number Information Scheme (50)Table 22: Part Number Example (51)Table 23: Part Number Information Scheme (51)Functional DescriptionThe M25P16 is an 16Mb (2Mb x 8) serial Flash memory device with advanced write pro-tection mechanisms accessed by a high speed SPI-compatible bus. The device supports high-performance commands for clock frequency up to 75MHz.The memory can be programmed 1 to 256 bytes at a time using the PAGE PROGRAM command. It is organized as 32 sectors, each containing 256 pages. Each page is 256bytes wide. Memory can be viewed either as 8,192 pages or as 2,097,152 bytes. The en-tire memory can be erased using the BULK ERASE command, or it can be erased one sector at a time using the SECTOR ERASE command.This datasheet details the functionality of the M25P16 device based on 110nm process.Figure 1: Logic DiagramS#V CCHOLD#V SSDQ1C DQ0W#Table 1: Signal NamesFigure 2: Pin Connections: SO8, VFQFPN , VDFPN1234V CC HOLD#5678DQ1V SSS#DQ0C W#Note:1.There is an exposed central pad on the underside of the MLP8 package that is pulled in-ternally to V SS , and must not be connected to any other voltage or signal line on the PCB. The Package Mechanical section provides information on package dimensions and how to identify pin 1.Figure 3: Pin Connections: SO16123416151413V CC HOLD#DNU DNU DNU DNU DNU DNU DNU DNU 56781211109DQ1V SS S#DQ0C W#/V PPNotes:1.DU = Don't Use2.The Package Mechanical section provides information on package dimensions and howto identify pin 1.Signal Descriptions Table 2: Signal DescriptionsSPI ModesThese devices can be driven by a microcontroller with its serial peripheral interface (SPI) running in either of the following two SPI modes:•CPOL=0, CPHA=0•CPOL=1, CPHA=1For these two modes, input data is latched in on the rising edge of serial clock (C), and output data is available from the falling edge of C.The difference between the two modes is the clock polarity when the bus master is in STANDBY mode and not transferring data:•C remains at 0 for (CPOL=0, CPHA=0)•C remains at 1 for (CPOL=1, CPHA=1)Figure 4: SPI Modes SupportedCMSBCPHADQ001CPOL01DQ1CMSBBecause only one device is selected at a time, only one device drives the serial data out-put (DQ1) line at a time, while the other devices are HIGH-Z. An example of three devi-ces connected to an MCU on an SPI bus is shown here.Figure 5: Bus Master and Memory Devices on the SPI BusSSNotes: 1.WRITE PROTECT (W#) and HOLD# should be driven HIGH or LOW as appropriate.2.Resistors (R) ensure that the memory device is not selected if the bus master leaves theS# line HIGH-Z.3.The bus master may enter a state where all I/O are HIGH-Z at the same time; for exam-ple, when the bus master is reset. Therefore, C must be connected to an external pull-down resistor so that when all I/O are HIGH-Z, S# is pulled HIGH while C is pulled LOW.This ensures that S# and C do not go HIGH at the same time and that the t SHCH require-ment is met.4.The typical value of R is 100 kΩ, assuming that the time constant R × C p (C p = parasiticcapacitance of the bus line) is shorter than the time during which the bus master leavesthe SPI bus HIGH-Z.5.Example: Given that C p = 50 pF (R × C p= 5μs), the application must ensure that the busmaster never leaves the SPI bus HIGH-Z for a time period shorter than 5μs.Operating FeaturesPage ProgrammingTo program one data byte, two commands are required: WRITE ENABLE, which is onebyte, and a PAGE PROGRAM sequence, which is four bytes plus data. This is followed bythe internal PROGRAM cycle of duration t PP. To spread this overhead, the PAGE PRO-GRAM command allows up to 256 bytes to be programmed at a time (changing bitsfrom 1 to 0), provided they lie in consecutive addresses on the same page of memory. Tooptimize timings, it is recommended to use the PAGE PROGRAM command to programall consecutive targeted bytes in a single sequence than to use several PAGE PROGRAMsequences with each containing only a few bytes.Sector Erase, Bulk EraseThe PAGE PROGRAM command allows bits to be reset from 1 to 0. Before this can beapplied, the bytes of memory need to have been erased to all 1s (FFh). This can be ach-ieved a sector at a time using the SECTOR ERASE command, or throughout the entirememory using the BULK ERASE command. This starts an internal ERASE cycle of dura-tion t SE or t BE. The ERASE command must be preceded by a WRITE ENABLE command. Polling during a Write, Program, or Erase CycleAn improvement in the time to complete the following commands can be achieved bynot waiting for the worst case delay (t W, t PP, t SE, or t BE).•WRITE STATUS REGISTER•PROGRAM•ERASE (SECTOR ERASE, BULK ERASE)The write in progress (WIP) bit is provided in the status register so that the applicationprogram can monitor this bit in the status register, polling it to establish when the pre-vious WRITE cycle, PROGRAM cycle, or ERASE cycle is complete.Active Power, Standby Power, and Deep Power-DownWhen chip select (S#) is LOW, the device is selected, and in the ACTIVE POWER mode.When S# is HIGH, the device is deselected, but could remain in the ACTIVE POWERmode until all internal cycles have completed (PROGRAM, ERASE, WRITE STATUSREGISTER). The device then goes in to the STANDBY POWER mode. The device con-sumption drops to I CC1.The DEEP POWER-DOWN mode is entered when the DEEP POWER-DOWN commandis executed. The device consumption drops further to I CC2. The device remains in thismode until the RELEASE FROM DEEP POWER-DOWN command is executed. While inthe DEEP POWER-DOWN mode, the device ignores all WRITE, PROGRAM, and ERASEcommands. This provides an extra software protection mechanism when the device isnot in active use, by protecting the device from inadvertent WRITE, PROGRAM, orERASE operations. For further information, see the DEEP POWER DOWN command.Status RegisterThe status register contains a number of status and control bits that can be read or set(as appropriate) by specific commands. For a detailed description of the status registerbits, see READ STATUS REGISTER (page 21).Data Protection by ProtocolNon-volatile memory is used in environments that can include excessive noise. The fol-lowing capabilities help protect data in these noisy environments.Power on reset and an internal timer (t PUW) can provide protection against inadvertentchanges while the power supply is outside the operating specification.PROGRAM, ERASE, and WRITE STATUS REGISTER commands are checked before theyare accepted for execution to ensure they consist of a number of clock pulses that is amultiple of eight.All commands that modify data must be preceded by a WRITE ENABLE command to setthe write enable latch (WEL) bit.In addition to the low power consumption feature, the DEEP POWER-DOWN mode of-fers extra software protection since all PROGRAM, and ERASE commands are ignoredwhen the device is in this mode.Software Data ProtectionMemory can be configured as read-only using the block protect bits (BP2, BP1, BP0) asshown in the Protected Area Sizes table.Hardware Data ProtectionHardware data protection is implemented using the write protect signal applied on theW# pin. This freezes the status register in a read-only mode. In this mode, the block pro-tect (BP) bits and the status register write disable bit (SRWD) are protected.Table 3: Protected Area SizesNote: 1.0 0 0 = unprotected area (sectors): The device is ready to accept a BULK ERASE commandonly if all block protect bits (BP2, BP1, BP0) are 0.Hold ConditionThe HOLD# signal is used to pause any serial communications with the device withoutresetting the clocking sequence. However, taking this signal LOW does not terminateany WRITE STATUS REGISTER, PROGRAM, or ERASE cycle that is currently in progress.To enter the hold condition, the device must be selected, with S# LOW. The hold condi-tion starts on the falling edge of the HOLD# signal, if this coincides with serial clock (C)being LOW. The hold condition ends on the rising edge of the HOLD# signal, if this co-incides with C being LOW. If the falling edge does not coincide with C being LOW, thehold condition starts after C next goes LOW. Similarly, if the rising edge does not coin-cide with C being LOW, the hold condition ends after C next goes LOW.During the hold condition, DQ1 is HIGH impedance while DQ0 and C are Don’t Care.Typically, the device remains selected with S# driven LOW for the duration of the holdcondition. This ensures that the state of the internal logic remains unchanged from themoment of entering the hold condition. If S# goes HIGH while the device is in the holdcondition, the internal logic of the device is reset. To restart communication with thedevice, it is necessary to drive HOLD# HIGH, and then to drive S# LOW. This preventsthe device from going back to the hold condition.Figure 6: Hold Condition ActivationHOLD#CHOLD condition (standard use)HOLD condition (nonstandard use)Configuration and Memory MapMemory Configuration and Block DiagramEach page of memory can be individually programmed; bits are programmed from 1 to 0. The device is sector or bulk-erasable, but not page-erasable; bits are erased from 0 to 1. The memory is configured as follows:•2, 097,152 bytes (8 bits each)•32 sectors (512Kb, 65KB each)•8,192 pages (256 bytes each)Figure 7: Block DiagramHOLD#S#W#CDQ0DQ1Micron M25P16 Serial Flash Embedded MemoryConfiguration and Memory MapMemory Map – 16Mb DensityTable 4: Sectors 31:0Micron M25P16 Serial Flash Embedded MemoryMemory Map – 16Mb DensityCommand Set OverviewAll commands, addresses, and data are shifted in and out of the device, most significantbit first.Serial data inputs DQ0 and DQ1 are sampled on the first rising edge of serial clock (C)after chip select (S#) is driven LOW. Then, the one-byte command code must be shiftedin to the device, most significant bit first, on DQ0 and DQ1, each bit being latched onthe rising edges of C.Every command sequence starts with a one-byte command code. Depending on thecommand, this command code might be followed by address or data bytes, by addressand data bytes, or by neither address or data bytes. For the following commands, theshifted-in command sequence is followed by a data-out sequence. S# can be drivenHIGH after any bit of the data-out sequence is being shifted out.•READ DATA BYTES (READ)•READ DATA BYTES at HIGHER SPEED•READ STATUS REGISTER•READ IDENTIFICATION•RELEASE from DEEP POWER-DOWNFor the following commands, S# must be driven HIGH exactly at a byte boundary. Thatis, after an exact multiple of eight clock pulses following S# being driven LOW, S# mustbe driven HIGH. Otherwise, the command is rejected and not executed.•PAGE PROGRAM•SECTOR ERASE•BULK ERASE•WRITE STATUS REGISTER•WRITE ENABLE•WRITE DISABLEAll attempts to access the memory array are ignored during a WRITE STATUS REGISTERcommand cycle, a PROGRAM command cycle, or an ERASE command cycle. In addi-tion, the internal cycle for each of these commands continues unaffected.Table 5: Command Set CodesWRITE ENABLEThe WRITE ENABLE command sets the write enable latch (WEL) bit.The WEL bit must be set before execution of every PROGRAM, ERASE, and WRITE com-mand.The WRITE ENABLE command is entered by driving chip select (S#) LOW, sending the command code, and then driving S# HIGH.Figure 8: WRITE ENABLE Command SequenceDon’t CareDQ[0]C DQ1S#WRITE DISABLEThe WRITE DISABLE command resets the write enable latch (WEL) bit.The WRITE DISABLE command is entered by driving chip select (S#) LOW, sending the command code, and then driving S# HIGH.The WEL bit is reset under the following conditions:•Power-up•Completion of any ERASE operation •Completion of any PROGRAM operation•Completion of any WRITE REGISTER operation •Completion of WRITE DISABLE operationFigure 9: WRITE DISABLE Command SequenceDon’t CareDQ[0]C DQ1S#READ IDENTIFICATIONThe READ IDENTIFICATION command reads the following device identification data:•Manufacturer identification (1 byte): This is assigned by JEDEC.•Device identification (2 bytes): This is assigned by device manufacturer; the first byte indicates memory type and the second byte indicates device memory capacity.•A Unique ID code (UID) (17 bytes,16 available upon customer request): The first byte contains length of data to follow; the remaining 16 bytes contain optional Customized Factory Data (CFD) content.Table 6: READ IDENTIFICATION Data Out SequenceNote:1.The CFD bytes are read-only and can be programmed with customer data upon demand.If customers do not make requests, the devices are shipped with all the CFD bytes pro-grammed to zero.A READ IDENTIFICATION command is not decoded while an ERASE or PROGRAM cy-cle is in progress and has no effect on a cycle in progress. The READ IDENTIFICATION command must not be issued while the device is in DEEP POWER-DOWN mode.The device is first selected by driving S# LOW. Then the 8-bit command code is shifted in and content is shifted out on DQ1 as follows: the 24-bit device identification that is stored in the memory, the 8-bit CFD length, followed by 16 bytes of CFD content. Each bit is shifted out during the falling edge of serial clock (C).The READ IDENTIFICATION command is terminated by driving S# HIGH at any time during data output. When S# is driven HIGH, the device is put in the STANDBY POWER mode and waits to be selected so that it can receive, decode, and execute commands.Figure 10: READ IDENTIFICATION Command SequenceidentificationidentificationDQ1MSBMSBCDQ0MSBDon’t CareREAD STATUS REGISTERThe READ STATUS REGISTER command allows the status register to be read. The status register may be read at any time, even while a PROGRAM, ERASE, or WRITE STATUS REGISTER cycle is in progress. When one of these cycles is in progress, it is recommen-ded to check the write in progress (WIP) bit before sending a new command to the de-vice. It is also possible to read the status register continuously.Figure 11: READ STATUS REGISTER Command SequenceDQ1CDQ0Don’t Care Figure 12: Status Register Formatb7SRWD 00BP2BP1BP0WEL WIP b0status register write protectblock protect bitswrite enable latch bitwrite in progress bitWIP BitThe write in progress (WIP) bit indicates whether the memory is busy with a WRITESTATUS REGISTER cycle, a PROGRAM cycle, or an ERASE cycle. When the WIP bit is setto 1, a cycle is in progress; when the WIP bit is set to 0, a cycle is not in progress.WEL BitThe write enable latch (WEL) bit indicates the status of the internal write enable latch.When the WEL bit is set to 1, the internal write enable latch is set; when the WEL bit isset to 0, the internal write enable latch is reset and no WRITE STATUS REGISTER, PRO-GRAM, or ERASE command is accepted.Block Protect BitsThe block protect bits are non-volatile. They define the size of the area to be softwareprotected against PROGRAM and ERASE commands. The block protect bits are writtenwith the WRITE STATUS REGISTER command.When one or more of the block protect bits is set to 1, the relevant memory area, as de-fined in the Protected Area Sizes table, becomes protected against PAGE PROGRAM andSECTOR ERASE commands. The block protect bits can be written provided that theHARDWARE PROTECTED mode has not been set. The BULK ERASE command is execu-ted only if all block protect bits are 0.SRWD BitThe status register write disable (SRWD) bit is operated in conjunction with the writeprotect (W#) signal. When the SRWD bit is set to 1 and W# is driven LOW, the device isput in the hardware protected mode. In the hardware protected mode, the non-volatilebits of the status register (SRWD, and the block protect bits) become read-only bits andthe WRITE STATUS REGISTER command is no longer accepted for execution. SRWD BitThe status register write disable (SRWD) bit is operated in conjunction with the writeprotect (W#/V PP) signal. When the SRWD bit is set to 1 and W#/V PP is driven LOW, thedevice is put in the hardware protected mode. In the hardware protected mode, thenon-volatile bits of the status register (SRWD, and the block protect bits) become read-only bits and the WRITE STATUS REGISTER command is no longer accepted for execu-tion.WRITE STATUS REGISTERThe WRITE STATUS REGISTER command allows new values to be written to the statusregister. Before the WRITE STATUS REGISTER command can be accepted, a WRITE EN-ABLE command must have been executed previously. After the WRITE ENABLE com-mand has been decoded and executed, the device sets the write enable latch (WEL) bit.The WRITE STATUS REGISTER command is entered by driving chip select (S#) LOW,followed by the command code and the data byte on serial data input (DQ0). TheWRITE STATUS REGISTER command has no effect on b6, b5, b4, b1, and b0 of the sta-tus register. The status register b6 b5, and b4 are always read as ‘0’. S# must be drivenHIGH after the eighth bit of the data byte has been latched in. If not, the WRITE STATUSREGISTER command is not executed.Figure 13: WRITE STATUS REGISTER Command SequenceCDQ0As soon as S# is driven HIGH, the self-timed WRITE STATUS REGISTER cycle is initi-ated; its duration is t W. While the WRITE STATUS REGISTER cycle is in progress, the sta-tus register may still be read to check the value of the write in progress (WIP) bit. TheWIP bit is 1 during the self-timed WRITE STATUS REGISTER cycle, and is 0 when thecycle is completed. Also, when the cycle is completed, the WEL bit is reset.The WRITE STATUS REGISTER command allows the user to change the values of theblock protect bits (BP2, BP1, BP0). Setting these bit values defines the size of the areathat is to be treated as read-only, as defined in the Protected Area Sizes table.The WRITE STATUS REGISTER command also allows the user to set and reset the statusregister write disable (SRWD) bit in accordance with the write protect (W#/V PP) signal.The SRWD bit and the W#/V PP signal allow the device to be put in the HARDWARE PRO-TECED (HPM) mode. The WRITE STATUS REGISTER command is not executed oncethe HPM is entered. The options for enabling the status register protection modes aresummarized here.Table 7: Status Register Protection ModesNotes: 1.Software protection: status register is writable (SRWD, BP2, BP1, and BP0 bit values canbe changed) if the WRITE ENABLE command has set the WEL bit.2.PAGE PROGRAM, SECTOR ERASE, AND BULK ERASE commands are not accepted.3.PAGE PROGRAM and SECTOR ERASE commands can be accepted.4.Hardware protection: status register is not writable (SRWD, BP2, BP1, and BP0 bit valuescannot be changed).5.PAGE PROGRAM, SECTOR ERASE, AND BULK ERASE commands are not accepted.When the SRWD bit of the status register is 0 (its initial delivery state), it is possible towrite to the status register provided that the WEL bit has been set previously by a WRITEENABLE command, regardless of whether the W#/V PP signal is driven HIGH or LOW.When the status register SRWD bit is set to 1, two cases need to be considered depend-ing on the state of the W#/V PP signal:•If the W#/V PP signal is driven HIGH, it is possible to write to the status register provi-ded that the WEL bit has been set previously by a WRITE ENABLE command.•If the W#/V PP signal is driven LOW, it is not possible to write to the status register evenif the WEL bit has been set previously by a WRITE ENABLE command. Therefore, at-tempts to write to the status register are rejected, and are not accepted for execution.The result is that all the data bytes in the memory area that have been put in SPM bythe status register block protect bits (BP2, BP1, BP0) are also hardware protectedagainst data modification.Regardless of the order of the two events, the HPM can be entered in either of the fol-lowing ways:•Setting the status register SRWD bit after driving the W#/V PP signal LOW•Driving the W#/V PP signal LOW after setting the status register SRWD bit.The only way to exit the HPM is to pull the W#/V PP signal HIGH. If the W#/V PP signal ispermanently tied HIGH, the HPM can never be activated. In this case, only the SPM isavailable, using the status register block protect bits (BP2, BP1, BP0).READ DATA BYTESThe device is first selected by driving chip select (S#) LOW. The command code for READ DATA BYTES is followed by a 3-byte address (A23-A0), each bit being latched-in during the rising edge of serial clock (C). Then the memory contents at that address is shifted out on serial data output (DQ1), each bit being shifted out at a maximum fre-quency f R during the falling edge of C.The first byte addressed can be at any location. The address is automatically incremen-ted to the next higher address after each byte of data is shifted out. Therefore, the entire memory can be read with a single READ DATA BYTES command. When the highest ad-dress is reached, the address counter rolls over to 000000h, allowing the read sequence to be continued indefinitely.The READ DATA BYTES command is terminated by driving S# HIGH. S# can be driven HIGH at any time during data output. Any READ DATA BYTES command issued while an ERASE, PROGRAM, or WRITE cycle is in progress is rejected without any effect on the cycle that is in progress.Figure 14: READ DATA BYTES Command SequenceDon’t CareDQ[0]CDQ1Note: 1.Cx = 7 + (A[MAX] + 1).READ DATA BYTES at HIGHER SPEEDThe device is first selected by driving chip select (S#) LOW. The command code for the READ DATA BYTES at HIGHER SPEED command is followed by a 3-byte address (A23-A0) and a dummy byte, each bit being latched-in during the rising edge of serial clock(C). Then the memory contents at that address are shifted out on serial data output (DQ1) at a maximum frequency f C , during the falling edge of C.The first byte addressed can be at any location. The address is automatically incremen-ted to the next higher address after each byte of data is shifted out. Therefore, the entire memory can be read with a single READ DATA BYTES at HIGHER SPEED command.When the highest address is reached, the address counter rolls over to 000000h, allow-ing the read sequence to be continued indefinitely.The READ DATA BYTES at HIGHER SPEED command is terminated by driving S# HIGH.S# can be driven HIGH at any time during data output. Any READ DATA BYTES at HIGHER SPEED command issued while an ERASE, PROGRAM, or WRITE cycle is in progress is rejected without any effect on the cycle that is in progress.Figure 15: READ DATA BYTES at HIGHER SPEED Command SequenceCDQ0DQ1Don’t Care Note: 1.Cx = 7 + (A[MAX] + 1).。

M25PE20-VMN6TP中文资料