KS88C6116中文资料

国泰怡安产品优势简介

G6系统特性

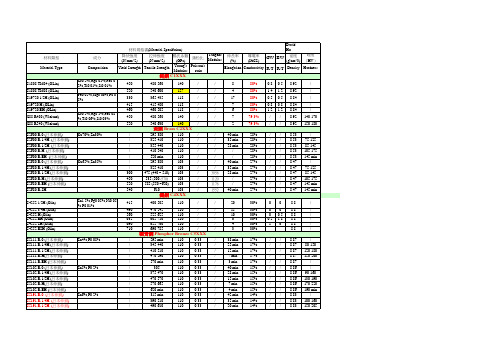

气体灭火控制器比较

公司 型号 每区线数 独立工作

海湾消防 海湾消防

QKP06 QKP-04/02 FS5090 JB-QB-QM200/4 EI-6000QT GK652 GK652B

11 4+4 14 18 14+2 7+4 4+4

与控制器配合 可以

壁挂/柜式 壁挂(新国标)

利达华信

3

G6系统特性

G6产品优势

• 但是由于二极管存在寄生电容,信号输出后会引 起畸变;线路好的情况可能无影响,但线路长时 或线路状况不好时,信号畸变的厉害,影响了总 线的稳定性;所以国外厂商都不采用这种方式, 抗干扰性、稳定性都不如有极性的;

回路线1

1

D? 4

2

输入波形

回路线2

3

输出波形

2009年4月20日

G6系统特性

国泰怡安产品优势简介

2009年4月20日

G6系统特性

G6系列控制器 型号 GK601H GK603 GK603G GK614 GK652

安装方式

最大容量 10200点 510 510 119+8 127

RS485

252个设备 126个设备 126个设备

备注

含6路联动 含6路联动 含1路联动 最多含4区气 体灭火控制

G6系统特性

探测器特性

• 采用美国Microchip公司的MCU,功能强、 可靠性高; • 内嵌智能算法、自动比对燃烧曲线,可探 测4种火产生的烟雾; • 对环境因素自动补偿; • 360度可见灯; • 亮灯巡检和灭灯巡检可设置;

2009年4月20日

G6系统特性

控制模块特性

• 真正的两总线结构,与控制器只需两线连接; • 可监视模块至受控设备间连线的断线、短路;及时发现设 备问题; • 采用美国Microchip公司的MCU,功能强、可靠性高;

SICK色标传感器型号

SICK色标传感器KT6W-P5116 KT6W-P6116 KT6W-N5116 KT6W-N6116产品的特点:1.KT6W 高性价比色标传感器具有其独特的性能优势,当遇到被检测物体的色标和背景色特别难辨认的情况采用具有三色LED 作为光源的KT6W系列产品。

KT6W针对不同亮度的被检物体,可以自动进行光源切换。

2.坚固的外壳可以延长使用寿命,并且提高检测质量。

针对被检物体的底色和背景色灰度的差异,KT6W可通过两步自学习的方式自动设定检测灰度门槛值,整个过程既简便又快捷。

4.除了提供两个安装孔位外,KT6W还提供了两个T型安装槽,这样一来,KT6W的安装方式既简便易行安全可NT8-01412 KTL5W-P23KT5G-2N1161 KT5G-2P1161NT8-02412 KT5G-2P1113S 23KT10W-2P2115 NT6-03018NT6-03012 KT10W-P1115S0 3KT5G-2P1112 NT6-04012NT6-03018 KT5W-2N1113S 24KT5W-2P1113 NT6-04022NT6-03022 KTL5W-2N13KT5W-2N1113 NT6-04011NT6-04012 KT10W-P1115F1 1KT10W-N2115 NT6-03023NT6-04018 KT5G-2P1116 KT5G-2P1111S 13NT6-03014NT6-04022 KTL5G-2P14KT5W-2P1213 NT6-03025NT6-13012 KT5W-2P2116 KT5W-2N1213 NT6-03062NT6-13022 KT5G-2N1251 KT5G-2N1112 NT6-13023 NT6-03018 KT5W-2N1316 KT5G-2P1212 NT6-03010S0 6NT6-04012 KT5W-2N1116S 27KT5G-2N1212 NT8-06412 NT6-04022 KT5G-2P1151S 28KT5G-2N1351 NT6-03042 NT6-04011 KT3W-P1126 KT5G-2P1311S 14NT6-03082NT6-03023 KT5G-2P1251S 29KTL5G-2P51NT6-03024 NT6-03014 KT3L-N3216 KTL5G-2N51NT6-03015 NT6-03025 KT3L-P3216 KT5G-2P1114 NT6-04018 NT6-03062 KT3W-N1116 KT5G-2N1114 NT6-03052 NT6-13023 KT5G-2P1111 KT5G-2P2151 NT6-13082 NT6-03010S0 6NT6-03022 KT5W-2P1123 NT8-02912KT5W-2N1116 KT5G-2P1214 NT6-04038KT5W-2N1116D NT6-04012 KT5G-2N1214 NTL6-B11KT5W-2P1116D KT10W-2P1115 KT5G-2P2112 NTL6-B12KT5W-2P1126D KT10W-2N1115 KT5G-2P1122 NT6-04008S1 1KT5W-2P1216D KT8W-P111C KT5G-2N1122 NTL6-E12KT5W-2P2116D KT8W-N111C KT5G-2N3151 NT6-13024P1216D KT5G-2P1411 NT6-14900S1 2KT5W-2N1216D KTH5W-N1216D KT2R-2B3711 NTL6-B18KT5W-2N1316D KT5W-2P1116 KT5G-2N1411 NT6-43302S2 0KT5W-2N2116D KT5W-2N1116 KT5W-2N2113 NT8-01412KT5W-2P1316D KT5W-2P1113 KT5W-2P2113 NT6-08024S1 4KT3W-N1115 KT5W-2N1113 KT5W-2P1116 NT6-040252P1213 KT5W-2N1116 NT6-N112KT3G-N1116 KT5W-2P1113S 24KT5G-2P2351 NT6-KT3G-P1116 KT5G-2P1111 KT5G-2N2351 NT6-14920S1 7KT3W-N1116 KT5G-2P1121 KT5G-2N2112 NT6-03212KT3W-P1116 KT5G-2P1211 KT5G-2N1111S 16NT6-03215KT3W-P1126 KT5G-2P1221 KT5G-2P2114 NT6-33322S1 82P1311 KT5W-2P1113S 17NT6-29042KT3L-P3216 KT5G-2P1321 KT5G-2N1111S 18NTL6-B10S01 NT6-03022 KT5G-2N1111 KT5G-2P1323S 19NTL6-P12NT6-13012 KT5G-2N1211 KT5G-2P1414 KT5L-P3611 NT6-13022 KT5G-2N1311 KT5G-2P1312 NT6-03218 NT6-07012 KT5G-2N111S1 6KT5W-2P1216 NT6-33342S2NT6-07022 KT5G-2P1112 KT5W-2P1126 NT6-03038 NT6-08022 KT5G-2N1112 KT5W-2P1323 NT6-07018 NT6-29022 KT5G-2P1212 KT5W-2P1123S 20NT6-29019 NT8-01412 KT5G-2N1212 KT5G-2P1223S 21NT6-03215E0 NT8-01422 KT5G-2P1114 KT5W-2P1316 NT8-00000S0 1NT8-01512 KT5G-2N1114 KT5G-2P1314 KT5L-N3611NT8-02412 KT5W-2P1116 KT5W-2P2216 KT5L-P3611 NT8-02422 KT5W-2N1116 KT5W-2N1216 KT5L-P3611E0 7NT8-02512 KT5L-P3611 KTL5G-2P24NT6-14920S2 9NT8-03612 KT5L-N3611 KT3W-N1116 KT5L-P3611S0 1NT8-04612 KTL5G2-P11KT3W-P1116 NT6-14920E0 2NT8-04712 KTL5G2-N11KT5G-2N1116 NT6-33342S3 0NT8-06932 KT3W-P1116 KT10W-N1115S0 2KT2G-2B3711 NT8-06432 KT3W-N1116 KT3G-N1116 KT5G-2N1111 NT8-16412 KT3G-P1116 KT3G-P1116 KT5G-2N1121 NT8-17412 KT3G-N1116 KT5G-2P1151S 22KT5G-2N1211 NT8-18432 KT2R-2B3711 KT5G-2P1251 KT5G-2N1311 NT8-19432 KT2G-2B3711 KT5G-2P1351 KT5G-2N2111NT8-21412 KT2G-2B3721 KTL5G-2P11KT5G-2N2211 NT8-22412 KT1M-P1 KTL5G-2N11KT5G-2N2311 NT8-22512 KT1M-P2 KT5G-2N1151 KT5G-2P1111 KT5G-2P2111 KT5G-2P2221 KT10W-2P1115 KT5G-2P1121 KT5G-2P2121 KT5G-2P2311 KT10W-2N1115 KT5G-2P1211 KT5G-2P2211 KT5G-2P2321 KT5G-2P1151 KT5G-2P1221NT8-02414 KT5G-2P1321 KT5G-2P1311。

CW61160×6000mm-18T技术说明

CW61160×6000mm重型卧式车床技术说明天水星火机床厂是生产各种大型卧式车床和大型数控卧式车床的骨干企业,经过30多年的发展壮大,在产品方面已形成了13个系列,110个品种,近400个规格的产品构成。

星火机床广泛应用于机械制造、航天、军工、造纸、造船、水泥机械、冶金机械、汽车制造等行业,畅销全国各地并已出口世界五大洲的44个国家和地区,整个产品具有结构可靠,技术指标先进,质量过硬等特点,在国内机床制造业中享有良好的声誉,企业已通过了ISO9001质量体系认证和欧洲CE安全体系认证。

在重型车床,重型数控车床方面引进了世界著名重型车床生产基地TACCHI和SAFOP的先进设计制造技术,产品的各项技术指标及性能达到了国际先进水平。

一、机床的总体介绍CW61160重型卧式车床通过总结设计制造经验和引进吸收世界著名重型车床生产基地TACCHI和SAFOP的先进技术后,成功开发的重型卧式车床并已形成了Φ1250~Φ2200的车床系列,承重18000~35000kg,和国内同类机床相比,具有很大的优越性。

本机床可承担各种车削工作,它能够车削各种零件的外圆、内孔、端面等;上刀架单独机动可车削短的锥度(锥体母线长L≤300毫米),上刀架与纵向进给配合可机动车削长的锥度;此外,还可满足钻孔、镗孔、套料等工艺要求,同时也适用于硬质合金刀具进行强力车削,加工各种黑色金属和有色金属。

此外,本机床还具有功率大、转速高、噪音小、刚性强、精度高和精度保持性好等内在特点,又具有造型美观大方、布局紧凑合理等外部特点,还具有手柄集中、标牌形象直观、操作灵活方便、安全可靠、宜人性好等优点,另外,根据用户的要求还可提供托辊装置、车锥装置等特供附件。

二、主要技术参数床身上最大回转直径Φ1600 mm 最大工件长度6000 mm 刀架上最大回转直径Φ1200 mm 顶尖间工件最大重量18000 kg 床身上部导轨宽度1100 mm 主轴端部ISO(GB) A2-20 主轴通孔直径100 mm 主轴前端锥孔1:7;Φ140 mm 主轴前轴承直径Φ240 mm 主轴转速三档(无级)1~125 r/min 纵向进给量97种0.064~12 mm 横向进给量97种0.032~6 mm 上刀架进给量97种0.016~3 mm 米制螺纹45种1~120 mm 英制螺纹42种30~1/4 t.p.i.模数螺纹46种0.5~60 mm 径节螺纹48种60~0.5 D.P 刀架最大横向行程1300 mm 中刀架最大行程400 mm 上刀架最大行程200 mm 刀架快速移动纵向3740 mm/min横向1870 mm/min上刀架935 mm/min 刀架回转角度±90°刀具截面尺寸(高×宽)45×45 mm 尾座套筒直径Φ240 mm 尾座套筒锥孔米制NO.80 尾座套筒最大行程300 mm 主电机功率49 kw 快速电机功率 1.5 kw 油泵电机功率0.55 kw 冷却电机功率0.15 kw 三、机床各主要部件介绍⑴床身床身采用分体拼接结构,树脂砂造型,导轨采用中频淬火磨削工艺,使得机床具有良好的耐磨性及精度保持性。

Hoffman Enclosures Inc. 电子变压器操作适配器(适用于Eaton Cutle

89115496

© 2018 Hoffman Enclosures Inc.

PH 763 422 2211 • /HOFFMAN

-3-

For Floor-Mounted, Two-Door Enclosures with Disconnect on Right Flange

0DVWHU 'RRU

)RURQHWKURXJKVL[GRRUIUHHVWDQGLQJHQFORVXUHV ZLWKWKHGLVFRQQHFWWKHWKHULJKWIODQJH 0DVWHU 'RRU

)RUIORRUPRXQWHGHQFORVXUHVZLWK WKHGLVFRQQHFWRQWKHFHQWHUSRVW

Step 5 Attach the bottom of the slide arm (item 4) to the offset arm of the lock release mechanism. Use two flat washers (item 8), two lockwashers (item 9), and two hex nuts (item 10). Do not tighten until parts are adjusted (see step 6B)

Item No. Description

Part No.

Qty.

1

MOUNTING PLATE, C-H C361 AND C371

26385001

1

2

GASKET, PLATE

89109613

1

3

SCREW, 1/4-20X1/2 PAN HEAD

99401031

4

4

陕柴PC2-6L备件图册_部分1

船舶主机PC2-6/2L柴油机备件图册陕西柴油机重工有限公司号名称主轴承部套号001装配图02.001.9002.00(014606/02)标识号名称及规格图号零件号(编码号)数量备注6缸8缸1主轴承螺栓214912/102.001.0012.0014182定位销423928/102.001.0124.00793轴承体110903/6110903/6794横向螺钉423154/202.001.0119.0014185螺母31752902.001.0329.0014186上半轴瓦26512402.001.0000.03797下半轴瓦26512302.001.0000.02791/1662/166号名称连杆部套号003装配图02.003.9082.45(018584/002 )标识号名称及规格图号零件号(编码号)数量备注6缸8缸1连杆杆身018582/005018582/005682连杆轴承盖156387/004156387/004683连杆大端下轴瓦112386/00202.003.0551.95684连杆大端上轴瓦104843/00602.003.0273.97685连杆螺钉208393/00452.003.0001.0024327连杆小端衬套112357/00052.003.0104.00688弹性销A24×35NFENISO13337/00000.235.2403.5268Q/SC346-1980 A24×353/1664/166号名称活塞总成部套号005装配图27.014.0409.97(026599/001)标识号名称及规格图号零件号(编码号)数量备注6缸8缸1活塞025662/004,266642/00052.005.9013.00681-1O型圈327×5NFL17160/00000.653.3275.6868Q/SC362-79 327×51-2定位销429660/00102.005.0006.00681-3活塞顶031799/0002.005.0567.85681-4活塞裙0131798/0052.005.0111.00681-5螺柱H22×150363495/00052.005.0103.0024321-6螺母458369/00052.005.0105.0024321-7衬套458368/00052.005.0104.0024326挡圈Ⅰ175×4NFE22165/00000.201.0101.751216Q/SC343-79 17510顶环316868/00102.005.0134.006811压力环312048/00502.005.0133.006812压力环309625/00502.005.0066.45121613刮油环(带弹簧)261625/00102.005.9038.7712165/1666/166号名称活塞销总成部套号005装配图157955/000标识号名称及规格图号零件号(编码号)数量备注6缸8缸2活塞销110802/00102.005.0027.57683管子216509/00002.005.0116.00684密封圈 AN24AN6227/00000.652.2435.631216Q/SC361-79 AN245弹性挡圈NFE22165/00000.201.0100.421216GB/T893.1-86 427/1668/166号名称气缸套总成部套号008装配图014621/06标识号名称及规格图号零件号(编码号)数量备注6缸8缸1缸套260117/0202.008.9000.03682水套109424/0402.008.0055.00683贯穿螺栓21491902.008.0039.0048644螺母36056552.008.0002.0048645保护螺母49073452.008.0113.004864GB/T5783-2000 M8×507"O"型圈 Ø6 Di=505NSE6.53100653.5056.681216Q/SC362-79 6×5058密封圈 8×444NSE6.53100.653.4448.711824Q/SC362-79 8×4449销子G5 Ø12×30NFE27.49400.225.1203.0568GB/T119.2-2000 12m6×3010密封胶PRC1005L99.361.1005.01————铁锚60911密封胶98.351.0330.02————乐泰2431207级密封剂99.360.0000.07————铁锚60913垫圈431269/0104.008.0054.006814缸盖垫片490343/152.008.0101.006815弹性销10×20NFE2748900.235.1002.0168GB/T879.1-2000 10 ×209/16610/166标识号名称及规格图号零件号(编码号)数量备注6缸8缸1缸盖本体025765/002,025766/001,025767/000,025768/001,025769/00002.010.5052.32682进气阀座(嵌入)319869/00652.010.0110.0012163盖板42804302.010.0202.00684垫片δ=142816800.686.0762.10685盖板419640/00102.010.0112.0024326垫片δ=1400153/00300.689.0762.1024327盖板30817602.010.0146.00688垫片δ=141738002.010.0076.61689盖板214407/00102.010.0027.006810垫片316540/00002.010.0003.006811法兰316508/00002.010.0008.006812垫片445710/00002.010.0010.006813闷塞 M16458065/00052.010.0118.00243214螺塞 M30×2421299/00403.010.0120.006815螺塞M60×2421301/00303.010.0124.00121616垫片9×14×1NFR93920/00000.651.0914.402432Q/SC134-79 917垫片20×26×1.5NFR93920/00000.651.2026.4068Q/SC135-79 20×26×1.5 18垫片45×55×2NFR93920/00000.651.4555.401216Q/SC135-79 45×55×2 19密封胶NSE1.3599.351.3200.00————乐泰573或铁锚350标识号名称及规格图号零件号(编码号)数量备注6缸8缸21双头螺柱M16×6000.082.1606.083040GB/T897-88 M16×60 22盖板360000/00102.010.0154.00121623垫片450135/00002.010.0070.00121624螺拴M16×3000.002.1603.08270360GB/T5786-2000 M16×30 25螺拴M12×4500.001.0204.582432GB/T5786-2000 M12×45 27双头螺柱(排气阀)319848/00002.010.0155.00364833定位销450428/00002.010.0150.00182435垫片447025/00002.010.0023.006836专用螺母448913/00002.010.0066.00121637双头螺柱448911/00002.010.0067.00121639双头螺柱45288102.010.0081.00121640专用螺母452882/00002.010.0082.00121641垫圈456647/00002.010.0151.00121642双头螺柱456646/00152.010.0115.00121643螺塞 M16×1.5DIN910/00098.B13.1000.0468Q/SC381-84 M16×1.5 45垫片16×22×1NFE21351/00000.651.1622.4068Q/SC135-79 16×22×1 46螺母425039/00202.010.0229.00364847垫圈491470/00052.010.0117.00364848弹性垫圈16NFE2762400.167.1602.30282376GB/T859-87 1613/166号名称进气阀总成部套号015装配图025400标识号名称及规格图号零件号(编码号)数量备注6缸8缸1进气阀111738/0352.015.0110.0012162下衬套360333/0152.015.0107.0012163环443347/0102.015.0151.0036484密封环441594/0102.015.0153.0036485上衬套315866/0102.015.0152.0012166内弹簧408770/0202.015.0022.0012167外弹簧408771/0202.015.0023.0012168弹簧座44922602.015.0168.0012169锥块424637/0102.015.0039.00243210衬套44922502.015.0170.00121614/16615/166号名称排气阀总成部套号015装配图02.015.0406.03 02.015.0406.04 (017669/01)标识号名称及规格图号零件号(编码号)数量备注6缸8缸1右侧排气阀壳016264/0602.015.0074.00682左侧排气阀壳016265/0602.015.0075.00683排气阀下衬套443346/0202.015.0155.0012164密封环441594/0102.015.0153.0036485环443347/0102.015.0151.0036486排气阀上衬套319969/0102.015.0006.7612167排气阀108522/0202.415.8129.0012168内弹簧408770/0202.015.0022.0012169外弹簧408771/0202.015.0023.00121610转阀机构99.525.5500.20121611锥块424637/0102.015.0039.00243212锥块套(排气阀)424636/0202.015.0036.00121613排气阀弹簧座456672/0252.015.0109.00121614连接管425041/0102.015.0219.00243218密封圈AN18NSE6.500.652.1835.684864Q/SC361-79 AN1819密封圈115×5NSE6.53100.653.1155.681216Q/SC362-79 5×11516/16617/166号名称喷油器部套号016装配图02.016.9001.00 (110701/1)标识号名称及规格图号零件号(编码号)数量备注6缸8缸1喷油器体110722/102.016.0051.00682喷嘴21636602.016.8001.00683针阀424777/402.016.0009.00684紧帽31684202.016.0024.00685衬圈423462/102.016.0006.00688弹簧424778/302.016.0030.006810接头424779/202.016.0011.00121613销子44177702.416.0077.00121614螺母400202/101.016.00036815双耳止动垫圈400203/101.016.00046817密封圈AN11NSE6500.652.11.26.633648Q/SC361-79 AN1118密封圈MS29513/228NSE6.53100.655.0563.6868Q/SC362-79 MS29513/22819密封圈AN34NSE6.500.652.34.53.6868Q/SC361-79 AN3420密封圈AN36NSE6.500.652.36.53.6868Q/SC361-79 AN3618/16619/166号名称气缸盖安全阀部套号017装配图110723/00标识号名称及规格图号零件号(编码号)数量备注6缸8缸1阀体207081/302.017.0110.00682塞座308033/202.017.0122.00683阀杆组件308034/202.417.8117.00684弹簧31880002.017.0020.00685推力套41918602.017.0118.00686调整垫片4531904531906810螺塞M30×2NSE1.161400.017.0026811密封圈AN28NSE6.500.652.28.53.6368Q/SC361-79 AN2812密封圈MS29513/145NSE6.53100.655.145.2.6368Q/SC362-79 MS29513/14513垫片NFR93.92000.651.30.38.4068Q/SC135-84 30×38×1.5号名称起动阀部套号018装配图110739/2标识号名称及规格图号零件号(编码号)数量备注6缸8缸1阀体21526902.018.0041.00682阀杆360469/102.018.9004.00683活塞43094202.018.0153.00684弹簧41914102.018.0054.00685压盖30801402.018.0055.00687密封圈AN29NSE6.500.652.2953.6368Q/SC361-79 AN298密封圈MS29513/145NSE6.53100.655.0642.631216Q/SC362-79 MS29513/1459密封圈jointFrancais 00.666.0391.6968Q/SC362-79 JF4n°28A 11开口销4×36NFE27.48700.210.040.36368GB/T91-88 4×3612止动垫圈12NSE1.3100.140.120.1101216GB/T854-86 12号名称示功阀部套号019装配图02.419.9011.00 (014675)标识号名称及规格图号零件号(编码号)数量备注6缸8缸2螺杆400295/503.019.0013.00683导向螺母400294/401.019.0019.00684阀头400296/201.019.0014.00686垫圈417289/303.019.0014.006813塞轴43845403.019.0001.006814连接螺母411529/303.019.0037.006817垫片27×35×1.5NFE2731100.651.2735.4068Q/SC135-84 27×35×1.5号名称气阀传动机构部套号020装配图(016370)标识号名称及规格图号零件号(编码号)数量备注6缸8缸1摇臂座装配图107465/102.420.8445.00681-2衬套 431102/102.020.0021.0012164衬套 411585/302.020.0069.00686长螺柱260742/0052.020.0110.0012167螺柱260741/0052.020.0109.0012168隔套44694302.020.0143.00121610调节螺钉与凹座总成446991/102.020.0169.002432号名称气阀传动机构部套号020装配图(014598)标识号名称及规格图号零件号(编码号)数量备注6缸8缸304滚轮导筒21489502.020.0110.0012165滚轮400240/401.020.000512166浮动滚轮衬套400322/501.020.000612167滚轮销400323/801.020.00071216310弹簧ø4418983/102.020.0310*******"O"型圈AN38NSE6.500.652.38.53.771216Q/SC361-79 AN38340螺塞M1041806302.032.0061.0068341垫片8.5×4.5×1NSE6.51100.661.04.080168Q/SC363-79 8.5×4.5×13146螺塞M14×1.541934502.020.0346.0068Q/SC362-79 8.5×4.5×2347密封圈1.9×6.4NSE6.5311216Q/SC362-79 1.9×6.4号名称气门罩壳部套号022装配图08392/4标识号名称及规格图号零件号(编码号)数量备注6缸8缸3垫片20859502.022.0003686定位螺钉42428102.022.000618247垫圈42428202.022.0007182415密封圈6.5×486400.022.0368105罩壳装配图107609/203.422.0003.0068105-3夹紧轴43868503.422.8001.001216105-4弹簧ø242626704.022.0114.001216105-5垫圈 δ=142068903.022.0125.001216105-6密封圈AN9NSE6.500.652.09.26.631216Q/SC361-79 AN9105-8密封圈AN79NSE6.500.652.80.70.6368Q/SC361-79 AN79324夹箍 1A SERFLEX 99.670.4038.011216328帽42225902.022.03281216330密封圈MS29513/141NSE6.53100.655.058.2.601216Q/SC362-79 MS29513/141332密封圈AN34NSE6.5200.652.34.53.602432Q/SC361-79 AN3430/16631/166号名称凸轮(顺时针旋转机)部套号024装配图016421/00标识号名称及规格图号零件号(编码号)数量备注6缸8缸1进气凸轮016395016395682排气凸轮016396016396683两半式燃油凸轮11016902.424.0069.00683-1螺钉457737457737243232/166。

2008年度第五批达国Ⅳ排放标准的重型柴油车

附件3:2008年度第五批达国Ⅳ排放标准的重型柴油车(下文出现的“*”代表随机变动实号,“(*)”代表随机变动实号或虚号)1、丹东黄海汽车有限责任公司DD6129K80 客车发动机:YC6L310-40(广西玉柴机器股份有限公司)喷油泵型号:G6000-1111100(DELPHI)喷油器型号:KBEL-P051(BOSCH)增压器型号:HX40W(无锡康明斯涡轮增压技术有限公司)SCR排气处理器型号:SC000000(上海华克排气系统有限公司)SCR系统尿素计量泵型号:UDS G2.5 AA 7.5(GRUNDFOS)2、江苏亚星客车集团扬州亚星客车股份有限公司JS6130SHJ 双层城市客车发动机:YC6L260-40(广西玉柴机器股份有限公司)喷油泵型号:CRCPN2(BOSCH)喷油器型号:CRIN-A38(BOSCH)增压器型号:HX40W(无锡康明斯涡轮增压技术有限公司)SCR排气处理器型号:SC000000(上海华克排气系统有限公司)SCR系统尿素计量泵型号:SM-A38 (BOSCH)3、厦门金龙旅行车有限公司XML6115J18C 城市客车发动机:YC6L240-40(广西玉柴机器股份有限公司)喷油泵型号:G6000-1111100(DELPHI)喷油器型号:KBEL-P051(博世汽车柴油系统股份有限公司)增压器型号:HX40W(无锡康明斯增压技术有限公司)SCR排气处理器型号:SC000000(上海华克排气系统有限公司)SCR系统尿素计量泵型号:UDS G2.5 AA 7.5(GRUNDFOS)XML6125J18C 城市客车发动机:YC6L280-40(广西玉柴机器股份有限公司)喷油泵型号:G6000-1111100(DELPHI)喷油器型号:KBEL-P051(BOSCH)增压器型号:HX40W(无锡霍尔塞特工程有限公司)SCR排气处理器型号:SC000000(上海华克排气系统有限公司)SCR系统尿素计量泵型号:SM-A38 (BOSCH)4、扬州亚星商用车有限公司YBL6123HE4 客车发动机:YC6L310-40(广西玉柴机器股份有限公司)喷油泵型号:CRCPN2(BOSCH)喷油器型号:CRIN-A38(BOSCH)增压器型号:HX40W(无锡康明斯涡轮增压技术有限公司)SCR排气处理器型号:SC000000(上海华克排气系统有限公司) SCR系统尿素计量泵型号:UDS G2.5 AA 7.5(GRUNDFOS)或喷油泵型号:G6000-1111100(DELPHI)喷油器型号:KBEL-P051(BOSCH)增压器型号:HX40W(无锡康明斯涡轮增压技术有限公司)SCR排气处理器型号:SC000000(上海华克排气系统有限公司) SCR系统尿素计量泵型号:UDS G2.5 AA 7.5(GRUNDFOS)5、郑州宇通客车股份有限公司ZK6127HE 客车发动机:YC6L310-40(广西玉柴机器股份有限公司)喷油泵型号:CRCPN2(BOSCH)喷油器型号:CRIN-A38(BOSCH)增压器型号:HX40W(无锡康明斯涡轮增压技术有限公司)SCR排气处理器型号:SC000000(上海华克排气系统有限公司) SCR系统尿素计量泵型号:UDS G2.5 AA 7.5(GRUNDFOS)。

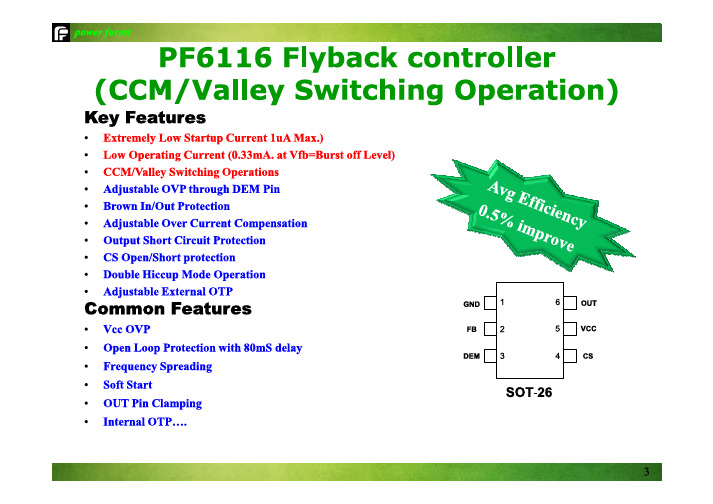

PF6116 资料

-பைடு நூலகம்-27

I D C J > B

$- "/ + ( , ! -")$ ! ") "# "/ 21 3 "/ 41 )/ 01 %& & 5 ")$. 01 2

8 8 9 : ; < = > ? @A D H ? : ; < = 9 ? @A 8 ? B

c( )( d # e 0f3 - !"# $%& & ' ( )' *

& !" #$

( & !" #$

'

0 1 2 3 4 6 1 4 3 7 8

9

9

9

9

9

9

9

9

9

! ! " # " $%# &

9 9 9 o v tl u

l ol u j v k l

g hi j k l ml n oqr st j u k j v wxv k k l y j z { | v }u j ~xxz ~ g qr sw l k u j y xv k k l y j z m} u j ~ v k j r ql l n

( )

0 1 2 3 4 6 1 4 3 7 8

K L M NPQRST N T QRU V W XYV Z[V W \ ]L ^Q_Q` a S

8 8 9 : ; < = > ? @A D H ? : ; < = 9 ? @A 8 ? B

9

9

常用连接器金属材料库2008

14% 14% 13% 13% 13% 13% 13% 30% 30% 30% 30% 13% 13% 13% 13% 13% 13% 13% 13% 13% 13% 13% 10% 10% 10% 10% 10% 45% 45% 45% 40% 40% 35% 43% 43% 43% 50% 50% 45% 50% 50% 47% 40% 40% 6%

Sn8%,P0.2%

Sn2%,Ni0.2%,P0.1%

588 660 / 570 675 710 667 / / / / 635 660 720 760 790 830 / 688 760 / / / / 813 940 997

635 min 710-760 470-610 647.5(590-705) 735(685-785) 764(735-835) 724 410-510 490-590 540-635 570-645 620-725 670-770 720-830 745-860 790-910 830-965 635(590-705) 729(685-785) 790(735-835) 853(785-885) 918(835-1000) 708(650-750) 805(750-850) 866(850-950) 990(950-1050) 1039(1000-1200) 725 745 815 620-760 655-830 690-860 620-760 650-780 690-800 710-830 770-900 840-970 800 850 600-720 750-850 880 375

GW BW

製表 David Ho 硬度 密度 (g/cm^3) (HV)

R/T R/T Density Hardness

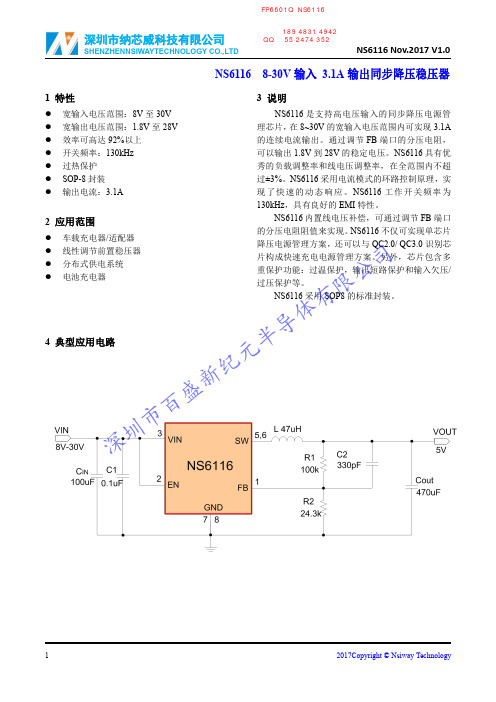

深圳市纳芯威科技有限公司NS6116输入输出同步降压稳压器说明书

NS61168-30V 输入3.1A 输出同步降压稳压器1特性●宽输入电压范围:8V 至30V ●宽输出电压范围:1.8V 至28V ●效率可高达92%以上●开关频率:130kHz ●过热保护●SOP-8封装●输出电流:3.1A2应用范围●车载充电器/适配器●线性调节前置稳压器●分布式供电系统●电池充电器3说明NS6116是支持高电压输入的同步降压电源管理芯片,在8~30V 的宽输入电压范围内可实现3.1A 的连续电流输出。

通过调节FB 端口的分压电阻,可以输出1.8V 到28V 的稳定电压。

NS6116具有优秀的负载调整率和线电压调整率,在全范围内不超过±3%。

NS6116采用电流模式的环路控制原理,实现了快速的动态响应。

NS6116工作开关频率为130kHz ,具有良好的EMI 特性。

NS6116内置线电压补偿,可通过调节FB 端口的分压电阻阻值来实现。

NS6116不仅可实现单芯片降压电源管理方案,还可以与QC2.0/QC3.0识别芯片构成快速充电电源管理方案。

另外,芯片包含多重保护功能:过温保护,输出短路保护和输入欠压/过压保护等。

NS6116采用SOP8的标准封装。

4典型应用电路深圳市百盛新纪元半导体有限公司FP6601Q NS6116,原装正品,技术支持,增值税代理商SOP-8的管脚图如下图所示:6极限工作参数●VIN 电压-0.3V ~33V ●FB 电压-0.3V ~33V ●SW 电压-0.3V ~33V ●EN 电压-0.3V ~33V ●工作温度范围-40℃~+85℃●存储温度范围-55℃~+150℃●结温范围+150℃●焊接温度(10s 内)+265℃注1:超过上述极限工作参数范围可能导致芯片永久性的损坏。

长时间暴露在上述任何极限条件下可能会影响芯片的可靠性和寿命。

注2:NS6116可以在0℃到70℃的限定范围内保证正常的工作状态。

超过-40℃至85℃温度范围的工作状态受设计和工艺控制影响。

KSZ8863MLL FLL RLL 评估板用户指南说明书

KSZ8863MLL/FLL/RLLEvaluation Board User’s GuideKSZ8863MLL/FLL/RLL Integrated 3-Port 10/100 Managed Switch with PHYsRevision 1.1 January 2011© Micrel, Inc. 2011All rights reservedMicrel is a registered trademark of Micrel and its subsidiaries in theUnited States and certain other countries. All other trademarks are theproperty of their respective owners.The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer. Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury.Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user.A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's ownrisk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.Revision HistoryRevision Date Summary of Changes1.0 07/15/09 Initial Release1.1 01/11/11 Update description.Micrel, Inc. January 11, 2011Table of Contents1.0Introduction (4)2.0Board Features (4)3.0Evaluation Kit Contents (4)4.0Hardware Description (4)4.1Strap In Mode (5)4.1.1Feature Setting Jumpers (6)4.2I2C Master (EEPROM) Mode (7)4.3SPI Slave Mode (8)4.410/100 Ethernet PHY Ports (KSZ8863MLL/RLL) (9)4.5100FX Fiber Port (KSZ8863FLL) (9)4.6LED Indicators (9)4.7MII Port Configuration (KSZ8863MLL/FLL) (9)4.8RMII Port Configuration (KSZ8863RLL) (9)5.0Reference Documents (10)List of TablesTable 1: Feature Setting Jumpers (6)Table 2: Reserved Jumpers (6)Table 3: EEPROM Mode Settings (8)Table 4: SPI Slave Mode Settings (8)Table 5: LED Modes (9)Table 6: RMII Clock Setting (10)List of FiguresFigure 1: KSZ8863MLL/FLL/RLL Evaluation Board Block Diagram (5)Micrel, Inc. January 11, 20111.0 IntroductionThe KSZ8863MLL/FLL/RLL is Micrel’s third generation fully integrated 3-port switch. The two PHY units of KSZ8863MLL/RLL support 10BASE-T and 100BASE-TX. The KSZ8863FLL supports 100BASE-FX. The devices have been designed for cost sensitive systems, however, still offer a multitude of features, such as switch management, port and tag based VLAN, QoS priority, one MII interfaces and CPU control and data interfaces.The KSZ8863MLL/FLL/RLL is an excellent choice for VoIP Phone, Set-top/Game Box, SOHO Residential Gateway, industrial Ethernet systems and as a standalone 3-port switch.The KSZ8863MLL/FLL/RLL Evaluation Board provides a convenient means to evaluate the KSZ8863MLL/FLL/RLL’s rich feature set. Easy access is provided to all of the KSZ8863MLL/FLL/RLL pins, with jumpers and interface connectors allowing quick configuration and re-configuration of the board. MIIM, EEPROM programming, SPI emulation software are also provided to access the more extensive features of the KSZ8863MLL/FLL/RLL, via a PC USB port.2.0 Board Features•Micrel’s KSZ8863MLL/FLL/RLL Integrated 3-Port 10/100 Managed Ethernet Switch•Two RJ-45 Jacks for Ethernet LAN Interfaces with corresponding Isolation Magnetics (KSZ98863MLL/RLL)•Auto MDI/MDI-X on the PHY port• 1 PHY Mode and 1 MAC Mode MII Connector for the Switch RMII/MII Interface• 2 100Base-FX fiber interface(KSZ8863FLL)• 1 USB port to emulate an MIIM, EEPROM, SPI Interface•On board EEPROM• 2 LEDs per port to Indicate the Status and Activity of the RJ45 port• 1 power jack for 5VDC Universal Power Supply3.0 Evaluation Kit ContentsThe KSZ8863MLL/FLL/RLL Evaluation kit includes the following:•KSZ8863MLL/FLL/RLL Evaluation Board Revision 1.0•KSZ8863MLL/FLL/RLL Evaluation Board User’s Guide•Micrel Switch Configuration Software Version 1.0.5•Micrel Switch Configuration Software User Guide•KSZ8863MLL/FLL/RLL Evaluation Board Schematic Revision 1.0(Contact your Micrel FAE for the latest schematic)Note: USB cable and 5V DC Wall Power Supply is not included in the design kit (the dimension of the output plug of 5V DC wall power supply is 2.5x5.5x9.5mm or 0.1x0.218x0.375inch)4.0 Hardware DescriptionThe KSZ8863MLL/FLL/RLL Evaluation Board is in a compact form factor and can sit on a bench near a computer. There are three options for configuration: strap in mode, EEPROM mode, and SPI mode. Strap in mode configuration is easily done with on board jumper options. EEPROM mode and SPI mode are accomplished through a built in USB port interface. With the Micrel software and your PC, you can use the USB port to reprogram the EEPROM on board, or use the SPI interface to access the KSZ8863MLL/FLL/RLL’s full feature set. The board also features oneMicrel, Inc. January 11, 2011MII connector for the Switch MII interface. It is to facilitate connection from the switch to either the external CPU or the external PHY.Figure 1: KSZ8863MLL/FLL/RLL Evaluation Board Block DiagramThe KSZ8863MLL/FLL/RLL evaluation board is easy to use. There are programmable LED indicators for link and activity on the PHY ports and a power LED. A manual reset button allows the user to reset the board without removing the power plug. The 5V power on the board can be supplied by a standard 5VDC power supply (close pin 1-2 of JP400 jumper) or by the USB cable (close pin 2-3 of JP400 jumper) which is used to access the registers in SPI mode. A standard 5VDC power supply is included so that the user can supply power from any 110 Volt AC wall or bench socket. Before to start to use the evaluation board, make sure the power connectors JP403, JP404, JP405, JP406 and JP31 are connected, and close pin 1-2 of J14.4.1 Strap in ModeStrap in configuration mode is the quickest and easiest way to get started. In this mode, the KSZ8863MLL/FLL/RLL acts as a standalone 3-port switch. Simply set the board’s configuration jumpers to the desired settings and apply power to the board. The configuration can be changed while power is applied to the board by changing the jumper settings and pressing the convenient manual reset button for the new settings to take effect. Note that even if no external strap in values are set, internal pull up and pull down resistors will set the KSZ8863MLL/FLL/RLL default configuration. Section 4.1.1 covers each jumper on the board and describes its function. To start in strap in configuration mode, make sure that the USB cable is unplugged, JP34, JP35, JP3and JP9 are connected, JP21, JP25 have jumpers fitted between pins 2 to 3.Micrel, Inc. January 11, 20114.1.1 Feature Setting JumpersThe evaluation board provides jumpers to allow easy setting of strap in configurations for the KSZ8863MLL/FLL/RLL. Table 1 describes the jumpers and their functionalities.Table 1: Feature Setting JumpersOPEN CLOSED JUMPER KSZ8863MLL/FLL/RLLSIGNALJP3 SPIQ SPI EEPROMJP25 P2LED0 EEPROM/SPI Setting. See Section 4.2 and 4.3JP21 P2LED1 EEPROM/SPI Setting. See Section 4.2 and 4.3JP78 FXSD1 Pins 1-2 closed : Disable FEF feature of FX.Pins 5-6 closed : Force port 1 TX modeFor KSZ8863MLL/RLL, close 5-6 since this devicedoesn’t support FX mode.For KSZ8863FLL, open JP77JP77 FXSD2 Pins 1-2 closed : Disable FEF feature of FX.Pins 5-6 closed : Force port 1 TX modeFor KSZ8863MLL/RLL, close 5-6 since this devicedoesn’t support FX mode.For KSZ8863FLL, open JP77JP2 PWRDN Normal Operation KSZ8863MLL/FLL/RLLChip Power DownJP101 SPIQ (P1FFC) Pull Down = DisablePull Up(default) = EnableJP102 SMRXDV3(P1DPX) Pull Down = Half DuplexPull Up(default) = Full DuplexJP103 P1LED1(P1SPD) Pull Down = 10BTPull Up(default) = 100BTJP104 P1LED0(P1ANEN) Pull Down(default) = DisablePull Up = EnableJP201 SMRXD30(P2FFC) Pull Down = DisablePull Up(default) = EnableJP202 SMRXD31(P2DPX) Pull Down = Half DuplexPull Up(default) = Full DuplexJP203 SMRXD32(P2SPD) Pull Down = 10BTPull Up(default) = 100BTJP204 SMRXD33(P2ANEN) Pull Down = DisablePull Up(default) = EnableNote: JP101, JP102, JP103, JP201, JP202, JP203 are only valid if Auto-Negotiation is disabled. The following table shows the recommended settings for the evaluation board reserved jumpers.JUMPER Description Recommended Setting JP30 3.3V Biased of transformerCenter (For test only)OpenJP11 Power for Fiber Module.(Port 2) KSZ8863MLL/RLL: Open For KSZ8863FLL:Close pin 1-2 for 3.3V Fiber Module.Close pin 3-2 for 5.0V Fiber Module.JP10 Power for Fiber Module.(Port 1) KSZ8863MLL/RLL: Open For KSZ8863FLL:Close pin 1-2 for 3.3V Fiber Module.Close pin 3-2 for 5.0V Fiber Module.JP28 REFCLKO3 enable. KSZ8863MLL/FLL: OpenKSZ8863RLL:Close pin 1-2: Enable REFCLKOClose pin 2-3: Disable REFCLKO4.2 I2C Master (EEPROM) ModeThe evaluation board has an EEPROM to allow the user to explore more extensive capabilities of the KSZ8863MLL/FLL/RLL. The user can conveniently program the EEPROM on board using the USB port from any computer with a WIN 2000/XP environment and the Micrel provided software. This makes it easy for the user to evaluate features like “broadcast storm protection” and “rate control”.To prepare the KSZ8863MLL/FLL/RLL evaluation board for EEPROM configuration follow these steps:1. Install the Micrel Switch Configuration Software to your computer.2. Set JP3, JP9, JP21, JP25, JP34 and JP35 as specified in Table 3 for EEPROM modeconfiguration. Make sure that the EEPROM is installed on the board.3.Connect the computer’s USB port to the KSZ8863MLL/FLL/RLL board with aUSB port cable.4. There are two way to power up the evaluation board:a). Connect the 5 VDC power supply to the KSZ8863MLL/FLL/RLL when JP400pin1-2 is closed.b). 5 VDC power source from the USB port when JP400 pin 2-3 is closed.5. The KSZ8863MLL/FLL/RLL will power up in its default configuration if there is noinformation in the EEPROM.6. Click the software icon to invoke the software to program the desired settings into theEEPROM. See the Micrel Switch Configuration Software User Guide for details.7. Press the manual reset button. The KSZ8863MLL/FLL/RLL will reset and read the newconfiguration in the EEPROM. After reset, the KSZ8863MLL/FLL/RLL is ready for normal operation.Micrel, Inc. January 11, 2011Table 3: EEPROM Mode SettingsJumper Description SettingJP9 SPIQ ClosedJP3 SCL_MDC_SW ClosedJP34 SCL_MDC ClosedJP35 SDA_MDIO ClosedJP25 Serial Bus Config. (P2LED0) Pins 2-3 closedJP21 Serial Bus Config. (P2LED1) Pins 2-3 closed4.3 SPI Slave ModeFrom SPI interface to the KSZ8863MLL/FLL/RLL, use a USB to SPI converter that allows accessing all of the KSZ8863MLL/FLL/RLL features and registers. The user can easily access the SPI interface using a computer connected to the evaluation board’s USB port interface. Micrel provides a Windows 2000/XP based program for the user to evaluate the KSZ8863MLL/FLL/RLL’s full feature set. In addition to all the registers available via EEPROM programming, a host CPU connected to theKSZ8863MLL/FLL/RLL’s SPI interface will be able to access all static MAC entries, the VLAN table, dynamic MAC address table and the MIB counters.To prepare the KSZ8863MLL/FLL/RLL evaluation board for SPI modeconfiguration follow these steps:1. Install the Micrel Switch Configuration Software on your computer.2. Set JP3, JP9, JP21, JP25, JP34 and JP35 as specified in Table 4 for SPI modeconfiguration.Table 4: SPI Slave Mode SettingsJumper Description SettingJP9 SPIQ OpenJP3 SCL_MDC_SW OpenJP34 SCL_MDC ClosedJP35 SDA_MDIO ClosedJP25 Serial Bus Config. (P2LED0) Pins 2-3 closedJP21 Serial Bus Config. (P2LED1) Pins 1-2 closed3.Connect the computer’s USB port to the KSZ8863MLL/FLL/RLL board with aUSB port cable.4.There are two way to power up the evaluation board:a). Connect the 5 VDC power supply to the KSZ8863MLL/FLL/RLL when JP400pin1-2 is closed.b). 5 VDC power source from the USB port when JP400 pin 2-3 is closed.5.The KSZ8863MLL/FLL/RLL will power up in its default configuration6.Click the software icon to invoke the software to program the desired settings. Micrel, Inc. January 11, 2011See the Micrel Switch Configuration Software User Guide for details.4.4 10/100 Ethernet PHY Ports (KSZ8863MLL/RLL)There are two 10/100 Ethernet PHY ports on the KSZ8863MLL/RLL evaluation board. The ports can be connected to an Ethernet traffic generator or analyzer via standard RJ-45 connectors using CAT-5 cables. Each port can be used as either an uplink or downlink. Both ports support auto MDI/MDI-X, eliminating the need for cross over cables.4.5 100FX Fiber Port (KSZ8863FLL)There are two 100FX PHY ports on the KSZ8863FLL evaluation board. The ports can be connected to an Ethernet traffic generator or analyzer via fiber transceiver and fiber cable. The fiber signal threshold can be set by register 192 bit 6(Port1) and bit 7(Port2). If the bits are 1, the threshold will be set to 2.0V, Otherwise it is 1.25V.The resister R76 also need to be adjusted if the FXSD signal value from the fiber module doesn’t meet the fiber signal threshold spec.4.6 LED IndicatorsThere is one column of LED indicator for one column for port 2. The LED indicators are programmable to three different modes. LED mode is selected through register 195 bit [5:4] setting. The LED mode definitions are specified in Table 5. See Figure 1 for the LEDs’ orientation on the KSZ8863MLL/FLL/RLL evaluation board.Table 5: LED ModesRegister 195 Bit[5:4]00 01 10 11PxLED1 = Speed PxLED1 = Active PxLED1 = Duplex PxLED1 = Duplex PxLED0 = Link/Active PxLED0 = Link PxLED0 = Link/Active PxLED0 = LinkThe KSZ8863MLL/FLL/RLL evaluation board provides two LEDs (PxLED1, PxLED0) for each PHY port.The KSZ8863MLL/FLL/RLL evaluation board also has a power LED (D3) for the 3.3V power supply. When D3 is lit, the board’s 3.3V power supply is “on”.4.7 MII Port Configuration (KSZ8863MLL/FLL)The evaluation board provides access to the KSZ8863MLL/FLL/RLL’s third MAC via the MII port interfaces. The MAC can be configured to MII PHY mode and MII MAC mode via register 53 bit 7. The default of the bit is 0 for MII PHY mode.In MII PHY mode, the MII transmit and receive signals will be on J3, the male MII port connectors. This mode is usually used to connect the KSZ8863MLL/FLL/RLL to an external MAC processor. In MII MAC mode, the MII transmit and receive signals will be on J4, the female MII port connector. This interface is normally used to connect the KSZ8863MLL/FLL/RLL to an external PHY, for example the Micrel KSZ8041NL.4.8 RMII Port Configuration (KSZ8863RLL)In RMII interface, the 50MHz reference clock can be provide by the KSZ8863RLL or by the link partner. When pin 1-2 of JP28 is closed, the reference clock will be output from REFCLKO on Micrel, Inc. January 11, 2011Micrel, Inc. January 11, 2011KSZ8863RLL. Register 198 bit[3] is used to select internal or external reference clock for the KSZ8863RLL RMII interface. If pin 2-3 of JP28 is closed, the REFCLKO disable.Table 6: RMII Clock Setting5.0 Reference DocumentsKSZ8863MLL/FLL/RLL Datasheet Rev. 1.1 (Contact Micrel for latest Datasheet)KSZ8863MLL/FLL/RLL Evaluation Board Schematic Rev. 1.0 (Contact Micrel for latest Schematic)KSZ8863MLL/FLL/RLL Evaluation Board Gerber files Micrel Switch Configuration Software User GuideReg198[3] EN_REFCLKO_3 Clock Source NoteExternal 50MHz OSC input to REFCLKI_3EN_REFCLKO_3 = 0 to DisableREFCLKO_3 for better EMI0 1REFCLKO_3 Output Is Feedback to REFCLKI_3 EN_REFCLKO_3 = 1 to Enable REFCLKO_3 1 1Internal Clock SourceREFCLKI_3 is unconnected EN_REFCLKO_3 = 1 to Enable REFCLKO_3 1 0Not suggestMouser ElectronicsAuthorized DistributorClick to View Pricing, Inventory, Delivery & Lifecycle Information:M icrochip:KSZ8863FLL-EVAL KSZ8863MLL-EVAL。

KS88C6108中文资料

1PRODUCT OVERVIEWSAM8 PRODUCT FAMILYSamsung's SAM8 family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-programmable ROM sizes. Important CPU features include:—Efficient register-oriented architecture—Selectable CPU clock sources—Idle and Stop power-down mode release by interrupt—Built-in basic timer with watchdog functionA sophisticated interrupt structure recognizes up to eight interrupt levels. Each level can have one or more interrupt sources and vectors. Fast interrupt processing (within a minimum six CPU clocks) can be assigned to specific interrupt levels.KS88C6108/C6116/P6116 MICROCONTROLLERSThe KS88C6108/C6116/P6116 single-chip 8-bit microcontroller is based on the powerful SAM8 CPU architecture. The internal register file is logically expanded to increase the on-chip register space. The KS88C6108/C6116/P6116 have 8/16 K bytes of on-chip program ROM.Following Samsung's modular design approach, the following peripherals were integrated with the SAM8 core:—Four programmable I/O ports (total 28 pins)—One 8-bit basic timer for oscillation stabilization and watchdog functions—One 8-bit general-purpose timer/counter with selectable clock sources—One 8-bit counter with selectable clock sources, including Hsync or Csync input—One 8-bit timer for interval mode—PWM block with seven 8-bit PWM circuits —Sync processor block (for Vsync and Hsync I/O, Csync input, and Clamp signal output)—Multi master IIC-bus with DDC support.The KS88C6108/C6116/P6116 are a versatile microcontroller that is ideal for use in multi-sync monitors or in general-purpose applications that require sophisticated timer/counter, PWM, sync signal processing, and multi-master IIC-bus support withDDC. It is available in a 42-pin SDIP or a 44-pin QFPpackage.Figure 1-1. KS88C6108/C6116/P6116MicrocontrollersFEATURESCPU•SAM8 CPU coreMemory•8/16-Kbyte internal program memory (ROM)•272-byte general-purpose register areaInstruction Set•78 instructions•IDLE and STOP instructions added for power-down modesInstruction Execution Time•500 ns minimum (with 12 MHz CPU clock)Interrupts•Nine interrupt sources•Nine interrupt vectors•Six interrupt levels•Fast interrupt processing for a select levelGeneral I/O•Four I/O ports (total 28 pins):8-Bit Basic Timer•Programmable timer for oscillation stabilization interval control or watchdog timer functions •Three selectable internal clock frequenciesTimer/Counters•One 8-bit general-purpose timer/counter with programmable operating modes and the following clock source options:—Two selectable internal clock frequencies •One 8-bit timer with interval operating mode •One 8-bit counter with the following clock source options:—Two selectable internal clock frequencies—Hsync (or Csync) input from the syncprocessor block—External clock sourcePulse Width Modulator•Seven 8-bit PWM modules:—8-bit basic frame—Four push-pull and three n-channel,open-drain output channels—Selectable clock frequencies: 46.875 kHz at12 MHz fosc.Sync Processor•Detection of sync input signals (Vsync-I, Hsync-I, and Csync-I)•Sync signal separation and output (Hsync-O, Vsync-O, and Clamp-O)•Pseudo sync signal output•Programmable clamp signal outputDDC and Multi-Master IIC-Bus•Serial peripheral interface•Support for display data channel (DDC) Oscillator Frequency• 6 MHz to 12 MHz external crystal oscillator •Interval Max. 12MHz CPU clockOperating Temperature Range•–40°C to + 85°COperating Voltage Range• 4.5 V to 5.5 VPackage Types•42-pin SDIP, 44-pin QFPBLOCK DIAGRAMRESET P1.0k 1.3X IN X OUTMAIN OSCP3.0k 3.7INTERNAL BUSP2.0k 2.7PORT 0P0.0k 0.7/INT0-INT2PORT 28-BIT PWM (7-CH)SYNC PRO-CESSORTIMER 0PORT 1PORT3PWM0PWM1•••PWM6Vsync-I Hsync-I Csync-I Vsync-O Hsync-O Clamp-OT0CAP8-blt Counter (TIMER 1)T1CKDDC and Multi master IIC-busSCL SDAINT0-INT2TESTInterval timer (TIMER 2)SAM8 CPU8/16-KBYTE MASK ROM272-BYTE REGISTER FILEI/O PORT and INTERRUPTCONTROLFigure 1-2. Block DiagramPIN ASSIGNMENTSP3.1P3.0P0.0 / INT0P0.1 / INT1P0.2 / INT2P0.3P0.4 / T0CAPP0.5 / T1CKVDDP0.6P0.7P1.0P1.1P1.2P1.3 P2.0 / PWM0 P2.1 / PWM1 P2.2 / PWM2 P2.3 / PWM3 P2.4 / PWM4 P2.5 / PWM 5KS88C6108/KS88C611642-SDIP(Top View)123456789101112131415161718192021424140393837363534333231302928272625242322P3.2VSS2P3.3P3.4P3.5P3.6P3.7RESETXOUTXINVSS1P2.7 / Csync-IHsync-IVsync-I (VCLK)Clamp-OHsync-OVsync-OSCLSDATESTP2.6 / PWM6Figure 1-3. Pin Assignment Diagram (42-SDIP Package)PIN ASSIGNMENTS (Cont.)P 2.0 / P W M 0P 1.3P 1.2P 1.1P 1.0P 0.7P 0.6V D DP 0.5 / T 1C KP 0.4 / T 0C A P P 0.3P2.1 / PWM1 P2.2 / PWM2 P2.3 / PWM3 P2.4 / PWM4 P2.5 / PWM5N.C.P2.6 / PWM6TEST SDA SCL Vsync-OP0.2 / INT2 P0.1 / INT1 P0.0 / INT0 P3.0 P3.1 NC P3.2 VSS2 P3.3 P3.4 P3.5H s y n c -OC l a m p -OV s y n c -IH s y n c -IP 2.7 / C s y n c -IV S S 1X I NX O U TR E S E TP 3.7P 3.634 35 36 37 38 39 40 41 42 43 4422 21 20 1918 17 16 15 14 13 12KS88C6108/ KS88C6116 44-QFP (Top View)12345678910113332313029282726252423Figure 1-4. Pin Assignment Diagram (44-QFP Package)PIN DESCRIPTIONSTable 1-1. KS88C6108/C6116/P6116 Pin DescriptionsPin NamesPinTypePinDescriptionCircuitTypeSDIP PinNumbersSharedFunctionsP0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7I/O General-purpose, 8-bit I/O port. Sharefunctions include three external interruptinputs, I/O for timers 0 and 1. You canselectively configure port 0 pins to input oroutput mode.D-13456781011INT0INT1INT2T0CAPT1CKP1.0–P1.3I/O General purpose, 8-bit I/O port. You canselectively configure port 1 pins to input orpush-pull output mode.D-112–15–P2.0 P2.1 P2.2 P2.3 P2.4 P2.5 P2.6 P2.7I/O General purpose, 8-bit I/O port. You canselectively configure port 2 pins to input oroutput mode. The port 2 pin circuit aredesigned to push-pull PWM output andCsync signal input.D-1D-1D-1D-1E-1E-1E-1D-11617181920212231PWM0PWM1PWM2PWM3PWM4PWM5PWM6Csync-IP3.0–P3.7I/O General-purpose, 8-bit I/O port. You canselectively configure port 3 pins to input oroutput mode.E2, 1, 42,40–36–Hsync-I Vsync-I Clamp-O Hsync-O Vsync-O SCL SDAIIOOOI/OI/OThe pins are sync processor signal I/O andIIC-bus clock and data I/OAAAAAG-3G-330292827262524–V DDV SS1, V SS2–Power supply pins–932, 41–X IN, X OUT–System clock input and output pins–33, 34–RESET I System reset pin B35–TEST I Factory test pin input0 V: normal operation5 V: factory test mode–23–NOTE:See ‘Pin Circuit Diagrams’ on next two pages for detailed information on circuit types A, B, D-1, E, E-1,and G-3.PIN CIRCUITSVssVddFigure 1-5. Pin Circuit Type AVddNoise Filter280 K ΩRESETFigure 1-6. Pin Circuit Type B (RESET )OutputVssVddOutput DisableData orOther functionDigital Input or TTL InputFigure 1-7. Pin Circuit Type D-1Typical 47-K ΩDataVddOutputPull-upenableInputVssOpen drainOutput DisableVddFigure 1-7. Pin Circuit Type EOutput DisableDataIN/OUTInputVssOpen drain VddFigure 1-8. Pin Circuit Type E-1Output DataVssInputFigure 1-9. Pin Circuit Type G-3NOTES16ELECTRICAL DATAOVERVIEWIn this section, KS88C6108/C6116 electrical characteristics are presented in tables and graphs. The information is arranged in the following order:—Absolute maximum ratings— D.C. electrical characteristics—I/O capacitance— A.C. electrical characteristics—Oscillation characteristics—Oscillation stabilization time—Schmitt trigger characteristicsTable 16-1. Absolute Maximum Ratings(T A = 25°C)Parameter Symbol Conditions Rating Unit Supply voltage V DD–– 0.3 to + 7.0V Input voltage V I1Type C (n-channel, open-drain)– 0.3 to+ 10V V I2All port pins except V I1– 0.3 to V DD + 0.3Output voltage V O All output pins– 0.3 to V DD + 0.3V Output currentHighI OH One I/O pin active– 10mAAll I/O pins active– 60Output currentLowI OL1One I/O pin active+ 30mAI OL2Total pin current except port 3+ 100I OL3Sync-processor I/O pins and IIC-busclock and data pins+ 150OperatingtemperatureT A–– 40 to + 85°CStoragetemperatureT STG–– 65 to + 150°CTable 16-2. D.C. Electrical Characteristics(T A= – 40°C to + 85°C, V DD = 4.5 V to 5.5 V)Parameter Symbol Conditions Min Typ Max Unit Input HighvoltageV IH1All input pins except V IH2 and V IH30.8 V DD–V DD VV IH2X IN, X OUT V DD – 0.5V DDV IH3TTL input (HsyncI, VsyncI and CsyncI) 2.0V DDInput Low voltage V IL1All input pins except V IL2and V IL3––0.2 V DD V V IL2X IN, X OUT0.4V IL3TTL input (HsyncI, VsyncI and CsyncI)0.8Output High voltage V OH1V DD= 4.5 V to 5.5 VI OH = – 8 mA Port 1 onlyV DD – 1.0––VV OH2V DD = 4.5 V to 5.5 VI OH = – 2 mA Ports 0, 2, ClampO, Hand VsyncOV DD – 1.0V OH3V DD = 4.5 V to 5.5 VI OH = – 6 mA, Port 3V DD – 1.0Table 16-2. D.C. Electrical Characteristics (Continued)(T A= – 40°C to + 85°C, V DD = 4.5 V to 5.5 V)Parameter Symbol Conditions Min Typ Max UnitOutput Low voltage V OL1V DD= 4.5 V to 5.5 VI OL = 8 mA, port 1 only––0.4VV OL2I OL = 2 mAPort 0, 2, ClampO, HsyncO andVsyncO0.4V OL3I OL = 6 mAPort 3, SCL and SDA0.4Input High leakage current I LIH1V IN = V DDAll input pins except X in, X out––3µAI LIH2V IN = V DDX OUT only––20I LIH3V IN = V DDX IN only2.5620Input Low leakage current I LIL1V IN= 0 VAll input pins except X in, X outand RESET–––3µAI LIL2V IN= 0 V; X OUT only––– 20I LIL3V IN= 0 V; X IN only– 2.5– 6– 20Output High leakage current I LOHL V OUT = V DDAll output pins except port 1––3µAOutput Lowleakage currentI LOL V OUT = 0 V––– 3µAPull-up resistor R L1V IN= 0 V;V DD = 4.5 V to 5.5 VPort 3204780kΩR L2V IN= 0 V;V DD = 4.5 V to 5.5 VRESET only150280480Supply current (NOTE)I DD1V DD= 4.5 V to 5.5 V12 MHz CPU clock–1530mAI DD2Idle mode;V DD = 4.5 V to 5.5 V12 MHz CPU clock510I DD3Stop mode; V DD = 5.0 V110µANOTE: Supply current does not include drawn internal pull–up resistors and external loads of output.Table 16-3. Data Retention Supply Voltage in Stop Mode(T A = – 40 °C to + 85 °C)Parameter Symbol ConditionsMin Typ Max Unit Data retention supply voltage V DDDR Stop mode2–6V Data retention supply currentI DDDRStop mode, V DDDR = 2.0 V––5µANOTES :1. During the oscillator stabilization wait time (t WAIT ), all CPU operations must be stopped.2. Supply current does not include drawn through internal pull–up resistors and external output current loads.V DDRESETEXECUTION OF STOP INSTRUCTIONV DDDRDATA RETENTION MODESTOP MODERESETOCCURSNORMAL OPERATING MODEOSCILLATION STABILIZATIONTIMEt WAITNOTE : t WAIT is the same as 4096 × 32 × 1 / f OSC .≈≈Figure 16-1. Stop Mode Release Timing When Initiated by a ResetTable 16-4. Input/Output Capacitance(T A = –40°C to + 85°C, V DD = 0 V)Parameter Symbol ConditionsMin Typ Max Unit Inputcapacitance C IN f = 1 MHz; unmeasured pins are connected to V SS––10pFOutputcapacitance C OUT I/O capacitanceC IOTable 16-5. A.C. Electrical Characteristics(T A = – 40°C to + 85°C, V DD= 4.5 V to 5.5V)Parameter Symbol Conditions Min Typ Max UnitNoise Filter t NF1H,t NF1L P0.2–P0.0, T0CAP andT1CK (RC delay)300––nst NF2RESET only (RC delay)800––1 t CPUt NF1L t NF1H0.8 V DDt NF20.2 V DDNOTE: The unit t CPU means one CPU clock period.Figure 16-2. Input Timing Measurement Points for P0.0–P0.2, T0CAP and T1CKTable 16-6. Oscillation Characteristics(T A = – 40°C + 85°C)Oscillator Clock CircuitConditionsMin Typ Max Unit Main crystal or ceramicC2C1X IN X OUT V DD = 4.5 V to 5.5 V6–12MHzExternal clock (main)X IN X OUTV DD = 4.5 V to 5.5 V6–12MHzNOTE :The maximum oscillator frequency is 12 MHz. If you use an oscillator frequency higher than 12 MHz, you cannotselect a non-divided CPU clock using CLKCON settings. That is, you must select one of the divide-by values.Table 16-7. Oscillation Stabilization Time(T A = – 40°C + 85°C, V DD = 4.5 V to 5.5 V)Oscillator Test ConditionMin Typ Max Unit Crystal V DD = 4.5 V to 5.5 V ––20msCeramic V DD = 4.5 V to 5.5V––10External clockX IN input High and Low level width (t XH , t XL )25–500ns NOTE :Oscillation stabilization time is the time required for the CPU clock to return to its normal oscillation frequency aftera power-on occurs, or when Stop mode is released.X INt XL t XH1 / f OSCV DD =0.5 V 0.4 VFigure 16-3. Clock Timing Measurement Points for X INV DD V SS V outA B C D V inA : 0.2 V DDB : 0.4 V DDC : 0.6 V DDD : 0.8 V DDFigure 16-4. Schmitt Trigger Characteristics (Normal Port; except TTL Input)NOTES17MECHANICAL DATAOVERVIEWThe KS88C6116 microcontroller is available in a 42-pin SDIP package (Samsung part number 42-SDIP-600) and a 44-QFP package (Samsung part number 44-QFP-1010B).NOTE : Dimensions are in millimeters.42-SDIP-60014.00 =0.20.50 =0.139.10 =0.20 ~ 15 °0.25+0.1 =0.05#121422215.24(1.77)1.00 =0.11.7780.51M I N3.50 =0.23.30 =0.35.08M A XFigure 17-1. 42-Pin SDIP Package Mechanical Data (42-SDIP-600)NOTE : Dimensions are in millimeters.44-QFP-1010B13.20 =0.3#44(1.00)#113.20 =0.30.35+0.10- 0.050.10 MAX0~8°0.05 MIN 2.05 =0.102.30 MAX0.80=.200.15+0.10 - 0.0510.00 =0.210.00 =0.20.80Figure 17-2. 44-Pin QFP Package Mechanical Data (44-QFP-1010B)18KS88P6116 OTPOVERVIEWThe KS88P6116 single-chip CMOS microcontroller is the OTP (One Time Programmable) version of the KS88C6108/C6116 microcontrollers. It has an on-chip EPROM instead of masked ROM. The EPROM is accessed by serial data format.The KS88P6116 is fully compatible with the KS88C6108/C6116, both in function and in pin configuration.Because of its simple programming requirements, the KS88P6116 is ideal for use as an evaluation chip for the KS88C6108/C6116.P3.2V SS2/V SS P3.3P3.4P3.5P3.6P3.7RESET /RESET XOUT XIN V SS1/V SS P2.7/Csync-1Hsync-1 Hsync-1 (VCLK)Clamp-O Hsync-O Vsync-O SLC SDA TEST/V PP P2.6/PWM6424140393837363534333231302928272625242322123456789101112131415161718192021KS88P611642-SDIP (Top View)P3.1P3.0P0.0/INT0P0.1/INT1P0.2/INT1P0.3P0.4/T0CAP P0.5/T1CK V DD /VDDP0.6P0.7SCLK /P1.0SDAT /P1.1P1.2P1.3P2.0/PWM0P2.1/PWM1P2.2/PWM2P2.3/PWM3P2.4/PWM4P2.5/PWM5NOTE: The bolds indicate an OTP pin name.Figure 18-1. KS88P6116 Pin Assignments (42-SDIP Package)P 2.0 / P W M 0P 1.3P 1.2P 1.1 / S D A TP 1.0 / S C L KP 0.7P 0.6V D D / V D DP 0.5 / T 1C KP 0.4 / T 0C A P P 0.3P2.1 / PWM1 P2.2 / PWM2 P2.3 / PWM3 P2.4 / PWM4 P2.5 / PWM5N.C.P2.6 / PWM6 V PP /TESTSDA SCL Vsync-OP0.2 / INT2 P0.1 / INT1 P0.0 / INT0 P3.0 P3.1 NC P3.2 VSS2 / VSS P3.3 P3.4 P3.5H s y n c -OC l a m p -OV s y n c -IH s y n c -IP 2.7 / C s y n c -IV S S / V S S 1X I NX O U TR E S E T / R E S E TP 3.7P 3.6KS88P6116 44-QFP (Top View)34 35 36 37 38 39 40 41 42 43 44123456789101122 21 20 1918 17 16 15 14 13 123332313029282726252423NOTE: The bolds indicate an OTP pin name.Figure 18-2. KS88P6116 Pin Assignments (44-QFP Package)Table 18-1. Descriptions of Pins Used to Read/Write the EPROMMain Chip During ProgrammingPin Name Pin Name Pin No.I/O Function P1.1SDAT13 (*30)I/O Serial DATa Pin (Output when reading, Inputwhen writing) Input & Push-pull Output Port canbe assignedP1.0SCLK12 (*29)I Serial CLocK Pin (Input Only Pin)TEST V PP(TEST)23 (*41)I EPROM Cell Writing Power Supply Pin(Indicates OTP Mode Entering) When writing12.5V is applied and when reading 5V isapplied.(Option)RESET RESET35 (*9)I Chip InitializationV DD / V SS1 /V SS2V DD / V SS /V SS9 / 32 / 41(*26 / 6 / 15)I Logic Power Supply Pin. V DD should be tied to5V during programming.NOTE:* means the 44-QFP OTP pin number.Table 18-2. Comparison of KS88P6116 and KS88C6108/C6116 Features Characteristic KS88P6116KS88C6108/C6116 Program Memory16 K byte EPROM16 K byte mask ROMOperating Voltage (V DD) 4.5 V to 5.5 V 4.5 V to 5.5VOTP Programming Mode V DD = 5 V, V PP(TEST)=12.5VPin Configuration42SDIP, 44QFP42SDIP, 44QFPEPROM Programmability User Program 1 time Programmed at the factory OPERATING MODE CHARACTERISTICSWhen 12.5 V is supplied to the V PP(TEST) pin of the KS88P6116, the EPROM programming mode is entered. The operating mode (read, write, or read protection) is selected according to the input signals to the pins listed in Table 16-3 below.Table 18-3. Operating Mode Selection CriteriaV DD VPP(TEST)REG/MEMADDRESS(A15-A0)R/W MODE5 V 5 V00000H1EPROM read12.5 V00000H0EPROM program12.5 V00000H1EPROM verify12.5 V10E3FH0EPROM read protection NOTE:"0" means Low level; "1" means High level.D.C. ELECTRICAL CHARACTERISTICSTable 18-4. D.C. Electrical Characteristics(T A= – 40 °C to + 85 °C, V DD = 4.5 V to 5.5 V)Parameter Symbol Conditions Min Typ Max UnitInput High leakage current I LIH1V IN = V DD;All input pins except X in, X out––3µAI LIH2V IN = V DD;X OUT only20I LIH3V IN = V DD;X IN only2.5620Input Low leakage current I LIL1V IN= 0 V;All input pins except X in, X outand RESET–––3µAI LIL2V IN= 0 V; X OUT only––– 20I LIL3V IN= 0 V; X IN only– 2.5– 6– 20Output Highleakage currentI LOH1V OUT = V DD––3µAOutput Lowleakage currentI LOL1V OUT = 0 V––– 3µA Supply current I DD1Normal operating mode;12 MHz CPU clock–1530mAI DD2IDLE mode;12 MHz CPU clock510I DD3Stop mode; V DD = 5.0 V–110µA Data retentionsupply voltageVDDDR Stop mode2–6VData retentionsupply voltageIDDDR Stop mode; VDDDR = 2V––5µASTART Address= First Location V DD=5V, V PP=12.5Vx = 0 Program One 1ms PulseIncrement Xx = 10Verify 1 ByteLast Address V DD = V PP= 5 V Compare All Byte Device Passed Increment AddressVerify ByteDevice FailedPASSFAILNOFAIL YESFAILNOFigure 18-3. OTP Programming AlgorithmNOTE。

6116芯片

6116芯片6116芯片是一种静态随机存储器(SRAM),采用16位数据总线和16位地址总线。

该芯片具有存储器容量为2048字节,即16K位,并且采用静电存储单元,可以实现数据的快速读写。

6116芯片是一种广泛应用于计算机以及其他电子设备中的存储器芯片,它在数据存储和读取方面具有高性能和可靠性。

下面将详细介绍6116芯片的架构、工作原理以及应用领域。

6116芯片的结构由多个存储元件组成,每个存储元件可以存储一个字节的数据。

这些存储元件以矩阵的形式排列,通过行和列地址进行访问。

6116芯片的地址总线宽度为16位,可以寻址2^16=65536个存储单元。

数据总线宽度也为16位,可以同时读取或写入16位的数据。

该芯片采用的是静电存储单元,即每个存储单元由六个电晶体管组成。

这种存储单元具有快速读取和写入的特性,但是也需要不断地刷新以保持数据的稳定性。

为了实现刷新操作,6116芯片内部集成了一个刷新计数器和一个刷新电路。

刷新计数器负责生成刷新周期,并通过刷新电路将刷新脉冲传递到存储单元,以防止数据丢失。

6116芯片的工作原理如下:首先,根据需要的地址,将地址信号传递给地址选择器。

地址选择器将地址信号转换为行和列地址信号,并将它们传递给存储单元。

存储单元根据行和列地址信号,选中需要读取或写入的存储单元。

如果需要读取数据,则存储单元将所选存储单元内的数据通过数据总线传递给数据输出缓冲器,然后再传递给外部设备。

如果需要写入数据,则将数据信号通过数据输入缓冲器传递给存储单元,并将其写入选中的存储单元。

6116芯片具有很多应用领域,其中最常见的是在计算机系统中作为主存储器使用。

它可以存储计算机程序、数据以及中间结果,以供CPU进行读取和写入。

另外,6116芯片还可以用于各种嵌入式系统中,如通信设备、工控设备以及嵌入式系统开发板等。

它的高性能和可靠性使得它成为了许多电子设备中不可或缺的组成部分。

此外,6116芯片还可以通过多个芯片并联来扩展存储容量,以满足更大规模的数据存储需求。

玉柴(Yu Chai)CK-6127J62-6B2AZ-RU公交车备件图册说明书

前言 Preface本备件图册针对的车型:CK-6127J62-6B2AZ-RUThe parts catalogue of bus model: CK-6127J62-6B2AZ-RU合同号:3141495Contract No.3141495本备件图册上的插图主要标示有关零部件的基本工艺图形。

插图上涉及到的零部件尺寸比例、安装方向以及装配顺序可能不精确,因此本备件图册建议仅用于指导用户采购零部件用,不建议用于指导装配或维修。

为避免出现不必要的错误,当您采购零部件配件时,请提供如下信息:Illustration in this spare parts catalogue shows mainly basic process sketch for related parts. The dimension scale, direction of installation and assembling procedures referred in the illustrations may be inaccurate; therefore it is recommended to be only used as a guide for part ordering but not for assembling and maintenance. While ordering parts, please provide the following information to avoid unnecessary mistakes:1. 整车型号、出厂编号(以上的型号、编号请参见位于车内乘客门上方的整车铭牌上);1. Whole bus model, serial No. (Please refer to interior nameplate located above the passenger door):2. 需采购的零部件件号及件名;2. Name and part No. of parts to be ordered;3. 所采购零部件的数量;3. Quantity of parts to be ordered;4. 零部件外形照片(可能的情况下)。

CW6116

型号:CW6116报警联动控制模块 安装操作手册一、概述:丛文®报警联动控制模块(CW6116)是与丛文®系列报警软件配套使用的可编程联动输出模块,可用于如报警中心驱动大型电子地图的LED,显示用户的报警、布撤防状态,也可以作为集成保安系统的报警联动CCTV的开关信号,或联动继电器驱动灯光等电气设备。

二、功能特点:z每个模块有16个报警联动输出信号,可用作开关和闪烁方式输出。

z每个输出为OC门开关信号(指平时对地呈高阻状态,输出时对地短路),可通过S1、S2拨码开关选择驱动LED或继电器。

z可对应丛文®报警系列软件(如警讯中心、天网中心、警卫中心等)中的用户、报警点、巡更点联动输出,对布撤防、报警、防区旁路、巡更点报告等各种状态可分别通过LED 的闪烁和亮灭方式来指示。

z可在警卫中心软件按事件(报警、未准备等)驱动,也可直接控制开关输出,驱动电气设备、CCTV设备等。

z多个模块采用并联方式扩充输出,安装简单。

z采用简便的RS485通讯方式,通讯距离最长可达1200m。

三、安装说明CW6116采用模块式结构,只需直接用螺丝通过安装孔固定在电子地图板上,如图连接线路和正确设置输出方式及设备地址即可。

CW2301四、输出方式选择S1和S2的16位分别对应16路输出选择,其中S1的8位开关分别对应9至16路输出,S2的8位开关分别对应1至8路输出,当拨在“OFF”上时,其相应位表示选择驱动LED 输出,当拨在“ON”上,其相应位表示选择驱动继电器输出。

五、测试状态SW1的第8位为测试开关,将其打在“ON”的位置时进入测试状态,此时所有16路OC门输出都变为导通:LED亮,继电器动作;将其打在“OFF”位置时,所有输出恢复进入测试前的状态。

六、地址设置SW1的第1-7位为地址码设置开关,设备地址码的设置方法如下表所示,其中开关打在“ON”位置表示相应位为“1”,打在“OFF”位置时表示该位为“0” 。

SC8863资料

1 C1 1uF Ceramic

EN

GND 2

SET

5 C2 1uF Ceramic

TYPICAL APPLICATION - EXTERNALLY SET OUTPUT VOLTAGE

U1 VIN > VOUT + VD(MAX) 3 VIN SC8863 VO 4 R1 1 EN GND 2 R2 10k SET 5

Part Number Package

(1)(2)

BLOCK DIAGRAM

SC8863-XXXCSK

SOT-23-5

Notes: (1) Where -XXX denotes voltage options. Available voltages are: 2.50V (-250), 2.80V (-280), 3.00V (-300), and 3.30 (-330)V. (2) Add suffix ‘TR’ for tape and reel.

(1)

VTH VSET IOUT = 1mA 1mA ≤ IOUT ≤ 150mA, 2.5V ≤ VIN ≤ 5.5V

20 1.225 1.206

55 1.250

80 1.275 1.294

mV V

SET Input Leakage Current

(3)

ISET

SET = 1.3V

0.015

2.500 5.000

-2.0% -3.5%

VOUT

+2.0% +3.5%

V

Line Regulation

(1)

REG(LINE)

5

10 12

mV

Load Regulation

XC6116H638资料

1/26XC6101_07_XC6111_17 ETR0207_009Preliminary◆CMOS Voltage Detector◆Manual Reset Input ◆Watchdog Functions ◆Built-in Delay Circuit ◆Detect Voltage Range: 1.6~5.0V, ± 2% ◆Reset Function is Selectable V DFL (Low When Detected) V DFH (High When Detected)■GENERAL DESCRIPTION The XC6101~XC6107, XC6111~XC6117 series aregroups of high-precision, low current consumption voltage detectors with manual reset input function and watchdog functions incorporating CMOS process technology. The series consist of a reference voltage source, delay circuit, comparator, and output driver.With the built-in delay circuit, the XC6101 ~ XC6107, XC6111 ~ XC6117 series’ ICs do not require any external components to output signals with release delay time. Moreover, with the manual reset function, reset can be asserted at any time. The ICs produce two types of output; V DFL (low when detected) and V DFH (high when detected).With the XC6101 ~ XC6105, XC6111 ~ XC6115 series’ ICs, the WD pin can be left open if the watchdog function is not used. Whenever the watchdog pin is opened, the internal counter clears before the watchdog timeout occurs. Since the manual reset pin is internally pulled up to the V IN pin voltage level, the ICs can be used with the manual reset pin left unconnected if the pin is unused.The detect voltages are internally fixed 1.6V ~ 5.0V in increments of 100mV, using laser trimming technology. Six watchdog timeout period settings are available in a range from 6.25msec to 1.6sec. Seven release delay time 1 are available in a range from 3.13msec to 1.6sec.■APPLICATIONS●Microprocessor reset circuits●Memory battery backup circuits ●System power-on reset circuits ●Power failure detection■TYPICAL APPLICATION CIRCUIT* Not necessary with CMOS output products.■FEATURESDetect Voltage Range: 1.6V ~ 5.0V, +2% (100mV increments)Hysteresis Range : V DF x 5%, TYP .(XC6101~XC6107)V DF x 0.1%, TYP .(XC6111~XC6117)Operating Voltage Range : 1.0V ~ 6.0V Detect Voltage Temperature Characteristics : +100ppm/O C (TYP .) Output Configuration : N-channel open drain,CMOSWatchdog Pin : Watchdog inputIf watchdog input maintains ‘H’ or ‘L’ within the watchdog timeout period, a reset signal is output to the RESET output pinManual Reset Pin : When driven ‘H’ to ‘L’levelsignal, the MRB pin voltage asserts forced reset on theoutput pin.Release Delay Time : 1.6sec, 400msec, 200msec,100msec, 50msec, 25msec, 3.13msec (TYP .) can be selectable.Watchdog Timeout Period : 1.6sec, 400msec, 200msec,100msec, 50msec,6.25msec (TYP .) can be selectable.■TYPICAL PERFORMANCE CHARACTERISTICS ●Supply Current vs. Input Voltage* ‘x’ represents both ‘0’ and ‘1’. (ex. XC61x1⇒XC6101 and XC6111)2/26XC6101~XC6107, XC6111~XC6117 SeriesPIN NUMBERXC6101, XC6102 XC6103 XC6104, XC6105XC6106, XC6107XC6111, XC6112 XC6113 XC6114, XC6115XC6116, XC6117SOT-25 USP-6C SOT-25 USP-6C SOT-25 USP-6C SOT-25USP-6CPIN NAMEFUNCTION1 4 - - 1 4 1 4 R ESETB Reset Output(V DFL : Low Level When Detected)2 5 2 5 2 5 2 5 V SSGround3 2 3 2 - -4 1 M RB ManualReset 4 1 4 1 4 1 - - WDWatchdog5 6 5 6 5 6 5 6 V IN Power Input - - 1 4 3 2 3 2 RESETReset Output (V DFH: High Level When Detected)■PIN CONFIGURATION SOT-25 (TOP VIEW)MRBV IN WD RESETBV SSMRBWD RESETV SSV IN RESETWD RESETBV SS V IN SOT-25 (TOP VIEW)RESETMRB RESETBV SS V IN SOT-25 (TOP VIEW) ■PIN ASSIGNMENT●SOT-25XC6101, XC6102 SeriesXC6111, XC6112 SeriesSOT-25 (TOP VIEW)XC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 Series●USP-6CXC6101, XC6102 Series XC6111, XC6112 SeriesXC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 SeriesUSP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)* The dissipation pad for the USP-6C package should be solder-plated in recommended mount pattern and metal masking so as to enhance mounting strength and heat release. If the pad needs to be connected to other pins, it should be connected to the V SS pin.3/26XC6101 ~ XC6107, XC6111~ XC6117SeriesRESET OUTPUTSERIES WATCHDOGMANUAL RESET V DFL (RESETB)V DFH (RESET)XC6101 XC6111 Available Available CMOS - XC6102XC6112AvailableAvailableN-channel open drain-XC6103 XC6113 Available Available - CMOS XC6104 XC6114 Available Not AvailableCMOS CMOS XC6105 XC6115 Available Not Available N-channel open drain CMOS XC6106 XC6116 Not Available AvailableCMOSCMOS XC6107XC6117Not AvailableAvailableN-channel open drainCMOSDESIGNATORDESCRIPTIONSYMBOLDESCRIPTION0 : V DF x 5% (TYP .) with hysteresis ① Hysteresis Range1 : V DF x 0.1% (TYP .) without hysteresis② Functions and Type of Reset Output1 ~ 7: Watchdog and manual functions, and reset output type as per Selection Guide in the above chartA : 3.13msec (TYP .)B : 25msec (TYP .) C: 50msec (TYP .) D : 100msec (TYP .) E : 200msec (TYP .) F : 400msec (TYP .) ③ Release Delay Time * H : 1.6sec (TYP .)0 : No WD timeout period forXC6106, XC6107, XC6116, XC6117 Series 1: 6.25msec (TYP .) 2 : 50msec (TYP .) 3 : 100msec (TYP .) 4 : 200msec (TYP .) 5 : 400msec (TYP .) ④ Watchdog Timeout Period6: 1.6sec (TYP .) ⑤⑥ Detect Voltage 16 ~ 50: Detect voltageex.) 4.5V: ⑤⇒4, ⑥⇒5M : SOT-25 ⑦ Package E : USP-6C R : Embossed tape, standard feed ⑧ Device OrientationL: Embossed tape, reverse feed* Please set the release delay time shorter than or equal to the watchdog timeout period. ex.) XC6101D427MR or XC6101D327MR■PRODUCT CLASSIFICATION ●Selection Guide ●Ordering Information XC61①②③④⑤⑥⑦⑧4/26XC6101~XC6107, XC6111~XC6117 Series■PACKAGING INFORMATION●SOT-25●USP-6C5/26XC6101 ~ XC6107, XC6111~ XC6117Series④ Represents production lot number0 to 9 and A to Z and inverted 0 to 9 and A to Z repeated. (G, I, J, O, Q, W expected.) * ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)■MARKING RULE●SOT-25①②③④SOT-25 (TOP VIEW)6/26XC6101~XC6107, XC6111~XC6117 Series① Represents product series② Represents release delay time MARK RELEASE DELAY TIME PRODUCT SERIES A 3.13msec XC61XxAxxxxx B 25msec XC61XxBxxxxx C 50msec XC61XxCxxxxx D 100msec XC61XxDxxxxx E 200msec XC61XxExxxxx F 400msec XC61XxFxxxxx H 1.6sec XC61XxHxxxxx③ Represents watchdog timeout period MARK WATCHDOG TIMEOUT PERIOD PRODUCT SERIES 0 XC61X6, XC61X7 series XC61Xxx0xxxx 1 6.25msec XC61Xxx1xxxx 2 50msec XC61Xxx2xxxx 3 100msec XC61Xxx3xxxx 4 200msec XC61Xxx4xxxx 5 400msec XC61Xxx5xxxx 6 1.6sec XC61Xxx6xxxx④⑤ Represents detect voltage MARK④ ⑤DETECT VOLTAGE (V)PRODUCT SERIES3 3 3.3 XC61Xxxx33xx 5 0 5.0XC61Xxxx50xx⑥ Represents production lot number0 to 9 and A to Z repeated. (G, I, J, O, Q, W excepted.)* No character inversion used. ** ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)MARK PRODUCT SERIES MARK PRODUCT SERIES 3 XC6101xxxxxx 8 XC6111xxxxxx 4 XC6102xxxxxx 9 XC6112xxxxxx 5 XC6103xxxxxx A XC6113xxxxxx 6 XC6104xxxxxx B XC6114xxxxxx 7 XC6105xxxxxx C XC6115xxxxxx 3 XC6106xxxxxx 8 XC6116xxxxxx 4 XC6107xxxxxx 9 XC6117xxxxxx■MARKING RULE (Continued)●USP-6CUSP-6C (TOP VIEW)7/26XC6101 ~ XC6107, XC6111~ XC6117Series■BLOCK DIAGRAMS●XC6101, XC6111 Series●XC6102, XC6112 Series●XC6103, XC6113 Series8/26XC6101~XC6107, XC6111~XC6117 Series■BLOCK DIAGRAMS (Continued)●XC6107, XC6117 Series●XC6106, XC6116 Series●XC6105, XC6115 Series●XC6104, XC6114 Series9/26XC6101 ~ XC6107, XC6111~ XC6117SeriesPARAMETERSYMBOL RATINGSUNITSV INV SS -0.3 ~ 7.0 VM RBV SS -0.3 ~ V IN +0.3 VInput Voltage WD V SS -0.3 ~ 7.0V Output Current I OUT 20 mACMOS Output RESETB/RESET V SS -0.3 ~ V IN +0.3Output Voltage N-ch Open Drain Output RESETB V SS -0.3 ~ 7.0VSOT-25 250Power Dissipation USP-6C Pd 100mWOperational Temperature Range Topr -40 ~ +85 OCStorage Temperature Range Tstg -40 ~ +125 OC■ABSOLUTE MAXIMUM RATINGSTa = 25O C10/26XC6101~XC6107, XC6111~XC6117 SeriesNOTE:*1: XC6101~XC6107 (with hysteresis) *2: XC6111~XC6117 (without hysteresis)*3: ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111) *4: V DF(T): Setting detect voltage*5: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).PARAMETERSYMBOLCONDITIONSMIN.TYP .MAX. UNITS CIRCUITDetect Voltage V DFL V DFHV DF(T)× 0.98V DF(T) V DF(T)× 1.02 V 1 Hysteresis Range XC6101~XC6107 (*1) V HYS V DF × 0.02V DF × 0.05 V DF× 0.08 V 1Hysteresis Range XC6111~XC6117 (*2) V HYS 0 V DF × 0.001 V DFx 0.01V 1V IN =V DF(T)×0.9V - 5 11 V IN =V DF(T)×1.1V- 10 16 XC61X1/XC61X2/XC61X3XC61X4/XC61X5 (*3)(The MRB & the WD Pin: No connection) V IN =6.0V - 1218 V IN =V DF(T)×0.9V - 4 10 V IN =V DF(T)×1.1V - 8 14 Supply Current I SS XC61X6/XC61X7 (*3)(The MRB Pin: No connection)V IN = 6.0V - 1016 µA 2Operating Voltage V IN 1.0 - 6.0 V 1VIN = 1.0V 0.15 0.5 -V IN =2.0V (V DFL(T)> 2.0V) 2.0 2.5 - V IN =3.0V (V DFL(T) >3.0V) 3.0 3.5 -N-ch.V DS = 0.5V V IN =4.0V (V DFL(T) >4.0V) 3.5 4.0 - 3 V DFL Output Current (RESETB) I RBOUTCMOS,P-chV DS = 0.5V V IN = 6.0V - - 1.1 -0.8 mA 4 N-chV DS = 0.5VV IN =6.0V 4.4 4.9 - 3V IN =1.0V - - 0.08 - 0.02 V IN =2.0V (V DFH(T)> 2.0V)- - 0.50 - 0.30 V IN =3.0V (V DFH(T)>3.0V)- - 0.75 - 0.55V DFHOutput Current (RESET) I ROUT P-ch. V DS = 0.5V V IN =4.0V (V DFH(T)>4.0V)- - 0.95 - 0.75 mA 4Temperature Characteristics △V DF / △Topr ・V DF -40OC < Topr < 85 O C - +100 - ppm / O C12 3.13 5 13 25 3825 50 75 60 100 140 120 200 280 240 400 560Release Delay Time(V DF <1.8V)T DR Time until V IN is increased from1.0V to2.0Vand attains to the release time level,and the Reset output pin inverts.960 1600 2240 ms 5 2 3.13 5 13 25 38 25 50 7560 100 140 120 200 280 240 400 560 Release Delay Time(V DF >1.9V)T DRTime until V IN is increased from1.0V to (V DF x1.1V) and attains to the releasetime level,and the Reset output pin inverts. 960 1600 2240ms 5 Detect Delay Time T DFTime until V IN is decreased from 6.0V to 1.0V and attains to the detect voltage level, and the Reset output pin detectswhile the WD pin left opened.- 3 30 µs 5V DFL /V DFH CMOS Output Leak CurrentI LEAK V IN =6.0V, RESETB=6.0V (V DFL ) V IN =6.0V, RESET=0V (V DFH )- 0.01 - µA 3V DFL N-ch Open DrainOutput Leak CurrentI LEAKV IN =6.0V, RESETB=6.0V-0.010.10µA 3■ELECTRICAL CHARACTERISTICS●XC6101~XC6107, XC6111~XC6117 SeriesTa = 25O CSeriesPARAMETERSYMBOL CONDITIONS MIN.TYP . MAX. UNITS CIRCUIT3.13 6.25 9.38 25 50 7560 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF <1.8V)T WDTime until V IN increases form1.0V to2.0V andthe Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 3.13 6.25 9.38 25 50 75 60 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF >1.9V)T WDTime until V IN increases form1.0V to (V DF x1.1V)and the Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 WatchdogMinimum Pulse Width T WDIN V IN =6.0V,Apply pulse from 6.0V to 0Vto the WD pin. 300 - - ns 7 Watchdog High Level VoltageV WDH V IN =V DF x 1.1V ~ 6.0V V IN x 0.7- 6 V 7 Watchdog Low Level Voltage V WDL V IN =V DF x 1.1V ~ 6.0V0 - V IN x 0.3 V 7 V IN =6.0V, V WD =6.0V (Avg. when peak )- 12 19Watchdog Input Current I WD V IN =6.0V, V WD =0V (Avg. when peak) - 19 -12 -µA 8 Watchdog Input ResistanceR WDV IN =6.0V, V WD =0V, R WD =V IN / |I WD |315500880k Ω8PARAMETERSYMBOL CONDITIONS MIN.TYP . MAX.UNITS CIRCUITMRBHigh Level VoltageV MRH V IN =V DF x1.1V ~ 6.0V 1.4 - V IN 9MRBLow Level VoltageV MRL V IN =V DF x1.1V ~ 6.0V-0.35 V9MRBPull-up Resistance R MR V IN =6.0V, MRB=0V, R MR =V IN / |I MRB | 1.6 2.4 3.0 M Ω 10 MRB Minimum Pulse Width (*3) XC6101~XC6105 XC6111~XC6115 T MRINV IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin 2.8 - -MRB Minimum Pulse Width (*4) XC6106, XC6107 XC6116, XC6117T MRIN V IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin1.2 - -µs11●XC6101 ~ XC6103, XC6106 ~ XC6107, XC6111 ~ XC6113, XC6116 ~ XC6117 Series NOTE:*1: V DF(T): Setting detect voltage *2: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected). *3: Watchdog function is available. *4: Watchdog function is not available.Ta = 25O CTa = 25O C ■ELECTRICAL CHARACTERISTICS (Continued)●XC6101~XC6105, XC6111~XC6115 Series■OPERATIONAL EXPLANATIONThe XC6101~XC6107, XC6111~XC6117 series compare, using the error amplifier, the voltage of the internal voltage reference source with the voltage divided by R1, R2 and R3 connected to the V IN pin. The resulting output signal from the error amplifier activates the watchdog logic, manual reset logic, delay circuit and the output driver. When the V IN pin voltage gradually falls and finally reaches the detect voltage, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type ICs.<RESETB / RESET Pin Output Signal>* V DFL (RESETB) type - output signal: Low when detected.The RESETB pin output goes from high to low whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESETB pin remains low for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the RESETB pin output remains low for the release delay time (T DR), and thereafter the RESET pin outputs high level signal. * V DFH (RESET) type – output signal: High when detected.The RESET pin output goes from low to high whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESET pin remains high for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the V OUT pin output remains high for the release delay time (T DR), and thereafter the RESET pin outputs low level signal.<Hysteresis>When the internal comparator output is high, the NMOS transistor connected in parallel to R3 is turned ON, activating the hysteresis circuit. The difference between the release and detect voltages represents the hysteresis range, as shown by the following calculations:V DF (detect voltage) = (R1+R2+R3) x Vref(R2+R3)V DR (release voltage) = (R1+R2) x Vref(R2)V HYS (hysteresis range)=V DR-V DF (V)V DR > V DF* Detect voltage (V DF) includes conditions of both V DFL (low when detected) and V DFH (high when detected).* Please refer to the block diagrams for R1, R2, R3 and Vref.Hysteresis range is selectable from V DF x 0.05V (XC6101~XC6107) or V DF x 0.001V (XC6111~XC6117).<Watchdog (WD) Pin>The XC6101~XC6107, XC6111~XC6117 series use a watchdog timer to detect malfunction or “runaway” of the microprocessor. If neither rising nor falling signals are applied from the microprocessor within the watchdog timeout period, the RESETB/RESET pin output maintains the detection state for the release delay time (T DR), and thereafter the RESET/RESETB pin output returns to the release state (Please refer to the FUNCTION CHART). The timer in the watchdog is then restarted. Six watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 6.25msec.<MRB Pin>Using the MRB pin input, the RESET/RESETB pin signal can be forced to the detection state. When the MRB pin is driven from high to low, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type. Even after the MRB pin is driven back high, the RESET/RESETB pin output maintains the detection state for the release delay time (T DR). Since the MRB pin is internally pulled up to the V IN pin voltage level, leave the MRB pin open if unused (Please refer to the FUNCTION CHART). A diode, which is an input protection element, is connected between the MRB pin and V IN pin. Therefore, if the MRB pin is applied voltage that exceeds V IN, the current will flow to V IN through the diode. Please use this IC within the stated maximum ratings (V SS -0.3 ~ V IN+0.3) on the MRB pin.<Release Delay Time>Release delay time (T DR) is the time that elapses from when the V IN pin reaches the release voltage, or when the watchdog timeout period expires with no rising signal applied to the WD pin, until the RESET/RESETB pin output is released from the detection state. Seven release delay time (T DR) watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 25msec, 3.13msec.<Detect Delay Time>Detect Delay Time (T DF) is the time that elapses from when the V IN pin voltage falls to the detect voltage until the RESET/ RESETB pin output goes into the detection state.Series■TIMING CHARTS●CMOS Output●T DF (CMOS Output)VINVDFL LevelGNDVIN Level VDFL Level GNDVIN x 0.1V■NOTES ON USE1. Please use this IC within the stated maximum ratings. Operation beyond these limits may cause degrading or permanent damage to the device.2. When a resistor is connected between the V IN pin and the input, the V IN voltage drops while the IC is operating and a malfunction may occur as a result of the IC’s through current. For the CMOS output products, the V IN voltage drops while the IC is operating and malfunction may occur as a result of the IC’s output current. Please be careful with using the XC6111~XC6117 series (without hysteresis).3. In order to stabilize the IC’s operations, please ensure that the V IN pin’s input frequency’s rise and fall times are more than 1 µ sec/V.4. Noise at the power supply may cause a malfunction of the watchdog operation or the circuit. In such case, please strength the line between V IN and the GND pin and connect about 0.22µF of a capacitor between the V IN pin and the GND pin.5. Protecting against a malfunction while the watchdog time out period, an ignoring time (no reaction time) occurs to the rise and fall times. Referring to the figure below, the ignoring time (no reaction time) lasts for 900µsec at maximum.GNDGNDGNDVIN Pin Wave FormWD Pin Wave FormRESETB Pin Wave Form (VDFL)SeriesPIN NAMELOGIC CONDITIONSH V IN >V DF +V HYS V IN L V IN <V DF H MRB>1.40V MRBL MRB<0.35V H When keeping W D >V WDH more than T WD L When keeping W D <V WDL more than T WD L → H V WDL → V WDH , T WDIN >300nsec WDH → L V WDH →V WDH , T WDIN >300nsecV IN MRB WD RESETB (*2) H HH LRepeat detect and release (H →L →H)H OpenH L → HH H or Open H → L H HLL *1 LV IN MRB WD RESETB (*3) H HH LRepeat detect and release (L →H →L)H OpenH L → HH H or Open H → L L HLL *1 HV IN WD RESETB (*2) RESET (*3) H HH L Repeat detect and release (H →L →H)Repeat detect and release (L →H →L)H OpenH L → HH H → L H L HL*1 L HV IN MRB RESETB (*2)RESET (*3)H H or Open H LH LL L H■PIN LOGIC CONDITIONSNOTE:*1: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).*2: For the details of each parameter, please see the electrical characteristics. V DF : Detect VoltageV HYS : Hysteresis RangeV WDH : WD High Level Voltage V WDL: WD Low Level Voltage T WDIN : WD Pulse Width T WD : WD Timeout Period■FUNCTION CHART●XC6103/XC61113 Series●XC6104/XC61114, XC6105/XC6115 Series●XC6106/XC61116, XC6107/XC6117 Series●XC6101/XC61111, XC6102/6112 Series*1: Including all logic of WD (WD=H, L, L →H, H →L, OPEN). *2: When the RESETB is High, the circuit is in the release state. When the RESETB is Low, the circuit is in the detection state. *3: When the RESET is High, the circuit is in the release state. When the RESET is Low, the circuit is in the detection state.■TEST CIRCUITSCircuit 1Circuit 2Circuit 3Circuit 4Series ■TEST CIRCUITS (Continued)Circuit 5Circuit 6Circuit 7■TEST CIRCUITS (Continued)Circuit 8Circuit 9Circuit 10Circuit 11Series■TYPICAL PERFORMANCE CHARACTERISTICS(1.1) Supply Current vs. Input Voltage(1.2) Supply Current vs. Input Voltage■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(2) Detect, Release Voltage vs. Ambient Temperature(1.2) Supply Current vs. Input Voltage (Continued)Series■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (3-1) Output Voltage vs. Input Voltage (V DFL ) (3.1) Detect, Release Voltage vs. Input Voltage (V DFL )(3.2) Detect, Release Voltage vs. Input Voltage (V DFH )■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(4) N-ch Driver Output Current vs. V DSSeries(6) P-ch Driver Output Current vs. Input Voltage 1■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(8) Release Delay Time vs. Ambient Temperature(7) P-ch Driver Output Current vs. Input Voltage 2■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (10) Release Delay Time vs. Input Voltage(11) Watchdog Timeout Period vs. Input VoltageSeries■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(14) MRB Low Level Voltage vs. Ambient Temperature(15) MRB High Level Voltage vs. Ambient Temperature* ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。