FPGA和单片机串行通信接口的实现

最新fpga实现串行接口 rs232资料讲解

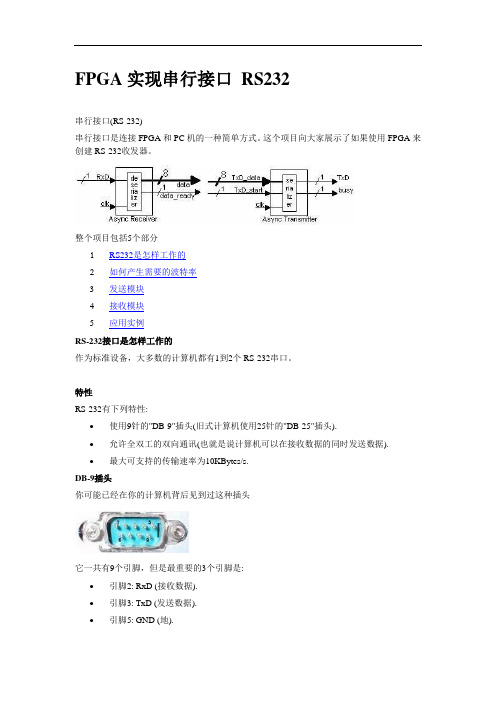

FPGA实现串行接口RS232串行接口(RS-232)串行接口是连接FPGA和PC机的一种简单方式。

这个项目向大家展示了如果使用FPGA来创建RS-232收发器。

整个项目包括5个部分1RS232是怎样工作的2如何产生需要的波特率3发送模块4接收模块5应用实例RS-232接口是怎样工作的作为标准设备,大多数的计算机都有1到2个RS-232串口。

特性RS-232有下列特性:•使用9针的"DB-9"插头(旧式计算机使用25针的"DB-25"插头).•允许全双工的双向通讯(也就是说计算机可以在接收数据的同时发送数据).•最大可支持的传输速率为10KBytes/s.DB-9插头你可能已经在你的计算机背后见到过这种插头它一共有9个引脚,但是最重要的3个引脚是:•引脚2: RxD (接收数据).•引脚3: TxD (发送数据).•引脚5: GND (地).仅使用3跟电缆,你就可以发送和接收数据.串行通讯数据以每次一位的方式传输;每条线用来传输一个方向的数据。

由于计算机通常至少需要若干位数据,因此数据在发送之前先“串行化”。

通常是以8位数据为1组的。

先发送最低有效位,最后发送最高有效位。

异步通讯RS-232使用异步通讯协议。

也就是说数据的传输没有时钟信号。

接收端必须有某种方式,使之与接收数据同步。

对于RS-232来说,是这样处理的:6串行线缆的两端事先约定好串行传输的参数(传输速度、传输格式等)7当没有数据传输的时候,发送端向数据线上发送"1"8每传输一个字节之前,发送端先发送一个"0"来表示传输已经开始。

这样接收端便可以知道有数据到来了。

9开始传输后,数据以约定的速度和格式传输,所以接收端可以与之同步10每次传输完成一个字节之后,都在其后发送一个停止位("1")让我们来看看0x55是如何传输的:0x55的二进制表示为:01010101。

单片机 串口通信原理

单片机串口通信原理

单片机串口通信是指通过串行口进行数据的传输和接收。

串口通信原理是利用串行通信协议,将数据按照一定的格式进行传输和接收。

在单片机中,串口通信一般是通过UART(通用异步收发传输器)模块来实现的。

UART模块包括发送和接收两部分。

发送部分将数据从高位到低位逐位发送,接收部分则是将接收到的数据重新组装成完整的数据。

串口通信的原理是利用串行通信协议将发送的数据进行分帧传输。

在传输的过程中,数据被分成一个个的数据帧,每帧包括起始位、数据位、校验位和停止位。

起始位和停止位用于标识数据的开始和结束,数据位则是用来存放需要传输的数据。

校验位用于校验数据的正确性。

在发送端,单片机将需要发送的数据按照一定的格式组装成数据帧,然后通过UART发送出去。

在接收端,UART接收到的数据也是按照数据帧的格式进行解析,然后重新组装成完整的数据。

通过这样的方式,发送端和接收端可以进行数据的传输和接收。

串口通信具有简单、可靠性高、适应性强等优点,广泛应用于各种领域,如物联网、嵌入式系统等。

掌握串口通信原理对于单片机的应用开发具有重要意义。

cpld和单片机接口

优点:

强大的信息(数据)处理、逻辑 分析、决策判断等能力; 体积小、性价比高、功能灵活、 可靠性高、易于人机对话。

CPLD/FPGA

优点:

用户可自定制逻辑,在线可编程, 开发便捷。 信号传输效率高,适合高速采样 场合; 可以加密,抗干扰能力强,功耗 低,可靠性高;

缺点:

低速;

缺点:

一般只能实现数字逻辑;

程序实现: 1)单片机部分

#define CPLD ADDRESS 0x0000 #include <absacc. h> main() { unsigned charA DDRESSIndex; //CPLD某个功能部件的地址 unsigned char DATA_READ,DATA_WRITE; XBYTE [CPLD_ADDRESS+ADDRESSIndex]=DATA_WRITE;//单片机向 CPLD写数据 DATA_READ=XBYTE[CPLD_ADDRESS+ADDRESSIndex]; // 单片机从 CPLD读数据 }

系统硬件构成框图:

图4 系统组成框图

CPLD与单片机及键盘、显示器的接口:

图5

键盘、显示器与CPLD及单片机的接口

打印机与CPLD及单片机的接口:

INT1

P0 WR RD CPLD

BUSY

Data1~7 8031

STROBE

图6

打印机与CPLD及单片机的接口

程序设计:

下位机负责数据的采集、抽样和发送。为了保证数据采集的 实时性,下位机在未收到上位机指令时,内部轮流对8路模拟 信号进行采集和变换,并存入缓冲存储器中。 上位机负责数据的接收、处理和打印。上 位机 发 送完指令 后,立即转人接收状态,等待从远端下位机回送两个字节的数 据,如果在规定的时间内未收到数据,或者是收到的数据中两 个字节不一致,则说明通讯线路有错误,不能接收该数据,故 重新发送一次指令,如果重发3次都未成功,则发出出错报替 信号,提醒用户检查线路或设备。否则,上位机对收到的有效 数据进行处理,将数值大小为0~255之间的数据转换为0^-5 V 的电压值,并进行显示。同时还要扫描键盘,处理各种功能键, 完成用户的功能要求。 CPLD主要完成接收单片机发送来的数据并控制4个LED数码管 显示相应的数码,同时控制打印机将上位机处理的结果打印输 出。

FPGA和51单片机通信接口的设计

FPGA和51单片机通信接口的设计作者:刘宇成李金凤来源:《卷宗》2015年第10期摘要:虽然FPGA速度快,但由于FPGA对采集到的数据的处理能力和控制能力比较差,故需要将其采集到的数据送到单片机系统上来实现数据的处理功能,这就使得FPGA系统与单片机系统之间的数据通信提到日程上。

本文给出部分VHDL源程序,并用Quartus II进行仿真。

关键词:FPGA;VHDL;单片机;通信单片机具有性价比高、功能灵活、易于人机对话、良好的数据处理能力的特点;FPGA则具有高速、可靠以及开发便捷等优点。

系统设计中将单片机数据处理的优势与FPGA、执行快速的特点相结合,能够设计出既有强大控制功能又能使各项功能快速执行的系统。

因此,单片机与FPGA之间的通信便显得尤为重要本文介绍利用VHDL语言实现FPGA与单片机的并行通信接口设计。

本文主要由以下三个部分组成:FPGA接收ADC0809数据;FPGA发送数据和单片机接收数据模块,VHDL程序及仿真结果。

本文着重对FPGA数据发送模块实现进行说明,原理图如图1所示:1 FPGA接收ADC0809数据ADC0809是美国国家半导体公司生产的CMOS工艺8通道,8位逐次逼近式A/D模数转换器。

其内部有一个8通道多路开关,它可以根据地址码锁存译码后的信号,只选通8路模拟输入信号中的一个进行A/D转换。

本系统用ADC0809把传感器采集的模拟信号变成数字信号,然后用FPGA控制数据流进程,并用外围LED电路显示。

FPGA与ADC0809接口电路图如图2所示。

为了实现对ADC0809精确地控制,所以本系统采用FPGA特有的状态机来进行时序上的控制,引脚说明如下:(1)ALE信号(引脚):高电平时把三个地址信号送入地址锁存器,并经译码器得到地址数据,以选择相应的模拟输入通道。

(2)OE信号(引脚)EN使能信号:电平由低变高时,打开数据输出锁存器,将转换数据送到数据总线上。

基于FPGA的高速串行数据收发接口设计

基于FPGA的高速串行数据收发接口设计随着信息技术的不断发展,高速串行数据收发接口已经成为许多应用领域中的关键技术。

而基于FPGA的高速串行数据收发接口设计,可以充分发挥FPGA的并行计算和可编程性优势,实现高速数据传输和处理。

本文将介绍基于FPGA的高速串行数据收发接口的设计原理、关键技术和应用。

一、设计原理在高速串行数据收发接口中,主要涉及到以下几个方面的技术:物理接口、时钟同步、帧同步、数据编码和解码、差分信号传输等。

1.物理接口物理接口是指FPGA与外部设备之间进行数据传输的接口。

常见的物理接口包括LVDS、USB、PCIe等。

在设计中,需要选择合适的物理接口,并实现与FPGA之间的连接。

2.时钟同步时钟同步是指接收端与发送端的时钟信号保持同步,以确保数据的准确传输。

常见的时钟同步技术包括PLL锁相环、FIFO缓存等。

在设计中,需要使用适当的时钟同步技术,保证数据的稳定传输。

3.帧同步帧同步是指接收端能够正确识别数据帧的起始和结束标志,以及数据帧中的各个字段。

在设计中,通过使用标志位或者特定的编码格式,可以实现帧同步,保证数据的正确接收和解析。

4.数据编码和解码数据编码和解码是指将要传输的数据进行编码,以提高传输速率和抗干扰能力。

常见的数据编码和解码算法包括差分编码、曼彻斯特编码、8b/10b编码等。

在设计中,需要根据具体的应用需求,选择合适的数据编码和解码算法。

5.差分信号传输差分信号传输是指将发送端的信号分为正负两路进行传输,以提高传输速率和抗干扰能力。

差分信号传输可以有效抑制共模干扰和噪声,提高信号的可靠传输。

二、关键技术在基于FPGA的高速串行数据收发接口设计中,需要关注以下几个关键技术。

1.时钟和数据恢复由于传输中的时钟和数据可能存在相位偏移和抖动等问题,因此需要使用时钟和数据恢复技术来保持时钟的稳定,并将数据恢复到正确的状态。

2.信号完整性由于传输线上会存在反射、串扰等问题,需要采取合适的电路设计和布线策略,以提高信号的抗干扰能力和抗噪声能力,保证数据的可靠传输。

基于FPGA串行收发器的通信接口设计与实现

基于 FPGA串行收发器的通信接口设计与实现摘要:随着信号处理带宽和吞吐量的需求与日俱增,多片FPGA协同工作成为一种发展趋势。

FPGA片间通信必然成为一个研究热点,特别是不同厂商FPGA间的通信。

基于FPGA串行收发器,利用8B/10B编码,实现了链路同步、数据收发以及流量控制。

通过板间验证表明:该设计与实现的通信接口稳定可靠,单对收发器通信速率可达10Gbps,并且可进行多路扩展应用,可应用于40G、100G等高速通信。

关键词:FPGA;8B/10B编码;高速收发器DESIGN AND INPLEMENTATION OF COMMUNICATION INTERFACE BASE ON FPGA SERIAL TRANSCEIVERYe Yun-feng, Ren Ji-kui, Huang rui, Yuan jun(No.30 Institute of CETC, Chengdu Sichuan 610041, China)Abstract:With the demand of signal processing bandwidth and throughput increases, multi-chip FPGA cooperative work becomes a trend. FPGA inter-chip communication must become a research hotspot,especially the communication between different FPGA of manufacturers. On the basis of FPGA serial transceiver, the link synchronization,data sending and receiving and traffic control are realized by using8B/10B coding. The inter-board verification shows that the communication interface is stable and reliable, the communication rate of single pair transceiver can reach 10Gbps, and can be applied tohigh speed communication such as 40Gbps or 100Gbps.Key words:FPGA; 8B/10B code; High-speed transceiver0 引言随着云计算与大数据技术的发展,用户对信息传输的需求不断增长,基带信号处理的带宽和吞吐量需求与日俱增[1]。

FPGA_8051_UART串行通信

多数示例提供完整源程序

KX2C5F+系统提供的大量电子设计自主创新演示项目于宽领域大深度培养能力、启迪智慧、激励创新

杭州康芯公司

实验4

8052 IP核UART串口应用和CPU与硬件频率计联合设计

多路选择器

输出数据接P1口的低4位数字频率计

频率计采样控制时钟

频率计待测信号输入口

锁存器,数据在开发板的LEDB 数码管显示

锁存器,数据在开发板的LEDA 数码管显示锁存器,数据在开发板的LEDC 数码管显示

显示译码器频率计信号采样控制模块

32位计数器32位锁存器

单片机IP核+内部RAM+内部程序ROM+频率计采样电路+RS232通信控制

待测频率信号:1Hz —200MHz

CycloneII FPGA SOC设计

I/O口

PC机显示频率数据

RS232串行通信

FPGA中51单片机核的工作程序

注意程序路径

下载文件

串行通信口连接PC机

黑线接地

棕线接RX,接P71

红线接TX,接P75

来自PC机的数据“123”,

检测双向通信功能

黑线接地

红线接TX,接P75

棕线接RX,接P71

锁存器VHDL描述

多路选择器VHDL描述译码器VHDL描述

频率计信号采样控制模块32位计数器

32位锁存器

键入3为16进制数据

按此键接受来自FPGA的数据

按此键向FPGA发送数据

UART串行通信测试程序加频率计文件

下载此程序,测试频率计功能

单纯UART串行通信测试程序

测得频率:32768Hz 键入数据

按此纽,向KX_7C板传送数据”ABC”按此纽,将KX_7C板测得的频率显示。

FPGA和单片机串行通信接口的实现

FPGA和单片机串行通信接口的实现FPGA(Field-Programmable Gate Array)和单片机(Microcontroller)是两种常用的数字电子设备,它们在串行通信接口方面有不同的实现方式。

首先,我们需要了解串行通信是一种将数据以位的形式逐个传输的通信方式。

常见的串行通信协议包括UART(Universal Asynchronous Receiver/Transmitter)、SPI(Serial Peripheral Interface)和I2C (Inter-Integrated Circuit)等。

对于FPGA和单片机之间的串行通信,我们可以基于以下几种方式进行实现:1. UART:UART是一种常见的串行通信协议,可以实现全双工的通信。

在FPGA和单片机之间建立UART通信,需要在FPGA中实现UART模块,并将其与单片机的UART接口连接。

在FPGA中,我们可以使用硬件语言(如Verilog或VHDL)来实现UART模块,该模块负责将FPGA内部的数据通过UART协议进行封装和解封装。

单片机与FPGA之间通过TX(发送)和RX (接收)引脚建立连接。

单片机可以通过串口发送数据给FPGA,FPGA接收到数据后进行处理,然后再通过串口将处理后的数据发送给单片机。

2.SPI:SPI是一种用于片上外设之间通信的串行通信协议,常用于FPGA与外部设备(例如传感器、显示器等)之间的通信。

在FPGA和单片机之间建立SPI通信,需要在FPGA中实现SPI控制器,并将其与单片机的SPI接口连接。

FPGA通过把数据写入SPI发送缓冲区或从SPI接收缓冲区读取数据来实现与单片机的通信。

单片机通过控制SPI接口的时钟、数据和使能信号来与FPGA进行数据传输。

3.I2C:I2C是一种双线制串行总线,常用于连接多个设备的系统,例如FPGA、单片机和其他外部设备之间的通信。

在FPGA和单片机之间建立I2C通信,需要在FPGA中实现I2C控制器,并将其与单片机的I2C接口连接。

8051单片机的FPGA设计与实现

第一章前言20世纪末在计算机技术逐渐发展的情况写,电子技术得到了飞速的发展,现代电子产品已经渗透到了社会的各个领域,有力的推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品的性能进一步提高,产品更新换代的节奏也越来越快。

电子技术发展的根基是微电子技术的进步,它表现在大规模集成电路加工技术,即半导体工艺技术的发展上,表征半导体工艺水平的线宽已经达到60nm以下,并还在不断缩小;在硅片单位面积上集成了更多的晶体管,集成电路设计在不断地向超大规模,极低功耗和超高速的方向发展;专用集成电路ASIC (Application Specific Integrated Circuit)的设计成本不断降低,在功能上,现代的集成电路已能够实现单片电子系统SOC(System on a chip)的功能。

另外集成电路(IC)技术在微电子领域中占有重要的地位。

且伴随着IC技术的发展,电子设计自动(Electronic Design Automation,EDA)已经逐渐成为重要的设计手段,其广泛应用于模拟与数字电路系统等许多领域。

单片机是一种集成电路芯片,是采用超大规模集成电路技术把具有数据处理能力中央处理器CPU、随机存储器RAM、只读存储器ROM、多种I/O口和中断系统、定时器/计时器等功能(可能还包括显示驱动电路、脉宽调制电路、模拟多路转换器、A/D转换器等电路)集成到一块硅片上构成的一个小而完善的微型计算机系统,在工业控制领域的广泛应用。

从上世纪80年代,由当时的4位、8位单片机,发展到现在的32位300M的高速单片机。

单片机具有体积小、功耗低、控制功能强、扩展灵活、微型化和使用方便等优点,广泛应用于仪器仪表中,结合不同类型的传感器,可实现诸如电压、电流、功率、频率、湿度、温度、流量、速度、厚度、角度、长度、硬度、元素、压力等物理量的测量。

采用单片机控制使得仪器仪表数字化、智能化、微型化,且功能比起采用电子或数字电路更加强大。

FPGA实现串口通信

FPGA实现串口通信UART接收。

因为只有数据线,没有时钟,这种叫异步通信。

首先双方必须约定好通信用的时钟频率,但是双方用的时钟必定有误差,而且不知道每个bit的起始时间。

这两点是造成你有时候收到对的,有时候收到错的原因。

所以必须要用高倍的时钟来采样,一般用8倍、16倍。

仅仅简单实现的话,用8倍举例,如果另一块板子(或PC)发过来的是数据,发送一个bit用的时钟频率是115200Hz的话,那么自己板子上要先产生一个115200x 8 = 921600Hz 的内部时钟。

用这个时钟对收到的串行数据进行采样,理论上讲,每个bit可以得到7-8个采样点。

如果FPGA晶振是50000000Hz(50MHz),则54.25分频得到921600Hz。

分频模块library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_arith.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity Clk_DIV isport (clk : in std_logic;CLK_O : out std_logic );end Clk_DIV;architecture Clk_DIV_arch of Clk_DIV issignal clk1,clk2 : std_logic;signal s1,s2 : integer range 0 to 53;beginprocess(clk)beginif rising_edge(clk) thenif s1 < 53 thens1<= s1+1;elses1<=0;end if;if s1 < 28 thenclk1 <= '1';elseclk1 <= '0';end if;end if;end process;process(clk)beginif falling_edge(clk) thenif s2 < 53 thens2<= s2+1;elses2<=0;end if;if s2 < 28 thenclk2 <= '1';elseclk2 <= '0';end if;end if;end process;CLK_O <=clk1 or clk2;end Clk_DIV_arch;接下来第一步就是找起始bit,如果连采3次(或4次)都是0的话,说明找到起始bit 了,并且当前采样点大概在这个bit的中间了。

FPGA和单片机串行通信接口的实现

FPGA和单片机串行通信接口的实现[ 作者: 加入时间:2006-10-28 15:31:42 来自: ]摘要:本文针对由FPGA构成的高速数据采集系统数据处理能力弱的问题,提出FPGA与单片机实现数据串行通信的解决方案。

在通信过程中完全遵守RS232协议,具有较强的通用性和推广价值。

关键词:FPGA;单片机;串行通信;RS2321 前言现场可编程逻辑器件(FPGA)在高速采集系统中的应用越来越广,由于FPGA对采集到的数据的处理能力比较差,故需要将其采集到的数据送到其他CPU系统来实现数据的处理功能,这就使FPGA系统与其他CPU系统之间的数据通信提到日程上,得到人们的急切关注。

本文介绍利用VHDL语言实现 FPGA 与单片机的串口异步通信电路。

整个设计采用模块化的设计思想,可分为四个模块:FPGA数据发送模块,FPGA波特率发生控制模块,FPGA总体接口模块以及单片机数据接收模块。

本文着重对FPGA数据发送模块实现进行说明。

2 FPGA数据发送模块的设计根据RS232 异步串行通信来的帧格式,在FPGA 发送模块胁捎玫拿恳恢「袷轿?位开始位+8位数据位+1位奇校验位+1位停止位,波特率为2400。

本系统设计的是将一个16位的数据封装成高位帧和低位帧两个帧进行发送,先发送低位帧,再发送高位帧,在传输数据时,加上文件头和数据长度,文件头用555555来表示,只有单片机收到555555时,才将下面传输的数据长度和数据位进行接收,并进行奇校验位的检验,正确就对收到的数据进行存储处理功能,数据长度可以根据需要任意改变。

由设置的波特率可以算出分频系数,具体算法为分频系数X=CLK/(BOUND*2)。

可由此式算出所需的任意波特率。

下面是实现上述功能的VHDL源程序。

Library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity atel2_bin isport( txclk: in std_logic; --2400Hz的波特率时钟 reset: in std_logic; --复位信号 din: in std_logic_vector(15 downto 0); --发送的数据start: in std_logic; --允许传输信号 sout: out std_logic --串行输出端口 );end atel2_bin;architecture behav of atel2_bin issignal thr,len: std_logic_vector(15 downto 0);signal txcnt_r: std_logic_vector(2 downto 0);signal sout1: std_logic;signal cou: integer:=0;signal oddb:std_logic;type s is(start1,start2,shift1,shift2,odd1,odd2,stop1,stop2);signal state:s:=start1;beginprocess(txclk)beginif rising_edge(txclk) thenif cou<3 then thr<="0000000001010101"; --发送的文件头elsif cou=3 thenthr<="0000000000000010"; --发送的文件长度elsif (cou>3 and state=stop2) then thr<=din;--发送的数据end if;end if;end process;process(reset,txclk)variable tsr,tsr1,oddb1,oddb2: std_logic_vector(7 downto 0);beginif reset="1" thentxcnt_r<=(others=>"0");sout1<="1";state<=start1;cou<=0;elsif txclk"event and txclk="1" thencase state iswhen start1=>if start="1" thenif cou=3 thenlen<=thr;end if;tsr:=thr(7 downto 0);oddb1:=thr(7 downto 0);sout1<="0"; --起始位txcnt_r<=(others=>"0");state<=shift1;elsestate<=start1;end if;when shift1=>oddb<=oddb1(7) xor oddb1(6) xor oddb1(5) xor oddb1(4) xor oddb1(3) xor oddb1(2) xor oddb1(1) xor oddb1(0);sout1<=tsr(0); --数据位tsr(6 downto 0):=tsr(7 downto 1);tsr(7):="0";txcnt_r<=txcnt_r+1;if (txcnt_r=7) thenstate<=odd1;cou<=cou+1;end if;when odd1=> --奇校验位if oddb="1" thensout1<="0";state<=stop1;elsesout1<="1";state<=stop1;end if;when stop1=>sout1<="1"; --停止位if cou<4 thenstate<=start1;elsestate<=start2;end if;when start2=>tsr1:=thr(15 downto 8);oddb2:=thr(15 downto 8);sout1<="0"; --起始位txcnt_r<=(others=>"0");state<=shift2;when shift2=>oddb<=oddb2(7) xor oddb2(6) xor oddb2(5) xor oddb2(4) xor oddb2(3) xor oddb2(2) xor oddb2(1) xor oddb2(0);sout1<=tsr1(0);--数据位tsr1(6 downto 0):=tsr1(7 downto 1);tsr1(7):="0";txcnt_r<=txcnt_r+1;if (txcnt_r=7) thenstate<=odd2;end if;when odd2=> --奇校验位if oddb="1" thensout1<="0";state<=stop2;elsesout1<="1";state<=stop2;end if;when stop2=>sout1<="1"; --停止位if len="0000000000000000" thenstate<=stop2;elsestate<=start1;len<=len-1;end if;end case;end if;end process;sout<=sout1;end behav;其中各信号的说明已在程序中标明了。

单片机与FPGA通信

MCS-51单片机与FPGA接口逻辑设计的VHDL实现付扬(辽宁石油化工大学信息工程学院抚顺,113001)摘要:本文阐述了单片机和现场可编程门阵列FPGA各自的特点,指出在波形发生器设计中两者相结合设计的优势和在设计中所遇到的接口逻辑设计这个难点,详细给出了接口逻辑设计的VHDL程序。

通过该接口程序设计,实现了单片机技术和EDA技术相结合,从而实现了所要求波形发生器的设计。

关键词:单片机FPGA(现场可编程门阵列)PLD(可编程逻辑器件)0引言可编程逻辑器件(PLD)及EDA技术的应用成为电子系统设计的潮流。

FPGA 是一种新兴的可编程逻辑器件(PLD),与其它PLD相比,具有更高的密度、更快的工作速度和更大的编程灵活性。

单片机以其体积小、功能齐全、价格低廉、可靠性高等方面所具有的独特优点,长期以来被广泛的应用在各领域。

基于FPGA的高密度、高速度、现场可编程的能力和单片机强大的数据处理功能,制作了波形发生系统,用于产生各种频率的正弦波、方波和三角波,其幅值0~5V可调,频率步进达到1Hz以下,频率范围1Hz~100kHz。

该波形发生器以单片机(MCS8031)为中心控制系统,FPGA片内实现DDS技PROM28c64术,在此DDS技术中,采用6级BCD比例乘法器级联。

首先由单片机将E2中存入波形数据。

FPGA在单片机的控制下,利用较高的时钟频率(16M)生成用户要求的频率的128倍频,并以此频率在EPROM28c64取波形数据,将其发送给2D/A转换器,并通过滤波器输出。

同时单片机实现对输出电压的控制。

本设计中,FPGA选用Altera公司的FLEX10K,晶振频率可达40MHz。

使用MAX+PLUSⅡ开发系统支持。

FLEX10K系列是FLEX系列当中非常有代表性的FPGA 器件系列,每个FLEX10K器件包含一个嵌入式阵列和一个逻辑阵列。

嵌入式阵列用来实现各种存储器及复杂的逻辑功能。

逻辑阵列用来实现普通逻辑功能。

基于FPGA的串口通信电路设计

基于FPGA的串口通信电路设计[摘要]串行通信接口是一种应用广泛的通信接口。

目前,大部分处理器都集成了支持rs-232接口的通用异步收发器,本文基于fpga开发板设计了一个串口数据采集和处理程序,介绍了用verilog hdl硬件描述语言来开发波特率发生器、接收模块和发送模块这三个模块,以及系统各个模块的具体设计方法和原理,用quartus ii软件进行仿真并给出结果,分别验证各个模块的正确性及用fpga实现串行通信的可行性。

[关键词]串行通信 rs-232 verilog hdl fpga中图分类号:tn 文献标识码:a 文章编号:1009-914x(2013)08-320-011.fpga概述fpga现场可编程逻辑门阵列是数字系统设计的主要硬件平台,其主要特点是完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写。

fpga具有运算速度快、根据需求在内部嵌入硬/软ip核,以及反复编程,擦写,使用的特点,被广泛应用于通信,数字信号处理,工业控制等领域。

2.rs232串口通信接口串口即串行数据接口主要用于网管控制或主业务数据的传输,支持数据的双向传输,速率9600-115200bps,即可以完成和pc的通信,也可以完成与带有标准串口的外设相连。

其中串口接口分为带插孔和带插针的两种,其中插针端称为dce,插孔端称为dte。

3.串口通信的verilog hdl实现本设计要求在fpga开发板上实现波特率为115200bps,停止位为1比特、1比特校验位的串口通信,并要求和pc机通过串口调试助手完成双向通信。

3.1波特率发生器模块的verilog hdl实现波特率发生器实际上是一个分频器,从给定的系统时钟频率得到要求的波特率。

一般来讲,为了提高系统的容错性处理,要求波特率发生器的输出时钟为实际串口数据波特率的n倍,n可以取值为8、16、32、64等。

在本设计中,系统的时钟为50mhz,取n为16,则分频系数为50000000/(16*115200)=27.127,取整为27。

fpga与单片机接口

51单片机加CPLD让系统更高效来源:本站整理作者:秩名2012年02月29日 11:23分享[导读]单片机市场可以用巨无霸来形容,其中51 单片机使用者就更多了,针对51 单片机无需更多的介绍,这里必须强调一点,只要你精通了51 单片机,以后在实际工作中选用其它单片机也很容关键词:51单片机CPLD单片机 一、引言 单片机市场可以用巨无霸来形容,其中51 单片机使用者就更多了,针对51 单片机无需更多的介绍,这里必须强调一点,只要你精通了51 单片机,以后在实际工作中选用其它单片机也很容易了,这就是初学者学习51 单片机的价值。

选择51 单片机学习入门容易,倒不是说51 系列单片机比别的型号简单,其实在8 位单片机家族中,51 系列单片机算是复杂的,但51 单片机在中国推广最彻底,教程也是最丰富,基本不用看英文资料就能学好,所以特别适合初学者学习用。

下面说说CPLD,从近来跟学生和爱好者交往中发现,初学者都很“讨厌”它,问我为什么要把单片机和CPLD 放一块儿,那样不是增加了学习的难度吗?其实深入学习单片机后,你就会发现,单独一片单片机芯片,实在是不够用,稍微复杂的系统都会缺少接口资源,IO 口不够用。

我们学单片机不能仅仅局限于LED(发光二极管,数码管等)驱动,输入还需要键盘、ADC,输出需要LCD、DAC 等,当把这些对象同时放在一个系统当中时,就需要用到很多其它分离的接口IC(芯片),各种逻辑IC。

学完单片机后大家都会知道这些芯片:如74373,7432,74138……随着数字电子技术的发展,一种新的器件正在被广泛应用,那就是CPLD(ComplexProgrammable Logic Device)复杂可编程逻辑器件,通俗的说就是可以把以上那些分离器件都放进去的一种可以二次开发的IC.关于CPLD 的详细介绍大家可以自己在网上浏览,很多很多。

基于此,本刊用这篇文章深入浅出的介绍一种采用51 单片机和CPLD 构建复杂电路系统的设计思想。

FPGA与51串口通信

宜宾学院(物理与电子工程学院论文设计)FPGA与51串口通信设计专业:电子信息科学与技术学生姓名: XXX 学生学号: XXXXXXXXX 院系:物理与电子工程学院班级: XXXXX 指导教师: XX2014年6月18日摘要 (1)第一章引言 (2)第二章设计要求 (3)第三章设计方案 (4)第四章仿真结果 (5)第五章总结 (6)第六章参考文献 (7)附录1 (8)本设计介绍了AT89C51单片机与FPGA之间进行简单的串口通信中FPGA部分。

FPGA从AT89C51单片机接收数据之后,再发送出去。

关键词: AT89C51单片机、FPGA、串口通信第一章引言单片机均内含异步串行通信口,如AT89C51单片机内为UART(即Universal Asynchronous Receiver Transmitter 通用异步收发器),可实现全双工串行通信,其串行通信非常方便。

FPGA发展十分迅速,集成度不断提高,可以完成很多复杂的功能,在其完成各种功能的同时,完全可以将串行通信接口构建于其中。

这样,FPGA与单片机的串行通信就变得极其方便。

第二章设计要求本设计只设计FPGA接收与发送部分。

当接收到接收信号时,FPGA从单片机P0与P2口接收数据,有地址锁存信号对其锁存。

当地址为7F00H时,锁存地址,并等待WR口下降沿到来。

当WR下降沿到来时,读P0口数据进行锁存,开始准备发送。

当接收发发送信号时,来一个时钟上升沿就对数据输出一位,直到8位数据全部输出,则FPGA又开始接收数据。

第三章 设计方案本设计采用AT89C51单片机与FPGA 进行串口通信,系统总程序框架如图3-1:图3-1 总程序框架实验程序代码见附录1初始化定义端口 是否锁存地址11是发送数据锁存数据判断握手信号是否发送完数是否否第四章仿真结果仿真结果结果如图4-1、图4-2所示:图4-1 串口通信仿真结果图4-2 串口通信仿真结果第五章总结该设计结果与预期结果一致,可以实现FPGA连续从单片机中接收与发送数据。

FPGA实现串行接口-RS232

FPGA实现串行接口 RS232串行接口(RS-232)串行接口是连接FPGA和PC机的一种简单方式。

这个项目向大家展示了如果使用FPGA来创建RS-232收发器。

整个项目包括5个部分1RS232是怎样工作的2如何产生需要的波特率3发送模块4接收模块5应用实例RS-232接口是怎样工作的作为标准设备,大多数的计算机都有1到2个RS-232串口。

特性RS-232有下列特性:•使用9针的"DB-9"插头(旧式计算机使用25针的"DB-25"插头).•允许全双工的双向通讯(也就是说计算机可以在接收数据的同时发送数据).•最大可支持的传输速率为10KBytes/s.DB-9插头你可能已经在你的计算机背后见到过这种插头它一共有9个引脚,但是最重要的3个引脚是:•引脚2: RxD (接收数据).•引脚3: TxD (发送数据).•引脚5: GND (地).仅使用3跟电缆,你就可以发送和接收数据.串行通讯数据以每次一位的方式传输;每条线用来传输一个方向的数据。

由于计算机通常至少需要若干位数据,因此数据在发送之前先“串行化”。

通常是以8位数据为1组的。

先发送最低有效位,最后发送最高有效位。

异步通讯RS-232使用异步通讯协议。

也就是说数据的传输没有时钟信号。

接收端必须有某种方式,使之与接收数据同步。

对于RS-232来说,是这样处理的:6串行线缆的两端事先约定好串行传输的参数(传输速度、传输格式等)7当没有数据传输的时候,发送端向数据线上发送"1"8每传输一个字节之前,发送端先发送一个"0"来表示传输已经开始。

这样接收端便可以知道有数据到来了。

9开始传输后,数据以约定的速度和格式传输,所以接收端可以与之同步10每次传输完成一个字节之后,都在其后发送一个停止位("1")让我们来看看0x55是如何传输的:0x55的二进制表示为:01010101。

单片机和fpga

单片机和fpga单片机和FPGA都是现代数字电路开发中的两种核心技术。

虽然它们在不同的领域有着不同的应用,但它们都是数字电路研究和设计领域中的两个重要分支。

本文将分别介绍单片机和FPGA的概念、原理与应用,并比较它们的优点和缺点。

单片机单片机(Microcontroller,简称MCU),是一种高度集成电路芯片,具有CPU、存储器、通信端口、定时器等外设,可以通过代码对其进行码的负载和控制,并控制外接的器件或设备。

单片机的主要优点是方便集成,可靠性高,并且可运行多种应用程序。

常见的单片机主要由以下几部分组成:1.中央处理器(CPU):负责运行程序指令和控制电器的操作。

2.存储器:存放程序、变量和常量等数据。

3.输入输出(I/O)接口:将信号传输到外部设备或接收外部设备的信号。

4.计时器/计数器:可用于定时或计数。

5.高速串行通讯接口:用于与其他设备进行通信。

单片机应用十分广泛,从家用电器到工业自动化系统都有单片机的身影。

例如,在家用电器方面,它可以被用来控制灯光、计数器、温度、湿度、风扇速度等;在工业自动化系统方面,它可以被用来控制传感器、机器人、闸门等。

FPGAFPGA(Field Programmable Gate Array),中文翻译为现场可编程门阵列,是一种高度灵活的可编程逻辑电路。

FPGA主要由数字逻辑单元(Logic Blocks)、可编程开关(CLB)、输入输出(IO)、内存、数字信号处理器(DSP)、时钟管理单元和片上系统(SoC)等部分组成。

FPGA的优点在于可重构性高、可定制性高、可裸机开发、抗干扰性高。

其缺点在于高成本、功耗高、应用难度相对较大。

FPGA经常被用于计算机硬件加速器,数字信号处理(DSP)、通信网络、航空航天、金融交易中高频交易、机器人控制、医疗等领域。

FPGA和单片机的对比单片机和FPGA的最大区别在于,单片机的逻辑固定,而FPGA的逻辑可以随意编程。

FPGA比单片机更加灵活,适用于数据量较大或计算量较大的应用场合,而单片机适用于简单的控制任务。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA和单片机串行通信接口的实现[ 作者: 加入时间:2006-10-28 15:31:42 来自: ]摘要:本文针对由FPGA构成的高速数据采集系统数据处理能力弱的问题,提出FPGA与单片机实现数据串行通信的解决方案。

在通信过程中完全遵守RS232协议,具有较强的通用性和推广价值。

关键词:FPGA;单片机;串行通信;RS2321 前言现场可编程逻辑器件(FPGA)在高速采集系统中的应用越来越广,由于FPGA对采集到的数据的处理能力比较差,故需要将其采集到的数据送到其他CPU系统来实现数据的处理功能,这就使FPGA系统与其他CPU系统之间的数据通信提到日程上,得到人们的急切关注。

本文介绍利用VHDL语言实现 FPGA 与单片机的串口异步通信电路。

整个设计采用模块化的设计思想,可分为四个模块:FPGA数据发送模块,FPGA波特率发生控制模块,FPGA总体接口模块以及单片机数据接收模块。

本文着重对FPGA数据发送模块实现进行说明。

2 FPGA数据发送模块的设计根据RS232 异步串行通信来的帧格式,在FPGA 发送模块胁捎玫拿恳恢「袷轿?位开始位+8位数据位+1位奇校验位+1位停止位,波特率为2400。

本系统设计的是将一个16位的数据封装成高位帧和低位帧两个帧进行发送,先发送低位帧,再发送高位帧,在传输数据时,加上文件头和数据长度,文件头用555555来表示,只有单片机收到555555时,才将下面传输的数据长度和数据位进行接收,并进行奇校验位的检验,正确就对收到的数据进行存储处理功能,数据长度可以根据需要任意改变。

由设置的波特率可以算出分频系数,具体算法为分频系数X=CLK/(BOUND*2)。

可由此式算出所需的任意波特率。

下面是实现上述功能的VHDL源程序。

Library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity atel2_bin isport( txclk: in std_logic; --2400Hz的波特率时钟 reset: in std_logic; --复位信号 din: in std_logic_vector(15 downto 0); --发送的数据start: in std_logic; --允许传输信号 sout: out std_logic --串行输出端口 );end atel2_bin;architecture behav of atel2_bin issignal thr,len: std_logic_vector(15 downto 0);signal txcnt_r: std_logic_vector(2 downto 0);signal sout1: std_logic;signal cou: integer:=0;signal oddb:std_logic;type s is(start1,start2,shift1,shift2,odd1,odd2,stop1,stop2);signal state:s:=start1;beginprocess(txclk)beginif rising_edge(txclk) thenif cou<3 then thr<="0000000001010101"; --发送的文件头elsif cou=3 thenthr<="0000000000000010"; --发送的文件长度elsif (cou>3 and state=stop2) then thr<=din;--发送的数据end if;end if;end process;process(reset,txclk)variable tsr,tsr1,oddb1,oddb2: std_logic_vector(7 downto 0);beginif reset="1" thentxcnt_r<=(others=>"0");sout1<="1";state<=start1;cou<=0;elsif txclk"event and txclk="1" thencase state iswhen start1=>if start="1" thenif cou=3 thenlen<=thr;end if;tsr:=thr(7 downto 0);oddb1:=thr(7 downto 0);sout1<="0"; --起始位txcnt_r<=(others=>"0");state<=shift1;elsestate<=start1;end if;when shift1=>oddb<=oddb1(7) xor oddb1(6) xor oddb1(5) xor oddb1(4) xor oddb1(3) xor oddb1(2) xor oddb1(1) xor oddb1(0);sout1<=tsr(0); --数据位tsr(6 downto 0):=tsr(7 downto 1);tsr(7):="0";txcnt_r<=txcnt_r+1;if (txcnt_r=7) thenstate<=odd1;cou<=cou+1;end if;when odd1=> --奇校验位if oddb="1" thensout1<="0";state<=stop1;elsesout1<="1";state<=stop1;end if;when stop1=>sout1<="1"; --停止位if cou<4 thenstate<=start1;elsestate<=start2;end if;when start2=>tsr1:=thr(15 downto 8);oddb2:=thr(15 downto 8);sout1<="0"; --起始位txcnt_r<=(others=>"0");state<=shift2;when shift2=>oddb<=oddb2(7) xor oddb2(6) xor oddb2(5) xor oddb2(4) xor oddb2(3) xor oddb2(2) xor oddb2(1) xor oddb2(0);sout1<=tsr1(0);--数据位tsr1(6 downto 0):=tsr1(7 downto 1);tsr1(7):="0";txcnt_r<=txcnt_r+1;if (txcnt_r=7) thenstate<=odd2;end if;when odd2=> --奇校验位if oddb="1" thensout1<="0";state<=stop2;elsesout1<="1";state<=stop2;end if;when stop2=>sout1<="1"; --停止位if len="0000000000000000" thenstate<=stop2;elsestate<=start1;len<=len-1;end if;end case;end if;end process;sout<=sout1;end behav;其中各信号的说明已在程序中标明了。

波形仿真图如图1所示。

图1 FPGA数据发送时序仿真图图中Din写入值为3355H,波特率为2400Hz,Start信号始终置逻辑1,即随时都能发送数据。

Reset信号逻辑1时复位,逻辑0时电路开始工作。

THR是数据寄存器,文件头、数据长度以及数据位都先寄存到THR中,Len是数据长度,TSR是低8位数据帧寄存器,TSR1是高8位数据帧寄存器。

数据长度Len定为02H,发送时先发送低8位55H,后发送高8位33H,一共发送两遍。

发送的数据格式说明:当发送55H时,其二进制为01010101,则发送的数据的二进制数为00101010111(1位开始位+8位数据位+1位奇校验位+1位停止位)。

单片机部分先对FPGA发送过来的文件头进行确认,正确就接收文件,否则放弃接收的数据。

根据FPGA发送模块的协议,对串口控制寄存器SCON和波特率控制寄存器PCON的设置即可实现。

3 总结目前电子产品的开发中经常要综合运用EDA技术、计算机控制技术、数字信号处理技术,那么电路各部分经常需要数据交换。

本文也是基于此给出这方面应用的实例,供开发者交流。

参考文献[1] 潘松,黄继业著.EDA技术实用教程[M].北京:科学出版社,2002.[2] 林敏,方颖立著.VHDL数字系统设计与高层次综合[M].北京:电子工业出版社,2002.[3] 王振红著.VHDL数字电路设计与应用实践教程[M].北京:机械工业出版社,2003.[4] 徐维祥,刘旭敏著.单片微型机原理及应用[M].大连:大连理工大学出版社,2002..。