基于定点DSP的软件锁相环的设计和实现

基于DSP的软件锁相环

一种基于DSP的软件锁相环模型与实现随着大规模集成电路及高速数字信号处理器的发展,通信领域的信号处理越来越多地在数字域付诸实现。

软件锁相技术是随着软件无线电的发展和高速DSP的出现而开展起来的一个研究课题。

在软件无线电接收机中采用的锁相技术是基于数字信号处理技术在DSP等通用可编程器件上的实现形式,由于这一类型锁相环的功能主要通过软件编程实现,因此可将其称为软件锁相环(software PLL)[1]。

尽管软件锁相环采用的基本算法思想与模拟锁相环和数字锁相环相比并没有太大变化,然而其实现方式却完全不同。

本文将建立软件锁相环的Z 域模型,分析软件锁相环中的延时估计、捕获速度及多速率条件下的软件锁相环模型问题[1]。

1软件锁相环的基本模型在模拟锁相环的基础上,利用数字、模拟系统彼此之间的联系,以二阶二型锁相环为例建立软件锁相环的Z 域模型。

文献[2]详细给出了锁相环的基本模型和原理。

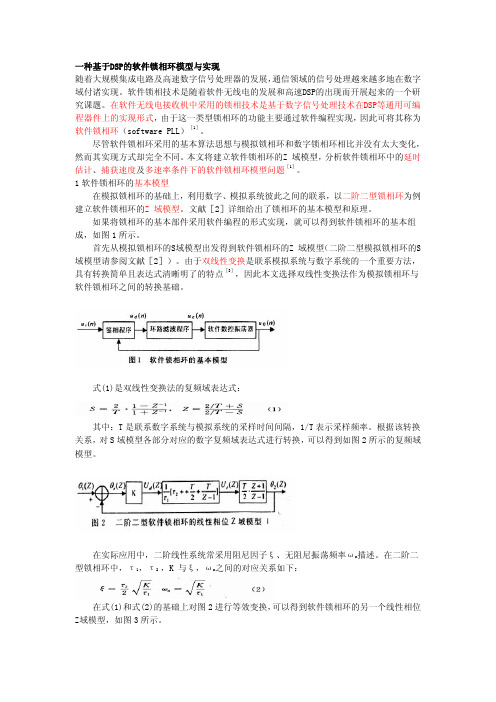

如果将锁相环的基本部件采用软件编程的形式实现,就可以得到软件锁相环的基本组成,如图1所示。

首先从模拟锁相环的S域模型出发得到软件锁相环的Z 域模型(二阶二型模拟锁相环的S 域模型请参阅文献[2])。

由于双线性变换是联系模拟系统与数字系统的一个重要方法,具有转换简单且表达式清晰明了的特点[3],因此本文选择双线性变换法作为模拟锁相环与软件锁相环之间的转换基础。

式(1)是双线性变换法的复频域表达式:其中:T是联系数字系统与模拟系统的采样时间间隔,1/T表示采样频率。

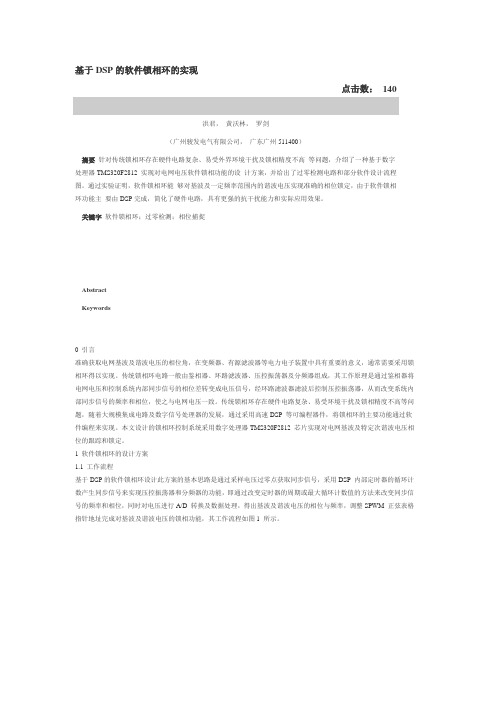

根据该转换关系,对S域模型各部分对应的数字复频域表达式进行转换,可以得到如图2所示的复频域模型。

在实际应用中,二阶线性系统常采用阻尼因子ξ、无阻尼振荡频率ωn描述。

在二阶二型锁相环中,τ1,τ2 ,K 与ξ,ωn之间的对应关系如下:在式(1)和式(2)的基础上对图2进行等效变换,可以得到软件锁相环的另一个线性相位Z域模型,如图3所示。

在模型Ⅰ中,参数τ1,τ2和K与实现电路功能的电阻、电容、压控振荡器密切相关。

基于DSP的逆变电源锁相环的设计与研究

文章编 号 :0 93 6 (0 7 0 —0 80 10 —6 4 2 0 )60 4 —3

冀 辩钠舞赞

基 于 DS P的逆 变 电 源锁 相 环 的设 计 与研 究

龚 益 民 , 小 惠 臧 ( 州 大 学城 轻工 学 院 , 州 23 6 ) 常 常 1 14 摘 要 :采 用基 于 D P的 数 字 锁 相 环 ( P ) 高频 逆 变 电 源输 出频 率 的 实 时控 制 , 实现 逆 变 器 工作 频 率 对 负载 谐 S D I 对 L 可 振频 率的同步跟踪 , 确保逆 变器开关 器件工作在零 电压 电流软 开关( VZ S 状 态, 著减小功 率器件 的开关损 耗和提 高 Z C) 显 装置 效率 。文 中在 给 出 D P控 制 的逆 变 电源 拓 扑 结 构 基 础 上 , 出 了适 用 于 高频 逆 变 电源 的锁 相 环 数 学 模 型 , Z域 中 S 推 在 对二 阶 数 字锁 相 环进 行 了稳 定性 分析 和 动 态设 计 。在 对 锁 相 环 Z域 传 递 函数 分 析 的 基 础 上 , 出二 阶 数 字 锁 相 环 的 稳 定 得 条件 , 给 出数 字锁 相 环 的软 件 实现 , 并 最后 进 行 了 实验 验 证 。 实验 结 果表 明在 Z域 中对 基 于 D P 的二 阶数 字 锁 相 环 的动 S 态分 析 和 设 计 是 合 理 可行 的 。 用此 方 法设 计 的 电源 具 有 良好 的 动 态 响 应 和抗 扰 性 能 。

Ab t a t sr c :Th g t l a e L c e o ( II) e h o o y b s d o g t l i n l o e s r( P)i a p id t e Di i a Ph s — o k d Lo p DP t c n l g a e n aDiia S g a c s o DS Pr s p l O e c n r l h p r t g f e u n y o n H ih Fr q e c — n e t r( o to e o e a i r q e c fa g — e u n y I v re HF— I v re )smu tn o sy O a o a a t v r t s o t n n e t r i la e u l ,S s t d p a i i f e e t e l a e o a tfe u n y t e p t e iv re l y r i g o VZ S ( e o Vo a c Z r re tS th n )mo e h o d r s n n r q e c O k e h n e t ra wa s wo k n n Z C Z r h g  ̄ e o Cu r n wic i g d. Att eme n i 。t e l s e f s th n o o e t r e u e b iu l n h fiin y o h o r i i r v d h a wh l e h o s s o wi i g c mp n n s a e r d c d o v o sy a d t e efce c f t e p we S mp o e c g e ty o r a l n ZVZ d .I h s p p r h o o o y o CS mo e n t i a e ,t e t p l g f HF— I v r e a e n DS sp e e td.a d PI Sma h ma i n e t rb s d o P i r s n e n ’ t e t I c mo e Ss tu ,wh c ss i b e f r HF— I v re .Th t b l y o e o d o d rDPI i n l z d,a d t e d n mi d — d l e p i ih i u t l o a n etr e sa i t fs c n r e i s a ay e I n h y a c e sg sc n i e e sn h in i o sd r d u i g t eZ— ta so m e h i u .At h a eo n lz n h r n f r tc n q e e b s fa ay i g t e Z— ta se u c i n o t r n f rf n to fDPI t es a i … I h tbl — i o d to fs c n r e t c n i n o e o d o d rDPL s p e e t d Th o t r ft e DP i i e y i L i rsn e . e s fwa e o h LI sg v n,a d t e c r e p n i g e p r n s n h o r s o d n x e i me ti d n i a l. Th e u t fe p rme t h w h tt e d n mi a ay i a d d sg fs c n r e ) r e s n b e o efn l y e r s ls o x e i n s s o t a h y a c n l ss n e in o e o d o d r IPI a e r a o a l I

基于DSP的三相软件锁相环设计

收稿日期:2004-05-13作者简介:琚兴宝(1976-),男,硕士研究生,研究方向为电力电子技术。

文章编号:1009-3664(2004)05-0001-04变换与控制基于DSP 的三相软件锁相环设计琚兴宝,徐至新,邹建龙,陈方亮(华中科技大学电气与电子工程学院,湖北武汉430074)摘要:准确获得电网电压的相位角,在电力电子装置设计中有重要的意义。

文中提出了一种在dq 坐标下用DSP 实现的三相软件锁相环,采用滞后控制器使其具有很强的抗干扰能力,和传统的锁相环相比,软件锁相环在实际应用中有更好的效果。

关键词:相位;锁相环;滞后控制;DSP 中图分类号:TN712T N715文献标识码:ADesign of SPLL Based on DSPJU Xing -bao,XU Zh-i x in,ZOU Jian -long,CHEN Fang -liang (Department of Electrical &Electronic Engineering,Huazhong U niversity of Science and Technology,Wuhan 430074,China)Abstract:To obtain phase accurately is important in a desig n of pow er electronic equipments.T hree phases Softw are Phase -Locked Loop(SPLL)based on DSP in the dq reference frame is proposed in this paper.Time -lag controller makes SPLL more robust.T he perform ance of SPLL is more satisfac -tory compared w ith the tradition ones.Key words:phase;phase -locked loop;time -lag controller;DSP 在设计某些电力电子装置(如U PS 、有源滤波器)时,准确而又快速地获得三相电网电压的相位角是保证整个系统具有良好的稳态和动态性能的前提条件。

基于DSP的软件锁相环的实现

基于DSP的软件锁相环的实现点击数:140洪君,黄沃林,罗剑(广州骏发电气有限公司,广东广州511400)摘要针对传统锁相环存在硬件电路复杂、易受外界环境干扰及锁相精度不高等问题,介绍了一种基于数字处理器TMS320F2812 实现对电网电压软件锁相功能的设计方案,并给出了过零检测电路和部分软件设计流程图。

通过实验证明,软件锁相环能够对基波及一定频率范围内的谐波电压实现准确的相位锁定,由于软件锁相环功能主要由DSP完成,简化了硬件电路,具有更强的抗干扰能力和实际应用效果。

关键字软件锁相环;过零检测;相位捕捉AbstractKeywords0 引言准确获取电网基波及谐波电压的相位角,在变频器、有源滤波器等电力电子装置中具有重要的意义,通常需要采用锁相环得以实现。

传统锁相环电路一般由鉴相器、环路滤波器、压控振荡器及分频器组成,其工作原理是通过鉴相器将电网电压和控制系统内部同步信号的相位差转变成电压信号,经环路滤波器滤波后控制压控振荡器,从而改变系统内部同步信号的频率和相位,使之与电网电压一致。

传统锁相环存在硬件电路复杂、易受环境干扰及锁相精度不高等问题,随着大规模集成电路及数字信号处理器的发展,通过采用高速DSP 等可编程器件,将锁相环的主要功能通过软件编程来实现。

本文设计的锁相环控制系统采用数字处理器TMS320F2812 芯片实现对电网基波及特定次谐波电压相位的跟踪和锁定。

1 软件锁相环的设计方案1.1 工作流程基于DSP的软件锁相环设计此方案的基本思路是通过采样电压过零点获取同步信号,采用DSP 内部定时器的循环计数产生同步信号来实现压控振荡器和分频器的功能,即通过改变定时器的周期或最大循环计数值的方法来改变同步信号的频率和相位,同时对电压进行A/D 转换及数据处理,得出基波及谐波电压的相位与频率,调整SPWM 正弦表格指针地址完成对基波及谐波电压的锁相功能,其工作流程如图1 所示。

通常,过零信号可以通过检测电网三相电压中任一相的过零点获取。

基于DSP的软件锁相环的实现

基于DSP的软件锁相环的实现软件锁相环(Software-Defined Phase-Locked Loop,简称软件锁相环,简写为SDPLL)是一种基于数字信号处理(Digital Signal Processing,简称DSP)的锁相环控制算法。

它通过使用数字信号处理器来执行各种计算和调整,实现了锁相环的全部功能。

锁相环(Phase-Locked Loop,简称PLL)是一种闭环控制系统,用于将输入信号的频率和相位与参考信号保持同步。

传统的锁相环通常使用模拟电路来实现,而软件锁相环则通过数字信号处理器中的算法和计算来实现。

软件锁相环的实现步骤如下:1.采样输入信号:软件锁相环首先需要采样输入信号,通常使用高速模数转换器(ADC)将连续的模拟信号转换为离散的数字信号。

2.数字信号处理:采样得到的数字信号经过数字信号处理器进行各种运算和处理。

首先,对信号进行滤波,以去除不需要的频率成分。

然后,进行频率和相位的测量。

这可以通过计算信号的快速傅里叶变换(FFT)来实现。

另外,还可以使用相关函数或自相关函数来测量相位。

3.锁相环控制:基于测量得到的频率和相位信息,软件锁相环通过控制数字信号处理器内部的参数来调整输出信号的频率和相位,使其与参考信号同步。

控制算法通常包括PID控制等经典控制方法,以及其他更复杂的先进算法,如模糊逻辑控制、神经网络控制等。

4.输出信号生成:根据锁相环控制算法的计算结果,软件锁相环生成调整后的输出信号。

通常,使用数字信号处理器内部的数字频率合成器(NCO)来生成所需的频率和相位。

软件锁相环具有以下优点:1.灵活性:软件锁相环可以根据不同的需求进行定制,可以实现更复杂和灵活的控制算法,适应不同的应用场景。

2.可编程性:软件锁相环的算法和参数可以通过编程进行调整和改变,不需要修改硬件电路,提高了系统的可调性和可维护性。

3.数字精度:软件锁相环的计算和控制都是基于数字信号处理器进行的,具有很高的计算精度和稳定性。

锁相环的研究与设计——用于DSP芯片时钟发生器的开题报告

锁相环的研究与设计——用于DSP芯片时钟发生器

的开题报告

一、研究背景

随着现代数字信号处理技术的日益成熟,数字信号处理(DSP)芯片在通信、音视频处理、图像处理等领域得到了广泛应用。

因为DSP芯片需要精确的时钟信号来同步各个模块之间的数据传输,常用的时钟发生器是基于晶振的,然而晶振的频率稳定性和精度难以满足高精度时钟信号的要求。

锁相环(PLL)是一种常用的时钟发生器,用于将一个参考时钟信号锁定到设定频率的输出时钟信号。

锁相环可以提供相对于晶振更高的频率稳定性和精度,适用于DSP芯片的时钟信号发生器。

二、研究内容

本论文将重点研究锁相环的理论原理与设计方法,并将其应用于DSP芯片的时钟发生器中。

主要研究内容包括:

1. 锁相环的基本结构和原理。

重点分析锁相环中的相位检测器、环路滤波器和控制电路等核心组成部分,并探讨其作用和影响因素。

2. 锁相环的设计方法。

基于理论分析和电路实现,设计一种高性能的锁相环,包括参数选取、电路布局和仿真验证等环节。

3. DSP芯片时钟发生器的整体设计。

将锁相环与其他电路模块相结合,构建一个完整的DSP芯片时钟发生器,并对其进行整体性能测试与验证。

三、研究意义

本论文的研究结果可以为DSP芯片时钟发生器的设计与制造提供参考,并为相关领域的进一步研究提供理论基础和实践经验。

同时,本研究探讨的锁相环设计方法可适用于其他电子设备中时钟发生器的设计与制造,具有一定的普适性和推广价值。

基于DSP2407的单相软件锁相环的实现

式 中 ,a 志 为鉴相 器增益 ;o V O增 益 。 k为 C

为 了 得 到 与模 拟 锁 相 环 具 有 相 似 功 能 的 S L P L, 需要 根 据模 拟锁 相 环确 立 S L P L算法 。S L P I运算 中 的信 号流程 图如 图 2 。

() , z

1 SL P L算法的确立

数字控 制振 荡器 / : 积分 器 ) CO( 。设信 号 () 正弦 为

图 1 锁 相 环 的 组成

参考 信 号 , ( 为 余 弦 反 馈 信 号 , 用 DS 20 。 ) 采 P 47的 AD采 样转 换模块 AD C对 进 行采样 ,

谶秘菠瓣 :

基 于 D P 4 7的 单 相 软件 锁 相 环 的 实现 S 20

徐 耀

( 海海事大学 , 海 203) 上 上 0 1 5 摘 要 : 件 锁 相 环 (P I 是 用 软 件 来 实现 模 拟锁 相 环 的 功 能 , 软 S L ) 已广 泛 地 运 用 到 光 伏 并 网逆 变 器 和 电机 的控 制 中 , 在 数 字 信 号 处理 器 ( S ) D P 时代 , D P实 现 软件 锁 相 环 比较 容 易 。 文 中介 绍 了一 种 基 于 D P 4 7的 单 相 软 件 锁 相 环 的 实 用 S S 20 现方法, 相位差控制在 0 1 使 - ℃范 围 内。

模拟锁 相环 是锁 相技术 基 于硬件模 拟 电路 的实现 形式 。锁相 环 由三 部 分 组 成 。 相 器 ( D) 环 路 滤 波 鉴 P 、

器 ( F 和压 控振 荡器 ( o) 如 图 1所示 。 L) vc ,

图 2 S LL 信 号 流 程 P

图 2中包 含 三 个 模 块 : 法 鉴相 器 , I 乘 P 滤波 器 和

基于DSP的多周期调节的软件锁相环设计

持一 致。该文研 究了基 于多周期调节原理 ,采用数字信号处理器芯片 T 3 0 F 4 7 MS 2 L 2 0 A实现软件锁相 环的设 计方法,实现逆变输 出电压对 市电电压的可靠跟踪 ,并给出 了软件设计流程 图和硬件 电路 。实验结果验证了该方法 的有效性和可行性 。 关键 词 : 相环 ;数字信号处理器 ;不 间断 电源 锁

O ep o o e t o ft r p s d me h d. h

[ yw rs h s o kdL o (L ; P U itru t l o e ytm( S Ke o d lP ae c e o pP L)DS ; nnerpi eP w r s UP ) L b S e

1 多周期调节 的索相 环算法 , 2 多周期 调节 锁相 是一种 把逆 变器 正弦波 基准 离散化 的

基于DSP的软件加密锁的设计与实现

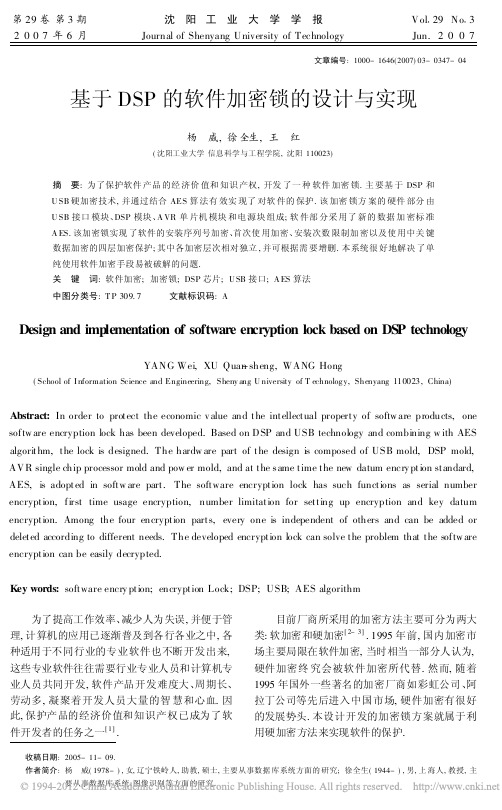

收稿日期:2005-11-09.作者简介:杨 威(1978-),女,辽宁铁岭人,助教,硕士,主要从事数据库系统方面的研究;徐全生(1944-),男,上海人,教授,主要从事数据库系统、图像识别等方面的研究.文章编号:1000-1646(2007)03-0347-04基于DSP 的软件加密锁的设计与实现杨 威,徐全生,王 红(沈阳工业大学信息科学与工程学院,沈阳110023)摘 要:为了保护软件产品的经济价值和知识产权,开发了一种软件加密锁.主要基于DSP 和U SB 硬加密技术,并通过结合AES 算法有效实现了对软件的保护.该加密锁方案的硬件部分由U SB 接口模块、DSP 模块、A VR 单片机模块和电源块组成;软件部分采用了新的数据加密标准A ES.该加密锁实现了软件的安装序列号加密、首次使用加密、安装次数限制加密以及使用中关键数据加密的四层加密保护;其中各加密层次相对独立,并可根据需要增删.本系统很好地解决了单纯使用软件加密手段易被破解的问题.关 键 词:软件加密;加密锁;DSP 芯片;U SB 接口;A ES 算法中图分类号:T P 309.7 文献标识码:ADesign and imp lementation of software en cryption lock based on DS P technologyYANG Wei,XU Quan -sheng,WANG Hong(School of I nformation Science and Engineering,Sheny ang U niversity of T echnolog y,Shenyang 110023,China)Abstract:In order to protect the economic v alue and the intellectual property of softw are products,one softw are encryption lock has been developed.Based on DSP and USB technology and combining w ith AES algorithm,the lock is designed.The hardw are part of the design is composed of USB mold,DSP mold,AVR single chip processor mold and pow er mold,and at the same time the new datum encry ption standard,AES,is adopted in softw are part.The software encryption lock has such functions as serial number encryption,first time usage encryption,number limitation for setting up encryption and key datum encryption.Among the four encryption parts,every one is independent of others and can be added or deleted according to different needs.The developed encryption lock can solve the problem that the softw are encryption can be easily decrypted.Key words:software encry ption;encryption Lock;DSP;USB;AES algorithm 为了提高工作效率、减少人为失误,并便于管理,计算机的应用已逐渐普及到各行各业之中,各种适用于不同行业的专业软件也不断开发出来,这些专业软件往往需要行业专业人员和计算机专业人员共同开发,软件产品开发难度大、周期长、劳动多,凝聚着开发人员大量的智慧和心血.因此,保护产品的经济价值和知识产权已成为了软件开发者的任务之一[1].目前厂商所采用的加密方法主要可分为两大类:软加密和硬加密[2-3].1995年前,国内加密市场主要局限在软件加密,当时相当一部分人认为,硬件加密终究会被软件加密所代替.然而,随着1995年国外一些著名的加密厂商如彩虹公司、阿拉丁公司等先后进入中国市场,硬件加密有很好的发展势头.本设计开发的加密锁方案就属于利用硬加密方法来实现软件的保护.第29卷第3期2007年6月沈 阳 工 业 大 学 学 报Journal of Shenyang University of TechnologyVol 129No 13Jun.20071带USB接口的DSP加密锁的优点以往的软件加密锁经常采用单一的存储器存储有用信息,PC机通过读取存储器中的内容来判断软件是否为正版.后来发展成为用单片机作为加密锁的核心处理单元,这在一定程度上加强了加密锁的可靠性,其缺点在于单片机处理速度慢,且不能在单片机中使用复杂的算法,所以其加密可靠性仍然不令人满意.为了克服以上加密锁的缺点,设计了一种采用DSP技术和U SB技术相结合的加密锁.该加密锁的硬件核心部分以U SB 和DSP为主要部件;软件则是结合了AES算法进行加密,实现了对软件使用授权的验证.加密锁对软件的安装和使用完成四层加密保护,即安装序列号加密、首次使用加密、安装次数限制加密、使用中关键数据加密.上述加密层次相对独立,可以根据需要增删.111DSP芯片概述DSP芯片,是一种特别适合于进行数字信号处理运算的微处理器,其主要应用是可以实时、快速地实现各种数字信号处理算法[4].根据数字信号处理的要求,DSP芯片一般具有如下主要特点:1)在一个指令周期内可完成一次乘法和一次加法,这为快速进行算法运算提供了良好的基础;2)程序和数据空间分开,可以同时访问指令和数据;3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;4)具有低开销或无开销循环及跳转的硬件支持;5)快速地中断处理和硬件I/O支持;6)具有在单周期内操作的多个硬件地址产生器;7)可以并行执行多个操作;8)支持流水线操作,使取指、译码和执行等操作可以重叠执行.作为新兴的处理器,DSP在硬件平台上具有良好的运算速度,满足了对软件保护高速的需求;且可以使用相对复杂的算法,弥补了以往加密锁的不足.基于其优越的特点,本文将DSP技术引入了系统的设计.112AES算法的结构为了实现的方便和速度的提高,本文采用的密钥长度为128bit.由于AES(加/解密的长度为128bit,密钥为128bit)的穷尽攻击的复杂度是2128,且目前在理论上还不存在有效的攻击方法,因此其安全强度是足够的.该结构由四个不同的阶段组成,包括一个混淆和三个代换:1)字节代换:用一个S盒完成分组中的按字节的代换;2)行移位:一个简单的置换;3)列混淆:一个利用在域GF(28)上的算术特性代换;4)轮密钥加:利用当前分组和扩展密钥的一部分进行按位XOR.对加密解密操作,算法由轮密钥加开始,接着执行九轮迭代运算,每轮都包括所有四阶段的代换,然后执行只包含三个阶段的最后一轮运算.在加密过程中使用密码反馈模式(CFB)和输出反馈模式(OFB).113AES算法优越性加密锁采用了安全性好、加密速度快的新的数据加密标准AES[5-6].在安全性方面,AES能抵抗目前己知的所有攻击,特别是线性分析和差分分析,也能抵抗某些物理攻击;在和其它算法有相同安全性时它需要的轮数最少.在代价方面, AES设计简单,不管是硬件上还是低内存环境下它都能快速执行,在所有的平台上始终有卓越的性能.AES灵活性比较大,它的分组长和密钥长可以随着安全性的要求而改变.由于它的密钥方案简单,生成速度快,对内存要求低,因此非常适合于智能加密锁的实现.基于AES算法的优越特点,与DSP相结合进行系统设计[7].2硬件设计加密锁硬件部分由USB接口模块、DSP模块,AVR单片机模块和电源块组成,各部分之间的组成关系如图1所示.图1硬件原理框图Fig.1Electric cir cuit diag ram348沈阳工业大学学报第29卷U SB 接口芯片是软件加密锁与PC 机进行通信的通道,它具有传输速度快的特点[8].USB 通用串行总线已逐渐取代PC 机上的并、串口成为主流,更适合软件加密锁技术.同时USB 接口还可以提供5V 、500mA 的电源,软件加密锁可以利用这个电源为软件加密锁上的其他电子元件提供电源,这样能实现软件加密锁的即插即用和热插拔功能,增加了软件加密锁设备的使用灵活性.电源芯片采用T I 公司的TPS73HD318芯片,它是专门的电源芯片,能够将5V 电压转换成DSP 所需要的313V 和118V 电压,这样就为DSP 芯片提供了电源.DSP 芯片采用T I 公司的T MS320VC5402,这款芯片除具有上述DSP 的全部优点外,还具有功耗低、价格低廉等优点,因此特别适用于软件加密锁的使用[9].AVR 芯片采用ATMEL 公司的ATMEGA8535L.本设计通过在AVR 单片机内部编写程序,能够对软件加密锁本身实现加密,防止软件加密锁的硬件设计被人仿制.这样AVR 单片机不但起到了存储器和缓冲器的作用,而且提高了加密锁的可靠性.3 软件设计U SB 加密锁要完成软件使用许可认证功能,需要高层和底层软件协同动作,高层软件负责监控,底层软件根据高层软件的需求,向高层提供产品序列号和加解密数据等.本系统软件部分主要采用了新的数据加密标准AES 算法.使用C 语言进行编码.311 软件结构组成U SB 软件加密锁的软件分为高层软件和底层软件两部分.高层软件和软件的安装程序、应用程序嵌在一起,底层软件嵌在AVR 单片机及DSP 芯片中,高层底层软件通信通过传递加密后的产品序列号和关键数据,实现对用户使用权限的认证.U SB 加密锁软件结构如图2所示.图2 软件结构图Fig.2 Software structure diagr am312 软件功能分析1)高层软件对应用程序运行监控过程在软件安装时,首先向加密锁索取安装产品序列号次数,若其大于三次则退出安装,否则向用户索取产品安装序列号,同时向加密锁发出索取产品安装序列号的请求,并将得到加密后的产品安装序列号验证;在首次使用时,向用户索取产品使用序列号,同时向加密锁发出取加密后的产品使用序列号的请求,得到产品使用序列号后进行验证;在用户使用应用软件时,若检测到端口存在加密锁,则向加密锁索取被加密后的关键数据,否则退出该应用软件.2)高层软件调用方法高层软件的设计是以高层监控程序为主体,以树状结构控制安装程序和应用程序并且通过驱动程序访问USB 接口,取得验证数据.高层软件结构如图3所示.图3 高层软件结构图Fig.3 P C softw ar e str ucture diag ram3)底层软件响应高层软件请求过程当高层发出索取产品安装序列号次数的请求时,则先从AVR 单片机内部的E 2PROM 中读取安装次数,若未超过三次,则从AVR 单片机内部的E 2PROM 中读取产品安装序列号;然后发给DSP 芯片,DSP 芯片运行加密算法对其加密后发给高层;当高层发出取产品使用序列号的请求时,从AVR 单片机内部的E 2PROM 中读取产品使用序列号,再发给DSP 芯片,DSP 芯片运行加密算法对其加密后发给高层;当高层向加密锁索取被加密后的关键数据时,从AVR 单片机内部的E 2PROM 中读取关键数据后发给DSP 芯片,DSP 芯片运行加密算法对其加密后发给高层.4 实验结论本文将DSP 和USB 硬加密技术与AES 算法相结合,设计实现了一个可靠性高、运行效率高、使用方便的软件加密锁.该加密锁实现了对软件的四层加密保护,即安装序列号加密、首次使用加349第3期杨 威,等:基于DSP 的软件加密锁的设计与实现密、安装次数限制加密、使用中关键数据加密,且各加密层次独立,并可根据需要进行增删.通过实验和调试得知,作为将先进加密技术AES和DSP硬件技术相结合的新型软件加密锁,本系统很好地解决了单纯使用软件加密手段易被破解的问题,对进一步提高软件产品的反盗版能力有一定的实用价值.参考文献:[1]飞天诚信.软件加密原理与应用[M].北京:电子工业出版社,2004.(FEI T IAN Safe.T he principle and application of soft-ware encrypt[M].Beijing:Electronics Industr y Press, 2004.)[2]秦志光.密码算法的现状和发展研究[J].计算机应用,2004(2):1-4.(Q IN Zh-i guang.Cryptog raphy alg orithm-surv ey and trends[J].Computer Application,2004(2):1-4.) [3]徐政五,龚耀寰.信息战中的信息加密技术[J].电子科技大学学报,2000(5):469-474.(XU Zheng-wu,GON G Y rmation encry p-tion technology in infor mation w ar fare[J].Journal of U niversity of Electronic Science and T echnology of Ch-i na,2000(5):469-474.)[4]谢庆国,邓忠华,万淑芸,等.改进的刘氏加密算法及其DSP实现[J].计算机工程与应用,2001(5):100-101,125.(XIE Q ing-guo,DEN G Zhong-hua,WA N Shu-yun,et al.Mo dified L IU S alg orithm and implement w ith DSP[J].Computer Eng ineering and Application,2001(5): 100-101,125.)[5]王新房,马安光.Rijndael算法代数性质及其七轮攻击[J].计算机工程与应用,2005,21:86-88.(WA NG X in-fang,M A An-guang.Some alg ebraic pr op-er ties and7-r ound attack of the rijndael[J].Computer Eng ineering&A pplication,2005,21:86-88.)[6]卢正鼎,廖振松.Rijndael算法的研究[J].计算机工程与科学,2005(6):72-74.(LU Zheng-ding,LIA O Zhen-song.Research on the r-i jndael algorit hm[J].Computer Engineering&Science, 2005(6):72-74.)[7]李金花,周大水,李大兴.AES算法在DSP中的实现及优化[J].计算机工程,2004,12:101-102.(L I Jin-hua,ZHOU Da-shui,L I Da-xing.Implementa-tion and optimization of A ES in DSP[J].Computer En-gineer ing,2004,12:101-102.)[8]梁中华,王子威.PC机与单片机串行通信的研究[J].沈阳工业大学学报,2005(3):302-307.(L IAN G Zhong-hua,WAN G Z-i wei.Research of serial communication between PC and M CS-51ser ial sing le chip[J].Journal of Shenyang University of T echnolo-gy,2005(3):302-307.)[9]刘长军,林嘉宇.为DSP程序构造的加密体制[J].单片机与嵌入式系统应用,2002(4):5-7.(LIU Chang-jun,L IN Jia-yu.T he encrypt system con-struction for DSP pro gramme[J].M icr ocontrollers& Embedded Systems,2002(4):5-7.)(责任编辑:吉海涛英文审校:王向东)350沈阳工业大学学报第29卷。

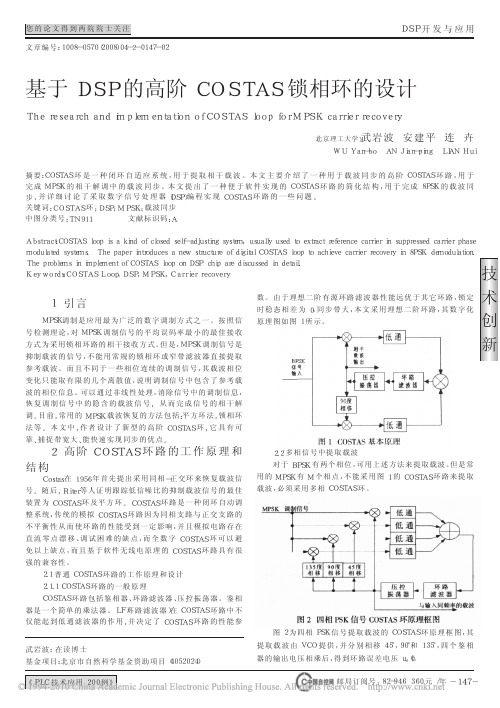

基于DSP的高阶COSTAS锁相环的设计

图 4 8PSK 接收端解调前星座图(AWGN 信道, SNR=17dB)

5 结束语

本 文 主 要 介 绍 了 一 种 新 型 的 适 用 于 MPSK 载 波 提 取 的 高 阶 COSTAS 环 路 , 能 满 足 MPSK 相 干 解 调 的 需 要 , 且 便 于 DSP 实现。针对 COSTAS 环 算 法的 DSP 实 时 实现 问 题 , 进行 了 详 细 的讨论。最后, 针对一个具有较高 数 据 速率 8PSK 调 制 解调 实 例 , 在单 片 C6416 上 完成 了 基 于高 阶 COSTAS 环 的载 波 同 步 及 相 干 解调 , 并 给 出了 通 过 CCS 工 具 观 察 到 的 DSP 实 现 结 果 , 证 明高阶 COSTAS 锁相环具有较好的载波同步性能。

4 高阶 COSTAS 环路的 DSP 实现结果

本 文 选 取 8PSK 的 符 号 速 率 为 2400kbps, 载 波 速 率 为 4800kHz,采样率为 230.4kHz。图 2 所示的两路信号分别是利用 CCS 开发 工 具的 观 察 窗口 观 察 到的 , 提 取 的 同 频 同 相 的 载 波 信 号和 8PSK 的调制信号。

的方 式 , 即由 EDMA 控 制 器控 制 数 据在 L2 内 存/缓 存 和 片 内 集 成外设及片外设备之间的传输, 而同时 CPU 可以并行的执行其 它指 令 。EDMA 是一 种 有 效的 数 据 传 输 方 式 , 可 以 有 效 的 减 少 EMIF 在 CPU 下操作需要的资源。

具体 实 现方 法 如 下: 在 片 内 数据 存 储 区定 BUF 的 长 度 , 并 一 分 为 二 , 可 设 为 BUF1 和 BUF2。 在 EMDA 里 BUF1 和 BUF2 都是等存储大 小 的。在 数 据 帧同 步 信 号的 上 升 沿, DSP 以 ED- MA 的 方 式从 外 部 读一 帧 的 数据 到 BUF1; 同 时 BUF2 内 的 数 据 进 行 MPSK 的 解调 算 法 。同理 , 在 下 一个 数 据 帧 同 步 信 号 的 上 升 沿 , DSP 以 EDMA 的 方 式 从 外 部 读 另 一 帧 的 数 据 到 BUF1 。 BUF1 读 满 后 , DSP 对 BUF1 内 的 数 据 进 行 MPSK 的 解 调 算 法 , 同时 BUF2 进行数据的读操作, 实现 EDMA 的乒乓处理。

基于DSP的三相软件锁相环设计

地 获得 三相 电 网电压 的相位 角是保 证 整个系 统具 有 良好 的 稳态和 动态性 能 的

前提条 件 。 下面 是基 于D S P 的三相 软件 锁 相环 的设 计 。 三相 S P L L 的基本 结 构框 图如 图2 所示 。 图中虚 线框 内的坐 标变 换 为鉴

=

设 =

时的最大计数值为 Ⅳ巾 =Ⅳ, 对应的定时器的周期为

,

( 2 z/ Ⅳ 国 ) 。 则当 g O :∞ + 一 时, 若保持 不变, 则最大计

数值为Ⅳ一 =Ⅳ , / ( 1 + & , c / ∞ ) , 由于正常隋 况下电网电压频率波动很 小,

即& 变,则

( s o a wa r e P L L ) 。 在 设计某 些 电力 电子 装置 ( P S 、 有源滤 波器 ) 时, 准确 而又 快速

振 荡频 率 。 用 D S P 实现 时 , 一般 采 用 D S P 内部 定时器 的循环 计数 来产 生 同

步信 号 、 实 现压控 振荡器 和分 频器 的功 能 , 因此 可通过 改变 定时器 的周 期 或最

科 学 论 坛

C hi n a s c i e n c e a nd T e c h n o l o g y R e vi e w

啊

l

基 于 DS P的三 相 软件 锁 相环 设 计

张为 飞 任倩儒

( 陕西 凌云 电器 集 团有 限公 司 7 2 1 0 0 6 ) [ 摘 要】 随着大 规模 集 成 电路 及 高速 数字信 号 处理 器的 发展 , 通信 领域 的信 号处 理越 来越 多地 在数 字 域付诸 实 现 。 软件 锁相 技 术是 随着 软件 无线 电 的发展 和高 速D S P 的出现 而开展 起 来 的一个研 究课 题 。 对 于三相 电网 , 采用 单相 同步 的方法 很 难准确 的 实现坐 标 系与 电网三 相 电压 合 成矢量 的 同步 , 必 须综 合三相 电压 的相 位信 息 。 根据 经 验 , 作者 基 于D S P 的三相 软件 锁相 环进 行 了设 计 , 望 能给 同仁 一些 帮助 。 [ 关键 词] 三相 软件 锁 相环 , D S P; 设计 中图分 类号 : T P 3 1 1 . 1 文 献标识 码 : A 文章编 号 : l 0 0 9 — 9 l 4 x ( 2 0 l 5 ) 3 2 — 0 3 6 7 — 0 1

基于DSP Builder三相锁相环的设计

科技资讯2016 NO.07SCIENCE & TECHNOLOGY INFORMATION动力与电气工程19科技资讯 SCIENCE & TECHNOLOGY INFORMATION 在直流输电、无功补偿等场合中,均要求准确获取电网电压相位信息。

目前,工程上多以数字信号处理器为核心,实现离散域的三相锁相环(PLL)算法,虽然具有编程灵活的优点[1],但是算法中的三角运算、乘法运算占用了大量CPU资源[2]。

而现场可编程门阵列(FPGA)以硬件电路形式并行运行,不存在占用CPU资源的问题,更适合于工程现场。

文献[3]以FPGA器件为核心实现了快速锁DOI:10.16661/ki.1672-3791.2016.07.019基于DSP Builder 三相锁相环的设计①罗文清1* 劳雪婷1 吕玉波2 刘畅3(1.东北电力大学电气工程学院 吉林吉林 132012;2.国网吉林省电力有限公司营销部 吉林长春 130021;3.国网吉林省电力有限公司吉林供电公司 吉林吉林 132021)摘 要:传统三相锁相环的设计方法占用资源多,开发效率低下,针对这一特点,该文在DSP Builder环境下实现了三相锁相环的设计。

在Simulink环境下进行建模仿真后,利用Signal Compiler模块将MDL文件直接转化为可综合的硬件描述语言,整个过程无须人工编程。

最后,将HDL代码下载到FPGA芯片上进行实物验证。

结果表明,此三相锁相环可以快速实现精确锁相,验证了该设计方法的可行性和有效性。

关键词:DSP Builder 三相锁相环 现场可编程门阵列 硬件描述语言中图分类号:TM76文献标识码:A文章编号:1672-3791(2016)03(a)-0019-02①通讯作者:罗文清(1991,7—),男,汉,福建漳州人,硕士,研究方向:柔性直流输电,E-mail:zhluo22@。

Signal Compiler图1 三相锁相环控制原理图图2 三相锁相环模型科技资讯2016 NO.07SCIENCE & TECHNOLOGY INFORMATION动力与电气工程20科技资讯 SCIENCE & TECHNOLOGY INFORMATION相,但是其基于底层Verilog HDL硬件描述语言的开发手段,存在开发效率低、优化困难等缺点。

基于DSP的高动态锁相环的实现

d e t e r mi n e s t h e q u a l i t y o f p h a s e - l o c k e d l o o p .F o c u s i n g o n t h e l o o p f i l t e r d e s i g n ,c o mb i n e d wi t h a p p l i c a t i o n o f P LL i n l o o p o f

0 引 言

随着 载波 跟踪 特 性逐 渐 优 良 , 锁 相 环 已被 广泛 应

为 了使输 出信 号 的频 率 可 以 自动 跟 踪输 入 信 号 的频 率, P L L通 常被应 用在 闭环 跟踪 锁 相 回路 。在 这个 过 程中, 当输 入 和输 出信号 相位保 持 不变 , 锁相 环进 入 锁

通 缱 电 潦 】 | :

2 0 1 5年 3月 2 5日第 3 2 卷第 2期

Te l e c o m Po we r Te c h n o l o g y Ma r .2 5,2 0 1 5,Vo 1 .3 2 No 2

.

文章编 号 : 1 0 0 9 — 3 6 6 4 ( 2 0 1 5 ) 0 2 — 0 0 6 0 — 0 3

( S h a n g h a i El e c t r i c Ce n t r a l Re s e a r c h I n s t i t u t e ,S h a n g h a i 2 0 0 0 7 0,Ch i n a )

电压不对称情形下基于DSP软件锁相环的设计

文章编号:1673-6397(2009)增01-0053-05电压不对称情形下基于DSP 软件锁相环的设计吕 飞,吕 运,张松涛(海军蚌埠士官学校机电系,安徽蚌埠 233012) 摘要:准确的相位信息对大部分现代电能变换装置的稳定运行至关重要,比如高频PW M整流。

软件锁相环(SP LL )具有设计自由、适应性强等优点可快速准确获得电网电压的相位和频率信息。

本文针对电网电压不对称的情形,分析SP LL 原理,获得SP LL 线性化模型,设计SP LL 控制器,讨论实际情况对控制器参数的要求,并用DSP 实现所设计SP LL 。

仿真表明所设计SP LL 良好运行于高频PW M 整流,并对其他电能变换装置中的SP LL 设计具有指导意义。

关键词:软件锁相环;坐标变换;数字信号处理器;延迟信号抵消中图分类号:T M46 文献标识码:A Design and R ealization of Softw are Phase -Locked Loop under G ridV oltage DissymmetryLV Fei ,LV Y un ,ZH ANG S ong -tao(E lectromechanical Department ,Bengbu Naval Petty O fficer Academy ,Bengbu 233012,China )Abstract :Accurate phase information is crucial for m ost of the m odern power -electronics apparatus such as the PW M rectifier ,PW M converter and s o on.A s oftware phase -lock loop (SP LL )has s o many advantages,such as freedom of design.Then it is usually proposed to obtain phase and frequency in formation of the grid v oltage.In this paper ,considering of the condition of grid v oltage dissymmetry ,the operational principle of SP LL is analyzed.The linearized m odel of SP LL is obtained ,and als o the SP LL controller is designed.The relations between controller parameters and operation conditions are discussed and the conceived SP LL is achieved by DSP.Simulation results indicate the designed SP LL can w ork well in a PW M rectifier.K ey Words :SP LL ;Frame T rans form ;DSP ;DSC作者简介:吕飞(1982-),男,安徽阜阳人,硕士,研究方向为电力电子与电力传动。

最新-基于定点DSP的软件锁相环的设计和实现 精品

基于定点DSP的软件锁相环的设计和实现摘要软件锁相环是软件接收机中执行载波恢复功能的关键部分。

提出了一种48位定点扩展精度的算法,可以有效地实现软件锁相环。

与浮点算法比较,能极大地降低的运算量,降低功耗,同时保证动态范围运算精度。

关键词低轨道卫星软件接收机软件锁相环定点扩展精度算法低轨小卫星通信是近年来卫星通信应用中一个方兴未艾的重要领域,"创新一号"小卫星是我国研制的具有完全自主知识产权的存储与转发通信小卫星,手持终端是专门为这颗小卫星研制的低功耗地面手持通信终端,支持调制数据速率达76.8的窄带信道。

基于公司的低功耗16位定点数字信号处理器3205510最高运算能力为200,完全用软件实现低中频数字接收机,其中包括执行载波恢复功能的软件锁相环--。

在用浮点算法实现软件锁相环时,由于3205510是一个定点处理器;没有浮点处理单元,只能用编译器产生模拟浮点运算的指令,运算量需要67.2,效率很低,因此需要一种能在3205510上执行的定点算法,有效地降低运算量。

本文提出了一种48位定点扩展精度算法实现,提高了效率,减少了运算量,同时保证了环路计算的精度和动态范围。

范文先生网收集整理1软件锁相环1.1软件锁相环的结构图1表示软件数字接收机中的解调器。

它包括由改进的环路构成的载波跟踪环路。

采样后的中频信号经过数字混频,滤掉高频分量,通过改进的环路产生控制信号,控制数控振荡器得到新的本振参考信号。

其中的相位检测器和环路滤波器结构如图2所示。

1.2软件锁相环的设计由图2可见,的计算由计算相位误差和更新环路中间变量、输出控制信号两部分组成。

算法描述可用伪码白表示中断发生{读取基带数据_=_=计算相相位误差=_×_**×_更新环路中间变量__=2×+_-1输出控制信号ΔΔ=1×+_设置载波频率=Δ+0***}注**_是归一化因子,由_和_和初始值决定***0是固定的中心频率算法描述中的中断周期就是环呼采样时间间隔。

基于DSP的软件锁相环的设计

基于DSP的软件锁相环的设计李进兵荣雅君董杰安刚虎燕山大学电气工程学院河北秦皇岛066004摘要文中分析了锁相环的工作原理和锁相环软件设计流程,设计了基于数字信号处理器TMS320LF2407A的数字锁相环,给出了锁相环程序流程图和部分程序,并给出了实验结果。

关键词锁相环,DSP,逆变电源1.引言在逆变器并网控制系统中,为了保证逆变器输出电流和电网电压同相,一般要采用锁相环(PLL—Phase Locked Loop)技术。

常用的模拟锁相环主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VC0)组成,如图1所示。

鉴相器比较输入信号Vi和压控振荡器的输出信号Vo之间的相位差,完成相位差--电压变换。

环路滤波器的作用是滤除鉴相器输出信号Vd中的高频分量和其它干扰分量。

压控振荡器的振荡频率受环路滤波器输出电压Vc的控制,实现电压--频率的变换。

从而完成锁相的功能。

图1 锁相环原理图传统的锁相方法电路复杂且精度不高,以高速DSP芯片实现的数字方法与模拟方法相比有如下优点:智能化程度更高,性能更加完美:控制灵活,甚至可以在线修改控制算法,而不必对硬件电路做改动;可靠性高;维护方便,一旦出现故障,可以很方便地进行在线调试。

因此,本文设计的锁相控制系统采用TI公司TMS320LF2407A芯片来实现对市电的跟踪。

2.锁相控制的设计与实现一般软件锁相环的程序流程图如2图所示图2 软件锁相环国家自然科学基金项目(资助号:50237020)2.1 市电频率信号波形整形电路由于DSPLF2407A的参考电压为3.3伏需要通过硬件电路将220伏电压转化成3.3伏的方波。

本文利用一个迟滞比较器把输入整形为一个和输入同频同相的矩形波,然后利用该波形在软件上进行频率和相位跟踪。

具体实现电路如图3所示。

整定电路的输出波形如图4所示。

图3 市电频率信号波形整定电路图4 整定电路输出波形2.2 SPWM波的发生逆变器输出电压基准正弦信号需要由DSP给出。

基于 DSP 的高动态锁相环的实现

基于 DSP 的高动态锁相环的实现唐丽婵;陆宇;汤雪华【摘要】文中介绍了常见锁相环的基本结构,分析了相位检测器、环路滤波器和压控振荡器的执行情况。

PLL 环路滤波器的系统函数表明,环路滤波器的性能基本上决定了锁相环的质量。

侧重于环路滤波器的设计,结合锁相在高动态GPS 接收机环路中的应用,提出了在高动态环境中,一种两相锁频环辅助三相锁相环数字滤波器的细节。

模拟结果表明,该锁相环的性能比普通 PLL 已大大改善,并完全符合高动态信号跟踪的要求。

%This paper introduces the basic structure of common phase-locked loop,and analyzes implementation of phase detector,loop filter and VCO.System function of PLL loop filter shows that the performance of loop filter basically determines the quality of phase-locked loop.Focusing on the loop filter design,combined with application of PLL in loop of high-dynamic GPS receiver,details of a digital filter in highly dynamic environment with two-phase frequency locked loop aiding a three-phase phase-locked loop are presented.The simulation results show that the proposed PLL has much better performance than common PLL,and is in full compliance with the requirements of high dynamic signal tracking.【期刊名称】《通信电源技术》【年(卷),期】2015(032)002【总页数】3页(P66-68)【关键词】锁相环;滤波器;DSP;高动态【作者】唐丽婵;陆宇;汤雪华【作者单位】上海电气集团股份有限公司中央研究院,上海 200070;上海电气集团股份有限公司中央研究院,上海 200070;上海电气集团股份有限公司中央研究院,上海 200070【正文语种】中文【中图分类】TM461随着载波跟踪特性逐渐优良,锁相环已被广泛应用在无线电技术的各个领域。

一种基于DSP的软件锁相环模型与实现

一种基于DSP的软件锁相环模型与实现

何一;张亚妮;葛临东

【期刊名称】《现代电子技术》

【年(卷),期】2003(000)008

【摘要】在分析软件锁相环的Z域模型基础上,阐述了在多速率条件的实现方法,仿真出软件锁相环频率与相位跟踪曲线,介绍了一种基于DSP的软件锁相环实例.【总页数】4页(P19-21,25)

【作者】何一;张亚妮;葛临东

【作者单位】信息工程大学,河南,郑州,450002;西安电子科技大学,陕西,西

安,710071;信息工程大学,河南,郑州,450002

【正文语种】中文

【中图分类】TP311.5

【相关文献】

1.基于DSP的高精度单相软件锁相环的实现 [J], 张启亮;刘倩影

2.基于定点DSP的软件锁相环的设计和实现 [J], 蒋毅凯;李国通;杨根庆

3.一种基于软件锁相环实现位同步的设计 [J], 张素琴

4.基于DSP2407的单相软件锁相环的实现 [J], 徐耀

5.一种基于软件锁相环实现位同步的设计 [J], 张素琴

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

低轨小卫星通信是近年来卫星通信应用中一个方兴未艾的重要领域,“创新一号”小卫星是我国研制的具有完全自主知识产权的存储与转发通信小卫星,cascom手持终端是专门为这颗小卫星研制的低功耗地面手持通信终端,支持调制数据速率达76.8kbps的BPSK窄带信道。基于TI公司的低功耗0(最高运算能力为200MIPS),完全用软件实现低中频数字接收机,其中包括执行载波恢复功能的软件锁相环SPLL(Software Phase-Locked Loops)。在用浮点算法实现软件锁相环时,由于TMS320VC5510是一个定点DSP处理器,没有浮点处理单元,只能用编译器产生模拟浮点运算浮点运算的指令,运算量需要67.2MIPS,效率很低,因此需要一种能在TMS320VC5510上执行的定点算法,有效地降低运算量。本文提出了一种48位定点扩展精度算法实现SPLL,提高了效率,减少了运算量,同时保证了环路计算的精度和动态范围。

在TMS320VC5510可编程DSP的基础上,利用48位定点扩展精度算法实现SPLL。在实现过程中,采取了模块化的思路。首先,把SPLL整个环路计算封装成一个可调用的C语言函数。函数参数包括C1、C2、K_norm、基带信号的I及Q分量、环路中间变量、调整频率。DSP的中断例程(ISR)可以直接调用环路计算函数,而且通过输入不同的C1、C2,适用于不同的载波恢复环路中。另外,在函数内部用汇编语言进行编程,以充分利用DSP的计算能力,把48位定点扩展精度算法的五个基本操作封装成用汇编指令写的宏(macro),对照计算流程,调用这些宏,完成SPLL的核心计算部分。经统计,每次环路计算需132个指令周期,总的运算量10.1MIPS,是浮点算法运算量(67.2MIPS)的14%。

f0是固定的NCO中心频率。至此,一次完整的SPLL计算完成。

在第三步和第四步计算中,环路滤波器系数C1,C2可以通过环路采样时间间隔T(或者环路更新时间间隔)、环路自由频率ωn及环路阻尼系数ζ确定,如下两式[2]:

Kd为相位检测器的增益,由于在实现软件锁相环时,基带信号的同相和正交分量都经过归一化处理,故Kd=1;K0为数控振荡器的增益,K0=2πT。T为调制数据速率的倒数(1/76800),ζ一般取0.707。在启动载波恢复之前有一个频率捕获过程,通过1024点的FFT,可保证接收的中频信号与本振信号之间的频率差Δf0最大不超过75Hz。另外系统设计要求SPLL的捕获时间(pull in time)小于50ms,由此可以确定环路自由频率ωn。ωn>150(rad·Hz),取ωn=300(rad·Hz)。将K0、Kd、ζ、ωn、T代入式(3)、(4)得,C1=67.3273309,C2=0.1859953。

1 软件锁相环

1.1 软件锁相环的结构

图1表示软件数字接收机中的解调器。它包括一个由改进的costas环路[1]构成的载波跟踪环路。

采样后的中频信号经过数字混频,滤掉高频分量,通过改进的costas环路产生控制信号,控制数控振荡器(NCO)得到新的本振参考信号。其中的相位检测器和环路滤波器结构。

由式(3)、(5)和(6)得:

即把同相数据硬判决后结果乘以正交项数据后再乘以归一化因子K_norm。K_norm初始值由I_baseband和Q_baseband的初始值决定,

由于定时恢复环路和AGC(自动增益控制)环路的作用,K_norm在解调过程中近似保持恒定。第三步更新环路中间变量s_pll(n),

基于定点DSP的软件锁相环的设计和实现

摘 要: 软件锁相环软件锁相环是软件接收机中执行载波恢复功能的关键部分。提出了一种48位定点扩展精度扩展精度的算法,可以有效地实现软件锁相环。与浮点算法浮点算法比较,能极大地降低DSP的运算量,降低功耗,同时保证动态范围动态范围和运算精度。 关键词: 低轨道卫星 软件接收机 软件锁相环 定点扩展精度算法

1.2 软件锁相环的设计

由图2可见,SPLL的计算由计算相位误差和更新环路中间变量、输出控制信号两部分组成。算法描述可用伪码表示:

算法描述中的中断周期就是环路采样时间间隔。

中断发生后,第一步读取基带同相项数据和正交项数据

A是基带信号幅度,θe是相位误差。第二步计算硬判决的同相数据乘以相位误差。

一个Q15.32数的表示范围是(-32768,32768),小数分辨率是远远超过16位定点表示的精度,以下用加(ADD_48)、减(SUB_48)、乘(MULT_48)三种基本运算来说明定点扩展精度算法。操作数X由X2、X1、X0构成,操作数Y由Y2、Y1、Y0构成,结果W由W2、W1、W0构成。执行48位加法运算时,W2W1W0=X2X1X0+Y2Y1Y0,首先把小数部分X1X0和Y1Y0相加,结果保存到W1W0中,产生的进位位CARRY与X2、Y2相加,结果保存到W2。执行48位减法运算时,W2W1W0=X2X1X0-Y2Y1Y0,首先X1X0减去Y1Y0,结果保存到W1W0,产生借位位BORROW,再由X2减去Y2和借位位BORROW,结果保存到W2。两个Q15.32数相乘时,乘积是一个Q30.64数,出于前面实现SPLL时对动态范围和计算精度的要求,该Q30.64数可以双向截位为Q15.32的48位定点数。具体做法是保留符号位和整数部分的低15位以及小数部分的高32位。48位定点数的乘法由图4所示。

用48位扩展精度算法实现软件接收机中的SPLL,解决了浮点算法运算量大的问题,同时还具备浮点算法动态范围大、精度高的优点,已经成功应用于“创新一号”小卫星地面手持低功耗通信终端中。另外,本文提出的SPLL实现算法,通过修改环路滤波器系数,也可以应用在其他软件接收机中,具有很好的扩展性。

2 48位定点扩展精度算法

图3描述的算法在TMS320VC5510上用C语言直接利用浮点运算实现时,只能通过C编译器产生模拟浮点运算的定点指令。这种方法效率很低,每次环路计算需耗费875个指令周期。在调制数据速率为76.8kbps的数字接收机中,需要67.2MIPS的运算量。为了降低环路计算的运算量,同时保持浮点运算具有动态范围大、精度高的优点,笔者提出了一种48位定点扩展精度计算的方法。参加运算的每个操作数由三个16位定点数W2、W1、W0级联表示,其中高16位为二进制补码的整数部分,低32位为二进制补码的小数部分,符号位在最高位,也可称为Q15.32格式,。

除了以上加、减、乘三种基本运算外,48位定点扩展精度算法还包括取负(NEG_48)、数据拷贝(MOVE_48)两种操作。取负操作即将X1X0取负,结果保存到W1W0,产生借位位BORROW,再用0减去X2和借位位BORROW,结果保存到W2;数据拷贝,即把X1X0拷贝到W1W0,X2拷贝到W2。