BB199,115;中文规格书,Datasheet资料

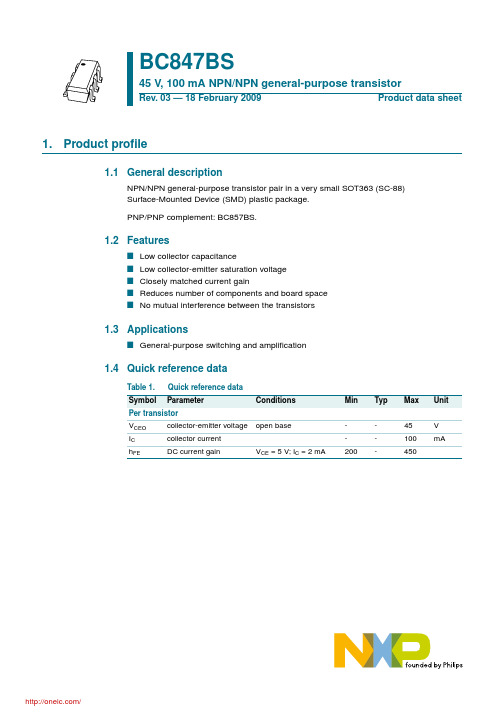

BC847BS,115;BC847BS,135;中文规格书,Datasheet资料

[1] Pulse test: tp ≤ 300 µs; δ ≤ 0.02.

BC847BS_3

Product data sheet

/

Rev. 03 — 18 February 2009

© NXP B.V. 2009. All rights reserved.

5 of 12

PNP/PNP complement: BC857BS.

1.2 Features

I Low collector capacitance I Low collector-emitter saturation voltage I Closely matched current gain I Reduces number of components and board space I No mutual interference between the transistors

103

Zth(j-a) (K/W)

102

δ=1 0.50 0.20

0.75 0.33

0.10

0.05 0.02

10 0.01

0

006aab421

1

10−5

10−4

10−3

10−2

10−1

1

10

102

103

tp (s)

Fig 3.

FR4 PCB, mounting pad for collector 1 cm2

current

-

-

15

nA

-

-

5

µA

-

-

100 nA

hFE

DC current gain

VCE = 5 V; IC = 2 mA

BAW56,215;BAW56W,115;BAW56W,135;BAW56T,115;BAW56S,135;中文规格书,Datasheet资料

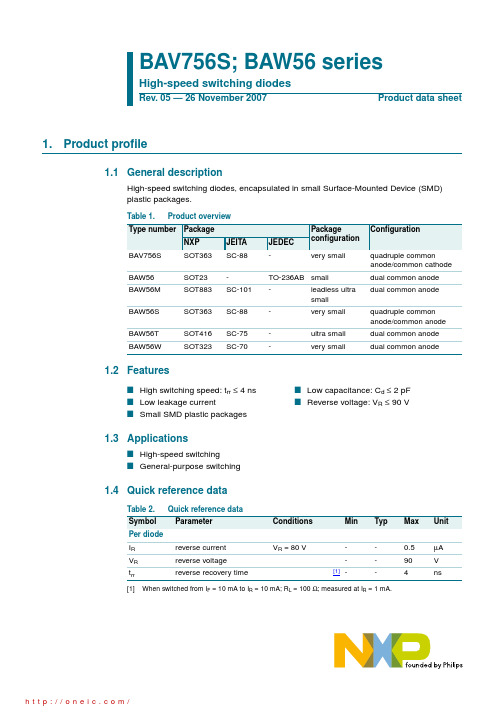

1.2 Features

I High switching speed: trr ≤ 4 ns I Low leakage current I Small SMD plastic packages

3. Ordering information

Table 4. Ordering information

Type number Package

Name

Description

BAV756S

SC-88

plastic surface-mounted package; 6 leads

BAW56

-

plastic surface-mounted package; 3 leads

-

-

625 K/W

BAV756S_BAW56_SER_5

Product data sheet

Rev. 05 — 26 November 2007

© NXP B.V. 2007. All rights reserved.

4 of 15

/

NXP Semiconductors

Symbol Parameter

Conditions

Min

IFRM

repetitive peak forward

-

current

IFSM

non-repetitive peak forward square wave

[1]

current

tp = 1 µs

-

tp = 1 ms

-

tp = 1 s

PMEG4020ER,115;中文规格书,Datasheet资料

PMEG4020ER_1

Product data sheet

/

Rev. 01 — 22 October 2009

© NXP B.V. 2009. All rights reserved.

4 of 13

NXP Semiconductors

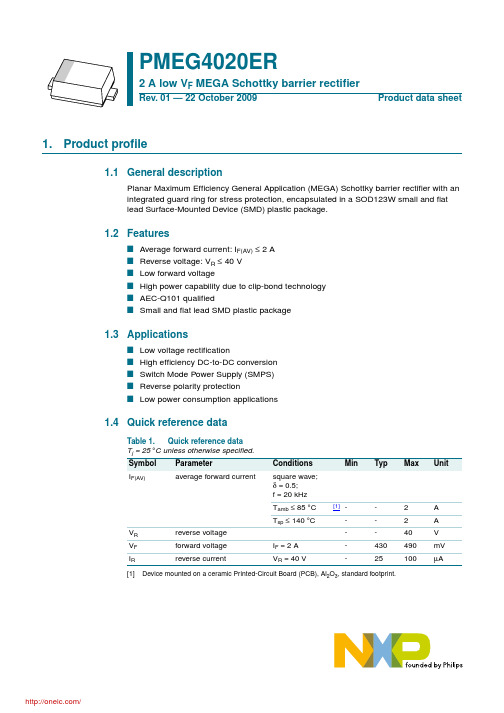

PMEG4020ER

2 A low VF MEGA Schottky barrier rectifier

7. Characteristics

Table 7. Characteristics Tj = 25 °C unless otherwise specified.

Symbol Parameter

Conditions

VF

forward voltage

IF = 0.1 A

IF = 1 A

IF = 2 A

IR

Version SOD123W

4. Marking

Table 4. Marking codes Type number PMEG4020ER

Marking code BE

5. Limiting values

Table 5. Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134).

2 A low VF MEGA Schottky barrier rectifier

2. Pinning information

Table 2. Pin 1 2

Pinning Description cathode anode

[1] The marking bar indicates the cathode.

1206;1205;中文规格书,Datasheet资料

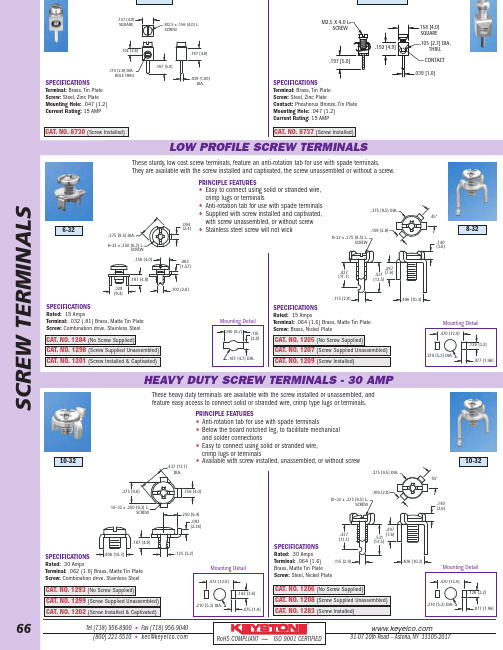

CAT.NO.1209(Screw Installed)CAT.NO.1207(Screw Supplied Unassembled)CAT.NO.1205(No Screw Supplied)CAT.NO.1283(Screw Installed)CAT.NO.1208(Screw Supplied Unassembled)CAT.NO.1206(No Screw Supplied)CAT.NO.1299(Screw Supplied Unassembled)CAT.NO.1202(Screw Installed &Captivated)CAT.NO.1201(Screw Installed &Captivated)CAT.NO.1298(Screw Supplied Unassembled)S C R E W T E R M I N A L S66HEAVY DUTY SCREW TERMINALS -30AMPThese sturdy,low cost screw terminals,feature an anti-rotation tab for use with spade terminals.They are available with the screw installed and captivated,the screw unassembled or without a screw..093[2.36].187[4.8].406[10.3].375[9.6].437[11.1]DIA..250[6.4].125[3.2]10-32 x .250 [6.3] L.SCREW.156[4.0]PRINCIPLE FEATURES•Easy to connect using solid or stranded wire,crimp lugs or terminals•Anti-rotation tab for use with spade terminals •Supplied with screw installed and captivated,with screw unassembled,or without screw •Stainless steel screw will not wickSPECIFICATIONSRated:15AmpsTerminal:.032(.81)Brass,Matte Tin Plate Screw:Combination drive,Stainless SteelSPECIFICATIONSRated:30AmpsTerminal:.062(1.6)Brass,Matte Tin Plate Screw:Combination drive,Stainless SteelMounting DetailMounting DetailThese heavy duty terminals are available with the screw installed or unassembled,and feature easy access to connect solid or stranded wire,crimp type lugs or terminals..375 [9.5]DIA.8-32 x .375 [9.5] L.SCREW.115 [2.9].531[13.5].437[11.1].140[3.6].297[7.6].406 [10.3].109[2.8]45°45°.109[2.8].406 [10.3].297[7.6].140[3.6].437[11.1].531[13.5].115 [2.9]10-32 x .375 [9.5] L.SCREW.375 [9.5]DIA..210 [5.3] DIA..077 [1.96].126 [3.2].470[12.0]SPECIFICATIONSRated:15AmpsTerminal:.064(1.6)Brass,Matte Tin Plate Screw:Brass,Nickel PlateSPECIFICATIONSRated:30AmpsTerminal:.064(1.6)Brass,Matte Tin Plate Screw:Steel,Nickel PlateMounting Detail.470[12.0].126 [3.2].077[1.96].210 [5.3] DIA.Mounting DetailPRINCIPLE FEATURES•Anti-rotation tab for use with spade terminals•Below the board notched leg,to facilitate mechanical and solder connections•Easy to connect using solid or stranded wire,crimp lugs or terminals•Available with screw installed,unassembled,or without screw.187[4.7]DIA..110[2.8].340[8.7].210 [5.3] DIA..075[1.9].142[3.6].472 [12.0].156[4.0].328[8.4].187 [4.8].094 [2.4].375 [9.5]DIA..100[2.6].062 [1.57]6-32x .250[6.3] L.SCREWLOW PROFILE SCREW TERMINALS10-328-32CAT.NO.1284(No Screw Supplied)CAT.NO.1293(No Screw Supplied)10-326-32Tel (718)956-8900•Fax (718)956-9040(800)221-5510•kec@31-0720th Road –Astoria,NY 11105-2017RoHS COMPLIANT ~ISO 9001CERTIFIED®THRU HOLECAT.NO.8730(Screw Installed).102 [2.6].039[1.00]DIA..187 [4.8].197 [5.0].157[4.0]SQUAREM2.5 x .156[4.0]L.SCREW.110 [2.8] DIA.HOLE THRUSPECIFICATIONSTerminal:Brass,Tin Plate Screw:Steel,Zinc Plate Mounting Hole:.047(1.2)Current Rating:15AMPWIRE CONTACTCAT.NO.8737(Screw Installed)CONTACT .197[5.0].039[1.0].192[4.9].105[2.7]DIA.THRU..158[4.0]SQUAREM2.5X 4.0L.SCREWSPECIFICATIONSTerminal:Brass,Tin Plate Screw:Steel,Zinc PlateContact:Phoshorus Bronze,Tin Plate Mounting Hole:.047(1.2)Current Rating:15AMP分销商库存信息: KEYSTONE-ELECTRONICS 12061205。

BFG198,115;中文规格书,Datasheet资料

1995 Sep 12

4

/

NXP Semiconductors

Product specification

NPN GHz wideband transistor

BFG198

LIMITING VALUES In accordance with the Absolute Maximum System (IEC 134). SYMBOL VCBO VCEO VEBO IC Ptot Tstg Tj Note 1. Ts is the temperature at the soldering point of the collector tab. 1995 Sep 12 2 PARAMETER collector-base voltage collector-emitter voltage emitter-base voltage DC collector current total power dissipation storage temperature junction temperature up to Ts = 135 C (note 1) open emitter open base open collector CONDITIONS 65 MIN. MAX. 20 10 2.5 100 1 +150 175 UNIT V V V mA W C C

C5 L4 L3 C4 L5 L6 C6 R1 R2 L1 L2 DUT R3 R4

MBB754

VCC = 8 V

output 75 Ω

Fig.2 Intermodulation distortion and second order intermodulation distortion test circuit. List of components (see test circuit) DESIGNATION C2 C1, C4, C6, C7 C3 C5 (note 1) C8 L1 (note 1) L2 L3 (note 1) L4 (note 1) L5 L6 R1 R2 (note 1) R3, R4 Note 1. Components C5, L1, L3, L4, and R2 are mounted on the underside of the PCB. The circuit is constructed on a double copper-clad printed circuit board with PTFE dielectric (r = 2.2); thickness 116 inch; thickness of copper sheet 2 x 35 m; see Fig.2. DESCRIPTION multilayer ceramic capacitor multilayer ceramic capacitor multilayer ceramic capacitor multilayer ceramic capacitor multilayer ceramic capacitor 1.5 turns 0.4 mm copper wire microstripline 0.4 mm copper wire 0.4 mm copper wire microstripline Ferroxcube choke metal film resistor metal film resistor metal film resistor 75 24 3.6 75 5 10 220 30 nH nH H VALUE 1.2 10 10 10 1.5 UNIT pF nF nF nF pF int. dia. 3 mm; winding pitch 1 mm length 22 mm; width 2.5 mm length 30 mm length 4 mm length 19 mm; width 2.5 mm 3122 108 20153 2322 180 73103 2322 180 73221 2322 180 73309 DIMENSIONS CATALOGUE NO. 2222 851 12128 2222 590 08627 2222 851 12128 2222 629 08103 2222 851 12158

P89LPC935FA,129,P89LPC936FDH系列,P89LPC935FDH,529,P89LPC933FDH系列规格书,Datasheet 资料

1. General descriptionThe P89LPC933/934/935/936 is a single-chip microcontroller, available in low costpackages, based on a high performance processor architecture that executes instructions in two to four clocks, six times the rate of standard 80C51 devices. Many system-level functions have been incorporated into the P89LPC933/934/935/936 in order to reduce component count, board space, and system cost.2. Features and benefits2.1Principal features4kB/8kB/16kB byte-erasable flash code memory organized into 1kB/2 kB sectorsand 64-byte pages. Single-byte erasing allows any byte(s) to be used as non-volatile data storage.256-byte RAM data memory. Both the P89LPC935 and P89LPC936 also include a512-byte auxiliary on-chip RAM.512-byte customer data EEPROM on chip allows serialization of devices, storage ofsetup parameters, etc. (P89LPC935/936).Dual 4-input multiplexed 8-bit A/D converters/DAC outputs (P89LPC935/936, singleA/D on P89LPC933/934).Two analog comparators with selectable inputs and reference source.Two 16-bit counter/timers (each may be configured to toggle a port output upon timeroverflow or to become a PWM output) and a 23-bit system timer that can also be used as an RTC.Enhanced UART with fractional baud rate generator, break detect, framing errordetection, and automatic address detection; 400kHz byte-wide I 2C-bus communication port and SPI communication port.Capture/Compare Unit (CCU) provides PWM, input capture, and output comparefunctions (P89LPC935/936).High-accuracy internal RC oscillator option allows operation without external oscillatorcomponents. The RC oscillator option is selectable and fine tunable.2.4V to3.6V V DD operating range. I/O pins are 5V tolerant (may be pulled up ordriven to 5.5V).28-pin TSSOP , PLCC, and HVQFN packages with 23 I/O pins minimum and up to 26I/O pins while using on-chip oscillator and reset options.P89LPC933/934/935/9368-bit microcontroller with accelerated two-clock 80C51 core 4 kB/8 kB/16 kB 3 V byte-erasable flash with 8-bit ADCsRev. 8 — 12 January 2011Product data sheet2.2Additional featuresA high performance 80C51 CPU provides instruction cycle times of 111ns to 222nsfor all instructions except multiply and divide when executing at 18MHz. This is sixtimes the performance of the standard 80C51 running at the same clock frequency. Alower clock frequency for the same performance results in power savings and reduced EMI.Serial flash In-Circuit Programming (ICP) allows simple production coding with commercial EPROM programmers. Flash security bits prevent reading of sensitiveapplication programs.Serial flash In-System Programming (ISP) allows coding while the device is mounted in the end application.In-Application Programming (IAP) of the flash code memory. This allows changing the code in a running application.Watchdog timer with separate on-chip oscillator, requiring no external components.The watchdog prescaler is selectable from eight values.Low voltage reset (brownout detect) allows a graceful system shutdown when power fails. May optionally be configured as an interrupt.Idle and two different power-down reduced power modes. Improved wake-up from Power-down mode (a LOW interrupt input starts execution). Typical power-downcurrent is 1μA (total power-down with voltage comparators disabled).Active-LOW reset. On-chip power-on reset allows operation without external reset components. A reset counter and reset glitch suppression circuitry prevent spuriousand incomplete resets. A software reset function is also available.Configurable on-chip oscillator with frequency range options selected by user programmed flash configuration bits. Oscillator options support frequencies from20kHz to the maximum operating frequency of 18MHz.Oscillator fail detect. The watchdog timer has a separate fully on-chip oscillator allowing it to perform an oscillator fail detect function.Programmable port output configuration options: quasi-bidirectional, open drain, push-pull, input-only.Port ‘input pattern match’ detect. Port0 may generate an interrupt when the value of the pins match or do not match a programmable pattern.LED drive capability (20mA) on all port pins. A maximum limit is specified for the entire chip.Controlled slew rate port outputs to reduce EMI. Outputs have approximately 10ns minimum ramp times.Only power and ground connections are required to operate theP89LPC933/934/935/936 when internal reset option is selected.Four interrupt priority levels.Eight keypad interrupt inputs, plus two additional external interrupt inputs.Schmitt trigger port inputs.Second data pointer.Emulation support.3. Product comparison overviewTable 1 highlights the differences between the four devices. For a complete list of device features please see Section 2 “Features and benefits”.4. Ordering information4.1Ordering optionsTable 1.Product comparison overviewDeviceFlash memory Sector size ADC1ADC0CCU Data EEPROM P89LPC933 4 kB 1 kB X ---P89LPC9348 kB 1 kB X ---P89LPC9358 kB 1 kB X X X X P89LPC93616 kB2 kBXXXXTable 2.Ordering informationType number Package NameDescriptionVersion P89LPC935FA PLCC28plastic leaded chip carrier; 28 leads SOT261-2P89LPC933HDH TSSOP28plastic thin shrink small outlinepackage; 28leads; body width 4.4mmSOT361-1P89LPC933FDH P89LPC934FDH P89LPC935FDH P89LPC936FDH P89LPC935FHNHVQFN28plastic thermal enhanced very thin quad flat package; no leads;28terminals; body 6×6×0.85mmSOT788-1Table 3.Ordering optionsType number Flash memory Temperature range Frequency P89LPC933HDH 4 kB −40°C to +125°C 0MHz to 18MHzP89LPC933FDH 4kB −40°C to +85°CP89LPC935FA 8kBP89LPC934FDH P89LPC935FDH P89LPC935FHN P89LPC936FDH16kB5. Block diagram6. Pinning information6.1Pinning6.2Pin descriptionTable 4.Pin descriptionSymbol Pin Type DescriptionTSSOP28,PLCC28HVQFN28P0.0 to P0.7I/O Port0: Port0 is an 8-bit I/O port with a user-configurable output type.During reset Port0 latches are configured in the input only mode with theinternal pull-up disabled. The operation of Port0 pins as inputs andoutputs depends upon the port configuration selected. Each port pin isconfigured independently. Refer to Section 8.13.1 “Port configurations”and Table 11 “Static characteristics” for details.The Keypad Interrupt feature operates with Port0 pins.All pins have Schmitt trigger inputs.Port0 also provides various special functions as described below:P0.0/CMP2/ KBI0/AD01327I/O P0.0 — Port0 bit0.O CMP2 — Comparator2 output.I KBI0 — Keyboard input0.I AD01 — ADC0 channel 1 analog input. (P89LPC935/936)P0.1/CIN2B/ KBI1/AD102622I/O P0.1 — Port0 bit1.I CIN2B — Comparator2 positive input B.I KBI1 — Keyboard input1.I AD10 — ADC1 channel 0 analog input.P0.2/CIN2A/ KBI2/AD112521I/O P0.2 — Port0 bit2.I CIN2A — Comparator2 positive input A.I KBI2 — Keyboard input2.I AD11 — ADC1 channel 1 analog input.P0.3/CIN1B/ KBI3/AD122420I/O P0.3 — Port0 bit3.I CIN1B — Comparator1 positive input B.I KBI3 — Keyboard input3.I AD12 — ADC1 channel 2 analog input.P0.4/CIN1A/ KBI4/DAC1/ AD132319I/O P0.4 — Port0 bit4.I CIN1A — Comparator1 positive input A.I KBI4 — Keyboard input4.O DAC1 — Digital-to-analog converter output 1.I AD13 — ADC1 channel 3 analog input.P0.5/ CMPREF/ KBI52218I/O P0.5 — Port0 bit5.I CMPREF — Comparator reference (negative) input.I KBI5 — Keyboard input5.P0.6/CMP1/ KBI62016I/O P0.6 — Port0 bit6.O CMP1 — Comparator1 output.I KBI6 — Keyboard input6.P0.7/T1/ KBI71915I/O P0.7 — Port0 bit7.I/O T1 — Timer/counter1 external count input or overflow output.I KBI7 — Keyboard input7.P1.0 to P1.7I/O, I [1]Port1: Port1 is an 8-bit I/O port with a user-configurable output type,except for three pins as noted below. During reset Port1 latches areconfigured in the input only mode with the internal pull-up disabled. Theoperation of the configurable Port1 pins as inputs and outputs dependsupon the port configuration selected. Each of the configurable port pinsare programmed independently. Refer to Section 8.13.1 “Portconfigurations” and Table 11 “Static characteristics” for details. P1.2 andP1.3 are open drain when used as outputs. P1.5 is input only.All pins have Schmitt trigger inputs.Port1 also provides various special functions as described below:P1.0/TXD1814I/O P1.0 — Port1 bit0.O TXD — Transmitter output for the serial port.P1.1/RXD1713I/O P1.1 — Port1 bit1.I RXD — Receiver input for the serial port.P1.2/T0/SCL128I/O P1.2 — Port1 bit2 (open-drain when used as output).I/O T0 — Timer/counter0 external count input or overflow output (open-drainwhen used as output).I/O SCL — I2C serial clock input/output.P1.3/INT0/ SDA 117I/O P1.3 — Port1 bit3 (open-drain when used as output).I INT0 — External interrupt0 input.I/O SDA — I2C serial data input/output.P1.4/INT1106I P1.4 — Port1 bit4.I INT1 — External interrupt1 input.P1.5/RST62I P1.5 — Port1 bit5 (input only).I RST — External reset input during power-on or if selected via UCFG1.When functioning as a reset input, a LOW on this pin resets themicrocontroller, causing I/O ports and peripherals to take on their defaultstates, and the processor begins execution at address0. Also used duringa power-on sequence to force ISP mode. When using an oscillatorfrequency above 12MHz, the reset input function of P1.5 must beenabled. An external circuit is required to hold the device in reset atpower-up until VDD has reached its specified level. When systempower is removed VDD will fall below the minimum specifiedoperating voltage. When using an oscillator frequency above12MHz, in some applications, an external brownout detect circuitmay be required to hold the device in reset when VDD falls below theminimum specified operating voltage.P1.6/OCB51I/O P1.6 — Port1 bit6.O OCB — Output Compare B. (P89LPC935/936)P1.7/OCC/ AD00428I/O P1.7 — Port1 bit7.O OCC — Output Compare C. (P89LPC935/936)I AD00 — ADC0 channel 0 analog input. (P89LPC935/936)Table 4.Pin description …continuedSymbol Pin Type Description TSSOP28,PLCC28HVQFN28P2.0 to P2.7I/OPort 2: Port 2 is an 8-bit I/O port with a user-configurable output type. During reset Port 2 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 2 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to Section 8.13.1 “Port configurations” and Table 11 “Static characteristics” for details.All pins have Schmitt trigger inputs.Port 2 also provides various special functions as described below:P2.0/ICB/ DAC0/AD03125I/O P2.0 — Port 2 bit 0.I ICB — Input Capture B. (P89LPC935/936)I DAC0 — Digital-to-analog converter output.IAD03 — ADC0 channel 3 analog input. (P89LPC935/936)P2.1/OCD/ AD02226I/O P2.1 — Port 2 bit 1.O OCD — Output Compare D. (P89LPC935/936)IAD02 — ADC0 channel 2 analog input. (P89LPC935/936)P2.2/MOSI 139I/O P2.2 — Port 2 bit 2.I/OMOSI — SPI master out slave in. When configured as master, this pin is output; when configured as slave, this pin is input.P2.3/MISO 1410I/O P2.3 — Port 2 bit 3.I/OMISO — When configured as master, this pin is input, when configured as slave, this pin is output.P2.4/SS 1511I/O P2.4 — Port 2 bit 4.I SS — SPI Slave select.P2.5/ SPICLK 1612I/O P2.5 — Port 2 bit 5.I/OSPICLK — SPI clock. When configured as master, this pin is output; when configured as slave, this pin is input. P2.6/OCA 2723I/O P2.6 — Port 2 bit 6.O OCA — Output Compare A. (P89LPC935/936)P2.7/ICA2824I/O P2.7 — Port 2 bit 7.IICA — Input Capture A. (P89LPC935/936)Table 4.Pin description …continuedSymbolPinTypeDescriptionTSSOP28, PLCC28HVQFN28[1]Input/output for P1.0 to P1.4, P1.6, P1.7. Input for P1.5.P3.0 to P3.1I/OPort 3: Port 3 is a 2-bit I/O port with a user-configurable output type.During reset Port 3 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 3 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to Section 8.13.1 “Port configurations” and Table 11 “Static characteristics” for details.All pins have Schmitt trigger inputs.Port 3 also provides various special functions as described below:P3.0/XTAL2/ CLKOUT95I/O P3.0 — Port 3 bit 0.O XTAL2 — Output from the oscillator amplifier (when a crystal oscillator option is selected via the flash configuration.OCLKOUT — CPU clock divided by 2 when enabled via SFR bit (ENCLK - TRIM.6). It can be used if the CPU clock is the internal RC oscillator, watchdog oscillator or external clock input, except when XTAL1/XTAL2 are used to generate clock source for the RTC/system timer.P3.1/XTAL184I/O P3.1 — Port 3 bit 1.IXTAL1 — Input to the oscillator circuit and internal clock generator circuits (when selected via the flash configuration). It can be a port pin if internal RC oscillator or watchdog oscillator is used as the CPU clock source, and if XTAL1/XTAL2 are not used to generate the clock for the RTC/system timer.V SS 73I Ground: 0V reference.V DD2117IPower supply: This is the power supply voltage for normal operation as well as Idle and Power-down modes.Table 4.Pin description …continuedSymbolPinTypeDescriptionTSSOP28, PLCC28HVQFN287. Logic symbols8. Functional descriptionRemark: Please refer to the P89LPC933/934/935/936 User manual for a more detailedfunctional description.8.1Special function registersRemark: SFR accesses are restricted in the following ways:•User must not attempt to access any SFR locations not defined.•Accesses to any defined SFR locations must be strictly for the functions for the SFRs.•SFR bits labeled ‘-’, logic 0 or logic 1 can only be written and read as follows:–‘-’ Unless otherwise specified, must be written with logic 0, but can return anyvalue when read (even if it was written with logic 0). It is a reserved bit and may beused in future derivatives.–Logic 0 must be written with logic 0, and will return a logic 0 when read.–Logic 1 must be written with logic 1, and will return a logic 1 when read.P89LPC933_934_935_936All information provided in this document is subject to legal disclaimers.© NXP B.V. 2011. All rights reserved.Product data sheet Rev. 8 — 12 January 2011 13 of 77NXP Semiconductors P89LPC933/934/935/9368-bit microcontroller with accelerated two-clock 80C51 coreTable 5.Special function registers - P89LPC933/934* indicates SFRs that are bit addressable. Name Description SFR addr.Bit functions and addresses Reset valueMSB LSB Hex Binary Bit address E7E6E5E4E3E2E1E0ACC*Accumulator E0H 0000000000ADCON0A/D control register 08EH -----ENADC0--0000000000ADCON1A/D control register 197H ENBI1ENADCI 1TMM1EDGE1ADCI1ENADC1ADCS11ADCS100000000000ADINS A/D input select A3H ADI13ADI12ADI11ADI10----0000000000ADMODA A/D mode register A C0H BNDI1BURST1SCC1SCAN1----0000000000ADMODB A/D mode register B A1H CLK2CLK1CLK0-ENDAC1ENDAC0BSA1-00000x 0000AD0DAT3A/D_0 data register 3F4H 0000000000AD1BH A/D_1 boundary high register C4H FF 11111111AD1BL A/D_1 boundary low register BCH 0000000000AD1DAT0A/D_1 data register 0D5H 0000000000AD1DAT1A/D_1 data register 1D6H 0000000000AD1DAT2A/D_1 data register 2D7H 0000000000AD1DAT3A/D_1 data register 3F5H 0000000000AUXR1Auxiliary function register A2H CLKLP EBRR ENT1ENT0SRST 0-DPS 00[1]000000x0Bit address F7F6F5F4F3F2F1F0B* B register F0H 0000000000BRGR0Baud rate generator rate low BEH 00[2]00000000BRGR1Baud rate generator rate high BFH 00[1][2]00000000BRGCON Baudrate generator control BDH ------SBRGS BRGEN 00[2]xxxx xx00CMP1Comparator 1 control register ACH --CE1CP1CN1OE1CO1CMF100[1]xx000000CMP2Comparator 2 control register ADH --CE2CP2CN2OE2CO2CMF200[1]xx000000DIVM CPU clock divide-by-M control95H 0000000000DPTR Data pointer (2bytes)DPH Data pointer high 83H 0000000000DPL Data pointer low 82H 0000000000FMADRH Program flash address high E7H 0000000000芯天下--/P89LPC933_934_935_936All information provided in this document is subject to legal disclaimers.© NXP B.V. 2011. All rights reserved.Product data sheet Rev. 8 — 12 January 2011 14 of 77NXP Semiconductors P89LPC933/934/935/9368-bit microcontroller with accelerated two-clock 80C51 core FMADRL Program flash address low E6H 0000000000FMCON Program flash control (Read)E4H BUSY ---HVA HVE SV OI 7001110000Program flash control (Write)E4H FMCMD.7FMCMD.6FMCMD.5FMCMD.4FMCMD.3FMCMD.2FMCMD.1FMCMD.FMDATA Program flash data E5H 0000000000I2ADR I 2C slave address register DBH I2ADR.6I2ADR.5I2ADR.4I2ADR.3I2ADR.2I2ADR.1I2ADR.0GC 0000000000Bit address DF DE DD DC DB DA D9D8I2CON*I 2C control register D8H -I2EN STA STO SI AA -CRSEL 00x00000x0I2DAT I 2C data register DAHI2SCLH Serial clock generator/SCL duty cycle register highDDH 0000000000I2SCLL Serial clock generator/SCL duty cycle register lowDCH 0000000000I2STAT I 2C status register D9H STA.4STA.3STA.2STA.1STA.0000F811111000ICRAH Input capture A register high ABH 0000000000ICRAL Input capture A register low AAH 0000000000ICRBH Input capture B register high AFH 0000000000ICRBL Input capture B register low AEH 0000000000Bit address AF AE AD AC AB AA A9A8IEN0*Interrupt enable 0A8H EA EWDRT EBO ES/ESR ET1EX1ET0EX00000000000Bit address EF EE ED EC EB EA E9E8IEN1*Interrupt enable 1E8H EAD EST --ESPI EC EKBI EI2C 00[3]00x00000Bit address BF BE BD BC BB BA B9B8IP0*Interrupt priority 0B8H -PWDRT PBO PS/PSR PT1PX1PT0PX000[3]x0000000IP0H Interrupt priority 0 high B7H -PWDRT H PBOH PSH/ PSRHPT1H PX1H PT0H PX0H 00[3]x0000000Bit address FF FE FD FC FB FA F9F8IP1*Interrupt priority 1F8H PAD PST --PSPI PC PKBI PI2C 00[3]00x00000IP1H Interrupt priority 1 high F7H PADH PSTH --PSPIH PCH PKBIH PI2CH 00[3]00x00000Table 5.Special function registers - P89LPC933/934 …continued* indicates SFRs that are bit addressable.Name Description SFR addr.Bit functions and addresses Reset valueMSB LSB Hex Binary芯天下--/P89LPC933_934_935_936All information provided in this document is subject to legal disclaimers.© NXP B.V. 2011. All rights reserved.Product data sheet Rev. 8 — 12 January 2011 15 of 77NXP Semiconductors P89LPC933/934/935/9368-bit microcontroller with accelerated two-clock 80C51 core KBCON Keypad control register 94H ------PATN _SELKBIF 00[3]xxxx xx00KBMASK Keypad interrupt mask register 86H 0000000000KBPATN Keypad pattern register 93H FF 11111111Bit address 8786858483828180P0*Port 080H T1/KB7CMP1/KB6CMPREF /KB5CIN1A /KB4CIN1B /KB3CIN2A /KB2CIN2B /KB1CMP2/KB0[3]Bit address 9796959493929190P1*Port 190H --RST INT1INT0/ SDAT0/SCL RXD TXD [3]Bit address A7A6A5A4A3A2A1A0P2*Port 2A0H --SPICLK SS MISO MOSI --[3]Bit address B7B6B5B4B3B2B1B0P3*Port 3B0H ------XTAL1XTAL2[3]P0M1Port 0 output mode 184H (P0M1.7)(P0M1.6)(P0M1.5)(P0M1.4)(P0M1.3)(P0M1.2)(P0M1.1)(P0M1.0)FF [3]11111111P0M2Port 0 output mode 285H (P0M2.7)(P0M2.6)(P0M2.5)(P0M2.4)(P0M2.3)(P0M2.2)(P0M2.1)(P0M2.0)00[3]00000000P1M1Port 1 output mode 191H (P1M1.7)(P1M1.6)-(P1M1.4)(P1M1.3)(P1M1.2)(P1M1.1)(P1M1.0)D3[3]11x1xx11P1M2Port 1 output mode 292H (P1M2.7)(P1M2.6)-(P1M2.4)(P1M2.3)(P1M2.2)(P1M2.1)(P1M2.0)00[3]00x0xx00P2M1Port 2 output mode 1A4H (P2M1.7)(P2M1.6)(P2M1.5)(P2M1.4)(P2M1.3)(P2M1.2)(P2M1.1)(P2M1.0)FF [3]11111111P2M2Port 2 output mode 2A5H (P2M2.7)(P2M2.6)(P2M2.5)(P2M2.4)(P2M2.3)(P2M2.2)(P2M2.1)(P2M2.0)00[3]00000000P3M1Port 3output mode 1B1H ------(P3M1.1)(P3M1.0)03[3]xxxx xx11P3M2Port 3 output mode 2B2H ------(P3M2.1)(P3M2.0)00[3]xxxx xx00PCON Power control register 87H SMOD1SMOD0BOPD BOI GF1GF0PMOD1PMOD00000000000PCONA Power control register A B5H RTCPD -VCPD ADPD I2PD SPPD SPD -00[3]00000000Bitaddress D7D6D5D4D3D2D1D0PSW*Program status word D0H CY AC F0RS1RS0OV F1P 0000000000PT0AD Port 0 digital input disable F6H --PT0AD.5PT0AD.4PT0AD.3PT0AD.2PT0AD.1-00xx00000x RSTSRC Reset source register DFH --BOF POF R_BK R_WD R_SF R_EX [4]RTCCON Real-time clock control D1H RTCF RTCS1RTCS0---ERTC RTCEN 60[3][5]011x xx00Table 5.Special function registers - P89LPC933/934 …continued* indicates SFRs that are bit addressable.Name Description SFR addr.Bit functions and addresses Reset valueMSB LSB Hex Binary芯天下--/P89LPC933_934_935_936All information provided in this document is subject to legal disclaimers.© NXP B.V. 2011. All rights reserved.Product data sheet Rev. 8 — 12 January 2011 16 of 77NXP Semiconductors P89LPC933/934/935/9368-bit microcontroller with accelerated two-clock 80C51 core RTCH Real-time clock register high D2H 00[5]00000000RTCL Real-time clock register low D3H 00[5]00000000SADDR Serial port address register A9H 0000000000SADEN Serial port address enable B9H 0000000000SBUF Serial Port data buffer register 99H xx xxxx xxxxBit address 9F 9E 9D 9C 9B 9A 9998SCON*Serial port control 98H SM0/FE SM1SM2REN TB8RB8TI RI 0000000000SSTAT Serial port extended status registerBAH DBMOD INTLO CIDIS DBISEL FE BR OE STINT 0000000000SP Stack pointer 81H 0700000111SPCTL SPI control register E2H SSIG SPEN DORD MSTR CPOL CPHA SPR1SPR00400000100SPSTAT SPI status register E1H SPIF WCOL ------0000xx xxxx SPDAT SPI data register E3H 0000000000TAMOD Timer 0 and 1 auxiliary mode 8FH ---T1M2---T0M200xxx0xxx0Bit address 8F 8E 8D 8C 8B 8A 8988TCON*Timer 0 and 1 control 88H TF1TR1TF0TR0IE1IT1IE0IT00000000000TH0Timer 0 high 8CH 0000000000TH1Timer 1 high 8DH 0000000000TL0Timer 0 low 8AH 0000000000TL1Timer 1 low 8BH 0000000000TMOD Timer 0 and 1 mode 89H T1GATE T1C/T T1M1T1M0T0GATE T0C/T T0M1T0M00000000000TRIM Internal oscillator trim register 96H RCCLK ENCLK TRIM.5TRIM.4TRIM.3TRIM.2TRIM.1TRIM.0[6] [5]WDCON Watchdog control register A7H PRE2PRE1PRE0--WDRUN WDTOF WDCLK [7] [5]Table 5.Special function registers - P89LPC933/934 …continued* indicates SFRs that are bit addressable.Name Description SFR addr.Bit functions and addresses Reset valueMSB LSB Hex Binary芯天下--/P89LPC933_934_935_936All information provided in this document is subject to legal disclaimers.© NXP B.V. 2011. All rights reserved.Product data sheet Rev. 8 — 12 January 2011 17 of 77NXP Semiconductors P89LPC933/934/935/9368-bit microcontroller with accelerated two-clock 80C51 core[1]Unimplemented bits in SFRs (labeled ’-’) are X (unknown) at all times. Unless otherwise specified, ones should not be written to these bits since they may be used for otherpurposes in future derivatives. The reset values shown for these bits are logic 0s although they are unknown when read.[2]BRGR1 and BRGR0 must only be written if BRGEN in BRGCON SFR is logic 0. If any are written while BRGEN =1, the result is unpredictable.[3]All ports are in input only (high-impedance) state after power-up.[4]The RSTSRC register reflects the cause of the P89LPC933/934/935/936 reset. Upon a power-up reset, all reset source flags are cleared except POF and BOF; the power-on resetvalue is xx110000.[5]The only reset source that affects these SFRs is power-on reset.[6]On power-on reset, the TRIM SFR is initialized with a factory preprogrammed value. Other resets will not cause initialization of the TRIM register.[7]After reset, the value is 111001x1, i.e., PRE2 to PRE0 are all logic 1, WDRUN =1 and WDCLK =1. WDTOF bit is logic 1 after watchdog reset and is logic 0 after power-on reset.Other resets will not affect WDTOF.WDL Watchdog load C1H FF 11111111WFEED1Watchdog feed 1C2HWFEED2Watchdog feed 2C3HTable 5.Special function registers - P89LPC933/934 …continued* indicates SFRs that are bit addressable.Name Description SFR addr.Bit functions and addresses Reset valueMSB LSB Hex Binary芯天下--/P89LPC933_934_935_936All information provided in this document is subject to legal disclaimers.© NXP B.V. 2011. All rights reserved.Product data sheet Rev. 8 — 12 January 2011 18 of 77NXP Semiconductors P89LPC933/934/935/9368-bit microcontroller with accelerated two-clock 80C51 coreTable 6.Special function registers - P89LPC935/936* indicates SFRs that are bit addressable. Name Description SFR addr.Bit functions and addresses Reset valueMSB LSB Hex BinaryBit address E7E6E5E4E3E2E1E0ACC*Accumulator E0H 0000000000ADCON0A/D control register 08EH ENBI0ENADCI 0TMM0EDGE0ADCI0ENADC0ADCS01ADCS000000000000ADCON1A/D control register 197H ENBI1ENADCI 1TMM1EDGE1ADCI1ENADC1ADCS11ADCS100000000000ADINS A/D input select A3H ADI13ADI12ADI11ADI10ADI03ADI02ADI01ADI000000000000ADMODA A/D mode register A C0H BNDI1BURST1SCC1SCAN1BNDI0BURST0SCC0SCAN00000000000ADMODB A/D mode register B A1H CLK2CLK1CLK0-ENDAC1ENDAC0BSA1BSA000000x 0000AD0BH A/D_0 boundary high register BBH FF 11111111AD0BL A/D_0 boundary low register A6H 0000000000AD0DAT0A/D_0 data register 0C5H 0000000000AD0DAT1A/D_0 data register 1C6H 0000000000AD0DAT2A/D_0 data register 2C7H 0000000000AD0DAT3A/D_0 data register 3F4H 0000000000AD1BH A/D_1 boundary high register C4H FF 11111111AD1BL A/D_1 boundary low register BCH 0000000000AD1DAT0A/D_1 data register 0D5H 0000000000AD1DAT1A/D_1 data register 1D6H 0000000000AD1DAT2A/D_1 data register 2D7H 0000000000AD1DAT3A/D_1 data register 3F5H 0000000000AUXR1Auxiliary function register A2H CLKLP EBRR ENT1ENT0SRST 0-DPS 00000000x0Bit address F7F6F5F4F3F2F1F0B* B register F0H 0000000000BRGR0[2]Baud rate generator rate low BEH 0000000000BRGR1[2]Baud rate generator rate high BFH 0000000000BRGCON Baudrate generator control BDH ------SBRGS BRGEN 00[2]xxxx xx00CCCRA Capture compare A control registerEAH ICECA2ICECA1ICECA0ICESA ICNFA FCOA OCMA1OCMA00000000000芯天下--/P89LPC933_934_935_936All information provided in this document is subject to legal disclaimers.© NXP B.V. 2011. All rights reserved.Product data sheet Rev. 8 — 12 January 2011 19 of 77NXP Semiconductors P89LPC933/934/935/9368-bit microcontroller with accelerated two-clock 80C51 core CCCRB Capture compare B control registerEBH ICECB2ICECB1ICECB0ICESB ICNFB FCOB OCMB1OCMB00000000000CCCRC Capture compare C control register ECH -----FCOC OCMC1OCMC000xxxx x000CCCRD Capture compare D control registerEDH -----FCOD OCMD1OCMD000xxxx x000CMP1Comparator 1 control register ACH --CE1CP1CN1OE1CO1CMF100[3]xx000000CMP2Comparator 2 control register ADH --CE2CP2CN2OE2CO2CMF200[3]xx000000DEECON Data EEPROM control registerF1H EEIF HVERR ECTL1ECTL0---EADR80E 00001110DEEDAT Data EEPROM data register F2H 0000000000DEEADR Data EEPROM address registerF3H 0000000000DIVM CPU clock divide-by-M control95H 0000000000DPTR Data pointer (2bytes)DPH Data pointer high 83H 0000000000DPL Data pointer low 82H 0000000000FMADRH Program flash address high E7H 0000000000FMADRL Program flash address low E6H 0000000000FMCON Program flash control (Read)E4H BUSY ---HVA HVE SV OI 7001110000Program flash control (Write)E4H FMCMD.7FMCMD.6FMCMD.5FMCMD.4FMCMD.3FMCMD.2FMCMD.1FMCMD.FMDATA Program flash data E5H 0000000000I2ADR I 2C slave address register DBH I2ADR.6I2ADR.5I2ADR.4I2ADR.3I2ADR.2I2ADR.1I2ADR.0GC 0000000000Bitaddress DF DE DD DC DB DA D9D8I2CON*I 2C control register D8H -I2EN STA STO SI AA -CRSEL 00x00000x0I2DAT I 2C data register DAHI2SCLH Serial clock generator/SCL duty cycle register highDDH 0000000000Table 6.Special function registers - P89LPC935/936 …continued* indicates SFRs that are bit addressable.Name Description SFR addr.Bit functions and addresses Reset valueMSB LSB Hex Binary芯天下--/。

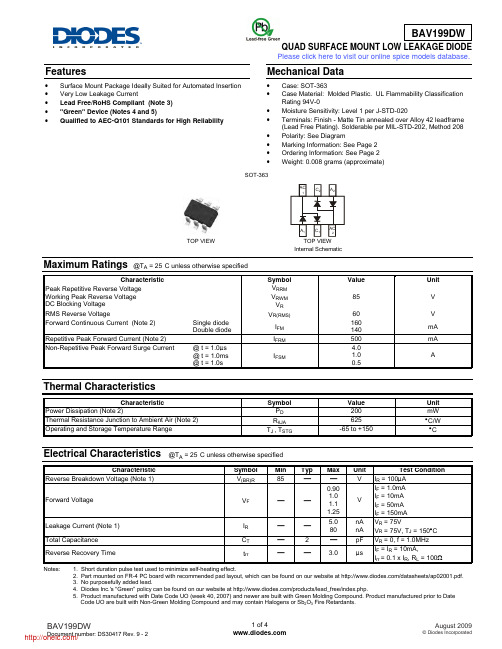

BAV199DW-7-F;BAV199DW-7;中文规格书,Datasheet资料

SOT-363

AC

1

C2

A2

TOP VIEW

A1

C1

AC

2

TOP VIEW

Internal Schematic

Maximum Ratings @TA = 25°C unless otherwise specified

Characteristic

Symbol

Value

Unit

Peak Repetitive Reverse Voltage Working Peak Reverse Voltage DC Blocking Voltage

1 of 4

August 2009

© Diodes Incorporated

PD, POWER DISSIPATION (mW)

300 250

200

150

100

50

0

0

25 50 75 100 125 150

TA, AMBIENT TEMPERATURE (°C) Fig. 1 Power Derating Curve, Total Package

Notes:

1. Short duration pulse test used to minimize self-heating effect. 2. Part mounted on FR-4 PC board with recommended pad layout, which can be found on our website at /datasheets/ap02001.pdf. 3. No purposefully added lead. 4. Diodes Inc.'s "Green" policy can be found on our website at /products/lead_free/index.php. 5. Product manufactured with Date Code UO (week 40, 2007) and newer are built with Green Molding Compound. Product manufactured prior to Date

INA199EVM;中文规格书,Datasheet资料

User's GuideSBOU085–May2010INA199A1-A3EVM This user’s guide describes the characteristics,operation,and use of the INA199A1-A3evaluation module (EVM).This EVM is designed to evaluate the performance of the INA199A1,INA199A2,and INA199A3 voltage output current shunt monitors in a variety of configurations.The EVM layout and design are flexible enough to allow evaluation of a wide range of applications.This document also includes a schematic,reference printed circuit board(PCB)layouts,and a complete bill of materials.Contents1Introduction and Overview (2)2Quick Start Setup and Use (4)3INA199A1-A3EVM Circuit (6)4Reference Voltage Setup (11)5INA199A1-A3EVM Schematic and PCB Layout (12)6Bill of Materials (14)List of Figures1Hardware Included with the INA199A1-A3EVM (3)2Measurement with Shunt (4)3Measurement without Shunt (5)4TO-247Package In R1 (6)5CS3Package in R1 (6)6TO-126Package in R1 (6)7TO-220Package in R1 (6)8Radial Package in R2 (8)9U1Footprint (10)10U1Populated with DIP Board (10)11INA199A1-A3EVM Schematic (12)12INA199A1-A3EVM PCB (13)All trademarks are the property of their respective owners.Introduction and Overview 1Introduction and Overview1.1INA199A1-A3The INA199A1-A3devices are voltage output,high-side measurement,bi-directional,zero-drift current shunt monitors.This family of devices has gains that range from50V/V to200V/V.The voltage developed across the device inputs is amplified by the corresponding gain of the specific device and is presented at the output pin.These devices can sense voltage drops across shunts at common-mode voltages from–0.3V to26V,independent of supply voltages.These devices operate with supply voltages between2.7V and26V and draw a maximum of100m A.The low offset of the zero-drift architecture enables currentsensing with maximum drops across the shunt as low as10mV full-scale.The INA199A1-A3devices are currently available in an SC70surface-mount package.Table1summarizes the available device options.Table1.INA199A1-A3Device SummaryProduct GainINA199A150INA199A2100INA199A32001.2INA199A1-A3EVMThe INA199A1-A3EVM is intended to provide basic functional evaluation of this device family.The fixture layout is not intended to be a model for the target circuit,nor is it laid out for electromagnetic compatibility (EMC)testing.The layout of the INA199A1-A3EVM printed circuit board(PCB)is designed to provide the followingfeatures:•Easy handling of the small package;a mechanical drawing of the recommended land pattern is found at the end of the product data sheet.•Easy access to all device pins•Space for optional input filtering capacitors and resistors as well as a prototype area for additional user defined circuitry•Space for shunt resistors of various footprints•Multiple input signal options•Evaluation of all gain options through provided device boards as well as a location to solder a test device directly onto the boardThe INA199A1-A3EVM allows the user to install a shunt resistor,and then connect both thecommon-mode voltage and load to develop the input voltage,or omit the shunt resistor and apply adifferential voltage directly to the device input.This flexibility allows a user to test the device operation in a simulated manner as well as an actual application.Refer to the INA199A1-A3product data sheet for comprehensive information about the INA199A1-A3family of devices. Introduction and Overview 1.3Hardware IncludedThe initial release of this evaluation board and user's guide may precede the actual release of somemembers of the INA199A1-A3device family.As additional devices with the family are released,theINA199A1-A3EVM evaluation board will be associated with them.A test fixture populated with anINA199A1is provided in all INA199A1-A3EVMs delivered,as Figure1shows.Figure1.Hardware Included with the INA199A1-A3EVMThe INA199A1-A3EVM kit is shipped with the following items:•INA199A1-A3EVM PCB•Three populated test boards(INA199A1,INA199A2,INA199A3)If any of these items are missing or damaged,please contact the Texas Instruments Product Information Center nearest you to inquire about a replacement.Quick Start Setup and Use 2Quick Start Setup and UseFollow these procedures to set up and use the INA199A1-A3EVM.Step1.Insert the device board to be evaluated into the U1location.The U1location allows the user to either evaluate one of the provided device boards or install the test device directly on thesurface-mount pads in the U1footprint.Step2.Connect an external dc supply voltage between2.7V and26V to the V+terminal referenced to the GND terminal of T3.The INA199A1-A3device output voltage is limited to50mV aboveground to200mV below the supply level.Step3.Connect the REF terminal of T3to ground.The voltage applied at the reference input can vary depending on how the device is to be used.Further details regarding the use of thereference voltage are discussed later in this document.Step4.Connect the input.2.1Measurement with ShuntThis connection method allows the user to install a shunt resistor on the EVM and connect thecommon-mode voltage and load to incorporate the test device directly into a sample application,asFigure2shows.To configure a measurement evaluation with a shunt,follow these procedures.1.Install a shunt resistor into the R2location.If not using a surface-mount or through-hole shunt,pleaserefer to Section3.1for a summary of R1component specifications.2.Connect the common-mode voltage to the Vterminal of T1.IN3.Connect load to the Load terminal of T1.Figure2.Measurement with ShuntV CMV DIFF Quick Start Setup and Use2.2Measurement without ShuntThis connection method allows the user to either simulate the voltage developed across a sense resistor based on a given set of system conditions,or to connect the INA199A1-A3EVM remotely to an existing shunt already included in an example application.Figure 3illustrates a measurement configuration without a shunt.To configure a measurement evaluation without a shunt,follow these procedures.1.Connect a differential voltage to the V IN+and V IN–terminals of T2.With the reference voltage set atground,ensure that the V IN+terminal is the more positive of the two inputs.2.Measure the output voltage at the V OUT terminal of T2.Figure 3.Measurement without ShuntNOTE:The output voltage is equal to the gain of the device multiplied by the differential voltagemeasured directly at the device input pins.INA199A1-A3EVM Circuit 3INA199A1-A3EVM CircuitThis section summarizes the INA199A1-A3EVM components.3.1R1R1can be used for shunt resistors that have a package that may not be easily adaptable to a standard, two-terminal,through-hole footprint or to a0603through1206surface-mount footprint.Specifically,this component location was added to allow the use of TO-126,TO-220,TO-247,and four terminal inlineradial packages such as the CS3series of shunts from Ohmite.The numbers located on the printed circuit board(PCB)between R1and J1correspond to each of the holes in the R1footprint.Holes with the same number are connected together.The designation of1and2indicates that a particular hole is connecteddirectly to the VIN+and VIN–inputs,respectively.The designation of3and4indicates that a particular holeis intended for the sense measurement of a four-wire shunt.Care must be taken to ensure that the shunt is placed in the correct position in the R1location.This placement consideration is evident when using a two-connection shunt with a spacing of200mils(.200in or5,080mm).As shown in Figure4and Figure7, the shunt must be placed in the second1-designated hole in order for the other leg to fit into the2 position.If the shunt is placed in the first1position,the second leg is left floating;no differential voltage will be generated for the current monitor.Additional packages can be tested by using the provided prototype area of the board.Figure4.TO-247Package In R1Figure5.CS3Package in R1 INA199A1-A3EVM CircuitFigure6.TO-126Package in R1Figure7.TO-220Package in R1INA199A1-A3EVM Circuit 3.2R2R2is intended to handle two-and four-terminal radial packages(as Figure8shows)as well assurface-mount packages that range in size from0603to1206.Figure8.Radial Package in R2 INA199A1-A3EVM Circuit 3.3R3,R4,C1R3and R4are factory-installed0Ωresistors.These resistors,in combination with C1,form an input filter.These locations allow for both through-hole and surface-mount packages that range in size from0603to 1206.Additional information regarding the use of input filtering is provided in the INA199A1-A3product data sheet.3.4Bypass Capacitors and JumpersC2and C3are0.1m F supply bypass capacitors.J1is intended to be used as measurements points of R1,if necessary.J2is used as a test port at the factory but can be used for the corresponding input and output pins,ifdesired.3.5U1U1is the location for the test device.Three device boards are supplied with the INA199A1-A3EVM board.Each board is populated with one of the available device gains.This interchangeable option allows users to test the devices and determine the gain setting that is best suited for a given application.Here is a list of the factors involved in selecting the appropriate device.•The INA199A1-A3devices are identical with the exception of different gain settings.•The differential input voltage is either applied across the inputs or developed based on the load current that flows through the shunt resistor.•The limiting factor that requires attention to be given to device selection is the output voltage.•The selected device must allow the output voltage to remain within the acceptable range after the developed input voltage is amplified by the respective device gain.The output voltage must remainwith the range of50mV above ground to200mV below the supply voltage.•An output below the minimum allowable output requires the selection of a device with a higher gain.Likewise,an output above the maximum allowable output requires the selection of a device with alower gain.INA199A1-A3EVM Circuit In addition to being able to accommodate the device boards,a surface-mount footprint is also included so the user can install one of these devices directly onto the board,if desired.Figure9illustrates the U1footprint on the EVM.Figure10shows the U1slot populated with a DIP board device.Figure9.U1Footprint Figure10.U1Populated with DIP Board分销商库存信息: TIINA199EVM。

BB145B,115;中文规格书,Datasheet资料

2004 Mar 29

4

/

NXP Semiconductors

Product specification

Low-voltage variable capacitance diode

DATA SHEET STATUS DOCUMENT STATUS(1) Objective data sheet Preliminary data sheet Product data sheet Notes 1. Please consult the most recently issued document before initiating or completing a design. PRODUCT STATUS(2) Development Qualification Production DEFINITION

NXP Semiconductors

Product specification

Low-voltage variable capacitance diode

FEATURES Ultra small plastic SMD package C4: 2.75 pF; ratio: 2.4 Low series resistance. APPLICATIONS Voltage controlled oscillators (VCO).

2004 Mar 29

2

/

NXP Semiconductors

Product specification

Low-voltage variable capacitance diode

GRAPHICAL DATA

BB145B

MCD782

handbook, full pagewidth

BAV199LT1G;BAV199LT1;中文规格书,Datasheet资料

Features

Байду номын сангаас

Low Leakage Current Applications Medium Speed Switching Times AEC−Q101 Qualified and PPAP Capable S Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS Compliant*

CD VF

pF mVdc

trr

ms

820W +10 V 2.0 k 100 mH 0.1 mF DUT 50 W OUTPUT PULSE GENERATOR 50 W INPUT SAMPLING OSCILLOSCOPE VR INPUT SIGNAL 90% IR iR(REC) = 1.0 mA OUTPUT PULSE (IF = IR = 10 mA; MEASURED at iR(REC) = 1.0 mA) IF 0.1 mF tr 10% tp t IF trr t

ORDERING INFORMATION

Device BAV199LT1G SBAV199LT1G SBAV199LT3G Package SOT−23 (Pb−Free) SOT−23 (Pb−Free) SOT−23 (Pb−Free) Shipping† 3,000 / Tape & Reel 3,000 / Tape & Reel 10,000 / Tape & Reel

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. Product profile1.1General descriptionThe BB199 is a low voltage variable capacitance diode for the Voltage ControlledOscillator (VCO) and Voltage Controlled Crystal Oscillator (VCXO) applications.1.2Features and benefitsSmall plastic SMD packageVery low operating voltage (1 V to 4 V)Large capacitance ratio (C d(0V5)/C d(2V)=2.8 minimum) Good capacitor-voltage (C-V) linearityVery low series resistance allowing high Q performance.1.3ApplicationsCommunication equipment Voltage Controlled Oscillators2. Pinning information[1]The marking bar indicates the cathode.BB199Variable capacitance diode for VCO and VCXORev. 1 — 1 December 2010Product data sheetCAUTIONThis device is sensitive to ElectroStatic Discharge (ESD). Therefore care should be takenduring transport and handling.Table 1.PinningPin Description Simplified outline Graphic symbol1cathode [1]2anodesym0083. Ordering informationTable 2.Ordering informationType number PackageName Description Version BB199SC-79plastic surface-mounted package; 2 leads SOD5234. MarkingTable 3.Marking codesType number Marking codeBB199K95. Limiting valuesTable 4.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol Parameter Conditions Min Max UnitV R reverse voltage-20VI F forward current-100mAP tot total power dissipation T sp = 90 °C-300mWT stg storage temperature−65+150°CT j junction temperature−65+150°C6. Thermal characteristicsTable 5.Thermal characteristicsSymbol Parameter Conditions Typ UnitR th(j-sp)thermal resistance from junction to solder point200K/W7. CharacteristicsTable 6.CharacteristicsT j=25°C unless otherwise specifiedSymbol Parameter Conditions Min Typ Max Unit I R reverse current V R=20V--1000nAV R=16V--5nAC d diode capacitance f=1MHzV R=0.5V36.5-42.5pFV R=2V11.8-13.8pFr s diode series resistance V R=1.5V; f=100MHz-0.250.5ΩC d(0V5)/C d(2V)diode capacitance ratio (0.5V to 2V) f = 1 MHz 2.8--8. Package outlinePlastic surface-mounted package; 2 leads SOD523Fig 6.Package outline SOD523 (SC-79)9. AbbreviationsTable 7.AbbreviationsAcronym DescriptionQ Quality factorSMD Surface Mounted Device10. Revision historyTable 8.Revision historyDocument ID Release date Data sheet status Change notice SupersedesBB199 v.120101201Product data sheet--11. Legal information11.1 Data sheet status[1]Please consult the most recently issued document before initiating or completing a design.[2]The term ‘short data sheet’ is explained in section “Definitions”.[3]The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product statusinformation is available on the Internet at URL .11.2 DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.11.3 DisclaimersLimited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors’ aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk. Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer’s applications and products planned, as well as for the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessary testing for the customer’s applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer’s third partycustomer(s). NXP does not accept any liability in this respect.Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at /profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer’s general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.Document status[1][2]Product status[3]DefinitionObjective [short] data sheet Development This document contains data from the objective specification for product development. Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.Product [short] data sheet Production This document contains the product specification.Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use ofnon-automotive qualified products in automotive equipment or applications. In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors’ warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors’ specifications such use shall be solely at customer’s own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors’ standard warranty and NXP Semiconductors’ product specifications. 11.4 TrademarksNotice: All referenced brands, product names, service names and trademarks are the property of their respective owners.12. Contact informationFor more information, please visit: For sales office addresses, please send an email to: salesaddresses@13. Contents1 Product profile. . . . . . . . . . . . . . . . . . . . . . . . . . 11.1 General description . . . . . . . . . . . . . . . . . . . . . 11.2 Features and benefits. . . . . . . . . . . . . . . . . . . . 11.3 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Pinning information. . . . . . . . . . . . . . . . . . . . . . 13 Ordering information. . . . . . . . . . . . . . . . . . . . . 24 Marking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 26 Thermal characteristics . . . . . . . . . . . . . . . . . . 27 Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . 28 Package outline. . . . . . . . . . . . . . . . . . . . . . . . . 59 Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . . 510 Revision history. . . . . . . . . . . . . . . . . . . . . . . . . 511 Legal information. . . . . . . . . . . . . . . . . . . . . . . . 611.1 Data sheet status . . . . . . . . . . . . . . . . . . . . . . . 611.2 Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 611.3 Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . . 611.4 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . . 712 Contact information. . . . . . . . . . . . . . . . . . . . . . 713 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8Please be aware that important notices concerning this document and the product(s)described herein, have been included in section ‘Legal information’.© NXP B.V.2010.All rights reserved.For more information, please visit: For sales office addresses, please send an email to: salesaddresses@分销商库存信息: NXPBB199,115。