Open Drain

推挽式输出和漏极式输出

单片机学习之推挽输出与漏极开路输出方式push- pull输出就是一般所说的推挽输出,在cmos电路里面应该较cmos输出更合适,因为在cmos里面的push-pull输出能力不可能做得双极那么大。

输出能力看ic内部输出极n管p管的面积。

和开漏输出相比,push-pull的高低电平由ic的电源低定,不能简单的做逻辑操作等。

push-pull是现在cmos电路里面用得最多的输出级设计方式。

一.什么是oc、od集电极开路门(集电极开路oc 或源极开路od)open-drain是漏极开路输出的意思,相当于集电极开路(open-collector)输出,即ttl中的集电极开路(oc)输出。

一般用于线或、线与,也有的用于电流驱动。

open-drain是对mos管而言,open-collector是对双极型管而言,在用法上没啥区别。

开漏形式的电路有以下几个特点:1.利用外部电路的驱动能力,减少ic内部的驱动。

或驱动比芯片电源电压高的负载.2. 可以将多个开漏输出的pin,连接到一条线上。

通过一只上拉电阻,在不增加任何器件的情况下,形成“与逻辑”关系。

这也是i2c,smbus等总线判断总线占用状态的原理。

如果作为图腾输出必须接上拉电阻。

接容性负载时,下降延是芯片内的晶体管,是有源驱动,速度较快;上升延是无源的外接电阻,速度慢。

如果要求速度高电阻选择要小,功耗会大。

所以负载电阻的选择要兼顾功耗和速度。

3.可以利用改变上拉电源的电压,改变传输电平。

例如加上上拉电阻就可以提供ttl/cmos电平输出等。

4.开漏pin不连接外部的上拉电阻,则只能输出低电平。

一般来说,开漏是用来连接不同电平的器件,匹配电平用的。

5.正常的cmos输出级是上、下两个管子,把上面的管子去掉就是open-drain了。

这种输出的主要目的有两个:电平转换和线与。

6.由于漏级开路,所以后级电路必须接一上拉电阻,上拉电阻的电源电压就可以决定输出电平。

强推挽输出和开漏输出

推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).我们先来说说集电极开路输出的结构。

集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。

对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V电源通过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。

图2中的开关受软件控制,“1”时断开,“0”时闭合。

很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

再看图三。

图三中那个1K的电阻即是上拉电阻。

如果开关闭合,则有电流从1K电阻及开关上流过,但由于开关闭其它三个口带内部上拉),当我们要使用输入功能时,只要将输出口设置为1即可,这样就相当于那个开关断开,而对于P0口来说,就是高阻态了。

对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。

将上面的三极管换成场效应管即可。

这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。

另一种输出结构是推挽输出。

推挽输出的结构就是把上面的上拉电阻也换成一个开关,当要输出高电平时,上面的开关通,下面的开关断;而要输出低电平时,则刚好相反。

比起OC 或者OD来说,这样的推挽结构高、低电平驱动能力都很强。

开漏 推挽电路

Open drain & push pull,IO口驱动,集电极开路Open drain & push pull最近在写GPIO的driver, 在配置GPIO管脚时,看见了感觉熟悉的两个名词:Open Drain and Push Pull。

可是一时对它们的原理及区别有感觉很模糊,故上网收集了一些资料复习一下。

所谓开漏电路概念中提到的“漏”就是指MOSFET的漏极。

同理,开集电路中的“集”就是指三极管的集电极。

开漏电路就是指以MOSFET的漏极为输出的电路。

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该由开漏器件和开漏上拉电阻组成。

如图1所示:图 1组成开漏形式的电路有以下几个特点:1. 利用外部电路的驱动能力,减少IC内部的驱动。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。

IC内部仅需很下的栅极驱动电流。

如图1。

2. 可以将多个开漏输出的Pin,连接到一条线上。

形成“与逻辑” 关系。

如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。

这也是I2C,SMBus等总线判断总线占用状态的原理。

3. 可以利用改变上拉电源的电压,改变传输电平。

如图2, IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。

这样我们就可以用低电平逻辑控制输出高电平逻辑了。

4. 开漏Pin不连接外部的上拉电阻,则只能输出低电平(因此对于经典的51单片机的P0口而言,要想做输入输出功能必须加外部上拉电阻,否则无法输出高电平逻辑)。

5. 标准的开漏脚一般只有输出的能力。

添加其它的判断电路,才能具备双向输入、输出的能力。

图 2应用中需注意:1. 开漏和开集的原理类似,在许多应用中我们利用开集电路代替开漏电路。

例如,某输入Pin要求由开漏电路驱动。

则我们常见的驱动方式是利用一个三极管组成开集电路来驱动它,即方便又节省成本。

推挽、开漏、强上拉、弱上拉、强下拉、弱下拉输出之间的区别

推挽、开漏、强上拉、弱上拉、强下拉、弱下拉输出推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).上拉电阻:1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于CO-MS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC(集电极开路)门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:1. 驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计时应注意两者之间的均衡。

2.下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3.高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

单片机I-O口推挽输出与开漏输出的区别

单片机I/O口推挽输出与开漏输出的区别

推挽输出:可以输出高,低电平,连接数字器件;

开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).

推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.

我们先来说说集电极开路输出的结构。

集电极开路输出的结构如图1所示,右边的那个三极管集电极什幺都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为0时,输出也为0)。

对于图1,当左端的输入为0时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V

电源通过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为1时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。

图2中的开关受软件控制,1时断开,0时闭合。

很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那幺输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

开漏电路与推挽电路

实际应用与选择

21

六、推挽与开漏的选择

该图中左边的便是推挽输出模式,其中比较器输出高电平时 下面的PNP管截止,而上面NPN管导通,输出电平VS+;当 比较器输出低电平时则恰恰相反,PNP管导通,输出和地相 连,为低电平。 右边的则可以理解为开漏输出形式,需要接上拉电阻。

22

六、推挽与开漏的选择

25

5

二、开漏电路的特点

2.可以将多个开漏输出的Pin,连接到一条在线。形成 “与 逻辑” 关系,也称作“线与功能”。 如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏 在线的逻辑就为0了。

6

二、开漏电路的特点

线与功能

PIN_OUT= PIN_A * PIN_B * PIN_C 只有当PIN_A、PIN_B、PIN_C都 为高电平时,PIN_OUT的逻辑才 会为高电平

12

三、开漏电路的不足

R阻值的选择——延时 Open drain带了上拉电阻的线路,即使以最快的速度去提 升电压,最快也要一个常量的R×C的时间。(其中R是电阻, C是寄生电容,包括了pin脚的电容和板子的电容) 电阻影响上升沿,不影响下降沿。如果使用中不关心上升沿 ,上拉电阻就可选择尽可能的大点,以减少对地通路的 电 流。如果对上升沿时间要求较高,电阻大小的选择应以芯片 功耗为参考。

10

三、开漏电路的不足

当然Open drain也不是没有代价,Open drain輸出電路带 来上升沿的延时,因为上升沿是通过外接上拉无源电阻对负 载充电的,当电阻选择小时,延时就小、但功耗大,反之延 时大功耗小。 Open drain提供了灵活的输出方式,但也是有代价的,如果 对延时有要求,建议用下降沿输出。

23

推挽输出与开漏输出的区别

推挽输出与开漏输出的区别推挽输出与开漏输出的区别推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.要实现‘线与’需要用OC(open collector)门电路.是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。

输出既可以向负载灌电流,也可以从负载抽取电流。

/////////////////////////////////////////////////////////////////////开漏电路特点及应用在电路设计时我们常常遇到开漏(open drain)和开集(open collector)的概念。

所谓开漏电路概念中提到的“漏”就是指MOSFET的漏极。

同理,开集电路中的“集”就是指三极管的集电极。

开漏电路就是指以MOSFET的漏极为输出的电路。

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该由开漏器件和开漏上拉电阻组成。

组成开漏形式的电路有以下几个特点:1. 利用外部电路的驱动能力,减少IC内部的驱动。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。

IC内部仅需很下的栅极驱动电流。

2. 可以将多个开漏输出的Pin,连接到一条线上。

形成“与逻辑” 关系。

当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。

这也是I2C,SMBus等总线判断总线占用状态的原理。

3. 可以利用改变上拉电源的电压,改变传输电平。

IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。

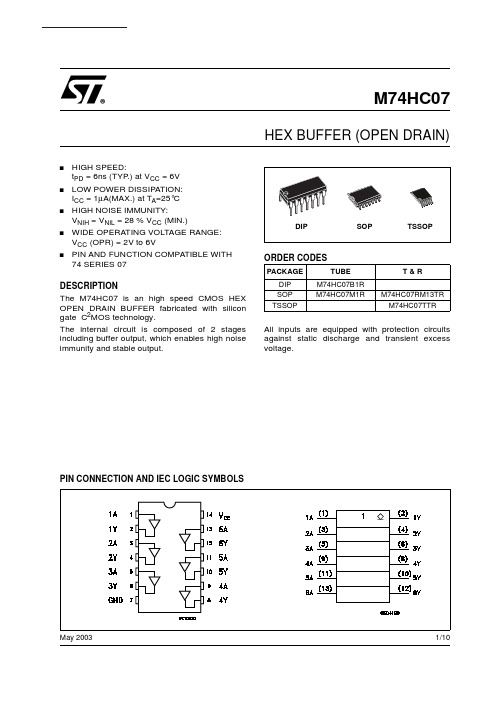

ST M74HC07 HEX BUFFER (OPEN DRAIN) 数据手册

1/10May 2003sHIGH SPEED:t PD =6ns (TYP .)at V CC =6V sLOW POWER DISSIPATION:I CC =1µA(MAX.)at T A =25°C sHIGH NOISE IMMUNITY:V NIH =V NIL =28%V CC (MIN.)sWIDE OPERATING VOLTAGE RANGE:V CC (OPR)=2V to 6VsPIN AND FUNCTION COMPATIBLE WITH 74SERIES 07DESCRIPTIONThe M74HC07is an high speed CMOS HEX OPEN DRAIN BUFFER fabricated with silicon gate C 2MOS technology.The internal circuit is composed of 2stages including buffer output,which enables high noise immunity and stable output.All inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HC07HEX BUFFER (OPENDRAIN)PIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T &R DIP M74HC07B1R SOP M74HC07M1RM74HC07RM13TR TSSOPM74HC07TTR查询74HC07供应商M74HC072/10INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEZ :High ImpedanceABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur.Functional operation under these conditions isnot implied(*)500mW at 65°C;derate to 300mW by 10mW/°C from 65°C to 85°CRECOMMENDED OPERATING CONDITIONSPIN No SYMBOL NAME AND FUNCTION 1,3,5,9,11,131A to 6A Data Inputs 2,4,6,8,10,121Y to 6Y Data Outputs 7GND Ground (0V)14V CCPositive Supply VoltageA Y L L HZSymbol ParameterValue Unit V CC Supply Voltage -0.5to +7V V I DC Input Voltage -0.5to V CC +0.5V V O DC Output Voltage -0.5to V CC +0.5V I IK DC Input Diode Current ±20mA I OK DC Output Diode Current ±20mA I ODC Output Current±25mA I CC or I GND DC V CC or Ground Current±50mA P DPower Dissipation 500(*)mW T stg Storage Temperature -65to +150°C T LLead Temperature (10sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2to 6V V I Input Voltage 0to V CC V V O Output Voltage 0to V CC V T op Operating Temperature -55to 125°C t r ,t fInput Rise and Fall TimeV CC =2.0V 0to 1000ns V CC =4.5V 0to 500ns V CC =6.0V0to 400nsM74HC073/10DC SPECIFICATIONSAC ELECTRICAL CHARACTERISTICS (C L =50pF,Input t r =t f =6ns)SymbolParameterTest ConditionValue UnitV CC (V)T A =25°C -40to 85°C -55to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage 2.0 1.5 1.5 1.5V 4.5 3.15 3.15 3.156.0 4.24.24.2V ILLow Level Input Voltage2.00.50.50.5V4.5 1.35 1.35 1.356.0 1.81.8 1.8V OLLow Level Output Voltage2.0I O =20µA 0.00.10.10.1V4.5I O =20µA 0.00.10.10.16.0I O =20µA 0.00.10.10.14.5I O =4.0mA 0.170.260.330.406.0I O =5.2mA 0.180.260.330.40I I Input Leakage Current6.0V I =V CC or GND ±0.1±1±1µA I OZ Output Leakage Current6.0V I =V IH or V IL V O =V CC or GND ±0.5±5±10µA I CCQuiescent Supply Current6.0V I =V CC or GND11020µA SymbolParameterTest ConditionValue UnitV CC (V)T A =25°C -40to 85°C -55to 125°C Min.Typ.Max.Min.Max.Min.Max.t THLOutput Transition Time2.0307595110ns 4.581519226.07131619t PLZPropagation Delay Time2.0R L =1K Ω1090115135ns4.571823276.06152023t PZLPropagation Delay Time2.0R L =1K Ω1790115135ns4.571823276.05152023M74HC074/10CAPACITIVE CHARACTERISTICS1)C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load.(Refer to Test Circuit).Average operating current can be obtained by the following equation.I CC(opr)=C PD x V CC x f IN +I CC /6(per gate)TEST CIRCUITL R T =Z OUT of pulse generator (typically 50Ω)WAVEFORM :PROPAGATION DELAY TIME (f=1MHz;50%duty cycle)SymbolParameterTest ConditionValue UnitV CC (V)T A =25°C -40to 85°C -55to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5.05101010pF C OUT OutputCapacitance5.03pF C PDPower Dissipation Capacitance (note 1)5.04pFM74HC07Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2003 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.© 10/10。

EM78P257的内部上,下拉、Open-drain等功能简述

EM78P257的内部上/下拉、Open-drain等功能简述EM78P257的内部上/下拉、Open-drain等功能简述****************************** 下拉控制(Pull Low)*****************************EM78P257有个专用的下拉控制寄存器(Pull-down Control Register)IOCB0:7 6 5 4 3 2 1 0/PD57 /PD56 /PD55 /PD54 /PD53 /PD52 /PD51 /PD50bit0~bit7: 分别为P5端口管脚的下拉使能控制位0: 内部下拉使能1: 内部下拉禁止其中bit6~bit7的下拉使能仅用于EM78P257B使用说明:将IOCB0控制寄存器所对应的位清0,即可使能其对应的I/O引脚内部下拉,置1即关闭内部下拉功能。

IOR IOCB0MOV A, @0b11111110IOW IOCB0 ; Enable P50 internal pull-down*************************** 漏极开路控制(Open drain)***************************EM78P257有个专用的漏极开路控制寄存器(Open-drain Control Register) IOCC0:7 6 5 4 3 2 1 0OD67 OD66 OD65 OD64 OD63 OD62 OD61 OD60Bit0~bit7: 分别为P6端口管脚的漏极开路使能控制位0: 漏极开路输出使能1: 漏极开路输出禁止使用说明将IOCC0控制寄存器所对应的位置1,即可使能其对应的I/O引脚为漏极开路输出,清0即关闭漏极开路输出功能。

IOR IOCC0OR A, @0b00000011IOW IOCC0 ; Enable P60、P61 open-drain output注意:若使能引脚漏极开路输出,需有外部上拉电阻。

开漏(open drain)和开集(open collector)的概念

开漏(open drain)和开集(open collector)的概念在电路设计时我们常常遇到开漏(open drain)和开集(open collector)的概念。

所谓开漏电路概念中提到的漏就是指MOSFET的漏极。

同理,开集电路中的集就是指三极管的集电极。

开漏电路就是指以MOSFET的漏极为输出的电路。

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该

由开漏器件和开漏上拉电阻组成。

如图1所示:

组成开漏形式的电路有以下几个特点:

1. 利用外部电路的驱动能力,减少IC内部的驱动。

当IC内部MOSFET 导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。

IC 内部仅需很下的栅极驱动电流。

如图:

2. 可以将多个开漏输出的Pin,连接到一条线上。

形成与逻辑关系。

如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。

这也是I2C,SMBus等总线判断总线占用状态的原理。

3. 可以利用改变上拉电源的电压,改变传输电平。

如图2, IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。

这样我们就可以用低电平。

EM78P447的内部上拉、Open-drain、R-option等功能简述

EM78P447的内部上拉、Open-drain、R-option等功能简述EM78P447的内部上拉、Open-drain、R-option等功能简述****************************** 上拉控制(Pull High)*****************************与EM78P447上拉功能相关的寄存器是CONT,即:控制寄存器(Control Register)7 6 5 4 3 2 1 0/PHEN /INT TS TE PAB PSR2 PSR1 PSR0Bit7(/PHEN): P60~P67, P74和P75上拉使能控制位0: 使能内部上拉1: 禁止内部上拉使用说明:将CONT寄存器第7位清0,即使能相应的I/O口内部上拉,置1即关闭内部上拉功能。

CONTRAND A, @0b01111111CONTW ; 使能P6端口与P74、P75引脚内部上拉EM78P447没有内部下拉功能。

*************************** Open-drain 与R-option**************************与EM78P447的Open-drain、R-option功能相关的寄存器是IOCE,即:WDT控制寄存器(WDT ControlRegister)7 6 5 4 3 2 1 0- ODE WDTE SLPC ROC - - /WUEBit3(ROC): ROC为P70、P71管脚的R-option功能控制位1: 使能R-option功能,其引脚P50~P51的状态可由控制器读出。

0: 禁止R-option功能。

Bit6(ODE): ODE为P76、P77管脚的漏极开路使能控制位0: 漏极开路输出禁止1: 漏极开路输出使能R-option功能使用说明:应用EM78P447的R-option功能编程与EM78P156一样,都需有一段引导程序,其步骤如下:(1)设置引脚P7.0、P7.1为输入状态。

OC门电路和OD门电路原理

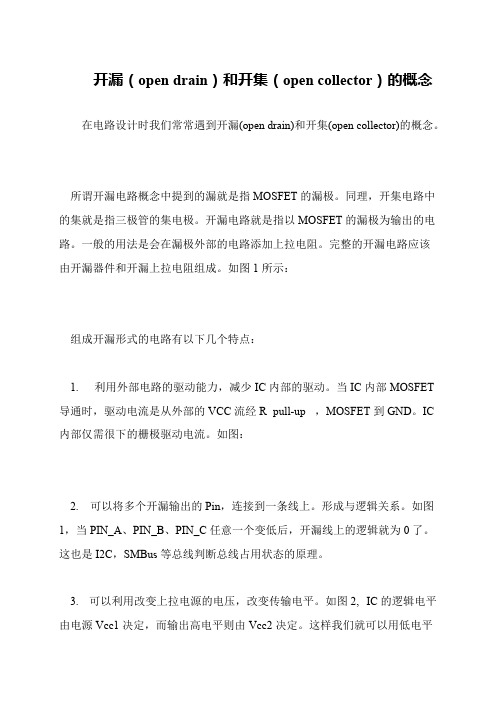

1、OC门

OC门和OD门它们的定义如下:

OC:集电极开路(OpenCollector)

OD:漏极输出(Open Drain)

这是相对于两个不同的元器件而命名的,OC门是相对于三极管而言,OD门是相对于MOS管。

我们先来分析下OC门电路的工作原理:

当INPUT输入高电平,Ube>0.7V,三极管U3导通,U4的b点电位为0,U4截止,OUTPUT高电平

当INPUT输入低电平,Ube<0.7V,三极管U3截止,U4的b点电位为高,U4导通,OUTPUT低电平

OC门电路

其中R25为上拉电阻:何为上拉电阻?将不确定的信号上拉至高电平。

假设:没有R25,那么OUTPUT的输出是通过ce与地连接在一起的,输出端悬空了,即高阻态。

这时候OUTPUT的电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平,它是不能输出高电平的。

因此,需要接一个电阻到VCC,而这个电阻就叫上拉电阻。

2、OD门

OC门与OD门是十分相似的,将三极管换成了MOS管当INPUT输入高电平,GS>阈值电压,MOS 管Q1导通,Q3的G点电位为0,Q3截止,OUTPUT高电平

当INPUT输入低电平,GS<阈值电压,MOS管Q1截止,Q3的G点电位为高,Q3导通,OUTPUT低电平

OD门

开漏它其实利用了外围电路的驱动能力,减少了IC内部的驱动,因此想让它作为驱动电路,必须接上拉电阻才能正常工作,例如51单片机的P0口。

而且驱动能力与上拉阻值和电压有关,电阻越大,相应的驱动电流就小。

Open drain output circuit

专利名称:Open drain output circuit发明人:Hiroshi Miyazaki申请号:US11633454申请日:20061205公开号:US20070247192A1公开日:20071025专利内容由知识产权出版社提供专利附图:摘要:An open drain output circuit for use as an IC bus interface. The open drain output circuit includes an output terminal. An input unit performs a first operation causing the potential at the output node to steeply fall and a second operation forgradually raising the potential in accordance with transition of an input signal. An outputtransistor connected to the output node of the input unit and the output terminal is turned OFF in the first operation and turned ON in the second operation. A delay time adjustment circuit reduces the difference between a delay time from transition of the input signal until when the output transistor is turned OFF in the first operation and a delay time from transition of the input signal until when the output transistor is turned ON in the second operation.申请人:Hiroshi Miyazaki地址:Kasugai JP国籍:JP更多信息请下载全文后查看。

open-drain结构

open-drain结构Open-drain结构是一种数字电路输出结构,通常用于连接到其他数字逻辑电路或微控制器输入端口。

Open-drain结构的输出引脚通常连接到负电源(地)或无源开关(如继电器或晶体管)。

在Open-drain结构中,当输出引脚被拉低时,数字信号被传输;当输出引脚离开地时,引脚上的数字信号被禁止。

这种输出结构的优点是可以连接到其他输出端口,从而扩展设备的功能,同时也可以保护前级电路中较弱的输出器件。

Open-drain结构通常与上拉电阻一起使用。

上拉电阻通过连接到正电源来提供一个默认状态的高电平。

当Open-drain输出引脚处于不活动状态时,上拉电阻将输出引脚拉高至高电平状态。

当Open-drain输出引脚拉低时,它形成了一个接地路径,使得芯片输出的电流能够通过Open-drain输出引脚和外部电路流回负电源,从而实现数字信号的传输。

Open-drain结构常被用于I²C、SPI等数字通信协议中。

在这些协议中,输出引脚需要在几个特定时刻产生不同的信号电平,Open-drain结构很好地满足了这些需求。

当Open-drain输出引脚被拉低时,由于它没有提供电流驱动,因此需要在输出引脚和外部器件之间使用一个电流限制电阻,以限制流入Open-drain输出引脚的电流。

这个电流限制电阻的值可以根据具体的应用需求来选择。

Open-drain结构还有一个重要的应用场景,即用于实现复杂的逻辑门电路。

例如在数字信号处理器或微控制器中,Open-drain结构通常会被用于实现多个输出信号的逻辑AND 或OR操作。

在这些应用场景中,一个集合的Open-drain输出引脚可以通过共享一个上拉电阻和电流限制电阻以及一个逻辑门电路来实现复杂的逻辑功能。

与Open-drain结构相对的是Push-pull结构,Push-pull输出器件可以产生高电平或低电平,而不仅仅是低电平。

但与Open-drain结构不同的是,Push-pull结构不能进行多路AND或OR操作,因为它们产生的信号需要保证互斥而不是共同传输。

OCOD门结构原理

OCOD门结构原理OC门和OD门是数字逻辑门的一种,用于构建数字电路中的组合逻辑电路。

OC门(Open Collector门)和OD门(Open Drain门)的结构原理和特性如下所述。

1.OC门的结构原理:OC门是由一个输出晶体管和上拉电阻组成的。

输出晶体管可以处于两种状态中的一种:断开(open)状态或者连接(closed)状态。

在断开状态下,输出晶体管的集电极没有连接到电源,此时输出端与输出电源断开,相当于高阻态。

而在连接状态下,输出晶体管的集电极连接到电源,输出端与电源相连接,相当于低阻态。

OC门的输入信号与输出晶体管的基极相连,当输入信号为逻辑1时,输出晶体管的基极为悬空状态,晶体管处于断开状态,输出端为高阻态;当输入信号为逻辑0时,输出晶体管的基极被拉低,晶体管处于连接状态,输出端为低阻态。

2.OD门的结构原理:OD门也是由一个输出晶体管和上拉电阻组成,但输出晶体管的基极被外部电路所控制。

与OC门不同的是,OD门的输出晶体管的集电极没有连接到电源,而是由外部连接到负电源(一般为地),因此输出端只能输出低电平。

OD门的输入信号与输出晶体管的引脚相连,当输入信号为逻辑1时,输出晶体管的基极为悬空状态,晶体管处于断开状态,输出端为高阻态;当输入信号为逻辑0时,输出晶体管的基极被拉低,晶体管处于连接状态,输出端为低电平。

3.OC门和OD门的比较:(1)输出极性:OC门的输出为低电平或高阻态,而OD门的输出只能为低电平。

(2)输入驱动能力:由于OC门和OD门的输出晶体管都是由外部电路控制的,因此它们的输入驱动能力较弱,一般需要与其他逻辑门连接使用。

4.应用领域:OC门和OD门常用于数字信号的收集与输出,特别是在多个数字输出端需要连接到一个总线上的场景下,它们可以防止电平冲突,并提供高灵活性和兼容性。

总之,OC门和OD门是一种常用的数字逻辑门,由输出晶体管和上拉电阻组成。

它们通过外部电路控制输出晶体管的开关状态,实现不同的输出态,并在数字电路中起到收集和输出信号的作用。

什么是OC门

什么是OC门OC门,又称集电极开路(漏极开路)与非门门电路,Open Collector(Open Drain)。

为什么引入OC门?实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。

因此,需要一种新的与非门电路--OC门来实现“线与逻辑”。

OC门主要用于3个方面:1、实现与或非逻辑,用做电平转换,用做驱动器。

由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。

OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

2、线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。

在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。

在硬件上,可用OC门或三态门(ST 门)来实现。

用OC门实现线与,应同时在输出端口应加一个上拉电阻。

3、三态门(ST门)主要用在应用于多个门输出共享数据总线,为避免多个门输出同时占用数据总线,这些门的使能信号(EN)中只允许有一个为有效电平(如高电平),由于三态门的输出是推拉式的低阻输出,且不需接上拉(负载)电阻,所以开关速度比OC门快,常用三态门作为输出缓冲器。

什么叫开漏输出开漏输出:OC门的输出就是开漏输出;OD门的输出也是开漏输出。

TTL电路有集电极开路OC门,MOS管也有和集电极对应的漏极开路的OD门,它的输出就叫做开漏输出。

它可以吸收很大的电流,但是不能向外输出电流。

所以,为了能输入和输出电流,它使用的时候要跟电源和上拉电阻一齐用。

OC门开漏输出和OD门开漏输出都是为了同一个目的,都是为了实现逻辑器件的线与逻辑,当然选用不同的外接电阻也可以实现外围驱动能力的增加。

open drain 开漏知识

开漏(open drain)和开集(open collector)在电路设计时我们常常遇到开漏(open drain)和开集(open collector)的概念。

所谓开漏电路概念中提到的“漏”就是指MOS FET的漏极。

同理,开集电路中的“集”就是指三极管的集电极。

开漏电路就是指以MOS FET的漏极为输出的电路。

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该由开漏器件和开漏上拉电阻组成。

如图1所示:组成开漏形式的电路有以下几个特点:1. 利用外部电路的驱动能力,减少IC内部的驱动。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。

IC内部仅需很下的栅极驱动电流。

如图1。

2. 可以将多个开漏输出的Pin,连接到一条线上。

形成“与逻辑”关系。

如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。

这也是I2C,SMBus等总线判断总线占用状态的原理。

3. 可以利用改变上拉电源的电压,改变传输电平。

如图2, IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。

这样我们就可以用低电平逻辑控制输出高电平逻辑了。

4. 开漏Pin不连接外部的上拉电阻,则只能输出低电平。

5. 标准的开漏脚一般只有输出的能力。

添加其它的判断电路,才能具备双向输入、输出的能力。

应用中需注意:1. 开漏和开集的原理类似,在许多应用中我们利用开集电路代替开漏电路。

例如,某输入Pin要求由开漏电路驱动。

则我们常见的驱动方式是利用一个三极管组成开集电路来驱动它,即方便又节省成本。

如图3。

2. 上拉电阻R pull-up的阻值决定了逻辑电平转换的沿的速度。

阻值越大,速度越低功耗越小。

反之亦然。

Push-Pull输出就是一般所说的推挽输出,在CMOS电路里面应该较CMOS 输出更合适,应为在CMOS里面的push-pull输出能力不可能做得双极那么大。

开漏输出,推挽输出

开漏输出,推挽输出1,开漏输出(Open-Drain)⾸先讲⼀下集电极开路输出(Open-Collector),单⽚机I/O常⽤的输出⽅式的开漏输出(Open-Drain),漏极开路电路概念中提到的"漏"是指 MOSFET的漏极。

同理,集电极开路电路中的"集"就是指三极管的集电极。

在数字电路中,分别简称OD门和OC门。

典型的集电极开路电路如图所⽰。

电路中右侧的三极管集电极什么都不接,所以叫做集电极开路,左侧的三极管⽤于反相作⽤,即左侧输⼊"0"时左侧三极管截⽌,VCC通过电阻加到右侧三极管基极,右侧三极管导通,右侧输出端连接到地,输出"0"。

从图中电路可以看出集电极开路是⽆法输出⾼电平的,如果要想输出⾼电平可以在输出端加上上拉电阻。

因此集电极开路输出可以⽤做电平转换,通过上拉电阻上拉⾄不同的电压,来实现不同的电平转换。

⽤做驱动器,由于OC门电路的输出管的集电极悬空,使⽤时需外接⼀个上拉电阻Rp到电源VCC。

OC门使⽤上拉电阻以输出⾼电平,此外为了加⼤输出引脚的驱动能⼒,上拉电阻阻值的选择原则:从降低功耗及芯⽚的灌电流能⼒考虑应当⾜够⼤;从确保⾜够的驱动电流考虑应当⾜够⼩。

将OC门输出连在⼀起时,再通过⼀个电阻接外电源,可以实现"线与"逻辑关系。

只要电阻的阻值和外电源电压的数值选择得当,就能做到既保证输出的⾼、低电平符合要求,⽽且输出三极管的负载电流⼜不⾄于过⼤。

集电极开路输出除了可以实现多门的线与逻辑关系外,通过使⽤⼤功率的三极管还可⽤于直接驱动较⼤电流的负载,如继电器、脉冲变压器、指⽰灯等。

由于现在MOS管⽤普遍,⽽且性能要⽐晶体管要好,所以很多开漏输出电路,和后⾯要讲的推挽输出电路都⽤MOS管实现。

再来就是开漏输出电路,和集电极开路⼀样,顾名思义,开漏电路就是指从MOSFET的漏极输出的电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

【Open-Drain开漏输出】

原理:

开漏电路就是指以MOSFET的漏极为输出的电路。

指内部输出和地之间有个N沟道的MOSFET (Q1),这些器件可以用于电平转换的应用。

输出电压由Vcc决定。

Vcc可以大于输入高电平电压VCC (call UP-Translate)也可以低于输入高电平电压VCC(call Down-Translate)

Open-Drain输出,则是比push-pull少了个top transistor,只有那个bottom transistor。

(就像push-pull中的那样)当bottom transistor关闭,则输出为高电平。

此处没法输出高电平,想要输出高电平,必须外部再接一个上拉电阻(pull-up resistor)。

Open-drain只能够漏电流(sink current),如果想要集电流(source current),则需要加一个上拉电阻。

优点:

(1)对于各种电压节点间的电平转换非常有用,可以用于各种电压节点的Up-translate和

Down-translate转换

(2)可以将多个开漏输出的Pin脚,连接到一条线上,形成“与逻辑”关系,即“线与”功能,任意一个变低后,开漏线上的逻辑就为0了。

这也是I2C,SMBus等总线判断总线占用状态的原理。

(3)利用外部电路的驱动能力,减少IC内部的驱动。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。

IC内部仅需很小的栅极驱动电流。

(4)可以利用改变上拉电源的电压,改变传输电平,如图,IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。

这样我们就可以用低电平逻辑控制输出高电平逻辑了。

OD输出电平的原理

缺点:开漏Pin不连接外部的上拉电阻,则只能输出低电平。

当输出电平为低时,N沟道三极管是导通的,这样在Vcc'和GND之间有一个持续的电流流过上拉电阻R和三极管Q1。

这会影响整个系统的功耗。

采用较大值的上拉电阻可以减小电流。

但是,但是大的阻值会使输出信号的上升时间变慢。

即上拉电阻R pull-up的阻值决定了逻辑电平转换的沿的速度。

阻值越大,速度越低功耗越小。

反之亦然。

==================================

常见的GPIO的模式可以配置为open-drain或push-pull,具体实现上,常为通过配置对应的寄存器的某些位来配置为open-drain或是push-pull。

当我们通过CPU去设置那些GPIO的配置寄存器的某位的时候,其GPIO硬件IC内部的实现是,会去打开或关闭对应的top transistor。

相应地,如果设置为了Open-D模式的话,是需要上拉电阻才能实现,也能够输出高电平的。

因此,如果硬件内部(internal)本身包含了对应的上拉电阻的话,此时会去关闭或打开对应的上拉电阻。

如果GPIO 硬件IC内部没有对应的上拉电阻的话,那么你的硬件电路中,必须自己提供对应的外部(external)的上拉电阻。

而push-pull输出的优势是速度快,因为线路是以两种方式驱动的。

而带了上拉电阻的线路,即使以最快的速度去提升电压,最快也要一个常量的R×C的时间。

其中R是电阻,C是寄生电容(parasitic capacitance),包括了pin脚的电容和板子的电容。

但是,push-pull相对的缺点是往往需要消耗更多的电流,即功耗相对大。

而open-drain所消耗的电流相对较小,由电阻R所限制,而R不能太小,因为当输出为低电平的时候,需要sink更低的transistor,这意味着更高的功耗。

而open-drain的好处之一是,允许你short多个open-drain的电路,共用一个上拉电阻,此种做法称为wired-OR连接,此时可以通过拉低任何一个IO的pin脚使得输出为低电平。

为了输出高电平,则所有的都输出高电平。

此种逻辑,就是“线与”的功能,可以不需要额外的门电路来实现此部分逻辑。