pcie处理层协议中文详解

pcie基本原理

pcie基本原理PCI Express(Peripheral Component Interconnect Express)是一种高速串行总线标准,用于连接计算机内部的各种设备和组件,例如显卡、网卡、声卡等。

PCIe基于串行传输方式和点对点连接的思想,相比传统的并行总线具有更高的带宽和更低的延迟。

1. PCIe物理层PCIe物理层包括差分信号传输、时钟恢复、电源管理等方面。

差分信号传输是PCIe最关键的特性之一,它使用两条反向传输线代表一个数据位,实现了抗干扰性能更好和更远距离的数据传输。

时钟恢复是指接收端通过解码发送端发送过来的时钟信息来恢复本地时钟,从而实现同步通信。

电源管理则是为了节省能源,在设备空闲或未使用时自动进入低功耗模式。

2. PCIe数据链路层PCIe数据链路层负责将上层逻辑层的请求转换成可被物理层发送的数据包,并在接收端将数据包还原成原始请求。

数据链路层分为两个子层:逻辑子层(Logical Sublayer)和传输子层(Transport Sublayer)。

逻辑子层主要负责错误检测和纠正,传输子层则负责流量控制和错误恢复。

3. PCIe传输层PCIe传输层是PCIe中最重要的层次之一,它定义了数据包如何在发送端和接收端之间传输。

PCIe采用基于令牌的流控制方式,发送端将数据包打成一个个TLP(Transaction Layer Packet),并通过令牌的方式将TLP交给接收端。

如果接收端准备好接收数据,则返回一个令牌给发送端,发送端才会将数据包发送出去。

这种流控制方式可以有效地避免数据包丢失和冲突。

4. PCIe事务层PCIe事务层是PCIe协议中最高层次的逻辑,它定义了如何进行读写操作、配置设备、中断处理等操作。

PCIe事务分为两种类型:读取(Read)和写入(Write)。

读取操作由请求者发起,写入操作由请求者或响应者发起。

配置空间是一种特殊的地址空间,用于存储设备的配置信息。

PCI总线标准协议(中文版)

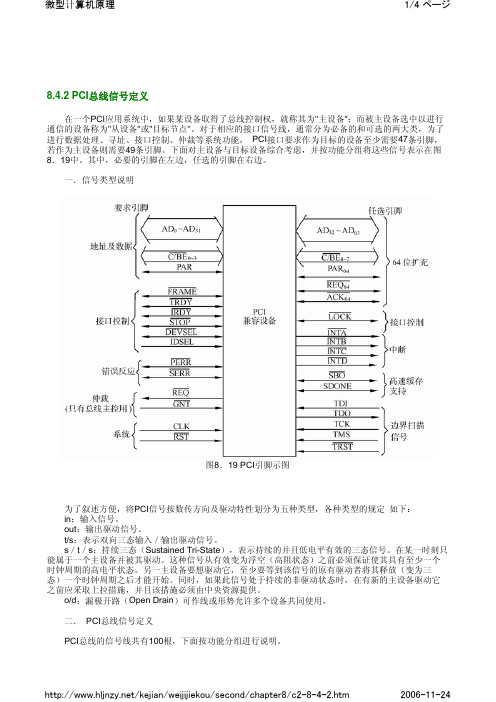

8.4.2 PCI总线信号定义在一个PCI应用系统中,如果某设备取得了总线控制权,就称其为"主设备";而被主设备选中以进行通信的设备称为"从设备"或"目标节点''。

对于相应的接口信号线,通常分为必备的和可选的两大类,为了进行数据处理、寻址、接口控制、仲裁等系统功能, PCI接口要求作为目标的设备至少需要47条引脚,若作为主设备则需要49条引脚。

下面对主设备与目标设备综合考虑,并按功能分组将这些信号表示在图8.19中。

其中,必要的引脚在左边,任选的引脚在右边。

一.信号类型说明图8.19 PCI引脚示图为了叙述方便,将PCI信号按数传方向及驱动特性划分为五种类型,各种类型的规定 如下:in:输入信号。

out:输出驱动信号。

t/s:表示双向三态输入/输出驱动信号。

s/t/s:持续三态(Sustained Tri-State),表示持续的并且低电平有效的三态信号。

在某一时刻只能属于一个主设备并被其驱动。

这种信号从有效变为浮空(高阻状态)之前必须保证使其具有至少一个时钟周期的高电平状态。

另一主设备要想驱动它,至少要等到该信号的原有驱动者将其释放(变为三态)一个时钟周期之后才能开始。

同时,如果此信号处于持续的非驱动状态时,在有新的主设备驱动它之前应采取上拉措施,并且该措施必须由中央资源提供。

o/d:漏极开路(Open Drain)可作线或形势允许多个设备共同使用,二. PCI总线信号定义PCI总线的信号线共有100根,下面按功能分组进行说明。

1.系统引线CLK in:时钟输入,为所有PCI上的接口传送提供时序。

其最高频率可达66MHz,最低频率一般为0(DC),这一频率也称为PCI的工作频率。

对于PCI的其他信号,除、、、之外,其余信号都在CLK的上升沿有效(或采样)。

in:复位,用来使PCI专用的特性寄存器和定时器相关的信号恢复规定的初始状况。

PCIe协议相关资料要点

PCIe协议相关资料要点PCIe(Peripheral Component Interconnect Express)是一种计算机总线标准,用于连接计算机系统的外部设备。

它在现代计算机中广泛应用于图形卡、存储卡和扩展卡等设备的连接。

下面是PCIe协议的相关资料要点。

一、PCIe协议概述PCIe协议是一种高速串行通信协议,用于在计算机系统中传输数据。

它取代了传统的PCI总线,提供更高的带宽和更可靠的性能。

PCIe协议具有以下特点:1. 高速性能:PCIe协议支持多个通道和多个数据传输通路,并且每个通道都可以达到多Gbps的传输速度。

2. 点对点连接:PCIe协议采用点对点连接方式,每个设备都直接连接到主机,并且不会与其他设备共享带宽。

3. 热插拔支持:PCIe协议支持热插拔功能,可以在计算机运行时插入或拔出设备,而无需重新启动系统。

4. 多功率状态支持:PCIe协议支持多功率状态,可以有效地管理设备的能耗。

二、PCIe协议架构PCIe协议的架构包括物理层、数据链路层和传输层。

每个层级都有不同的功能和责任。

1. 物理层(Physical Layer):物理层负责在发送和接收设备之间传输数据。

它定义了数据传输的电气特性、传输速度和功耗等参数。

2. 数据链路层(Data Link Layer):数据链路层负责在发送和接收设备之间建立可靠的数据传输连接。

它通过发送和接收数据包来确保数据的完整性和可靠性。

3. 传输层(Transport Layer):传输层负责数据的路由和传输。

它根据设备的地址和标识符来确定数据的发送和接收。

三、PCIe协议数据传输PCIe协议的数据传输分为读取和写入两种方式。

1. 读取(Read):读取是指从PCIe设备读取数据到主机内存。

读取传输由主机启动,并且主机提供要读取的目标地址。

读取过程中,设备将数据传输到主机内存中的指定地址。

2. 写入(Write):写入是指将数据从主机内存写入到PCIe设备。

pcie协议

pcie协议第一篇:PCIe协议概述PCIe是Peripheral Component Interconnect Express 的缩写,是一种计算机总线标准,用于连接计算机内部各种组件和外部设备。

PCIe可以用于连接图形卡、网卡、声卡、存储设备、专用加速器等各种设备,是现代计算机系统中最常用的总线标准之一。

PCIe协议是为了解决传统PCI总线面临的瓶颈问题而提出的。

传统的PCI总线由于采用并行数据传输技术,在传输数据时存在严重的时序问题和信号完整性问题,随着计算机系统的发展,越来越难以满足高速数据传输的需求。

为了解决这些问题,PCI-SIG(Peripheral Component Interconnect Special Interest Group)组织推出了PCIe协议,这种协议采用串行数据传输技术,在数据传输速度、可扩展性、信号完整性等方面都有较大的优势。

PCIe协议定义了物理层、数据链路层、传输层和应用层等四个层次,每个层次都有相应的协议规范。

其中,物理层规范定义了PCIe总线的物理连线方式、电气特性和传输速率等信息;数据链路层规范定义了数据的帧格式、编码方式和错误检测等信息;传输层规范定义了总线控制、数据流控制和仲裁协议等信息;应用层规范定义了各种设备和驱动程序在PCIe 总线上的交互方式。

PCIe协议的优势在于可以实现高速、可靠的数据传输,同时还具有可扩展性和灵活性等优点。

随着计算机应用场景的不断拓展和计算能力的不断提升,PCIe协议在现代计算机系统中发挥着越来越重要的作用。

第二篇:PCIe协议的物理层PCIe协议的物理层是指PCIe总线物理层协议规范,在PCIe总线系统中,物理层主要是用来定义总线的物理连线方式、电气特性和传输速率等信息。

PCIe协议中规定了四种不同的物理层规范,分别是PCIe 1.0、PCIe 2.0、PCIe 3.0和PCIe 4.0。

PCIe 1.0是最初的版本,采用8b/10b编码方式,传输速率最高可达250MB/s。

PCI-E_数据链路层协议

数据链路层协议数据链路层作为处理层和物理层的中间层,为处理层TLP 在链路中传递提供可靠机制。

数据链路层主要负责TLP的可靠传输。

所以数据链路层完成的主要任务是:1、数据交换。

接收发送方处理层的TLP包,并送到物理层。

另外从物理层接收TLP 包并送到接收端的处理层。

2、出错检测和裁决。

LCRC和序列号(TLP Sequence Number)的生成;存储发送端的TLP用于再试重发;为TLP和DLLP 做数据完成性检测(crc校验);DLLP 的ack和nack响应;错误指示;链接确认超时重试机制。

3、初始化和电源管理。

跟踪链路状态并传送链路活动、链路复位、链路失去连连等状态给处理层;4、生成DLLP。

用于链路管理功能包括TLP确认、电源管理、流程控制信息(VC通道初始化) 交流。

在链接两端的数据链路层点对点传输.数据完整性检测就是为DLLP和TLP做crc校验DLLP使用crc-16,TLP使用32bit的LCRC,此外,TLP还有一个序列号(sequence Number),用于检测TLP 丢失与否。

LCRC 和sequence Number检测有误的TLP或者在发送过程中丢失的TLP,将被发送端重新发送。

发送端存放TLP的备份,在需要的时候将备份发送或者在收到接收端的正确接收确认后清除备份。

数据链路层跟踪链路连接的状态,并和处理层和物理层交流链路状态,通过物理层来完成对链路的管理。

链路层中包含状态机DLCMSM (Data Link Control and Management State Machine) 来完成这些任务,以下详细介绍。

•DL_Inactive - Physical Layer reporting Link is non-operational or nothing is connected to the Port•DL_Init - Physical Layer reporting Link is operational, initialize Flow Control for the default Virtual Channel•DL_Active - Normal operation modeStatus output:•DL_Down - The Data Link Layer is not communicating with the component on the other side of the Link.•DL_Up - The Data Link Layer is communicating with the component on the other side of the Link.Dl_Inactive状态随PCIE复位之后,将所有数据链路状态信息恢复到默认值,并放弃数据层重试缓冲器中的内容。

pcie,协议,中文

竭诚为您提供优质文档/双击可除pcie,协议,中文篇一:pcie学习资料whitepaper了解pciexpress的基本工作原理synopsys产品市场营销经理scottknowlton20xx年9月从并行转向串行pciexpress(或称pcie),是一项高性能、高带宽,此标准由互连外围设备专业组(pci-sig)制订,用于替代pci、pciextended(pci-x)等基于总线的通讯体系架构以及图形加速端口(agp)。

转向pcie主要是为了实现显著增强系统吞吐量、扩容性和灵活性的目标,同时还要降低制造成本,而这些都是基于总线的传统互连标准所达不到的。

pciexpress标准在设计时着眼于未来,并且能够继续演进,从而为系统提供更大的吞吐量。

第一代pcie规定的吞吐量是每秒2.5千兆比特(gbps),第二代规定的吞吐量是5.0gbps,而最近公布pcie3.0标准已经支持8.0gbps的吞吐量。

在pcie标准继续充分利用最新技术来提供不断加大的吞吐量的同时,采用分层协议也便于pci向pcie的演进,并保持了与现有pci应用的驱动程序软件兼容性。

虽然最初的目标是计算机扩展卡以及图形卡,但pcie目前也广泛适用于涵盖更广的应用门类,包括网络组建、通信、存储、工业电子设备和消费类电子产品。

本白皮书的目的在于帮助读者进一步了解pciexpress以及成功pcie成功应用。

pciexpress基本工作原理拓扑结构本节介绍了pcie协议的基本工作原理以及当今系统中实现和支持pcie协议所需要的各个组成部分。

本节的目标在于提供pcie的相关工作知识,并未涉及到pcie协议的具体复杂性。

pcie的优势就在于降低了复杂度所带来的成本。

pcie属于一种基于数据包的串行连接协议,它的复杂度估计在pci并行总线的10倍以上。

之所以有这样的复杂度,部分是由于对以千兆级的速度进行并行至串行的数据转换的需要,部分是由于向基于数据包实现方案的转移。

PCIE总线的分层协议介绍

在PCIE总线中信息是以封包的形式传输的,下面为大家介绍一下数据在PCIE设备中是如何封包以及怎样传输的,这里我们将省去路由寻址、流量控制等一些细节,只介绍数据在设备中的传输过程。

PCIE总线采用了串行连接方式,并使用数据包(Packet)进行数据传输,采用这种结构有效去除了在PCI 总线中存在的一些边带信号,如INTx和PME#等信号。

在PCIE总线中,数据报文在接收和发送过程中,需要通过多个层次,包括事务层、数据链路层和物理层,才能完成数据的传输。

PCIE总线的层次结构如图1所示。

图1 PCIE总线的层次结构在PCIE体系结构中,数据报文首先在设备的核心层(Device Core)中产生,然后再经过该设备的事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer),最终发送出去。

而接收端的数据也需要通过物理层、数据链路和事务层,并最终到达Device Core。

下面将介绍各个层次的功能以及该层数据的封包形态,每个层次从发送端和接收端两个方面来讲:1、事务层(Transaction Layer)事务层是三层协议结构的最高层,数据在这一层组成最基本的数据包,即事务层数据包(Transaction Layer Packet,TLP)。

在发送端,当处理器或者其他PCIE设备访问PCIE设备时,事务层接收来自PCIE设备核心层的数据,并将其封装为TLP后,发向数据链路层。

在接收端,事务层可以从数据链路层中接收数据报文,然后转发至PCIE设备的核心层。

接收部分将入站的TLP保存在虚拟通道缓冲区中,根据TLP中的ECRC字段检查CRC错误。

若无误,则删去ECRC字段,将在TLP Header中得到的信息及数据有效载荷(Data Payload)发送给用户接口。

事务层数据包(TLP)主要由一个或多个可选的TLP Prefixes、一个TLP Header、一个Data Payload 和一个可选的TLP Digest组成。

PCIE事务层协议(Transaction Layer Specifications)范文

处理层协议(transaction Layer specification)◆TLP概况。

◆寻址定位和路由导向。

◆i/o,memory,configuration,message request、completetion详解。

◆请求和响应处理机制。

◆virtual channel(vc)Mechanism虚拟通道机制。

◆data integrity数据完整性。

一.TLP概况处理层(transaction Layer specification)是请求和响应信息形成的基础。

包括四种地址空间,三种处理类型,从下图可以看出在transaction Layer 中形成的包的基本概括。

一类是对i/o口和memory的读写包(TLPS:transaction Layers packages),另一类是对配置寄存器的读写设置包,还有一类是信息包,描述通信状态,作为事件的信号告知用户。

对memory的读写包分为读请求包和响应包、写请求包(不需要存储器的响应包)。

而i/o类型的读写请求都需要返回I/O口的响应包,configuration包对配置寄存器的读写请求也有响应包。

这些请求包还可以按属性来分就是:NP-nonposted ,即请求需要返回completion的响应包;还有一种就是;poste,即不需要completion返回响应包。

例如上面的存储器写入请求包和Message包都隶属于posted包。

包的主要格式结构如下:每种类型的包都有一定格式的包头(Tlp Header),根据不同的包的特性,还包括有效数据负荷(Data Payload)和tlp开销块(Tlp Digest)。

包头中的数据用于对包的管理和控制。

有效数据负荷域存放有效数据信息。

具有数据的TLP传递是有一定规则的:以DW为长度单位,发送端数据承载量不得超过“Device Control Register”中的“Max_Payload_Size”数值,接收端中,所接收到的数据量也不能超过接收端“Device Control Register”中的“Max_Payload_Size”数值。

pci总线标准协议

pci总线标准协议PCI总线标准协议。

PCI(Peripheral Component Interconnect)总线是一种用于连接外部设备和主板的总线标准,它是一种高速、并行的总线结构,可以支持多种设备的连接。

PCI总线标准协议是为了规范PCI总线的通信协议而制定的,它规定了PCI设备之间的通信方式、数据传输规范和电气特性等,对于PCI设备的互操作性和兼容性起到了重要的作用。

首先,PCI总线标准协议规定了PCI设备之间的通信方式。

PCI设备之间的通信是通过地址、数据和控制信号进行的,协议规定了这些信号的传输方式和时序要求,确保了设备之间的正常通信。

同时,协议还规定了总线仲裁、数据传输和中断请求等机制,保证了多个设备之间的协调工作。

其次,PCI总线标准协议规定了数据传输的规范。

在PCI总线上,数据传输是通过读写操作进行的,协议规定了数据传输的时序、速率和错误检测等要求,保证了数据的可靠传输。

此外,协议还规定了总线的带宽分配和数据缓冲机制,以提高数据传输的效率和可靠性。

另外,PCI总线标准协议还规定了PCI设备的电气特性。

由于PCI总线是一种并行总线,对于信号的电平和时序要求非常严格,协议规定了总线上信号的电气特性,包括电压、电流和信号波形等,以确保设备能够正常工作并且不会对其他设备造成干扰。

总的来说,PCI总线标准协议是对PCI总线通信协议的规范,它规定了PCI设备之间的通信方式、数据传输规范和电气特性等,保证了设备之间的互操作性和兼容性。

在实际应用中,遵循PCI总线标准协议可以有效地提高系统的稳定性和可靠性,同时也为设备的设计和开发提供了统一的标准,促进了整个行业的发展。

总的来说,PCI总线标准协议是一项非常重要的技术规范,它为PCI设备的设计、开发和应用提供了统一的标准,保证了设备之间的互操作性和兼容性。

在实际应用中,遵循PCI总线标准协议可以有效地提高系统的稳定性和可靠性,同时也为设备的设计和开发提供了统一的标准,促进了整个行业的发展。

pcie协议

pcie协议

PCIe协议是一种计算机总线标准,用于连接主板和外设,旨在取代老旧的PCI总线。

PCIe协议采用串行传输,具有高速、高扩展性、可靠性强等优点,已成为现代计算机中最常用的总线之一。

PCIe协议分为基本协议、物理层协议和传输层协议。

其

中基本协议定义了总线操作的控制流程,如传输格式、数据流、延迟等。

物理层协议定义了硬件接口形式、传输速率、信号幅度等。

传输层协议则对应用软件层提供了一些服务和接口。

PCIe协议支持多级拓扑结构,可以在主板和外设之间增

加多个USB和扩展卡以满足系统扩展的需求。

同时,PCIe协

议也支持热插拔,外设在未关机的情况下,可以在不影响系统正常工作的情况下进行更换。

PCIe协议的传输速率越来越高,现在最新版的PCIe4.0

协议传输速率已经达到了16 GT/s,相比较PCIe 3.0协议的8 GT/s速率提升了两倍。

并且PCIe 4.0协议允许在同一时刻进

行多次传输,大大提升了数据的传输效率,使计算机性能得到全面提升。

总之,PCIe协议是一种高效、高速、可靠的计算机总线

标准,广泛应用于现代计算机中的各类外设连接和数据传输。

随着技术的不断发展,PCIe协议的传输速率和性能将会进一

步提升,相信未来会有更多的应用场景出现。

pcie处理层协议中文详解

p c i e(P C I-E x p r e s s)处理层协议中文详解处理层协议(transaction Layer specification)◆TLP概况。

◆寻址定位和路由导向。

◆i/o,memory,configuration,message request、completion详解。

◆请求和响应处理机制。

◆virtual channel(vc)Mechanism虚拟通道机制。

◆data integrity数据完整性。

一.TLP概况处理层(transaction Layer specification)是请求和响应信息形成的基础。

包括四种地址空间,三种处理类型,从下图可以看出在transaction Layer 中形成的包的基本概括。

一类是对i/o口和memory的读写包(TLPS:transaction Layers packages),另一类是对配置寄存器的读写设置包,还有一类是信息包,描述通信状态,作为事件的信号告知用户。

对memory 的读写包分为读请求包和响应包、写请求包(不需要存储器的响应包)。

而i/o类型的读写请求都需要返回I/O口的响应包,configuration包对配置寄存器的读写请求也有响应包。

这些请求包还可以按属性来分就是:NP-non posted ,即请求需要返回completion的响应包;还有一种就是;poste,即不需要completion返回响应包。

例如上面的存储器写入请求包和Message包都隶属于posted包。

包的主要格式结构如下:每种类型的包都有一定格式的包头(Tlp Header),根据不同的包的特性,还包括有效数据负荷(Data Payload)和tlp开销块(Tlp Digest)。

包头中的数据用于对包的管理和控制。

有效数据负荷域存放有效数据信息。

具有数据的TLP传递是有一定规则的:以DW为长度单位,发送端数据承载量不得超过“Device Control Register”中的“Max_Payload_Size”数值,接收端中,所接收到的数据量也不能超过接收端“Device Control Register”中的“Max_Payload_Size”数值。

什么是PCIExpress协议

什么是PCIExpress协议外围设备互连(PCI)插槽是计算机体系结构中不可或缺的⼀部分,以⾄于⼤多数⼈将其存在视为理所当然。

多少年来,PCI ⼀直是将声卡、显卡和⽹卡连接到主板的万能且实⽤的⽅法。

但PCI也有⼀些不⾜之处。

处理器、显卡、声卡和⽹络的速度越来越快,并且功能越来越强⼤,⽽PCI却⼀直在“原地踏步”。

它的带宽固定为32位,⽽且每次只能处理5个设备。

新款的64位PCI-X总线可以提供更⾼的带宽,但也随之带来了⼀些其他的PCI问题。

⼀种名为PCI Express(PCIe)的新协议消除了其中许多的不⾜,提供更⾼的带宽,并且与现有的操作系统兼容。

在本⽂中,我们将了解PCIe与PCI的区别所在。

我们还将介绍PCI Express如何使计算机运⾏得更快、如何能潜在地增加图形性能,以及能否代替AGP插槽。

HowStuffWorks Shopper供图PCI Express连接的每条线路包含两对导线,其中⼀对⽤于发送,另⼀对⽤于接收。

数据包以每周期⼀位的速度在线路间传输。

x1连接,即最⼩的PCIe连接,有⼀条由四根导线组成的线路。

各⽅向上每周期都传输⼀位。

x2链接包含⼋根导线,⼀次传输两位,x4链接传输四位,以此类推。

其他配置还有x12、x16和x32。

但是⼀个串⾏连接是如何快于PCI的32根导线或PCIx的64根导线的呢?在下⼀部分中,我们将介绍PCIe如何以串⾏格式提供⾼带宽。

速度更快,连接更少32位PCI总线的最⼤速度可以达到33兆赫兹,即总线每秒最多可传输133兆字节的数据。

64位PCI-X总线是PCI总线带宽的两倍。

不同的PCI-X规范允许的数据传输速度也不同,范围从每秒512兆字节到1G字节。

使⽤PCI的设备共享通⽤总线,但每个使⽤PCI Express的设备与交换机之间都具有⾃⼰的专⽤连接。

⼀条PCI Express线路每个⽅向每秒钟可以处理200兆字节的通信量。

x16PCIe连接器每个⽅向每秒钟可以传输惊⼈的6.4G字节数据。

PCI-E_事务层协议

处理层协议(transaction Layer specification)◆TLP概况。

◆寻址定位和路由导向。

◆i/o,memory,configuration,message request、completetion详解。

◆请求和响应处理机制。

◆virtual channel(vc)Mechanism虚拟通道机制。

◆data integrity数据完整性。

一.TLP概况处理层(transaction Layer specification)是请求和响应信息形成的基础。

包括四种地址空间,三种处理类型,从下图可以看出在transaction Layer 中形成的包的基本概括。

一类是对i/o口和memory的读写包(TLPS:transaction Layers packages),另一类是对配置寄存器的读写设置包,还有一类是信息包,描述通信状态,作为事件的信号告知用户。

对memory的读写包分为读请求包和响应包、写请求包(不需要存储器的响应包)。

而i/o类型的读写请求都需要返回I/O口的响应包,configuration包对配置寄存器的读写请求也有响应包。

这些请求包还可以按属性来分就是:NP-non posted ,即请求需要返回completion的响应包;还有一种就是;poste,即不需要completion返回响应包。

例如上面的存储器写入请求包和Message包都隶属于posted包。

包的主要格式结构如下:每种类型的包都有一定格式的包头(Tlp Header),根据不同的包的特性,还包括有效数据负荷(Data Payload)和tlp开销块(Tlp Digest)。

包头中的数据用于对包的管理和控制。

有效数据负荷域存放有效数据信息。

具有数据的TLP传递是有一定规则的:以DW为长度单位,发送端数据承载量不得超过“Device Control Register”中的“Max_Payload_Size”数值,接收端中,所接收到的数据量也不能超过接收端“Device Control Register”中的“Max_Payload_Size”数值。

pcie处理层协议中文详解

pcie ( PCI-Express )处理层协议中文详解处理层协议(transaction Layer specification ♦TLP概况。

♦寻址定位和路由导向。

♦i/o,memory,configuration,message request、completion 详解。

♦请求和响应处理机制。

♦virtual channel(vc)Mechanism 虚拟通道机制。

♦data integrity数据完整性。

一.TLP概况处理层(transaction Layer specification)是请求和响应信息形成的基础。

包括四种地址空间,三种处理类型,从下图可以看出在transaction Layer中形成的包的基本概括。

一类是对i/o 口和memory 的读写包(TLPS : transaction Layerspackages),另一类是对配置寄存器的读写设置包,还有一类是信息包,描述通信状态,作为事件的信号告知用户。

对memory 的读写包分为读请求包和响应包、写请求包(不需要存储器的响应包)。

而i/o类型的读写请求都需要返回I/O 口的响应包,configuration包对配置寄存器的读写请求也有响应包。

这些请求包还可以按属性来分就是:NP-non posted,即请求需要返回completion 的响应包;还有一种就是;poste,即不需要completion 返回响应包。

例如上面的存储器写入请求包和Message包都隶属于posted包。

包的主要格式结构如下:每种类型的包都有一定格式的包头(Tlp Header),根据不同的包的特性,还包括有效数据负荷(Data Payload)和tip开销块(Tip Digest)。

包头中的数据用于对包的管理和控制。

有效数据负荷域存放有效数据信息。

具有数据的TLP传递是有一定规则的:以DW为长度单位,发送端数据承载量不得超过“ Device Control Register” 中的“ Max_Payload_Size 数值,接收端中,所接收到的数据量也不能超过接收端“Device Co ntrol Register ”中的“ Max_Payload_Size”数值。

pcie处理层协议详情中文详解

pcie(PCI-Express)处理层协议中文详解处理层协议(transaction Layer specification)◆TLP概况。

◆寻址定位和路由导向。

◆i/o,memory,configuration,message request、completion详解。

◆请求和响应处理机制。

◆virtual channel(vc)Mechanism虚拟通道机制。

◆data integrity数据完整性。

一.TLP概况处理层(transaction Layer specification)是请求和响应信息形成的基础。

包括四种地址空间,三种处理类型,从下图可以看出在transaction Layer 中形成的包的基本概括。

一类是对i/o口和memory的读写包(TLPS:transaction Layers packages),另一类是对配置寄存器的读写设置包,还有一类是信息包,描述通信状态,作为事件的信号告知用户。

对memory的读写包分为读请求包和响应包、写请求包(不需要存储器的响应包)。

而i/o类型的读写请求都需要返回I/O口的响应包,configuration包对配置寄存器的读写请求也有响应包。

这些请求包还可以按属性来分就是:NP-non posted ,即请求需要返回completion的响应包;还有一种就是;poste,即不需要completion返回响应包。

例如上面的存储器写入请求包和Message包都隶属于posted包。

包的主要格式结构如下:每种类型的包都有一定格式的包头(Tlp Header),根据不同的包的特性,还包括有效数据负荷(Data Payload)和tlp开销块(Tlp Digest)。

包头中的数据用于对包的管理和控制。

有效数据负荷域存放有效数据信息。

具有数据的TLP传递是有一定规则的:以DW为长度单位,发送端数据承载量不得超过“Device Control Register”中的“Max_Payload_Size”数值,接收端中,所接收到的数据量也不能超过接收端“Device Control Register”中的“Max_Payload_Size”数值。

pcie协议,中文

竭诚为您提供优质文档/双击可除pcie协议,中文篇一:pcie总线的分层协议介绍在pcie总线中信息是以封包的形式传输的,下面为大家介绍一下数据在pcie设备中是如何封包以及怎样传输的,这里我们将省去路由寻址、流量控制等一些细节,只介绍数据在设备中的传输过程。

pcie总线采用了串行连接方式,并使用数据包(packet)进行数据传输,采用这种结构有效去除了在pci总线中存在的一些边带信号,如intx和pme#等信号。

在pcie总线中,数据报文在接收和发送过程中,需要通过多个层次,包括事务层、数据链路层和物理层,才能完成数据的传输。

pcie总线的层次结构如图1所示。

图1pcie总线的层次结构在pcie体系结构中,数据报文首先在设备的核心层(devicecore)中产生,然后再经过该设备的事务层(transactionlayer)、数据链路层(datalinklayer)和物理层(physicallayer),最终发送出去。

而接收端的数据也需要通过物理层、数据链路和事务层,并最终到达devicecore。

下面将介绍各个层次的功能以及该层数据的封包形态,每个层次从发送端和接收端两个方面来讲:1、事务层(transactionlayer)事务层是三层协议结构的最高层,数据在这一层组成最基本的数据包,即事务层数据包(transactionlayerpacket,tlp)。

在发送端,当处理器或者其他pcie设备访问pcie设备时,事务层接收来自pcie设备核心层的数据,并将其封装为tlp后,发向数据链路层。

在接收端,事务层可以从数据链路层中接收数据报文,然后转发至pcie设备的核心层。

接收部分将入站的tlp保存在虚拟通道缓冲区中,根据tlp 中的ecRc字段检查cRc错误。

若无误,则删去ecRc字段,将在tlpheader中得到的信息及数据有效载荷(datapayload)发送给用户接口。

事务层数据包(tlp)主要由一个或多个可选的tlpprefixes、一个tlpheader、一个datapayload和一个可选的tlpdigest组成。

PCI总线标准协议(中文版)

PCI总线标准协议(中⽂版)8.4.2 PCI总线信号定义在⼀个PCI应⽤系统中,如果某设备取得了总线控制权,就称其为"主设备";⽽被主设备选中以进⾏通信的设备称为"从设备"或"⽬标节点''。

对于相应的接⼝信号线,通常分为必备的和可选的两⼤类,为了进⾏数据处理、寻址、接⼝控制、仲裁等系统功能, PCI接⼝要求作为⽬标的设备⾄少需要47条引脚,若作为主设备则需要49条引脚。

下⾯对主设备与⽬标设备综合考虑,并按功能分组将这些信号表⽰在图8.19中。

其中,必要的引脚在左边,任选的引脚在右边。

⼀.信号类型说明图8.19 PCI引脚⽰图为了叙述⽅便,将PCI信号按数传⽅向及驱动特性划分为五种类型,各种类型的规定如下:in:输⼊信号。

out:输出驱动信号。

t/s:表⽰双向三态输⼊/输出驱动信号。

s/t/s:持续三态(Sustained Tri-State),表⽰持续的并且低电平有效的三态信号。

在某⼀时刻只能属于⼀个主设备并被其驱动。

这种信号从有效变为浮空(⾼阻状态)之前必须保证使其具有⾄少⼀个时钟周期的⾼电平状态。

另⼀主设备要想驱动它,⾄少要等到该信号的原有驱动者将其释放(变为三态)⼀个时钟周期之后才能开始。

同时,如果此信号处于持续的⾮驱动状态时,在有新的主设备驱动它之前应采取上拉措施,并且该措施必须由中央资源提供。

o/d:漏极开路(Open Drain)可作线或形势允许多个设备共同使⽤,⼆. PCI总线信号定义PCI总线的信号线共有100根,下⾯按功能分组进⾏说明。

1.系统引线CLK in:时钟输⼊,为所有PCI上的接⼝传送提供时序。

其最⾼频率可达66MHz,最低频率⼀般为0(DC),这⼀频率也称为PCI的⼯作频率。

对于PCI的其他信号,除、、、之外,其余信号都在CLK的上升沿有效(或采样)。

in:复位,⽤来使PCI专⽤的特性寄存器和定时器相关的信号恢复规定的初始状况。

(完整版)PCIe协议相关资料

(完整版)PCIe协议相关资料1.PCIe简介PCI-Express是最新的总线和接⼝标准,它原来的名称为“3GIO”,是由英特尔提出的,很明显英特尔的意思是它代表着下⼀代I/O接⼝标准。

交由PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为“PCI-Express”。

这个新标准将全⾯取代现⾏的PCI和AGP,最终实现总线标准的统⼀。

它的主要优势就是数据传输速率⾼,⽬前最⾼可达到10GB/s以上,⽽且还有相当⼤的发展潜⼒。

PCI Express也有多种规格,从PCI Express 1X到PCI Express 16X,能满⾜现在和将来⼀定时间内出现的低速设备和⾼速设备的需求。

能⽀持PCI Express的主要是英特尔的i915和i925系列芯⽚组。

PCI Express(以下简称PCI-E)采⽤了⽬前业内流⾏的点对点串⾏连接,⽐起PCI以及更早期的计算机总线的共享并⾏架构,每个设备都有⾃⼰的专⽤连接,不需要向整个总线请求带宽,⽽且可以把数据传输率提⾼到⼀个很⾼的频率,达到PCI所不能提供的⾼带宽。

相对于传统PCI总线在单⼀时间周期内只能实现单向传输,PCI-E的双单⼯连接能提供更⾼的传输速率和质量,它们之间的差异跟半双⼯和全双⼯类似。

PCI-E的接⼝根据总线位宽不同⽽有所差异,包括X1、X4、X8以及X16,⽽X2模式将⽤于内部接⼝⽽⾮插槽模式。

PCI-E规格从1条通道连接到32条通道连接,有⾮常强的伸缩性,以满⾜不同系统设备对数据传输带宽不同的需求。

此外,较短的PCI-E卡可以插⼊较长的PCI-E插槽中使⽤,PCI-E接⼝还能够⽀持热拔插,这也是个不⼩的飞跃。

PCI-E X1的250MB/秒传输速度已经可以满⾜主流声效芯⽚、⽹卡芯⽚和存储设备对数据传输带宽的需求,但是远远⽆法满⾜图形芯⽚对数据传输带宽的需求。

因此,⽤于取代AGP接⼝的PCI-E 接⼝位宽为X16,能够提供5GB/s的带宽,即便有编码上的损耗但仍能够提供约为4GB/s左右的实际带宽,远远超过AGP 8X的2.1GB/s的带宽。

pci协议

pci协议PCI(Peripheral Component Interconnect)即外围设备互联协议,是一种用于计算机内部各种外围设备(如显卡、声卡、网卡等)与主板之间进行通信的标准接口规范。

它是由美国PCI局(PCI-SIG)制定并推广的,旨在提供高性能、低功耗、可扩展的外围设备连接方式。

PCI协议的出现对计算机行业产生了深远的影响。

首先,它标准化了各种外围设备与主板之间的接口,使得不同厂商的设备可以在同一主板上互换。

这种标准化降低了硬件的开发和制造成本,加速了外围设备的发展。

其次,PCI协议提供了高带宽和高速率传输的能力,使得外围设备可以与主机快速的进行数据交换,从而提升了整个系统的运行效率。

另外,PCI协议还支持热插拔功能,即在计算机运行的同时插入或拔出外部设备,而无需重新启动计算机,这大大提高了硬件设备的可维护性和可升级性。

PCI协议的特点之一是其高性能。

PCI总线的传输速率可以达到133MB/s,使得外围设备可以迅速地传输大量的数据。

此外,PCI协议还支持多通道传输,即可以同时进行多个设备的数据传输,对于需要大量数据交换的应用来说,这一点尤为重要。

PCI协议的另一个重要特点是其良好的兼容性和可扩展性。

PCI协议可以与PCI Express等其他高速传输协议进行兼容,使得计算机在升级外围设备时具备更大的灵活性。

此外,PCI协议还支持总线的扩容,即可以通过增加PCI插槽的数量来扩展更多的外围设备的连接。

对于企业和个人用户来说,遵循PCI协议可以带来一系列的好处。

首先,使用PCI接口的外围设备具备更好的通用性,可以在不同的计算机系统中灵活使用。

其次,PCI协议的高性能和高带宽特点可以提升计算机系统的整体性能,使计算机的数据处理能力得到提升。

最后,PCI协议的可扩展性可以保证计算机系统在日后升级外围设备时的兼容性和扩展性。

总的来说,PCI协议是一种重要的计算机接口标准,它具备高性能、低功耗、可扩展等多种特点,为计算机内部各种外围设备的连接提供了规范。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

pcie(PCI-Express)处理层协议中文详解处理层协议(transaction Layer specification)◆TLP概况。

◆寻址定位和路由导向。

◆i/o,memory,configuration,message request、completion详解。

◆请求和响应处理机制。

◆virtual channel(vc)Mechanism虚拟通道机制。

◆data integrity数据完整性。

一.TLP概况处理层(transaction Layer specification)是请求和响应信息形成的基础。

包括四种地址空间,三种处理类型,从下图可以看出在transaction Layer 中形成的包的基本概括。

一类是对i/o口和memory的读写包(TLPS:transaction Layers packages),另一类是对配置寄存器的读写设置包,还有一类是信息包,描述通信状态,作为事件的信号告知用户。

对memory 的读写包分为读请求包和响应包、写请求包(不需要存储器的响应包)。

而i/o类型的读写请求都需要返回I/O口的响应包,configuration包对配置寄存器的读写请求也有响应包。

这些请求包还可以按属性来分就是:NP-non posted ,即请求需要返回completion的响应包;还有一种就是;poste,即不需要completion 返回响应包。

例如上面的存储器写入请求包和Message包都隶属于posted包。

包的主要格式结构如下:每种类型的包都有一定格式的包头(Tlp Header),根据不同的包的特性,还包括有效数据负荷(Data Payload)和tlp开销块(Tlp Digest)。

包头中的数据用于对包的管理和控制。

有效数据负荷域存放有效数据信息。

具有数据的TLP传递是有一定规则的:以DW为长度单位,发送端数据承载量不得超过“Device Control Register”中的“Max_Payload_Size”数值,接收端中,所接收到的数据量也不能超过接收端“Device Control Register”中的“Max_Payload_Size”数值。

TLp Digest域是32位的ECRC校验。

具体的包结构图如下:由此图可看出数据从低字节的高位先发送,从左到右。

以下详细介绍TLPS的每个成分。

R为保留信息位,应设为0,路由器switch对此位不做修改,接收器应该忽略此位。

▲Fmt[1:0]:Format of TLP (see Table 2-2) –bits 6:5 of byte0▲Type[4:0]:Type of TLP – bits 4:0 of byte 0▲TC[2:0]:Traffic Class – bits [6:4] of byte1,关于TC的作用将在下文说明。

▲Attr[1:0]:Attributes – bits [5:4] of byte 2,详细介绍见下文▲TD:1b indicates presence of TLP digest in the form of a single DW at the end of the TLP标志TLPDigest域的有无。

▲EP: indicates the TLP is poisoned – bit 6 of byte 2有效数据中毒(出错)机制。

▲Length[9:0]:Length of data payload in DW.Fmt开销位说明TLP Header的长度和TLP是否包含数据,见下图。

▲Fmt[1:0]=00b,代表3DW的包头,没有数据。

▲Fmt[1:0]=01b,代表4DW的包头,没有数据。

▲Fmt[1:0]=10b,代表3DW的包头,有数据。

▲Fmt[1:0]=11b,代表4DW的包头,有数据。

Fmt和Type开销组合定义了包(TLP)的类型如下。

上图定义了各种类型的包,图中的r[2:0]用于定义Message 包的隐含寻址方式,在下文中更为详细。

Length域定义了有效负荷的DW长度如下。

在不包含data payload块的包中Length的值应被设置为保留值R,并被接收端忽略。

余下的各个开销位将在后文提到。

二.TLP打包定址和路由导向方式主要有三种TLP寻址方式:地址路由(address)、ID识别路由、间接路由(implicit)。

下面主要解释address和ID寻址方式,间接寻址将在后面提及。

address寻址主要用于memory和i/o request请求包,memory 读写请求包支持64位地址和32位地址,i/o读写请求只支持32位地址。

64位地址寻址的TLP Header有4DW(16字节),32位地址寻址的TLP Header有3DW长。

上图就是64位地址的4DW的包头和32位地址的3DW的包头。

对于memory读写request包,AT(address Type field)有如下的编码。

ID寻址方式主要用在configuration 请求包、部分message 包、响应包中。

ID包括Bus number、Divce number、function number 为TLP定位目标接收器。

ID寻址的TLP包头长度也有4DW和3DW两种,ID在TLP中位置见下图。

第七个Byte(Byte7)是第一个DW数据负荷和最后一个DW 数据负荷使能位(Byte Enables),Byte Enables在于memory,i/o,configuration 请求包中有效,如图。

对于last DW BE和1st DW BE中的每一个位,为0表示相应的数据字节不被读或写,为1表示相应的数据字节有效。

每个使能位相对应的字节如下。

处理层描述符(transaction Descriptor),用于请求器件和应答器件间转送处理层信息,包括三部分,Transaciton ID、Attributes、Traffic class(TC)。

如下图。

其中Transaction ID包括: Requester ID、Tag,如图。

Tag[7:0]是由产生请求包的器件生成的,如果请求器件需要应答,则每个Tag[7:0]和Function Number是独一无二的。

Transaction ID是一个全局标识符用于响应包寻址请求器件。

TC的规定如下,描述服务的层次和用于映射虚拟通道:处理层描述符在请求包中第二个DW:。

中图中看出,描述字符放在第二个DW的前三个字节中。

三.i/o,memory,configuration,message request、completetion 详解。

memory、i/o、configuration request包头除了基本的域之外还包括:Transaction ID即requester ID、Tag、Last DW BE、1st DW BE,放在第二个DW中。

以下分别介绍这三种不同的请求包。

memory request package:采用直接地址寻址,有64bit地址和32bit地址两种,其中读请求包的Length域不应大于Max_Read_Request_Size寄存器设置的值。

请求器件不会示例一个所访问的memory空间超过4KB的read request包。

以下是两种不同地址长度的memory request 包。

I/O request 包:I/O request 包只有32位地址寻址。

有如下限制:▲TC[2:0] must be 000b▲Attr[1:0] must be 00b▲AT[1:0] must be 00b▲Length[9:0] must be 00 0000 0001b▲Last DW BE[3:0] must be 0000b格式如下:可见每次只传送一个DW数据。

configuration request包:configuration request包采用ID寻址方式,包头(Tlp Header长度是3DW)。

有如下规定:• TC[2:0] must be 000b• Attr[1:0] must be 00b• AT[1:0] must be 00b• [9:0] must be 00 0000 0001b• Last DW BE[3:0] must be 0000b包格式:Message 包:Message包分为:INTx Interrupt Signaling INTx中断信息包Power Management 电源管理机能。

Error Signaling错误信息包Locked Transaction Support 锁住交易的支持Slot Power Limit Support插槽电源限制的支持Vendor-Defined Messages制造商自行定义信息所有的Message包都用Msg编码,即不包括数据负荷的Message包,除了Vendor_Defined Messages和Set_Slot_Power_Limit Message包,Message包有以下限制:□The Message Code field must be fullydecoded (Message aliasing is not permitted).□Except as noted, the Attr[1:0] field is reserved.保留Attr域。

□AT[1:0] must be 00b.□Except as noted, bytes 8 through 15 arereserved.保留包头部分的bytes8到byte15.□Message Requests are posted and do notrequire Completion.Message包不需要返回响应包。

□Message Requests follow the same ordering rules as Memory Write Requests.寻址方式:隐含寻址,由Type域中的r[2:0]决定,即Type域的最后三位。

具体寻址映射如下:r[2:0]是010时,寻址方式就是ID寻址。

completion rules(应答机制):completion包用ID 寻址方式,寻址使用的ID就是request提供的requester ID。

除了那些正常的域以外,还包括:◆Completer ID[15:0] – Identifies theCompleter – described in detail below◆Completion Status[2:0] – Indicates the statusfor a Completion◆BCM – Byte Count Modified◆Byte Count[11:0] – The remaining byte countfor Request◆Tag[7:0] – in combination with the RequesterID field, corresponds to the Transaction ID◆Lower Address[6:0] – lower byte address forstarting byte of Completioncompl.Status位有如下含义:四.请求和应答处理机制处理机制就是对接收到的经Data Link Layer进行数据完整性验证的Tlp进行处理。