EPM1270 cpld实验板原理图,以通过调试。

CPLD应用设计平台 调试说明(1)

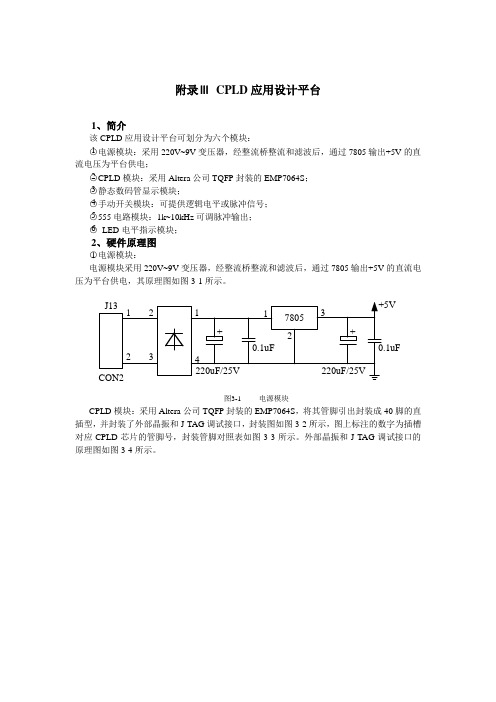

附录ⅢCPLD应用设计平台1、简介该CPLD应用设计平台可划分为六个模块:○1电源模块:采用220V~9V变压器,经整流桥整流和滤波后,通过7805输出+5V的直流电压为平台供电;○2CPLD模块:采用Altera公司TQFP封装的EMP7064S;○3静态数码管显示模块;○4手动开关模块:可提供逻辑电平或脉冲信号;○5555电路模块:1k~10kHz可调脉冲输出;○6LED电平指示模块;2、硬件原理图○1电源模块:电源模块采用220V~9V变压器,经整流桥整流和滤波后,通过7805输出+5V的直流电压为平台供电,其原理图如图3-1所示。

图3-1电源模块CPLD模块:采用Altera公司TQFP封装的EMP7064S,将其管脚引出封装成40脚的直插型,并封装了外部晶振和J-TAG调试接口,封装图如图3-2所示,图上标注的数字为插槽对应CPLD芯片的管脚号,封装管脚对照表如图3-3所示。

外部晶振和J-TAG调试接口的原理图如图3-4所示。

图3-2封装图图3-3封装管脚对照表图3-4外部晶振和J-TAG调试接口○3数码管显示模块,采用共阳极数码管静态显示,用74LS47译码和驱动参阅第4章。

在图3-5中,将最高位的74LS47的/RBI接地,/BI/RBO接到低一位的/RBI引脚,最低位/BI/RBO接高电平,这样级联即可实现灭零显示。

图3-5数码管显示模块○4逻辑开关模块:采用RS触发器74LS279从而消抖并提供逻辑电平或脉冲信号,如图3-6所示,逻辑开关模块如图3-7所示。

图3-6 74LS279管脚图图3-7逻辑开关模块○5555电路模块:555电路模块可实现1k~10kHz 可调脉冲输出,其原理图如图3-8所示。

图中,R A =10k,R B =50k(可调电位器),输出频率范围1k~10kHz 可调脉冲输出。

+V CCR BC 17U +5VU +5V U +5V U +5V 图3-8 555电路模块图3-9 LED 模块○6LED 模块,低电平时点亮,如图3-9所示。

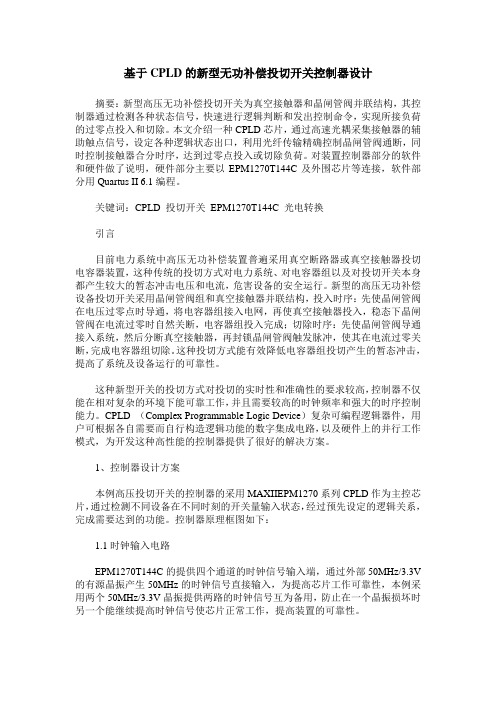

基于CPLD的新型无功补偿投切开关控制器设计

基于CPLD的新型无功补偿投切开关控制器设计摘要:新型高压无功补偿投切开关为真空接触器和晶闸管阀并联结构,其控制器通过检测各种状态信号,快速进行逻辑判断和发出控制命令,实现所接负荷的过零点投入和切除。

本文介绍一种CPLD芯片,通过高速光耦采集接触器的辅助触点信号,设定各种逻辑状态出口,利用光纤传输精确控制晶闸管阀通断,同时控制接触器合分时序,达到过零点投入或切除负荷。

对装置控制器部分的软件和硬件做了说明,硬件部分主要以EPM1270T144C及外围芯片等连接,软件部分用Quartus II 6.1编程。

关键词:CPLD 投切开关EPM1270T144C 光电转换引言目前电力系统中高压无功补偿装置普遍采用真空断路器或真空接触器投切电容器装置,这种传统的投切方式对电力系统、对电容器组以及对投切开关本身都产生较大的暂态冲击电压和电流,危害设备的安全运行。

新型的高压无功补偿设备投切开关采用晶闸管阀组和真空接触器并联结构,投入时序:先使晶闸管阀在电压过零点时导通,将电容器组接入电网,再使真空接触器投入,稳态下晶闸管阀在电流过零时自然关断,电容器组投入完成;切除时序:先使晶闸管阀导通接入系统,然后分断真空接触器,再封锁晶闸管阀触发脉冲,使其在电流过零关断,完成电容器组切除。

这种投切方式能有效降低电容器组投切产生的暂态冲击,提高了系统及设备运行的可靠性。

这种新型开关的投切方式对投切的实时性和准确性的要求较高,控制器不仅能在相对复杂的环境下能可靠工作,并且需要较高的时钟频率和强大的时序控制能力。

CPLD (Complex Programmable Logic Device)复杂可编程逻辑器件,用户可根据各自需要而自行构造逻辑功能的数字集成电路,以及硬件上的并行工作模式,为开发这种高性能的控制器提供了很好的解决方案。

1、控制器设计方案本例高压投切开关的控制器的采用MAXIIEPM1270系列CPLD作为主控芯片,通过检测不同设备在不同时刻的开关量输入状态,经过预先设定的逻辑关系,完成需要达到的功能。

CPLD可编程数字信号发生器通信原理实验正文

实验一CPLD可编程数字信号发生器实验实验项目名称:CPLD可编程数字信号发生器实验项目性质:验证性所属课程名称:数字通信原理实验计划学时:2一、实验目的1.熟悉各种时钟信号的特点及波形2.熟悉各种数字信号的特点及波形二、实验电路的工作原理1、CPLD可编程模块电路的功能及电路组成图2-1是CPLD可编程模块的电路图。

CPLD可编程模块(芯片位号:U101)用来产生实验系统所需要的各种时钟信号和数字信号。

它由CPLD可编程器件ALTERA公司的EPM7128(或者是Xilinx公司的XC95108)、编程下载接口电路(J101)和一块晶振(OSC1)组成。

晶振用来产生系统内的16.384MHz 主时钟。

本实验要求参加实验者了解这些信号的产生方法、工作原理以及测量方法,才可通过CPLD可编程器件的二次开发生成这些信号,理论联系实践,提高实际操作能力。

2、各种信号的功用及波形CPLD型号为EPM7128由计算机编好程序从J101下载写入芯片,OSC1为晶体,频率为16.384MHz,经8分频得到2.048MHz主时钟,面板测量点与EPM7128各引脚信号对应关系如下:SP101 2048kHz主时钟方波对应U101EPM7128 11脚SP102 1024kHz 方波对应U101EPM7128 10脚SP103 512kHz 方波对应U101EPM7128 9脚SP104 256kHz 方波对应U101EPM7128 8脚SP105 128kHz 方波对应U101EPM7128 6脚SP106 64K 方波对应U101EPM7128 5脚SP107 32K 方波对应U101EPM7128 4脚SP108 16K 方波对应U101EPM7128 81脚SP109 8K 方波对应U101EPM7128 80脚SP110 4K 方波对应U101EPM7128 79脚SP111 2K 方波对应U101EPM7128 77脚SP112 1K 方波对应U101EPM7128 76脚SP113 PN32K 32kHz伪随机码对应U101EPM7128 75脚SP114 PN2K 2kHz伪随机码对应U101EPM7128 74脚SP115 自编自编码波形,波形由对应U101EPM7128 73脚J102开关位置决定SP116 长0长1码码形为1、0连“1”对应U101EPM7128 70脚与1、0连“0”码SP117 X 绝对码输入对应U101EPM7128 69脚SP118 Y 相对码输出对应U101EPM7128 68脚SP119 F80 8kHZ时隙取样脉冲对应U101EPM7128 12脚此外,取样时钟、编码时钟、同步时钟、时序信号还将被接到需要的单元电路中。

CPLD实验板共20页word资料

实验电路板的设计太原理工大学自动化系夏路易自己设计制作实验板是非常有意思的事情。

第一部分实验板方案选择(一)目前的数字电路实验随着数字电子技术的发展,对数字电路的教学要求也越来越高,不仅要求同学们学会一般数字电路的原理,而且要求同学们能用中小规模数字电路设计一定复杂程度的数字系统。

数字电路的实验也应该配合教材,从验证性实验向设计性实验发展,满足培养21世纪人才的要求。

但是,目前的各种数字电路实验装置不能满足教学要求,采用这些装置进行数字电路实验有如下缺点:1.为满足各种实验,需要种类繁多的数字集成电路,增加了实验费用和管理的难度,若是由于经费问题未购得所需的数字集成器件,则不能开设需要该器件的实验。

2.实验电路连线复杂,集成电路好坏难辫,经常导致实验的失败,并损坏实验电路或实验装置。

3.实验中,数字集成电路器件经常损坏严重,导致实验费用增加。

4.因为一个课程设计题目所需器件的种类多并且连线复杂,所以进行数字电路课程设计很困难。

5.中小规模集成电路在数字系统设计中已经很少使用,学生在学校不能学到新的数字系统的设计方法(二)基于可编程逻辑器件的数字电路实验可编程逻辑器件是一种可以通过编程,改变系统连线,达到系统重构的器件,该器件可以现场编程,就是说当该器件安装到电路板上后,可以对它的功能进行重新设置,这样就可以非常方便的进行数字系统的设计与制作。

由于可编程逻辑器件的价格不断降低,门密度不断增大,所以该器件取代中小规模数字集成电路只是时间问题。

可编程逻辑器件是数字系统设计中的首选器件,它增加系统可靠性、减少系统体积和功耗、缩短设计周期并降低系统成本,由于它的工作速度快,所以在数字信号处理、自动控制、计算机接口板等方面应用非常广泛。

可编程逻辑器件用于数字电路实验有如下特点:1.设计方法先进在计算机上输入数字电路原理图或用硬件描述语言描述数字电路,经过编译,然后将编译后的数据文件下载到可编程逻辑器件中是目前最流行的数字电路设计方法。

USBCPLD开发板使用手册

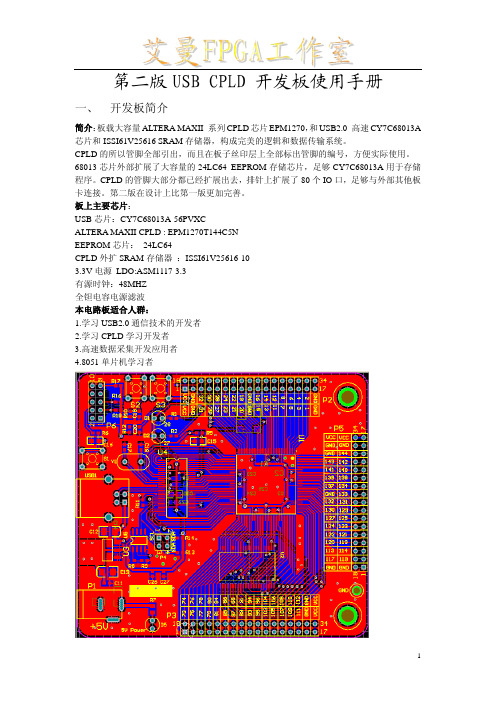

第二版USB CPLD 开发板使用手册一、开发板简介简介:板载大容量ALTERA MAXII 系列CPLD芯片EPM1270,和USB2.0 高速CY7C68013A 芯片和ISSI61V25616 SRAM存储器,构成完美的逻辑和数据传输系统。

CPLD的所以管脚全部引出,而且在板子丝印层上全部标出管脚的编号,方便实际使用。

68013芯片外部扩展了大容量的24LC64 EEPROM存储芯片,足够CY7C68013A用于存储程序。

CPLD的管脚大部分都已经扩展出去,排针上扩展了80个IO口,足够与外部其他板卡连接。

第二版在设计上比第一版更加完善。

板上主要芯片:USB芯片:CY7C68013A-56PVXCALTERA MAXII CPLD : EPM1270T144C5NEEPROM芯片:24LC64CPLD外扩SRAM存储器:ISSI61V25616-103.3V电源LDO:ASM1117-3.3有源时钟:48MHZ全钽电容电源滤波本电路板适合人群:1.学习USB2.0通信技术的开发者2.学习CPLD学习开发者3.高速数据采集开发应用者4.8051单片机学习者二、CY7C68013与EPM1270连接管脚定义表三、其它管脚定义说明1.板卡背面有源晶振连接CPLD PIN 20 时钟输入管脚。

2.两个LED灯连接CPLD PIN27,PIN28管脚,在板子的丝印层已经标出。

3.EEPROM相关R8是给EEPROM 的A0脚上拉,R9是给A0脚下拉,我们板子上使用24LC64芯片,所以焊接R8,针对24LC00,24LC02,24LC04芯片,请去掉R8电阻,将R9短路。

P4的4个针脚是IIC总线的信号线,我们将3,4短路,则EEPROM连接至IIC总线上,如果断开,则跟总线断开。

1,2脚分别是IIC总线的SCL,SDA信号。

使用的时候,如果你将板卡的EEPROM里面烧写了数据,不能被EZUSB CONTROL PANNEL识别,那么请将3,4断开,安装EEPROM恢复步骤来擦除24LC64里面的内容。

第二讲—CPLD的基本结构和原理

11.03.2019

8

浮栅型电可擦除熔丝结构

G1 S

G2 SiO 2 D

大多数CPLD器 件采用此工艺

n+

n+

可反复编程 不用每次上电重新 下载,但相对速度 慢,功耗较大

11.03.2019

9

(4)SRAM编程技术

与浮栅型熔丝结构基本相同。SRAM编程技术是 在FPGA器件中采用的主要编程工艺之一。SRAM型的 FPGA是易失性的,断电后其内部编程数据(构造代码) 将丢失,需在外部配接ROM存放FPGA的编程数据。 可反复编程,实现系统功能的动态重构 每次上电需重新下载,实际应用时需外 挂EEPROM用于保存程序

11.03.2019

10

二、复杂可编程逻辑器件(CPLD)的基本原理

CPLD由可编程逻辑的功能块围绕一个可编程 互连矩阵构成。由固定长度的金属线实现逻辑 单元之间的互连,并增加了I/O控制模块的数量 和功能。可以把CPLD的基本结构看成由可编 程逻辑阵列(LAB)、可编程I/O控制模块和可 编程内部连线(PIA)等三部分组成。

11.03.2019

15

EPM7128E乘积项扩展和并联扩展项的结构图

来 自 上 一 个 宏 单 元 Preset 乘 积 项 选 择 矩 阵 宏 单 元 乘 积 项 逻 辑

Clock Clear

共 享 乘 积 项

并 联 扩 展

Preset 乘 积 项 选 择 矩 阵 宏 单 元 乘 积 项 逻 辑

11.03.2019

13

宏单元结构图

0 1 2 3 4 5 6 7 8 9 10

11.03.2019

14

(1)乘积项共享结构

在CPLD的宏单元中,如果输出表达式的与项较 多,对应的或门输入端不够用时,可以借助可编程开 关将同一单元(或其他单元单元中提供未使用的乘积项 给其他宏单元使用。

EPM1270T144I5中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

f

有关等效宏单元详细信息,请参阅

宏单元转换方法

白皮书.

MAX II逻辑元素

MAX II和MAX IIG器件有三种速度等级:-3,-4,-5,与

-3是最快.同样,MAX IIZ器件有三种速度等级可供选择:-6,

-7,和-8,以-6是最快.这些速度等级代表总体相对

性能,而不是任何特定时序参数.对于传播延迟定时

2006年12月, 1.6版 2006年8月, 1.5版 2006年7月, 1.4版

■ 更新 表1-2.

■ 更新"简介"一节. ■ 更新新文档格式. ■ 通过表1-5更新表1-1. ■ 增加"参考文献"部分. ■ 添加文档修订历史记录.

■ 次要更新功能列表.

■ 次要更新表.

更改摘要

增加信息速度等级-8 —

在256引脚EPM570,EPM1270和EPM2210设备之间迁移

FineLine BGA封装).垂直迁移意味着你可以迁移到设备

其专用引脚和JTAG引脚是相同电源引脚子集或

超集跨设备密度一个给定包.在任何最大密度

包具有最高数量电源引脚;你必须制定出最大

在一个包计划密度以提供必要电源引脚进行迁移.供

EPM 2210 EPM 2210G

2,210 1,700 1,270 to 2,210 8,192 272

7.0 304 1.2 4.6

EPM 240Z 240 192

128至240 8,192 80 7.5 152 2.3 6.5

EPM 570Z 570 440

240至570 8,192 160 9.0 152 2.2 6.7

100-Pin FineLine

BGA

最新CPLD实验板汇总

C P L D实验板实验电路板的设计太原理工大学自动化系夏路易自己设计制作实验板是非常有意思的事情。

第一部分实验板方案选择(一)目前的数字电路实验随着数字电子技术的发展,对数字电路的教学要求也越来越高,不仅要求同学们学会一般数字电路的原理,而且要求同学们能用中小规模数字电路设计一定复杂程度的数字系统。

数字电路的实验也应该配合教材,从验证性实验向设计性实验发展,满足培养21世纪人才的要求。

但是,目前的各种数字电路实验装置不能满足教学要求,采用这些装置进行数字电路实验有如下缺点:1.为满足各种实验,需要种类繁多的数字集成电路,增加了实验费用和管理的难度,若是由于经费问题未购得所需的数字集成器件,则不能开设需要该器件的实验。

2.实验电路连线复杂,集成电路好坏难辫,经常导致实验的失败,并损坏实验电路或实验装置。

3.实验中,数字集成电路器件经常损坏严重,导致实验费用增加。

4.因为一个课程设计题目所需器件的种类多并且连线复杂,所以进行数字电路课程设计很困难。

5.中小规模集成电路在数字系统设计中已经很少使用,学生在学校不能学到新的数字系统的设计方法(二)基于可编程逻辑器件的数字电路实验可编程逻辑器件是一种可以通过编程,改变系统连线,达到系统重构的器件,该器件可以现场编程,就是说当该器件安装到电路板上后,可以对它的功能进行重新设置,这样就可以非常方便的进行数字系统的设计与制作。

由于可编程逻辑器件的价格不断降低,门密度不断增大,所以该器件取代中小规模数字集成电路只是时间问题。

可编程逻辑器件是数字系统设计中的首选器件,它增加系统可靠性、减少系统体积和功耗、缩短设计周期并降低系统成本,由于它的工作速度快,所以在数字信号处理、自动控制、计算机接口板等方面应用非常广泛。

可编程逻辑器件用于数字电路实验有如下特点:仅供学习与交流,如有侵权请联系网站删除谢谢01.设计方法先进在计算机上输入数字电路原理图或用硬件描述语言描述数字电路,经过编译,然后将编译后的数据文件下载到可编程逻辑器件中是目前最流行的数字电路设计方法。

CPLD开发板CA127

CPLD开发板CA127Abstract 摘要:CPLD开发板CA127核心器件为 Altera MAX II系列的EPM1270,CA127具有丰富的板载资源,由于板载有51单片机,CA127还可以作为51单片机的学习开发板。

CA127实现了3.3V系统与5V系统对接功能,具体是通过74LVXC3245(或简称3245)实现的。

CA127随板资料中包括丰富的开发实例和制作开发实例的详细步骤说明,以及Quartus II环境下的设计输入,综合,仿真等内容。

CA127的EDA开发实例全部有VHDL和Verilog两个版本,CA127的51单片机开发实例包括汇编和C语言两个版本。

同时CA127还包括详细的使用手册和丰富的配套资料,非常适合CPLD,VHDL,Verilog开发学习者使用。

另外CA127随板CDROM中还包括的开发实例,在学习EDA开发,51单片机开发的同时还可以学习到开发环境中C#程序的开发,和C#也是系统上主要的开发环境和编程语言。

1概述联华众科CPLD开发板CA127核心器件为 Altera MAX II系列的EPM1270,CA127外观如下图所示。

整板为双面PCB,CPLD芯片可方便更换,板载LCD1602液晶屏在调试单片机程序或HDL程序是可作为输出设备使用。

CA127同时也可以作为单片机学习者使用。

联华众科CPLD开发板CA127具有丰富的板载资源。

核心器件包括CPLD芯片Altera EPM1270和PLCC封装的单片机STC89LE52。

EPM1270可用I/O分4组全部以插针的形式引出,以供外部扩展时使用。

时钟资源包括频率为66M有源晶振和1个外接有源晶振插座,外接有源晶振插座可直接安装用户自己希望的任何频率有源晶振。

显示资源包括6位共阳七段数码管,8位LED(绿色),1片1602LCD显示屏。

键盘资源包括4*4按键阵列,4个独立按键,和1个复位按键。

复位芯片为IMP812T,IMP812T输出高电平有效的复位脉冲,脉冲宽度为140ms。

基于CPLD器件MAXII EPM1270和PCI总线实现数据接收卡的设计

基于CPLD器件MAXII EPM1270和PCI总线实现数据接收卡的设计PCI9656支持66Mhz、64bit的PCIR2.2规范,提供了兼容PICMG2.1R2.0规范的CompactPCIHotSwap接口,其局部总线达到66MHz、32bit(支持0“66MHz、8/16bit),可为PCI(CompactPCI)适配器及嵌入式系统设计提供高性能的总线接口。

PCI9656的配置寄存器与PCI9054、PCI9056兼容,也方便了原有设计的移植。

PCI9656具有6条独立的数据通道,用于DirectMaster、DirectSlave以及DMA功能模式下的数据传输,其深FIFO设计有效提升了总线的突发传输性能。

1DirectMaster模式。

用于局部总线到PCI(CompactPCI)的数据传输,16QWords(128byte)和32QWords(256byte)的FIFO各应用于数据的读、写通道。

2DirectSlave模式。

用于PCI(CompactPCI)到局部总线的数据传输,16QWords(128byte)和32QWords(256byte)的FIFO各应用于数据的读、写通道。

3DMA模式。

PCI9656提供了两条DMA通道(Channel0、Channel1),使用了两独立的32QWords(256byte)双向FIFO。

两条DMA通道可同时传输数据,通过PCI9656的MARBR寄存器可配置其优先级关系。

PCI9656的DMA方式有常规的块模式(Blockmode)和集散模式(Scatter/Gathermode),而且支持以DREQ#、DASK#信号请求、应答的命令模式(Demandmode),可应用于通信领域中的实时数据传输。

在局部总线端,PCI9656简化了数据的传输控制逻辑,与ISA总线类似,方便了传输控制的设计实现。

PCI9656的局部总线有三种应用模式,可以适用不同的嵌入式处理器。

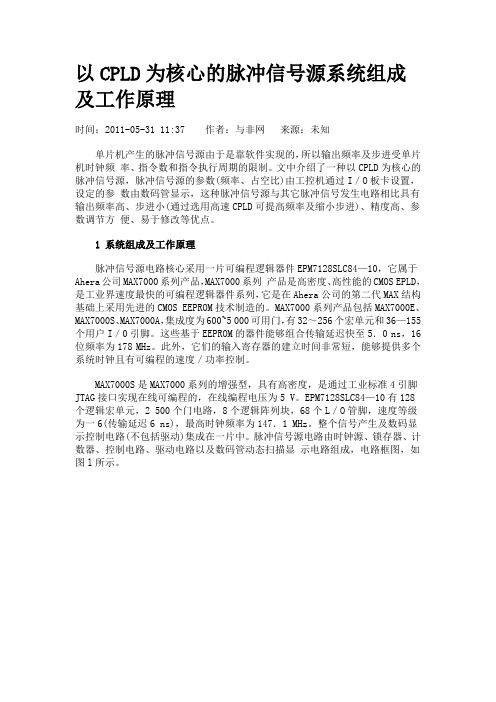

以CPLD为核心的脉冲信号源系统组成及工作原理(转自赛微电子网)

以CPLD为核心的脉冲信号源系统组成及工作原理时间:2011-05-31 11:37 作者:与非网来源:未知单片机产生的脉冲信号源由于是靠软件实现的,所以输出频率及步进受单片机时钟频率、指令数和指令执行周期的限制。

文中介绍了一种以CPLD为核心的脉冲信号源,脉冲信号源的参数(频率、占空比)由工控机通过I/O板卡设置,设定的参数由数码管显示,这种脉冲信号源与其它脉冲信号发生电路相比具有输出频率高、步进小(通过选用高速CPLD可提高频率及缩小步进)、精度高、参数调节方便、易于修改等优点。

1 系统组成及工作原理脉冲信号源电路核心采用一片可编程逻辑器件EPM7128SLC84—10,它属于Ahera公司MAX7000系列产品,MAX7000系列产品是高密度、高性能的CMOS EPLD,是工业界速度最快的可编程逻辑器件系列,它是在Ahera公司的第二代MAX结构基础上采用先进的CMOS EEPROM技术制造的。

MAX7000系列产品包括MAX7000E、MAX7000S、MAX7000A,集成度为600~5 000可用门,有32~256个宏单元和36—155个用户I/0引脚。

这些基于EEPROM的器件能够组合传输延迟快至5.0 ns,16位频率为178 MHz。

此外,它们的输入寄存器的建立时间非常短,能够提供多个系统时钟且有可编程的速度/功率控制。

MAX7000S是MAX7000系列的增强型,具有高密度,是通过工业标准4引脚JTAG接口实现在线可编程的,在线编程电压为5 V。

EPM7128SLC84—10有128个逻辑宏单元,2 500个门电路,8个逻辑阵列块,68个L/O管脚,速度等级为一6(传输延迟6 ns),最高时钟频率为147.1 MHz。

整个信号产生及数码显示控制电路(不包括驱动)集成在一片中。

脉冲信号源电路由时钟源、锁存器、计数器、控制电路、驱动电路以及数码管动态扫描显示电路组成,电路框图,如图l所示。

数字光纤通信线路编译码CPLD仿真实验报告

数字光纤通信线路编译码CPLD仿真实验一、实验目的1.熟悉m序列NRZ码、任意周期码产生原理以及光纤线路CMI编译码原理。

2.初步熟练Altera公司Maxplus II仿真平台的使用。

3.进一步熟悉数字电路设计技巧。

4.基本掌握如何进行CPLD的电路设计与仿真。

5.深入理解光纤线路编译码在光纤通信系统中的实际运用方法。

二、实验内容1.学习使用Altera公司Maxplus II仿真平台进行CPLD数字电路的设计与仿真。

2.设计m序列NRZ码产生电路以及光纤线路CMI编译码电路。

m序列: 伪随机序列;NRZ: 不归零码;CMI编码规则: 0码:01;1码::00/11 交替;3.通过CPLD仿真确保上述电路的正确设计。

4.总结光纤线路编译码在光纤通信系统中的实际运用。

三、实验要求A 实验过程要求在MAX+plus II软件仿真环境中,1.用绘制原理图的方法建立新工程,设计CPLD内部下述电路:15位m序列NRZ码的生成电路;CMI编码电路;CMI编码输入的选择电路:周期15位m序列与由周期15位二进制码表示本组内某学号最后四位(前面可补零)分别选择作为CMI编码输入;CMI译码电路(在实验室条件下使用统一系统时钟,输入为CMI编码输出)。

2.对所做设计完成正确编译。

3.使用仿真环境完成信号波形仿真。

CPLD电路仿真的输入输出信号即各测试点信号要求如下:输入:电路的总复位信号:1路(位);系统时钟信号(2Mbps):1路;CMI编码输入的选择信号:1路;输出:周期15位m序列NRZ码:1路;周期15位二进制后四位学号:1路;CMI编码输出信号:1路;CMI译码输出信号:1路;4.对仿真信号波形结果进行原理分析,发现可能的问题并加以解决,得到正确的仿真结果。

B 结果要求1.实验报告:总结实验目的、工作原理、实验内容、设计电路;对比设计报告中的信号波形理论分析结果与实际仿真结果是否存在差异,如果有差异,分析产生差异的原因;实验中出现的问题及解决方法;心得体会。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

U1D IO IO IO IO IO IO IO IO IO IO/DEV_CLRn IO/DEV_OE IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO 72 71 70 69 68 67 66 63 62 61 60 59 58 57 55 53 52 51 50 49 48 45 44 43 42 41 40 39 38 37 PIN54 PIN53 PIN52 PIN51 PIN50 PIN49 PIN48 PIN47 PIN46 PIN45 PIN44 PIN43 PIN42 PIN41 PIN40 PIN39 PIN38 PIN37 PIN36 PIN35 PIN34 PIN33 PIN32 PIN31 PIN30 PIN29 PIN28 PIN27 PIN26 PIN25

C23 0.1uF PIN18 PIN17 PIN16 PIN15 PIN14 PIN13 PIN12 PIN11 PIN10 PIN9 PIN8 PIN7 PIN6 PIN5 PIN4 PIN3 PIN2 PIN1 VCC P2 MOSI RST SCK MISO 1 3 5 7 9 2 4 6 8 10 VCC C32 U4 C31 1uF C30 1uF PIN60 TXD RP9 PIN61 D11 LED-RXD 3.3V D10 RXD 1 2 3 4 330 8 7 6 5 1 3 4 5 11 10 12 9 15 C1+ C1C2+ C2T1IN T2IN R1OUT R2OUT GND VDD VCC 2 16 1uF 3.3V 1 6 2 7 3 8 4 9 5 C33 1uF J4 C 11 10

C13 0.1uF

C14 0.1uF

C15 0.1uF

C16 0.1uF U3 3.3V K1 2 3 CF2 10uF MOSI MISO SCK RST PIN35 PIN34 PIN33 PIN32 PIN31 PIN30 PIN29 PIN28 PIN27 PIN26 PIN25 PIN24 PIN23 PIN22 PIN21 PIN20 PIN19 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 P1.0 VCC P1.1 P0.0 P1.2 P0.1 P1.3 P0.2 P1.4 P0.3 P1.5 P0.4 P1.6 P0.5 P1.7 P0.6 RST/VPD P0.7 P3.0/RxD EA/Vpp P3.1/TxD ALE/PROG P3.2/INT0 PSEN P3.3/INT1 P2.7 P3.4/T0 P2.6 P3.5/T1 P2.5 P3.6/WR P2.4 P3.7/RD P2.3 XTAL2 P2.2 XTAL1 P2.1 GND P2.0 89S51 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

1

1

1

1

1

3.3_VIO J2 C1 0.1uF 1 2 EN GND 32MHz VCC OUT 4 3 R8 R7 0 0 GCLK2 GCLK3

1 2 3 4 5 6 7 8

0.1uF C25

PIN50

0.1uF

1 2 3 4 5

8位拨码开关电路

C24

PIN51

6

DIG1

DIG2

DIG3

DIG4

D

U1E TDI TDO TCK TMS 34 36 35 33 TDI TDO TCK TMS EPM1270GT144C5

10uF PIN62 PIN64 PIN66 PIN68 PIN70 PIN72 PIN74 PIN76 PIN78 PIN80 PIN82 PIN84 PIN86

PIN63 10uF PIN65 PIN67 PIN69 PIN71 PIN73 PIN75 PIN77 PIN79 PIN81 PIN83 PIN85 PIN87

3.3V C29

VCC P4 R15 VCC PIN98 PIN97 PIN96 PIN95 PIN94 PIN93 PIN92 PIN91 PIN90 PIN89 PIN88 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 1602LCD Q6 PNP

EPM1270GT144C5

1

2

3

4

5

6

7

8

U1A IO IO IO IO IO IO IO IO IO IO IO/GCLK1 IO/GCLK0 IO IO IO IO IO IO IO IO IO IO IO IO IO IO 32 31 30 29 28 27 24 23 22 21 20 18 16 15 14 13 12 11 8 7 6 5 4 3 2 1 PIN24 PIN23 PIN22 PIN21 PIN20 PIN19 PIN18 PIN17 PIN16 PIN15 GCLK1 GCLK0 PIN14 PIN13 PIN12 PIN11 PIN10 PIN9 PIN8 PIN7 PIN6 PIN5 PIN4 PIN3 PIN2 PIN1

OUT OUT

Y1 XTAL24M

D Connector 9

LED-TXD

C7 0.1uF VCC D+ DGND 1 2 3 4

1 USB

GND GND

1

RS232通信电路

6 5

5 6 7 8

5 6 7 8

RP1 1K

RP4 1K

3.3V

3.3V

PIN112 PIN111 PIN110 PIN109 PIN108 PIN107

RP6 1K

3.3V

R10 1K

R11 1K

R12 1K

R13 1K

R16 1K

R17 1K

16 15 14 13 12 11 10 9

K5 S1 SW-DIP8 1 4 SW-PB1 K4 1 4 SW-PB1 K3 1 4 2 3 SW-PB1 K2 1 4 SW-PB1 2 3 2 3 2 3

C22 1 4 0.1uF C21 1 4 0.1uF C20 1 4 0.1uF C19 1 4 0.1uF

PIN47

K9 2 3 SW-PB1 K8 2 3 SW-PB1 K7 2 3 SW-PB1 K6 2 3 SW-PB1

C27

3 3 3 3 3 3

4 3 2 1

4 3 2 1

B Q7 2 MPSA13

DIG5

0.1uF

Error : 未命名 .JPG file not 未命名.J : 未命名 .J : 未命名 .JPG file not f file not f und Error : 未命名.JPG file not f file . PG file . ot 未命名.J o und. o . Error : f und. PG und f und : f und. PG o Error o Error o Error o not n

BANK 1

BANK 2

BANK 3

BANK 4

U1G 10 26 47 65 83 99 115 135 GNDIO GNDIO GNDIO GNDIO GNDIO GNDIO GNDIO GNDIO GNDINT GNDINT GNDINT GNDINT 17 54 92 128 C28

3.3V P3 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34

DP G D

DIG6

U5 JM-S03661B

8位按键电路

R4 1k TCK TDO TMS TDI 3.3V P1 1 3 5 7 9 2 4 6 8 10 3.3V RP3 1 2 3 4 330 D6 A 3.3V 1k R2 1k R1 RP2 1 2 3 4 330 D2 LED PIN59 8 7 6 5 D4 D3 LED LED PIN57 PIN58 1k R3 D5 LED PIN56 LED PIN55 8 7 6 5 D8 D7 LED LED PIN53 PIN54 D9 LED PIN52 PIN106 PIN105 PIN104 PIN103 PIN102 PIN101 PIN100 PIN99 8 7 6 5 8 7 6 5 RP8 100 RP7 100 1 2 3 4 1 2 3 4

10

11

12

13

14

7

8

9

A

C

B

E

F

Header 5X2

6位数码管电路-共阳极

A

Title Size Number 18-Aug-2011 Sheet of E:\MAX2-CPLD开发板 \m axcpld-v1.0\MAXCPLD.ddb By: Drawn 8 Revision

Header 5X2 VCC

T1OUT T2OUT R1IN R2IN VEE

14 7 13 8 6

C18 J1 1 2 3 Phonejack TN 30PF VCC 3 U2 VIN AMS1117-3.3

GND

AT89S51及ISP电路

MAX232ACWE

3.3V 2 4 CF1 10uF C12 0.1uF 30PF D1 LED R9 120 3.3V C17

U1C IO IO IO IO IO IO IO IO IO IO IO IO IO IO IO/GCLK3 IO/GCLK2 IO IO IO IO IO IO IO IO IO IO IO IO IO IO 108 107 106 105 104 103 102 101 98 97 96 95 94 93 91 89 88 87 86 85 84 81 80 79 78 77 76 75 74 73 PIN82 PIN81 PIN80 PIN79 PIN78 PIN77 PIN76 PIN75 PIN74 PIN73 PIN72 PIN71 PIN70 PIN69 GCLK3 GCLK2 PIN68 PIN67 PIN66 PIN65 PIN64 PIN63 PIN62 PIN61 PIN60 PIN59 PIN58 PIN57 PIN56 PIN55