重点内容08 处理器多周期实现

六章CPU设计

下地址控制编码方式

一般情况下后继微指令旳地址有下列几种给出方式:顺序递增法:将µPC设置成可实现自动加1旳功能,每当完毕目前指令旳执行,就以µPC +1后旳值为地址在控制存储器中取下一条微指令。直接给出法:下一条微指令旳地址直接取自微指令中旳下地址字段。分支转移法:在包括分支转移旳微指令中常设置一种条件选择子区域,用于指出哪些鉴定条件被测试,与此同步转移地址被存储在下地址字段。当转移条件满足时,将下地址字段旳内容读入到µPC中,取下一条微指令,实现微程序转移。若转移条件不满足,微程序则顺序执行。微程序入口地址旳形成:每条机器指令所相应旳微程序旳入口地址(首地址),一般由指令旳操作码所决定。在机器加电后,第一条微指令旳地址一般是由专门旳逻辑电路生成,也能够采用由外部直接输入旳形式取得。

操作控制编码方式

在操作控制字段一般涉及一种或多种操作控制域,每个控制域可控制一种或一组控制信号旳生成,根据控制信号是直接生成于控制域还是译码生成控制信号旳不同可分为下列几种形式。直接控制法:操作控制字段旳每一位都与一种独立控制信号相相应。若目前微指令旳某一位ki=1,则与之相应ci控制信号有效,不然ci控制信号无效。分段编码控制法:在微程序级别,许多微操作是能够并行执行。一般采用将微指令旳操作控制字段提成k个相互独立旳控制域,每一种控制域存储一组微操作,每一种编码相应一种微操作,每一种微操作都能够与其他控制域所存储旳任意一种微操作并行执行,但在组内旳微操作之间是互斥旳,不允许在同一时间段内发生或有效。分段间接编码控制法:在微指令格式里,假如一种字段旳含义不只决定本字段编码,还兼由其他字段决定,则可采用分段间接编码控制法。此时一种字段兼有两层或两层以上旳含义。其他方式:在实际微指令中操作控制编码并不是只单独采用上述三种编码方式中旳一种,而是将上述三种混合使用,以确保能综合考虑指令旳字长、灵活性和执行微程序旳速度等方面旳要求。

MIPS架构多周期CPU的设计

MIPS架构多周期CPU的设计蔡晓燕;袁春风;张泽生【摘要】针对教育部最新提出的计算机专业系统结构课程设置要求,分析利用VerilogHDL代码完成多周期CPU设计的具体过程和方案,以南京大学计算机科学与技术系为例,总结将其应用在教学上的效果。

提出在计算机专业本科教学阶段可进行计算机组成与设计相关实践课程教学的观点。

【期刊名称】《计算机教育》【年(卷),期】2014(000)017【总页数】4页(P93-96)【关键词】MIPS架构;多周期;数据通路;状态图【作者】蔡晓燕;袁春风;张泽生【作者单位】南京大学计算机科学与技术系江苏南京 210046;南京大学计算机科学与技术系江苏南京 210046;南京大学计算机科学与技术系江苏南京210046【正文语种】中文【中图分类】G642近年来,教育部计算机专业教学指导委员会组织了对该专业学生能力培养和实践教学体系的研究。

研究指出,教学必须树立系统观,培养学生的系统眼光。

使学生学会在不同层面把握不同层次的系统,并全面考虑系统各部分与外界的逻辑与联系,能够完成一定规模的系统设计[1]。

研究还指出,有了计算机系统基础和计算机组成与设计课程的基础,学生将更容易从计算机系统整体角度理解操作系统、编译原理等后续课程[1]。

研究确定以MIPS为模型机进行讲解,讲透原理,强化实践。

MIPS架构的微处理器是最简单的体系结构之一,作为一种开放的架构,用户可自行开发MIPS内核,并在其中添加指令。

MIPS架构被国际上许多著名大学用于计算机系统结构的本科生和研究生教学。

CPU结构由其所能够执行的指令决定,MIPS 32位架构是一种采用RISC(精简指令集)的处理器架构,它指令长度固定,采用load/store数据模型,算术和逻辑运算采用三目操作数的形式,带有32个通用寄存器[2-3]。

自2007年起开始,南京大学计算机科学与技术系开始探索用Verilog HDL代码实现MIPS架构多周期CPU设计。

单片机中的多任务处理技术

单片机中的多任务处理技术多任务处理技术是指在单片机系统中同时执行多个任务的能力。

随着单片机技术的快速发展,越来越多的应用需要同时处理多个任务,因此掌握多任务处理技术成为了单片机编程的重要一环。

一、多任务处理技术的原理及实现方法多任务处理技术的实现原理主要有两种:基于时间片轮转和基于优先级调度。

下面将分别对这两种方法进行介绍。

1. 基于时间片轮转的多任务处理技术基于时间片轮转的多任务处理技术是将系统时间划分为若干个时间片,每个任务被分配一个时间片进行执行。

当任务的时间片用完时,系统会切换到下一个任务,并将当前任务的状态保存,以便后续恢复执行。

这种方法的优点是能够保证每个任务都有机会被执行,避免任一任务长时间独占处理器资源。

同时,由于任务之间的切换速度很快,能够达到近乎同时执行的效果。

2. 基于优先级调度的多任务处理技术基于优先级调度的多任务处理技术是根据每个任务的优先级确定执行顺序。

具有较高优先级的任务将先于优先级较低的任务执行。

这种方法的优点是可以按照任务的紧急程度进行排序,确保紧急任务能够及时得到处理。

对于时间敏感的应用来说,这种方法更加适合。

二、多任务处理技术的应用场景多任务处理技术在单片机系统中有着广泛的应用场景,下面将介绍几个常见的应用。

1. 实时控制系统实时控制系统通常需要同时处理多个任务,例如数据采集、参数处理和控制输出等。

通过多任务处理技术,可以确保各个任务按时完成,提高系统的响应速度和稳定性。

2. 通信系统通信系统中常常需要同时进行数据的接收、处理和发送等任务。

多任务处理技术能够有效地分配处理器资源,确保数据能够实时处理和传输。

3. 智能家居系统智能家居系统需要同时处理多个设备的控制和数据处理任务,例如照明系统、安防系统和环境监测系统等。

多任务处理技术能够快速响应用户的操作,并确保各个子系统之间的平稳协调。

三、多任务处理技术的注意事项在使用多任务处理技术时,需要注意以下几点。

1. 任务的划分合理的任务划分是多任务处理技术的关键。

8核16线程原理

8核16线程原理

在计算机技术领域中,核心和线程是关于处理器的重要概念。

在现代计算机中,处理器的核心数和线程数对计算性能起着关键

作用。

8核16线程(8-core 16-thread)是指处理器具有8个物理核心和16个线程。

物理核心是处理器中真实存在的独立处理单元。

每个核心都可

以独立执行指令,包括算术、逻辑和控制操作。

物理核心可以同

时处理多个任务,提高计算机的处理速度。

线程是程序执行的最小单位。

线程是处理器执行任务的一种方式。

每个线程都有自己的程序计数器、寄存器和栈,可以独立执

行指令。

多线程技术利用线程的并行执行能力提高了计算性能。

8核16线程处理器具有8个物理核心和16个线程。

这是通过

超线程技术实现的。

超线程技术允许物理核心同时执行多个线程,提高了处理器的利用率。

在8核16线程处理器中,每个核心可以

同时处理两个线程,从而总共可以处理16个线程。

通过8核16线程处理器,可以实现更高的计算速度和更好的

多任务处理能力。

对于多线程的应用程序,8核16线程处理器可

以同时处理多个线程,提高了应用程序的执行效率。

在多任务的

情况下,每个核心可以分配给不同的任务,减少了任务之间的竞争,提高了系统的响应速度。

8核16线程处理器利用超线程技术,允许8个物理核心同时处

理16个线程,提高了计算机的处理速度和多任务处理能力。

这种

处理器在高性能计算和多线程应用程序中表现出色,为用户提供

更流畅的计算体验。

【10】2021清华大学912计算机专业基础综合考研经验+真题+参考书目

2021清华大学912计算机专业基础综合考研经验真题参考书目清华大学912计算机专业基础综合考试科目,2020年初试时间安排为12月22日下午14:00-17:00业务课二进行笔试,清华大学自主命题,考试时间3小时。

一、适用院系及专业清华大学计算机科学与技术系081200计算机科学与技术清华大学网络科学与网络空间研究院083900网络空间安全清华大学深圳国际研究生院085400电子信息专业学位清华大学清华大学全球创新学院0812J3数据科学和信息技术二、考研参考书目清华大学912计算机专业基础综合没有官方指定的考研参考书目,盛世清北根据专业老师指导及历年考生学员用书,推荐使用如下参考书目:《数据结构》第三版清华大学出版社邓俊辉《计算机网络》第五版清华大学出版社特南鲍姆《计算机组成软件硬件接口》第四版机械工业出版社帕特森《操作系统精髓与设计原理》第八版机械工业出版社威尔逊(1)参考书的阅读方法目录法:先通读各本参考书的目录,对于知识体系有着初步了解,了解书的内在逻辑结构,然后再去深入研读书的内容。

体系法:为自己所学的知识建立起框架,否则知识内容浩繁,容易遗忘,最好能够闭上眼睛的时候,眼前出现完整的知识体系。

问题法:将自己所学的知识总结成问题写出来,每章的主标题和副标题都是很好的出题素材。

尽可能把所有的知识要点都能够整理成问题。

(2)学习笔记的整理方法A:通过目录法、体系法的学习形成框架后,在仔细看书的同时应开始做笔记,笔记在刚开始的时候可能会影响看书的速度,但是随着时间的发展,会发现笔记对于整理思路和理解课本的内容都很有好处。

B:做笔记的方法不是简单地把书上的内容抄到笔记本上,而是把书上的关键点、核心部分记到笔记上,关上书本,要做到仅看笔记就能将书上的内容复述下来,最后能够通过对笔记的记忆就能够再现书本。

三、重难点知识梳理计算机组成原理部分一、整体要求1.理解单处理器计算机系统中各部件的内部工作原理、组成结构以及相互连接方式,具有完整的计算机系统的整机概念;2.理解计算机系统层次化结构概念,掌握以MIPS为代表的RISC指令集体系结构的基本知识,能对MIPS汇编程序设计语言的相关问题进行分析;3.理解计算机存储系统的层次化结构,掌握层次化存储系统的设计、分析和性能计算;4.能根据指令语义进行单周期、多周期或流水线MIPS处理器的数据通路及其控制器的分析和简单设计;5.理解并掌握输入输出系统的基本知识。

MIPS指令多周期CPU设计

MIPS指令多周期CPU设计MIPS(Microprocessor without Interlocked Pipeline Stages)是一种经典的指令集架构,也是一种常用的计算机体系结构之一、在本文中,将介绍如何设计一个多周期CPU来执行MIPS指令。

多周期CPU是一种在各个阶段使用不同时钟周期数的中央处理器设计。

其核心思想是将指令处理过程划分为若干个阶段,每个阶段由单独的硬件电路来执行。

通过这种方式,可以提高CPU的效率和性能。

下面将逐步介绍多周期CPU的设计步骤:1. 指令存储器(Instruction Memory):首先,需要设计一个指令存储器,用于存储MIPS指令。

指令存储器通常使用随机存取存储器(Random Access Memory, RAM),可以通过指令地址来读取指令。

2. 指令解码(Instruction Decode):在该阶段中,需要将从指令存储器中读取的指令进行解码。

解码的目的是确定指令的类型以及操作数的位置。

根据指令的类型,还需要通过控制信号来决定执行的下一步操作。

3. 寄存器读取(Register Read):在这个阶段中,需要从寄存器文件中读取操作数。

MIPS架构中有32个通用寄存器,它们存储着变量和数据。

4. 执行(Execute):在这个阶段中,需要执行指令的操作。

具体的操作取决于指令的类型。

例如,加法操作需要将操作数相加,存储结果。

5. 存储器访问(Memory Access):在这个阶段中,需要进行内存访问操作。

MIPS架构中,可以使用lw(load word)指令将数据从内存中加载到寄存器中,使用sw(store word)指令将数据从寄存器中存储到内存中。

6. 寄存器写入(Register Write):在这个阶段中,需要将执行阶段的结果写入到寄存器文件中。

以上是多周期CPU的基本设计流程。

在设计过程中,还需要考虑异常处理和分支跳转等特殊情况。

基于MIPS架构的多周期CPU设计

基于MIPS架构的多周期CPU设计柳成;荣静【摘要】为了提高多周期CPU流水线的效率,在指令存储器和数据存储器的数据读取中设计发送地址在上升沿、读取数据在下降沿,从而实现译码和访存在一个周期内完成.在取指级不再单独设置加法器,把PC+4放在ALU中完成.通过大量的多路选择器与数据交互总线来进行数据联通.采用Verilog HDL语言设计出CPU,并在VIVADO平台上实现仿真,最后通过龙芯公司的LS-CPU-EXB-002试验箱来进行验证,结果表明所设计的多周期CPU的有效性.【期刊名称】《软件》【年(卷),期】2018(039)008【总页数】5页(P40-44)【关键词】流水线;VerilogHDL;多周期CPU;LS-CPU-EXB-002试验箱【作者】柳成;荣静【作者单位】扬州大学广陵学院,江苏扬州 225000;扬州大学广陵学院,江苏扬州225000【正文语种】中文【中图分类】TP332MIPS架构是为流水线而生,每条MIPS指令的执行分为五个部分,每一个部分为一个流水级。

MIPS是最简单且内核开源的微处理器之一,相对于其它架构微处理器,相同位数的MIPS架构的时钟频率较低,其运行速度也较慢。

高效的CPU要求流水线的每一个阶段都占用固定的时间,再通过缩短流水线各个阶段的执行时间来提高时钟频率,在此我们通过改进取地址和读数据时钟控制来实现。

传统的MIPS架构多周期CPU的设计中,在发送地址的下一拍才能获得相应的数据,从指令和数据存储器中读取数据就需要等待一个周期,这样往往会造成资源浪费。

为了消除这个闲置时间,将发送地址设计在时钟的上升沿,读取数据放在下降沿,最终实现32位MIPS架构多周期CPU。

MIPS体系结构主要采用了流水线技术[1],它把一条指令的执行分为几个周期来完成。

这样每个周期处理器只做一件事,大大的减轻了处理器的任务,使处理器的频率更快,处理器也更高效。

通过改进文献[2]中的五级流水线得到如图1所示的多周期CPU流水线设计。

计算机组成原理课程大纲

计算机组成原理课程大纲一、课程简介计算机组成原理课程是计算机科学与技术专业的重要基础课程之一,旨在让学生全面了解计算机组成及其内部运行原理。

本课程内容涵盖计算机硬件组成、指令系统结构、处理器设计与实现、存储器层次结构、I/O系统等方面的知识,通过理论讲解与实践操作相结合的方式,培养学生的计算机系统分析、设计与优化能力。

二、课程目标1. 理解计算机系统的层次结构与组成部件,掌握计算机系统的发展历程;2. 掌握指令系统设计与硬件描述语言的基本原理与方法;3. 理解处理器的主要功能与运行原理,能够进行处理器的设计与实现;4. 理解计算机存储器层次结构、高速缓存、虚拟存储器等相关概念与技术;5. 了解计算机的I/O系统、总线结构及工作原理。

三、课程大纲与内容安排1. 第一章:引言1.1 计算机的发展历程1.2 计算机系统的层次结构1.3 计算机性能指标与评价方法2. 第二章:计算机硬件组成2.1 冯·诺依曼体系结构2.2 中央处理器(CPU)的组成与功能 2.3 存储器的层次结构与分类2.4 输入输出设备与接口控制器2.5 总线与主板3. 第三章:指令系统结构3.1 指令的格式与编码方式3.2 寻址方式与寻址模式3.3 指令的执行过程与流水线技术4. 第四章:处理器设计与实现4.1 单周期与多周期处理器设计4.2 流水线处理器设计与优化4.3 异常处理与中断机制5. 第五章:存储器层次结构5.1 存储器的分类与特性5.2 高速缓存的工作原理与替换策略5.3 虚拟存储器的概念与实现6. 第六章:I/O系统6.1 输入输出系统的基本概念与功能6.2 I/O接口与设备控制器6.3 DMA技术与中断处理四、教学方法与评估方式本课程以理论授课、实践操作、课堂讨论等形式相结合,培养学生的综合分析与解决问题的能力。

通过课堂作业、实验报告以及期末考试等方式进行综合评估,考核学生对计算机组成原理的理解与应用能力。

cpu的多线程原理

cpu的多线程原理

CPU的多线程原理主要是通过时间片的轮转来实现的。

在单核CPU的时代,CPU在同一时间只能处理一条线程,但是CPU会在多个线程之间进行快速切换,切换的速度非常快,人的肉眼是看不到的,这就造成了多条线程并行的假象。

这种切换方式被称为时间片的轮转,它是多线程的基础。

随着技术的发展,现在的CPU已经可以实现多核,每个核都有自己的线程,可以同时执行多个线程,进一步提高程序的运行效率。

但是,多线程并不意味着无限制地开线程,如果线程数量过多,会导致CPU在各个线程之间频

繁切换,占用大量CPU资源,反而会降低程序的运行效率。

因此,合理地

使用多线程,才能发挥其最大的优势。

计算机体系结构实验-多周期MIPS处理器

13

多周期 控制

CLK

PCWrite

Branch

IorD Control PCSrc

MemWrite Unit ALUControl2:0

IRWrite

ALUSrcB1:0

31:26 Op 5:0 Funct

ALUSrcA RegWrite

MemtoReg

RegDst

CLK

PC'

PC

EN

CLK

WE

Memory WD

CLK Instr 25:21

EN

CLK

CLK

WE3

A1

RD1

A

A2

RD2

A3 Register File

WD3

SignImm

15:0

Sign Extend

SignImm是Instr的组合功能,在当前指令处 理过程中不会改变,因此不需要寄存。

6

多周期 数据路径-4

lw rt, imm(rs)

1

00

4 01 SrcB 10

11

ALU

CLK

ALUResult

ALUOut

SignImm

15:0

Sign Extend

11

多周期 数据路径-9

R-Type

• Read from rs and rt • Write ALUResult to register file • Write to rd (instead of rt)

Instr 25:21

20:16

EN

CLK

20:16 0 15:11 1

Data

CLK

CLK

WE3

A1

RD1

计算机组成原理-第11章 MIPS处理器设计(单周期、多周期)1 [兼容模式]

![计算机组成原理-第11章 MIPS处理器设计(单周期、多周期)1 [兼容模式]](https://img.taocdn.com/s3/m/72c9d32567ec102de2bd89a3.png)

llxx@

12

A conceptual view – computational instructions

• Both source

operands and

Read data 2

Register File

Datapath Control Points

RegWrite (“write enable” control point)

寄存器号 Instruction

R-type指令的执行

Read

register 1

Read

Read

data 1

register 2

– beq为相对寻址:以npc为基准,指令中的 target为16位,进行32位有符号扩展后左移两 位(补“00”,字对准)。

– jump为pseudodirect:指令中的target为26位, 而PC为32位。将target左移2位拼装在PC的低 28位上,PC高4位保持不变。

J-type

op(6 bits) rs(5 bits) rt(5 bits) op(6 bits)

data

16 Sign 32 extend

I-type

MemRead

R-type

llxx@

22

Instruction

条件转移beq

PC + 4 from instruction datapath

Add Sum

Branch target

Read

register 1

Read

Read

rt:ld的目的,sw的源

处理器调度算法c语言

处理器调度算法c语言一、概述处理器调度算法是操作系统中一个非常重要的问题。

在多任务操作系统中,有多个进程同时运行,而处理器只有一个,因此需要对进程进行调度,使得每个进程都能够得到适当的执行时间。

二、常见的处理器调度算法1. 先来先服务(FCFS)FCFS算法是最简单的调度算法之一。

它按照进程到达时间的先后顺序进行调度,即先到达的进程先执行。

这种算法容易实现,但可能会导致长作业等待时间过长。

2. 最短作业优先(SJF)SJF算法是根据每个进程所需的CPU时间来进行排序,并按照顺序进行调度。

这种算法可以减少平均等待时间和平均周转时间,并且可以最大限度地利用CPU资源。

3. 优先级调度优先级调度是根据每个进程的优先级来进行排序,并按照顺序进行调度。

这种算法可以确保高优先级进程得到更多的CPU时间,但可能会出现低优先级进程饥饿问题。

4. 时间片轮转(RR)RR算法将CPU分配给每个任务一定量的时间片,在该时间片内运行任务。

如果任务在该时间片内未完成,则将其放回队列尾部,并分配给下一个任务时间片。

这种算法可以确保公平性,并且可以避免长作业等待时间过长。

三、C语言中的处理器调度算法实现1. FCFS算法实现#include <stdio.h>int main(){int n, i, j;float avg_waiting_time = 0, avg_turnaround_time = 0;printf("Enter the number of processes: ");scanf("%d", &n);int burst_time[n], waiting_time[n], turnaround_time[n];printf("Enter the burst time for each process:\n");for(i=0; i<n; i++)scanf("%d", &burst_time[i]);waiting_time[0] = 0;turnaround_time[0] = burst_time[0];for(i=1; i<n; i++){waiting_time[i] = waiting_time[i-1] + burst_time[i-1];turnaround_time[i] = waiting_time[i] + burst_time[i];avg_waiting_time += waiting_time[i];avg_turnaround_time += turnaround_time[i];}avg_waiting_time /= n;avg_turnaround_time /= n;printf("\nProcess\tBurst Time\tWaiting Time\tTurnaround Time\n");for(i=0; i<n; i++)printf("P%d\t%d\t\t%d\t\t%d\n", i+1, burst_time[i], waiting_time[i], turnaround_time[i]);printf("\nAverage Waiting Time: %.2f\n", avg_waiting_ time);printf("Average Turnaround Time: %.2f\n", avg_turnaround_ time);return 0;}2. SJF算法实现#include <stdio.h>int main(){int n, i, j, temp;float avg_waiting_time = 0, avg_turnaround_time = 0; printf("Enter the number of processes: ");scanf("%d", &n);int burst_time[n], waiting_time[n], turnaround_time[n]; printf("Enter the burst time for each process:\n");for(i=0; i<n; i++)scanf("%d", &burst_time[i]);for(i=0; i<n-1; i++)for(j=i+1; j<n; j++)if(burst_time[i] > burst_time[j]){temp = burst_time[i];burst_time[i] = burst_time[j]; burst_time[j] = temp;}waiting_time[0] = 0;turnaround_time[0] = burst_time[0];for(i=1; i<n; i++){waiting_time[i] = waiting_time[i-1] + burst_time[i-1];turnaround_time[i] = waiting_time[i] + burst_time[i];avg_waiting_time += waiting_time[i];avg_turnaround_time += turnaround_time[i];}avg_waiting_time /= n;avg_turnaround_time /= n;printf("\nProcess\tBurst Time\tWaiting Time\tTurnaround Time\n");for(i=0; i<n; i++)printf("P%d\t%d\t\t%d\t\t%d\n", i+1, burst_time[i], waiting_time[i], turnaround_time[i]);printf("\nAverage Waiting Time: %.2f\n", avg_waiting_ time);printf("Average Turnaround Time: %.2f\n", avg_turnaround_ time);return 0;}3. 优先级调度算法实现#include <stdio.h>int main(){int n, i, j, temp;float avg_waiting_time = 0, avg_turnaround_time = 0;printf("Enter the number of processes: ");scanf("%d", &n);int burst_time[n], waiting_time[n], turnaround_time[n], priority[n];printf("Enter the burst time and priority for each process:\n"); for(i=0; i<n; i++)scanf("%d %d", &burst_time[i], &priority[i]);for(i=0; i<n-1; i++)for(j=i+1; j<n; j++)if(priority[i] > priority[j]){temp = priority[i];priority[i] = priority[j];priority[j] = temp;temp = burst_time[i];burst_time[i] = burst_time[j]; burst_time[j] = temp;}waiting_time[0] = 0;turnaround_time[0] = burst_time[0];for(i=1; i<n; i++){waiting_time[i] = waiting_time[i-1] + burst_time[i-1];turnaround_time[i] = waiting_time[i] + burst_time[i];avg_waiting_ time += waiting_ time[i];avg_turnaround_ time += turnaround_ time[i];}avg_waiting_ time /= n;avg_turnaround_ time /= n;printf("\nProcess\tBurst Time\tPriority\tWaiting Time\tTurnaround Time\n");for(i=0; i<n; i++)printf("P%d\t%d\t\t%d\t\t%d\t\t%d\n", i+1, burst_ time[i], priority[i], waiting_time[i], turnaround_time[i]);printf("\nAverage Waiting Time: %.2f\n", avg_waiting_ time);printf("Average Turnaround Time: %.2f\n", avg_turnaround _ time);return 0;}4. RR算法实现#include <stdio.h>int main(){int n, i, j, time_quantum;float avg_waiting_time = 0, avg_turnaround_time = 0;printf("Enter the number of processes: ");scanf("%d", &n);int burst_time[n], remaining_time[n], waiting_time[n], turnaround_time[n];printf("Enter the burst time for each process:\n");for(i=0; i<n; i++)scanf("%d", &burst_time[i]);printf("Enter the time quantum: ");scanf("%d", &time_quantum);for(i=0; i<n; i++)remaining_time[i] = burst_time[i];int t=0;while(1){int done = 1;for(i=0; i<n; i++){if(remaining_time[i] > 0){done = 0;if(remaining_ time[i] > time_ quantum){t += time_ quantum;remaining_ time[i] -= time_ quantum;}else{t += remaining _ time[i];waiting_time[i] = t - burst_time[i];remaining_ time[i] = 0;turnaround_ time[i] = waiting_time[i] + burst_time[i];avg_waiting_ time += waiting_ time[i];avg_turnaround _ time += turnaround_ time[i];}}}if(done == 1)break;}avg_waiting_ time /= n;avg_turnaround_ time /= n;printf("\nProcess\tBurst Time\tWaiting Time\tTurnaround Time\n");for(i=0; i<n; i++)printf("P%d\t%d\t\t%d\t\t%d\n", i+1, burst_time[i], waiting_time[i], turnaround_time[i]);printf("\nAverage Waiting Time: %.2f\n", avg_waiting_ time);printf("Average Turnaround Time: %.2f\n", avg_turnaround _ time);return 0;}四、总结以上是常见的处理器调度算法的C语言实现方式。

大话计算机 计算机系统底层架构原理极限剖析

大话计算机计算机系统底层架构原理极限剖析计算机是一种基础性的工具,它的发展已经深刻影响了人类社会的方方面面。

为了更好地理解计算机,我们需要从计算机系统的底层架构原理入手,深入剖析其设计与实现,揭示其中的奥秘。

计算机系统的底层架构主要包括硬件、操作系统和应用软件。

其中,硬件是计算机系统的基础,包括中央处理器(CPU)、内存、存储设备、输入输出设备等。

操作系统是指控制计算机硬件和软件资源的程序,它为应用软件提供了统一的接口。

应用软件则是运行在计算机系统上的各种程序和应用,如文本编辑器、游戏、浏览器等。

计算机的核心是中央处理器,它负责执行计算机指令和控制计算机的操作。

CPU的设计涉及到电路设计、指令集和微架构等方面。

其中,指令集是CPU的操作码集合,是CPU与应用软件之间的桥梁,它直接影响到CPU的性能和使用效率。

CPU是所有计算机硬件组件中最复杂和精密的部件之一,包含了大量的逻辑门、存储单元和控制单元等。

从微架构的角度来看,CPU可以分为:单周期处理器、多周期处理器和流水线式处理器。

单周期处理器包含一个时钟周期内执行一条指令的逻辑,它简单易懂,但效率较低。

而多周期处理器和流水线式处理器采用分阶段的操作方式,可以在一个时钟周期内执行多条指令,性能更高。

内存是计算机数据存储的主要容器,也是计算机系统速度的瓶颈之一。

内存的设计要考虑到存储器结构、容量和速度等因素。

现代计算机已经采用了高速缓存存储器(Cache)和虚拟内存技术,以提高内存的访问速度和容量。

存储设备是计算机系统的另一个重要组成部分,包括硬盘、固态硬盘和光盘等。

存储设备的设计要考虑到容量、速度、可靠性和价格等方面,不同类型的存储设备适用于不同的应用场景。

输入输出设备是计算机系统与外部世界交互的接口,包括鼠标、键盘、显示器和打印机等。

输入输出设备的设计要考虑到易用性、响应速度和精度等因素。

操作系统是计算机系统的核心软件之一,它负责管理计算机各种资源,提供各种服务和接口,是应用软件运行的基础。

基于龙芯开源CPU的计算机组成原理实验课程改革

摘 要:以基于龙芯开源 CPU 的计算机组成原理实验平台为载体,结合该实验平台在高校的试点使用 成果,详细探讨新一代实验平台在教学中的利弊以及可改进的方向,并对存在的问题提出建议和思考。 关键词:计算机组成原理;龙芯开源 CPU;教学实验

0 引 言

计算机组成原理是一门偏硬件的计算机基础 核心课程,பைடு நூலகம்课程对学生了解计算机各组成部件 及其内部运行机制具有重要意义。目前,国内高 校普遍采用的教材介绍了计算机指令集、CPU 设 计、存储器层次结构、I/O 系统、总线系统等计 算机核心组成部件 。 [1-2] 该课程涉及计算机的多 个部件,概念较为抽象,因此其实验环节尤为重 要。只有通过动手充分了解计算机各部件的内部 运行机制,才能加深学生对计算机组成知识的理 解,提升学生的实践动手能力,并为其今后的学 习和深造打好坚实的基础。

实验用到的龙芯实验箱型号为 LS-CPU-EXB002,主要由以下部件组成:Spartan6-XC6SLX150FGG676 FPGA 芯片、双色 LED 灯、单色 LED 灯、 LED 点阵、数码管、下载 JTAG 接口、UART 接 口、VGA 接口、LAN 接口、USB 接口、PS2 接口、 电源开关、拨码开关、脉冲开关、4×4 键盘、复 位键、LCD 显示屏。实验箱 LS-CPU-EXB-002 见 图 1。

硬件实验平台对于计算机组成原理课程的教 学效果具有重要意义,因此,如何选定合适的实 验平台是计算机组成原理课程教学改革的重点和 难点问题。为此,笔者基于龙芯开源 CPU 的教 学实验平台 [7],就计算机组成原理课程开展了一 系列教学改革尝试,并取得了较好的效果。

基金项目:国家自然科学基金项目(61602264);国家博士后自然科学基金项目(2017M611882);南京邮电大学 引进人才科研启动基金资助项目(NY215044)。 第一作者简介:王俊昌,男,讲师,研究方向为计算机系统结构,wangjc@。

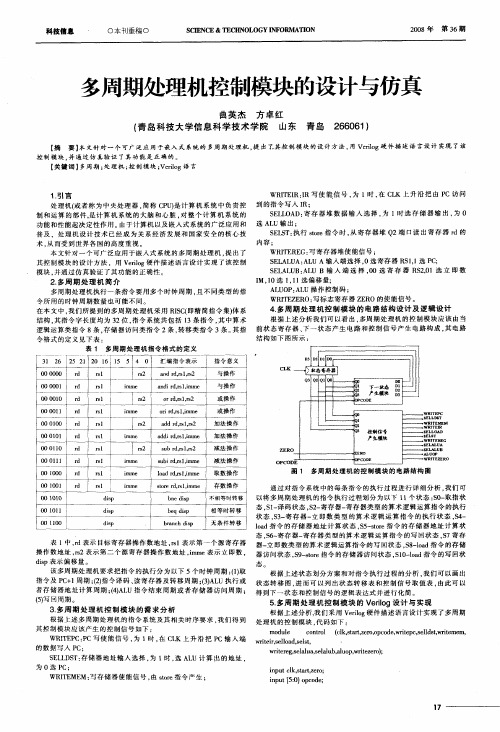

多周期处理机控制模块的设计与仿真

2 多周 期 处 理 机简 介 .

多 周 期 处理 机 执 行 一 条 指 令要 用 多 个 时 钟 周 期 , 不 同类 型 的 指 且 令所 用 的时 钟 周 期数 量 也 可 能 不 同 。

I ,0选 11 M 1 ,1选 偏 移量 ; AL O AL U P: U操 作 控 制 码 ;

控 制 模 块 , 通过 仿 真验 证 了其 功 能是 正 确 的 。 并

【 键 词 】 周期 ; 理 机 ; 制模 块 ; ro 关 多 处 控 Vei g语 言 l

1 引 言 .

WRT I 1 写 使 能 信 号 , l时 , C K 上 升 沿 把 由 P 访 问 IE R: R 为 在 L C

令格 式 的定 义 见下 表 : 表 1 多周 期 处 理 机 指 令 格式 的定 义

3 2 2 2 2 l l 5 4 0 1 6 5 l 0 6 5 汇 编指 令 表 示 指 令 意 义

结 构 如下 图所 示 :

0 0 0 0o 0 o 0 1 oO 0 0 0 0 00 1

U输 出 : 功能 和 性 能起 决定 性 作 用 。 于计 算 机 以及 嵌 入 式 系统 的广 泛 应 用 和 选 AL 由 S L T: 行 s r 令 时 , 寄 存 器 堆 Q ES 执 t e指 o 从 2端 口读 出 寄 存 器 r d的 普 及 ,处 理 机 设 计 技 术 已经 成 为 关 系 经 济 发 展 和 国家 安 全 的核 心技 内容; 术 , 而 受 到 世 界各 国的 高 度 重 视 。 从 WR T R G: 寄存 器 堆 使 能信 号 ; IE E 写 本 文 针对 一 个 可 广 泛 应 用 于嵌 入 式 系 统 的 多周 期 处 理 机 , 出 了 提 S L U AL E AL A: U A输 入 端选 择 , 寄 存 器 R 11 P ; 0选 S , 选 C 其控 制 模 块 的 设 计 方 法 ,用 V ro 件 描 述 语 言 设 计 实 现 了 该 控 制 ei g硬 l S L U A U B 输 入 端 选 择 ,o选 寄 存 器 R 2 1选 立 即 数 E AL B: L o S, 0 模 块 。 通 过 仿 真验 证 了其 功 能 的正 确 性 。 并

为什么现在使用多周期CPU,而单周期CPU被弃用?

为什么现在使⽤多周期CPU,⽽单周期CPU被弃⽤? 最初设计的CPU结构简单,内部不复杂。

之所以制造它是为了让机器⾃动跑程序,算数。

早期CPU都是单周期的,⼈们没考虑那么多,性能啥的。

就让CPU每个时钟周期跑⼀个指令,这些时钟周期等长。

这样下来,有的指令跑完耗时长,有的指令跑完耗时短,⽽CPU 是⾛完⼀条指令再处理下⼀条的,给每个指令的时钟周期都是相同的,那么⽊桶原理,时钟周期肯定就是耗时最长的指令所需的时间。

后来⼈们意识到了计算机的巨⼤威⼒,便开始专⼼制造更强的电⼦计算机。

这时,为了提升CPU的速度,优化CPU的结构,有⼈设计了⼀套多周期CPU结构。

对指令集的所有指令作分析,可以发现它们处理过程有相同的地⽅,那这下好了,我把所有的指令切成⼏段基本操作(换句话说,所有的指令都可以看成是⼏个基本操作的序列组成),例如:指令1可以看成{opA——>opC——>opV},指令2可以看成{opA ——>opK——>opV——>opT}。

然后让时钟周期适配op,⽽不是单条指令。

每个指令需要多个周期(周期值较⼩)。

这⾥的多周期CPU依然是逐条执⾏每个指令。

下图为⼀个多周期CPU的控制器状态⾃动机。

举例对⽐上⾯所述单周期CPU和多周期CPU的耗时: CPU的指令集Ins中有多条指令,指令4耗时最长,执⾏⼀次它需要800ps。

单周期CPU的时钟周期最少设为800ps。

此时假如我们要执⾏指令1,2,3,4,5,6,那么总共耗时6x800ps=4800ps。

多周期CPU,分别可以把指令123456分解为3个op,2个op,4个op,8个op,3个op,5个op。

每个op延时为100ps。

那么假如我们要执⾏指令1,2,3,4,5,6,则总共耗时为(3+2+4+8+3+5)x100ps=2500ps。

这样⼀对⽐多周期CPU相较于单周期CPU的优势是不是很明显啦。

在这之后,有⼈发现了上⾯所说的多周期CPU还可以改进优化提速,他把流⽔线的思想拿到了CPU设计上,允许指令并⾏执⾏,这样⼀来速度⼜得到了提升。

【基础知识】CPU指令周期

【基础知识】CPU指令周期完整执⾏⼀条指令所需要的时间基本概念指令周期,读取-执⾏周期(fetch-and-execute cycle)是指要执⾏指令经过的步骤。

计算机之所以能⾃动地⼯作,是因为CPU能从存放程序的内存⾥取出⼀条指令并执⾏这条指令;紧接着⼜是取指令,执⾏指令,如此周⽽复始,构成了⼀个封闭的循环。

除⾮遇到停机指令,否则这个循环将⼀直继续下去。

cpu执⾏完每条指令后,都会检测是否有中断信息。

指令周期 :CPU从内存取出⼀条指令并执⾏这条指令的时间总和。

CPU周期 :⼜称机器周期,CPU访问⼀次内存所花的时间较长,因此⽤从内存读取⼀条指令字的最短时间来定义。

时钟周期: 通常称为节拍脉冲或T周期。

⼀个CPU周期包含若⼲个。

[1]在取指令的阶段,指令是放在存储器(也就是内存)⾥的,实际上,通过PC寄存器和指令寄存器取出指令的过程,是由控制器(Control Unit)操作的。

指令的解码过程,也是由控制器进⾏的。

⼀旦到了执⾏指令阶段,⽆论是进⾏算术操作、逻辑操作的 R 型指令,还是进⾏数据传输、条件分⽀的 I 型指令,都是由算术逻辑单元(ALU)操作的,也就是由运算器处理的。

不过,如果是⼀个简单的⽆条件地址跳转,那么可以直接在控制器⾥⾯完成,不需要⽤到运算器。

冯诺伊曼的指令周期模型IF(Instruction fetch) 取指:从 Instruction-Memory 中读取指令,并在下⼀个时钟上升沿到来时把指令送到 ID 级的指令缓冲器 id_ir 中。

该级控制信号决定下⼀个指令指针的 pc 信号(即 Instruction-Memory 的指令地址 i_addr)ID(Instruction decode)指令译码:对 IF 级的指令进⾏译码,根据指令操作码获取操作数read reg_1、read reg_2 或者要直接储存的数据内容 smdr,并在下⼀个时钟上升沿到来前把指令 id_ir(前 8 位,操作码+operand1)送到 EX 级的指令缓冲器 ex_ir 中EX(Execute)执⾏:该级进⾏算术运算(加、减)、简单传输(JUMP 操作)、逻辑运算(与、或、异或) 或移位操作(逻辑左移、逻辑右移、算术左移、算术右移)。

多任务系统 原理

多任务系统原理多任务系统是一种操作系统的核心功能,它允许在同一时间内运行多个任务。

多任务系统的原理是通过时间片轮转和任务调度来实现的。

在传统的单任务系统中,一次只能运行一个任务,当一个任务执行完成后,才能执行下一个任务。

这种方式效率低下,无法满足用户的需求。

而多任务系统则可以同时运行多个任务,从而提高系统的效率和响应速度。

多任务系统的原理是基于时间片轮转的。

时间片是操作系统分配给每个任务的最小时间单位。

系统将CPU的执行时间划分为若干个时间片,每个任务在一个时间片内执行一定的指令。

当一个时间片执行完后,系统会切换到下一个任务,继续执行下一个时间片。

这样循环往复,就实现了多个任务的并行执行。

除了时间片轮转,多任务系统还需要进行任务调度。

任务调度是指根据一定的策略,决定将哪些任务放入执行队列,以及选择哪个任务来执行的过程。

任务调度的目的是充分利用系统资源,提高系统的吞吐量和响应速度。

任务调度可以根据任务的优先级来进行。

每个任务都会有一个优先级,优先级高的任务会被优先调度执行。

这样可以保证重要任务的及时执行。

另外,任务调度还可以根据任务的状态来进行。

比如,当一个任务等待某个事件的发生时,可以将它挂起,让其他任务先执行。

当事件发生后,再将该任务唤醒继续执行。

多任务系统的原理使得操作系统能够同时处理多个任务,从而提高了系统的并发能力和响应速度。

它可以让用户同时进行多个操作,比如打开多个应用程序、同时进行下载和浏览网页等。

多任务系统还可以提供对任务的管理和控制,比如可以暂停、恢复或取消某个任务的执行。

当然,多任务系统也存在一些问题。

由于CPU每个时间片只能执行一部分指令,因此对于一些需要实时响应的任务,可能会出现延迟。

另外,多个任务之间的资源竞争也可能导致系统的性能下降。

因此,需要合理安排任务的优先级和资源的分配,以充分发挥多任务系统的优势。

多任务系统是现代操作系统的重要功能之一。

它通过时间片轮转和任务调度实现多个任务的并行执行,提高了系统的效率和响应速度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

话题八处理器多周期实现

主要内容:

1. 基本概念

2. 数据通路

3. 指令执行过程

4. 控制单元设计

重点内容: 指令执行过程, 控制单元设计

一. 基本概念

1. 指令周期, 机器周期, 节拍周期

指令周期: 一条指令从取指到执行完毕准备取下一条指令所花费的时间

机器周期: 指令分阶段执行时, 每一阶段(每一步)所花费的时间

节拍周期: 节拍周期由若干个时钟周期构成

时钟周期: 计算机系统中往往有一个时钟源, 它负责为整个系统提供统一的时钟信号. 但是由于不同部件工作速度的差异, 这个时钟源提供的时钟信号往往需要经过处理(倍频, 分频等)后才能送给不同部件使用. CPU使用的节拍信号(也叫工作脉冲)往往是由时钟信号经过倍频得到的.

指令周期由若干个机器周期构成, 而且由于功能的差别, 不同的指令需要的机

器周期数也有差异.

机器周期由若干个节拍周期构成, 而且由于每一步所做的操作的差别, 不同的机器周期需要的节拍周期数也有差异.

节拍周期由固定数量的时钟周期构成. 为了简化问题, 机器周期也往往由固定数量的节拍周期构成, 通常由每一步操作所需要的时间中的最大者(往往和存储访问有关)来确定.

2. 多周期实现

指令的执行过程分成若干个阶段, 每一阶段执行一步操作, 即指令分步执行.

多周期实现就是指令周期由多个机器

周期构成, 每个机器周期执行一步操作.

多周期硬布线控制器的基本结构如下:

二. 数据通路

1. 高层视图

分步执行, 每一步只含一个主要功能单元, 工作量尽量均衡. 每个主要的功能单

元后增加相应的寄存器用来保存此功能单元的处理结果, 供下一级功能单元使用.

增加时钟控制

每一步引入时钟控制, 在时钟信号的后期将下一级功能单元要使用的数据存入局部寄存器(对程序员不可见), 而后续指令要使用的数据则存入全局寄存器(对程序员可见).

此处局部寄存器包括:

IR –指令寄存器

MDR –存储器数据寄存器

A和B –寄存器文件读数据寄存器

ALUout – ALU输出寄存器

所有局部寄存器(除IR外) 只在相邻的两个时钟之间保存数据, 因此它们无需写

控制信号.

2. 完整的带控制单元的多周期数据通路

说明: 本图由PPT课件第4章第1部分及顶层视图综合而来, 而且: 指令存储器和数据存储器合二为一, 不再分开设置; 减少了ALU, 不再重复设置; 为满足多周期实现的需要, 调整并增加了几个控制信号!

回顾单周期结构图

三. 指令执行过程

指令执行的全过程可以分为5个阶段, 即5步操作.

第一步: 取指令, 所有指令都有, 而且

做同样的操作.

第二步: 指令译码并读寄存器, 所有指令都有, 而且

第三步: 执行指令,

第四步: 继续执行,

第五步: 继续执行, 只有取数指令lw 才有.

1. 取指令:

数据通路的活动:

需要的控制信号:

2. 指令译码并读寄存器

数据通路活动:

需要的控制信号:

3. 执行(所有指令, 不同指令有所差别)

内存访问指令的数据通路活动:

R型指令的数据通路活动:

Beq指令的数据通路活动:

J指令的数据通路活动:

需要的控制信号:

4. 继续执行

取数lw指令的数据通路:

存数sw指令的数据通路:

R型指令的数据通路:

此时需要的控制信号:

5. 继续执行

取数指令lw的数据通路活动:

此时需要的控制信号:

四. 控制单元的设计

采用多周期实现时, ALU控制单元的实现跟单周期实现一样, 主控制单元的实现需要做相应的调整: 主要是引入时钟信号, 根据时钟信号, 分步产生各步操作需要的控制信号.

1. 回顾ALU控制单元的设计

主控制单元根据指令opcode字段产生ALU操作位ALUOp bits

ALU控制单元根据ALUOp bits及指令的funct字段产生ALU 操作控制信号.

2. 主控制单元的设计

多周期实现时, 主控制单元产生控制信号的根据包括指令操作码和当前操作阶段. 换言之, 指令不同, 操作阶段不同, 需要的控制信号也有所不同.

因此可以用一个有限状态机来实现主控制单元.

有限状态机:

有限状态机在时钟信号的作用下根据指令的不同及操作阶段的不同在不同状态间转换.

主控制单元基本结构:

主控制单元的有限状态机实现:

主控制单元产生的控制信号真值表:

主控制单元的次态真值表:。