FPGA可编程逻辑器件芯片EP2AGX95EF35I3N中文规格书

FPGA可编程逻辑器件芯片EP2AGZ350FF35C4N中文规格书

Either of these interrupts can be enabled or disabled. However, the PIXC only has one interrupt line output, so it raises an interrupt (under the appropriate condition) when either of these two interrupts is triggered. If both interrupts are enabled, the interrupt status register of the PIXC indicates which of the two conditions caused the interrupt to occur. Once the PIXC generates an interrupt, it stalls the pixel processing until a software ISR clears the interrupt. However, the FIFOs do not stall and keep filling up even when the PIXC is in a stalled state. Both interrupts can be cleared by writing a 1 to the respective inter-rupt status bits.After each interrupt (whether it is a last-valid-overlay interrupt or an end-of-frame interrupt), the PIXC restarts processing with coordinate register set A. In other words, at the time of clearing the interrupt: •If coordinate set A is enabled (PIXC_CTL.OVENA = 1), the PIXC assumes that the first incoming data over the bus is to be overlaid on the area specified in coordinate set A.•If coordinate set A is disabled (PIXC_CTL.OVENA = 0), and coordinate set B is enabled (PIXC_CTL.OVENB = 1), the PIXC assumes that the first incoming data over the data bus is to be overlaid on the area specified in coordinate set B.•If both coordinate sets are disabled, the PIXC flushes the overlay FIFO and make no more data requests on the overlay DMA channel.NOTE:The overlay enable bits PIXC_CTL.OVENA and PIXC_CTL.OVENB should only be changed inside the interrupt service routines of the PIXC interrupts, or when the overlay block is disabled.Note that the module enable bit (PIXC_CTL.EN) is the root enable for the PIXC. Both the PIXC_CTL.OVENA and PIXC_CTL.OVENB bits are gated with PIXC_CTL.EN bit, so if PIXC_CTL.EN = 0, the individual overlay enable bits have no effect, and the module remains disabled. When PIXC_CTL.EN = 1, both the image and overlay FIFOs are flushed and no more DMA requests are made on either of the DMA channels.Once the DMAs are enabled, the PIXC keeps track of the current pixel being displayed from the main image data by reading from the PIXC_PPL and PIXC_LPF programmable registers.When the pixel count reaches the top left corner (H-Start, V-Start) of overlay data, the PIXC starts the overlay. When the pixel count reaches the top right corner (H-End, V-Start) of overlay data, the PIXC stops the overlay. It starts again at the next line at (H-Start, V-Start + 1) and stop at (H-End, V-Start + 1), and so on until the entire overlay frame is processed.NOTE:Internally, the start of the overlay DMA is preempted by the PIXC before the actual processing of the first overlay pixel, and DMA data is requested until the overlay FIFO is full. Similarly, theoverlay DMA does not stop at the end of a line. The overlay FIFO continues to be filled with DMA data, even when the current pixel is not an overlay pixel, but the supply of overlay pixels from the overlay FIFO is simply halted.The PIXC decides whether or not to perform overlay mixing for the current pixel by using the various PIXC register values as follows.•The PIXC_PPL and PIXC_LPF registers must be programmed correctly (and cannot be 0).•The PIXC_HSTART_A and PIXC_HEND_A must be less than or equal to PIXC_PPL.Color Space ConversionDepending on the input data format and display device used, there may be a color space conversionperformed on the data stream of the PIXC. If the input data is in YUV format, a YUV-to-RGB conversion can be performed for output to an LCD panel. If the input data is in RGB format, a RGB-to-YUV conver-sion can be performed for output to NTSC/PAL displays. The color space conversion may happen on any of the three paths (for example, the main image data path, the overlay image data path, or the combined data path). Registers are used to specify the input, overlay and output formats. The color space converter block controls a number of cases of operation.•Both the image and the overlay data are in the same format.•The image and the overlay data are in different formats.•Color space conversion onlyEach case is described below, along with several special usage cases. Note that various scenarios may be shown in the same figure based on the output device chosen, though only a single output destination is supported at one time.Case 1 - Image and Overlay in the Same FormatBoth input data streams (main image and overlay) are in the same format, either YUV 4:2:2 or RGB888, so a color space conversion may be performed after alpha blending, depending on the output type.Figure 32-7:Image and Overlay in the Same FormatCase 2 - Image and Overlay in Different FormatsP IXEL C OMPOSITOR (PIXC)PIXC F UNCTIONAL D ESCRIPTIONNTSC/PALThe two most common video standards used. NTSC is the video system or standard used in NorthAmerica and most of South America. In NTSC, 30 frames are transmitted each second. Each frame is made up of 525 individual scan lines. PAL is the predominant video system or standard mostly used overseas. In PAL, 25 frames are transmitted each second. Each frame is made up of 625 individual scan lines.RGB888 formatRGB is a color space where pixels are defined by three color values; one red (R), one green (G) and one blue (B). The suffix signifies the bit widths for these color components. In this case, RGB888 means that each red, green and blue value is 8-bits each.YUV 4:2:2 interleaved formatYUV is a color space where pixels are defined by a luminance (Y) component and chrominance (UV) components. The suffix signifies how the chrominance components have been decimated as well asformatting. In this case, the YUV422 format has the chrominance decimated by two, meaning only half of each chrominance component are available. Typical YUV422 formatting interleaves the luminance and chrominance such as U1Y1V1Y2U2Y3V2Y4.Data OverlayProcess of blending or replacing a pixel from an image with another pixel.PIXC Block DiagramA top-level micro architecture diagram of the PIXC appears in the following figure. As shown in the figure,the PIXC uses three DMA channels: one for the image data, one for the overlay data and one for storing the results back to memory. Frame C (output frame) can also be fed back to the PIXC for multiple stages of processing, taking the place of frame A (main input image) when this happens. The main input image and output frame can alternatively be piped from or to another peripheral via the video subsystem, respec-tively.。

FPGA可编程逻辑器件芯片EP4SGX290HF35I3N中文规格书

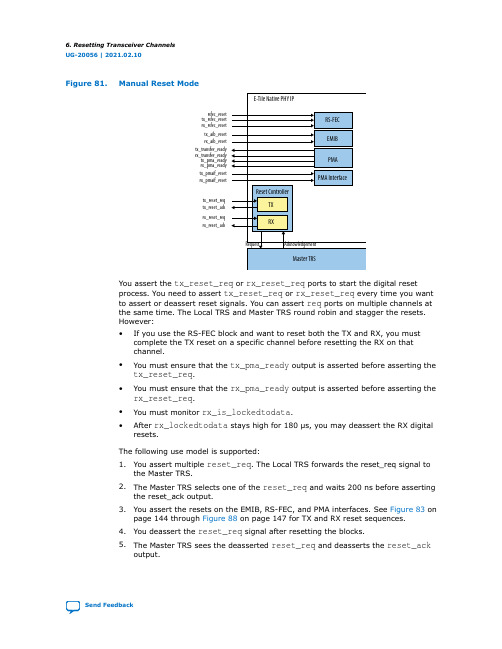

Figure 81.Manual Reset Modetx_reset_reqtx_reset_ackrx_reset_reqrx_reset_ackrsfec_reset tx_rsfec_reset rx_rsfec_resettx_aib_reset rx_aib_resettx_transfer_ready rx_transfer_ready tx_pma_ready rx_pma_readytx_pmaif_resetrx_pmaif_reset You assert the tx_reset_req orrx_reset_req ports to start the digital reset process. You need to assert tx_reset_req or rx_reset_req every time you want to assert or deassert reset signals. You can assert req ports on multiple channels at the same time. The Local TRS and Master TRS round robin and stagger the resets.However:•If you use the RS-FEC block and want to reset both the TX and RX, you must complete the TX reset on a specific channel before resetting the RX on that channel.•You must ensure that the tx_pma_ready output is asserted before asserting the tx_reset_req .•You must ensure that the rx_pma_ready output is asserted before asserting the rx_reset_req .•You must monitor rx_is_lockedtodata .•After rx_lockedtodata stays high for 180 µs, you may deassert the RX digital resets.The following use model is supported:1.You assert multiple reset_req . The Local TRS forwards the reset_req signal to the Master TRS.2.The Master TRS selects one of the reset_req and waits 200 ns before asserting the reset_ack output.3.You assert the resets on the EMIB, RS-FEC, and PMA interfaces. See Figure 83 on page 144 through Figure 88 on page 147 for TX and RX reset sequences.4.You deassert the reset_req signal after resetting the blocks.5.The Master TRS sees the deasserted reset_req and deasserts the reset_ack output.6.Resetting Transceiver ChannelsUG-20056 | 2021.02.10Send FeedbackNote: The Master TRS automatically deasserts the reset_ack output after 400 µs if you have not deasserted the reset_req input. In that case, you must deassert and reassert the reset_req input to enter the round robin pool again.6.The Master TRS goes to the next request in a round robin fashion and waits 200ns before asserting the next reset_ack .The figure below shows how to use the tx_reset_req /rx_reset_req inputs to request a reset window and how tx_reset_ack /rx_reset_ack marks the Master TRS returning a valid reset window.Figure 82.Manual Mode Reset Timing Model During the timing window when the reset_ack output is high, reset the blocks in sequence. The numbers refer to the steps above.reset_req[0]reset_req[1]reset_req[2]reset_req[3]reset_ack[0]reset_ack[1]reset_ack[2]reset_ack[3]Figure 83 on page 144 and Figure 84 on page 145 below show how to assert TX and RX reset.Figure 83.RX Reset Assertion Timing Waveformrx_pma_readyrx_reset_req (1)rx_reset_ackrx_aib_resetrx_transfer_readyNote:1. If you enabled the RS-FEC block, you must assert rx_reset_req after the tx_transfer_ready output is asserted.2. See Master-Slave Clocking Option 2 Reset Details for information about whether or not to assert tx_aib_reset or rx_aib_reset ports.6.Resetting Transceiver Channels UG-20056 | 2021.02.10Send FeedbackFigure 84.TX Reset Assertion Timing Waveformtx_pma_readytx_reset_reqtx_reset_acktx_aib_resettx_transfer_ready1. See Master-Slave Clocking Option 2 Reset Details for information about whether or not to assert tx_aib_reset or rx_aib_reset ports.Figure 85 on page 145 and Figure 86 on page 146 below show how to deassert TX and RX reset.Figure 85.RX Reset Deassertion Timing Waveformrx_pma_readyrx_reset_ackrx_aib_resetrx_transfer_ready 1. If you enabled the RS-FEC block, you must assert rx_reset_req after the tx_transfer_ready output is asserted.2. See Master-Slave Clocking Option 2 Reset Details for information about whether or not to assert tx_aib_reset or rx_aib_reset ports.6.Resetting Transceiver ChannelsUG-20056 | 2021.02.10Send Feedback。

FPGA可编程逻辑器件芯片EP2AGX95EF29C5中文规格书

•Condition 2 - None of the error bits in the bit fields [23:16] of the PKTE_CTL_STAT register is set, the packet is processed normally (without errors). Update the host processor maintained version of the SA record and state record with the result read from the packet engine registers:•Sequence number•Sequence number mask•Result IV•Result digest count•Result digestPKTE Mode ConfigurationBefore using the packet engine, it must be configured. The mode of the packet engine must be defined and the PRNG (if used) must be initialized.Configure the packet engine in one of three command modes:•Autonomous Ring Mode: PKTE_CFG.MODE =b'11•Target Command Mode: PKTE_CFG.MODE =b'10•Direct Host Mode: PKTE_CFG.MODE =b'00PKTE Programming ConceptsThe following sections provide conceptual information for programming the PKTE.Packet Engine DescriptorIMPOR-TANT:Depending on the mode, ARM, TCM, or DHM, the descriptor is either:•in the memory of the host processor in the command descriptor ring, or•written directly to the descriptor registers in the packet engineReferences to descriptor registers are for either the register that is mirrored in the descriptor structure in memory or for the actual register itself.Command descriptors are host-supplied commands that control the real-time operation of the packet engine. The packet engine returns result descriptors at the end of an operation that provide the status information to the host. The Command Descriptor Structure and the Result Descriptor Structure tables show these descriptors.HOST MEMORY.FIXED SIZEFigure 15-3: Descriptor Rings in Autonomous Ring ModeDescription and Use of the SA Record and State Record StructureThe SA record is a packed structure that contains the remainder of the information needed by the packet engine to process a packet. Most of the information fields in the SA record, such as the key and encryption mode, are static for the lifetime of the association. The fields do not require frequent manipulation by the host processor. The SA record non-static fields are the sequence number and sequence number mask.The SA record can have a corresponding state record that is used to save results from the current operations that can be used for future operations. The state record can hold the IV, the hash byte count, and the intermediate hash digest.There is no practical limit to how many SA records and corresponding state records the packet engine can support.In the autonomous ring mode and target command mode, once the packet engine has validated a command descrip-tor, it automatically fetches the SA record and optional state record. After processing, the packet engine updates the stateful fields in the SA record and state record in the host processor memory.In direct host mode, after the descriptor is validated, the host must write the SA record directly into the internal registers of the packet engine. After processing, the host reads the stateful fields from the SA registers of the packet engine and saves them back to the SA record in the host processor memory.SA Record StructureThe SA Record Structure table shows the structure for an SA Record. When using direct host mode, the correspond-ing elements are accessed directly with the registers. When using autonomous ring mode or target command mode,the SA Record is defined, configured and accessed in host memory.PKTE Programming ConceptsNOTE:For SSL/TLS and SRTP, no header processing is performed in hardware.。

FPGA可编程逻辑器件芯片EP2AGX125EF35C3N中文规格书

D IRECT M EMORY A CCESS (DMA)DMA C HANNEL F UNCTIONAL D ESCRIPTIONTransmit Restart or FinishNo restart or finish control command may be issued by a peripheral to a channel configured for memory read unless all the following conditions are met.•The peripheral has already performed at least one DMA transfer in the current work unit.•The current work unit has (FIFO_SIZE/DMA_CFG.MSIZE) + 1 memory transfers remaining.The first item ensures that the work unit has started. The second item ensures that the work unit has not completed. The second item is sufficiently large that it is always at least five more than the maximum data count prior to any restart or finish command. This implies that any work unit which might be managed by restart or finish commands must have DMA_XCNT_CUR and DMA_YCNT_CUR register values representing at least five data items.The second item can be satisfied by ensuring that the number of memory transfers described by thedescriptor is (FIFO_SIZE/DMA_CFG.MSIZE) + 1 larger than the maximum number of memory transfers expected.Receive Restart or FinishNo restart or finish control command may be issued by a peripheral to a channel configured for memory write unless either of the following conditions is met.•The number of peripheral transfers completed is less than (DMA_CFG.MSIZE/DMA_CFG.PSIZE) × (trans-fers described by descriptor)In addition to either of the above two conditions, one of the following two conditions must also be met.•The previous work unit was terminated by a finish command AND the peripheral has done at least one transfer in the current work unit.•The peripheral has done (FIFO_SIZE/DMA_CFG.PSIZE) + 1 transfers in the current work unit.The first set of conditions ensures that the descriptor is still active while the second set ensures that data from the previous descriptor has left the FIFO and that the current descriptor has started.Finish OnlyThe peripheral has completed exactly (DMA_CFG.MSIZE/DMA_CFG.PSIZE) × (transfers described bydescriptor) and gives the restart/finish command immediately in the next cycle following the last data transfer.Memory DMA and TriggeringA memory DMA (MDMA) channel provides a means of doing memory-to-memory DMA transfersamong the various memory spaces that have DMA support.Memory DMA (MDMA) channels are implemented by interfacing two DMA channels via the peripheral DMA bus interface. One DMA channel is used for memory read operations and the second is used forADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCED IRECT M EMORY A CCESS (DMA)DMA C HANNEL F UNCTIONAL D ESCRIPTIONADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCEMinimum Enable RequirementsTo start a DMA operation on a given channel, some or all of the DMA parameter registers must first be initialized and configured to the DMA channels desired operating mode.•For descriptor array based flow modes – At a minimum the DMA_DSCPTR_CUR register must be writtenprior to writing to the DMA_CFG register, which is the special action required to start the DMA channel.•For descriptor list based flow modes – At a minimum the DMA_DSCPTR_NXT register must be writtenprior to writing to the DMA_CFG register, which is the special action required to start the DMA channel.•For non descriptor based flow modes – The DMA_ADDRSTART , DMA_XCNT and DMA_XMOD registers mustbe written prior to the DMA_CFG register.Programs can write other registers that might remain static throughout the course of the DMA activity. The DMA operation begins once the DMA_CFG register is written.ATTENTION :When the DMA_CFG register is written directly by software, the DMA controller recognizesthis as the special startup condition that occurs when starting DMA for the first time on thischannel or after the DMA channel is stopped. It is possible for a DMA error condition to beflagged regardless of the DMA_CFG.EN bit setting.Startup OperationWhen the DMA_CFG register is written directly by software, the DMA channel recognizes this as the special startup condition that occurs when starting DMA for the first time on this channel or after the channel has entered to the stop state.When the descriptor fetch is complete and the DMA channel is enabled, the DMA_CFG descriptor element that was read into the DMA_CFG register assumes control. Before this point, the direct write to the DMA_CFG register had control.At startup, the selected flow mode and the and descriptor size determine the course of the DMA initializa-tion process. The DMA_CFG.FLOW field determines whether to load more current registers from descriptor sets in memory, while the DMA_CFG.NDSIZE field details how many descriptor elements to fetch before starting the DMA. DMA registers not included in the descriptor are not modified from their prior values.For descriptor list flow modes, the DMA_DSCPTR_NXT register is copied into the DMA_DSCPTR_CUR register. Then, fetches of new descriptor elements from memory are performed, indexed by the DMA_DSCPTR_CUR register, which is incremented after each fetch. After completion of the descriptor fetch, the DMA_DSCPTR_CUR register points to the next 32-bit word in memory past the end of the descriptor.If the descriptor fetch is for a descriptor array mode transfer, then the DMA_DSCPTR_NXT register is not copied into the DMA_DSCPTR_CUR register. Instead the descriptor fetch indexing begins with the value in the DMA_DSCPTR_CUR register.If DMA_CFG is not part of the fetched descriptor set, then the previous value, (originally as written on startup) controls the work unit operation. If the DMA_CFG register is part of the fetched descriptor set, then the value programmed by the MMR access controls only the loading of the first descriptor fetched fromD IRECT M EMORY A CCESS (DMA)DMA C HANNEL F UNCTIONAL D ESCRIPTIONADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCE Work Unit Receive and MDMA Destination TransitionsIn DMA receive (memory write) channels, the DMA_CFG.SYNC bit controls the handling of the DMA FIFO between descriptor chains (not individual descriptor sets), when the DMA channel is paused. The DMA channel pauses after descriptor sets configured with stop flow mode complete, and the channel may be restarted (for example, after an interrupt) by writing the channel’s DMA_CFG register with a value that enables the DMA channel. If the synchronization is disabled in the new work unit’s DMA_CFG value, a continuous transition is selected. In this mode, any data items received into the DMA FIFO while the channel was paused are retained, and they are the first items written to memory in the new work unit. This mode of operation provides lower latency at work unit transitions and ensures that no data items are dropped during a DMA pause, at the cost of certain restrictions on the DMA descriptors.NOTE :If the DMA_CFG.SYNC bit is configured to disable synchronization on the first descriptor of adescriptor chain after a DMA pause, the DMA_CFG.PSIZE field of the new chain must not change from the configuration of the previous descriptor chain that was active before the pause, unless the DMA channel is reset between chains by disabling and then re-enabling the DMA channel.A synchronized transition is selected if the DMA_CFG.SYNC bit is configured to enable synchronization. In this mode, only the data received from the peripheral by the DMA channel after the write to the DMA_CFG register is delivered to memory. Any prior data items transferred from the peripheral to the DMA FIFO before this register write are discarded. This provides direct synchronization between the data stream received from the peripheral and the timing of the channel restart (when the DMA_CFG register is written).For receive DMA operations, the synchronization has no effect in transitions between work units in the same descriptor chain (that is, when the previous descriptor’s flow mode was not stop, so that the DMA channel did not pause).If a descriptor chain begins with synchronization enabled, there is no restriction on the DMA_CFG.PSIZE of the new chain in comparison to the previous chain.NOTE :The peripheral transfer size (DMA_CFG.PSIZE ) must not change between one descriptor and thenext in any DMA receive (memory write) channel within a single descriptor chain, regardless of the DMA_CFG.SYNC bit setting. In other words, all memory write descriptor sets in a descriptorchain must have the same DMA_CFG.PSIZE value. For any DMA receive (memory write) channel, there is no restriction on changes of peripheral transfer size (internal versus external) betweendescriptors or descriptor chains.Transfer Termination and ShutdownThis section describes channel transfer termination and shutdown in stop flow mode and in autobuffer flow mode.Stop Flow ModeIn stop flow mode, the DMA channel stops automatically after the work unit is complete. If a list or array of descriptors is used to control DMA transfers, and if every descriptor contains a DMA_CFG descriptor element, then the final DMA_CFG descriptor element should have the flow configured to stop mode setting to gracefully stop the channel. Upon completion the DMA channel remains in the stop state. This state。

FPGA可编程逻辑器件芯片5SEE9F45I3L中文规格书

UART Port ControllersIrDA Transmit OperationTo generate the IrDA pulse transmitted by the UART, the normal NRZ output of the transmitter is first inverted if the TPOLC bit is cleared, so a 0 is transmitted as a high pulse of 16 UART clock periods and a 1 istransmitted as a low pulse for 16 UART clock periods. The leading edge of the pulse is then delayed by six UART clock periods. Similarly, the trailing edge of the pulse is truncated by eight UART clock periods. This results in the final representation of the original 0 as a high pulse of only 3/16 clock periods in a 16-cycle UART clock period. The pulse is centered around the middle of the bit time, as shown in Figure25-4. The final IrDA pulse is fed to the off-chip infrared driver.Figure 25-4. IrDA Transmit PulseThis modulation approach ensures a pulse width output from the UART of three cycles high out of every 16 UART clock cycles. As shown inTable25-2 on page25-19, the error terms associated with the bit rate gen-erator are very small and well within the tolerance of most infraredtransceiver specifications.ADSP-BF54x Blackfin Processor Hardware ReferenceADSP-BF54x Blackfin Processor Hardware Reference General-Purpose Ports PB5PB511:10UART2 RX ---TACI22PB6PB613:12UART3 TX ----PB7PB715:14UART3 RX ---TACI32PB8PB817:16SPI2 SS TMR0---PB9PB919:18SPI2 SSEL1TMR1---PB10PB1021:20SPI2 SSEL2TMR2---PB11PB1123:22SPI2 SSEL3TMR3--HWAIT 3PB12PB1225:24SPI2 SCK ----PB13PB1327:26SPI2 MOSI ----PB14PB1429:28SPI2 MISO ----1 PB_0 and PB_1 are I 2C pins which also have GPIO capability. Since the I 2C pads can only drive low, the GPIO for these two bits cannot drive a 1. These pads should be used with an external pull-up, so that a 1 is seen when they are not pulling down.2 To enable timer alternate capture and clock Inputs, either the GPIO or the multiplexed periph-eral must enable the pin input driver. This driver is not enabled by the timer.3 The Boot Host Wait (HWAIT) signal is a GPIO output that is driven and toggled by the boot kernel at boot time. An external pulling resistor is required for proper operation. A pull-up re-sistor instructs the HWAIT signal to behave active high (low when ready for data). A pull-down resistor instructs the HWAIT signal to behave active low (high when ready for data). After boot it can be used for other purposes. If PB11 is used for other purposes (for example, timer or SPI operation), the HWAITA signal on PH7 can be used alternatively. The Alternate Host Wait (HWAITA) can be alternatively used instead of HWAIT on PH7 when programming the OTP_ALTERNATE_HWAIT bit in the PBS_MAIN_LO OTP memory page. For details, see “System Reset and Booting” on page 17-1.Table 9-3. Port B Pin Configuration (Cont’d)Pin GPIOPORTB_MU X 1st Function (MUX = 00)2nd Function (MUX = 01)3rd Function (MUX = 10)4th Function (MUX = 11)Additiona l Use。

FPGA可编程逻辑器件芯片EP4SGF35I3NAA中文规格书

DC & Switching CharacteristicsTable5–97.DQS Phase Jitter Specifications for DLL-Delayed Clock(tDQS PHASE_JITTER) Note(1)Number of DQS DelayDQS Phase Jitter UnitBuffer Stages (2)130ps260ps390ps4120psNotes to Table5–97:(1)Peak-to-peak phase jitter on the phase shifted DDS clock (digital jitter is causedby DLL tracking).(2)Delay stages used for requested DQS phase shift are reported in your project’sCompilation Report in the Quartus II software.Table5–98.DQS Phase-Shift Error Specifications for DLL-Delayed Clock (tDQS_PSERR)(1)Number of DQS Delay Buffer Stages (2)–3 Speed Grade–4 Speed Grade–5 Speed Grade Unit 1253035ps2506070ps37590105ps4100120140ps Notes to Table5–98:(1)This error specification is the absolute maximum and minimum error. For example, skew on three delay bufferstages in a C3 speed grade is 75ps or ± 37.5ps.(2)Delay stages used for requested DQS phase shift are reported in your project’s Compilation Report in theQuartus II software.Table5–99.DQS Bus Clock Skew Adder Specifications(tDQS_CLOCK_SKEW_ADDER)Mode DQS Clock Skew Adder Unit×4 DQ per DQS40ps×9 DQ per DQS70ps×18 DQ per DQS75ps×36 DQ per DQS95psNote to Table5–99:(1)This skew specification is the absolute maximum and minimum skew. Forexample, skew on a ×4 DQ group is 40 ps or ±20ps.Stratix II Device Handbook, Volume 1Section I.Stratix II DeviceFamily Data SheetThis section provides the data sheet specifications for Stratix®II devices.This section contains feature definitions of the internal architecture,configuration and JTAG boundary-scan testing information, DCoperating conditions, AC timing parameters, a reference to powerconsumption, and ordering information for Stratix II devices.This section contains the following chapters:■Chapter1, Introduction■Chapter2, Stratix II Architecture■Chapter3, Configuration & Testing■Chapter4, Hot Socketing & Power-On Reset■Chapter5, DC & Switching Characteristics■Chapter6, Reference & Ordering InformationRevision History Refer to each chapter for its own specific revision history. For informationon when each chapter was updated, refer to the Chapter Revision Datessection, which appears in the full handbook.Section I–1Logic Array BlocksFigure2–2.Stratix II LAB StructureLAB InterconnectsThe LAB local interconnect can drive ALMs in the same LAB. It is drivenby column and row interconnects and ALM outputs in the same LAB.Neighboring LABs, M512 RAM blocks, M4K RAM blocks, M-RAMblocks, or DSP blocks from the left and right can also drive an LAB's localinterconnect through the direct link connection. The direct linkconnection feature minimizes the use of row and column interconnects,providing higher performance and flexibility. Each ALM can drive24ALMs through fast local and direct link interconnects. Figure2–3shows the direct link connection.Stratix II Device Handbook, Volume 1。

FPGA可编程逻辑器件芯片EP2AGX260FF35C5N中文规格书

U NIVERSAL A SYNCHRONOUS R ECEIVER /T RANSMITTER (UART)UART O PERATING M ODESADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCENOTE :The UART’s status interrupt goes directly to the system event controller (SEC), bypassing theDMA unit completely.For transmit DMA, programs should set the DMA_CFG.SYNC bit. With this bit set, interrupt generation is delayed until the entire DMA FIFO is drained to the UART module. The UART transmit DMA interrupt service routine is allowed to disable the DMA or to clear the UART_IMSK.ETBEI control bit only when the DMA_CFG.SYNC bit is set, otherwise up to four data bytes might be lost.When the UART_IMSK.ETBEI bit is set, an initial transmit DMA request is issued immediately. The program should then clear the UART_IMSK.ETBEI bit through the DMA service routine.In DMA transmit mode, the UART_IMSK.ETBEI bit enables the peripheral request to the DMA FIFO. The strobe on the memory side is still enabled by the DMA_CFG.EN bit. If the DMA count is less than the DMA FIFO depth, which is 4, then the DMA interrupt might be requested before the UART_IMSK.ETBEI bit is set. If this is behavior not wanted, set the DMA_CFG.SYNC bit.Regardless of the DMA_CFG.SYNC setting, the DMA stream has not left the UART transmitter completely at the time the interrupt is generated. Transmission may abort in the middle of the stream, causing data loss, if the UART clock was disabled without additional synchronization with the UART_STAT.TEMT bit.The UART provides functionality to avoid resource consuming polling of the UART_STAT.TEMT bit. The UART_IMSK_SET.EDTPTI bit enables the UART_STAT.TEMT bit to trigger a DMA interrupt. To delay the DMA completion interrupt until the last data word of a STOP DMA has left the UART, keep the DMA_CFG.DI_EN bit cleared and set the UART_IMSK_SET.EDTPTI bit instead. Then, the normal DMA completion interrupt is suppressed. Later, the UART_STAT.TEMT event triggers a DMA interrupt after the DMA’s last word has left the UART transmit buffers. If DI_EN and UART_IMSK.EDTPTI are set, when finishing STOP mode, the DMA requests two interrupts.The UART’s DMA supports 8-bit and 16-bit operation, but not 32-bit operation. Sign extension is also not supported.Mixing DMA and Core ModesSwitching from DMA mode to core operation on the fly requires some consideration, especially fortransmit operations. By default, the interrupt timing of the DMA is synchronized with the memory side of the DMA FIFOs. Normally, the transmit DMA completion interrupt is generated after the last byte is copied from the memory into the DMA FIFO. The transmit DMA interrupt service routine is not yet permitted to disable the DMA_CFG.EN bit. The interrupt is requested by the time the DMA_STAT.IRQDONE bit is set. The DMA_STAT.RUN bit, however, remains set until the data has completely left the transmit DMA FIFO.Therefore, when planning to switch from a DMA to the core mode, always set the DMA_CFG.SYNC bit in the word of the last descriptor or work unit before handing over control to core mode. Then, after the interrupt occurs, software can write new data into the UART_THR register as soon as the UART_STAT.THRE bit permits. If the DMA_CFG.SYNC bit cannot be set, software can poll the DMA_STAT.RUN bit instead. Alternatively, using the UART_IMSK.EDTPTI bit can avoid expensive status bit polling.U NIVERSAL A SYNCHRONOUS R ECEIVER/T RANSMITTER (UART)UART O PERATING M ODESThe two force error bits, UART_CTL.FPE and UART_CTL.FFE, are intended for test purposes. They areuseful for debugging software, especially in loop back mode.The UART can be set to internal loop back mode (UART_CTL.LOOP_EN=1). Loop back mode disconnects the receiver’s input from the receive pin and internally redirects the transmit output to the receiver. The transmit pin remains active and continues to transmit data externally as well. Loop back mode also forces the UART_RTS pin to de-assert, disconnects the UART_STAT.CTS bit from the UART_CTS input pin, and connects the internal version of UART_RTS to the UART_STAT.CTS bit.Additionally, the UART_TX pin can be forced to zero asynchronously using the UART_CTL.SB bit. UART Operating ModesThe UART’s main operating modes are described in the following sections.•UART Mode•IrDA SIR Mode•Multi-Drop Bus ModeUART ModeThe UART Mode follows an asynchronous serial communication protocol with these options:• 1 start bit•5-8 data bits•Address bit (available in MDB mode only)•None, even, odd or sticky parity•1, 1½, or 2 stop bits (1½ stop bits valid only in 5-bit word length)The format of received and transmitted character frames is controlled by the UART_CTL register. Data is always transmitted and received with the least significant bit (LSB) first.The following figure shows a typical physical bit stream measured on a UART_TX pin.ADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCEU NIVERSAL A SYNCHRONOUS R ECEIVER /T RANSMITTER (UART)UART O PERATING M ODESADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCE The transmission of break command/inter-frame gap is followed by transmission of the number of stop bits as set in the UART_CTL.STB and UART_CTL.STBH bit fields.The UART receiver can detect break commands through the break indicator (UART_STAT.BI ) flag. This flag reports that an entire UART frame has been received in low state. It does not report whether the dura-tion of the received low pulse was exact or at least 13 bit times as LIN masters transmit. Typically, the break indicator meets LIN requirements. If however the pulse width needs to be determined more precisely, the GP timers can be used.On ADSP-BF60x processors each UART_RX pin is also routed to any of the GP timers through their alter-nate capture input (TACI). This is not only useful for bit rate detection (autobaud ) but also helps to precisely measure the pulse widths on the UART_RX input. Additionally, the new windowed watchdog width mode of the GP timers can issue an interrupt or a fault condition if the received pulse width is shorter than a bit time or longer than the worst case break condition.UART Mode Receive Operation (Core)The receive operation uses the same data format as the transmit configuration, except that one valid stop bit is always sufficient; that is, the UART_CTL.STB and UART_CTL.STBH bits have no impact to the receiver.The UART receiver senses the falling edges of the receive input. When an edge is detected, the receiver starts sampling the input according to settings in the UART_CLK register. The start bit is sampled (majority sampling) close to its midpoint. If sampled low, a valid start condition is assumed. Otherwise, the detected falling edge is discarded.After detection of the start bit, the received word is shifted into the UART_RSR register.After the corresponding stop bit is received, the content of the UART_RSR register is transferred to the 8-deep receive FIFO and is accessible by reading the UART_RBR register.The receive FIFOs and the UART_RBR register can be seen as a 9-stage receive buffer. If the stop bit of the 9th word is received before software reads the UART_RBR register, an overrun error is reported. Overruns protect data in the UART_RBR register and the receive FIFO from being overwritten by further data until the UART_STAT.OE bit is cleared by software. However, the data in the UART_RSR register is immediately destroyed as soon as the overrun occurs.The sampling clock is 16 times faster than the bit clock. The receiver over samples every bit 16 times and makes a majority decision based on the middle three samples. This improves immunity against noise and hazards on the line. Spurious pulses of less than two times the sampling clock period are disregarded.Normally, every incoming bit is sampled at exactly the 7th, 8th and 9th sample clock. If, however, the UART_CLK.EDBO bit is set to 1 to achieve better bit rate granularity and accuracy as required at high oper-ation speeds, the bits are one roughly sampled at 7/16th, 8/16th and 9/16th of their period. Hardware design should ensure that the incoming signal is stable between 6/16th and 10/16th of the nominal bit period.Reception starts when a falling edge is detected on the UART_RX input pin. The receiver attempts to see a start bit. The data is shifted into the UART_RSR register. After the 9th sample of the first stop bit is。

FPGA可编程逻辑器件芯片EP2AGX125EF35I3N中文规格书

CRC P ROGRAMMING M ODEL3.Initialize CRC_RESULT_CUR.A DDITIONAL I NFORMATION:This register may be initialized to provide an initial seed for the CRC opera-tion that is about to take place.4.Initialize CRC_COMP.A DDITIONAL I NFORMATION:This register contains the pre-calculated final CRC signature result for thememory region that is used in the final compare operation.5.Initialize CRC_INEN.A DDITIONAL I NFORMATION:This register is used to enable the generation of the CRC interrupts for notifi-cation of compare errors and block completion. Configure these interrupts as required. If enabledensure the corresponding interrupt handlers are also configured.6.Initialize CRC_CTL with CRC_CTL.OPMODE set to memory scan compute compare mode and CRC_CTL.BLKEN configured to enable the CRC peripheral.•CRC_CTL.OBRSTALL and CRC_CTL.IRRSTALL options must be disabled for this task example.•All mirroring and bit reversal options should also be configured.•CRC auto clear options should also be configured.S TEP R ESULT:The CRC peripheral is now enabled and ready for data to be written by the core or DMA channel.7.Write memory region data to the CRC peripheral and read it back to the new destination.a.While CRC_STAT.IBR indicates input buffer is ready, write CRC_DFIFO with 32-bit data.b.While CRC_STAT.OBR indicates output buffer is ready, read CRC_DFIFO and store data to new desti-nation.A DDITIONAL I NFORMATION:These two steps are repeated until all required data has been processed through theCRC peripheral and copied to the new destination.8.Poll CRC_STAT.DCNTEXP if the interrupt was disabled.A DDITIONAL I NFORMATION:This step is required only if the counter expired interrupt is disabled. Pollingis required to ensure all the data has been processed.9.Poll CRC_STAT.CMPERR if the interrupt was disabled to check for a compare error.A DDITIONAL I NFORMATION:This step is only required if the compare error interrupt is not enabled.CRC P ERIPHERAL AND DMA C HANNEL L IST6.Configure and enable the memory-to-memory destination DMA channel for memory write STOPmode.A DDITIONAL I NFORMATION:This step starts the data transfer taking the constant 32-bit value from the CRCperipheral and writing the data to the DMA channel.7.Poll CRC_STAT.DCNTEXP if the interrupt was disabled.A DDITIONAL I NFORMATION:This step is required only if counter expired interrupt is disabled. Polling isrequired to ensure all the data has been processed.8.Write CRC_STAT to clear CRC_STAT.DCNTEXP.A DDITIONAL I NFORMATION:If interrupts were enabled then the clearing of this status bit should beperformed within the interrupt handlers for the respective interrupts.S TEP R ESULT:The CRC memory transfer fill operation is now complete and the CRC peripheral is readyto be configured for the next CRC operation.R ESULT:The memory region is now filled with the constant data and the CRC peripheral is ready to be configuredfor a new operation.A FTER C OMPLETING T HIS T ASK:Ensure any W1C CRC status bits and DMA status bits are cleared before performing a further CRC oper-ation.CRC Peripheral and DMA Channel ListTable 12-4:CRC DMA ChannelsDMA Channel Peripheral FIFO Depth (Bytes)Bandwidth Limit/Monitor Support DMA21CRC0Receive128Y esDMA22CRC0Transmit64Y esDMA23CRC1Receive64Y esDMA24CRC1Transmit64Y esTable 12-5:CRC DMA Channels (Continued)DMA Channel Memory BusWidth Peripheral Bus Width Max Outstanding Reads Max Outstanding WritesDMA2132-bit32-bit87 DMA2232-bit32-bit84C YCLIC R EDUNDANCY C HECK (CRC)ADSP-BF60X CRC R EGISTER D ESCRIPTIONS16 (R/W)BITMIRR Bit Mirroring.The CRC_CTL.BITMIRR enables the CRC's data mirror block tomirror the bits within each byte of the 32-bit input data, beforefurther processing.0Disable bit mirroring1Enable bit mirroring13 (R/W)IRRSTALL Intermediate Result Ready Stall.The CRC_CTL.IRRSTALL enables stalling the state machine for inputdata when there is a valid intermediate result to be read in CRC_RESULT_CUR. This feature should be used only in CRC computationmodes (for example, CRC_CTL.OPMODE =1 or =3).0Do not stall1Stall on IRR12 (R/W)OBRSTALL Output Buffer Ready Stall.The CRC_CTL.OBRSTALL enables stalling the state machine for inputdata when there is a valid data in the output buffer. This featureshould be used only in memory-to-memory transfer modes (forexample, CRC_CTL.OPMODE =1).0Do not stall1Stall on OBR9 (R/W)AUTOCLRF Auto Clear to One.The CRC_CTL.AUTOCLRF enables auto clear to one when the CRC isin intermediate results ready stall mode (CRC_CTL.IRRSTALL=1) andthe CRC data count expires (CRC_DCNT=0). Note that CRC_CTL.AUTOCLRZ must be disabled, or the CRC_CTL.AUTOCLRF has no effect.0No auto clear1Auto clear8 (R/W)AUTOCLRZ Auto Clear to Zero.The CRC_CTL.AUTOCLRZ enables auto clear to zero when the CRC isin intermediate results ready stall mode (CRC_CTL.IRRSTALL=1) andthe CRC data count expires (CRC_DCNT=0). Note that CRC_CTL.AUTOCLRF must be disabled, or the CRC_CTL.AUTOCLRZ has no effect.0No auto clear1Auto clearTable 12-7:CRC_CTL Register Fields (Continued)Bit No.(Access)Bit Name Description/Enumeration。

FPGA可编程逻辑器件芯片EP2AGX95EF35I5N中文规格书

Cascading PLLsYou can cascade the corner and center PLLs through the GCLK and RCLK networks(Arria II GX devices) or left/right and top/bottom PLLs through the GCLK andRCLK networks (Arria II GZ devices). In addition, where two PLLs exist next to eachother, there is a direct connection between them that does not require the GCLK andRCLK network. By cascading PLLs, you can use this path to reduce clock jitter. ForArria II GX devices, the direct PLL cascading feature is available in PLL_5 and PLL_6on the right side of EP2AGX95, EP2AGX125, EP2AGX190, and EP2AGX260 devices.Arria II GX devices allow cascading of PLL_1 and PLL_4 to the transceiver PLLs (clockmanagement unit PLLs and receiver clock data recoveries [CDRs]). Arria II GZdevices allows cascading the left and right PLLs to transceiver PLLs (CMU PLLs andreceiver CDRs).If your design cascades PLLs, the source (upstream) PLL must have a low-bandwidthsetting, while the destination (downstream) PLL must have a high-bandwidth setting.Ensure that there is no overlap of the bandwidth ranges of the two PLLs.f For more information, refer to the “FPGA Fabric PLLs-Transceiver PLLs Cascading”section in the Transceiver Clocking in Arria II Devices chapter.f For more information about PLL cascading in external memory interfaces designs,refer to the External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction UserGuide.PLLs in Arria II DevicesArria II GX devices offer up to six PLLs per device and seven outputs per PLL, whileArria II GZ devices offer up to eight PLLs that provide robust clock management andsynthesis for device clock management, external system clock management, andhigh-speed I/O interfaces. The nomenclature for the PLLs follows their geographicallocation in the device floor plan. For the location and number of PLLs in Arria IIdevices, refer to Figure5–1 on page5–4 through Figure5–4 on page5–6.1Depending on the package, Arria II GX devices offer up to eight transceivertransmitter (TX) PLLs per device that can be used by the FPGA fabric if they are notused by the transceiver.f For more information about the number of general-purpose and transceiver TX PLLsin each device density, refer to the Overview for Arria II Device Family chapter. For moreinformation about using the transceiver TX PLLs in the transceiver block, refer to theTransceiver Clocking in Arria II Devices chapter.All Arria II PLLs have the same core analog structure and support features withminor differences in the features that are supported for Arria II GZ devices.Chapter 5:Clock Networks and PLLs in Arria II DevicesPLLs in Arria II Devices Table5–13 lists the PLL features in Arria II devices.Table5–13.PLL Features in Arria II DevicesFeature Arria II GX PLLsArria II GZ PLLsTop/Bottom PLLs Left/Right PLLsC (output) counters7107M, N, C counter sizes 1 to 512 1 to 512 1 to 512Dedicated clock outputs 1 single-ended or 1 differentialpair3 single-ended or 3 differentialpairs (1), (2)6 single-ended or4single-ended and1differential pair2 single-ended or 1 differentialpairClock input pins 4 single-ended or 2 differentialpin pairs4 single-ended or 2differential pin pairs4 single-ended or 2 differentialpin pairsExternal feedback input pin No Single-ended or differential Single-ended only Spread-spectrum input clocktrackingYes (3)Yes (3)Yes (3)PLL cascading Through GCLK and RCLK anddedicated path betweenadjacent PLLs. Cascadingbetween the general-purposePLL and transceiver PLL issupported in PLL_1 andPLL_4.Through GCLK and RCLKand a dedicated pathbetween adjacent PLLsThrough GCLK and RCLK anddedicated path betweenadjacent PLLs (4)Compensation modes All except external feedbackmode when you usedifferential I/OsAll except LVDS clocknetwork compensationAll except external feedbackmode when you usedifferential I/OsPLL drives DIFFCLK andLOADENYes No YesVCO output drives DPA clock Yes No YesPhase shift resolution Down to 96.125ps (5)Down to 96.125ps (5)Down to 96.125ps (5) Programmable duty cycle Yes Yes YesOutput counter cascading Yes Yes YesInput clock switchover Yes Yes YesNotes to Table5–13:(1)PLL_5 and PLL_6 do not have dedicated clock outputs.(2)The same PLL clock output drives three single-ended or three differential I/O pairs. This is only supported in PLL_1 and PLL_3 of EP2AGX95,EP2AGX125, EP2AGX190, and EP2AGX260 devices.(3)This is applicable only if the input clock jitter is within the input jitter tolerance specifications.(4)The dedicated path between adjacent PLLs is not available on L1, L4, R1, and R4 PLLs.(5)The smallest phase shift is determined by the voltage-controlled oscillator (VCO) period divided by eight. For degree increments, the Arria II devicecan shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and C counter value.Chapter 5:Clock Networks and PLLs in Arria II Devices PLLs in Arria II DevicesPLL Hardware Overview in Arria II DevicesFigure 5–20 shows a simplified block diagram of the major components of the Arria II PLL.1You can drive the GCLK or RCLK clock input with an output from another PLL, a pin-driven GCLK or RCLK, or through a clock control block, provided the clockcontrol block is fed by an output from another PLL, or a pin driven dedicated GCLK or RCLK. An internally-generated global signal or general purpose I/O (GPIO) pin cannot drive the PLL.PLL Clock I/O PinsFor Arria II GX devices, each PLL supports one of the following clock I/O pin configurations:■One single-ended I/O or one differential I/O pair.■Three single-ended I/O or three differential I/O pairs (this is only supported in PLL _1 and PLL _3 of EP2AGX95, EP2AGX125, EP2AGX190, and EP2AGX260devices). You can only access one differential I/O pair or one single-ended pin at a time.Figure 5–20.PLL Block Diagram for Arria II DevicesNotes to Figure 5–20:(1)The number of post-scale counters is seven for left and right PLLs and ten for top and bottom PLLs.(2)This is the VCO post-scale counter K .(3)The FBOUT port is fed by the M counter in Arria II PLLs. The FBOUT port is only available in Arria II GZ devices.Chapter 5:Clock Networks and PLLs in Arria II DevicesPLLs in Arria II Devices Figure5–21 shows the clock I/O pins associated with Arria II GX PLLs.Figure5–21.External Clock Outputs for Arria II GX PLLsChapter 5:Clock Networks and PLLs in Arria II Devices PLLs in Arria II Devices。

FPGA可编程逻辑器件芯片5SEE9F45I3N中文规格书

MXVR RegistersADSP-BF54x Blackfin Processor Hardware ReferenceThe MXVR Crystal Oscillator Clock Enable (MXTALCEN ) bit enables or dis-ables the clock output by the MXVR Crystal Oscillator which is used by the MXVR PLLs. The MXTALCEN bit enables or disables the clock regardless of whether a crystal is used between the MXI and MXO pins or whether a clock is directly driven into the MXI pin. When MXTALCEN is set to 1, the clock supplied by the MXVR Crystal Oscillator is enabled, and when MXTALCEN is set to 0, the clock supplied by the MXVR Crystal Oscillator is disabled. The MXTALCEN is set to 1 by reset. The MXTALCEN can be used to gate off the clock to the MXVR in order to save power when the network is not in operation. Note that the crystal should be at frequency and MXTALCEN should be enabled, or the clock driven on the MXI input should be at frequency and the MXTALCEN should be enabled prior to starting up the MXVR PLLs.The MXVR Crystal Oscillator Feedback Enable (MXTALFEN ) bit enables or disables the resistive feedback between the MXVR Crystal Input pin (MXI ) and the MXVR Crystal Output pin (MXO ). The MXVR Crystal Oscillator supplies a clock which is used by the MXVR PLLs. A crystal can be placed between the MXI and MXO pins (along with the appropriate capacitors) or a clock may be driven directly into the MXI pin and the MXO pin can be left unconnected. When using a crystal, if the MXTALFEN is set to 1, the resistive feedback between MXI and MXO is enabled and the crystal will oscillate. When using a crystal, if MXTALFEN is set to 0, the resistive feedback is dis-abled and the crystal will not oscillate. If a crystal is not used and a clock is driven directly onto the MXI pin, the MXTALFEN must be set to 1 for proper operation. The MXTALFEN is set to 1 by reset, so that if a crystal is used, the crystal will start up during the reset time and software boot time.The MXVR must either be supplied with an externally generated clock driven on the MXI pin or must have a crystal (and appropriate external components) connected between the MXI and MXO pins. In either case, the frequency should be 256 * Fs, 384 * Fs, 512 * Fs, or 1024 * Fs. The fre-quency that is being supplied should be programmed into the MXTALMUL bits in the MXVR_CLK_CTL register. If a crystal is placed between MXI and MXO , and the network will be disabled for an extended period of time, theMXVR RegistersADSP-BF54x Blackfin Processor Hardware Reference The programming of the MXVR_PAT_EN_x registers determines which of the bits in each of the four bytes will be used to check for a pattern match and controls the number of bytes to be matched.MXVR Pattern Enable (MXVR_PAT_EN_0,MXVR_PAT_EN_1) RegistersThe MXVR_PAT_EN_x registers contain bit enables that allow individual bits within a Match Data Byte to be selectively enabled (a “care”) or disabled (a “don't care”) in the comparison with the incoming synchronous data bytes in a logical channel while checking for the occurrence of a “start pat-tern” or a “stop pattern” when a DMA channel is in one of the Synchronous Packet modes.For example, if the Byte0-Bit 7 Match Enable is set to 1 and all the other bit match enables are set to 0, then only bit 7 of Match Data Byte 0 is used in the comparison and bits 6–0 of Match Data Byte 0 are “don't cares”. Therefore, for a pattern match to occur, only bit 7 of the received synchronous data byte in the logical channel must match bit 7 of Match Data Byte 0.Figure 29-34. MXVR Pattern Data Registers。

FPGA可编程逻辑器件芯片EP2AGX190FF35I3N中文规格书

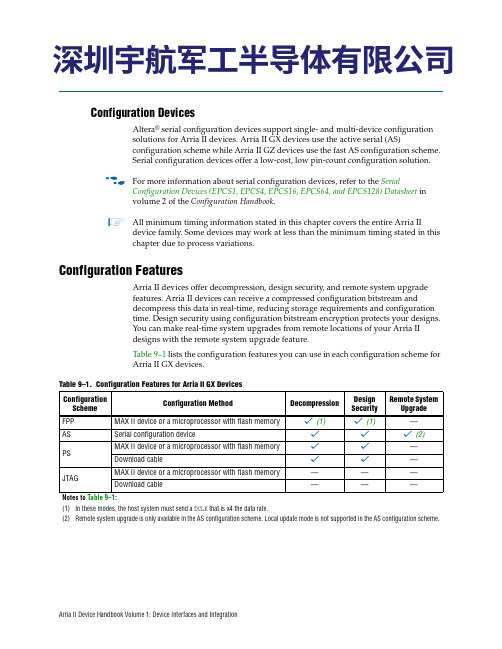

Configuration DevicesAltera® serial configuration devices support single- and multi-device configurationsolutions for Arria II devices. Arria II GX devices use the active serial (AS)configuration scheme while Arria II GZ devices use the fast AS configuration scheme.Serial configuration devices offer a low-cost, low pin-count configuration solution.f For more information about serial configuration devices, refer to the SerialConfiguration Devices (EPCS1, EPCS4, EPCS16, EPCS64, and EPCS128) Datasheet involume2 of the Configuration Handbook.1All minimum timing information stated in this chapter covers the entire Arria II device family. Some devices may work at less than the minimum timing stated in thischapter due to process variations.Configuration FeaturesArria II devices offer decompression, design security, and remote system upgradefeatures. Arria II devices can receive a compressed configuration bitstream anddecompress this data in real-time, reducing storage requirements and configurationtime. Design security using configuration bitstream encryption protects your designs.You can make real-time system upgrades from remote locations of your Arria IIdesigns with the remote system upgrade feature.Table9–1 lists the configuration features you can use in each configuration scheme forArria II GX devices.Table9–1.Configuration Features for Arria II GX DevicesConfiguration Scheme Configuration Method DecompressionDesignSecurityRemote SystemUpgradeFPP MAX II device or a microprocessor with flash memory v(1)v(1)—AS Serial configuration device v v v(2)PS MAX II device or a microprocessor with flash memory v v—Download cable v v—JTAG MAX II device or a microprocessor with flash memory———Download cable———Notes to Table9–1:(1)In these modes, the host system must send a DCLK that is x4 the data rate.(2)Remote system upgrade is only available in the AS configuration scheme. Local update mode is not supported in the AS configuration scheme.Configuration FeaturesTable9–2 lists the configuration features you can use in each configuration scheme forArria II GZ devices.Fast Passive Parallel ConfigurationRaw Binary File SizeTable9–8 lists the uncompressed raw binary file (.rbf) configuration file sizes forArria II devices.Table9–8.Uncompressed .rbf Sizes for Arria II DevicesDevice Data Size (bits)EP2AGX4529,599,704EP2AGX6529,599,704EP2AGX9550,376,968EP2AGX12550,376,968EP2AGX19086,866,440EP2AGX26086,866,440EP2AGZ22594,557,472EP2AGZ300128,395,584EP2AGZ350128,395,584Use the data in Table9–8 to estimate the file size before design compilation. Differentconfiguration file formats, such as a hexidecimal (.hex) or tabular text file (.ttf) format,have different file sizes. For the different types of configuration file and file sizes, referto the Quartus II software. However, for a specific version of the Quartus II software,any design targeted for the same device has the same uncompressed configuration filesize. If you are using compression, the file size can vary after each compilationbecause the compression ratio depends on your design.f For more information about setting device configuration options or creatingconfiguration files, refer to the Device Configuration Options and Configuration FileFormats chapters in volume2 of the Configuration Handbook.Fast Passive Parallel ConfigurationFPP configuration in Arria II devices is designed to meet the continuously increasingdemand for faster configuration times. Arria II devices are designed with thecapability of receiving byte-wide configuration data per clock cycle.You can perform FPP configuration of Arria II devices using an intelligent host suchas a MAX II device or microprocessor.FPP Configuration Using a MAX II Device as an External HostFPP configuration using an external host provides the fastest method to configureArria II devices. In this configuration scheme, you can use a MAX II device ormicroprocessor as an intelligent host that controls the transfer of configuration datafrom a storage device, such as flash memory, to the target Arria II device. You canstore configuration data in .rbf, .hex, or .ttf format. When using the MAX II device ormicroprocessor as an intelligent host, a design that controls the configuration process,such as fetching the data from flash memory and sending it to the device, must bestored in the MAX II device or microprocessor.Chapter 9:Configuration, Design Security, and Remote System Upgrades in Arria II DevicesFast Passive Parallel Configuration 1If you use the Arria II decompression and/or design security features, the external host must send a DCLK frequency that is x4 the data rate.The x4 DCLK signal does not require an additional pin and is sent on the DCLK pin. Themaximum DCLK frequency is 125MHz, which results in a maximum data rate of250Mbps. For Arria II GX devices, if you are not using the decompression or designsecurity features, the data rate is x1 the DCLK frequency. For Arria II GZ devices, if youare not using the decompression or design security features, the data rate is x8 theDCLK frequency.Figure9–1 shows the configuration interface connections between an Arria II deviceand a MAX II device for single device configuration.Figure9–1.Single Device FPP Configuration Using an External Host.C. (3)Chapter 9:Configuration, Design Security, and Remote System Upgrades in Arria II DevicesFast Passive Parallel ConfigurationFigure9–2.Multi-Device FPP Configuration Using an External Host.C.。

FPGA可编程逻辑器件芯片EP2AGX260FF35I6N中文规格书

P ULSE-W IDTH M ODULATOR (PWM)F UNCTIONAL D ESCRIPTIONSwitching Dead Time (PWM_DT) RegisterThe second important parameter that must be set up in the initial configuration of the PWM Controller is the switching dead time. This is a short delay introduced between turning off one PWM signal (forexample, AH) and turning on the complementary signal (for example, AL). This short time delay permits the power switch being turned off (AH in this case) to completely recover its blocking capability before the complementary switch is turned on. This time delay prevents a potentially destructive short-circuit condi-tion from developing across the dc link capacitor of a typical voltage source inverter.The 10-bit, read/write PWM_DT register controls the dead time. This register controls the dead time inserted into the three pairs of PWM output signals. Dead time (T d) is related to the value in the PWM_DT register by: T d = PWM_DT × 2 × t SCLKTherefore, a PWM_DT value of 0x00A introduces a 200 ns delay (for a SCLK of 100 MHz) between turning off any PWM signal (for example, AH) and then turning on its complementary signal (for example, AL).The length of the dead time can therefore be programmed in increments of 2 × t SCLK (or 20 ns for an SCLK of 100 MHz). The PWM_DT register is a 10-bit register whose maximum value of 0x3FF (1023 decimal) corresponds to a maximum programmed dead time of:T d(max) = 1023 × 2 × t SCLK = 1023 × 2 × 10 × 10-9 = 20.5 μsfor an f SCLK rate of 100 MHz. The dead time can be programmed to be zero by writing 0 to the PWM_DT register.Duty Cycle with Dead-Time Control: Calculations for PULSEMODE 00The duty cycle registers are scaled such that a value of 0 represents a 50% PWM duty, cycle. The switching signals produced are also adjusted to incorporate the programmed dead time value in the PWM_DT register.The unit in this case produces active low signals so that a low level corresponds to a command to turn on the associated power device.A typical pair of PWM outputs, PWM_AH and PWM_AL, is shown in the following figure. The time values inthe figure indicate the integer value in the associated register and can be converted to time by multiplying by the fundamental time increment, t CK. In the example channel A is working off of PWMTMR0.Because PULSEMODE is set to 00, the switching patterns are perfectly symmetrical about the mid-point of the switching period. The dead time is incorporated by moving the switching instants of both PWM signals away from the instant set by the PWM_AH0 register. Both switching edges are moved by an equal amount (PWMDT × t CK) to preserve the symmetrical output patterns. Also shown is the PWM_SYNC_OUT pulse whose rising edge denotes the beginning of the switching period, and the PWM_STAT.TMR0PHASE bit.ADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCEP ULSE -W IDTH M ODULATOR (PWM)E VENT C ONTROLADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCEeven in the event of a loss of the processor clock. In addition to the hardware shutdown features, the PWM system may be shutdown in software by means of the PWM_CTL.SWTRIP bit.Status information about the PWM is available to the user in the PWM_STAT register, which stores all status bits, including raw interrupt status bits. In particular, the period boundary of each timer is available, as well as status bits that indicate whether the operation is in the first half or the second half of the timer. Addi-tionally the TRIP status is also available.The PWM_IMSK and PWM_ILAT registers allow masking and show masked interrupt status bits respectively. The interrupt bits are latched and held on the interrupt event and the software must write a 1 to clear the interrupt bit, usually during the Interrupt Service routine.Trip Control UnitThe PWM Trip unit processes hardware or software fault conditions and shuts down the PWM channel outputs immediately on the occurrence of these conditions. This shut down mechanism can be enabled separately for each channel. The design also allows for a self-restart mechanism to be enabled on a channel. Self-restart re-enables the channel outputs following the fault condition (allowed only on hardware trips) when the PWMTMR-y that the channel is using reaches its period boundary.There are 2 external hardware sources that can indicate a hardware fault condition:1.PWMTRIP0 input pin2.PWMTRIP1 input pinThese are active low inputs where a falling edge on either of these pins indicates a fault condition.To enable the trip unit to shut down a particular channel's output in response to the fault event on either of these PWM_TRIPn pins, program the PWM_TRIPCFG.EN0A bit corresponding to that channel.The PWM_TRIPCFG.MODE0A bits must be programmed to specify the restart mechanism for a channel that has been tripped.1.If PWM_TRIPCFG.MODE0A = 0, once tripped, a trip condition is registered on this channel in the PWM_STAT.FLTTRIPA bit and the outputs of that channel are immediately shut down. This is called a FAULT TRIP condition. To resume channel output when a FAULT TRIP occurs, clear the PWM_STAT.FLTTRIPA bit by writing a 1 to it. Note that the bit cannot be cleared by a processor write if the trip condition is still active. The RAW trip status is available for both the pins in the PWM_STAT.RAWTRIP0register bits.2.If PWM_TRIPCFG.MODE0A = 1, once tripped, a trip condition is registered on this channel in the PWM_STAT.SRTRIPA bit and the outputs of that channel are immediately shut down. This is called a self-restart trip condition. At the next period boundary of the PWMTMR-y that the channel is using, if the tripping condition is not active, the design clears the status register bit and restores the outputs.The trip input pins should have an external pull-down resistor on the chip pin, so that if the pin becomes unconnected the PWM will be disabled.P ULSE-W IDTH M ODULATOR (PWM)F UNCTIONAL D ESCRIPTIONFigure 18-15:XOVR and DISHI/DISLO FunctionalityBrushless DC Motor (Electronically Commutated Motor) ControlIn the control of an electronically commutated motor (ECM), only two inverter legs are switched at any time. Often, the high-side device in one leg must be switched on at the same time as the low-side driver ina second leg. Therefore, by programming identical duty cycles values for two PWM channels (for example,PWM_CHA = PWM_CHB) and setting the PWM_BCTL.XOVR bit to crossover the BH/BL pair if PWM signals, it is possible to turn on the high-side switch of phase A and the low-side switch of phase B at the same time.To control ECM, normally the third inverter leg (phase C in this example) is disabled for a number of PWM cycles. To implement this function, both the PWM_CH and PWM_CL outputs are disabled by setting the PWM_CCTL.DISHI and PWM_CCTL.DISLO bits.In normal ECM operation, each inverter leg is disabled for certain time periods so that the PWM channel registers change based on the position of the rotor shaft (motor commutation).ADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCE。

FPGA可编程逻辑器件芯片EP2AGX95EF29C4N中文规格书

AIIGX51001-4.4The Arria® II device family is designed specifically for ease-of-use. Thecost-optimized, 40-nm device family architecture features a low-power,programmable logic engine and streamlined transceivers and I/Os. Commoninterfaces, such as the Physical Interface for PCI Express® (PCIe®), Ethernet, andDDR3 memory are easily implemented in your design with the Quartus®II software,the SOPC Builder design software, and a broad library of hard and soft intellectualproperty (IP) solutions from Altera. The Arria II device family makes designing forapplications requiring transceivers operating at up to 6.375Gbps fast and easy.This chapter contains the following sections:■“Arria II Device Feature” on page1–1■“Arria II Device Architecture” on page1–6■“Reference and Ordering Information” on page1–14Arria II Device FeatureThe Arria II device features consist of the following highlights:■40-nm, low-power FPGA engine■Adaptive logic module (ALM) offers the highest logic efficiency in the industry■Eight-input fracturable look-up table (LUT)■Memory logic array blocks (MLABs) for efficient implementation of smallFIFOs■High-performance digital signal processing (DSP) blocks up to 550MHz■Configurable as 9 x 9-bit, 12 x 12-bit, 18 x 18-bit, and 36 x 36-bit full-precisionmultipliers as well as 18 x 36-bit high-precision multiplier■Hardcoded adders, subtractors, accumulators, and summation functions■Fully-integrated design flow with the MATLAB and DSP Builder softwarefrom Altera■Maximum system bandwidth■Up to 24 full-duplex clock data recovery (CDR)-based transceivers supportingrates between 600Mbps and 6.375Gbps■Dedicated circuitry to support physical layer functionality for popular serialprotocols, including PCIe Gen1 and PCIe Gen2, Gbps Ethernet, SerialRapidIO® (SRIO), Common Public Radio Interface (CPRI), OBSAI,SD/HD/3G/ASI Serial Digital Interface (SDI), XAUI and Reduced XAUI(RXAUI), HiGig/HiGig+, SATA/Serial Attached SCSI (SAS), GPON,SerialLite II, Fiber Channel, SONET/SDH, Interlaken, Serial Data Converter(JESD204), and SFI-5.Table1–2 and Table1–3 list the Arria II device package options and user I/O pincounts, high-speed LVDS channel counts, and transceiver channel counts for UltraFineLine BGA (UBGA) and FineLine BGA (FBGA) devices.Table1–2.Package Options and I/O Information for Arria II GX Devices(Note1), (2),(3), (4), (5), (6), (7)Device358-Pin Flip Chip UBGA17 mm x 17 mm572-Pin Flip Chip FBGA25 mm x 25 mm780-Pin Flip Chip FBGA29 mm x 29 mm1152-Pin Flip Chip FBGA35 mm x 35 mmI/O LVDS (8)XCVRsI/O LVDS (8)XCVRsI/O LVDS (8)XCVRsI/O LVDS (8)XCVRsEP2AGX4515633(R D or eTX)+32(RX, TX,or eTX)425257(R D oreTX) +56(RX, TX,or eTX)836485(R D or eTX)+84(RX, TX,or eTX)8———EP2AGX6515633(R D or eTX)+32(RX, TX,or eTX)425257(R D oreTX) +56(RX, TX,or eTX)836485(R D or eTX)+84(RX,TX,eTX)8———EP2AGX95———26057(R D oreTX) +56(RX, TX,or eTX)837285(R D or eTX)+84(RX, TX, oreTX)12452105(R D oreTX) +104(RX, TX, oreTX)12EP2AGX125———26057(R D oreTX) +56(RX,TX, oreTX)837285(R D or eTX)+84(RX,TX, oreTX)12452105(R D oreTX) +104(RX, TX, oreTX)12EP2AGX190——————37285(R D or eTX)+84(RX, TX, oreTX)12612145(R D oreTX) +144(RX, TX, oreTX)16EP2AGX260——————37285(R D, eTX)+84(RX, TX, oreTX)12612145(R D, eTX) +144(RX, TX, oreTX)16Notes to Table1–2:(1)The user I/O counts include clock pins.(2)The arrows indicate packages vertical migration capability. Vertical migration allows you to migrate to devices whose dedicated pins, configuration pins,and power pins are the same for a given package across device densities.(3)R D = True LVDS input buffers with on-chip differential termination (R D OCT) support.(4)RX = True LVDS input buffers without R D OCT support.(5)TX = True LVDS output buffers.(6)eTX = Emulated-LVDS output buffers, either LVDS_E_3R or LVDS_E_1R.(7)The LVDS channel count does not include dedicated clock input pins and PLL clock output pins.(8)These numbers represent the accumulated LVDS channels supported in Arria II GX row and column I/O banks.Chapter 1:Overview for the Arria II Device Family Arria II Device FeatureTable 1–3.Package Options and I/O Information for Arria II GZ Devices(Note 1),(2), (3), (4), (5)Device780-Pin Flip Chip FBGA29 mm x 29 mm1152-Pin Flip Chip FBGA35 mm x 35 mm1517-Pin Flip Chip FBGA40 mm x 40 mmI/OLVDS (6)X C V R sI/O LVDS (7)X C V R sI/O LVDS (7)X C V R s EP2AGZ225———554135 (RX or eTX) + 140 (TX or eTX)16734179 (RX or eTX) + 184 (TX or eTX)24EP2AGZ30028168 (RX or eTX) +72 eTX 16554135 (RX or eTX) + 140 (TX or eTX)16734179 (RX or eTX) + 184 (TX or eTX)24EP2AGZ35028168 (RX or eTX) +72 eTX16554135 (RX or eTX) + 140 (TX or eTX)16734179 (RX or eTX) + 184 (TX or eTX)24Chapter 1:Overview for the Arria II Device FamilyArria II Device ArchitectureArria II Device ArchitectureArria II devices include a customer-defined feature set optimized for cost-sensitiveapplications and offer a wide range of density, memory, embedded multiplier, I/O,and packaging options. Arria II devices support external memory interfaces and I/Oprotocols required by wireless, wireline, broadcast, computer, storage, and militarymarkets. They inherit the 8-input ALM, M9K and M144K embedded RAM block, andhigh-performance DSP blocks from the Stratix® IV device family with acost-optimized I/O cell and a transceiver optimized for 6.375Gbps speeds.Figure1–1 and Figure1–2 show an overview of the Arria II GX and Arria II GZ devicearchitecture, respectively.Figure1–1.Architecture Overview for Arria II GX Devices。

FPGA可编程逻辑器件芯片EP2AGX95DF25C3N中文规格书

The data toggle state can be switched from its current state by writing to the appropriate USB_EPn_TXCSR_H or USB_EPn_RXCSR_H register to set the data toggle write enable and data toggle bits that are included inthese registers when the core is in host mode.Data toggle write enable and data toggle bits are also included in the USB_EP0_CSRn_H register. However, control operations carried out through the core’s Endpoint 0 should normally always leave the data toggle in the expected state.Where control packets are handled through an endpoint other than Endpoint 0, programs need to prompt for each setup token to be sent. This involves setting the USB_EPn_TXCSR_H.SETUPPKT bit when the core is operating in host mode, alongside the USB_EPn_TXCSR_H.TXPKTRDY bit. If the USB_EPn_TXCSR_H.SETUPPKT bit is not set, an OUT token is sent.Overall, the recommendation is to use the controller’s Endpoint 0 to handle control packets for all of the devices attached to the controller, and to switch the allocation of this endpoint as appropriate. Sending the correct token is ensured, as is ensuring that the data toggle is correctly set for this endpoint.Using a different endpoint for this function is possible, as described above, but there are further points to note:•The control function must be allocated to an Rx/Tx endpoint pair (with the same endpoint number).•The chosen endpoints must each be associated with FIFOs that can accommodate the packet size asso-ciated with EP0 transactions at the chosen operating speed which can be a minimum of 8 bytes for low- or full-speed transactions but 64 bytes for high-speed transactions.Multi-Point Bandwidth ConsiderationsThe ability of a multi-point system to cope with isochronous transactions, in particular, is determined by the available bandwidth.Once an endpoint has been set up, all scheduling is handled in hardware. However, as with PC-based EHCI/OHCI/UHCI hosts, before opening a periodic pipe (for use by isochronous or interrupt traffic), software must determine that there is sufficient bandwidth available.Further, if the periodic pipe is opened to a full-speed device through a high-speed hub, software must confirm that sufficient bandwidth is available both on the local high-speed bus and the full-speed bus generated by the transaction translator in the hub. The bandwidth required for different transactions can be determined using similar algorithms to those used in connection with PC-based hosts (detailed inSection 5.11.3 of the USB 2.0 Specification).Note that the available bandwidth is greater where the hub used supports multiple transaction translators. Babble InterruptIf the bus is still active at the end of a frame, the USB controller assumes that the function it is connected to has malfunctioned, suspends all transactions, and generates a babble interrupt (USB_IRQ.RSTBABBLE).The USB controller does not start a transaction until the bus is inactive for at least the minimumIRQ.SUSPEND interrupt has been enabled, an interrupt is generated at this time. The USB_IRQ.SUSPENDoutput also goes low (if enabled).At this point, the POWERDWN signal is also asserted to indicate that the application may save power by stopping USB_CLKIn. POWERDWN then remains asserted until either power is removed from the bus (indicating that the device has been disconnected) or resume signaling or reset signaling is detected on the bus.2.When resume signaling occurs on the bus, the USB_CLKIn must be restarted if necessary. The USBcontroller then automatically exits suspend mode. If the USB_IRQ.RESUME interrupt is enabled, aninterrupt is generated.3.Initiating a remote wakeup. To initiate a remote wakeup while the controller is in suspend mode, setthe USB_POWER.RESUME bit=1. (Note: If USB_CLKIn has been stopped, it will need to be restarted beforethis write can occur.) The software should leave then this bit set for approximately 10 ms (minimum of2 ms, a maximum of 15 ms) before resetting it to 0. By this time the hub should have taken over drivingResume signaling on the USB.NOTE:The USB_IRQ.RESUME interrupt is not generated when the software initiates a remote wakeup.NOTE:Suspend/Resume By Inactivity On The USB Bus (L0 To L2 State) In Host ModeThe following steps occur in this mode.1.Entry into suspend mode. When operating as a host, the USB controller can be prompted to go intosuspend mode by setting the USB_POWER.SUSPEND bit. When this bit is set, the USB controllercompletes the current transaction then stops the transaction scheduler and frame counter. No furthertransactions are started and no SOF packets are generated. If the USB_POWER.SUSEN bit is set, theUTMI+ PHY goes into low-power mode when the controller goes into suspend mode and stop USB_CLKIn.2.Sending resume signaling. When the application requires the controller to leave suspend mode, it clearsthe USB_POWER.SUSPEND bit, sets the USB_POWER.RESUME bit and leaves it set for 20 ms. While the USB_ POWER.RESUME bit is high, the controller generates Resume signaling on the bus. After 20 ms, theprocessor core should clear the USB_POWER.RESUME bit, at which point the frame counter and transac-tion scheduler are started.3.Responding to remote wake-up. If resume signaling is detected from the target while the USBcontroller is in suspend mode, the UTMI+ PHY is brought out of low-power mode and restart USB_CLKIn. The controller then exits suspend mode and automatically sets the USB_POWER.RESUME bit to 1to take over generating the resume signaling from the target. If the USB_IRQ.RESUME interrupt isenabled, an interrupt is generated.U NIVERSAL S ERIAL B US (USB)USB E VENT C ONTROL•After three attempts at receiving a packet and no data packet is received (host mode).Interrupts can be generated from the USB status (USB_IRQ) under the following conditions:•When VBUS drops below the VBUS valid threshold during a session (A device only).•When SRP signaling is detected (A device only).•When device disconnect is detected (host mode).•When a session ends (peripheral mode).•Device connection detected (host mode).•Start-of-frame (SOF)•Reset signaling detected on USB (peripheral mode).•Babble detected (host mode).•In suspend mode when resume signaling detected on USB.•When suspend signaling is detected (peripheral mode).Interrupts are generated for the following VBUS control requests by the USB controller:•drive VBUS greater than 4.4 V (default A device)•stop driving VBUS•start charging VBUS (peripheral mode)•stop charging VBUS•start discharging VBUS (peripheral mode)•stop discharging VBUSInterrupt HandlingWhen the processor core is interrupted with a USB interrupt, it needs to read the interrupt status register to determine which endpoint(s) have caused the interrupt and jump to the appropriate routine. If multiple endpoints have caused the interrupt, Endpoint 0 should be serviced first, followed by the other endpoints.A flowchart for the USB interrupt service routine is shown in the USB Interrupt Service Routine figure.。

FPGA可编程逻辑器件芯片5SGXEA7K2F35I3LN中文规格书