MEMORY存储芯片STM32F103C8T6中文规格书

stm32f103c8t6的数据手册

《STM32F103C8T6的数据手册》一、概述STM32F103C8T6是ST公司生产的32位ARM Cortex-M3内核的微控制器,具有丰富的外设接口和强大的性能,广泛应用于工业控制、自动化设备、消费类电子产品等领域。

本文旨在对STM32F103C8T6的数据手册进行全面的介绍,帮助读者更好地理解和应用这款微控制器。

二、概览1. 器件简介STM32F103C8T6是一款高性能、低功耗的微控制器,拥有72MHz 工作频率,64KB Flash存储器和20KB RAM。

其丰富的外设接口包括多个通用定时器、串行通信接口、模拟-数字转换器等,适用于各种复杂的应用场景。

2. 功能特性STM32F103C8T6的主要功能特性包括:- ARM Cortex-M3内核- 64KB Flash存储器、20KB RAM- 丰富的外设接口:通用定时器、串行通信接口、模拟-数字转换器等- 低功耗模式:多种低功耗模式可选,满足不同需求3. 应用领域STM32F103C8T6广泛应用于工业控制、自动化设备、消费类电子产品等领域,如工业控制器、电源管理系统、医疗设备等。

三、详细规格1. 通用定时器STM32F103C8T6内置了多个通用定时器,可用于生成精准的定时脉冲,计数器和PWM输出等功能。

2. 串行通信接口该微控制器支持多种串行通信接口,包括SPI、I2C和USART,可用于与外部设备进行高速数据传输。

3. 模拟-数字转换器STM32F103C8T6配备了多个模拟-数字转换器,可实现精确的模拟信号采集和处理。

4. 中断控制器中断控制器可实现对各种外部事件的响应,提高系统的实时性和稳定性。

5. 时钟控制时钟控制模块支持多种时钟源和分频设置,可满足不同应用场景的时序要求。

6. 低功耗模式STM32F103C8T6支持多种低功耗模式,包括待机模式、休眠模式和停止模式,有效降低系统功耗,延长电池寿命。

7. 引脚定义STM32F103C8T6具有多种引脚,可供用户定义为输入/输出口,用于连接外部设备和传感器。

stm32f103c8t6中文手册

stm32f103c8t6中文手册STM32F103系列微处理器,STM32F103器件* * STM32F103 * * Cortex-M3内核,CPU速度为72 MHz,最大闪存为1 MB。

包括电机控制外设和USB全速接口。

STM32系列臂式Cortex-M3 32位闪存微控制器具有低功耗,低电压,出色的性能和实时功能。

包类型系列适用于您的嵌入式应用程序。

MCU体系结构具有易于使用的STM32平台,适用于包括电机驱动,PC和游戏,HVAC以及工业应用在内的应用。

32位RISC引脚对引脚软件兼容的SRAM 高达96 KB 闪存高达1MB电源:2 V至3.6 V温度范围:-40至+ 85°C或-40至+ 105°C?stm32f1系列32位臂?皮质?-M3微控制器,意法半导体的STM32闪存微控制器。

STM32系列是基于ARM cortex Gamma M3的核心突破-嵌入式应用程序特殊开发的核心。

STM32系列受益于对Cortex-M3体系结构的增强,其中包括thumb-2指令集,该指令集提供了更高的性能,更好的编码密度,更快的中断响应以及所有领先的工业功耗。

出色的实时性能,出色的效率和新的外围设备,最大限度地提高了串行引脚,外围设备和软件兼容性之间的集成Stm32f103c8t6是中密度性能线,配备了Arm Cortex-M3 32位微控制器和48通道LQFP 封装。

它结合了高性能RISC内核,72MHz的工作频率,高速嵌入式存储器,增强的I / O范围以及与两条APB总线的外部连接。

Stm32f103c8t6具有12位ADC,计时器,PWM计时器,标准和高级通信接口。

全面的省电模式使设计人员能够设计低功耗应用。

工作电压范围:2V至3.6v.64k字节闪存。

20K字节SRAM.CRC 计算单元,96位唯一ID。

两个12位,1μs ADC(最多10个通道)。

7通道DMA控制器,3个通用定时器和1个高级控制定时器。

基于STM单片机STM32F103CBT6应用方案-奥伟斯

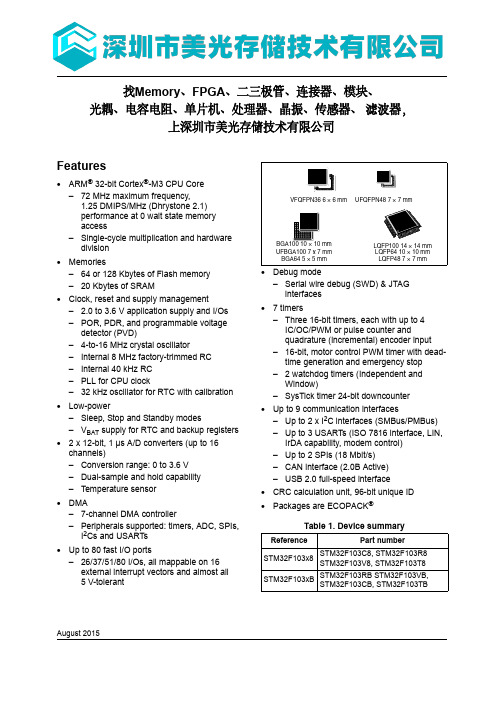

奥伟斯科技为您提供STM单片机STM32F103CBT6应用参考设计方案●内容导航:●公司简介●STM32F103CBT6产品规格书●产品图片●优势产品简介STM32F103C8T6基于ARM的32位MCU,带闪存,USB,CAN,7个16位定时器,2个ADC和9个通信接口-奥伟斯科技STM32F103C8T6特征■内核:ARM 32位Cortex™-M3 CPU- 72 MHz,90 DMIPS,1.25 DMIPS / MHz- 单周期乘法和硬件师- 带有43的嵌套中断控制器可屏蔽中断通道- 中断处理(低至6个CPU尾部链接■回忆- 32至128 KB的闪存- 6至20 KB的SRAM■时钟,复位和电源管理- 2.0至3.6 V应用电源和I / O.- POR,PDR和可编程电压探测器(PVD)- 4至16 MHz石英振荡器- 内部8 MHz工厂调整RC- 内部32 kHz RC- 用于CPU时钟的PLL- 用于RTC的专用32 kHz振荡器校准■低功耗- 睡眠,停止和待机模式- 用于RTC和备份寄存器的VBAT电源■2 x 12位,1μsA/ D转换器(16通道)- 转换范围:0至3.6 V.- 双采样和保持功能- 可与高级控制计时器同步- 温度感应器■DMA- 7通道DMA控制器- 支持外设:定时器,ADC,SPI,I2Cs和USART■调试模式- 串行线调试(SWD)和JTAG接口■最多80个快速I / O端口- 32/49/80 5个V容错I / O.- 全部可映射16个外部中断矢量- 原子读/修改/写操作■最多7个计时器- 最多三个16位定时器,每个定时器最多4个IC / OC / PWM或脉冲计数器- 16位,6通道高级控制定时器:PWM输出最多6个通道死时间的产生和紧急情况停- 2个16位看门狗定时器(独立和窗口)- SysTick计时器:一个24位的向下计数器■最多9个通信接口- 最多2个I2C接口(SMBus / PMBus)- 最多3个USART(ISO 7816接口,LIN,IrDA功能,调制解调器控制)- 最多2个SPI(18 Mbit / s)- CAN接口(2.0B有源)- USB 2.0全速接口STM32F103系列订购型号:STM32F103C6T6 STM32F103R6T6 STM32F103C8T6 STM32F103R8T6 STM32F103V8T6STM32F103RBT6 STM32F103VBT6公司简介深圳市奥伟斯科技有限公司是一家专注触摸芯片,单片机,电源管理芯片,语音芯片,场效应管,显示驱动芯片,网络接收芯片,运算放大器,红外线接收头及其它半导体产品的研发,代理销售推广的高新技术企业.奥伟斯科技自成立以来一直致力于新半导体产品在国内的推广与销售,年销售额超过壹亿人民币是一家具有综合竞争优势的专业电子元器件代理商.本公司代理推广的一系列优秀触摸芯片及语音芯片,现以大批量应用到智能电子锁、饮水机、电饭煲、LED台灯等控制器为顾客提供最佳解决方案,受到广大客户的一致赞誉。

stm32f103c8t6中文参数

stm32f103c8t6中文参数1.简介本文档将介绍ST M32F103C8T6微控制器的中文参数。

S T M32F103C8T6是一款基于AR MC or tex-M3内核的高性能微控制器,具有丰富的外设和低功耗特性。

本文将详细介绍其主要技术参数和特性。

2.技术参数S T M32F103C8T6的主要技术参数如下:-核心:AR M32位Cor t ex-M3C PU-频率:最高工作频率为72MH z-存储器:64K BF la sh存储器,20K BR AM-时钟:内部高精度8M Hz RC振荡器,外部时钟输入支持-通信接口:2个SP I接口,3个I2C接口,2个UA RT接口,1个U S B接口-A DC:12位模数转换器,最多16个通道-P WM:16路输出-G PI O:最多37个通用I/O引脚-供电电压:3.3V3.特性3.1高性能S T M32F103C8T6的A R MC or te x-M3处理器提供高性能的计算能力和快速响应速度。

其最高工作频率为72M Hz,可以满足大部分应用的需求。

3.2丰富的外设该微控制器配备了多种外设,包括SP I、I2C、UA RT和U SB接口,可以方便地与其他设备进行通信。

同时,内部集成了12位模数转换器,可以实现精确的模拟信号采集。

3.3低功耗特性S T M32F103C8T6具备低功耗特性,可满足对功耗敏感的应用需求。

其内部集成了8MH zR C振荡器,可以有效减少功耗,并支持外部时钟输入。

3.4强大的G P I O该微控制器拥有最多37个通用I/O引脚,可以灵活地实现各种输入输出功能。

G PI O引脚具备多种工作模式和中断功能,适用于各种应用场景。

4.应用领域由于ST M32F103C8T6具备高性能、丰富的外设和低功耗特性,它在各种领域都有广泛的应用,包括但不限于:-工业自动化控制系统-智能家居系统-医疗仪器设备-汽车电子控制系统-智能电源管理系统-物联网终端设备5.总结本文对S TM32F103C8T6微控制器的中文参数进行了详细介绍。

STM32F051C8T6开发板用户手册说明书

Open051C User ManualContentsOPEN051C USER MANUAL (1)1.OVERVIEW (2)1.1.W HAT’S ON BOARD (2)2.DEMO (4)2.1.8I OS (5)2.2.ADC+DMA (5)2.3.DAC+DMA (6)2.4.GPIO_LED (7)2.5.GPIO_LED_KEY (7)2.6.I2C (7)2.7.I2S UDA1380&SD_FATFS (8)2.8.JOYSTICK (8)2.9.LCD22 (8)2.10.LCD22-T OUCH (9)2.11.FATFS V0.08A-SD C ARD (10)2.12.NRF24L01 (10)2.13.O NE-W IRE (11)2.14.PS2 (11)2.15.RTC (12)2.16.SPI (12)2.17.U COS II (13)ART (13)3.REVISION HISTORY (14)1. Overview 1.1. What’s on board[ MCU ]1. STM32F051C8T6the high performance STM32 MCU which features:Core:Cortex-M0 32-bit RISC;Operating Frequency:48MHz;Operating Voltage:2-3.6V;Package:LQFP48;I/Os: 39;Memories:64KB Flash, 8kB RAM;Communication Interfaces: 2 x SPI, 2 x USART, 2 x I2C, 1 x I2S;[ Component ]3. Power supply switch5V DC or USB4. Power indicator5. User LEDfor indicating I/O status6. Reset key7. User LEDfor I/O input and/or interact with running code 8. Joystickfive positionAD & DA converters : 1 x AD (12-bit, 1μs, shares 16 channels);Debugging/Programming : supports SWD (serial wire debug) interfaces, supports IAP2. AMS1117-3.33.3V voltage regulator[ Interface ]11. 8I/Os + DAC + ADC Interfaceeasily connects to keypad, motor, etc. 12. SPI1 / SPI2 interfaceeasily connects to SPI peripherals such as FLASH (AT45DBxx), SD card, MP3, etc.convenient for connecting AD module, thanks to the SPI1 alternative AD function 13. I2C1 / I2C2 interfaceeasily connects to I2C peripherals such as I/O expander (PCF8574), EEPROM (AT24Cxx), etc.14. LCD interfaceeasily connects to the touch screen LCD 15. ONE-WIRE interfaceeasily connects to ONE-WIRE devices (TO-92 package), such as temperature sensor (DS18B20), electronic registration number (DS2401), etc. 16. USART1 interfaceeasily connects to RS232, RS485, USB TO 232 17. USART2 interfaceeasily connects to RS232, RS485, USB TO 232 18. I2S / I2C1 interfaceeasily connects to I2S peripherals such as audio module, etc. 19. PS/2 interfacefor connecting PS/2 keyboard/mouse.9. 32.768K crystal oscillatorused for internal RTC, also supports clock calibration10. 8M crystal oscillatorenables the MCU run at 48M frequency by frequency multiplication[ Other interfaces ]20. 5V DC jack21. 5V/3.3 V power input/outputusually used for power output, or common ground with other user board 22. MCU pins connectorall the MCU pins are accessible on expansion connectors for further expansion 23. SWD interfacefor debugging/programming[Jumper/switch]20. Boot mode selectionfor configuring the BOOT0 pins 21. User key jumpershort the jumper to connect the user key to I/Os used in example codeopen the jumper to connect the user key to other custom pins via jumper wires 22. Joystick jumpershort the jumper to connect the joystick to I/Os used in example codeopen the jumper to connect the joystick to other custom pins via jumper wires 23. PS/2 interface jumperI/O ;short the jumper to connect the PS/2 interface to I/Os used in example codeopen the jumper to connect the PS/2 interface to other custom pins via jumper wires 24. VBAT selection jumpershort the jumper to use system power supply open the jumper to connect the VBAT to external power, such as battery2. DemoKEIL MDK Version:4.54Programmer/Debugger: ULINK/V2Programming/Debugging interface: SWD Serial port settings:Select a proper COM portBaud rate 115200Data bits 8Stop bits 1Parity bits NoneFlow control None2.1. 8Ios◆ Overview8bit I/Os demo◆ Hardware connectionConnect the board to 5V power via 5VDCinterfaceConnect the ULINK board to the board via SWDinterfaceConnect the 8 Push Button to the board via8I/Os+DAC+DAC interface (The G pin on the module connect to the GND pin on the board) USART1 Connect a serial portconverter(RS232) to the board via UART1 interface◆ Operation and resultThe below information will be printed on the serial debugging assistant:2.2. ADC+DMA◆ OverviewADC analog voltage acquisition demo◆Hardware connectionConnect the board to 5V power via 5VDCinterfaceConnect the ULINK2 board to the board viaSWD interfaceConnect a serial port converter(RS232) to the board via UART1 interfaceConnect the Analog Test Board to the boardvia 8I/Os+DAC+DAC interface◆ Operation and resultRotate the potentiometer on the Analog Test Board, the below information will be printed on the serialdebugging assistant:2.3. DAC+DMA◆ OverviewDAC demo◆ Hardware connectionConnect the board to 5V power via 5VDCinterfaceConnect the ULINK2 board to the board viaSWD interfaceConnect the Analog Test Board to the board via 8I/Os+DAC+DAC interfaceConnect the 5V pin headers on both the mainboard and the Analog Test Board via jumper wire◆ Operation and resultYou should hear sound from the Analog Test Board.2.4. GPIO_LED◆OverviewGPIO_LED demo◆Operation and resultShort the LED JMP◆Operation and resultThe LED blinking2.5. GPIO_LED _KEY◆OverviewLED, joystick demo◆Hardware connectionShort the LED JMP◆Operation and resultPush the joystick, the LED status should keep changing accordingly.2.6. I2C◆OverviewI2C EEPROM demo◆Hardware connectioninterfaceConnect the ULINK2 board to the board viaSWD interfaceConnect a serial port converter to the boardvia UART1 interfaceConnect the AT24CXX EEPROM Board tothe board via I2CX interface( connect toI2C1 or I2C2 depends on the program)◆Operation and resultThe below information will be printed on the serial debugging assistant:2.7. I2S UDA1380 & SD_FATFS◆ OverviewAudio file placed on SD Card (with FATFS) ◆ Hardware connectionConnect the board to 5V power via 5VDCinterfaceConnect the ULINK2 board to the board viaSWD interfaceConnect the UDA1380 Board to theonboard I2S interfaceConnect an earphone to theUDA1380Board LINEOUT interfaceConnect the Micro SD Storage Board (withSD card) to the onboard SPI2 interfaceConnect the CD pin on the Micro SDStorage Board to the onboard PB0 pin using a jumper wire.◆ Operation and resultThe below information will be printed on the serial debugging assistant:2.8. JOYSTICK◆ OverviewJoystick demo◆ Hardware connectionShort the LED JMP ,JOYSTICK JMP ,KEY JMP . ◆ Operation and resultPush the joystick or the keys, the LED status should keep changing accordingly.2.9. LCD22◆ OverviewLCD demo◆Hardware connectionConnect the board to 5V power via 5VDC interface Connect the ULINK2 board to the board via SWDinterfaceConnect the "2.2inch 320x240 Touch LCD (A)" to theboard.◆ Operation and resultDisplay image on the LCD2.10. LCD22-Touch◆ OverviewLCD demo◆ Hardware connectionConnect the board to 5V power via 5VDC interfaceConnect the ULINK2 board to the board via SWD interface Connect the "2.2inch 320x240 Touch LCD (A)" to the board.◆ Operation and resultDisplay image on the LCDMessage will be displayed on the LCD◆ ApplicationHandheld device display2.11. FATFS V0.08A-SD Card◆ OverviewSD_FatFS demo ◆ Hardware connectionConnect the board to 5V power via 5VDCinterfaceConnect the ULINK2 board to the board viaSWD interfaceConnect a serial port converter to the board viaUART1Connect the Micro SD Storage Board (with SDcard) to the board via SPI2 interfaceConnect the CD pin on the Micro SD StorageBoard to the onboard PB0 pin using a jumper wire.◆ Software configuration ◆ Operation and resultThe below information will be printed on the serial debugging assistant:2.12. NRF24L01◆ OverviewNRF24L01 demo ◆ Hardware connectionConnect the board to 5V power via 5VDCinterfaceConnect the ULINK2 board to the board viaSWD interfaceConnect the ULINK2 board to the board viaSWD interfaceConnect the NRF24L01 Board to the boardvia SPI interface◆ Software configurationDownload the transmitting and receiving program to the two NRF24L01 board respectively. ◆ Operation and resultMessage will be printed on the serial debugging assistant.2.13. One-Wire◆ OverviewOne-wire demo◆ Hardware connectionConnect the board to 5V power via 5VDC interfaceConnect the ULINK2 board to the board via SWD interfaceConnect a serial port converter to the onboard USART1 interface Connect the DS18B20 to the onboard One-wire socket◆ Operation and resultThe below information will be printed on the serial debugging assistant:2.14. PS2◆ OverviewPS2 keyboard demo ◆ Hardware connectionConnect the board to 5V power via 5VDCinterfaceConnect the ULINK2 board to the board viaSWD interfaceConnect the ULINK2 board to the board viaSWD interfaceConnect the PS2 keyboard to the board via PS2interface.Short the PS2 JMP .◆ Operation and resultPress keys on the PS2 keyboard, the related key value will display on the serial debugging assistant:2.15. RTC◆ OverviewRTC demo◆ Hardware connectionConnect the board to 5V power via 5VDC interfaceConnect the ULINK2 board to the board via SWD interface◆ Operation and resultThe below information will be printed on the serial debugging assistant:2.16. SPI◆ OverviewSPI demo◆ Hardware connectionConnect the board to 5V power via 5VDC interface Connect the ULINK2 board to the board via SWDinterfaceConnect the "AT45DBXX DataFlash Board" to theonboard SPIX interface (connect to SPI1 or SPI2 depends on the program)Connect a serial port converter to the onboardUSART1 interface◆ Software connectionSoftware configuration:Launch the serial debugging assistant SSCOM32, choose related COM port, set baud rate as 115200, click to open it.◆Operation and resultThe below information will be printed on the serial debugging assistant: Array2.17. Ucos II◆OverviewUcos ii demo◆Hardware connectionConnect the board to 5V power via 5VDCinterfaceConnect the board to 5V power via 5VDCinterfaceShort the LED jumper◆Operation and resultThe two LED blinking in different frequency.2.18. USART◆OverviewUSART demo◆Hardware connectionConnect the board to 5V power via 5VDC interfaceConnect the board to 5V power via 5VDC interfaceConnect a serial port converter to the onboard USARTX interface (connect to USART1 or USART2 depends on the program)◆Operation and resultThe below information will be printed on the serial debugging assistant:3. Revision historyVersion Description Date AuthorV1.0 Initial revision 2014/05/17 Waveshare team。

MEMORY存储芯片STM32F051K8T6中文规格书

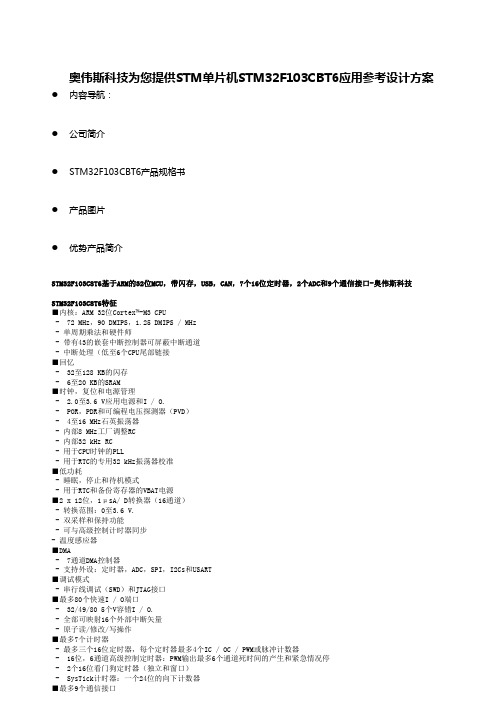

ARM®-based 32-bit MCU, 16 to 64 KB Flash, 11 timers, ADC, DAC and communication interfaces, 2.0-3.6 VDatasheet - production dataFeatures•Core: ARM® 32-bit Cortex®-M0 CPU, frequency up to 48 MHz•Memories–16 to 64 Kbytes of Flash memory–8 Kbytes of SRAM with HW parity checking •CRC calculation unit•Reset and power management–Digital and I/O supply: V DD = 2.0 V to 3.6 V –Analog supply: V DDA = from V DD to 3.6 V–Power-on/Power down reset (POR/PDR)–Programmable voltage detector (PVD)–Low power modes: Sleep, Stop, Standby–V BAT supply for RTC and backup registers •Clock management– 4 to 32 MHz crystal oscillator–32 kHz oscillator for RTC with calibration–Internal 8 MHz RC with x6 PLL option–Internal 40 kHz RC oscillator•Up to 55 fast I/Os–All mappable on external interrupt vectors –Up to 36 I/Os with 5 V tolerant capability •5-channel DMA controller•One 12-bit, 1.0 µs ADC (up to 16 channels)–Conversion range: 0 to 3.6 V–Separate analog supply from 2.4 up to 3.6•One 12-bit DAC channel•Two fast low-power analog comparators with programmable input and output•Up to 18 capacitive sensing channels supporting touchkey, linear and rotary touchsensors•Up to 11 timers–One 16-bit 7-channel advanced-control timer for 6 channels PWM output, withdeadtime generation and emergency stop –One 32-bit and one 16-bit timer, with up to4 IC/OC, usable for IR control decodingdeadtime generation and emergency stop –Two 16-bit timers, each with IC/OC and OCN, deadtime generation, emergencystop and modulator gate for IR control –One 16-bit timer with 1 IC/OC–Independent and system watchdog timers –SysTick timer: 24-bit downcounter–One 16-bit basic timer to drive the DAC •Calendar RTC with alarm and periodic wakeupfrom Stop/Standby•Communication interfaces–Up to two I2C interfaces, one supporting Fast Mode Plus (1 Mbit/s) with 20 mAcurrent sink, SMBus/PMBus and wakeupfrom Stop mode–Up to two USARTs supporting master synchronous SPI and modem control, onewith ISO7816 interface, LIN, IrDAcapability, auto baud rate detection andwakeup feature–Up to two SPIs (18 Mbit/s) with 4 to 16 programmable bit frame, one with I2Sinterface multiplexed•HDMI CEC interface, wakeup on header reception•Serial wire debug (SWD)•96-bit unique ID•All packages ECOPACK®2Table 1. Device summaryReference Part numberSTM32F051xx STM32F051C4, STM32F051K4, STM32F051R4 STM32F051C6, STM32F051K6, STM32F051R6 STM32F051C8, STM32F051K8, STM32F051R8, STM32F051T8January 2017DocID022265 Rev 7Functional overview STM32F051x4 STM32F051x6 STM32F051x8DocID022265 Rev 7sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.The ADC can be served by the DMA controller.An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.3.10.1 Temperature sensorThe temperature sensor (TS) generates a voltage V SENSE that varies linearly withtemperature.The temperature sensor is internally connected to the ADC_IN16 input channel which is used to convert the sensor output voltage into a digital value.The sensor provides good linearity but it has to be calibrated to obtain good overallaccuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.To improve the accuracy of the temperature sensor measurement, each device isindividually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.3.10.2Internal voltage reference (V REFINT )The internal voltage reference (V REFINT ) provides a stable (bandgap) voltage output for the ADC and comparators. V REFINT is internally connected to the ADC_IN17 input channel. The precise voltage of V REFINT is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.Table 3. Temperature sensor calibration valuesCalibration value nameDescriptionMemory address TS_CAL1TS ADC raw data acquired at a temperature of 30 °C (± 5 °C), V DDA = 3.3 V (± 10 mV)0x1FFF F7B8 - 0x1FFF F7B9TS_CAL2TS ADC raw data acquired at a temperature of 110 °C (± 5 °C), V DDA = 3.3 V (± 10 mV)0x1FFF F7C2 - 0x1FFF F7C3Table 4. Internal voltage reference calibration valuesCalibration value nameDescriptionMemory address VREFINT_CALRaw data acquired at atemperature of 30 °C (± 5 °C), V DDA = 3.3 V (± 10 mV)0x1FFF F7BA - 0x1FFF F7BBSTM32F051x4 STM32F051x6 STM32F051x8Functional overview 3.10.3 V BAT battery voltage monitoringThis embedded hardware feature allows the application to measure the V BAT battery voltageusing the internal ADC channel ADC_IN18. As the V BAT voltage may be higher than V DDA,and thus outside the ADC input range, the V BAT pin is internally connected to a bridgedivider by 2. As a consequence, the converted digital value is half the V BAT voltage.(DAC)converter3.11 Digital-to-analogThe 12-bit buffered DAC channels can be used to convert digital signals into analog voltagesignal outputs. The chosen design structure is composed of integrated resistor strings andan amplifier in non-inverting configuration.This digital Interface supports the following features:•Left or right data alignment in 12-bit mode•Synchronized update capability•DMA capability•External triggers for conversionFive DAC trigger inputs are used in the device. The DAC is triggered through the timertrigger outputs and the DAC interface is generating its own DMA requests.(COMP)3.12 ComparatorsThe device embeds two fast rail-to-rail low-power comparators with programmablereference voltage (internal or external), hysteresis and speed (low speed for low power) andwith selectable output polarity.The reference voltage can be one of the following:•External I/O•DAC output pins•Internal reference voltage or submultiple (1/4, 1/2, 3/4).Refer to Table 24: Embedded internal reference voltage for the value and precision of the internal reference voltage.Both comparators can wake up from STOP mode, generate interrupts and breaks for thetimers and can be also combined into a window comparator.3.13 Touch sensing controller (TSC)The STM32F051xx devices provide a simple solution for adding capacitive sensingfunctionality to any application. These devices offer up to 18 capacitive sensing channelsdistributed over 6 analog I/O groups.Capacitive sensing technology is able to detect the presence of a finger near a sensor whichis protected from direct touch by a dielectric (glass, plastic...). The capacitive variationintroduced by the finger (or any conductive object) is measured using a provenimplementation based on a surface charge transfer acquisition principle. It consists incharging the sensor capacitance and then transferring a part of the accumulated chargesinto a sampling capacitor until the voltage across this capacitor has reached a specificthreshold. To limit the CPU bandwidth usage, this acquisition is directly managed by theDocID022265 Rev 7Functional overview STM32F051x4 STM32F051x6 STM32F051x8DocID022265 Rev 7hardware touch sensing controller and only requires few external components to operate. For operation, one capacitive sensing GPIO in each group is connected to an external capacitor and cannot be used as effective touch sensing channel.The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.Table 5. Capacitive sensing GPIOs available on STM32F051xx devicesGroupCapacitive sensingsignal name Pin name GroupCapacitive sensingsignal name Pin name 1TSC_G1_IO1PA04TSC_G4_IO1PA9TSC_G1_IO2PA1TSC_G4_IO2PA10TSC_G1_IO3PA2TSC_G4_IO3PA11TSC_G1_IO4PA3TSC_G4_IO4PA122TSC_G2_IO1PA45TSC_G5_IO1PB3TSC_G2_IO2PA5TSC_G5_IO2PB4TSC_G2_IO3PA6TSC_G5_IO3PB6TSC_G2_IO4PA7TSC_G5_IO4PB73TSC_G3_IO1PC56TSC_G6_IO1PB11TSC_G3_IO2PB0TSC_G6_IO2PB12TSC_G3_IO3PB1TSC_G6_IO3PB13TSC_G3_IO4PB2TSC_G6_IO4PB14Table 6. Effective number of capacitive sensing channels on STM32F051xxAnalog I/O groupNumber of capacitive sensing channelsSTM32F051RxSTM32F051CxSTM32F051TxSTM32F051KxU (UFQFPN32)STM32F051KxT (LQFP32)G133333G233333G332221G433333G533333G633000Number of capacitive sensing channels1817141413DocID022265 Rev 7STM32F051x4 STM32F051x6 STM32F051x8Functional overviewTable 7. Timer feature comparisonTimer typeTimerCounter resolution Counter typePrescaler factorDMA request generationCapture/compare channels ComplementaryoutputsAdvancedcontrol TIM116-bitUp, down, up/down integer from 1 to 65536Yes 43General purposeTIM2 32-bit Up, down, up/down integer from 1 to 65536Yes 4- TIM316-bit Up, down, up/down integer from 1 to 65536Yes 4-TIM1416-bit Up integer from1 to 65536No 1-TIM1516-bit Up integer from 1 to 65536Yes 21TIM16TIM1716-bit Up integer from 1 to 65536Yes 11BasicTIM616-bitUpinteger from 1 to 65536Yes--。

MEMORY存储芯片STM32F373C8T6中文规格书

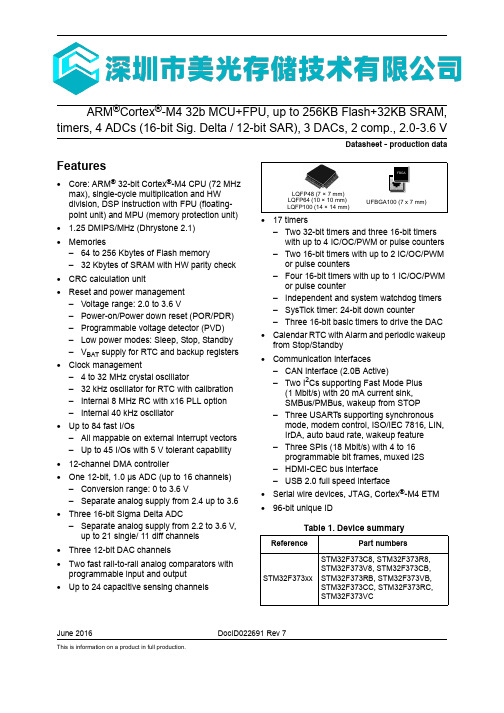

This is information on a product in full production.June 2016DocID022691 Rev 7ARM ®Cortex ®-M4 32b MCU+FPU, up to 256KB Flash+32KB SRAM,timers, 4 ADCs (16-bit Sig. Delta / 12-bit SAR), 3 DACs, 2 comp., 2.0-3.6 VDatasheet - production dataFeatures•Core: ARM ® 32-bit Cortex ®-M4 CPU (72 MHz max), single-cycle multiplication and HW division, DSP instruction with FPU (floating-point unit) and MPU (memory protection unit)• 1.25 DMIPS/MHz (Dhrystone 2.1)•Memories–64 to 256Kbytes of Flash memory–32Kbytes of SRAM with HW parity check •CRC calculation unit•Reset and power management –Voltage range: 2.0 to 3.6V–Power-on/Power down reset (POR/PDR)–Programmable voltage detector (PVD)–Low power modes: Sleep, Stop, Standby –V BAT supply for RTC and backup registers •Clock management– 4 to 32MHz crystal oscillator–32kHz oscillator for RTC with calibration –Internal 8MHz RC with x16 PLL option –Internal 40kHz oscillator •Up to 84 fast I/Os–All mappable on external interrupt vectors –Up to 45 I/Os with 5 V tolerant capability •12-channel DMA controller•One 12-bit, 1.0 µs ADC (up to 16 channels)–Conversion range: 0 to 3.6 V–Separate analog supply from 2.4 up to 3.6•Three 16-bit Sigma Delta ADC–Separate analog supply from 2.2 to 3.6 V,up to 21 single/ 11 diff channels •Three 12-bit DAC channels•Two fast rail-to-rail analog comparators with programmable input and output •Up to 24 capacitive sensing channels•17 timers–Two 32-bit timers and three 16-bit timers with up to 4 IC/OC/PWM or pulse counters –Two 16-bit timers with up to 2 IC/OC/PWM or pulse counters–Four 16-bit timers with up to 1 IC/OC/PWM or pulse counter–Independent and system watchdog timers –SysTick timer: 24-bit down counter–Three 16-bit basic timers to drive the DAC •Calendar RTC with Alarm and periodic wakeup from Stop/Standby •Communication interfaces–CAN interface (2.0B Active)–Two I 2Cs supporting Fast Mode Plus (1Mbit/s) with 20 mA current sink,SMBus/PMBus, wakeup from STOP –Three USARTs supporting synchronous mode, modem control, ISO/IEC 7816, LIN,IrDA, auto baud rate, wakeup feature –Three SPIs (18 Mbit/s) with 4 to 16programmable bit frames, muxed I2S –HDMI-CEC bus interface –USB 2.0 full speed interface •Serial wire devices, JTAG, Cortex ®-M4 ETM •96-bit unique IDTable 1. Device summaryReferencePart numbersSTM32F373xxSTM32F373C8, STM32F373R8, STM32F373V8, STM32F373CB, STM32F373RB, STM32F373VB,STM32F373CC, STM32F373RC, STM32F373VCLQFP64 (10 × 10 mm)LQFP100 (14 × 14 mm)LQFP48 (7 × 7 mm)STM32F373xxPinouts and pin descriptionDocID022691 Rev 7Pinouts and pin descriptionSTM32F373xxDocID022691 Rev 767D114129PA8I/O FT -SPI2_SCK/I2S2_CK,I2C2_SMBA, USART1_CK, TIM4_ETR, TIM5_CH1_ETR, MCO-68D104230PA9I/O FTf -SPI2_MISO/I2S2_MCK,I2C2_SCL, USART1_TX, TIM2_CH3, TIM15_BKIN,TIM13_CH1, TSC_G4_IO1-69C124331PA10I/O FTf -SPI2_MOSI/I2S2_SD,I2C2_SDA, USART1_RX,TIM2_CH4, TIM17_BKIN, TIM14_CH1, TSC_G4_IO2-70B124432PA11I/O FT -SPI2_NSS/I2S2_WS, SPI1_NSS/I2S1_WS, USART1_CTS, CAN_RX, TIM4_CH1, USB_DM, TIM5_CH2, COMP1_OUT -71A124533PA12I/O FT -SPI1_SCK/I2S1_CK, USART1_RTS, CAN_TX, USB_DP , TIM16_CH1, TIM4_CH2, TIM5_CH3, COMP2_OUT-72A114634PA13I/O FT -SPI1_MISO/I2S1_MCK,USART3_CTS, IR_OUT, TIM16_CH1N, TIM4_CH3,TIM5_CH4, TSC_G4_IO3,SWDIO-JTMS-73C114735PF6I/O FTf -SPI1_MOSI/I2S1_SD,USART3_RTS, TIM4_CH4, I2C2_SCL-74F11--VSS_3S -(2)Ground 75G11--VDD_3S -(2)Digital power supply--4836PF7I/O FTf -I2C2_SDA, USART2_CK -76A104937PA14I/OFTf-I2C1_SDA, TIM12_CH1, TSC_G4_IO4, SWCLK-JTCK-Table 11. STM32F373xx pin definitions (continued)Pin numbersPin name(function after reset)PintypeI /O s t r u c t u r eN o t e sPin functionsL Q F P 100U F B G A 100L Q F P 64L Q F P 48Alternate function Additional functionsDocID022691 Rev 7STM32F373xx Pinouts and pin description77A95038PA15I/O FTf -SPI1_NSS/I2S1_WS, SPI3_NSS/I2S3_WS,I2C1_SCL, TIM2_CH1_ETR, TIM12_CH2, TSC_SYNC, JTDI -78B1151-PC10I/O FT (2)SPI3_SCK/I2S3_CK,USART3_TX, TIM19_CH1-79C1052-PC11I/O FT (2)SPI3_MISO/I2S3_MCK,USART3_RX, TIM19_CH2-80B1053-PC12I/O FT (2)SPI3_MOSI/I2S3_SD,USART3_CK, TIM19_CH3-81C9--PD0I/O FT (2)CAN_RX, TIM19_CH4-82B9--PD1I/O FT (2)CAN_TX, TIM19_ETR -83C854-PD2I/O FT (2)TIM3_ETR-84B8--PD3I/O FT (2)SPI2_MISO/I2S2_MCK,USART2_CTS -85B7--PD4I/O FT (2)SPI2_MOSI/I2S2_SD,USART2_RTS -86A6--PD5I/O FT (2)USART2_TX -87B6--PD6I/O FT (2)SPI2_NSS/I2S2_WS,USART2_RX -88A5--PD7I/OFT(2)SPI2_SCK/I2S2_CK,USART2_CK-89A85539PB3I/O FT -SPI1_SCK/I2S1_CK, SPI3_SCK/I2S3_CK,USART2_TX, TIM2_CH2, TIM3_ETR, TIM4_ETR, TIM13_CH1, TSC_G5_IO1,JTDO-TRACESWO-90A75640PB4I/O FT -SPI1_MISO/I2S1_MCK, SPI3_MISO/I2S3_MCK, USART2_RX, TIM16_CH1, TIM3_CH1, TIM17_BKIN, TIM15_CH1N, TSC_G5_IO2, NJTRST-Table 11. STM32F373xx pin definitions (continued)Pin numbers Pin name(function after reset)PintypeI /O s t r u c t u r eN o t e sPin functionsL Q F P 100U F B G A 100L Q F P 64L Q F P 48Alternate function Additional functionsPinouts and pin descriptionSTM32F373xxDocID022691 Rev 791C55741PB5I/O FT -SPI1_MOSI/I2S1_SD, SPI3_MOSI/I2S3_SD,I2C1_SMBAl, USART2_CK, TIM16_BKIN, TIM3_CH2, TIM17_CH1, TIM19_ETR -92B55842PB6I/O FTf -I2C1_SCL, USART1_TX, TIM16_CH1N, TIM3_CH3, TIM4_CH1, TIM19_CH1, TIM15_CH1, TSC_G5_IO3-93B45943PB7I/O FTf -I2C1_SDA, USART1_RX,TIM17_CH1N, TIM3_CH4, TIM4_CH2, TIM19_CH2, TIM15_CH2, TSC_G5_IO4-94A46044BOOT0I B -Boot memory selection95A36145PB8I/O FTf -SPI2_SCK/I2S2_CK, I2C1_SCL, USART3_TX, CAN_RX, CEC, TIM16_CH1, TIM4_CH3, TIM19_CH3, COMP1_OUT, TSC_SYNC -96B36246PB9I/O FTf -SPI2_NSS/I2S2_WS, I2C1_SDA, USART3_RX, CAN_TX, IR_OUT,TIM17_CH1, TIM4_CH4, TIM19_CH4, COMP2_OUT -97C3--PE0I/O FT (2)USART1_TX, TIM4_ETR -98A2--PE1I/OFT (2)USART1_RX-99D36347VSS_1 S --Ground 100C46448VDD_1S--Digital power supply1.PC13, PC14 and PC15 are supplied through the power switch. Since the switch sinks only a limited amount of current (3 mA), the use of GPIO PC13 to PC15 in output mode is limited:-The speed should not exceed 2 MHz with a maximum load of 30 pF-These GPIOs must not be used as current sources (e.g. to drive an LED)After the first backup domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on thecontent of the Backup registers which is not reset by the main reset. For details on how to manage these GPIOs, refer to the Battery backup domain and BKP register description sections in the RM0313 reference manual.2.When using the small packages (48 and 64 pin packages), the GPIO pins which are not present on these packages, must notbe configured in analog mode.3.these pins are powered by VDDSD12.4.these pins are powered by VDDSD3.Table 11. STM32F373xx pin definitions (continued)Pin numbersPin name(function after reset)PintypeI /O s t r u c t u r eN o t e sPin functionsL Q F P 100U F B G A 100L Q F P 64L Q F P 48Alternate function Additional functions。

MEMORY存储芯片STM32F103ZET6中文规格书

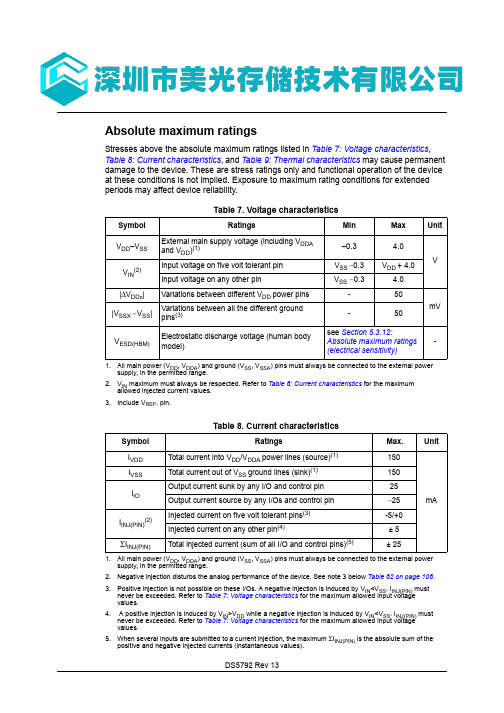

DS5792 Rev 13Absolute maximum ratingsStresses above the absolute maximum ratings listed in Table 7: Voltage characteristics , Table 8: Current characteristics , and Table 9: Thermal characteristics may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.Table 7. Voltage characteristicsSymbol RatingsMin Max UnitV DD –V SS External main supply voltage (including V DDAand V DD)(1)1.All main power (V DD , V DDA ) and ground (V SS , V SSA ) pins must always be connected to the external powersupply, in the permitted range.–0.3 4.0V V IN (2)2.V IN maximum must always be respected. Refer to Table 8: Current characteristics for the maximumallowed injected current values.Input voltage on five volt tolerant pin V SS − 0.3V DD + 4.0 Input voltage on any other pinV SS − 0.34.0|ΔV DDx |Variations between different V DD power pins -50mV |V SSX − V SS |Variations between all the different ground pins (3)3.Include V REF- pin.-50V ESD(HBM)Electrostatic discharge voltage (human body model)see Section 5.3.12:Absolute maximum ratings (electrical sensitivity)-Table 8. Current characteristicsSymbol RatingsMax.UnitI VDD Total current into V DD /V DDA power lines (source)(1)1.All main power (V DD , V DDA ) and ground (V SS , V SSA ) pins must always be connected to the external powersupply, in the permitted range.150mA I VSS Total current out of V SS ground lines (sink)(1)150I IO Output current sunk by any I/O and control pin 25Output current source by any I/Os and control pin − 25I INJ(PIN)(2)2.Negative injection disturbs the analog performance of the device. See note 3 below Table 62 on page 108.Injected current on five volt tolerant pins (3)3.Positive injection is not possible on these I/Os. A negative injection is induced by V IN <V SS . I INJ(PIN) mustnever be exceeded. Refer to Table 7: Voltage characteristics for the maximum allowed input voltage values.-5/+0Injected current on any other pin (4)4.A positive injection is induced by V IN >V DD while a negative injection is induced by V IN <V SS . I INJ(PIN) must never be exceeded. Refer to Table 7: Voltage characteristics for the maximum allowed input voltage values.± 5ΣI INJ(PIN)Total injected current (sum of all I/O and control pins)(5)5.When several inputs are submitted to a current injection, the maximum ΣI INJ(PIN) is the absolute sum of thepositive and negative injected currents (instantaneous values).± 25Electrical characteristics STM32F103xC, STM32F103xD, STM32F103xEDS5792 Rev 135.3 Operating conditions5.3.1General operating conditionsTable 9. Thermal characteristicsSymbol RatingsValue Unit T STG Storage temperature range –65 to +150°C T JMaximum junction temperature150°CTable 10. General operating conditionsSymbol ParameterConditionsMin Max Unitf HCLK Internal AHB clock frequency -0 72MHz f PCLK1Internal APB1 clock frequency -0 36f PCLK2Internal APB2 clock frequency -0 72V DDStandard operating voltage -2 3.6V V DDA (1)1.When the ADC is used, refer to Table 59: ADC characteristics .Analog operating voltage(ADC not used)Must be the same potential as V DD (2)2.It is recommended to power V DD and V DDA from the same source. A maximum difference of 300mVbetween V DD and V DDA can be tolerated during power-up and operation.2 3.6VAnalog operating voltage (ADC used)2.43.6V BATBackup operating voltage- 1.8 3.6V P DPower dissipation at T A = 85°C for suffix 6 or T A = 105°C for suffix 7(3)3.If T A is lower, higher P D values are allowed as long as T J does not exceed T J max (see Table 6.7: Thermalcharacteristics on page 132).LQFP144-666mW LQFP100-434LQFP64-444LFBGA100-500LFBGA144-500WLCSP64-400T AAmbient temperature for 6 suffix versionMaximum power dissipation -4085°C Low-power dissipation (4)4.In low-power dissipation state, T A can be extended to this range as long as T J does not exceed T J max (seeTable 6.7: Thermal characteristics on page 132).-40105Ambient temperature for 7 suffix versionMaximum power dissipation -40105°CLow-power dissipation (4)-40125T JJunction temperature range6 suffix version -40105°C7 suffix version-40125DS5792 Rev 13STM32F103xC, STM32F103xD, STM32F103xE Electrical characteristics5.3.2 Operating conditions at power-up / power-downThe parameters given in Table 11 are derived from tests performed under the ambienttemperature condition summarized in Table 10.5.3.3 Embedded reset and power control block characteristicsThe parameters given in Table 12 are derived from tests performed under ambient temperature and V DD supply voltage conditions summarized in Table 10.Table 11. Operating conditions at power-up / power-downSymbol ParameterConditionsMin Max Unit t VDDV DD rise time rate -0∞µs/VV DD fall time rate20∞Table 12. Embedded reset and power control block characteristicsSymbolParameterConditionsMin Typ Max UnitV PVDProgrammable voltage detector level selection PLS[2:0]=000 (rising edge) 2.1 2.18 2.26V PLS[2:0]=000 (falling edge)2 2.08 2.16PLS[2:0]=001 (rising edge) 2.19 2.28 2.37PLS[2:0]=001 (falling edge) 2.09 2.18 2.27PLS[2:0]=010 (rising edge) 2.28 2.38 2.48PLS[2:0]=010 (falling edge) 2.18 2.28 2.38PLS[2:0]=011 (rising edge)2.38 2.48 2.58PLS[2:0]=011 (falling edge) 2.28 2.38 2.48PLS[2:0]=100 (rising edge)2.47 2.58 2.69PLS[2:0]=100 (falling edge) 2.37 2.48 2.59PLS[2:0]=101 (rising edge) 2.57 2.68 2.79PLS[2:0]=101 (falling edge) 2.47 2.58 2.69PLS[2:0]=110 (rising edge) 2.66 2.78 2.9PLS[2:0]=110 (falling edge) 2.56 2.68 2.8PLS[2:0]=111 (rising edge) 2.76 2.883PLS[2:0]=111 (falling edge)2.66 2.78 2.9V PVDhyst (2)PVD hysteresis--100-mV V POR/PDR Power on/power down reset threshold Falling edge 1.8(1)1.The product behavior is guaranteed by design down to the minimum V POR/PDR value.1.88 1.96V Rising edge 1.84 1.922.0V PDRhyst (2)PDR hysteresis--40-mV T RSTTEMPO (2)2.Guaranteed by design.Reset temporization-12.54.5msElectrical characteristics STM32F103xC, STM32F103xD, STM32F103xEDS5792 Rev 13DS5792 Rev 13STM32F103xC, STM32F103xD, STM32F103xE Electrical characteristicsTable 14. Maximum current consumption in Run mode, code with data processingrunning from FlashSymbolParameterConditionsf HCLK Max (1)1.Guaranteed by characterization results.UnitT A = 85°CT A = 105°CI DDSupply current in Run modeExternal clock (2), all peripherals enabled 2.External clock is 8 MHz and PLL is on when f HCLK > 8 MHz.72 MHz 6970mA48 MHz5050.536 MHz 3939.524 MHz272816 MHz2020.58 MHz 1111.5External clock (2), all peripherals disabled 72 MHz 3737.548 MHz2828.536 MHz 2222.524 MHz16.51716 MHz 12.5138 MHz88Table 15. Maximum current consumption in Run mode, code with data processingrunning from RAMSymbolParameterConditionsf HCLK Max (1)1.Guaranteed by characterization results at V DD max, f HCLK max.UnitT A = 85°CT A = 105°CI DDSupply current in Run modeExternal clock (2), all peripherals enabled 2.External clock is 8 MHz and PLL is on when f HCLK > 8 MHz.72 MHz 6667mA48 MHz43.545.536 MHz 333524 MHz2324.516 MHz16188 MHz 910.5External clock (2), all peripherals disabled 72 MHz 3333.548 MHz2323.536 MHz 1818.524 MHz1313.516 MHz 1010.58 MHz66.5。

stm32f103c8t6中文手册

STM32F103系列微处理器,STM微电子设备**STM32F103**Cortex-M3内核,CPU速度为72MHz,最大闪存为1MB。

包括电机控制外设和USB全速接口。

STM32系列arm型Cortex-M3 32位闪存微控制器具有功耗低、电压低、性能优良、实时性好等特点。

这一系列的包类型可以在您的嵌入式应用程序中使用。

MCU架构具有易于使用的STM32平台,适用于电机驱动、PC和游戏、HVAC和工业应用等应用。

32位RISC针对针软件兼容SRAM高达96 KB闪存高达1MB电源:2 V至3.6 V温度范围:-40至+85°C或-40至+105°C stm32f1系列32位arm?皮质?-m3微控制器,STMicroelectronics(STMicroelectronics)基于arm cortex的32位闪存微控制器STM32系列™M3核心突破了嵌入式应用的特殊开发核心。

STM32系列得益于Cortex-M3体系结构的增强,包括Thumb-2指令集,它可以传递更高的性能、更好的编码密度、更快的中断响应以及所有领先的工业功耗。

卓越的实时性能、卓越的效率和全新的外围设备可以最大限度地实现系列管脚之间的集成、外围设备和软件的兼容性Stm32f103c8t6是一款中密度性能线,配备Arm Cortex-M3 32位微控制器,48路LQFP 封装。

它结合了一个高性能的RISC核心,72MHz工作频率,高速嵌入式存储器,增强的I/O范围和外部连接两个APB总线。

Stm32f103c8t6具有12位模数转换器、定时器、PWM定时器、标准和高级通信接口。

综合省电模式允许设计师设计低功耗应用. 工作电压范围:2V到3.6v。

64k字节的闪存。

20K字节SRAM.CRC计算单元,96位唯一ID。

两个12位1μs ADC(最多10个通道)。

7通道DMA控制器,3个通用定时器和1个高级控制定时器。

STM32F103C8T6中文资料_引脚图_最小系统

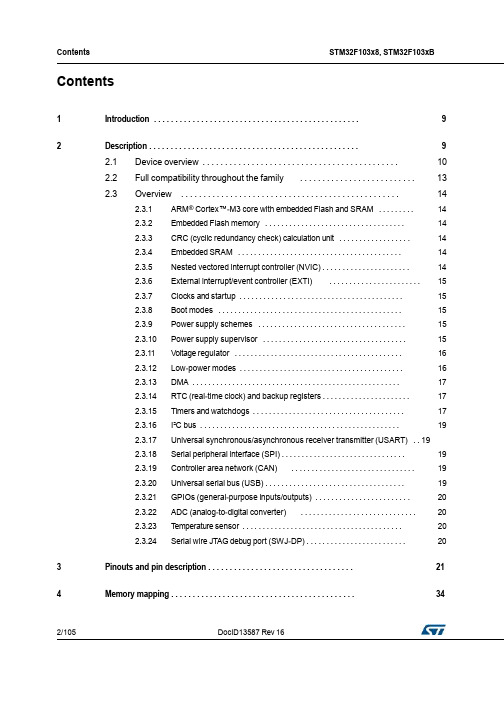

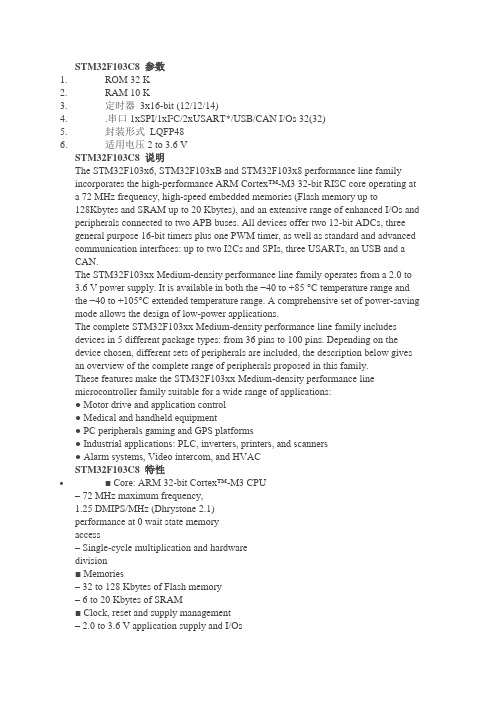

Contents STM32F103x8,STM32F103xB Contents1Introduction (9)2Description (9)2.1Device overview (10)2.2Full compatibility throughout the family (13)2.3Overview (14)2.3.1ARM®Cortex™-M3core with embedded Flash and SRAM (14)2.3.2Embedded Flash memory (14)2.3.3CRC(cyclic redundancy check)calculation unit (14)2.3.4Embedded SRAM (14)2.3.5Nested vectored interrupt controller(NVIC) (14)2.3.6External interrupt/event controller(EXTI) (15)2.3.7Clocks and startup (15)2.3.8Boot modes (15)2.3.9Power supply schemes (15)2.3.10Power supply supervisor (15)2.3.11Voltage regulator (16)2.3.12Low-power modes (16)2.3.13DMA (17)2.3.14RTC(real-time clock)and backup registers (17)2.3.15Timers and watchdogs (17)2.3.16I²C bus (19)2.3.17Universal synchronous/asynchronous receiver transmitter(USART)..192.3.18Serial peripheral interface(SPI) (19)2.3.19Controller area network(CAN) (19)2.3.20Universal serial bus(USB) (19)2.3.21GPIOs(general-purpose inputs/outputs) (20)2.3.22ADC(analog-to-digital converter) (20)2.3.23T emperature sensor (20)2.3.24Serial wire JTAG debug port(SWJ-DP) (20)3Pinouts and pin description (21)4Memory mapping (34)2/105DocID13587Rev16STM32F103x8,STM32F103xB Contents5Electrical characteristics (35)5.1Parameter conditions (35)5.1.1Minimum and maximum values (35)5.1.2Typical values (35)5.1.3Typical curves (35)5.1.4Loading capacitor (35)5.1.5Pin input voltage (35)5.1.6Power supply scheme (36)5.1.7Current consumption measurement (37)5.2Absolute maximum ratings (37)5.3Operating conditions (38)5.3.1General operating conditions (38)5.3.2Operating conditions at power-up/power-down (39)5.3.3Embedded reset and power control block characteristics (40)5.3.4Embedded reference voltage (41)5.3.5Supply current characteristics (41)5.3.6External clock source characteristics (51)5.3.7Internal clock source characteristics (55)5.3.8PLL characteristics (57)5.3.9Memory characteristics (57)5.3.10EMC characteristics (58)5.3.11Absolute maximum ratings(electrical sensitivity) (60)5.3.12I/O current injection characteristics (61)5.3.13I/O port characteristics (62)5.3.14NRST pin characteristics (68)5.3.15TIM timer characteristics (69)5.3.16Communications interfaces (70)5.3.17CAN(controller area network)interface (75)5.3.1812-bit ADC characteristics (76)5.3.19T emperature sensor characteristics (80)6Package characteristics (81)6.1Package mechanical data (81)6.2Thermal characteristics (93)6.2.1Reference document (93)6.2.2Selecting the product temperature range (94)DocID13587Rev163/105Contents STM32F103x8,STM32F103xB7Ordering information scheme (96)8Revision history (97)4/105DocID13587Rev16STM32F103x8,STM32F103xB List of tables List of tablesT able1.Device summary (1)T able2.STM32F103xx medium-density device features and peripheral counts (10)T able3.STM32F103xx family (13)T able4.Timer feature comparison (17)T able5.Medium-density STM32F103xx pin definitions (28)T able6.Voltage characteristics (37)T able7.Current characteristics (38)T able8.Thermal characteristics (38)T able9.General operating conditions (38)T able10.Operating conditions at power-up/power-down (39)T able11.Embedded reset and power control block characteristics (40)T able12.Embedded internal reference voltage (41)T able13.Maximum current consumption in Run mode,code with data processingrunning from Flash (42)T able14.Maximum current consumption in Run mode,code with data processingrunning from RAM (42)T able15.Maximum current consumption in Sleep mode,code running from Flash or RAM (44)T able16.Typical and maximum current consumptions in Stop and Standby modes (45)T able17.Typical current consumption in Run mode,code with data processingrunning from Flash (48)T able18.Typical current consumption in Sleep mode,code running from Flash orRAM (49)T able19.Peripheral current consumption (50)T able20.High-speed external user clock characteristics (51)T able21.Low-speed external user clock characteristics (51)T able22.HSE4-16MHz oscillator characteristics (53)T able23.LSE oscillator characteristics(f LSE=32.768kHz) (54)T able24.HSI oscillator characteristics (55)T able25.LSI oscillator characteristics (56)T able26.Low-power mode wakeup timings (57)T able27.PLL characteristics (57)T able28.Flash memory characteristics (57)T able29.Flash memory endurance and data retention (58)T able30.EMS characteristics (59)T able31.EMI characteristics (59)T able32.ESD absolute maximum ratings (60)T able33.Electrical sensitivities (60)T able34.I/O current injection susceptibility (61)T able35.I/O static characteristics (62)T able36.Output voltage characteristics (66)T able37.I/O AC characteristics (67)T able38.NRST pin characteristics (68)T able39.TIMx characteristics (69)T able40.I2C characteristics (70)T able41.SCL frequency(f PCLK1=36MHz.,V DD_I2C=3.3V) (71)T able42.SPI characteristics (72)T B startup time (74)T B DC electrical characteristics (75)DocID13587Rev165/105List of tables STM32F103x8,STM32F103xBT B:Full-speed electrical characteristics (75)T able46.ADC characteristics (76)T able47.R AIN max for f ADC=14MHz (77)T able48.ADC accuracy-limited test conditions (77)T able49.ADC accuracy (78)T able50.TS characteristics (80)T able51.VFQFPN366x6mm,0.5mm pitch,package mechanical data (82)T able52.UFQFPN487x7mm,0.5mm pitch,package mechanical data (83)T able53.LFBGA100-10x10mm low profile fine pitch ball grid array packagemechanical data (85)T able54.LQPF100,14x14mm100-pin low-profile quad flat package mechanical data (87)T able55.UFBGA100-ultra fine pitch ball grid array,7x7mm,0.50mm pitch,packagemechanical data (88)T able56.LQFP64,10x10mm,64-pin low-profile quad flat package mechanical data (89)T able57.TFBGA64-8x8active ball array,5x5mm,0.5mm pitch,package mechanical data (90)T able58.LQFP48,7x7mm,48-pin low-profile quad flat package mechanical data (92)T able59.Package thermal characteristics (93)T able60.Ordering information scheme (96)T able61.Document revision history (97)6/105DocID13587Rev16STM32F103x8,STM32F103xB List of figures List of figuresFigure1.STM32F103xx performance line block diagram (11)Figure2.Clock tree (12)Figure3.STM32F103xx performance line LFBGA100ballout (21)Figure4.STM32F103xx performance line LQFP100pinout (22)Figure5.STM32F103xx performance line UFBGA100pinout (23)Figure6.STM32F103xx performance line LQFP64pinout (24)Figure7.STM32F103xx performance line TFBGA64ballout (25)Figure8.STM32F103xx performance line LQFP48pinout (26)Figure9.STM32F103xx performance line UFQFPN48pinout (26)Figure10.STM32F103xx performance line VFQFPN36pinout (27)Figure11.Memory map (34)Figure12.Pin loading conditions (36)Figure13.Pin input voltage (36)Figure14.Power supply scheme (36)Figure15.Current consumption measurement scheme (37)Figure16.Typical current consumption in Run mode versus frequency(at3.6V)-code with data processing running from RAM,peripherals enabled (43)Figure17.Typical current consumption in Run mode versus frequency(at3.6V)-code with data processing running from RAM,peripherals disabled (43)Figure18.Typical current consumption on V BAT with RTC on versus temperature at differentV BAT values (45)Figure19.Typical current consumption in Stop mode with regulator in Run mode versustemperature at V DD=3.3V and3.6V (46)Figure20.Typical current consumption in Stop mode with regulator in Low-power mode versustemperature at V DD=3.3V and3.6V (46)Figure21.Typical current consumption in Standby mode versus temperature atV DD=3.3V and3.6V (47)Figure22.High-speed external clock source AC timing diagram (52)Figure23.Low-speed external clock source AC timing diagram (52)Figure24.Typical application with an8MHz crystal (53)Figure25.Typical application with a32.768kHz crystal (55)Figure26.Standard I/O input characteristics-CMOS port (64)Figure27.Standard I/O input characteristics-TTL port (64)Figure28.5V tolerant I/O input characteristics-CMOS port (65)Figure29.5V tolerant I/O input characteristics-TTL port (65)Figure30.I/O AC characteristics definition (68)Figure31.Recommended NRST pin protection (69)Figure32.I2C bus AC waveforms and measurement circuit (71)Figure33.SPI timing diagram-slave mode and CPHA=0 (73)Figure34.SPI timing diagram-slave mode and CPHA=1(1) (73)Figure35.SPI timing diagram-master mode(1) (74)B timings:definition of data signal rise and fall time (75)Figure37.ADC accuracy characteristics (78)Figure38.Typical connection diagram using the ADC (79)Figure39.Power supply and reference decoupling(V REF+not connected to V DDA) (79)Figure40.Power supply and reference decoupling(V REF+connected to V DDA) (80)Figure41.VFQFPN366x6mm,0.5mm pitch,package outline(1) (82)Figure42.VFQFPN36recommended footprint(dimensions in mm)(1)(2) (82)DocID13587Rev167/105List of figures STM32F103x8,STM32F103xBFigure43.UFQFPN487x7mm,0.5mm pitch,package outline (83)Figure44.UFQFPN48recommended footprint (84)Figure45.LFBGA100-10x10mm low profile fine pitch ball grid array packageoutline (85)Figure46.Recommended PCB design rules(0.80/0.75mm pitch BGA) (86)Figure47.LQFP100,14x14mm100-pin low-profile quad flat package outline (87)Figure48.LQFP100recommended footprint(1) (87)Figure49.UFBGA100-ultra fine pitch ball grid array,7x7mm,0.50mm pitch,package outline (88)Figure50.LQFP64,10x10mm,64-pin low-profile quad flat package outline (89)Figure51.LQFP64recommended footprint(1) (89)Figure52.TFBGA64-8x8active ball array,5x5mm,0.5mm pitch,package outline (90)Figure53.Recommended PCB design rules for pads(0.5mm pitch BGA) (91)Figure54.LQFP48,7x7mm,48-pin low-profile quad flat package outline (92)Figure55.LQFP48recommended footprint(1) (92)Figure56.LQFP100P D max vs.T A (95)8/105DocID13587Rev16STM32F103x8,STM32F103xB Introduction 1IntroductionThis datasheet provides the ordering information and mechanical device characteristics ofthe STM32F103x8and STM32F103xB medium-density performance line microcontrollers.For more details on the whole STMicroelectronics STM32F103xx family,please refer toSection2.2:Full compatibility throughout the family.The medium-density STM32F103xx datasheet should be read in conjunction with the low-,medium-and high-density STM32F10xxx reference manual.The reference and Flash programming manuals are both available from theSTMicroelectronics website .For information on the Cortex™-M3core please refer to the Cortex™-M3T echnicalReference Manual,available from the website at the following address:/help/index.jsp?topic=/com.arm.doc.ddi0337e/2DescriptionThe STM32F103xx medium-density performance line family incorporates the high-performance ARM Cortex™-M332-bit RISC core operating at a72MHz frequency,high-speed embedded memories(Flash memory up to128Kbytes and SRAM up to20Kbytes),and an extensive range of enhanced I/Os and peripherals connected to two APB buses.Alldevices offer two12-bit ADCs,three general purpose16-bit timers plus one PWM timer,aswell as standard and advanced communication interfaces:up to two I2Cs and SPIs,threeUSART s,an USB and a CAN.The devices operate from a2.0to3.6V power supply.They are available in both the–40to+85°C temperature range and the–40to+105°C extended temperature range.Acomprehensive set of power-saving mode allows the design of low-power applications.The STM32F103xx medium-density performance line family includes devices in six differentpackage types:from36pins to100pins.Depending on the device chosen,different sets ofperipherals are included,the description below gives an overview of the complete range ofperipherals proposed in this family.These features make the STM32F103xx medium-density performance line microcontrollerfamily suitable for a wide range of applications such as motor drives,application control,medical and handheld equipment,PC and gaming peripherals,GPS platforms,industrialapplications,PLCs,inverters,printers,scanners,alarm systems,video intercoms,andHVACs.DocID13587Rev169/105TimersCommunicationDescription STM32F103x8,STM32F103xB 2.1Device overviewTable2.STM32F103xx medium-density device features and peripheral1.On the TFBGA64package only15channels are available(one analog input pin has been replaced by‘Vref+’).10/105DocID13587Rev16Peripheral STM32F103Tx STM32F103Cx STM32F103Rx STM32F103Vx Flash-Kbytes64128641286412864128SRAM-Kbytes20202020 General-purpose3333Advanced-control1111SPI12222I C1222USART2333USB1111CAN1111 GPIOs2637518012-bit synchronized ADCNumber of channels210channels210channels2(1)16channels216channels CPU frequency72MHzOperating voltage 2.0to3.6VOperating temperaturesAmbient temperatures:-40to+85°C/-40to+105°C(see Table9)Junction temperature:-40to+125°C(see Table9)Packages VFQFPN36LQFP48,UFQFPN48LQFP64,TFBGA64LQFP100,LFBGA100,UFBGA100f l a s ho b lI n t e r f a c eB u s M a t r i xA HB :F m a x =48/72M H zA PB 2:F m a x =48/72M H zA PB 1:F m a x =24/36M H zpbusPCLK2 HCLK CLOCK RTC AWUTAMPER -RTCSTM32F103x8, STM32F103xBDescriptionFigure 1. STM32F103xx performance line block diagramTRACECLKTRACED[0:3] as ASNJTRSTTRSTJTDIJTCK/SWCLK JTMS/SWDIOJTDO as AFTPIUTrace/trigSW/JTAGCortex -M3 CPUIbusF max : 7 2M Hz DbusTraceControlle rFlash 128 KB64 bitPOWERVOLT. REG. 3.3V TO 1.8V@VDDV DD = 2 to 3.6VV SSNVICSystemSRAM20 KB@VDDGP DMA7 channelsPCLK1 FCLKPLL &MANAGTXTAL OSC4-16 MHzOSC_INOSC_OUTRC 8 MHzNRST @VDDASUPPLYSUPERVISIONRC 40 kHz @VDDA@VBATIWDG Standby interfaceV BATVDDA VSSA 80AF PA[15:0] PB[15:0]POR / PDRPVDEXTIWAKEUPGPIOAGPIOBRstIntAHB2 AHB2APB2 APB1XTAL 32 kHzBackup reg Backu p i nterf ace TIM2 TIM3OSC32_IN OSC32_OUT4 Channels 4 ChannelsPC[15:0]GPIOCTIM 44 ChannelsPD[15:0]GPIOD PE[15:0] GPIOEUSART2USART3RX,TX, CTS, RTS,CK, SmartCard as AFRX,TX, CTS, RTS, CK, SmartCard as AF4 Channels3 compl. ChannelsETR and BKINMOSI,MISO, SCK,NSS as AFRX,TX, CTS, RTS,TIM1SPI12x(8x16bit)SPI2I2C1 I2C2MOSI,MISO,SCK,NSS as AFSCL,SDA,SMBA as AFSCL,SDA as AFSmartCard as AFUSART1@VDDAbxCANUSBDP/CAN_TXUSB 2.0 FSUSBDM/CAN_RX16AF V REF+ V REF -12bit ADC1 IF12bit ADC2 IFSRAM 512BWWDGTemp sensorai14390d1. T A = –40 °C to +105 °C (junction temperature up to 125 °C).2. AF = alternate function on I/O port pin.DocID13587 Rev 1611/105peripheralsIf (APB2 prescaler =1) x1 ADC /2, 4, 6, 8 ADCCLKDescriptionSTM32F103x8, STM32F103xBFigure 2. Clock treeFLITFCLKto Flash programming interface8 MHz HSI RCHSIUSBPrescaler 48 MHzUSBCLKto USB interface/2/1, 1.572 MHz maxClockHCLKto AHB bus, core, memory and DMA PLLSRCSWPLLMUL/8Enable (3 bits)to Cortex System timerFCLK Cortex..., x16 x2, x3, x4 PLLHSIPLLCLK HSESYSCLK72 MHz max AHB Prescaler /1, 2..512 APB1Prescaler/1, 2, 4, 8, 16free running clock36 MHz max PCLK1to APB1Peripheral Clock Enable (13 bits)TIM2,3, 4to TIM2, 3and 4CSSIf (APB1 prescaler =1) x1 TIMXCLKelse x2 Peripheral ClockEnable (3 bits)OSC_OUTOSC_IN4-16 MHzHSE OSCPLLXTPRE/2APB2Prescaler/1, 2, 4, 8, 16TIM1 timer 72 MHz maxPeripheral ClockEnable (11 bits) PCLK2peripherals to APB2to TIM1 TIM1CLK else x2 Peripheral ClockOSC32_INOSC32_OUTLSE OSC32.768 kHz/128LSERTCCLKto RTCPrescaler Enable (1 bit) to ADCRTCSEL[1:0]LSI RCLSIto Independent Watchdog (IWDG)40 kHzIWDGCLKLegend:HSE = high -speed external clock signalHSI = high -speed internal clock signalMCOMainClock Output/2PLLCLKHSI LSI = low -speed internal clock signal LSE = low -speed external clock signalHSESYSCLKMCOai149031. When the HSI is used as a PLL clock input, the maximum system clock frequency that can be achieved is 64 MHz.2. For the USB function to be available, both HSE and PLL must be enabled, with USBCLK running at 48 MHz.3. To have an ADC conversion time of 1 µs, APB2 must be at 14 MHz, 28 MHz or 56 MHz.12/105DocID13587 Rev 16STM32F103x8, STM32F103xBDescription2.2 Full compatibility throughout the familyThe STM32F103xx is a complete family whose members are fully pin -to -pin, software and feature compatible. In the reference manual, the STM32F103x4 and STM32F103x6 are identified as low -density devices, the STM32F103x8 and STM32F103xB are referred to as medium -density devices, and the STM32F103xC, STM32F103xD and STM32F103xE are referred to as high -density devices.Low - and high -density devices are an extension of the STM32F103x8/B devices, they are specified in the STM32F103x4/6 and STM32F103xC/D/E datasheets, respectively. Low - density devices feature lower Flash memory and RAM capacities, less timers and peripherals. High -density devices have higher Flash memory and RAM capacities, and additional peripherals like SDIO, FSMC, I 2S and DAC, while remaining fully compatible with the other members of the STM32F103xx family .The STM32F103x4, STM32F103x6, STM32F103xC, STM32F103xD and STM32F103xE are a drop -in replacement for STM32F103x8/B medium -density devices, allowing the user to try different memory densities and providing a greater degree of freedom during the development cycle.Moreover, the STM32F103xx performance line family is fully compatible with all existing STM32F101xx access line and STM32F102xx USB access line devices.1.For orderable part numbers that do not show the A internal code after the temperature range code (6 or 7),the reference datasheet for electrical characteristics is that of the STM32F103x8/B medium -density devices.DocID13587 Rev 16 13/105PinoutLow -density devicesMedium -density devices High -density devices 16 KB Flash 32 KB Flash (1) 64 KB Flash 128 KB Flash 256 KB Flash 384 KB Flash 512 KB Flash6 KB RAM 10 KB RAM 20 KB RAM 20 KB RAM 48 KB RAM 64 KB RAM 64 KB RAM144 5 × USART s 4 × 16-bit timers, 2 × basic timers2 3 × SPIs, 2 × I Ss, 2 × I2Cs USB, CAN, 2 × PWM timers 3 × ADCs, 2 × DACs, 1 × SDIOFSMC (100 and 144 pins) 100 3 × USART s 3 × 16-bit timers 2 2 × SPIs, 2 × I Cs, USB, CAN, 1 × PWM timer2 × ADCs 64 2 × USART s 2 × 16-bit timers 2 1 × SPI, 1 × I C, USB, CAN, 1 × PWM timer 2 × ADCs 48 36Description STM32F103x8,STM32F103xB 2.3Overview2.3.1ARM®Cortex™-M3core with embedded Flash and SRAMThe ARM Cortex™-M3processor is the latest generation of ARM processors for embeddedsystems.It has been developed to provide a low-cost platform that meets the needs of MCUimplementation,with a reduced pin count and low-power consumption,while deliveringoutstanding computational performance and an advanced system response to interrupts.The ARM Cortex™-M332-bit RISC processor features exceptional code-efficiency,delivering the high-performance expected from an ARM core in the memory size usuallyassociated with8-and16-bit devices.The STM32F103xx performance line family having an embedded ARM core,is thereforecompatible with all ARM tools and software.Figure1shows the general block diagram of the device family.2.3.2Embedded Flash memory64or128Kbytes of embedded Flash is available for storing programs and data.2.3.3CRC(cyclic redundancy check)calculation unitThe CRC(cyclic redundancy check)calculation unit is used to get a CRC code from a32-bitdata word and a fixed generator polynomial.Among other applications,CRC-based techniques are used to verify data transmission orstorage integrity.In the scope of the EN/IEC60335-1standard,they offer a means ofverifying the Flash memory integrity.The CRC calculation unit helps compute a signature ofthe software during runtime,to be compared with a reference signature generated at link-time and stored at a given memory location.2.3.4Embedded SRAMTwenty Kbytes of embedded SRAM accessed(read/write)at CPU clock speed with0waitstates.2.3.5Nested vectored interrupt controller(NVIC)The STM32F103xx performance line embeds a nested vectored interrupt controller able tohandle up to43maskable interrupt channels(not including the16interrupt lines ofCortex™-M3)and16priority levels.•Closely coupled NVIC gives low-latency interrupt processing•Interrupt entry vector table address passed directly to the core•Closely coupled NVIC core interface•Allows early processing of interrupts•Processing of late arriving higher priority interrupts•Support for tail-chaining•Processor state automatically saved•Interrupt entry restored on interrupt exit with no instruction overhead14/105DocID13587Rev16万联芯城专注电子元器件配单服务,只售原装现货库存,万联芯城电子元器件全国供应,专为终端生产,研发企业提供现货物料,价格优势明显,BOM配单采购可节省逐个搜索购买环节,只需提交BOM物料清单,商城即可为您报价,解决客户采购烦恼,为客户节省采购成本,点击进入万联芯城。

stm32f103c8t6 手册

很高兴能成为你的文章写手,并协助你撰写关于STM32F103C8T6的一篇深度、广度兼具的文章。

在本文中,我将全面评估并深入探讨这个主题,希望能帮助你更深入地理解这款产品。

第一部分:STM32F103C8T6概述1. STM32F103C8T6是什么STM32F103C8T6是意法半导体公司生产的一款低功耗、高性能的32位微控制器。

它采用ARM Cortex-M3内核,拥有丰富的外设和丰富的通信接口,广泛应用于工业自动化、消费类电子产品和通信设备等领域。

2. 主要特性- ARM Cortex-M3内核- 最高72MHz主频- 64KB闪存和20KB SRAM- 丰富的外设:定时器、通信接口、模拟输入输出等- 低功耗设计- 丰富的开发工具和生态系统3. 应用领域STM32F103C8T6广泛应用于各种领域,包括工业自动化(PLC、工业控制)、消费类电子产品(智能家居、智能穿戴设备)、通信设备(路由器、交换机)等。

第二部分:深入探讨STM32F103C8T61. 开发环境和工具在使用STM32F103C8T6进行开发时,我们可以使用意法半导体提供的STM32CubeMX和Keil等集成开发环境,以及丰富的示例代码和文档。

2. 外设和通信接口STM32F103C8T6具有丰富的外设和通信接口,比如定时器、串口通信、I2C、SPI等。

这些外设和通信接口的灵活应用能够满足各种不同应用场景的需求。

3. 低功耗设计在物联网和便携式设备等领域,低功耗设计是十分重要的。

STM32F103C8T6通过低功耗模式和智能电源管理单元等设计,可以满足对功耗要求较高的应用需求。

第三部分:我的个人观点和理解在使用STM32F103C8T6进行开发的过程中,我深刻体会到了它的灵活性和强大性能,尤其是在处理复杂的任务和对功耗要求严格的场景下表现突出。

意法半导体提供的丰富开发工具和文档也为开发者提供了极大的便利。

我相信,在未来的发展中,STM32F103C8T6将在更多领域展现出其强大的潜力,并推动物联网和智能设备等领域的发展。

stm32f103c8t6中文手册

STM32F103系列微处理器,STM32F103器件* * STM32F103 * * Cortex-M3内核,CPU速度为72 MHz,最大闪存为1 MB。

包括电机控制外设和USB全速接口。

STM32系列臂式Cortex-M3 32位闪存微控制器具有低功耗,低电压,出色的性能和实时功能。

包类型系列适用于您的嵌入式应用程序。

MCU体系结构具有易于使用的STM32平台,适用于包括电机驱动,PC和游戏,HVAC以及工业应用在内的应用。

32位RISC引脚对引脚软件兼容的SRAM 高达96 KB闪存高达1MB电源:2 V至3.6 V温度范围:-40至+ 85°C或-40至+ 105°Cᦇstm32f1系列32位臂?皮质?-M3微控制器,意法半导体的STM32闪存微控制器。

STM32系列是基于ARM cortex Gamma M3的核心突破-嵌入式应用程序特殊开发的核心。

STM32系列受益于对Cortex-M3体系结构的增强,其中包括thumb-2指令集,该指令集提供了更高的性能,更好的编码密度,更快的中断响应以及所有领先的工业功耗。

出色的实时性能,出色的效率和新的外围设备,最大限度地提高了串行引脚,外围设备和软件兼容性之间的集成Stm32f103c8t6是中密度性能线,配备了Arm Cortex-M3 32位微控制器和48通道LQFP 封装。

它结合了高性能RISC内核,72MHz的工作频率,高速嵌入式存储器,增强的I / O范围以及与两条APB总线的外部连接。

Stm32f103c8t6具有12位ADC,计时器,PWM计时器,标准和高级通信接口。

全面的省电模式使设计人员能够设计低功耗应用。

工作电压范围:2V至3.6v.64k字节闪存。

20K字节SRAM.CRC计算单元,96位唯一ID。

两个12位,1μs ADC(最多10个通道)。

7通道DMA控制器,3个通用定时器和1个高级控制定时器。

STM32中文参考手册-stm32f103中文参考手册

STM32F10xxx参考手册参考手册小,中和大容量的STM32F101xx, STM32F102xx和STM32F103xxARM内核32位高性能微控制器导言本参考手册针对应用开发,提供关于如何使用小容量、中容量和大容量的STM32F101xx、STM32F102xx或者STM32F103xx微控制器的存储器和外设的详细信息。

在本参考手册中STM32F101xx、STM32F102xx和STM32F103xx被统称为STM32F10xxx。

STM32F10xxx系列拥有不同的存储器容量,封装和外设配置。

关于订货编号、电气和物理性能参数,请参考STM32F101xx、STM32F102xx和STM32F103xx 的数据手册。

关于芯片内部闪存的编程,擦除和保护操作,请参考STM32F10xxx闪存编程手册。

关于ARM Cortex™-M3内核的具体信息,请参考Cortex™-M3技术参考手册。

相关文档● Cortex™-M3技术参考手册,可按下述链接下载:/help/topic/com.arm.doc.ddi0337e/DDI0337E_cortex_m3_r1p1_trm.pdf下述文档可在ST网站下载(/mcu/):● STM32F101xx、STM32F102xx和STM32F103xx的数据手册。

● STM32F10xxx闪存编程手册。

* 感谢南京万利提供原始翻译文档目录1文中的缩写 161.1寄存器描述表中使用的缩写列表 161.2术语表161.3可用的外设16 2存储器和总线构架 172.1系统构架172.2存储器组织182.3存储器映像192.3.1嵌入式SRAM 202.3.2位段202.3.3嵌入式闪存 212.4启动配置23 3CRC计算单元(CRC) 253.1CRC简介253.2CRC主要特性253.3CRC功能描述253.4CRC寄存器263.4.1数据寄存器(CRC_DR) 263.4.2独立数据寄存器(CRC_IDR) 263.4.3控制寄存器(CRC_CR) 273.4.4CRC寄存器映像 27 4电源控制(PWR) 284.1电源284.1.1独立的A/D转换器供电和参考电压 284.1.2电池备份区域 294.1.3电压调节器 294.2电源管理器294.2.1上电复位(POR)和掉电复位(PDR) 294.2.2可编程电压监测器(PVD) 304.3低功耗模式304.3.1降低系统时钟 314.3.2外部时钟的控制 314.3.3睡眠模式 314.3.4停止模式 324.3.5待机模式 334.3.6低功耗模式下的自动唤醒(AWU) 344.4电源控制寄存器 354.4.1电源控制寄存器(PWR_CR) 354.4.2电源控制/状态寄存器 364.4.3PWR寄存器地址映像 37 5备份寄存器(BKP) 385.1BKP简介385.2BKP特性385.3BKP功能描述385.3.1侵入检测 385.3.2RTC校准 395.4BKP寄存器描述 395.4.1备份数据寄存器x(BKP_DRx) (x = 1 … 10) 395.4.2RTC时钟校准寄存器(BKP_RTCCR) 395.4.3备份控制寄存器(BKP_CR) 405.4.4备份控制/状态寄存器(BKP_CSR) 405.4.5BKP寄存器映像 42 6复位和时钟控制(RCC) 456.1复位456.1.1系统复位 456.1.2电源复位 456.1.3备份域复位 466.2时钟466.2.1HSE时钟 486.2.2HSI时钟 486.2.3PLL 496.2.4LSE时钟 496.2.5LSI时钟496.2.6系统时钟(SYSCLK)选择 506.2.7时钟安全系统(CSS) 506.2.8RTC时钟 506.2.9看门狗时钟 506.2.10时钟输出 506.3RCC寄存器描述 516.3.1时钟控制寄存器(RCC_CR) 516.3.2时钟配置寄存器(RCC_CFGR) 526.3.3时钟中断寄存器 (RCC_CIR) 546.3.4APB2外设复位寄存器 (RCC_APB2RSTR) 566.3.5APB1外设复位寄存器 (RCC_APB1RSTR) 586.3.6AHB外设时钟使能寄存器 (RCC_AHBENR) 606.3.7APB2外设时钟使能寄存器(RCC_APB2ENR) 616.3.8APB1外设时钟使能寄存器(RCC_APB1ENR) 626.3.9备份域控制寄存器 (RCC_BDCR) 656.3.10控制/状态寄存器 (RCC_CSR) 666.3.11RCC寄存器地址映像 68 7通用和复用功能I/O(GPIO和AFIO) 697.1GPIO功能描述697.1.1通用I/O(GPIO) 707.1.2单独的位设置或位清除 717.1.3外部中断/唤醒线 717.1.4复用功能(AF) 717.1.5软件重新映射I/O复用功能 717.1.6GPIO锁定机制 717.1.7输入配置 717.1.8输出配置 727.1.9复用功能配置 737.1.10模拟输入配置 737.2GPIO寄存器描述 757.2.1端口配置低寄存器(GPIOx_CRL) (x=A..E) 757.2.2端口配置高寄存器(GPIOx_CRH) (x=A..E) 757.2.3端口输入数据寄存器(GPIOx_IDR) (x=A..E) 767.2.4端口输出数据寄存器(GPIOx_ODR) (x=A..E) 767.2.5端口位设置/清除寄存器(GPIOx_BSRR) (x=A..E) 777.2.6端口位清除寄存器(GPIOx_BRR) (x=A..E) 777.2.7端口配置锁定寄存器(GPIOx_LCKR) (x=A..E) 777.3复用功能I/O和调试配置(AFIO) 787.3.1把OSC32_IN/OSC32_OUT作为GPIO 端口PC14/PC15 787.3.2把OSC_IN/OSC_OUT引脚作为GPIO端口PD0/PD1 787.3.3CAN复用功能重映射 797.3.4JTAG/SWD复用功能重映射 797.3.5ADC复用功能重映射 807.3.6定时器复用功能重映射 807.3.7USART复用功能重映射 817.3.8I2C 1 复用功能重映射 827.3.9SPI 1复用功能重映射 827.4AFIO寄存器描述 837.4.1事件控制寄存器(AFIO_EVCR) 837.4.2复用重映射和调试I/O配置寄存器(AFIO_MAPR) 837.4.3外部中断配置寄存器1(AFIO_EXTICR1) 867.4.4外部中断配置寄存器2(AFIO_EXTICR2) 867.4.5外部中断配置寄存器3(AFIO_EXTICR3) 877.4.6外部中断配置寄存器4(AFIO_EXTICR4) 877.5GPIO 和AFIO寄存器地址映象 88 8中断和事件 898.1嵌套向量中断控制器 898.1.1系统嘀嗒(SysTick)校准值寄存器 898.1.2中断和异常向量 898.2外部中断/事件控制器(EXTI) 918.2.1主要特性 918.2.2框图928.2.3唤醒事件管理 928.2.4功能说明 928.2.5外部中断/事件线路映像 948.3EXTI 寄存器描述 958.3.1中断屏蔽寄存器(EXTI_IMR) 958.3.2事件屏蔽寄存器(EXTI_EMR) 958.3.3上升沿触发选择寄存器(EXTI_RTSR) 968.3.4下降沿触发选择寄存器(EXTI_FTSR) 968.3.5软件中断事件寄存器(EXTI_SWIER) 978.3.6挂起寄存器(EXTI_PR) 978.3.7外部中断/事件寄存器映像 98 9DMA 控制器(DMA) 999.1DMA简介999.2DMA主要特性999.3功能描述1009.3.1DMA处理 1009.3.2仲裁器1009.3.3DMA 通道 1019.3.4可编程的数据传输宽度,对齐方式和数据大小端 1029.3.5错误管理 1039.3.6中断1039.3.7DMA请求映像 1049.4DMA寄存器1079.4.1DMA中断状态寄存器(DMA_ISR) 1079.4.2DMA中断标志清除寄存器(DMA_IFCR) 1089.4.3DMA通道x配置寄存器(DMA_CCRx)(x = 1…7) 1089.4.4DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1…7) 1109.4.5DMA通道x外设地址寄存器(DMA_CPARx)(x = 1…7) 1109.4.6DMA通道x存储器地址寄存器(DMA_CPARx)(x = 1…7) 1109.4.7DMA寄存器映像 111 10模拟/数字转换(ADC) 11310.1ADC介绍11310.2ADC主要特征11310.3ADC功能描述11410.3.1ADC开关控制 11510.3.2ADC时钟 11510.3.3通道选择 11510.3.4单次转换模式 11510.3.5连续转换模式 11610.3.6时序图11610.3.7模拟看门狗 11610.3.8扫描模式 11710.3.9注入通道管理 11710.3.10间断模式 11810.4校准11910.5数据对齐11910.6可编程的通道采样时间 12010.7外部触发转换12010.8DMA请求12110.9双ADC模式12110.9.1同步注入模式 12210.9.2同步规则模式 12310.9.3快速交替模式 12310.9.4慢速交替模式 12410.9.5交替触发模式 12410.9.6独立模式 12510.9.7混合的规则/注入同步模式 12510.9.8混合的同步规则+交替触发模式 12510.9.9混合同步注入+交替模式 12610.10温度传感器12610.11ADC中断12710.12ADC寄存器描述 12810.12.1ADC状态寄存器(ADC_SR) 12810.12.2ADC控制寄存器1(ADC_CR1) 12910.12.3ADC控制寄存器2(ADC_CR2) 13110.12.4ADC采样时间寄存器1(ADC_SMPR1) 13310.12.5ADC采样时间寄存器2(ADC_SMPR2) 13310.12.6ADC注入通道数据偏移寄存器x (ADC_JOFRx)(x=1..4) 13410.12.7ADC看门狗高阀值寄存器(ADC_HTR) 13410.12.8ADC看门狗低阀值寄存器(ADC_LRT) 13410.12.9ADC规则序列寄存器1(ADC_SQR1) 13510.12.10ADC规则序列寄存器2(ADC_SQR2) 13510.12.11ADC规则序列寄存器3(ADC_SQR3) 13610.12.12ADC注入序列寄存器(ADC_JSQR) 13610.12.13ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4) 13710.12.14ADC规则数据寄存器(ADC_DR) 13710.12.15ADC寄存器地址映像 138 11数字/模拟转换(DAC) 14011.1DAC简介14011.2DAC主要特征14011.3DAC功能描述14111.3.1使能DAC通道 14111.3.2使能DAC输出缓存 14111.3.3DAC数据格式 14211.3.4DAC转换 14211.3.5DAC输出电压 14311.3.6选择DAC触发 14311.3.7DMA请求 14411.3.8噪声生成 14411.3.9三角波生成 14511.4双DAC通道转换 14511.4.1无波形生成的独立触发 14511.4.2带相同LFSR生成的独立触发 14611.4.3带不同LFSR生成的独立触发 14611.4.4带相同三角波生成的独立触发 14611.4.5带不同三角波生成的独立触发 14611.4.6同时软件启动 14711.4.7不带波形生成的同时触发 14711.4.8带相同LFSR生成的同时触发 14711.4.9带不同LFSR生成的同时触发 14711.4.10带相同三角波生成的同时触发 14711.4.11带不同三角波生成的同时触发 14811.5DAC寄存器14911.5.1DAC控制寄存器(DAC_CR) 14911.5.2DAC软件触发寄存器(DAC_SWTRIGR) 15111.5.3DAC通道1的12位右对齐数据保持寄存器(DAC_DHR12R1) 15211.5.4DAC通道1的12位左对齐数据保持寄存器(DAC_DHR12L1) 15211.5.5DAC通道1的8位右对齐数据保持寄存器(DAC_DHR8R1) 15211.5.6DAC通道2的12位右对齐数据保持寄存器(DAC_DHR12R2) 15311.5.7DAC通道2的12位左对齐数据保持寄存器(DAC_DHR12L2) 15311.5.8DAC通道2的8位右对齐数据保持寄存器(DAC_DHR8R2) 15311.5.9双DAC的12位右对齐数据保持寄存器(DAC_DHR12RD) 15411.5.10双DAC的12位左对齐数据保持寄存器(DAC_DHR12LD) 15411.5.11双DAC的8位右对齐数据保持寄存器(DAC_DHR8RD) 15411.5.12DAC通道1数据输出寄存器(DAC_DOR1) 15511.5.13DAC通道2数据输出寄存器(DAC_DOR2) 15511.5.14DAC寄存器映像 156 12高级控制定时器(TIM1和TIM8) 15712.1TIM1和TIM8简介 15712.2TIM1和TIM8主要特性 15712.3TIM1和TIM8功能描述 15812.3.1时基单元 15812.3.2计数器模式 16012.3.3重复计数器 16712.3.4时钟选择 16812.3.5捕获/比较通道 17112.3.6输入捕获模式 17312.3.7PWM输入模式 17412.3.8强置输出模式 17412.3.9输出比较模式 17512.3.10PWM模式 17612.3.11互补输出和死区插入 17812.3.12使用刹车功能 17912.3.13在外部事件时清除OCxREF信号 18012.3.14产生六步PWM输出 18112.3.15单脉冲模式 18212.3.16编码器接口模式 18312.3.17定时器输入异或功能 18512.3.18与霍尔传感器的接口 18512.3.19TIMx定时器和外部触发的同步 18712.3.20定时器同步 19012.3.21调试模式 19012.4TIM1和TIM8寄存器描述 19112.4.1控制寄存器1(TIMx_CR1) 19112.4.2控制寄存器2(TIMx_CR2) 19212.4.3从模式控制寄存器(TIMx_SMCR) 19312.4.4DMA/中断使能寄存器(TIMx_DIER) 19512.4.5状态寄存器(TIMx_SR) 19612.4.6事件产生寄存器(TIMx_EGR) 19712.4.7捕获/比较模式寄存器1(TIMx_CCMR1) 19812.4.8捕获/比较模式寄存器2(TIMx_CCMR2) 20012.4.9捕获/比较使能寄存器(TIMx_CCER) 20212.4.10计数器(TIMx_CNT) 20312.4.11预分频器(TIMx_PSC) 20412.4.12自动重装载寄存器(TIMx_ARR) 20412.4.13重复计数寄存器(TIMx_RCR) 20412.4.14捕获/比较寄存器1(TIMx_CCR1) 20512.4.15捕获/比较寄存器2(TIMx_CCR2) 20512.4.16捕获/比较寄存器3(TIMx_CCR3) 20512.4.17捕获/比较寄存器(TIMx_CCR4) 20612.4.18刹车和死区寄存器(TIMx_BDTR) 20612.4.19DMA控制寄存器(TIMx_DCR) 20812.4.20连续模式的DMA地址(TIMx_DMAR) 20812.4.21TIM1和TIM8寄存器图 209 13通用定时器(TIMx) 21113.1TIMx简介21113.2TIMx主要功能21113.3TIMx功能描述21213.3.1时基单元 21213.3.2计数器模式 21313.3.3时钟选择 22113.3.4捕获/比较通道 22313.3.5输入捕获模式 22513.3.6PWM输入模式 22513.3.7强置输出模式 22613.3.8输出比较模式 22613.3.9PWM 模式 22713.3.10单脉冲模式 22913.3.11在外部事件时清除OCxREF信号 23113.3.12编码器接口模式 23113.3.13定时器输入异或功能 23313.3.14定时器和外部触发的同步 23313.3.15定时器同步 23513.3.16调试模式 23913.4TIMx寄存器描述 24013.4.1控制寄存器1(TIMx_CR1) 24013.4.2控制寄存器2(TIMx_CR2) 24113.4.3从模式控制寄存器(TIMx_SMCR) 24213.4.4DMA/中断使能寄存器(TIMx_DIER) 24313.4.5状态寄存器(TIMx_SR) 24413.4.6事件产生寄存器(TIMx_EGR) 24513.4.7捕获/比较模式寄存器1(TIMx_CCMR1) 24613.4.8捕获/比较模式寄存器2(TIMx_CCMR2) 24913.4.9捕获/比较使能寄存器(TIMx_CCER) 25113.4.10计数器(TIMx_CNT) 25213.4.11预分频器(TIMx_PSC) 25213.4.12自动重装载寄存器(TIMx_ARR) 25213.4.13捕获/比较寄存器1(TIMx_CCR1) 25213.4.14捕获/比较寄存器2(TIMx_CCR2) 25313.4.15捕获/比较寄存器3(TIMx_CCR3) 25313.4.16捕获/比较寄存器4(TIMx_CCR4) 25313.4.17DMA控制寄存器(TIMx_DCR) 25413.4.18连续模式的DMA地址(TIMx_DMAR) 25413.4.19TIMx寄存器图 255 14基本定时器(TIM6和TIM7) 25714.1TIM6和TIM7简介 25714.2TIM6和TIM7的主要特性 25714.3TIM6和TIM7的功能 25814.3.1时基单元 25814.3.2计数模式 25914.3.3时钟源26114.3.4调试模式 26214.4TIM6和TIM7寄存器 26214.4.1控制寄存器1(TIMx_CR1) 26214.4.2控制寄存器2(TIMx_CR2) 26314.4.3DMA/中断使能寄存器(TIMx_DIER) 26314.4.4状态寄存器(TIMx_SR) 26414.4.5事件产生寄存器(TIMx_EGR) 26414.4.6计数器(TIMx_CNT) 26414.4.7预分频器(TIMx_PSC) 26514.4.8自动重装载寄存器(TIMx_ARR) 26514.4.9TIM6和TIM7寄存器图 266 15实时时钟(RTC) 26715.1RTC简介26715.2主要特性26715.3功能描述26715.3.1概述26715.3.2复位过程 26815.3.3读RTC寄存器 26815.3.4配置RTC寄存器 26915.3.5RTC标志的设置 26915.4RTC寄存器描述 27015.4.1RTC控制寄存器高位(RTC_CRH) 27015.4.2RTC控制寄存器低位(RTC_CRL) 27015.4.3RTC预分频装载寄存器(RTC_PRLH/RTC_PRLL) 27115.4.4RTC预分频器余数寄存器(RTC_DIVH / RTC_DIVL) 27215.4.5RTC计数器寄存器 (RTC_CNTH / RTC_CNTL) 27215.4.6RTC闹钟寄存器(RTC_ALRH/RTC_ALRL) 27315.4.7RTC寄存器映像 275 16独立看门狗(IWDG) 27616.1简介27616.2IWDG主要性能27616.3IWDG功能描述27616.3.1硬件看门狗 27616.3.2寄存器访问保护 27616.3.3调试模式 27616.4IWDG寄存器描述 27716.4.1键寄存器(IWDG_KR) 27716.4.2预分频寄存器(IWDG_PR) 27816.4.3重装载寄存器(IWDG_RLR) 27816.4.4状态寄存器(IWDG_SR) 27916.4.5IWDG寄存器映像 279 17窗口看门狗(WWDG) 28017.1WWDG简介28017.2WWDG主要特性 28017.3WWDG功能描述 28017.4如何编写看门狗超时程序 28117.5调试模式28217.6寄存器描述28217.6.1控制寄存器(WWDG_CR) 28217.6.2配置寄存器(WWDG_CFR) 28317.6.3状态寄存器(WWDG_SR) 28317.6.4WWDG寄存器映像 284 18灵活的静态存储器控制器(FSMC) 28518.1FSMC功能描述28518.2框图28518.3AHB接口28618.3.1支持的存储器和操作 28618.4外部设备地址映像 28718.4.1NOR和PSRAM地址映像 28818.4.2NAND和PC卡地址映像 28818.5NOR闪存和PSRAM控制器 28918.5.1外部存储器接口信号 29018.5.2支持的存储器及其操作 29118.5.3时序规则 29118.5.4NOR闪存和PSRAM时序图 29118.5.5同步的成组读 30418.5.6NOR闪存和PSRAM控制器寄存器 30818.6NAND闪存和PC卡控制器 31318.6.1外部存储器接口信号 31318.6.2NAND闪存/PC卡支持的存储器及其操作 31418.6.3NAND闪存、ATA和PC卡时序图 31418.6.4NAND闪存操作 31518.6.5NAND闪存预等待功能 31618.6.6NAND闪存的纠错码ECC计算(NAND闪存) 31718.6.7NAND闪存和PC卡控制器寄存器 31718.7FSMC寄存器地址映象 324 19SDIO接口(SDIO) 32519.1SDIO主要功能32519.2SDIO总线拓扑32519.3SDIO功能描述32819.3.1SDIO适配器 32919.3.2SDIO AHB接口 33619.4卡功能描述33619.4.1卡识别模式 33619.4.2卡复位33619.4.3操作电压范围确认 33719.4.4卡识别过程 33719.4.5写数据块 33819.4.6读数据块 33819.4.7数据流操作,数据流写入和数据流读出(只适用于多媒体卡) 33819.4.8擦除:成组擦除和扇区擦除 33919.4.9宽总线选择和解除选择 34019.4.10保护管理 34019.4.11卡状态寄存器 34219.4.12SD状态寄存器 34419.4.13SD I/O模式 34719.4.14命令与响应 34819.5响应格式35019.5.1R1(普通响应命令) 35119.5.2R1b 35119.5.3R2(CID、CSD寄存器) 35119.5.4R3(OCR寄存器) 35119.5.5R4(快速I/O) 35219.5.6R4b 35219.5.7R5(中断请求) 35219.5.8R6(中断请求) 35319.6SDIO I/O卡特定的操作 35319.6.1使用SDIO_D2信号线的SDIO I/O读等待操作 35319.6.2使用停止SDIO_CK的SDIO读等待操作 35319.6.3SDIO暂停/恢复操作 35419.6.4SDIO中断 35419.7CE-ATA特定操作 35419.7.1命令完成指示关闭 35419.7.2命令完成指示使能 35419.7.3CE-ATA中断 35419.7.4中止CMD61 35419.8硬件流控制35419.9SDIO寄存器35519.9.1SDIO电源控制寄存器(SDIO_POWER) 35519.9.2SDIO时钟控制寄存器(SDIO_CLKCR) 35519.9.3SDIO参数寄存器(SDIO_ARG) 35619.9.4SDIO命令寄存器(SDIO_CMD) 35619.9.5SDIO命令响应寄存器(SDIO_RESPCMD) 35719.9.6SDIO响应1..4寄存器(SDIO_RESPx) 35719.9.7SDIO数据定时器寄存器(SDIO_DTIMER) 35819.9.8SDIO数据长度寄存器(SDIO_DLEN) 35819.9.9SDIO数据控制寄存器(SDIO_DCTRL) 35819.9.10SDIO数据计数器寄存器(SDIO_DCOUNT) 36019.9.11SDIO状态寄存器(SDIO_STA) 36019.9.12SDIO清除中断寄存器(SDIO_ICR) 36119.9.13SDIO中断屏蔽寄存器(SDIO_MASK) 36219.9.14SDIO FIFO计数器寄存器(SDIO_FIFOCNT) 36419.9.15SDIO数据FIFO寄存器(SDIO_FIFO) 36419.9.16SDIO寄存器映像 365 20USB全速设备接口(USB) 36620.1USB简介36620.2USB主要特征36620.3USB功能描述36720.3.1USB功能模块描述 36820.4编程中需要考虑的问题 36920.4.1通用USB设备编程 36920.4.2系统复位和上电复位 36920.4.3双缓冲端点 37220.4.4同步传输 37320.4.5挂起/恢复事件 37420.5USB寄存器描述 37520.5.1通用寄存器 37520.5.2端点寄存器 38020.5.3缓冲区描述表 38220.5.4USB寄存器映像 385 21控制器局域网(bxCAN) 38721.1bxCAN简介38721.2bxCAN主要特点 38721.2.1总体描述 38821.3bxCAN工作模式 38921.3.1初始化模式 39021.3.2正常模式 39021.3.3睡眠模式(低功耗) 39021.3.4测试模式 39021.3.5静默模式 39021.3.6环回模式 39121.3.7环回静默模式 39121.4bxCAN功能描述 39221.4.1发送处理 39221.4.2时间触发通信模式 39321.4.3接收管理 39321.4.4标识符过滤 39521.4.5报文存储 39821.4.6出错管理 39921.4.7位时间特性 40021.5bxCAN中断40221.6CAN 寄存器描述 40321.6.1寄存器访问保护 40321.6.2控制和状态寄存器 40321.6.3邮箱寄存器 41121.6.4CAN过滤器寄存器 41521.6.5bxCAN寄存器列表 419 22串行外设接口(SPI) 42222.1SPI简介42222.2SPI和I2S主要特征 42222.2.1SPI特征42222.2.2I2S功能42322.3SPI功能描述42422.3.1概述42422.3.2SPI从模式 42622.3.3SPI主模式 42722.3.4单工通信 42822.3.5状态标志 42822.3.6CRC计算 42922.3.7利用DMA的SPI通信 42922.3.8错误标志 43022.3.9关闭SPI 43022.3.10SPI中断43022.4I2S功能描述43122.4.1I2S功能描述 43122.4.2支持的音频协议 43222.4.3时钟发生器 43722.4.4I2S主模式 43822.4.5I2S从模式 43922.4.6状态标志位 44022.4.7错误标志位 44122.4.8I2S中断44122.4.9DMA功能 44122.5SPI和I2S寄存器描述 44222.5.1SPI控制寄存器1(SPI_CR1)(I2S模式下不使用) 44222.5.2SPI控制寄存器2(SPI_CR2) 44322.5.3SPI 状态寄存器(SPI_SR) 44422.5.4SPI 数据寄存器(SPI_DR) 44522.5.5SPI CRC多项式寄存器(SPI_CRCPR) 44622.5.6SPI Rx CRC寄存器(SPI_RXCRCR) 44622.5.7SPI Tx CRC寄存器(SPI_TXCRCR) 44622.5.8SPI_I2S配置寄存器(SPI_I2S_CFGR) 44722.5.9SPI_I2S预分频寄存器(SPI_I2SPR) 44822.5.10SPI 寄存器地址映象 449 23I2C接口45023.1I2C简介45023.2I2C主要特点45023.3I2C功能描述45123.3.1模式选择 45123.3.2I2C从模式 45223.3.3I2C主模式 45423.3.4错误条件 45623.3.5SDA/SCL线控制 45723.3.6SMBus 45723.3.7DMA请求 45923.3.8包错误校验(PEC) 46023.4I2C中断请求46123.5I2C调试模式46223.6I2C寄存器描述46223.6.1控制寄存器1(I2C_CR1) 46223.6.2控制寄存器2(I2C_CR2) 46423.6.3自身地址寄存器1(I2C_OAR1) 46523.6.4自身地址寄存器2(I2C_OAR2) 46523.6.5数据寄存器(I2C_DR) 46523.6.6状态寄存器1(I2C_SR1) 46623.6.7状态寄存器2 (I2C_SR2) 46823.6.8时钟控制寄存器(I2C_CCR) 46923.6.9TRISE寄存器(I2C_TRISE) 47023.6.10I2C寄存器地址映象 471 24通用同步异步收发器(USART) 47224.1USART介绍47224.2USART主要特性 47224.3USART功能概述 47324.3.1USART 特性描述 47424.3.2发送器47524.3.3接收器47724.3.4分数波特率的产生 48024.3.5多处理器通信 48124.3.6校验控制 48224.3.7LIN(局域互联网)模式 48324.3.8USART 同步模式 48524.3.9单线半双工通信 48724.3.10智能卡48724.3.11IrDA SIR ENDEC 功能块 48824.3.12利用DMA连续通信 49024.3.13硬件流控制 49124.4USART中断请求 49224.5USART模式配置 49324.6USART寄存器描述 49424.6.1状态寄存器(USART_SR) 49424.6.2数据寄存器(USART_DR) 49524.6.3波特比率寄存器(USART_BRR) 49624.6.4控制寄存器1(USART_CR1) 49624.6.5控制寄存器2(USART_CR2) 49824.6.6控制寄存器3(USART_CR3) 49924.6.7保护时间和预分频寄存器(USART_GTPR) 50124.6.8USART寄存器地址映象 502 25器件电子签名 50325.1存储器容量寄存器 50325.1.1闪存容量寄存器 50325.2产品唯一身份标识寄存器(96位) 503 26调试支持(DBG) 50526.1概况50526.2ARM参考文献50626.3SWJ调试端口(serial wire and JTAG) 50626.3.1JTAG-DP和SW-DP切换的机制 50726.4引脚分布和调试端口脚 50726.4.1SWJ调试端口脚 50726.4.2灵活的SWJ-DP脚分配 50726.4.3JTAG脚上的内部上拉和下拉 50826.4.4利用串行接口并释放不用的调试脚作为普通I/O口 50826.5STM32F10xxx JTAG TAP 连接 50926.6ID 代码和锁定机制 50926.6.1微控制器设备ID编码 50926.6.2边界扫描TAP 51026.6.3Cortex-M3 TAP 51026.6.4Cortex-M3 JEDEC-106 ID代码 51126.7JTAG调试端口51126.8SW调试端口51226.8.1SW协议介绍 51226.8.2SW协议序列 51226.8.3SW-DP状态机(Reset, idle states, ID code) 51326.8.4DP和AP读/写访问 51326.8.5SW-DP寄存器 51326.8.6SW-AP寄存器 514 26.9对于JTAG-DP或SWDP都有效的AHB-AP (AHB 访问端口) 514 26.10内核调试515 26.11调试器主机在系统复位下的连接能力 515 26.12FPB (Flash patch breakpoint) 515 26.13DWT(data watchpoint trigger) 516 26.14ITM (instrumentation trace macrocell) 51626.14.1概述51626.14.2时间戳包,同步和溢出包 516 26.15MCU调试模块(MCUDBG) 51726.15.1低功耗模式的调试支持 51726.15.2支持定时器、看门狗、bxCAN和I2C的调试 51826.15.3调试MCU配置寄存器 518 26.16TPIU (trace port interface unit) 52026.16.1导言52026.16.2跟踪引脚分配 52026.16.3TPUI格式器 52226.16.4TPUI帧异步包 52226.16.5同步帧包的发送 52226.16.6同步模式 52226.16.7异步模式 52326.16.8TRACECLKIN在STM32F10xxx内部的连接 52326.16.9TPIU寄存器 52326.16.10配置的例子 524 26.17DBG寄存器地址映象 5241 文中的缩写1.1 寄存器描述表中使用的缩写列表在对寄存器的描述中使用了下列缩写:read / write (rw) 软件能读写此位。

MEMORY存储芯片STM32F103C8T6中文规格书