DDS课程设计 (1)

基于DDS的信号发生器单片机期末课程设计

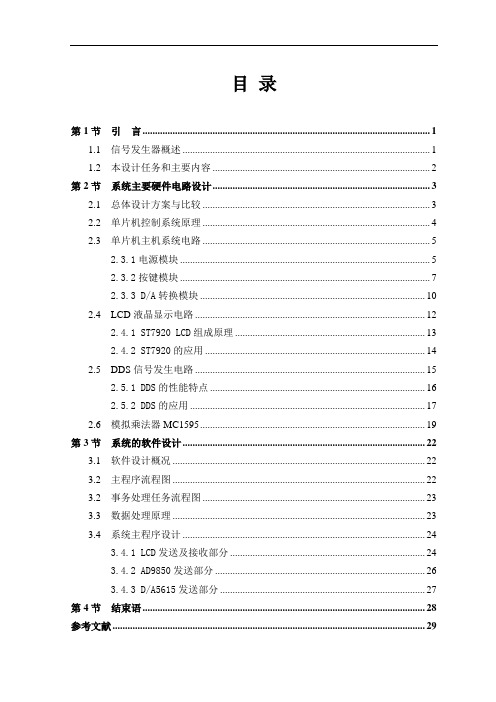

目录第1节引言 (1)1.1 信号发生器概述 (1)1.2 本设计任务和主要内容 (2)第2节系统主要硬件电路设计 (3)2.1 总体设计方案与比较 (3)2.2 单片机控制系统原理 (4)2.3 单片机主机系统电路 (5)2.3.1电源模块 (5)2.3.2按键模块 (7)2.3.3 D/A转换模块 (10)2.4 LCD液晶显示电路 (12)2.4.1 ST7920 LCD组成原理 (13)2.4.2 ST7920的应用 (14)2.5 DDS信号发生电路 (15)2.5.1 DDS的性能特点 (16)2.5.2 DDS的应用 (17)2.6 模拟乘法器MC1595 (19)第3节系统的软件设计 (22)3.1 软件设计概况 (22)3.2 主程序流程图 (22)3.2 事务处理任务流程图 (23)3.3 数据处理原理 (23)3.4 系统主程序设计 (24)3.4.1 LCD发送及接收部分 (24)3.4.2 AD9850发送部分 (26)3.4.3 D/A5615发送部分 (27)第4节结束语 (28)参考文献 (29)基于DDS技术的信号发生器第1节引言信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

本设计分五个模块:单片机控制及显示模块、数模(D/A)转换模块、波形产生模块、输出显示模块、电源模块。

使用AT89C51作为主控制台,结合DDS芯片ADC9850产生1HZ~10MHZ频率可调的三种信号波(正弦波、方波、三角波),步进为1HZ;配合使用DA5615采集电压通过模拟乘法器和AD811放大电压,在50 负载条件下输出正弦波信号的电压峰-峰值Vopp在0~5V范围内可调,调节步进间隔可达到0.1V,通过ZLG7289控制按键进行设置。

系统采用液晶屏操作方式,显示清晰,简洁明了,且有一定的系统稳定性。

DDS函数信号发生器的设计与实现-课程设计.docx

DDS函数信号发生器的设计与实现•课程设计DDS函数信号发生器的设计与实现一、主要功能要求:1、设计任务(1)正弦波、三角波、方波、锯齿波输出频率范围:1KHZ~1MHZ(2)具有频率设置功能,频率步骤:100HZ;(3)输出信号频率定度:优于10 A4(4)输出电压幅度:在5K负载电阻上的电压峰一一峰值Vopp^lV;(5)失真度:用示波器观察使无明显失真。

2、基本要求:(1)掌握采用FPGA硬件特性、及软件开发工具MAXPLUS II的使用。

(2)掌握DDS函数信号发生器的原理,并采用VIIDL语言设计DDS内核单元。

(3 )掌握单片机与DDS单无连接框图原理,推导出频率控制字、相位控制字的算法。

(4)设计键盘输入电路和程序并调试。

掌握键盘和显示(LCD1602)配合使用的方法和技巧。

(5)掌握硬件和软件联合调试的方法。

(6)完成系统硬件电路的设计和制作。

(7)完成系统程序的设计。

(8)完成整个系统的设计、调试和制作。

(9)完成课程设计报告。

3、捉高部分:(1)三角波、方波输出频率范围:1KHZ〜1MHZ;(2)产生二进制PSK、ASK信号:再50KHZ固定频率载波进行二进制键控,二进制基带序列码速率固定为10Kbps,二进制基带序列信号自行产生。

(3)设计高速DA转换电路。

4、发挥部分:(1)对数据频率进行倍频。

二、整体设计框图及整机概述:1、DDS的实现原理:它建立在采样定理的基础上,首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后再通过查表将数据读出,经过D/A转换器转换成模拟量,把存入的波形重新合成出来.2、整体设计框图图一DDS函数信号发生器系统框图结构3、整机概述:整个DDS信号发生器由单片机子系统,DDS子系统,模拟子系统三部分组成。

单片机子系统由单片机、人机接口组成,人机接口由液晶显示器和键盘组成,通过键盘选择信号波形和输入信号频率,液晶用来显示波的类型和波当前的频率值。

数字信号处理课程设计

index=1; while n<=N IND(n)=index; index=index+k; index=mod(index, 2^Bits); n=n+1; end m=IND; IND=IND+1; y=LUT(IND); subplot(212) plot(t,y) figure(1); axis([0 endtime-1.2 1.2]); grid on 3、测试结果 ⑴输入 dds(10,100,10,0.5),输出波形图如图 2

结论:实验测得输出频率为 10Hz,与理论值相符,实验正确。

题目二

数字锁相环的 MATLAB 实现 及仿真

一、 设计目的

1、理解数字锁相环的原理,熟悉实现流程。 2、学会用 MATlab 进行一些信号分析

二、 数字锁相环原理

1、数字锁相环简介 锁相环 (phase-locked loop)为无线电发射中使频率较为稳定的一种方法, 主要有 VCO(压控振荡器)和 PLL IC (锁相环集成电路),压控振荡器给出一个 信号,一部分作为输出,另一部分通过分频与 PLL IC 所产生的本振信号作相位比 较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则 PLL IC 的电压输出端的电压发生变化,去控制 VCO,直到相位差恢复,达到锁频 的目的, 是一种能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环 电子电路。 锁相环的用途是在收、 发通信双方建立载波同步或位同步,分为模拟锁相环 和数字锁相环两种。 随着数字电路技术的发展,数字锁相环以其独有的优势在调 制解调、频率合成、FM 立体声解码、彩色副载波同步、图象处理等各个方面得 到了广泛的应用。 数字锁相环不仅吸收了数字电路可靠性高、体积小、价格低 等优点, 还解决了模拟锁相环的直流零点漂移、器件饱和及易受电源和环境温度 变化等缺点, 此外还具有对离散样值的实时处理能力,已成为锁相技术发展的方 向。 2、DPLL 基本模型和原理 全数字锁相环包括数字鉴相鉴频器(PFD) 、数字滤波器(LPF) 、数字振荡 器(NCO)三部分,如下图所示:

dds信号源课程设计

dds信号源课程设计一、课程目标知识目标:1. 学生能理解DDS(直接数字频率合成器)信号源的基本原理,掌握其工作流程。

2. 学生能掌握DDS信号源的关键参数,如频率、相位、幅度等,并了解它们之间的关系。

3. 学生能解释DDS信号源在电子技术中的应用,如信号发生、通信系统等。

技能目标:1. 学生能够操作DDS信号源硬件,进行基本的信号生成与调制。

2. 学生能够利用相关软件对DDS信号源进行编程控制,实现特定信号的输出。

3. 学生能够通过实验,分析DDS信号源的性能,提出优化方案。

情感态度价值观目标:1. 学生对电子技术产生兴趣,培养探索精神和创新意识。

2. 学生在实验和讨论过程中,培养团队合作精神和沟通能力。

3. 学生认识到DDS信号源在科技发展中的重要作用,增强社会责任感和使命感。

课程性质:本课程为电子技术实践课程,结合理论讲解和实验操作,提高学生对DDS信号源的理解和应用。

学生特点:学生为高中年级,具备一定的电子技术基础,对实验操作感兴趣,但需引导深入理解理论知识。

教学要求:注重理论与实践相结合,鼓励学生动手实践,培养解决实际问题的能力。

在教学过程中,关注学生个体差异,提供针对性的指导。

通过课程学习,使学生能够将所学知识应用于实际电子技术领域。

二、教学内容1. DDS信号源原理介绍:- 数字频率合成技术背景- DDS信号源基本工作原理- 频率、相位、幅度控制原理2. DDS信号源硬件结构:- 主要组成部分及其功能- 常见DDS芯片介绍- 硬件连接与操作方法3. DDS信号源编程控制:- 编程接口与协议- 常用编程语言及工具- 实例演示:信号生成与调制4. DDS信号源应用案例分析:- 信号发生器- 通信系统- 频率合成器5. 实验教学:- 实验一:DDS信号源基本操作- 实验二:信号生成与调制- 实验三:性能分析与优化6. 教学进度安排:- 第一周:原理介绍与硬件结构学习- 第二周:编程控制与实例演示- 第三周:应用案例分析- 第四周:实验教学与实践教学内容关联教材章节:- 第一章:电子技术基础- 第二章:数字频率合成技术- 第三章:DDS信号源硬件与编程- 第四章:实验与实践三、教学方法本课程采用以下多样化的教学方法,以激发学生的学习兴趣和主动性,提高教学效果:1. 讲授法:- 对于DDS信号源的基本原理、硬件结构、编程控制等理论知识,采用讲授法进行系统讲解,使学生掌握必要的基础知识。

-基于DDS的信号发生器单片机期末课程设计

目录第1节引言 (1)1.1 信号发生器概述 (1)1.2 本设计任务和主要内容 (2)第2节系统主要硬件电路设计 (3)2.1 总体设计方案与比较 (3)2.2 单片机控制系统原理 (4)2.3 单片机主机系统电路 (5)2.3.1电源模块 (5)2.3.2按键模块 (7)2.3.3 D/A转换模块 (10)2.4 LCD液晶显示电路 (12)2.4.1 ST7920 LCD组成原理 (13)2.4.2 ST7920的应用 (14)2.5 DDS信号发生电路 (15)2.5.1 DDS的性能特点 (16)2.5.2 DDS的应用 (17)2.6 模拟乘法器MC1595 (19)第3节系统的软件设计 (22)3.1 软件设计概况 (22)3.2 主程序流程图 (22)3.2 事务处理任务流程图 (23)3.3 数据处理原理 (23)3.4 系统主程序设计 (24)3.4.1 LCD发送及接收部分 (24)3.4.2 AD9850发送部分 (26)3.4.3 D/A5615发送部分 (27)第4节结束语 (28)参考文献 (29)基于DDS技术的信号发生器第1节引言信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

本设计分五个模块:单片机控制及显示模块、数模(D/A)转换模块、波形产生模块、输出显示模块、电源模块。

使用AT89C51作为主控制台,结合DDS芯片ADC9850产生1HZ~10MHZ频率可调的三种信号波(正弦波、方波、三角波),步进为1HZ;配合使用DA5615采集电压通过模拟乘法器和AD811放大电压,在50 负载条件下输出正弦波信号的电压峰-峰值Vopp在0~5V范围内可调,调节步进间隔可达到0.1V,通过ZLG7289控制按键进行设置。

系统采用液晶屏操作方式,显示清晰,简洁明了,且有一定的系统稳定性。

【EDA课程设计】--”DDS信号发生器“

电子课程设计------DDS信号发生器合成器学院:专业班级:姓名:学号:指导老师:2012年12月直接数字频率合成器(DDS)一、设计任务与要求直接数字频率综合技术,即DDS技术,是一种新型的频率合成技术和信号产生方法。

利用EDA技术和FPGA实现直接数字频率合成器DDS的设计。

设计要求:1、利用QuartusII软件实验箱实现DDS的设计;2、通过实验箱上的开关输入DDS的频率和相位控制字,并能用示波器观察加以验证;3、系统具有清零和使能的功能;4、DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的ROM实现。

二、总体框图图1 DDS总体框图1、模块的功能(1)频率预置和调节电路不变量K称作相位增量,也叫频率控制字。

此模块实现频率控制量的输入。

(2)相位累加器相位累加器是一个带有累加功能的N位加法器,它以设定的N位频率控制字K作为步长进行线性累加,当其和满时,计数器清零,并进行重新运算,它使输出频率正比于时钟频率和相位增量之积。

(3) 相位寄存器相位寄存器是一个N 位的寄存器,它对输入端输入的数据进行寄存,当下一个时钟到来时,输出寄存的数据。

图2 相位累加器相位累加器的组成=N 位加法器+N 位寄存器相位累加器的作用:在时钟的作用下,进行相位累加注意:当相位累加器累加满量时就会产生一次溢出,完成一个周期 的动作。

(4) 正弦查找表正弦查找表ROM 是DDS 最关键的部分,也是最复杂的部分,设计时首先需对正弦函数进行离散采样,接着将采样的结果放到ROM 模块的对应存储单元中,每一位地址对应一个数值,输出为8位。

ROM 中必须包含完整的正弦采样值,此设计采样256点,而且还要注意避免在按地址读取ROM 内容时可能引起的不连续点,避免量化噪音集中于基频的谐波上。

作用:进行波形的相位----幅值转换 原理:ROM 的N 位地址把0° 360°的正弦角度离散成具有2N 个样值的序列 ROM 的D 位数据位则2N 个样值的幅值量化为D 位二进制数据(5) D/A 转换器D/A 转换器的作用:把已经合成的正弦波的数字量转换成模拟量。

数电dds课程设计

数电dds课程设计英文回答:For my digital design and simulation (DDS) course project, I was tasked with designing a circuit usingdigital logic gates. I chose to design a 4-bit binary counter circuit. This circuit counts from 0 to 15 and then resets back to 0.To design this circuit, I first needed to understand the functionality of a binary counter. A binary counter is a sequential circuit that counts in binary from 0 to its maximum value and then resets back to 0. In a 4-bit binary counter, there are four flip-flops, each representing a bit position (Q3, Q2, Q1, Q0). The clock signal is connected to the clock inputs of all the flip-flops.The circuit design involves connecting the outputs of the flip-flops to the inputs of the next flip-flop. For example, the output Q0 of the first flip-flop is connectedto the input D1 of the second flip-flop. This creates a ripple effect, where the least significant bit (LSB) toggles on each clock pulse, and the other bits toggle when the previous bit transitions from 1 to 0.To implement the reset functionality, I used a combination of logic gates. When the counter reaches its maximum value (1111 in binary), the output of the fourth flip-flop (Q3) is connected to a NAND gate along with the clock signal. The output of the NAND gate is connected to the reset inputs of all the flip-flops, causing them to reset back to 0.I simulated the circuit using a digital logic simulator software. I provided clock pulses and observed the outputs of the flip-flops. The simulation showed that the circuit correctly counts from 0 to 15 and then resets back to 0, as expected.Overall, designing this 4-bit binary counter circuit was a challenging but rewarding experience. It allowed me to apply the knowledge I gained in the DDS course andunderstand the practical implementation of digital logic gates.中文回答:在我的数字设计与模拟(DDS)课程项目中,我被要求设计一个使用数字逻辑门的电路。

DDS正弦信号发生器课程设计报告

EDA设计报告----基于DDS的正弦信号发生器专业:班级:学号:姓名:目录一、DDS信号发生器原理 (2)二、基于DDS的正弦信号发生器设计实现 (3)三、DDS信号发生器原理图 (6)四、仿真结果 (7)五、硬件调试结果及分析 (7)六、心得与体会 (9)一. DDS信号发生器原理对于正弦信号发生器, 它的输出可以用下式来描述:其中, Sout是指该信号发生器的输出信号波形, fout 只输出信号对应的频率。

上式的表述对于时间t是连续的, 为了用数字逻辑实现该表达式, 必须进行离散化处理, 用基准时钟clk进行抽样, 令正弦信号的的相位θ为在一个clk周期Tclk, 相位θ的变化量为其中fclk指clk的频率对于2π可以理解为“满”相位, 为了对Δθ进行数字量化, 把2π切割成2N, 用词每个clk周期的相位增量Δθ用量化值BΔθ来描述: BΔθ=(Δθ·2N)/2π, 且BΔθ为整数与上式联立可得:显然, 信号发生器可以描述其中θk-1指前一个clk周期的相位值, 同样得出由以上推倒可以得出, 只要对相位的量化值进行简单的累加运算, 就可以得到正弦信号的当前相位值, 而用于累加的香味增量量化值BΔθ决定了信号的输出频率fout并呈现简单的线性关系。

直接数字合成器DDS就是根据以上原理而设计的数控频率合成器, 下图为其基本DDS结构, 主要有相位累加器、相位调制器、正弦ROM查找表构成图中的相位累加器、相位调制器、正弦ROM查找表是DDS结构中的数字部分,二、基于DDS的正弦信号发生器设计实现根据设计原理框图分别设计出加法器、寄存器、正弦波ROM。

1.32位加法器ADDER32设计在原理图文件文件下在空白处双击, 单击“MegaWizard Plug-In Manager”选择第一项选择器件为cyclone, 语言方式为VerilogHDL。

在算数项Arithmetic中选择计数器LPM_ADD_SUB.存于所建工程文件夹下命名为ADDER32.单击NEXT,进入以后对话框后选择32位加法器工作模式选择有一位加法进位输出, 选择有符号加法方式, 选择2级流水线工作模式 ,此时该加法器变为有时序电路的模块, 最后至finish按钮, 编辑完成。

最新电子线路课程设计DDS

电子线路课程设计1直接数字频率合成器234567891011姓名:1213学号:1415院系:电光学院16指导老师:171819完成时间:202122目录摘要 (3)2324ABSTRACT (3)25一、实验设计内容及要求 (4)261、内容 (4)272、设计基本要求 (4)283、设计提高部分 (5)二、设计方案 (5)2930三、子模块电路设计 (7)311、分频模块 (7)32(1)2分频电路 (7)33(2)5分频电路 (8)34(3)48分频电路 (9)35(4)100分频电路 (10)36(5)1000分频电路 (10)2、频率,相位预制和调节模块 (11)3738(1)频率控制字电路 (11)39(2)相位控制字电路 (12)40(3)同步寄存器 (13)413、累加器模块 (13)424、加法器模块 (14)435、波形存储器 (15)44(1)正弦波 (15)45(2)余弦波 (18)46四、提高设计部分 (19)471、按键输入频率或相位控制字 (19)48(1)二进制——BCD码转码电路 (20)49(2)译码显示模块 (21)502、测频模块 (22)513、多种波形 (24)52(1)锯齿波 (24)53(2)方波 (25)54五、总电路 (28)55六、调试、仿真、下载 (28)56七、实验中遇到的问题及解决方法 (29)57八、实验收获与体会 (29)58九、参考文献 (30)59摘要60本报告主要介绍设计一个具有清零、使能、频率控制、相位控制、输出多种61波形(包括正余弦、锯齿波、方波)、经过D/A转换之后能在示波器上显示的直62接数字频率合成器。

报告分析了DDS的设计原理及电路的工作原理。

电路设计借助了QuartusII 7.0软件,并在SmartSOPC实验系统中进行硬件测试6364关键词:QuartusII SmartSOPC 正弦波频率控制相位控制测频6566Abstract67The report mainly intraoduced designing Direct digital synthesizer 68can control using、reset、change frequency and phase、output various wave 69form(including sine(cosine),sawtooth,square waveform)and after 70conversion after also displayed on the oscilloscope。

DDS课程设计 (1)

input [2:0] switchin; wire [9:0] address; output [7:0] q; wire [28:0] length; wire [2:0] keyout; output [6:0] sm_db0; output [6:0] sm_db1; output [6:0] sm_db2; output [6:0] sm_db3; output [2:0] led; key(clk,keyin,keyout); control(clk,keyout,switchin,length); counter(clk,length,address); shumaguan(clk,length,sm_db0,sm_db1,sm_db2,sm_db3,led); lpm_rom0(address,clk,q); endmodule module counter(clk,fre_word,address); input clk; output reg [9:0] address; input [28:0] fre_word; reg[28:0] phaseadder; always@(posedge clk) begin phaseadder= phaseadder+ fre_word; address= phaseadder[28:19]; end endmodule

顶层设计采用 Verilog HDL 程序将上面所述的各个模块连接在一起, 就可以得到 DDs 核心 实现模块,实验调试时,可以使用 5MHz 正方波作为系统时钟输入信号。 module sin(clk,keyin,switchin,q,sm_db0,sm_db1,sm_db2,sm_db3,led); input clk; input [2:0] keyin;

dds设计文档

1.设计概述(述一下你的设计,如:设计意图,适用范围以及针对用户群。

同时请简要阐述一下你选用本款 Altera 器件来进行设计的原因。

) 为了能拥有一个操作简单,输出频率精度高且稳定,并且拥有足够宽的输出频率范围,所以本项目设计了基于FPGA的任意波形发生器。

本项目的设计由以下几个模块组成:PS/2键盘,FPGA-ER4CE6F17C8开发板,高速D/A模块,TFT 显示屏。

PS/2键盘主要功能是选择任意波形任意2.功能概述(说明你作品的功能以及如何实现该功能)本次设计的100M-DDS波形发生器外设有PS/2键盘输入,TFT彩屏输出。

本波形发生器有2路输出,第1路为固定零点相位输出,第2路可以选择相位位移。

使用者首先在PS/2键盘输入所需输出的波形选择,按确认键,然后选择相位位移度,按确认键,再输入输出频率,再按确认键,则可以看到TFT彩屏输出要求的波形频率,显示屏同时将波形的相关信息显示出来。

3.性能参数(说明你的设计的性能参数。

如果可能,请再比较一下设计参数和该性能实际的实现情况,并评价一下您所使用的 Altera 器件在设计中的功能。

)在设计中使用了IP核中的PLL功能,使得原本50M的时钟频率上升至100M,并且使用了IP核中的ROM功能,在使用ROM功能时将设置ROM中每位数据的位宽为8以及数据量深度位32,所以此设计的输出波形频率可以达到20M,频率精度能达到100M/2^32=0.02HZ。

4.设计结构(设计框图,或同时给出硬件设计框图和软件流程图)5.设计方法(阐述设计的实现方法和设计实现的步骤,并着重描述如何使用SOPC 概念来实现你的设计)通过PS/2键盘的输入,可以选择输出波形,调节相位输出,调节频率输出。

按键信息发送到FPGA中经过FPGA的处理。

FPGA将需要输出的频率通过公式:K=(2^N)*f0/f1计算,其中K为频率控制字,f0为输出频率,f1位输入频率,得出频率控制字K,FPGA再将频率控制字K通过相位累加器得出一系列数据,这些数据就是ROM中的地址,再将ROM中的地址输出,得出输出数字信号,此数字信号则为输出波形的数字信号,再由D/A模块将数字信号转成模拟信号,将模拟信号通过滤波器得出平滑的曲线信号,同时通过TFT彩屏显示输出波形的各项信息。

eda课程设计dds发生器设计

eda课程设计dds发生器设计一、课程目标知识目标:1. 学生能够理解DDS(Direct Digital Synthesis)发生器的工作原理,掌握其基本组成和功能。

2. 学生能够运用EDA工具进行DDS发生器的电路设计与仿真,并了解其在实际应用中的限制和改进方法。

3. 学生能够掌握DDS发生器中相位累加器、正弦查找表等关键部分的原理和设计要点。

技能目标:1. 学生能够运用所学知识,独立完成DDS发生器的电路设计和仿真,提高解决实际工程问题的能力。

2. 学生能够通过小组合作,进行EDA工具的操作和电路调试,培养团队协作和沟通技巧。

情感态度价值观目标:1. 学生在学习过程中,培养对电子设计自动化(EDA)技术的兴趣,激发探索精神和创新意识。

2. 学生通过DDS发生器设计实践,认识到电子技术在社会发展中的重要作用,增强社会责任感和使命感。

3. 学生在团队合作中,学会尊重他人,提高自我管理和组织协调能力。

课程性质:本课程为电子技术实践课程,以DDS发生器设计为主题,结合EDA工具进行电路设计与仿真。

学生特点:学生具备一定的电子技术基础知识,对EDA工具有一定了解,具有较强的动手能力和学习兴趣。

教学要求:教师需注重理论与实践相结合,引导学生通过实际操作,掌握DDS 发生器的设计方法,培养解决实际问题的能力。

同时,关注学生的情感态度价值观培养,提高综合素质。

通过分解课程目标为具体学习成果,为后续教学设计和评估提供依据。

二、教学内容1. DDS发生器原理介绍:包括DDS发生器的基本工作原理、组成结构及其在信号发生领域的应用优势。

- 相关教材章节:第三章“数字信号发生器”第1节“DDS发生器概述”2. EDA工具使用:以Cadence、Protel等EDA软件为例,介绍DDS发生器设计的基本操作和仿真方法。

- 相关教材章节:第四章“电子设计自动化工具”第2节“电路设计与仿真”3. DDS发生器关键部分设计:- 相位累加器设计原理与实现- 正弦查找表设计与优化- DAC转换器与模拟滤波器设计- 相关教材章节:第三章“数字信号发生器”第2节“DDS发生器的关键部分设计”4. 实践操作与电路调试:指导学生进行DDS发生器电路设计、仿真及硬件测试。

DDS信号源的设计-电子技术课程设计

电子技术设计说明书题目:DDS信号源的设计目录1 选题背景 (2)1.1背景 (2)1.2设计任务 (2)2 方案论证 (2)2.1可选方案 (2)2.2方案比较 (3)3 设计过程 (3)3.1 DDS的基本原理 (3)3.2基本参数确定 (4)3.3 器件选择 (4)4 各单元电路及其工作原理 (4)4.1频率控制字产生电路 (4)4.2相位累加及锁存电路 (5)4.3 正弦函数表 (6)4.4 D/A转换电路 (7)4.5低通滤波电路 (8)4.6 555脉冲产生电路 (8)4.7消抖电路 (9)4.8电源滤波 (9)5 总原理图 (10)6 元器件清单 (11)7 结果分析 (11)8 存在的问题及改进意见 (12)9 总结 (12)参考文献 (14)1 选题背景1.1 背景在电子技术日新月异的形势下,信息技术随之迅猛发展。

信息是存在于客观世界的一种事物现象,人们正是通过信息的获取、存储、传输和处理等来不断认识和改造世界的。

而信号作为信息的载体,是指带有信息的随时间或其他自变量变化的物理量或物理现象,信号时使用极为广泛的基本概念,无论是在自然科学领域,还是在社会科学领域都存在大量的应用研究问题。

直接数字频率合成(Direct Digital Synthesizer,简称:DDS)技术是一种新的全数字的频率合成原理,它从相位的角度出发直接合成所需波形。

这种技术由美国学者J.Tiercy,M.Rader和B.Gold于1971年首次提出,但限于当时的技术和工艺水平,DDS技术仅仅在理论上进行了一些探讨,而没有应用到实际中去。

近30年来,随着超大规模集成(Very Large Scale Integration,简称:VLSI)、复杂可编程逻辑器件(Complex Programmable Logic Device,简称:CPLD)、现场可编程门阵列(Field Programmable Gate Array,简称:FPGA)等技术的出现以及对DDS理论的进一步探讨,使得DDS得到了飞速的发展。

《电工电子技术与基础》教学设计之----DDS正弦信号发生器的设计

《电工电子技术与基础》教学设计之----DDS正弦信号发生器的设计摘要函数信号发生器在教学及科研中应用非常广泛,本设计是采用直接数字频率合成原理设计出符合本课程实验需求的函数信号发生器。

采用的的单片机为AT89C52,DDS芯片为AD9851,采用的功放为AD811。

由单片机AT89C52控制的4*4键盘可输入正弦波频率,液晶显示LCD1602可实现输入频率的显示,实现设计中人机对话。

关键词:函数信号发生器,DDS,AD9851,AD8111.前言1.1本课题背景和意义本文是面向中等职业技术教育的基础课程《电工电子技术与基础》的教学设计,本设计不仅涉及电子线路设计中常用方法和技巧,还包含了所学放大电路、稳压电源、芯片选择等知识内容。

1.2本课题研究内容与主要工作本设计主要利用DDS原理,采用DDS集成芯片AD9851构成具有正弦波输出、频率分辨率高、幅值可调范围大,并且适合实验教学使用的正弦信号发生器。

完成此设计所需要做的工作有:系统拆分模块,并设计模块功能,掌握核心器件的工作原理,利用Multisim进行仿真实验,经过调试设计出系统电路,制作出成品。

1.3本课题的预期研究成果设计并制作出DDS正弦信号发生器,达到输出预置频率正弦波功能,符合输出频率在1HZ~5MHZ范围内,硬件电路在保证达到波形输出幅度1V~10V可调的同时满足其余指标并调试成功。

2.设计内容2.1 系统总体硬件框图与工作原理本设计主要由信号发生部分与信号的放大部分组成,系统的总体硬件框图如图1所示。

本系统的主要工作原理为:单片机作为控制单元控制并协调整个系统的工作,通过键盘预置输入信号的频率,并通过显示模块显示输入的频率。

单片机将控制信号输出到DDS模块,由AD9851控制输出的正弦波信号,因为输出的信号幅度太小且不可调,不便于日常生活的应用,所以输出信号连接了两级放大电路,对信号幅度进行放大,并在相应范围内对幅度进行调节。

实现DDS信号发生器信息处理课程设计

任务书任务一:实现DDS信号发生器(一)输出波形的频率范围100Hz~20kHz;(二)具有频率设置和频率步进功能,频率步进50Hz;(三)在100Hz~20kHz频率范围内,增加矩形波输出信号,频率可任意预置,频率步进20Hz,频率精度0.05%;任务二:简易数字信号传输性能分析仪设计(一)设计并制作一个数字信号发生器;(二)设计三个低通滤波器,用来模拟传输性道的幅频特性。

(三)设计一个伪随机信号发生器用来模拟信道噪声。

(四)利用数字信号发生器产生的时钟信号进行同步,显示数字信号的信号眼图,并测试眼幅度。

任务三:电子琴设计(一)掌握常用的音阶产生原理,运用仿真研究其性能;(二)根据VHDL的语法规则,对系统的逻辑行为进行描述,然后通过综合工具进行电路结构的综合、编译、优化。

扩展为多个音阶的电子琴,并利用FPGA内部的ROM装上多首歌曲,可用手动或自动选择歌曲。

(三)设计控制输入电路、FPGA、显示电路和扬声器电路,实现声音滤波系统的整体实现。

目录任务一:实现DDS信号发生器 (1)(一)设计目的 (1)(二)设计原理 (1)(三)设计结果 (3)(四)心得体会 (5)任务二:简易数字信号传输性能分析仪设计 (6)(一)设计目的 (6)(二)设计原理 (6)(三)设计结果 (7)(四)心得体会 (10)任务三:电子琴设计 (11)(一)设计目的 (11)(二)设计原理 (11)(三)电子琴各模块的设计实现 (12)(四)设计结果 (17)(五)心得体会 (20)四.结束语 (21)五.附录 (22)六.参考文献 (23)任务一:实现DDS信号发生器(一)设计目的1、掌握DDS基本结构2、掌握DSP Builder层次化设计3、掌握DSP Builder中SignalTapII的使用4、掌握频率设置和频率步进功能的算法设计(二)设计原理1、DDS电路的设计算法直接数字频率合成(Direct Digital Synthesizer DDS)技术是从相位概念出发直接合成所需波形的一种新的频率合成技术,这种方法不仅可以产生不同频率的正弦波,而且可以控制波形的初始相位。

现代频率合成技术课程设计—基于.MATLAB的DDS设计与仿真

基于MATLAB的DDS设计与仿真摘要:利用matlab仿真工具建立数字频率合成器DDS的仿真模型.便于我们直截了当地了解DDS的工作原理和各部分模块的功能.而且便于我们分析DDS的工作性能和各种参数指标。

1.实验背景随着技术和器件水平的提高.称之为直接数字式频率合成器(DDS)新的频率合成技术得到飞速的发展。

DDS在相对带宽﹑频率转换时间﹑相位连续性﹑正交输出﹑高分辨力以及集成化等一系列指标方面.已远远超过了传统的频率合成器所达到的水平.完成了频率合成技术的又一次飞跃。

DDS与传统的DS和IS 一起构成了现代频率合成技术体系.将频率合成技术推向了一个新的阶段。

2.DDS的原理:数字频率合成是从相位概念出发直接合成所需波形的一种新技术.它采用一个恒定的输入参数时钟.通过数据处理的方式产生频率﹑相位可调的输出信号。

DDS系统由相位累加器﹑波形ROM﹑D/A转换器和低通滤波器构成。

它具有频率分辨率高﹑频率切换时相位连续等优点。

DDS是继直接合成技术和锁相环式频率合成技术之后的第三代频率合成技术。

他的工作原理是基于相位与幅度的对应关系.通过改变频率控制字(K)来改变相位累加器(位数为N)的相位累加速度.然后在固定时钟的控制下取样.取样得到的相位值(去取相位累加器的高M位)通过相位幅度转换得到与相位值对应的幅度序列.幅度序列通过数模转换及低通滤波得到正弦波输出。

下图为DDS的原理图。

图1 DDS原理框图其中.K为频率控制字.为基准时钟频率.N为相位累加器的字长.D为ROM 数据位及D/A转换器的字长。

相位累加器在基准时钟 的控制字下以步长K做累加.把相加后的结果送至相位累加器的输入.相位累加器一方面在上一时钟周期作用后产生的新的想位数据反馈到自身的输入端.在下一个时钟的作用下继续与频率控制数据K相加.另一方面将这个值作为取样地址输出.送入正弦查找表ROM.作为波形ROM的地址.对波形ROM进行寻址。

波形ROM输出D位的幅度码S(n)经D/A转换器变成阶梯波S(t).再经过低通滤波器平滑后就可以得到合成的信号波形。

基于VHDL的DDS设计

信息与通信工程学院VHDL课程设计2013年5月基于VHDL语言的DDS的设计1.设计内容DDS即直接数字频率合成,是近年来发展起来的一种新的频率合成技术,其主要优点是相对带宽很大,频率转换时间极短(可小于20 ns),频率分辨率很高,全数字化结构便于集成,输出相位连续可调,且频率、相位和幅度均可实现程控。

DDS 能够与计算机技术紧密结合在一起,克服了模拟频率合成和锁相频率合成等传统频率合成技术电路复杂、设备体积较大、成本较高的不足,因此它是一种很有发展前途的频率合成技术。

DDS 技术现已在接收机本振、信号发生器、通信系统、雷达系统等方面得到广泛应用。

数字频率合成器作为一种信号产生装置己经越来越受到人们的重视,它可以根据用户的要求产生相应的波形,具有重复性好、实时性强等优点,己经逐步取代了传统的函数发生器。

我们组本次课程设计的目的是设计基于所学课程VHDL硬件描述语言开发出一个能产生正弦波、方波、三角波、锯齿波等波形的信号源。

2.实现方案2.1 DDS原理直接数字频率合成是采用数字化技术,通过控制相位的变化速度,直接产生各种不同频率、不同波形信号的一种频率合成方法。

DDS 的基本结构如图1 所示,它主要由相位累加器、正弦ROM 表、D/A 转换器和低通滤波器构成。

图1 DDS工作原理图DDS 工作时,在时钟脉冲fc的控制下对频率控制字K 用累加器进行处理以得到相应的相位码,然后由相位码寻址波形存储器进行相位码―幅度编码变换,再经过D/A 数模变换器得到相应的阶梯波,最后经过低通滤波器对阶梯波进行平滑处理即可得到由频率控制字K 决定的频率可调的输出波形。

参考频率源一般是高稳定的晶体振荡器,用于DDS 中各部件的同步工作,因此DDS 输出的合成信号频率稳定度与晶体振荡器是相同的。

在标准频率参考源的控制下,频率控制字K可决定相应的相位增量,相位累加器则以步长K进行线性累加,相位累加器积满时就会产生一次溢出,从而完成一个周期性动作,这个动作周期即是DDS合成信号的一个周期。

dds课程设计

dds课程设计一、教学目标本课程的教学目标是使学生掌握XX学科的基本概念、原理和方法,能够运用所学知识解决实际问题;提高学生的科学思维能力和创新能力;培养学生对XX学科的兴趣和热情,树立正确的科学态度和价值观。

具体来说,知识目标包括:1.掌握XX学科的基本概念、原理和方法;2.了解XX学科的发展趋势和应用领域;3.学会使用XX学科的相关工具和仪器。

技能目标包括:1.能够运用所学知识解决实际问题;2.具备科学实验的基本技能,能够进行实验操作和数据分析;3.能够运用科学思维方法进行创新性研究。

情感态度价值观目标包括:1.培养学生对XX学科的兴趣和热情;2.树立正确的科学态度,注重科学方法和实证精神;3.培养学生的团队协作能力和交流表达能力。

二、教学内容本课程的教学内容主要包括XX学科的基本概念、原理和方法,以及实际应用案例。

具体安排如下:1.第一章:XX学科的基本概念和原理2.第二章:XX学科的方法和技术3.第三章:XX学科的应用案例每章内容包括若干个小节,每个小节结束后安排一次课堂讨论或实验操作,以便巩固所学知识。

三、教学方法为了提高教学效果,我们将采用多种教学方法,包括:1.讲授法:用于传授基本概念、原理和方法;2.讨论法:通过小组讨论,培养学生的思考能力和团队协作精神;3.案例分析法:通过分析实际案例,使学生了解XX学科在现实生活中的应用;4.实验法:安排实验课程,培养学生的实验技能和科学思维方法。

四、教学资源为了支持教学内容和教学方法的实施,我们将准备以下教学资源:1.教材:选用国内权威出版的XX学科教材;2.参考书:推荐学生阅读相关领域的经典著作和最新研究论文;3.多媒体资料:制作课件、教学视频等,以丰富教学手段;4.实验设备:配备必要的实验仪器和设备,保障实验教学的顺利进行。

五、教学评估本课程的评估方式包括平时表现、作业、考试等,以全面客观地反映学生的学习成果。

1.平时表现:通过课堂参与、提问、讨论等环节,评估学生的学习态度和思考能力;2.作业:布置适量作业,评估学生对所学知识的掌握和应用能力;3.考试:安排期中考试和期末考试,评估学生的综合运用能力和知识水平。