CY7C1219H-100AXI中文资料

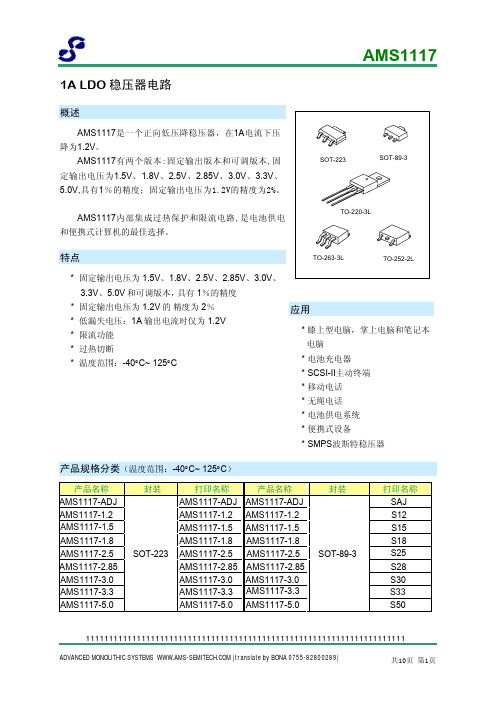

1117中文资料

管脚名称 GND/ADJ

VOUT VIN

I/O

--/O 地/ADJ。

O

输出电压。

I

输入工作电压。

功能

1111111111111111111111111111111111111111111111111111111111111111111111111111111111

ADVANCED MONOLITHIC SYSTEMS (translate by BONA 0755-82800289)

封装 TO-252-2L TO-263-3L

打印名称

AMS1117-ADJ AMS1117-1.2 AMS1117-1.5 AMS1117-1.8 AMS1117-2.5 AMS1117-2.85 AMS1117-3.0 AMS1117-3.3 AMS1117-5.0 AMS1117-2.85 AMS1117-3.0 AMS1117-3.3 AMS1117-5.0

AMS1117-1.5, IOUT=10mΑ, VIN=3.5V ,TJ=25°C 10mA≤IOUT≤1A, 3.0V≤VIN≤10V

1.176 1.2 1.224 V 1.152 1.2 1.248

1.485 1.500 1.515 V 1.470 1.500 1.530

VOUT AMS1117-1.8,

V

0≤IOUT≤1A, 4.25V≤VIN ≤10V

2.790 2.850 2.910

0≤IOUT≤500mA, VIN =4.10V

2.790 2.850 2.910

AMS1117-3.0,

IOUT=10mA, VIN=4.5V,TJ=25°C , 2.970 3.000 3.030 V

VOUT 0≤IOUT≤1A, 4.4V≤VIN≤10V

Sonics Vibra-Cell VCX 750 Manual

军品电池与充器介绍

一:锂离子蓄电池组1.军用7串25.2V锂离子蓄电池产品概述:HML-J7C1OC型是军品级锂离子蓄电池,机壳采用铝合金材料,全密封,各项指标均达到国军标要求,以其优越的品质广泛应用于军工领域。

产品性能:1.安全防爆2.体积小,重量轻,使用方便。

3.自放电小,可长久使用。

技术参数:1、标称电压:25.2V2、额定容量:≥10Ah3、工作温度范围:-40℃~+55℃4、循环寿命:400次5. 电磁兼容性:满足GJB151A-1977中RS103的规定2.军用锂离子蓄电池组产品概述:HML-J4C09C型是军品级锂离子蓄电池,产品主要性能指标:1、标称电压:14.4V2、额定容量:≥9Ah3、工作温度范围:﹣40℃~+55℃4、循环寿命:400次供应配套军品级充电器3.负40度锂离子蓄电池组可根据需求定制,产品各项指标符合国军标要求。

二铅酸蓄电池组1. 12V/165AH型军用高功率免维护启动用蓄电池HMQ-G12165C型是军品级铅酸电瓶,各项指标均达到国军标要求,以其优越的品质广泛应用于军工领域。

产品主要性能指标:额定电压:12 (V)额定容量(20小时率):165(Ah)储备容量: 326 (min)起动电流(零下18度):600(A)外形尺寸(长x宽x高(总高)): 513×223×195(223)(mm)参考重量(干/湿):30.5/42.5(kg)对应国标型号: 6-QW-165适用车型: 重型货车、大客车、斯太尔、金龙经中国船级社认可中国渔业船舶检验局ZY认可2.12V/100Ah型军用铅酸蓄电池HMQ-G12100C型是军品级铅酸电瓶,各项指标均达到国军标要求,以其优越的品质广泛应用于军工领域。

产品主要性能指标:额定电压:12 (V)额定容量(20小时率):100 (Ah)储备容量:182 (min)起动电流(零下18度):440(A)外形尺寸(长x宽x高(总高)): 406×176×210(230)(mm)参考重量(干/湿):19.5/29.5(kg)对应国标型号: 6-QW-100适用车型: 重型货车、越野车、公共汽车:东风、解放、日野KM三:锂离子电池充电器1.军用锂电池充电器产品性能:HMC20-C1202型军用智能充电器是军品级锂离子电池组充电设备,其充电制式为恒流转恒压。

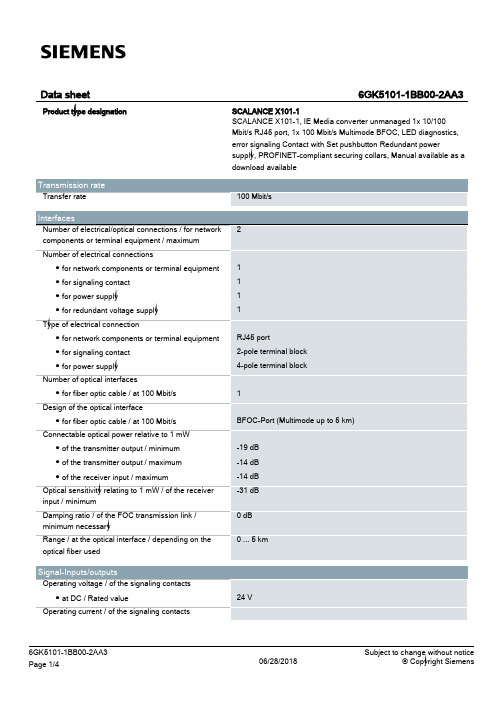

SCALANCE X101-1 商品说明书

24 V

6GK5101-1BB00-2AA3 Page 1/4

06/28/2018

Subject to change without notice © Copyright Siemens

● at DC / maximum

Supply voltage, current consumption, power loss Supply voltage ● external ● external Type of voltage / of the supply voltage Product component / fusing at power supply input Fuse protection type / at input for supply voltage Consumed current ● maximum Power loss [W] ● at DC / at 24 V

Compact 40 mm 125 mm 124 mm 0.55 kg

Yes Yes Yes

No No

FM3611: Class 1, Divison 2, Group A, B, C, D / T.., Class 1, Zone 2, Group IIC, T.. EN 600079-15 II 3 G EEx nA II T.. KEMA 06 ATEX 0021 X

Yes

Yes Yes Yes Yes Yes No 134 y

/snst

/simatic-net https:// /industry/infocenter /bilddb /cax https://

Security information

UL 60950-1, CSA C22.2 No. 60950-1 UL 1604 and UL 2279-15 (Hazardous Location), Class 1 / Division 2 / Group A, B, C, D / T.., Class 1 / Zone 2 / Group IIC / T.. EN 61000-6-3 EN 61000-6-4:2001 EN 61000-6-2:2001, EN 61000-6-4:2001 Yes Yes Yes

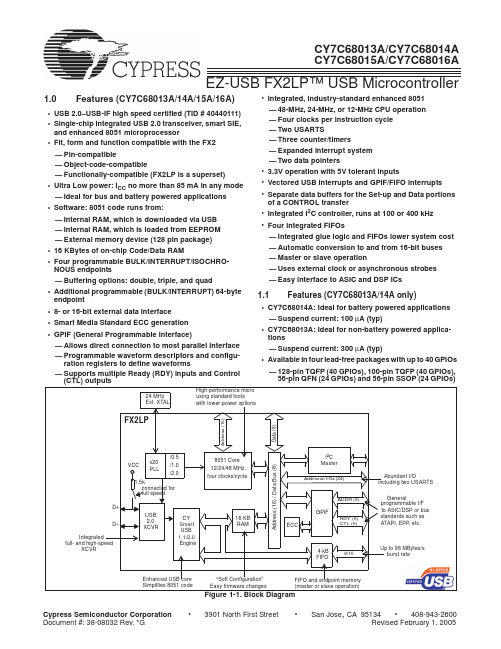

USB控制芯片cy7c68013中文手册

■ CY7C68013A:适合非电池供电应用 ❐ 挂起电流:300 μA (typ)

■ 有五种无铅封装供选择,可包含多达 40 个 GPIO ❐ 128 引脚 TQFP (40 个 GPIO)、 100 引脚 TQFP (40 个 GPIO)、 56 引脚 QFN (24 个 GPIO)、 56 引脚 SSOP (24 个 GPIO)和 56 引脚 VFBGA (24 个 GPIO)

注 1. 以 115 KBaud 的速率运行也是可能的,只要分别针对 UART0、 UART1 或针对二者将 8051 SMOD0 或 SMOD1 位编程为 “1” 即可。

文件编号:001-50431 修订版 **

第 3 页,共 61 页

[+] Feedback

CY7C68013A, CY7C68014A CY7C68015A, CY7C68016A

■ 有商业和工业温度等级供选择 (除 VFBGA 外的所有封装)

Cypress Semiconductor Corporation • 198 Champion Court 文件编号:001-50431 修订版 **

• San Jose, CA 95134-1709 • 408-943-2600

修订时间 2008 年 12 月 11 日

1.2 特色 (仅限 CY7C68015A/16A)

■ CY7C68016A:适合电池供电应用 ❐ 挂起电流:100 μA (typ)

■ CY7C68015A:适合非电池供电应用 ❐ 挂起电流:300 μA (typ)

■ 采用无铅 56 引脚 QFN 封装 (26 个 GPIO) ❐ 比 CY7C68013A/14A 多 2 个 GPIO,可在同样的空间内实现 额外的功能

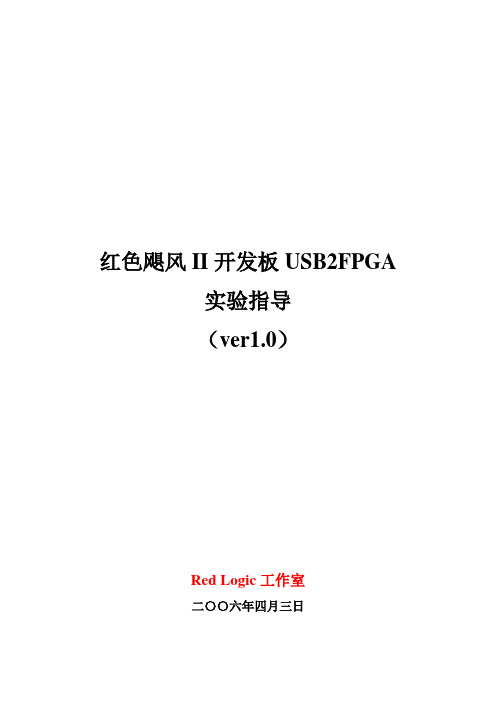

CY7C68013A_slave_fifo说明文档

红色飓风II开发板USB2FPGA实验指导(ver1.0)Red Logic工作室二〇〇六年四月三日目录第一章FX2特性介绍 (3)1.1介绍 (3)1.2结构 (3)1.3特征 (4)第二章Slave FIFO传输 (5)2.1概述 (5)2.2硬件连接 (5)2.3 Slave FIFO的几种传输方式 (6)2.3.1 同步Slave FIFO写 (6)2.3.2 同步Slave FIFO读 (9)2.3.3异步Slave FIFO写 (11)2.3.4异步Slave FIFO读 (12)第三章寄存器设置 (15)3.1 IFCONFIG (15)3.2 PINFLAGSAB/CD (16)3.3 FIFORESET (17)3.4 FIFOPINPOLAR (18)3.5 EPxCFG (18)3.6 EPxFIFOCFG (19)3.7 EPxAUTOINLENH/L (20)3.8 EPxFIFOPFH/L (21)3.9 INPKTEND (22)3.10 OUTPKTEND (22)3.11 EPxFIFOIE和EPxFIFOIRQ (22)3.12PORTACFG (23)3.13 EPxFIFOBCH EPxFIFOBCL (23)3.14 EP24\68FIFOFLAG (24)3.15其它通用寄存器 (25)第四章同步slave fifo测试操作指南 (26)4.1安装软件包 (26)4.2同步写FIFO测试 (26)4.3同步读FIFO测试 (30)4.4同步读写FIFO测试 (31)第五章红色飓风II开发板USB2FPGA软件设计 (33)5.1 68013固件程序设计 (33)5.2 FPGA源代码设计 (35)第六章USB2FPGA硬件原理图 (37)第七章改板后注意的问题 (37)附录1 版本历史 (39)一.FX2特性介绍1.1介绍Cypress Semiconductor公司的EZ-USB FX2是世界上第一款集成USB2.0的微处理器,它集成了USB2.0收发器、SIE(串行接口引擎)、增强的8051微控制器和可编程的外围接口。

BCX51 52 53 PNP中间功率导电器SOT89数据手册说明书

Features• BV CEO > -45V, -60V & -80V• I C = -1A Continuous Collector Current • I CM = -2A Peak Pulse Current• Low Saturation Voltage V CE(sat) <************• Gain Groups 10 and 16• Complementary NPN Types: BCX54, 55, and 56• Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2) • Halogen- and Antimony-Free. "Green" Device (Note 3)•For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAPcapable, and manufactured in IATF 16949 certified facilities),please contact us or your local Diodes representative.https:///quality/product-definitions/Mechanical Data• Case: SOT89• Case Material: Molded Plastic, “Green” Molding Compound; UL Flammability Rating 94V-0• Moisture Sensitivity: Level 1 per J-STD-020•Terminals: Matte Tin Finish Leads; Solderable per MIL-STD-202 Method 208•Weight: 0.052 grams (Approximate)Applications • Medium Power Switching or Amplification Applications • AF Driver and Output StagesOrdering Information (Note 4)Product Compliance Marking Reel Size (inches)Tape Width (mm)Quantity per ReelBCX51TA Standard AA 7 12 1,000 BCX51-13R Standard AA 13 12 4,000 BCX5110TA Standard AC 7 12 1,000 BCX5116TA Standard AD 7 12 1,000 BCX5116TC Standard AD 13 12 4,000 BCX52TA Standard AE 7 12 1,000 BCX5210TA Standard AG 7 12 1,000 BCX5216TA Standard AM 7 12 1,000 BCX53TA Standard AH 7 12 1,000 BCX5310TA Standard AK 7 12 1,000 BCX5316TA Standard AL 7 12 1,000 BCX5316TC Standard AL 13 12 4,000 BCX5316-13R Standard AL 13 12 4,000 BCX5110TC Standard AC 13 12 4,000 BCX51TC Standard AA 13 12 4,000 BCX5210TC Standard AG 13 12 4,000 BCX5216TC Standard AM 13 12 4,000 BCX52TC Standard AE 13 12 4,000 BCX5310TC Standard AK 13 12 4,000 BCX53TCStandardAH13124,000Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.2. See https:///quality/lead-free/ for more information about Diodes Incorporated’s definitions of Halogen- and Antimony-free, "Green" and Lead-free.3. Halogen- and Antimony-free "Green” products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.4. For packaging details, go to our website at https:///design/support/packaging/diodes-packaging/.Top View Device SymbolTop View Pin-Out SOT89E C BMarking InformationAbsolute Maximum Ratings (@ T A = +25°C, unless otherwise specified.)CharacteristicSymbol BCX51 BCX52 BCX53 Unit Collector-Base Voltage V CBO -45 -60 -100 V Collector-Emitter Voltage V CEO -45-60 -80V Emitter-Base Voltage V EBO -5 V Continuous Collector CurrentI C -1 A Peak Pulse Collector Current (Single pulse) I CM -2 Continuous Base CurrentI B -100 mAPeak Pulse Base Current (Single pulse) I BM-200Thermal Characteristics (@ T A = +25°C, unless otherwise specified.)CharacteristicSymbol Value Unit Power Dissipation(Note 5) P D1 W(Note 6) 1.5 (Note 7) 2.0 Thermal Resistance, Junction to Ambient Air (Note 5) R θJA 125 °C/W (Note 6) 83 (Note 7)60 Thermal Resistance, Junction to Lead (Note 8) R θJL 13 °C/W Thermal Resistance, Junction to Case (Note 9)R θJC 27 °C/W Operating and Storage Temperature Range T J, T STG-55 to +150°CESD Ratings (Note 10)CharacteristicSymbol Value Unit JEDEC ClassElectrostatic Discharge - Human Body Model ESD HBM 4,000 V 3A Electrostatic Discharge - Machine ModelESD MM400VCNotes: 5. For a device mounted with the exposed collector pad on 15mm x 15mm 1oz copper that is on a single-sided 1.6mm FR4 PCB; device is measured under still air conditions whilst operating in a steady-state.6. Same as Note 5, except the device is mounted on 25mm x 25mm 1oz copper.7. Same as Note 5, except the device is mounted on 50mm x 50mm 1oz copper.8. Thermal resistance from junction to solder-point (on the exposed collector pad).9. Thermal resistance from junction to the top of the case.10. Refer to JEDEC specification JESD22-A114 and JESD22-A115.xx = Product Type Marking Code, as follows:BCX51 = AA BCX52 = AEBCX53 = AH BCX5110 = AC BCX5210 = AG BCX5310 = AK BCX5116 = AD BCX5216 = AMBCX5316 = ALThermal Characteristics and Derating Information2550751001251500.00.20.40.60.81.0Derating CurveTemperature (°C) M a x P o w e r D i s s i p a t i o n (W )Transient Therm al Im pedanceT h e r m a l R e s i s t a n c e (°C /W )Pulse Width (s)Pulse Power DissipationPulse Width (s)M a x P o w e r D i s s i p a t i o n (W )Copper Area (sqmm)M a x i m u m P o w e r (W )Copper Area (sqmm)T h e r m a l R e s i s t a n c e (°C /W )Note:11. Measured under pulsed conditions. Pulse width ≤ 300µs. Duty cycle ≤ 2%.Typical Electrical Characteristics (@ T A = +25°C, unless otherwise specified.)-I , COLLECTOR CURRENT (A)C h ,D C C U R RE N T G A I NF E Fig. 2 Typical DC Current Gain vs. Collector CurrentDC Current Gain vs. Collector Current -V , COLLECTOR-EMITTER VOLTAGE (V)CE I , C O L L E C T O R C U R R E N T (A )CFig. 1 Typical Collector Current vs. Collector-Emitter VoltageCollector Current vs. Collector-Emitter Voltage -h FE V I CI C V V CETypical Electrical Characteristics (continued.)0.20.40.60.81.0-V , B A S E -E M I T T E R T U R N -O N V O L T A G E (V )B E (O N)-I , COLLECTOR CURRENT (A)C -V , C O L L E C T O R -E M I T T E R S A T U R A T I O N V O L T A G E (V )C E (S A T )Fig. 4 Typical Collector-Emitter Saturation Voltagevs. Collector Current 0.20.40.60.81.01.2-V , B A S E -E M I T T E R S A T U R A T I O N V O L T A G E (V B E (S AT )-I , COLLECTOR CURRENT (mA)C f , G A I N -B A ND W I D T H P R O D U C T (M H z )T Fig. 6 Typical Gain-Bandwidth Product vs. Collector Current V , REVERSE VOLTAGE (V)R C A P A C I T A N C E (p F )Fig. 7 Typical Capacitance Characteristics -V B E (s a t ), B A S E -E M I T T E R S A T U R A T I O N V O L T A G E )-V B E (o n ), B A S E -E M I T T E R T U R N -O N V O L T A G E (V )-V C E (s a t ) , C O L L E C T O R -E M I T T E RC v V RVCE(sat) V I Cf T V I CPackage Outline DimensionsPlease see /package-outlines.html for the latest version.SOT89SOT89Dim Min Max TypA 1.40 1.60 1.50B 0.50 0.62 0.56B1 0.42 0.540.48c 0.35 0.43 0.38D 4.40 4.60 4.50D1 1.62 1.83 1.733D2 1.61 1.81 1.71E 2.40 2.60 2.50E2 2.05 2.35 2.20e - - 1.50H 3.95 4.25 4.10H1 2.63 2.93 2.78L 0.90 1.20 1.05L1 0.327 0.527 0.427z 0.20 0.40 0.30All Dimensions in mmSuggested Pad LayoutPlease see /package-outlines.html for the latest version.SOT89Dimensions Value(in mm)C 1.500G 0.244X 0.580X1 0.760X2 1.933Y 1.730Y1 3.030Y2 1.500Y3 0.770Y4 4.530TOP VIEW。

AC7Z100核心板用户手册说明书

ZYNQ7000开发平台用户手册AC7Z100核心板2 / 31芯驿电子科技(上海)有限公司文档版本控制目录文档版本控制 (2)(一)简介 (4)(二)ZYNQ芯片 (5)(三)DDR3 DRAM (8)(四)QSPI Flash (14)(五)eMMC Flash (15)(六)时钟配置 (16)(七)LED灯 (19)(八)复位电路 (20)(九)电源 (20)(十)结构图 (23)(十一)连接器管脚定义 (23)3 / 314 / 31芯驿电子科技(上海)有限公司(一) 简介AC7Z100(核心板型号,下同)核心板,ZYNQ 芯片是基于XILINX 公司的ZYNQ7000系列的XC7Z100-2FFG900。

ZYNQ 芯片的PS 系统集成了两个ARM Cortex™-A9处理器,AMBA®互连,内部存储器,外部存储器接口和外设。

ZYNQ 芯片的FPGA 内部含有丰富的可编程逻辑单元,DSP 和内部RAM 。

这款核心板使用了4片Micron 的512MB 的DDR3芯片MT41J256M16HA-125,总的容量达4GB 。

其中PS 和PL 端各挂载两片,分别组成32bit 的总线宽度。

PS 端的DDR3 SDRAM 的最高运行速度可达533MHz(数据速率1066Mbps),PL 端的DDR3 SDRAM 的最高运行速度可达800MHz(数据速率1600Mbps)。

另外核心板上也集成了2片256MBit 大小的QSPI FLASH 和8GB 大小的eMMC FLASH 芯片,用于启动存储配置和系统文件。

为了和底板连接,这款核心板的4个板对板连接器扩展出了PS 端的USB 接口,千兆以太网接口,SD 卡接口及其它剩余的MIO 口;也扩展出了ZYNQ 的16对高速收发器GTX 接口;以及PL 端的几乎所有IO 口(114个3.3V IO 和48个1.8V IO ),其中BANK10和BANK11的IO 的电平可以通过更换核心板上的LDO 芯片来修改,满足用户不用电平接口的要求。

CY7C68013A-128AXC中文资料

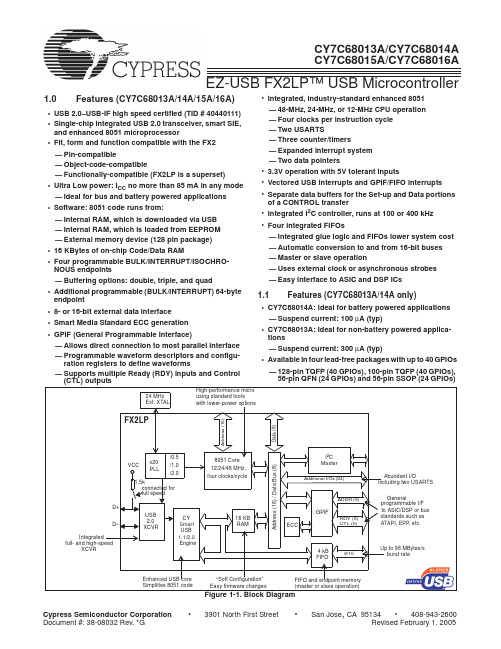

• CY7C68016A: Ideal for battery powered applications — Suspend current: 100 µA (typ) • CY7C68015A: Ideal for non-battery powered applications — Suspend current: 300 µA (typ) • Available in lead-free 56-pin QFN package (26 GPIOs) — 2 more GPIOs than CY7C68013A/14A enabling additional features in same footprint Cypress Semiconductor Corporation’s (Cypress’s) EZ-USB FX2LP (CY7C68013A/14A) is a low-power version of the EZ-USB FX2 (CY7C68013), which is a highly integrated, low-power USB 2.0 microcontroller. By integrating the USB 2.0 transceiver, serial interface engine (SIE), enhanced 8051 microcontroller, and a programmable peripheral interface in a single chip, Cypress has created a very cost-effective solution that provides superior time-to-market advantages with low power to enable bus powered applications. The ingenious architecture of FX2LP results in data transfer rates of over 53 Mbytes per second, the maximum-allowable USB 2.0 bandwidth, while still using a low-cost 8051 microcontroller in a package as small as a 56 QFN. Because it incorporates the USB 2.0 transceiver, the FX2LP is more economical, providing a smaller footprint solution than USB 2.0 SIE or external transceiver implementations. With EZ-USB FX2LP, the Cypress Smart SIE handles most of the USB 1.1 and 2.0 protocol in hardware, freeing the embedded microcontroller for application-specific functions and decreasing development time to ensure USB compatibility. The General Programmable Interface (GPIF) and Master/Slave Endpoint FIFO (8- or 16-bit data bus) provides

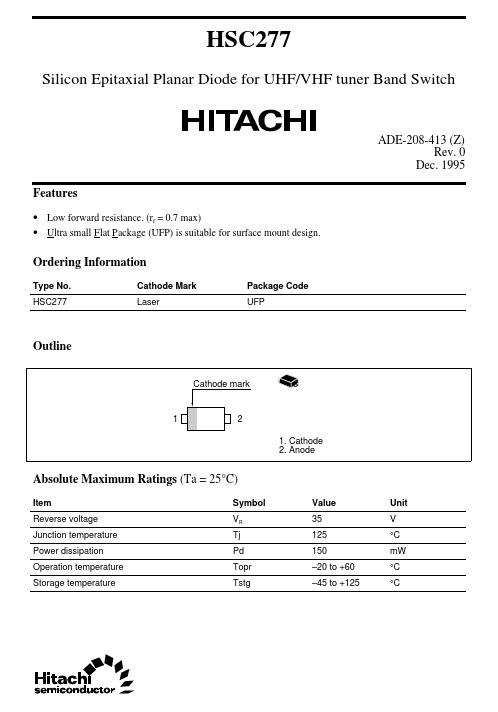

HSC277中文资料

HSC277Silicon Epitaxial Planar Diode for UHF/VHF tuner Band SwitchADE-208-413 (Z)Rev. 0Dec. 1995 Features• Low forward resistance. (r f = 0.7max)• U l tra small F l at P a ckage (UFP) is suitable for surface mount design.Ordering InformationType No.Cathode Mark Package CodeHSC277Laser UFPOutlineAbsolute Maximum Ratings (Ta = 25°C)Item Symbol Value Unit35VReverse voltage VRJunction temperature Tj125°CPower dissipation Pd150mWOperation temperature Topr–20 to +60°CStorage temperature Tstg–45 to +125°CHSC2772Electrical Characteristics (Ta = 25°C)ItemSymbol Min Typ Max Unit Test Condition Reverse voltage V R 35——V I R = 10µA Reverse current I R ——50µA V R = 25V Forward voltage V F —— 1.0V I F = 10mA Capacitance C —— 1.2pF V R = 6V, f = 1MHz Forward resistancer f——0.7ΩI F = 2mA, f = 100MHzFig.1 Forward current Vs. Forward voltageHSC277Fig.2 Reverse current Vs. Reverse voltageFig.3 Capacitance Vs. Reverse voltage3HSC277Fig.4 Forward resistance Vs. Forward current 4HSC277 Package Dimensions5Cautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.Hitachi Asia Pte. Ltd.16 Collyer Quay #20-00Hitachi TowerSingapore 049318Tel: 535-2100Fax: 535-1533URLNorthAmerica : http:/Europe : /hel/ecg Asia (Singapore): .sg/grp3/sicd/index.htm Asia (Taiwan): /E/Product/SICD_Frame.htm Asia (HongKong): /eng/bo/grp3/index.htm Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.Taipei Branch Office3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105)Tel: <886> (2) 2718-3666Fax: <886> (2) 2718-8180Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components)7/F., North Tower, World Finance Centre,Harbour City, Canton Road, Tsim Sha Tsui,Kowloon, Hong Kong Tel: <852> (2) 735 9218Fax: <852> (2) 730 0281 Telex: 40815 HITEC HXHitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 778322Hitachi Europe GmbHElectronic components Group Dornacher Stra§e 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:。

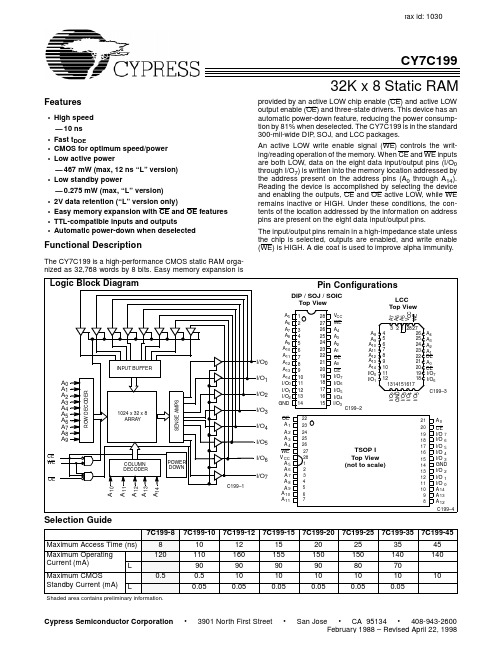

CY7C199中文资料

32K x 8 Static RAMfax id: 1030CY7C199Features•High speed —10 ns •Fastt DOE•CMOS for optimum speed/power •Low active power—467 mW (max, 12 ns “L” version)•Low standby power—0.275 mW (max, “L” version)•2V data retention (“L” version only)•Easy memory expansion with CE and OE features •TTL-compatible inputs and outputs•Automatic power-down when deselectedFunctional DescriptionThe CY7C199 is a high-performance CMOS static RAM orga-nized as 32,768 words by 8 bits. Easy memory expansion isprovided by an active LOW chip enable (CE) and active LOW output enable (OE) and three-state drivers. This device has an automatic power-down feature, reducing the power consump-tion by 81% when deselected. The CY7C199 is in the standard 300-mil-wide DIP , SOJ, and LCC packages.An active LOW write enable signal (WE) controls the writ-ing/reading operation of the memory. When CE and WE inputs are both LOW, data on the eight data input/output pins (I/O 0through I/O 7) is written into the memory location addressed by the address present on the address pins (A 0 through A 14).Reading the device is accomplished by selecting the device and enabling the outputs, CE and OE active LOW, while WE remains inactive or HIGH. Under these conditions, the con-tents of the location addressed by the information on address pins are present on the eight data input/output pins.The input/output pins remain in a high-impedance state unless the chip is selected, outputs are enabled, and write enable (WE) is HIGH. A die coat is used to improve alpha immunity.Logic Block DiagramPin ConfigurationsA 1A 2A 3A 4A 5A 6A 7A 8COLUMN DECODERR O W D E C O D E RS E N S E A M P SINPUT BUFFERPOWER DOWNWE OEI/O 0CE I/O 1I/O 2I/O 312345678910111415162019181721242322Top ViewDIP / SOJ / SOIC 121325282726GNDA 6A 7A 8A 9A 10A 11A 12A 13WE V CC A 4A 3A 2A 1I/O 7I/O 6I/O 5I/O 4A 14A 5I/O 0I/O 1I/O 2CE OE A 0I/O 31024x 32x 8ARRAYI/O 7I/O 6I/O 5I/O 4A 9A 0A 11A 13A 12A 14A 1028456789103212713141516172625242322212011121918A 7V C CI /O 5G N D W EA 6A 5I /O 4I /O 3I /O 2A 8A 9A 10A 11A 12A 13A 14CE A 3A 2A 1A 0I/O 1I/O 7I/O 6A 4OE I/O 0Top ViewLCC C199–1C199–2C199–322232425262728125101115141312161918173420217689OE A 1A 2A 3A 4WE V CC A 5A 6A 7A 8A 9A 0CE I/O 7I/O 6I/O 5GND I/O 2I/O 1I/O 4I/O 0A 14A 10A 11A 13A 12C199–4I/O 3TSOP I Top View (not to scale)Selection Guide7C199-87C199-107C199-127C199-157C199-207C199-257C199-357C199-45Maximum Access Time (ns)810121520253545Maximum Operating Current (mA)120110160155150150140140L 909090908070Maximum CMOSStandby Current (mA)0.50.5101010101010L0.050.050.050.050.050.05Shaded area contains preliminary information.Maximum Ratings(Above which the useful life may be impaired. For user guide-lines, not tested.)Storage T emperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage to Ground Potential(Pin 28 to Pin 14)...........................................–0.5V to +7.0V DC Voltage Applied to Outputsin High Z State[1]....................................–0.5V to V CC + 0.5V DC Input Voltage[1].................................–0.5V to V CC + 0.5V Output Current into Outputs (LOW).............................20 mA Static Discharge Voltage.......................................... >2001V (per MIL-STD-883, Method 3015)Latch-Up Current.................................................... >200 mA Operating RangeRange Ambient Temperature[2]V CC Commercial0°C to +70°C 5V ± 10% Industrial–40°C to +85°C5V ± 10% Military–55°C to +125°C 5V ± 10%Electrical Characteristics Over the Operating Range[3]7C199-87C199-107C199-127C199-15 Parameter Description Test Conditions Min.Max.Min.Max.Min.Max.Min.Max.Unit V OH Output HIGHVoltageV CC=Min., I OH=–4.0 mA 2.4 2.4 2.4 2.4VV OL Output LOWVoltageV CC=Min., I OL=8.0 mA0.40.40.40.4VV IH Input HIGHVoltage 2.2V CC+0.3V2.2V CC+0.3V2.2V CC+0.3V2.2V CC+0.3VVV IL Input LOWVoltage–0.50.8–0.50.8–0.50.8–0.50.8VI IX Input LoadCurrentGND < V I < V CC–5+5–5+5–5+5–5+5µAI OZ Output LeakageCurrent GND < V O < V CC,Output Disabled–5+5–5+5–5+5–5+5µAI CC V CC OperatingSupply Current V CC = Max.,I OUT = 0 mA,f = f MAX = 1/t RCCom’l120110160155mAL8585100mAMil180mAI SB1Automatic CEPower-DownCurrent— TTLInputs Max. V CC, CE >V IH,V IN > V IH orV IN < V IL, f = f MAXCom’l553030mAL555mAI SB2Automatic CEPower-DownCurrent— CMOSInputs Max. V CC,CE > V CC – 0.3VV IN > V CC – 0.3Vor V IN < 0.3V, f = 0Com’l0.50.51010mAL0.050.050.050.05mAMil15mAShaded area contains preliminary information.Notes:1.V IL (min.)= –2.0V for pulse durations of less than 20 ns.2.T A is the “instant on” case temperature.3.See the last page of this specification for Group A subgroup testing information.Electrical Characteristics Over the Operating Range[3] (continued)7C199-207C199-257C199-357C199-45 Parameter Description Test Conditions Min.Max.Min.Max.Min.Max.Min.Max.Unit V OH Output HIGHVoltageV CC=Min., I OH=–4.0 mA 2.4 2.4 2.4 2.4VV OL Output LOWVoltageV CC=Min., I OL=8.0 mA0.40.40.40.4VV IH Input HIGHVoltage 2.2V CC+0.3V2.2V CC+0.3V2.2V CC+0.3V2.2V CC+0.3VVV IL Input LOWVoltage–0.50.8-0.50.8-0.50.8-0.50.8VI IX Input LoadCurrentGND < V I < V CC–5+5–5+5–5+5–5+5µAI OZ Output LeakageCurrent GND < V I < V CC,Output Disabled–5+5–5+5–5+5–5+5µAI CC V CC OperatingSupply Current V CC = Max.,I OUT = 0 mA,f = f MAX = 1/t RCCom’l150150140140mAL90807070mAMil170150150150mAI SB1Automatic CEPower-DownCurrent—TTL Inputs Max. V CC, CE > V IH,V IN > V IHor V IN < V IL, f = f MAXCom’l30302525mAL5555mAI SB2Automatic CEPower-DownCurrent—CMOS Inputs Max. V CC,CE > V CC – 0.3VV IN > V CC – 0.3V orV IN < 0.3V, f=0Com’l10101010mAL0.050.050.050.05µAMil15151515mACapacitance[4]Parameter Description Test Conditions Max.UnitC IN Input Capacitance T A = 25°C, f = 1 MHz,V CC = 5.0V 8pFC OUT Output Capacitance8pFAC Test Loads and Waveforms [5]Data Retention Characteristics Over the Operating Range (L version only)Parameter DescriptionConditions [6]Min.Max.Unit V DR V CC for Data Retention 2.0V I CCDR Data Retention CurrentCom’lV CC = V DR = 2.0V ,CE > V CC – 0.3V ,V IN > V CC – 0.3V orV IN < 0.3V µACom’l L 10µA t CDR [4]Chip Deselect to Data Retention Time 0ns t R [5]Operation Recovery Timet RCns3.0V 5V OUTPUTR1 481ΩR2255Ω30pF INCLUDING JIGAND SCOPEGND90%10%90%10%≤t r≤t r5V OUTPUTR1 481ΩR2255Ω5pFINCLUDING JIGAND SCOPE(a)(b)OUTPUT1.73VEquivalent to:THÉ V ENIN EQUIVALENTALL INPUT PULSES C199–5C199–6167ΩData Retention WaveformNotes:4.T ested initially and after any design or process changes that may affect these parameters.5.t R < 3 ns for the -12 and -15 speeds. t R < 5 ns for the -20 and slower speeds.6.No input may exceed V CC + 0.5V.C199–73.0V 3.0V t CDRV DR >2VDA T A RETENTION MODEt RCEV CCSwitching Characteristics Over the Operating Range[3, 7]7C199-87C199-107C199-127C199-15 Parameter Description Min.Max.Min.Max.Min.Max.Min.Max.Unit READ CYCLEt RC Read Cycle Time8101215nst AA Address to Data Valid8101215nst OHA Data Hold from Address Change3333nst ACE CE LOW to Data Valid8101215nst DOE OE LOW to Data Valid 4.5557nst LZOE OE LOW to Low Z[8]0000nst HZOE OE HIGH to High Z[8, 9]5557nst LZCE CE LOW to Low Z[8]3333nst HZCE CE HIGH to High Z[8,9]4557nst PU CE LOW to Power-Up0000nst PD CE HIGH to Power-Down8101215ns WRITE CYCLE[10, 11]t WC Write Cycle Time8101215nst SCE CE LOW to Write End77910nst AW Address Set-Up to Write End77910nst HA Address Hold from Write End0000nst SA Address Set-Up to Write Start0000nst PWE WE Pulse Width7789nst SD Data Set-Up to Write End5589nst HD Data Hold from Write End0000nst HZWE WE LOW to High Z[9]5677nst LZWE WE HIGH to Low Z[8]3333ns Shaded area contains preliminary information.Notes:7.T est conditions assume signal transition time of 3 ns or less for -12 and -15 speeds and 5 ns or less for -20 and slower speeds, timing reference levels of 1.5V,input pulse levels of 0 to 3.0V, and output loading of the specified I OL/I OH and 30-pF load capacitance.8.At any given temperature and voltage condition, t HZCE is less than t LZCE, t HZOE is less than t LZOE, and t HZWE is less than t LZWE for any given device.9.t HZOE, t HZCE, and t HZWE are specified with C L = 5 pF as in part (b) of AC T est Loads. T ransition is measured ±500 mV from steady-state voltage.10.The internal write time of the memory is defined by the overlap of CE LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can terminatea write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.11.The minimum write cycle time for write cycle #3 (WE controlled, OE LOW) is the sum of t HZWE and t SD.Switching Characteristics Over the Operating Range [3,7] (continued)7C199-207C199-257C199-357C199-45Parameter DescriptionMin.Max.Min.Max.Min.Max.Min.Max.UnitREAD CYCLE t RC Read Cycle Time 20253545ns t AA Address to Data Valid 20253545ns t OHA Data Hold from Address Change3333ns t ACE CE LOW to Data Valid 20253545ns t DOE OE LOW to Data Valid 9101616ns t LZOE OE LOW to Low Z [8]0ns t HZOE OE HIGH to High Z [8,9]9111515ns t LZCE CE LOW to Low Z [8]3333ns t HZCE CE HIGH to High Z [8,9]9111515ns t PU CE LOW to Power-Up 0ns t PD CE HIGH to Power-Down 20202025ns WRITE CYCLE [10,11]t WC Write Cycle Time 20253545ns t SCE CE LOW to Write End 15182222ns t AW Address Set-Up to Write End 15203040ns t HA Address Hold from Write End 0000ns t SA Address Set-Up to Write Start 0000ns t PWE WE Pulse Width15182222ns t SD Data Set-Up to Write End 10101515ns t HD Data Hold from Write End 0ns t HZWE WE LOW to High Z [9]10111515ns t LZWEWE HIGH to Low Z [8]3333nsSwitching WaveformsRead Cycle No. 1[12, 13]Notes:12.Device is continuously selected. OE, CE = V IL .13.WE is HIGH for read cycle.ADDRESSDAT A OUTPREVIOUS DAT A VALIDDA T A VALIDt RCt AAt OHAC199–8Read Cycle No. 2 [13, 14]Write Cycle No. 1 (WE Controlled)[10, 15, 16]Write Cycle No. 2 (CE Controlled)[10, 15, 16]Notes:14.Address valid prior to or coincident with CE transition LOW.15.Data I/O is high impedance if OE = V IH .16.If CE goes HIGH simultaneously with WE HIGH, the output remains in a high-impedance state.Switching Waveforms (continued)50%50%DA T A VALIDt RCt ACEt DOEt LZOEt LZCEt PUDAT A OUTHIGH IMPEDANCEIMPEDANCEICCISBt HZOE t HZCEt PDOECEHIGH V CC SUPPL Y CURRENTC199–9t HDt SDt PWEt SAt HAt AWt WCDAT A I/OADDRESSCEWEOEt HZOEC199–10DAT A IN VALIDt WCt AWt SAt HAt HDt SDt SCEWEDAT A I/OADDRESSCEC199–11DA T A IN VALIDWrite Cycle No. 3 (WE Controlled OE LOW)[11, 16]Switching Waveforms (continued)DA T A I/OADDRESSt HDt SDt LZWEt SAt HAt AWt WCCEWEt HZWEC199–12DA T A IN VALIDTypical DC and AC Characteristics1.21.41.00.60.40.24.04.55.05.56.01.61.4 1.21.00.8–5525125–55251251.21.00.8N O R M A L I Z E D t A A120100806040200.01.02.03.04.0O U T P U T S O U R C E C U R R E N T (m A )SUPPL Y VOLT AGE (V)NORMALIZED SUPPL Y CURRENT vs.SUPPL Y VOLTAGENORMALIZED ACCESS TIME vs.AMBIENT TEMPERATURE AMBIENT TEMPERA TURE (°C)NORMALIZED SUPPLY CURRENT vs.AMBIENT TEMPERATUREAMBIENT TEMPERA TURE (°C)OUTPUT VOLT AGE (V)OUTPUT SOURCE CURRENT vs.OUTPUT VOLTAGE 0.00.81.41.11.00.94.04.55.05.56.0N O R M A L I Z E D t SUPPL Y VOLT AGE (V)NORMALIZED ACCESS TIME vs.SUPPLY VOLTAGE 120140*********0.01.02.03.04.0O U T P U T S I N K C U R R E N T (m A )080OUTPUT VOLT AGE (V)OUTPUT SINK CURRENT vs.OUTPUT VOLTAGE0.60.40.20.0N O R M A L I Z E D I C C ,I S BN O R M A L I Z E D I C C ,I S BI SBI CCI CCV CC =5.0VV CC =5.0V T A =25°CV CC =5.0V T A =25°CI SBT A =25°C0.60.80A A1.31.2V IN =5.0V T A =25°C 1.4V CC =5.0V V IN =5.0VTypical DC and AC Characteristics (continued)3.0 2.52.01.51.00.50.01.02.03.04.0N O R M A L I Z E D I P OSUPPL Y VOLT AGE (V)TYPICAL POWER-ON CURRENT vs.SUPPLY VOLTAGE 30.025.020.015.010.05.00200400600800D E L T A t (n s )A A CAPACIT ANCE (pF)TYPICAL ACCESS TIME CHANGE vs.OUTPUT LOADING1.251.000.7510203040N O R M A L I Z E D I C CCYCLE FREQUENCY (MHz)NORMALIZED I CC vs.CYCLE TIME0.05.00.010000.50V CC =4.5V T A =25°CV CC =5.0V T A =25°C V IN =0.5VTruth TableCE WE OE Inputs/Outputs ModePower H X X High Z Deselect/Power-DownStandby (I SB )L H L Data Out Read Active (I CC )L L X Data In WriteActive (I CC )LHHHigh ZDeselect, Output DisabledActive (I CC )Ordering InformationSpeed (ns)Ordering Code Package Name Package TypeOperating Range 8CY7C199-8VC V2128-Lead Molded SOJCommercialCY7C199-8ZC Z2828-Lead Thin Small Outline Package CY7C199L-8VC V2128-Lead Molded SOJCY7C199L-8ZC Z2828-Lead Thin Small Outline Package 10CY7C199-10VC V2128-Lead Molded SOJCommercialCY7C199-10ZC Z2828-Lead Thin Small Outline Package CY7C199L-10VC V2128-Lead Molded SOJCY7C199L-10ZC Z2828-Lead Thin Small Outline Package CY7C199-10VI V2128-Lead Molded SOJIndustrialCY7C199-10ZI Z2828-Lead Thin Small Outline Package CY7C199L-10VI V2128-Lead Molded SOJCY7C199L-10ZI Z2828-Lead Thin Small Outline Package 12CY7C199-12PC P2128-Lead (300-Mil) Molded DIP CommercialCY7C199-12VC V2128-Lead Molded SOJCY7C199-12ZC Z2828-Lead Thin Small Outline Package CY7C199L-12PC P2128-Lead (300-Mil) Molded DIP CY7C199L-12VC V2128-Lead Molded SOJCY7C199L-12ZC Z2828-Lead Thin Small Outline Package CY7C199-12VI V2128-Lead Molded SOJIndustrialCY7C199-12ZI Z2828-Lead Thin Small Outline Package CY7C199L-12VI V2128-Lead Molded SOJCY7C199L-12ZIZ2828-Lead Thin Small Outline PackageShaded area contains preliminary information. Contact your Cypress sales representative for availability15CY7C199-15PC P2128-Lead (300-Mil) Molded DIP CommercialCY7C199-15VC V2128-Lead Molded SOJCY7C199-15ZC Z2828-Lead Thin Small Outline Package CY7C199L-15PC P2128-Lead (300-Mil) Molded DIP CY7C199L-15VC V2128-Lead Molded SOJCY7C199L-15ZC Z2828-Lead Thin Small Outline Package CY7C199-15VI V2128-Lead Molded SOJIndustrial CY7C199-15ZI Z2828-Lead Thin Small Outline Package CY7C199-15DMB D2228-Lead (300-Mil) CerDIPMilitaryCY7C199-15LMB L5428-Pin Rectangular Leadless Chip Carrier CY7C199L-15DMB D2228-Lead (300-Mil) CerDIPCY7C199L-15LMB L5428-Pin Rectangular Leadless Chip Carrier 20CY7C199-20PC P2128-Lead (300-Mil) Molded DIP CommercialCY7C199-20VC V2128-Lead Molded SOJCY7C199-20ZC Z2828-Lead Thin Small Outline Package CY7C199L-20PC P2128-Lead (300-Mil) Molded DIP CY7C199L-20VC V2128-Lead Molded SOJCY7C199L-20ZC Z2828-Lead Thin Small Outline Package CY7C199-20VI V2128-Lead Molded SOJIndustrial CY7C199-20ZI Z2828-Lead Thin Small Outline Package CY7C199-20DMB D2228-Lead (300-Mil) CerDIPMilitaryCY7C199-20LMB L5428-Pin Rectangular Leadless Chip Carrier CY7C199L-20DMB D2228-Lead (300-Mil) CerDIPCY7C199L-20LMB L5428-Pin Rectangular Leadless Chip Carrier 25CY7C199-25PC P2128-Lead (300-Mil) Molded DIP CommercialCY7C199-25SC S2128-Lead Molded SOIC CY7C199-25VC V2128-Lead Molded SOJCY7C199-25ZC Z2828-Lead Thin Small Outline Package CY7C199L-25ZI Z2828-Lead Thin Small Outline Package Industrial CY7C199-25DMB D2228-Lead (300-Mil) CerDIPMilitary CY7C199-25LMB L5428-Pin Rectangular Leadless Chip Carrier 35CY7C199-35PC P2128-Lead (300-Mil) Molded DIP CommercialCY7C199-35SC S2128-Lead Molded SOIC CY7C199-35VC V2128-Lead Molded SOJCY7C199-35ZC Z2828-Lead Thin Small Outline Package CY7C199-35DMB D2228-Lead (300-Mil) CerDIPMilitary CY7C199-35LMB L5428-Pin Rectangular Leadless Chip Carrier 45CY7C199-45DMB D2228-Lead (300-Mil) CerDIPMilitaryCY7C199-45LMBL5428-Pin Rectangular Leadless Chip CarrierOrdering Information (continued)Speed (ns)Ordering Code Package Name Package TypeOperating Range Shaded area contains preliminary information. Contact your Cypress sales representative for availabilityMILITARY SPECIFICATIONS Group A Subgroup TestingDC CharacteristicsParameter SubgroupsV OH1, 2, 3V OL1, 2, 3V IH1, 2, 3V IL Max.1, 2, 3I IX1, 2, 3I OZ1, 2, 3I CC1, 2, 3I SB11, 2, 3I SB21, 2, 3Switching CharacteristicsParameter Subgroups READ CYCLEt RC7, 8, 9, 10, 11t AA7, 8, 9, 10, 11t OHA7, 8, 9, 10, 11t ACE7, 8, 9, 10, 11t DOE7, 8, 9, 10, 11 WRITE CYCLEt WC7, 8, 9, 10, 11t AA7, 8, 9, 10, 11t AW7, 8, 9, 10, 11t HA7, 8, 9, 10, 11t SA7, 8, 9, 10, 11t PWE7, 8, 9, 10, 11t SD7, 8, 9, 10, 11t HD7, 8, 9, 10, 11Document #: 38–00239–EPackage Diagrams28-Lead(300-Mil)CerDIP D22MIL–STD–1835D–15 Config.A28-Pin Rectangular Leadless ChipCarrier L54MIL–STD–1835 C–11APackage Diagrams (continued)28-Lead(300-Mil)Molded DIP P2128-Lead(300-Mil)Molded SOIC S21© Cypress Semiconductor Corporation, 1998. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Package Diagrams (continued)28-Lead (300-Mil)MoldedSOJ V2128-Lead Thin Small Outline PackageZ28。

Henkel Ireland Limited 99C 362 5C 产品说明书

Safety Data Sheet according to (EC) No 1907/2006Page 1 of 8sds no. : 221815V004.0 99C 362 5CRevision: 14.05.2012printing date: 23.07.2012SECTION 1: Identification of the substance/mixture and of the company/undertaking1.1. Product identifier99C 362 5C1.2. Relevant identified uses of the substance or mixture and uses advised againstIntended use:Solder Wire1.3. Details of the supplier of the safety data sheetHenkel Ireland LimitedProduct Safety & Regulatory AffairsTallaght Business Park, WhitestownDublin 24IrelandPhone: +353 (14046444)Fax-no.: +353 (14519926)*****************************.com1.4. Emergency telephone number24 Hours Emergency Tel: +44 (0)1442 278497SECTION 2: Hazards identification2.1. Classification of the substance or mixtureClassification (DPD):SensitizingR43 May cause sensitisation by skin contact.2.2. Label elementsLabel elements (DPD):Xi - IrritantRisk phrases:R43 May cause sensitisation by skin contact.Safety phrases:S24 Avoid contact with skin.S37 Wear suitable gloves.S23 Do not breathe fumes.Contains:Rosin2.3. Other hazardsFlux fumes emitted during reflow will irritate the nose and throat and may cause an asthmatic type reaction.Regulations forbid the use of lead solder in any private or public drinking water supply system.SECTION 3: Composition/information on ingredients Declaration of the ingredients according to CLP (EC) No 1272/2008:Hazardous componentsCAS-No.EC NumberREACH-Reg No.content ClassificationTin 7440-31-5231-141-801-2119486474-28>= 90- < 100%Copper Metal7440-50-8231-159-6 >= 0,1- < 1%Rosin 8050-09-7 232-475-7 >= 1- < 5% Skinsensitizer1H317For full text of the H - statements and other abbreviations see section 16 "Other information". Substances without classification may have community workplace exposure limits available. Declaration of ingredients according to DPD (EC) No 1999/45:Hazardous componentsCAS-No.EC NumberREACH-Reg No.content ClassificationTin 7440-31-5231-141-801-2119486474-28>= 90 - < 100 %Copper Metal7440-50-8231-159-6 >= 0,1 - < 1 %Rosin 8050-09-7 232-475-7 >= 1 - < 5 %R43For full text of the R-Phrases indicated by codes see section 16 'Other Information'. Substances without classification may have community workplace exposure limits available.SECTION 4: First aid measures4.1. Description of first aid measuresInhalation:Move to fresh air. If symptoms persist, seek medical advice.Skin contact:Rinse with running water and soap.Obtain medical attention if irritation persists.Eye contact:Flush eyes with plenty of water for at least 5 minutes. If irritation persists seek medical attention.Ingestion:Do not induce vomiting.Seek medical advice.4.2. Most important symptoms and effects, both acute and delayedFlux fumes may irritate the nose, throat and lungs and may after prolonged/repeated exposure give an allergic reaction (asthma).SKIN: Rash, Urticaria.4.3. Indication of any immediate medical attention and special treatment neededSee section: Description of first aid measuresSECTION 5: Firefighting measures5.1. Extinguishing mediaSuitable extinguishing media:Carbon dioxide, foam, powderFine water sprayExtinguishing media which must not be used for safety reasons:Do not use water on fires where molten metal is present.5.2. Special hazards arising from the substance or mixtureHigh temperatures may produce heavy metal dust, fumes or vapours.The flux medium will give rise to irritating fumes.5.3. Advice for firefightersWear self-contained breathing apparatus.SECTION 6: Accidental release measures6.1. Personal precautions, protective equipment and emergency proceduresWear protective equipment.6.2. Environmental precautionsDo not empty into drains / surface water / ground water.6.3. Methods and material for containment and cleaning upScrape up spilled material and place in a closed container for disposal.6.4. Reference to other sectionsSee advice in chapter 8SECTION 7: Handling and storage7.1. Precautions for safe handlingExtraction is necessary to remove fumes evolved during reflow.When using do not eat, drink or smoke.Wash hands before breaks and immediately after handling the product.Avoid breathing fumes given out during soldering.See advice in chapter 8Hygiene measures:Good industrial hygiene practices should be observed.Do not eat, drink or smoke while working.After handling solder wash hands with soap and water before eating, drinking or smoking.7.2. Conditions for safe storage, including any incompatibilitiesEnsure good ventilation/extraction.Store in a cool, dry place.7.3. Specific end use(s)Solder WireSECTION 8: Exposure controls/personal protection8.1. Control parametersValid forGreat BritainIngredient ppm mg/m3Type Category RemarksTIN (INORGANIC COMPOUNDS AS SN) 7440-31-5 2 Time Weighted Average(TWA):Indicative ECTLVROSIN-BASED SOLDER FLUX FUME 8050-09-7 0,05 Time Weighted Average(TWA):EH40 WELROSIN-BASED SOLDER FLUX FUME 8050-09-7 0,15 Short Term ExposureLimit (STEL):EH40 WELColophony (Rosin) and derivatives: Rosin-based flux fume as total resin acids.8.2. Exposure controls:Engineering controls:Extraction is necessary to remove fumes evolved during reflow.Where reasonably practicable this should be achieved by the use of local exhaust ventilation and good general extraction.Ensure good ventilation/extraction.Respiratory protection:Ensure adequate ventilation.An approved mask or respirator fitted with an organic vapour cartridge should be worn if the product is used in a poorly ventilated areaIn case of aerosol formation, we recommend wearing of appropriate respiratory protection equipment with ABEK P2 filter.This recommendation should be matched to local conditions.Hand protection:Please note that in practice the working life of chemical resistant gloves may be considerably reduced as a result of many influencing factors (e.g. temperature). Suitable risk assessment should be carried out by the end user. If signs of wear and tear are noticed then the gloves should be replaced.The use of chemical resistant gloves such as Nitrile are recommended.Eye protection:Safety glasses with sideshields or chemical safety goggles should be worn if there is a risk of splashing.Skin protection:Wear suitable protective clothing.SECTION 9: Physical and chemical properties9.1. Information on basic physical and chemical propertiesAppearance solidgreyOdor NoneapplicablepH notInitial boiling point No data available / Not applicableFlash point NoneDecomposition temperature No data available / Not applicableVapour pressure not applicable7,3 g/cm3Density(25 °C (77 °F))Bulk density No data available / Not applicableViscosity No data available / Not applicableViscosity (kinematic) No data available / Not applicableExplosive properties No data available / Not applicableInsolubleSolubility (qualitative)(Solvent: Water)Solidification temperature No data available / Not applicableMelting point227 °C (440.6 °F)Flammability No data available / Not applicableAuto-ignition temperature No data available / Not applicableExplosive limits No data available / Not applicablePartition coefficient: n-octanol/water Not applicableEvaporation rate No data available / Not applicableVapor density No data available / Not applicableOxidising properties No data available / Not applicable9.2. Other informationNo data available / Not applicableSECTION 10: Stability and reactivity10.1. ReactivitySolder alloy will react with concentrated nitric acid to produce toxic fumes of nitrogen oxides.10.2. Chemical stabilityStable under recommended storage conditions.10.3. Possibility of hazardous reactionsSee section reactivity10.4. Conditions to avoidNo decomposition if stored and applied as directed.10.5. Incompatible materialsNone if used properly.10.6. Hazardous decomposition productsThermal decomposition can lead to release of irritating gases and vapors.SECTION 11: Toxicological information11.1. Information on toxicological effectsGeneral toxicological information:The preparation is classified based on the conventional method outlined in Article 6(1)(a) of Directive 1999/45/EC. Relevant available health/ecological information for the substances listed under Section 3 is provided in the following.Oral toxicity:This material is considered to have low toxicity if swallowed.Inhalative toxicity:Fumes evolved at soldering temperatures will irritate the nose, throat and lungs. Prolonged or repeated exposure to flux fumes may result in sensitisation in sensitive workers.Dermal toxicity:This product is considered to have low dermal toxicity.Skin irritation:Fumes emitted during soldering may irritate the skin.Eye irritation:Fumes emitted during soldering may irritate the eyes.Sensitizing:May cause sensitization by skin contact.Skin corrosion/irritation:Hazardous components CAS-No. Result ExposuretimeSpecies MethodCopper Metal7440-50-8irritating Serious eye damage/irritation:Hazardous components CAS-No. Result ExposuretimeSpecies MethodCopper Metal7440-50-8irritatingSECTION 12: Ecological informationGeneral ecological information:Do not empty into drains / surface water / ground water.The preparation is classified based on the conventional method outlined in Article 6(1)(a) of Directive 1999/45/EC. Relevant available health/ecological information for the substances listed under Section 3 is provided in the following.Ecotoxicity:May cause long-term adverse effects in the aquatic environment.Mobility:The product is insoluble and sinks in water.Persistence and Biodegradability:The product is not biodegradable.Bioaccumulative potential:Octanol/Water distribution coefficient: Not applicable12.1. ToxicityHazardous componentsCAS-No. ValuetypeValue AcuteToxicityStudyExposuretimeSpecies MethodCopper Metal 7440-50-8 LC50> 10 mg/l Fish96 h Lepomis macrochirus OECD Guideline203 (Fish, AcuteToxicity Test)Rosin 8050-09-7 LC50> 1.000 mg/l Fish96 h Pimephales promelas OECD Guideline203 (Fish, AcuteToxicity Test)Rosin 8050-09-7 EC50911 mg/l Daphnia48 h Daphnia magna OECD Guideline202 (Daphnia sp.AcuteImmobilisationTest)Rosin 8050-09-7 EC50> 100 mg/l Algae72 h Scenedesmus subspicatus (newname: Desmodesmussubspicatus)12.2. Persistence and degradabilityHazardous componentsCAS-No. Result RouteofapplicationDegradability MethodRosin 8050-09-7aerobic 36 - 46 % OECD Guideline 301 F (ReadyBiodegradability: ManometricRespirometry Test) SECTION 13: Disposal considerations13.1. Waste treatment methodsProduct disposal:Wherever possible unwanted solder alloy should be recycled for recovery of metal.Otherwise dispose of in accordance with local and national regulations.Disposal of uncleaned packages:Dispose of as unused product.Waste code06 04 05 - wastes containing other heavy metalsSECTION 14: Transport informationGeneral information:Not hazardous according to RID, ADR, ADNR, IMDG, IATA-DGR.SECTION 15: Regulatory information15.1. Safety, health and environmental regulations/legislation specific for the substance or mixtureVOC content< 5,0 %National regulations/information (Great Britain):Remarks The Health & Safety at Work Act 1974.The Control of Substances Hazardous to Health Regulations. L5:GeneralApproved Code of Practice to the COSHH Regulations. HS(G)97:A Step by StepGuide to the COSHH Regulations. HS(G)193:COSHH essentials: Easy steps tocontrol chemicals.IND (G)248L:Solder fume and you. IND(G)249L:Controlling health risks fromrosin (colophony) based solder fluxes.SECTION 16: Other informationThe labelling of the product is indicated in Section 2. The full textof all abbreviations indicated by codes in this safety data sheet are as follows:R43 May cause sensitisation by skin contact.H317 May cause an allergic skin reaction.Further information:This information is based on our current level of knowledge and relates to the product in the state in which it is delivered. It is intended to describe our products from the point of view of safety requirements and is not intended to guarantee anyparticular properties.This safety data sheet was prepared in accordance with Council Directive 67/548/EEC and it's subsequent amendments, and Commission Directive 1999/45/EC.。

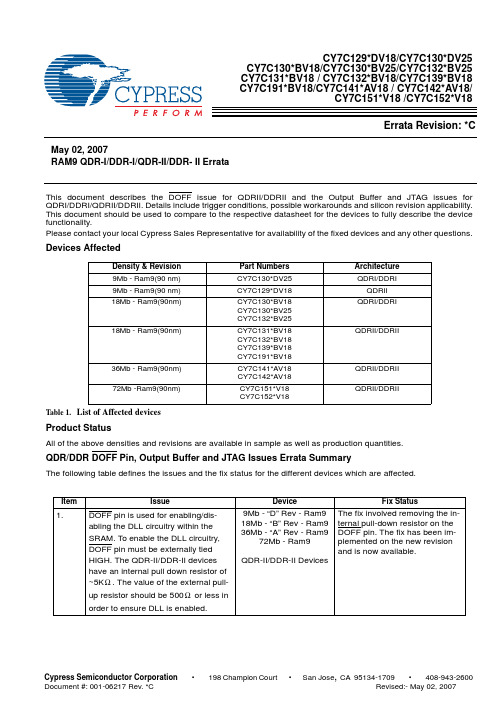

CY7C1417AV18资料

Errata Revision: *CMay 02, 2007RAM9 QDR-I/DDR-I/QDR-II/DDR- II ErrataCY7C129*DV18/CY7C130*DV25CY7C130*BV18/CY7C130*BV25/CY7C132*BV25CY7C131*BV18 / CY7C132*BV18/CY7C139*BV18CY7C191*BV18/CY7C141*AV18 / CY7C142*AV18/CY7C151*V18 /CY7C152*V18This document describes the DOFF issue for QDRII/DDRII and the Output Buffer and JTAG issues for QDRI/DDRI/QDRII/DDRII. Details include trigger conditions, possible workarounds and silicon revision applicability.This document should be used to compare to the respective datasheet for the devices to fully describe the device functionality.Please contact your local Cypress Sales Representative for availability of the fixed devices and any other questions.Devices AffectedTable 1. List of Affected devicesProduct StatusAll of the above densities and revisions are available in sample as well as production quantities.QDR/DDR DOFF Pin, Output Buffer and JTAG Issues Errata SummaryThe following table defines the issues and the fix status for the different devices which are affected.Density & Revision Part Numbers Architecture 9Mb - Ram9(90 nm)CY7C130*DV25QDRI/DDRI 9Mb - Ram9(90 nm)CY7C129*DV18QDRII 18Mb - Ram9(90nm)CY7C130*BV18CY7C130*BV25CY7C132*BV25QDRI/DDRI18Mb - Ram9(90nm)CY7C131*BV18CY7C132*BV18CY7C139*BV18CY7C191*BV18QDRII/DDRII36Mb - Ram9(90nm)CY7C141*AV18CY7C142*AV18QDRII/DDRII 72Mb -Ram9(90nm)CY7C151*V18CY7C152*V18QDRII/DDRIIItemIssueDeviceFix Status1.DOFF pin is used for enabling/dis-abling the DLL circuitry within the SRAM. To enable the DLL circuitry, DOFF pin must be externally tied HIGH. The QDR-II/DDR-II devices have an internal pull down resistor of ~5K . The value of the external pull-up resistor should be 500 or less in order to ensure DLL is enabled.9Mb - “D” Rev - Ram918Mb - “B” Rev - Ram936Mb - “A” Rev - Ram972Mb - Ram9QDR-II/DDR-II DevicesThe fix involved removing the in-ternal pull-down resistor on the DOFF pin. The fix has been im-plemented on the new revision and is now available.ΩΩTable 2.Issue Definition and fix status for different devices1. DOFF Pin Issue•ISSUE DEFINITIONThis issue involves the DLL not turning ON properly if a large resistor is used (eg:-10K ) as an external pullup resistor to enable the DLL. If a 10K or higher pullup resistor is used externally, the voltage on DOFF is not high enough to enable the DLL.•PARAMETERS AFFECTEDThe functionality of the device will be affected because of the DLL is not turning ON properly. When the DLL is enabled, all AC and DC parameters on the datasheet are met. •TRIGGER CONDITION(S)Having a 10K or higher external pullup resistor for disabling the DOFF pin.•SCOPE OF IMPACTThis issue will alter the normal functionality of the QDRII/DDRII devices when the DLL is disabled.•EXPLANATION OF ISSUEFigure 1 shows the DOFF pin circuit with an internal 5K internal resistor. The fix planned is to disable the internal 5K leaker.•WORKAROUND2.O/P Buffer enters a locked up unde-fined state after controls or clocks are left floating. No proper read/write access can be done on the device until a dummy read is performed.9Mb - “D” Rev - Ram918Mb - “B” Rev - Ram936Mb - “A” Rev - Ram972Mb - Ram9QDR-I/DDR-I/QDR-II/DDR-II Devices The fix has been implemented onthe new revision and is now avail-able.3.The EXTEST function in the JTAG test fails when input K clock is floating in the JTAG mode.9Mb - “D” Rev - Ram918Mb - “B” Rev - Ram936Mb - “A” Rev - Ram972Mb - Ram9QDR-I/DDR-I/QDR-II/DDR-II DevicesThe fix involved bypassing the ZQ circuitry in JTAG mode. This was done by overriding the ZQ circuit-ry by the JTAG signal. The fix has been implemented on the new re-vision and is now available.Figure 1.DOFF pin with the 5K internal resistorItemIssueDeviceFix StatusΩΩΩΩΩΩThe workaround is to have a low value of external pullup resistor for the DOFF pin (recommended value is <500). When DOFF pins from multiple QDR devices are connected through the same pull-up resistors on the board, it is recommended that this DOFF pin be directly connected to Vdd due to the lower effective resistance since the "leakers" are in parallel.Figure 2 shows the proposed workaround and the fix planned.•FIXSTATUSFix involved removing the internal pull-down resistor on the DOFF pin. The fix has been implemented on the new revision and is now available. The new revision is an increment of the existing revision. The following table lists the devices affected, current revision and the new revision after the fix.Table 3.List of Affected Devices and the new revison2.Output Buffer IssueFigure 2.Proposed workaround with the 500 external pullupCurrent Revision New Revision after the FixCY7C129*DV18CY7C129*EV18CY7C131*BV18CY7C131*CV18CY7C132*BV18CY7C132*CV18CY7C139*BV18CY7C139*CV18CY7C191*BV18CY7C191*CV18CY7C141*AV18CY7C141*BV18CY7C142*AV18CY7C142*BV18CY7C151*V18CY7C151*AV18CY7C152*V18CY7C152*AV18ΩΩ•ISSUE DEFINITIONThis issue involves the output buffer entering an unidentified state when the input signals (only Control signals or Clocks) are floating during reset or initialization of the memory controller after power up. •PARAMETERS AFFECTEDNo timing parameters are affected. The device may drive the outputs even though the read operation is not enabled. A dummy read is performed to clear this condition.•TRIGGER CONDITION(S)Input signals(namely RPS# for QDR-I/QDRII , WE# and LD# for DDR-I/DDRII) or Clocks (K/K# and/or C/C#) are floating during reset or initialization of the memory controller after power up.•SCOPE OF IMPACTThis issue will jeopardize any number of writes or reads which take place after the controls or clock are left floating. This can occur anywhere in the SRAM access ( all the way from power up of the memory device to transitions taking place for read/write accesses to the memory device) if the above trigger conditions are met.•EXPLANATION OF ISSUEFigure 3 shows the output register Reset circuit with an SR Latch circled. This latch has two inputs with one of them coming from some logic affected by the clock and RPS#(QDR) or WE# and LD#(DDR).The issue happens when clocks are glitching/toggling with controls floating. This will cause the SR latch to be taken into an unidentified state. The SR Latch will need to be reset by a dummy read operation if this happens. Array•WORKAROUNDThis is viable only if the customer has the trigger conditions met during reset or initialization of the memory controller after power up. In order for the workaround to perform properly, Cypress recommends the insertion of a minimum of 16 “dummy” READ operations to every SRAM device on the board prior to writing any meaningful data into the SRAM. After this one “dummy” READ operation, the device will perform properly.“Dummy” READ is defined as a read operation to the device that is not meant to retrieve required data. The “dummy” READ can be to any address location in the SRAM. Refer to Figure 4 for the dummy read implemen-tation.In systems where multiple SRAMs with multiple RPS# lines are used, a dummy read operation will have to be performed on every SRAM on the board. Below is an example sequence of events that can be performed before valid access can be performed on the SRAM.1) Initialize the Memory Controller2) Assert RPS# Low for each of the memory devicesNote:For all devices with x9 bus configuration, the following sequence needs to be performed:1) For the 72M / 36M / 18M x9 devices drive address pin A2 / A10 / A3 low respectively and perform dummyread.2) For the 72M / 36M / 18M x9 devices drive address pin A2 / A10 / A3 high respectively and perform dummyread.If the customer has the trigger conditions met during normal access to the memory then there is no workaround at this point.•FIX STATUSThe fix has been implemented on the new revision and is now available. The new revision is an increment of the existing revision. Please refer to Table 4 for the list of devices affected, current revision and the new revision after the fix.3. JTAG Mode Issue•ISSUE DEFINITIONIf the input clock (K Clock) is left floating when the device is in JTAG mode, spurious high frequency noise on this input can be interpreted by the device as valid clocks. This could cause the impedance matching circuitry (ZQ) on the QDR/DDR devices to periodically load itself with incorrect values. These incorrect values in the ZQ register could force the outputs into a High-Impedance state. The ZQ circuitry requires at least 1000 valid K clock cycles to drive the outputs from high impedance to low impedance levels.•PARAMETERS AFFECTEDThis issue only affects the EXTEST command when the device is in the JTAG mode. The normal functionality of the device will not be affected.•TRIGGER CONDITION(S)EXTEST command executed immediately after power-up without providing any K clock cycles.•SCOPE OF IMPACTThis issue only impacts the EXTEST command when device is tested in the JTAG mode. Normal functionality of the device is not affected. •EXPLANATION OF ISSUEImpedance matching circuitry (ZQ) is present on the QDR/DDR devices to set the desired impedance on the outputs. This ZQ circuitry is updated every 1000 clock cycles of K clock to ensure that the impedance of the O/P is set to valid state. However, when the device is operated in the JTAG mode immediately after power-up, high frequency noise on the input K clock can be treated by the ZQ circuitry as valid clocks thereby setting the outputs in to a high-impedance mode. If a minimum of 1000 valid K clocks are applied before performing the JTAG test, this should clear the ZQ circuitry and ensure that the outputs are driven to valid impedance levels.•WORKAROUNDElimination of the issue: After power-up, before any valid operations are performed on the device, insert a minimum of 1000 valid clocks on K input.•FIX STATUSThe fix involved bypassing the ZQ circuitry in JTAG mode. This was done by overriding the ZQ circuitry by the JTAG signal. The fix has been implemented on the new revision and is now available. The new revision is an increment of the existing revision. Please refer to Table 4 for the list of devices affected, current revision and the new revision after the fix..Table 4.List of Affected devices and the new revisionCurrent Revision New Revision after the FixCY7C129*DV18CY7C129*EV18CY7C130*DV25CY7C130*EV25CY7C130*BV18CY7C130*CV18CY7C130*BV25CY7C130*CV25CY7C132*BV25CY7C132*CV25CY7C131*BV18CY7C131*CV18CY7C132*BV18CY7C132*CV18CY7C139*BV18CY7C139*CV18CY7C191*BV18CY7C191*CV18CY7C141*AV18CY7C141*BV18CY7C142*AV18CY7C142*BV18CY7C151*V18CY7C151*AV18CY7C152*V18CY7C152*AV18ReferencesAll 90nm QDRI/DDRI/QDRII/DDRII datasheets:-Table 5.List of Datasheet spec# for the Affected devicesSpec#Part#DensityArchitecture38-05628CY7C1304DV259-MBIT QDR(TM) SRAM 4-WORD BURST 38-05632CY7C1308DV259-MBIT DDR-I SRAM 4-WORD BURST 001-00350CY7C1292DV18/1294DV189-MBIT QDR- II(TM) SRAM 2-WORD BURST 38-05621CY7C1316BV18/1916BV18/1318BV18/1320BV1818-MBIT DDR-II SRAM 2-WORD BURST 38-05622CY7C1317BV18/1917BV18/1319BV18/1321BV1818-MBIT DDR-II SRAM 4-WORD BURST 38-05623CY7C1392BV18/1393BV18/1394BV1818-MBIT DDR-II SIO SRAM 2-WORD BURST 38-05631CY7C1323BV2518-MBIT DDR-I SRAM 4-WORD BURST 38-05630CY7C1305BV25/1307BV2518-MBIT QDR(TM) SRAM 4-WORD BURST 38-05627CY7C1303BV25/1306BV2518-MBIT QDR(TM) SRAM 2-WORD BURST 38-05629CY7C1305BV18/1307BV1818-MBIT QDR(TM) SRAM 4-WORD BURST 38-05626CY7C1303BV18/1306BV1818-MBIT QDR(TM) SRAM 2-WORD BURST 38-05619CY7C1310BV18/1910BV18/1312BV18/1314BV1818-MBIT QDR - II (TM) SRAM 2-WORD BURST 38-05620CY7C1311BV18/1911BV18/1313BV18/1315BV1818-MBIT QDR - II SRAM 4-WORD BURST 38-05615CY7C1410AV18/1425AV18/1412AV18/1414AV1836-MBIT QDR-II(TM) SRAM 2-WORD BURST 38-05614CY7C1411AV18/1426AV18/1413AV18/1415AV1836-MBIT QDR(TM)-II SRAM 4-WORD BURST 38-05616CY7C1416AV18/1427AV18/1418AV18/1420AV1836-MBIT DDR-II SRAM 2-WORD BURST 38-05618CY7C1417AV18/1428AV18/1419AV18/1421AV1836-MBIT DDR-II SRAM 4-WORD BURST 38-05617CY7C1422AV18/1429AV18/1423AV18/1424AV1836-MBIT DDR-II SIO SRAM 2-WORD BURST 38-05489CY7C1510V18/1525V18/1512V18/1514V1872-MBIT QDR-II SRAM 2-WORD BURST 38-05363CY7C1511V18/1526V18/1513V18/1515V1872-MBIT QDR(TM)-II SRAM 4-WORD BURST 38-05563CY7C1516V18/1527V18/1518V18/1520V1872-MBIT DDR-II SRAM 2-WORD BURST 38-05565CY7C1517V18/1528V18/1519V18/1521V1872-MBIT DDR-II SRAM 4-WORD BURST 38-05564CY7C1522V18/1529V18/1523V18/1524V1872-MBITDDR-II SIO SRAM 2-WORD BURSTDocument History PageDocument Title: RAM9 QDR-I/DDR-I/QDR-II/DDR- II Errata Document #: 001-06217 Rev. *CREV.ECN NO.IssueDateOrig. ofChange Description of Change**419849See ECN REF New errata for Ram9 QDR2/DDR2 SRAMs.*A493936See ECN QKS Added Output buffer and JTAG mode issues, Item#2 and #3Added 9Mb QDR-II Burst of 2 and QDR-1/DDR-I part numbers.*B733176See ECN NJY Added missing part numbers in the title for Spec#’s 38-05615,38-05614,38-05363,38-05563 on Table 5 on page 7.*C1030020 See ECN TBE Updated the fix status of the three issues, and modified the description forthe Output Buffer workaround for x9 devices on page 5.。

Agilent HSMx-C110 C170 C190 C191 C150 ChipLED 数据手册

Agilent HSMx-C110/C170/C190/C191/C150High Performance ChipLEDData SheetFeatures•High brightness AlInGaP material •Small size•Industry standard footprint •Diffused optics•Top emitting or right angle emitting•Available in 3 colors (red, orange, amber)•Compatible with IR soldering •Available in 8 mm tape on 7" diameter reel•Reel sealed in zip locked moisture barrier bagsApplications• LCD backlighting• Push button backlighting • Front panel indicator • Symbol indicator • Microdisplays• Small message panel signageThese ChipLEDs come either in two top emitting packages(HSMx-C170/C190/C191/C150)or in a side emitting package (HSMx-C110). The right angle ChipLEDs are suitable forapplications such as LCD back-lighting. The top emitting ChipLEDs with wide viewingangle are suitable for light piping and direct backlighting ofkeypads and panels. In order to facilitate pick and place opera-tion, these ChipLEDs are shipped in tape and reel, with 4000 units per reel for HSMx-C170/C190/C191 and 3000 units per reel for HSMx-C110/C150.These packages are compatible with IR soldering process.DescriptionThese chip-type LEDs utilize Alu-minum Indium Gallium Phosphide (AlInGaP) material technology.The AlInGaP material has a very high luminous efficiency, capable of producing high light output over a wide range of drivecurrents. The available colors in this surface mount series are 592 nm Amber, 605 nm Orange,626 nm Red for AS AlInGaP and 631 nm red for TS AlInGaP.All packages are binned by both color and intensity, except for red color.HSMA-C110/C170/C190/C191/C150HSML-C110/C170/C190/C191/C150HSMC-C110/C170/C190/C191/C150HSMZ-C110/C170/C190Package DimensionsTERMINALHSMx-C170NOTES:1. ALL DIMENSIONS IN MILLIMETERS (INCHES).2. TOLERANCE IS ± 0.1 mm (± 0.004 IN.) UNLESS OTHERWISE SPECIFIED.HSMx-C190TERMINAL HSMx-C191TERMINALTERMINALHSMx-C110Package Dimensions, continuedNotes:1. Dimensions in mm.2. Tolerance ± 0.1 mm unless otherwise noted.Device Selection Guide Footprint AS AlInGaP AS AlInGaP AS AlInGaP TS AlInGaP Package (mm)[1,2]Amber Orange Red Red Description 1.6 x 0.8 x 0.8HSMA-C190HSML-C190HSMC-C190HSMZ-C190Untinted, Diffused 2.0 x 1.25 x 0.8HSMA-C170HSML-C170HSMC-C170HSMZ-C170Untinted, Diffused 3.2 x 1.0 x 1.5HSMA-C110HSML-C110HSMC-C110HSMZ-C110Untinted, Nondiffused 1.6 x 0.8 x 0.6HSMA-C191HSML-C191HSMC-C191Untinted, Diffused 3.2 x 1.6 x 1.1HSMA-C150HSML-C150HSMC-C150Untinted, DiffusedAbsolute Maximum Ratings T A = 25°CHSMA-C110/170/190/191/150HSML-C110/170/190/191/150ParameterHSMC-C110/170/190/191/150HSMZ-C110/170/190Units DC Forward Current [1,2]2525mA Power Dissipation6065mW Reverse Voltage (I R = 100µA)55V LED Junction Temperature 9595°C Operating Temperature Range –30 to +85–30 to +85°C Storage Temperature Range –40 to +85–40 to +85°CSoldering TemperatureSee reflow soldering profile (Figure 7 & 8)Notes:1. Derate linearly as shown in Figure 4.2. Drive currents above 5 mA are recommended for best long term performance.HSMx-C1500.50 ± 0.2TERMINALNOTES:1. ALL DIMENSIONS IN MILLIMETERS (INCHES).2. TOLERANCE IS ± 0.1 mm (± 0.004 IN.) UNLESS OTHERWISE SPECIFIED.Electrical CharacteristicsT A = 25°CForward Voltage Reverse Breakdown Capacitance C ThermalV F (Volts)V R (Volts)(pF), V F = 0,Resistance@ I F = 20 mA@ I R = 100 µA f = 1 MHz RθJ-PIN = (°C/W) Parameter Number Typ. Max.Min.Typ.Typ.HSMA-C110 1.9 2.4545600HSML-C110 1.9 2.4545600HSMC-C110 1.9 2.4545600HSMZ-C110 2.2 2.8535600HSMA-C170/190/191/150 1.9 2.4545300HSML-C170/190/191/150 1.9 2.4545300HSMC-C170/190/191/150 1.9 2.4545300HSMZ-C170/190 2.2 2.6535300Optical CharacteristicsT A = 25°CLuminous Color,Viewing LuminousIntensity Peak Dominant Angle EfficacyI v (mcd)Wavelength Wavelength 2 θ1/2ηvPart@ 20 mA[1]λpeak(nm)λd[2](nm)Degrees[3](lm/w) Number Color Min. Typ.Typ.Typ.Typ.Typ. HSMA-C110AS Amber28.5 95595592130480 HSMA-C170/190/191/150AS Amber28.5 90595592170480 HSML-C110AS Orange28.5 95609605130370 HSML-C170/190/191/150AS Orange28.5 90609605170370 HSMC-C110AS Red28.5 95637626130155 HSMC-C170/190/191/150AS Red28.5 90637626170155 HSMZ-C110TS Red45 170643631130122 HSMZ-C170/190TS Red45 165643631170122 Notes:1.The luminous intensity,I v, is measured at the peak of the spatial radiation pattern which may not be aligned with the mechanical axis of thelamp package.2.The dominant wavelength,λd, is derived from the CIE Chromaticity Diagram and represents the perceived color of the device.3.θ1/2 is the off-axis angle where the luminous intensity is 1/2 the peak intensity.Color Bin Limits[1]Orange Color Bins[1]Dom. Wavelength (nm)Bin ID Min.Max.A597.0600.0B600.0603.0C603.0606.0D606.0609.0E609.0612.0F612.0615.0Tolerance: ± 1 nm.Yellow/Amber Color Bins[1]Dom. Wavelength (nm)Bin ID Min.Max.A582.0584.5B584.5587.0C587.0589.5D589.5592.0E592.0594.5F594.5597.0Tolerance: ± 0.5 nm.Note:1.Bin categories are established for classification of products. Productsmay not be available in all categories. Please contact your Agilent rep-resentative for information on currently available bins.Light Intensity (Iv) Bin Limits[1]Intensity (mcd)Intensity (mcd)Bin ID Min.Max.Bin ID Min.Max.A0.110.18N28.5045.00B0.180.29P45.0071.50C0.290.45Q71.50112.50D0.450.72R112.50180.00E0.72 1.10S180.00285.00F 1.10 1.80T285.00450.00G 1.80 2.80U450.00715.00H 2.80 4.50V715.001125.00J 4.507.20W1125.001800.00K7.2011.20X1800.002850.00L11.2018.00Y2850.004500.00M18.0028.50Tolerance: ± 15%.Note:1.Bin categories are established for classification of products. Products may not be available in allcategories. Please contact your Agilent representative for information on currently available bins.Figure 3. Luminous intensity vs. forward current.Figure 2. Forward current vs. forward voltage.Figure 4. Maximum forward current vs.ambient temperature.Figure 1. Relative intensity vs. wavelength.1010.1V F – FORWARD VOLTAGE – V I F – F O R W A R D C U R R E N T – m A51530I F – FORWARD CURRENT – mA 00.41.01.4L U M I N O U S I N T E N S I T Y (N O R M A L I Z E D A T 20 m A )200.60.20.810251.2WAVELENGTH – nmTS AlInGaP REDAS AlInGaPAMBERR E L A T I V E I N T E N S I T Y0.5500550600650700750AS AlInGaP ORANGEAS AlInGaP REDI F M A X . – M A X I M U M F O R W A R D C U R R E N T – m AT A – AMBIENT TEMPERATURE – °CFigure 5. Relative intensity vs. angle for HSMx-C110.Figure 6. Relative intensity vs. angle for HSMx-C170, C190, C191, and C150.R E L A T I V E I N T E N S I T Y – %ANGLE0.800.600.500.700.200.100.300.400.90-70-50-3002030507090-90-20-80-60-40-1010406080R E L A T I V E I N T E N S I T Y – %1.000ANGLE0.800.600.500.700.200.100.300.400.90-70-50-3002030507090-90-20-80-60-40-1010406080R E L A T I V E I N T E N S I T Y – %1.000ANGLE0.800.600.500.700.200.100.300.400.90-70-50-3002030507090-90-20-80-60-40-1010406080Figure 8. Recommended Pb-free reflow soldering profile.Figure 9. Recommended soldering pattern for HSMx-C110.Figure 10. Recommended soldering pattern for HSMx-C170.Figure 11. Recommended soldering pattern for HSMx-C190 and C191.Figure 12. Recommended soldering pattern for HSMx-C150.(0.059)(0.059)(0.079)(0.035)0.8(0.028)(0.059)(0.059)(0.079)Note: All dimensions in millimeters (inches).* THE TIME FROM 25 °C TO PEAK TEMPERATURE = 6 MINUTES MAX.Figure 7. Recommended reflow soldering profile.T E M P E R A T U R EFigure 13. Reeling orientation.Figure 14. Reel dimensions.Ø 20.20 MIN.(Ø 0.795 MIN.)Ø 13.1 ± 0.5Note: All dimensions in millimeters (inches).Figure 15. Tape dimensions.Figure 16. Tape leader and trailer dimensions.Convective IR Reflow Soldering For more information on IR reflow soldering, refer toApplication Note 1060,Surface Mounting SMT LED Indicator Components.Storage Condition: 5 to 30˚C @ 60% RH max.Baking is required under the condition:a)the blue silica gel indicator becoming white/transparent colorb)the pack has been opened for more than 1 weekBaking recommended condition:60 +/– 5˚C for 20 hours.END STARTSEALED WITH COVER TAPE.SEALED WITH COVER TAPE.OF CARRIER AND/ORCOVER TAPE.NOTES:1. ALL DIMENSIONS IN MILLIMETERS (INCHES).2. TOLERANCE IS ± 0.1 mm (± 0.004 IN.) UNLESS OTHERWISE SPECIFIED.TABLE 1DIMENSIONS IN MILLIMETERS (INCHES)DIM. A ± 0.10 (± 0.004)DIM. B ± 0.10 (± 0.004)PART NUMBERDIM. C± 0.10 (± 0.004)HSMx-C170 SERIES 2.30 (0.091) 1.45 (0.057) 0.95 (0.037)HSMx-C190 SERIES 1.80 (0.071) 0.95 (0.037) 0.87 (0.034)HSMx-C110 SERIES 3.40 (0.134) 1.70 (0.067) 1.20 (0.047)HSMx-C191 SERIES 1.86 (0.073) 0.89 (0.035) 0.87 (0.034)HSMx-C150 SERIES 3.50 (0.138) 1.88 (0.074) 1.27 (0.050)/semiconductors For product information and a complete list of distributors, please go to our web site.For technical assistance call:Americas/Canada: +1 (800) 235-0312 or (916) 788-6763Europe: +49 (0) 6441 92460China: 10800 650 0017Hong Kong: (+65) 6756 2394India, Australia, New Zealand: (+65) 6755 1939 Japan: (+81 3) 3335-8152 (Domestic/Interna-tional), or 0120-61-1280 (Domestic Only) Korea: (+65) 6755 1989Singapore, Malaysia, Vietnam, Thailand, Philippines, Indonesia: (+65) 6755 2044 Taiwan: (+65) 6755 1843Data subject to change.Copyright © 2005 Agilent Technologies, Inc. Obsoletes 5989-0519ENAugust 1, 20055989-3604EN。

CY7C68013A-100AXC中文资料

元器件交易网

CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A

1.2 Features (CY7C68015A/16A only)

an easy and glueless interface to popular interfaces such as ATA, UTOPIA, EPP, PCMCIA, and most DSP/processors. The FX2LP draws considerably less current than the FX2 (CY7C68013), has double the on-chip code/data RAM and is fit, form and function compatible with the 56-, 100-, and 128pin FX2. Four packages are defined for the family: 56 SSOP, 56 QFN, 100 TQFP, and 128 TQFP.

• CY7C68016A: Ideal for battery powered applications — Suspend current: 100 µA (typ) • CY7C68015A: Ideal for non-battery powered applications — Suspend current: 300 µA (typ) • Available in lead-free 56-pin QFN package (26 GPIOs) — 2 more GPIOs than CY7C68013A/14A enabling additional features in same footprint Cypress Semiconductor Corporation’s (Cypress’s) EZ-USB FX2LP (CY7C68013A/14A) is a low-power version of the EZ-USB FX2 (CY7C68013), which is a highly integrated, low-power USB 2.0 microcontroller. By integrating the USB 2.0 transceiver, serial interface engine (SIE), enhanced 8051 microcontroller, and a programmable peripheral interface in a single chip, Cypress has created a very cost-effective solution that provides superior time-to-market advantages with low power to enable bus powered applications. The ingenious architecture of FX2LP results in data transfer rates of over 53 Mbytes per second, the maximum-allowable USB 2.0 bandwidth, while still using a low-cost 8051 microcontroller in a package as small as a 56 QFN. Because it incorporates the USB 2.0 transceiver, the FX2LP is more economical, providing a smaller footprint solution than USB 2.0 SIE or external transceiver implementations. With EZ-USB FX2LP, the Cypress Smart SIE handles most of the USB 1.1 and 2.0 protocol in hardware, freeing the embedded microcontroller for application-specific functions and decreasing development time to ensure USB compatibility. The General Programmable Interface (GPIF) and Master/Slave Endpoint FIFO (8- or 16-bit data bus) provides

FPGA可编程逻辑器件芯片XC7Z100-1FFG900C中文规格书

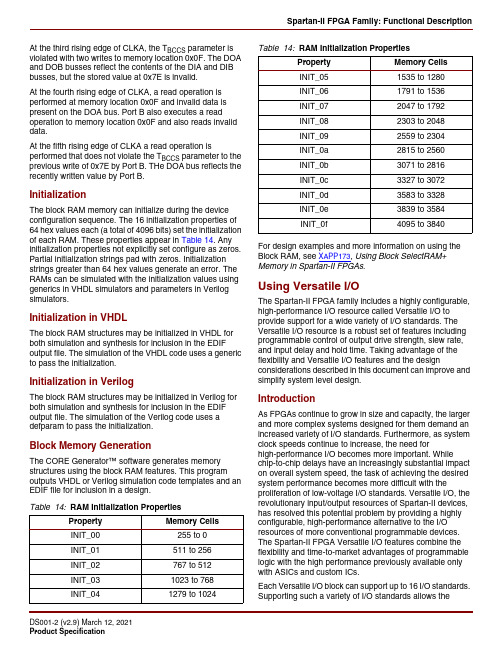

DS001-2 (v2.9) March 12, 2021Product Specification At the third rising edge of CLKA, the T BCCS parameter is violated with two writes to memory location 0x0F. The DOA and DOB busses reflect the contents of the DIA and DIB busses, but the stored value at 0x7E is invalid.At the fourth rising edge of CLKA, a read operation is performed at memory location 0x0F and invalid data is present on the DOA bus. Port B also executes a read operation to memory location 0x0F and also reads invalid data.At the fifth rising edge of CLKA a read operation is performed that does not violate the T BCCS parameter to the previous write of 0x7E by Port B. THe DOA bus reflects the recently written value by Port B.Initialization The block RAM memory can initialize during the device configuration sequence. The 16 initialization properties of64 hex values each (a total of 4096 bits) set the initialization of each RAM. These properties appear in Table 14. Any initialization properties not explicitly set configure as zeros. Partial initialization strings pad with zeros. Initialization strings greater than 64 hex values generate an error. The RAMs can be simulated with the initialization values using generics in VHDL simulators and parameters in Verilog simulators.Initialization in VHDL The block RAM structures may be initialized in VHDL for both simulation and synthesis for inclusion in the EDIF output file. The simulation of the VHDL code uses a generic to pass the initialization.Initialization in VerilogThe block RAM structures may be initialized in Verilog for both simulation and synthesis for inclusion in the EDIF output file. The simulation of the Verilog code uses a defparam to pass the initialization.Block Memory Generation The CORE Generator™ software generates memory structures using the block RAM features. This program outputs VHDL or Verilog simulation code templates and an EDIF file for inclusion in a design.For design examples and more information on using the Block RAM, see XAPP173, Using Block SelectRAM+ Memory in Spartan-II FPGAs .Using Versatile I/O The Spartan-II FPGA family includes a highly configurable,high-performance I/O resource called Versatile I/O to provide support for a wide variety of I/O standards. The Versatile I/O resource is a robust set of features including programmable control of output drive strength, slew rate, and input delay and hold time. Taking advantage of the flexibility and Versatile I/O features and the designconsiderations described in this document can improve and simplify system level design. Introduction As FPGAs continue to grow in size and capacity, the larger and more complex systems designed for them demand anincreased variety of I/O standards. Furthermore, as system clock speeds continue to increase, the need forhigh-performance I/O becomes more important. Whilechip-to-chip delays have an increasingly substantial impact on overall system speed, the task of achieving the desired system performance becomes more difficult with theproliferation of low-voltage I/O standards. Versatile I/O, the revolutionary input/output resources of Spartan-II devices, has resolved this potential problem by providing a highly configurable, high-performance alternative to the I/O resources of more conventional programmable devices. The Spartan-II FPGA Versatile I/O features combine the flexibility and time-to-market advantages of programmable logic with the high performance previously available only with ASICs and custom ICs.Each Versatile I/O block can support up to 16 I/O standards. Supporting such a variety of I/O standards allows the Table 14: RAM Initialization Properties Property Memory Cells INIT_00255 to 0INIT_01511 to 256INIT_02767 to 512INIT_031023 to 768INIT_041279 to 1024INIT_051535 to 1280INIT_061791 to 1536INIT_072047 to 1792INIT_082303 to 2048INIT_092559 to 2304INIT_0a 2815 to 2560INIT_0b 3071 to 2816INIT_0c3327 to 3072INIT_0d3583 to 3328INIT_0e3839 to 3584INIT_0f 4095 to 3840Table 14: RAM Initialization Properties Property Memory CellsDS001-2 (v2.9) March 12, 2021Product Specificationdrivers are disabled. Maintaining a valid logic level in this way helps eliminate bus chatter.Because the weak-keeper circuit uses the IOB input buffer to monitor the input level, an appropriate V REF voltage must be provided if the signaling standard requires one. The provision of this voltage must comply with the I/O banking rules.I/O Banking Some of the I/O standards described above require V CCO and/or V REF voltages. These voltages are externally connected to device pins that serve groups of IOBs, called banks. Consequently, restrictions exist about which I/O standards can be combined within a given bank.Eight I/O banks result from separating each edge of the FPGA into two banks (see Figure 3). Each bank has multiple V CCO pins which must be connected to the same voltage. Voltage is determined by the output standards in use.Within a bank, output standards may be mixed only if they use the same V CCO . Compatible standards are shown in Table 4. GTL and GTL+ appear under all voltages because their open-drain outputs do not depend on V CCO .Some input standards require a user-supplied threshold voltage, V REF . In this case, certain user-I/O pins are automatically configured as inputs for the V REF voltage. About one in six of the I/O pins in the bank assume this role.V REF pins within a bank are interconnected internally and consequently only one V REF voltage can be used within each bank. All V REF pins in the bank, however, must be connected to the external voltage source for correct operation.In a bank, inputs requiring V REF can be mixed with those that do not but only one V REF voltage may be used within a bank. Input buffers that use V REF are not 5V tolerant. LVTTL, LVCMOS2, and PCI are 5V tolerant. The V CCO and V REF pins for each bank appear in the device pinout tables.Within a given package, the number of V REF and V CCO pins can vary depending on the size of device. In larger devices, more I/O pins convert to V REF pins. Since these are always a superset of the V REF pins used for smaller devices, it is possible to design a PCB that permits migration to a larger device. All V REF pins for the largest device anticipated must be connected to the V REF voltage, and not used for I/O.Configurable Logic Block The basic building block of the Spartan-II FPGA CLB is the logic cell (LC). An LC includes a 4-input function generator, carry logic, and storage element. Output from the function generator in each LC drives the CLB output and the D inputof the flip-flop. Each Spartan-II FPGA CLB contains four LCs, organized in two similar slices; a single slice is shown in Figure 4.In addition to the four basic LCs, the Spartan-II FPGA CLB contains logic that combines function generators to provide functions of five or six inputs.Look-Up Tables Spartan-II FPGA function generators are implemented as 4-input look-up tables (LUTs). In addition to operating as a function generator, each LUT can provide a 16x 1-bit synchronous RAM. Furthermore, the two LUTs within a slice can be combined to create a 16x 2-bit or 32x 1-bit synchronous RAM, or a 16x 1-bit dual-port synchronous RAM.The Spartan-II FPGA LUT can also provide a 16-bit shift register that is ideal for capturing high-speed or burst-mode data. This mode can also be used to store data inapplications such as Digital Signal Processing.Figure 3: Spartan-II I/O BanksTable 4: Compatible Output Standards V CCOCompatible Standards 3.3VPCI, LVTTL, SSTL3 I, SSTL3 II, CTT, AGP, GTL, GTL+2.5VSSTL2 I, SSTL2 II, LVCMOS2, GTL, GTL+1.5V HSTL I, HSTL III, HSTL IV, GTL, GTL+DS001_03_060100Independent Banks AvailablePackageVQ100PQ208CS144TQ144FG256FG456Independent Banks 148。

CY7C1515AV18资料

Page 2 of 31 [+] Feedback

元器件交易网

Logic Block Diagram (CY7C1513AV18)

CY7C1511AV18, CY7C1526AV18 CY7C1513AV18, CY7C1515AV18

18 D[17:0]

A(19:0) 20

■ Variable drive HSTL output buffers

■ JTAG 1149.1 compatible test access port

■ Delay Lock Loop (DLL) for accurate data placement

Configurations

CY7C1511AV18 – 8M x 8 CY7C1526AV18 – 8M x 9 CY7C1513AV18 – 4M x 18 CY7C1515AV18 – 2M x 36

Address Register

21

A(20:0)

2M x 8 Array 2M x 8 Array 2M x 8 Array 2M x 8 Array

Read Data Reg. 32 16

16

Control Logic

RPS

C C

Reg.

Reg. 8 8

Reg.

8

8

8

CQ CQ Q[7:0]

Logic Block Diagram (CY7C1526AV18)

Address Register

21