L816BSRC中文资料

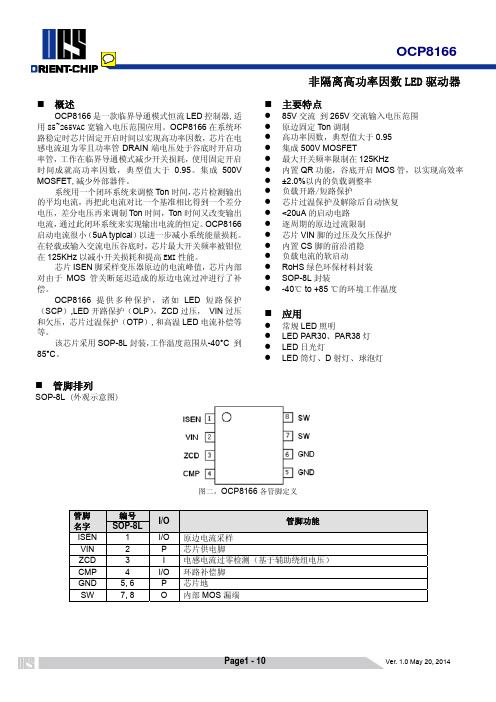

OCP8166 最新资料(2014版)

Temperature(℃)

LED Current (mA)

315.0 313.0 311.0 309.0 307.0 305.0 303.0 301.0 299.0 297.0 295.0

85

LED Current vs Linear Voltage

芯片 ISEN 脚采样变压器原边的电流峰值,芯片内部 对由于 MOS 管关断延迟造成的原边电流过冲进行了补 偿。

OCP8166 提 供 多 种 保 护 , 诸 如 LED 短 路 保 护 (SCP),LED 开路保护(OLP),ZCD 过压, VIN 过压 和欠压,芯片过温保护(OTP),和高温 LED 电流补偿等 等。

RDS(ON) BVDSS

IDSS 保护

MOSFET 开启电阻 MOSFET 击穿电压

MOSFET 漏电

VGATE_H

VIN 及 GATE 脚电压钳位

TRESET

系统重启延迟时间

TSD

过温保护温度

TSDHS

过温保护解除迟滞

T80%

80%电流温度

注: 1, 设计保证

条件

VIN 上升 VIN 下降 通过欠压实现

范围

单位

VIN脚对GND电压

VIN

+9.0 to +20

V

最大输出电流

ILED

250

mA

最大输出功率

85~265VAC 220VAC±15%

POMAX

12 18

W W

工作温度范围

TOP

-40 to +85

℃

最大热阻

SOP-8L

ΘJA

FM24CL16B中文资料

•

198 Champion Court

•

San Jose, CA 95134-1709

• 408-943-2600 Revised April 21, 2014

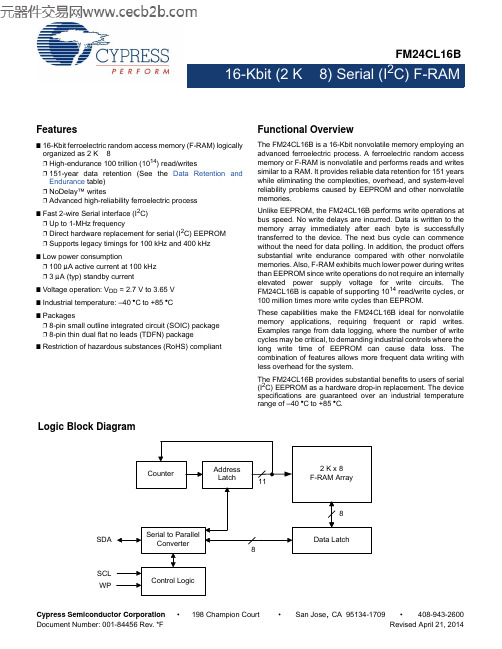

FM24CL16B

Contents

Pinouts .............................................................................. 3 Pin Definitions .................................................................. 3 Overview............................................................................ 4 Memory Architecture........................................................ 4 I2C Interface ...................................................................... 4 STOP Condition (P)..................................................... 4 START Condition (S)................................................... 4 Data/Address Transfer ................................................ 5 Acknowledge / No-acknowledge ................................. 5 Slave Device Address ................................................. 6 Addressing Overview (Word Address) ........................ 6 Data Transfer .............................................................. 6 Memory Operation............................................................ 6 Write Operation ........................................................... 6 Read Operation ........................................................... 7 Endurance ......................................................................... 8 Maximum Ratings............................................................. 9 Operating Range............................................................... 9 DC Electrical Characteristics .......................................... 9 Data Retention and Endurance ..................................... 10 Capacitance .................................................................... Thermal Resistance........................................................ AC Test Loads and Waveforms..................................... AC Test Conditions ........................................................ AC Switching Characteristics ....................................... Power Cycle Timing ....................................................... Ordering Information...................................................... Ordering Code Definitions ......................................... Package Diagrams.......................................................... Acronyms ........................................................................ Document Conventions ................................................. Units of Measure ....................................................... Document History Page ................................................. Sales, Solutions, and Legal Information ...................... Worldwide Sales and Design Support....................... Products .................................................................... PSoC® Solutions ...................................................... Cypress Developer Community................................. Technical Support ..................................................... 10 10 10 10 11 12 13 13 14 16 16 16 17 18 18 18 18 18 18FM2 NhomakorabeaCL16B

恒星芯片B4161A 2.4GHz 19dBm无线芯片板文档说明书

EFR32MG12 2.4 GHz 19 dBm Radio Board BRD4161A Reference ManualRADIO BOARD FEATURES•Wireless SoC:EFR32MG12P432F1024GL125•CPU core: ARM Cortex ®-M4 with FPU •Flash memory: 1024 kB •RAM: 256 kB•Operation frequency: 2.4 GHz •Transmit power: 19 dBm•Integrated PCB antenna, UFL connector (optional).•Touch Slider•Crystals for LFXO and HFXO: 32.768 kHz and 38.4 MHz.The BRD4161A Mighty Gecko Radio Board enables developers to develop Zigbee ®, Thread,Bluetooth ® low energy and proprietary wireless applications. The board con-tains a Mighty Gecko Wireless System on Chip 2.4 GHz and optimized for operation with 19 dBm output power. With the on-board printed antenna and RF connector radi-ated and conducted testing is supported.The BRD4161A Mighty Gecko Radio Board plugs into the Wireless Starter Kit Main-board provided with the Mighty Gecko Starter Kit to get access to display, buttons and additional features from Expansion Boards. With the supporting Simplicity Studio suite of tools, developers can take advantage of graphical wireless application development; mesh networking debug and packet trace; and visual energy profiling and optimization. The board also serves as an RF reference design for applications targeting 2.4 GHz wireless operation with 19 dBm output power.This document contains brief introduction and description of the BRD4161A Radio Board features focusing on the RF sections and performance.| Smart. Connected. Energy-friendly.Rev. 1.00Introduction 1. IntroductionThe EFR32 Mighty Gecko Radio Boards provide a development platform (together with the Wireless Starter Kit Mainboard) for the Silicon Labs EFR32 Mighty Gecko Wireless System on Chips and serve as reference designs for the matching network of the RF inter-face.The BRD4161A Radio Board is designed to operate in the 2400-2483.5 MHz band with the RF matching network optimized to operate with 19 dBm output power.To develop and/or evaluate the EFR32 Mighty Gecko, the BRD4161A Radio Board can be connected to the Wireless Starter Kit Main-board to get access to display, buttons and additional features from Expansion Boards and also to evaluate the performance of the RF interface.2. Radio Board Connector2.1 IntroductionThe board-to-board connector scheme allows access to all EFR32MG12 GPIO pins as well as the RESETn signal. For more informa-tion on the functions of the available pin functions, see the EFR32MG12 data sheet.2.2 Radio Board Connector Pin AssociationsThe figure below shows the pin mapping on the connector to the radio pins and their function on the Wireless Starter Kit Mainboard.GNDF9 / PA3 / VCOM_RTS 3v3VCOM_RTS / PA3 / P36P200Upper RowNC / P38NC / P40PF9 / P42PF11 / P44DEBUG.TMS_SWDIO / PF1 / F0DISP_ENABLE / PD15 / F14UIF_BUTTON0 / PF6 / F12UIF_LED1 / PF4 / F10VCOM_CTS / PA2 / F8DEBUG.RESET / RADIO_#RESET / F4DEBUG.TDO_SWO / PF2 / F2DISP_SI / PC6 / F16VCOM_TXD / PA0 / F6PTI_DATA / PB12 / F20DISP_EXTCOMIN / PD13 / F18USB_VBUS5VBoard ID SCLGNDBoard ID SDAUSB_VREG F7 / PA1 / VCOM_RXD F5 / PA5 / VCOM_ENABLE F3 / PF3 / DEBUG.TDIF1 / PF0 / DEBUG.TCK_SWCLK P45 / PF12P43 / PF10P41 / PF8P39 / NC P37/ PB10 / SENSOR_ENABLE F11 / PF5 / UIF_LED1F13 / PF7 / UIF_BUTTON1F15 / PC8 / DISP_SCLK F17 / PD14 / DISP_SCS F19 / PB13 / PTI_FRAME F21 / PB11 / PTI_CLK GND VMCU_IN PD8 / P0P201Lower RowPD9 / P2PD10 / P4PD11 / P6GNDNCP35 / PA2 / VCOM_CTS P7 / PA9P5 / PA8P3 / PA7P1 / PA6P33 / PA0 / VCOM_TXD P31 / PK2P29 / PK0P27 / PJ14P25 / PI2P23 / PI0P21 / PF14P19 / NC P17 / PC5P15 / PB9P13 / PC11P11 / PB7P9 / PB6VCOM_RXD / P34 / P34BODEN / P32PK1/ P30PJ15 / P28PI3 / P26PI1 / P24PF15 / P22PF13 / P20NC / P18PC4 / P16PB8 / P14PC10 / P12PC9 / P10PD12 / P8Figure 2.1. BRD4161A Radio Board Connector Pin MappingRadio Board Connector3. Radio Board Block Summary3.1 IntroductionThis section gives a short introduction to the blocks of the BRD4161A Radio Board.3.2 Radio Board Block DiagramThe block diagram of the EFR32MG Radio Board is shown in the figure below.Figure 3.1. BRD4161A Block Diagram3.3 Radio Board Block Description3.3.1 Wireless MCUThe BRD4161A Mighty Gecko Radio Board incorporates an EFR32MG12P432F1024GL125 Wireless System on Chip featuring 32-bit Cortex®-M4 with FPU core, 1024 kB of flash memory and 256 kB of RAM and a 2.4 GHz band transceiver with output power up to 19 dBm. For additional information on the EFR32MG12P432F1024GL125, refer to the EFR32MG12 Data Sheet.3.3.2 LF Crystal Oscillator (LFXO)The BRD4161A Radio Board has a 32.768 kHz crystal mounted.3.3.3 HF Crystal Oscillator (HFXO)The BRD4161A Radio Board has a 38.4 MHz crystal mounted.| Smart. Connected. Energy-friendly.Rev. 1.00 | 33.3.4 Matching Network for 2.4 GHzThe BRD4161A Radio Board incorporates a 2.4 GHz matching network which connects the 2.4 GHz TRX pin of the EFR32MG12 to the one on-board printed Inverted-F antenna. The component values were optimized for the 2.4 GHz band RF performace and current con-sumption with 19 dBm output power.For detailed description of the matching network, see Chapter 4.2.1 Description of the 2.4 GHz RF Matching.3.3.5 Inverted-F AntennaThe BRD4161A Radio Board includes a printed Inverted-F antenna (IFA) tuned to have close to 50 Ohm impedance at the 2.4 GHz band.For detailed description of the antenna see Chapter 4.5 Inverted-F Antenna.3.3.6 UFL ConnectorTo be able to perform conducted measurements, Silicon Labs added an UFL connector to the Radio Board. The connector allows an external 50 Ohm cable or antenna to be connected during design verification or testing.Note: By default the output of the matching network is connected to the printed Inverted-F antenna by a series component. It can be connected to the UFL connector as well through a series 0 Ohm resistor which is not mounted by default. For conducted measurements through the UFL connector the series component to the antenna should be removed and the 0 Ohm resistor should be mounted (see Chapter 4.2 Schematic of the RF Matching Network for further details).3.3.7 Radio Board ConnectorsTwo dual-row, 0.05” pitch polarized connectors make up the EFR32MG Radio Board interface to the Wireless Starter Kit Mainboard. For more information on the pin mapping between the EFR32MG12P432F1024GL125 and the Radio Board Connector, refer to Chapter 2.2 Radio Board Connector Pin Associations.3.3.8 Capacitive Touch SliderThe touch slider (T2) utilizes the capacitive touch capability of the Capacitance Sense Module of the EFR32MG12. The slider interpo-lates 4 separate pads to find the exact position of a finger.The figure below shows the pin mapping of the touch slider to the Wireless SoC.Wireless SoCFigure 3.2. Touch Slider Pin MappingRev. 1.00 | 44. RF Section4.1 IntroductionThis section gives a short introduction to the RF section of the BRD4161A.4.2 Schematic of the RF Matching NetworkThe schematic of the RF section of the BRD4161A Radio Board is shown in the following figure.2.4 GHz Matching 2.4 GHz RF OutputSelection & Inverted-F AntennaFigure 4.1. Schematic of the RF Section of the BRD4161A4.2.1 Description of the 2.4 GHz RF MatchingThe 2.4 GHz matching connects the 2G4RF_IOP pin to the on-board printed Inverted-F Antenna. The 2G4RF_ION pin is connected to ground. For higher output powers (13 dBm and above), besides the impedance matching circuitry, it is recommended to use additional harmonic filtering as well at the RF output. The targeted output power of the BRD4161A board is 19 dBm. Therefore, the RF output of the IC is connected to the antenna through a four-element impedance matching and harmonic filter circuitry.For conducted measurements the output of the matching network can also be connected to the UFL connector by removing the series R1 component between the antenna and the output of the matching and adding a 0 Ohm resistor to the R2 resistor position between the output of the matching and the UFL connector.4.3 RF Section Power SupplyOn the BRD4161A Radio Board the power supply pins of the RF section (RFVDD, PAVDD) are directly connected to the output of the on-chip DC-DC converter. This way, by default, the DC-DC converter provides 1.8 V for the entire RF section (for details, see the sche-matic of the BRD4161A).4.4 Bill of Materials for the 2.4 GHz MatchingThe Bill of Materials of the 2.4 GHz matching network of the BRD4161A Radio Board is shown in the following table.| Smart. Connected. Energy-friendly.Rev. 1.00 | 5Table 4.1. Bill of Materials for the BRD4161A 2.4GHz RF Matching Network4.5 Inverted-F AntennaThe BRD4161A Radio Board includes an on-board printed Inverted-F Antenna tuned for the 2.4 GHz band. Due to the design restric-tions of the Radio Board, the input of the antenna and the output of the matching network can't be placed directly next to each other. As a result, a 50 Ohm transmission line was necessary to connect them. With the actual line length the impedance of the antenna at the double-harmonic frequency is transformed closer to a "critical load impedance range" resulting in the radiated level of the harmonic increases.To reduce the harmonic radiation a tuning component was used between the matching network output and the antenna input. For the actual Radio Board design (with the actual transmission line length) a small value inductor was used (instead of the R1 resistor with value of 1.8 nH) to transform the impedance at the double-frequency harmonic away from the critical region while keeping the impe-dance at the funamental close to 50 Ohm. With this the suppression of the radiated double-frequency harmonic increases by approxi-mately 3-4 dB. The resulting impedance and reflection measured at the output of the matcing network are shown in the following figure. As it can be observed the impedance is close to 50 Ohm (the reflection is better than -10 dB) for the entire 2.4 GHz band.Figure 4.2. Impedance and Reflection of the Inverted-F Antenna of the BRD4161A Board Measured from the Matching Output Note: The same value and type of 1.8 nH inductor was used as the one in the matching network (L1). | Smart. Connected. Energy-friendly.Rev. 1.00 | 65. Mechanical DetailsThe BRD4161A Mighty Gecko Radio Board is illustrated in the figures below.Figure 5.1. BRD4161A Top View24 mmConnectorConnector Figure 5.2. BRD4161A Bottom ViewMechanical DetailsRev. 1.00 | 7EMC Compliance 6. EMC Compliance6.1 IntroductionCompliance of the fundamental and harmonic levels is tested against the following standards:• 2.4 GHz:•ETSI EN 300-328•FCC 15.2476.2 EMC Regulations for 2.4 GHz6.2.1 ETSI EN 300-328 Emission Limits for the 2400-2483.5 MHz BandBased on ETSI EN 300-328 the allowed maximum fundamental power for the 2400-2483.5 MHz band is 20 dBm EIRP. For the unwan-ted emissions in the 1 GHz to 12.75 GHz domain the specified limit is -30 dBm EIRP.6.2.2 FCC15.247 Emission Limits for the 2400-2483.5 MHz BandFCC 15.247 allows conducted output power up to 1 Watt (30 dBm) in the 2400-2483.5 MHz band. For spurious emmissions the limit is -20 dBc based on either conducted or radiated measurement, if the emission is not in a restricted band. The restricted bands are speci-fied in FCC 15.205. In these bands the spurious emission levels must meet the levels set out in FCC 15.209. In the range from 960 MHz to the frequency of the 5th harmonic it is defined as 0.5 mV/m at 3 m distance (equals to -41.2 dBm in EIRP).Additionally, for spurious frequencies above 1 GHz, FCC 15.35 allows duty-cycle relaxation to the regulatory limits. For the EmberZNet PRO the relaxation is 3.6 dB. Therefore, the -41.2 dBm limit can be modified to -37.6 dBm.If operating in the 2400-2483.5 MHz band the 2nd, 3rd and 5th harmonics can fall into restricted bands. As a result, for those the -37.6 dBm limit should be applied. For the 4th harmonic the -20 dBc limit should be applied.6.2.3 Applied Emission Limits for the 2.4 GHz BandThe above ETSI limits are applied both for conducted and radiated measurements.The FCC restricted band limits are radiated limits only. Besides that, Silicon Labs applies those to the conducted spectrum i.e., it is assumed that, in case of a custom board, an antenna is used which has 0 dB gain at the fundamental and the harmonic frequencies. In that theoretical case, based on the conducted measurement, the compliance with the radiated limits can be estimated.The overall applied limits are shown in the table below.Table 6.1. Applied Limits for Spurious Emissions for the 2.4 GHz Band | Smart. Connected. Energy-friendly.Rev. 1.00 | 87. RF Performance7.1 Conducted Power MeasurementsDuring measurements, the EFR32MG Radio Board was attached to a Wireless Starter Kit Mainboard which was supplied by USB. The voltage supply for the Radio Board was 3.3 V.7.1.1 Conducted Measurements in the 2.4 GHz bandThe BRD4161A board was connected directly to a Spectrum Analyzer through its UFL connector (the R1 component was removed and a 0 Ohm resistor was soldered to the R2 resistor position). During measurements, the voltage supply for the board was 3.3 V provided by the mainboard. The supply for the radio (RFVDD) was 1.8 V provided by the on-chip DC-DC converter, the supply for the power amplifier (PAVDD) was 3.3 V (for details, see the schematic of the BRD4161A). The transceiver was operated in continuous carrier transmission mode. The output power of the radio was set to 19 dBm.The typical output spectrum is shown in the following figure.Figure 7.1. Typical Output Spectrum of the BRD4161AAs it can be observed, the fundamental is slightly lower than 19 dBm limit and the strongest unwanted emission is the double-frequency harmonic and it is under the -37.6 dBm applied limit.Note: The conducted measurement is performed by connecting the on-board UFL connector to a Spectrum Analyzer through an SMA Conversion Adapter (P/N: HRMJ-U.FLP(40)). This connection itself introduces approximately 0.3 dB insertion loss.RF PerformanceRev. 1.00 | 97.2 Radiated Power MeasurementsDuring measurements, the EFR32MG Radio Board was attached to a Wireless Starter Kit Mainboard which was supplied by USB. The voltage supply for the Radio Board was 3.3 V. The radiated power was measured in an antenna chamber by rotating the DUT 360degrees with horizontal and vertical reference antenna polarizations in the XY , XZ and YZ cuts. The measurement axes are shown inthe figure below.Figure 7.2. DUT: Radio Board with the Wireless Starter Kit Mainboard (Illustration)Note: The radiated measurement results presented in this document were recorded in an unlicensed antenna chamber. Also the radi-ated power levels may change depending on the actual application (PCB size, used antenna, and so on). Therefore, the absolute levels and margins of the final application are recommended to be verified in a licensed EMC testhouse.7.2.1 Radiated Measurements in the 2.4 GHz bandFor the transmitter antenna the on-board printed Inverted-F antenna of the BRD4161A board was used (the R1 component was moun-ted). During measurements, the board was attached to a Wireless Starter Kit Mainboard (BRD4001 (Rev. A02) ) which was supplied through USB. During the measurements the voltage supply for the board was 3.3 V provided by the mainboard. The supply for the radio (RFVDD) was 1.8 V provided by the on-chip DC-DC converter, the supply for the power amplifier (PAVDD) was 3.3 V (for details, see the schematic of the BRD4161A). The transceiver was operated in continuous carrier transmission mode. The output power of the radio was set to 19 dBm based on the conducted measurement.The results are shown in the table below.Table 7.1. Maximums of the measured radiated powers in EIRP [dBm]As it can be observed, thanks to the high gain of the Inverted-F antenna, the level of the fundamental is higher than 19 dBm. The stron-gest harmonic is the double-frequency one and thanks to the additional suppression provided by the instead of the R1 resistor its level is under -50 dBm.RF PerformanceEMC Compliance Recommendations 8. EMC Compliance Recommendations8.1 Recommendations for 2.4 GHz ETSI EN 300-328 complianceAs it was shown in the previous chapter, the radiated power of the fundamental of the BRD4161A Mighty Gecko Radio Board complies with the 20 dBm limit of the ETSI EN 300-328 in case of the conducted measurement but due to the high antenna gain the radiated power is higher than the limit by 2 dB. In order to comply, the output power should be reduced (with different antennas, depending on the gain of the used antenna, the necessary reduction can be different). The harmonic emissions are under the -30 dBm limit. Although the BRD4161A Radio Board has an option for mounting a shielding can, that is not required for the compliance.8.2 Recommendations for 2.4 GHz FCC 15.247 complianceAs it was shown in the previous chapter, the radiated power of the fundamental of the BRD4161A Mighty Gecko Radio Board complies with the 30 dBm limit of the FCC 15.247. The harmonic emissions are under the -37.6 dBm applied limit both in case of the conducted and the radiated measurements. Although the BRD4161A Radio Board has an option for mounting a shielding can, that is not required for the compliance.Document Revision History 9. Document Revision HistoryTable 9.1. Document Revision HistoryBoard Revision History 10. Board Revision HistoryTable 10.1. BRD4161A Radio Board RevisionsErrata 11. ErrataThere are no known errata at present.Table of Contents1. Introduction (1)2. Radio Board Connector (2)2.1 Introduction (2)2.2 Radio Board Connector Pin Associations (2)3. Radio Board Block Summary (3)3.1 Introduction (3)3.2 Radio Board Block Diagram (3)3.3 Radio Board Block Description (3)3.3.1 Wireless MCU (3)3.3.2 LF Crystal Oscillator (LFXO) (3)3.3.3 HF Crystal Oscillator (HFXO) (3)3.3.4 Matching Network for 2.4 GHz (4)3.3.5 Inverted-F Antenna (4)3.3.6 UFL Connector (4)3.3.7 Radio Board Connectors (4)3.3.8 Capacitive Touch Slider (4)4. RF Section (5)4.1 Introduction (5)4.2 Schematic of the RF Matching Network (5)4.2.1 Description of the 2.4 GHz RF Matching (5)4.3 RF Section Power Supply (5)4.4 Bill of Materials for the 2.4 GHz Matching (5)4.5 Inverted-F Antenna (6)5. Mechanical Details (7)6. EMC Compliance (8)6.1 Introduction (8)6.2 EMC Regulations for 2.4 GHz (8)6.2.1 ETSI EN 300-328 Emission Limits for the 2400-2483.5 MHz Band (8)6.2.2 FCC15.247 Emission Limits for the 2400-2483.5 MHz Band (8)6.2.3 Applied Emission Limits for the 2.4 GHz Band (8)7. RF Performance (9)7.1 Conducted Power Measurements (9)7.1.1 Conducted Measurements in the 2.4 GHz band (9)7.2 Radiated Power Measurements (10)7.2.1 Radiated Measurements in the 2.4 GHz band (10)8. EMC Compliance Recommendations (11)8.1 Recommendations for 2.4 GHz ETSI EN 300-328 compliance (11)8.2 Recommendations for 2.4 GHz FCC 15.247 compliance (11)9. Document Revision History (12)10. Board Revision History (13)11. Errata (14)Table of Contents (15)Silicon Laboratories Inc.400 West Cesar Chavez Austin, TX 78701USASimplicity StudioOne-click access to MCU and wireless tools, documentation, software, source code libraries & more. Available for Windows, Mac and Linux!IoT Portfolio /IoTSW/HW/simplicityQuality/qualitySupport and CommunityDisclaimerSilicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.Trademark InformationSilicon Laboratories Inc.® , Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.。

LH28F640BFN-PTTLZ2资料

• Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.• When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.(1) The products covered herein are designed and manufactured for the following application areas. When using theproducts covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph(3).• Office electronics• Instrumentation and measuring equipment• Machine tools• Audiovisual equipment• Home appliance• Communication equipment other than for trunk lines(2) Those contemplating using the products covered herein for the following equipment which demands highreliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.• Control and safety devices for airplanes, trains, automobiles, and other transportation equipment• Mainframe computers• Traffic control systems• Gas leak detectors and automatic cutoff devices• Rescue and security equipment• Other safety devices and safety equipment, etc.(3) Do not use the products covered herein for the following equipment which demands extremely high performancein terms of functionality, reliability, or accuracy.• Aerospace equipment• Communications equipment for trunk lines• Control equipment for the nuclear power industry• Medical equipment related to life support, etc.(4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a salesrepresentative of the company.• Please direct all queries regarding the products covered herein to a sales representative of the company.PAGE 44-Lead SOP Pinout (3)Pin Descriptions (4)Memory Map (5)Identifier Codes and OTP Addressfor Read Operation (6)OTP Block Address Map for OTP Program (7)Bus Operation (8)Command Definitions (9)Functions of Block Lock and Block Lock-Down (11)Block Locking State Transitions uponCommand Write (11)Status Register Definition (12)Extended Status Register Definition (13)PAGE 1 Electrical Specifications (14)1.1 Absolute Maximum Ratings (14)1.2 Operating Conditions (14)1.2.1 Capacitance (15)1.2.2 AC Input/Output Test Conditions (15)1.2.3 DC Characteristics (16)1.2.4 AC Characteristics- Read-Only Operations (17)1.2.5 AC Characteristics- Write Operations (20)1.2.6 Reset Operations (22)1.2.7 Block Erase, Full Chip Erase,(Page Buffer) Program andOTP Program Performance (23)2 Related Document Information (24)CONTENTSLH28F640BFN-PTTLZ2 64Mbit (4Mbit×16) Page Mode Flash MEMORY64M density with 16Bit I/O InterfaceHigh Performance Reads• 90/35ns 8-Word Page ModeLow Power Operation• 2.7V Read and Write Operations• Automatic Power Savings Mode Reduces I CCRin Static ModeEnhanced Code + Data Storage• 5µs Typical Erase/Program SuspendsOTP (One Time Program) Block• 4-Word Factory-Programmed Area• 4-Word User-Programmable AreaHigh Performance Program with Page Buffer• 16-Word Page BufferOperating Temperature 0°C to +70°CFlexible Blocking Architecture• Eight 4K-word Parameter Blocks• One-hundred and twenty-seven 32K-word Main Blocks• Top Parameter LocationCMOS Process (P-type silicon substrate) Enhanced Data Protection Features• Individual Block Lock and Block Lock-Down with Zero-Latency• All blocks are locked at power-up or device reset.• Block E rase, Full Chip E rase, (Page Buffer) Word Program Lockout during Power TransitionsAutomated Erase/Program Algorithms• 3.0V Low-Power 11µs/Word (Typ.)ProgrammingCross-Compatible Command Support• Basic Command Set• Common Flash Interface (CFI)Extended Cycling Capability• Minimum 100,000 Block Erase Cycles44-Lead SOPETOX TM* Flash TechnologyNot designed or rated as radiation hardenedThe product, which is Page Mode Flash memory, is a low power, high density, low cost, nonvolatile read/write storage solution for a wide range of applications. The product can operate at V CC=2.7V-3.6V. Its low voltage operation capability greatly extends battery life for portable applications.The product provides high performance asynchronous page mode. It allows code execution directly from Flash, thus eliminating time consuming wait states.The memory array block architecture utilizes Enhanced Data Protection features, and provides separate Parameter and Main Blocks that provide maximum flexibility for safe nonvolatile code and data storage.Fast program capability is provided through the use of high speed Page Buffer Program.Special OTP (One Time Program) block provides an area to store permanent code such as a unique number.* ETOX is a trademark of Intel Corporation.Table 1.Pin DescriptionsSymbol Type Name and FunctionA0-A21INPUT ADDRESS INPUTS: Inputs for addresses. 64M: A0-A21DQ0-DQ15INPUT/OUTPUT DATA INPUTS/OUTPUTS: Inputs data and commands during CUI (Command User Interface) write cycles, outputs data during memory array, status register, query code and identifier code reads. Data pins float to high-impedance (High Z) when the chip or outputs are deselected. Data is internally latched during an erase or program cycle.CE#INPUT CHIP ENABLE: Activates the device’s control logic, input buffers, decoders and sense amplifiers. CE#-high (V IH) deselects the device and reduces power consumption to standby levels.RST#INPUT RESET: When low (V IL), RST# resets internal automation and inhibits write operations which provides data protection. RST#-high (V IH) enables normal operation. After power-up or reset mode, the device is automatically set to read array mode. RST# must be low during power-up/down.OE#INPUT OUTPUT ENABLE: Gates the device’s outputs during a read cycle.WE#INPUT WRITE ENABLE: Controls writes to the CUI and array blocks. Addresses and data are latched on the rising edge of CE# or WE# (whichever goes high first).V CC SUPPLY DE VICE POWE R SUPPLY (2.7V-3.6V): With V CC≤V LKO, all write attempts to the flash memory are inhibited. Device operations at invalid V CC voltage (see DC Characteristics) produce spurious results and should not be attempted.GND SUPPLY GROUND: Do not float any ground pins.NOTES:1. Top parameter device has its parameter blocks at the highest address.2. DQ 15-DQ 2 are reserved for future implementation.3. OTP-LK=OTP Block Lock configuration.4. OTP=OTP Block data.Table 2.Identifier Codes and OTP Address for Read OperationCodeAddress [A 21-A 0]Data [DQ 15-DQ 0]NotesManufacturer Code Manufacturer Code 000000H 00B0H Device CodeTop Parameter Device Code 000001H 00B0H 1Block Lock Configuration CodeBlock is Unlocked Block Address + 2DQ 0 = 02Block is LockedDQ 0 = 12Block is not Locked-Down Block Address + 2DQ 1 = 02Block is Locked-DownDQ 1 = 12OTPOTP Lock000080HOTP-LK 3OTP 000081-000088HOTP4NOTES:1. See DC Characteristics for V IL or V IH voltages.2. X can be V IL or V IH for control pins and addresses.3. RST# at GND±0.2V ensures the lowest power consumption.4. Command writes involving block erase, full chip erase, (page buffer) program or OTP program are reliably executed when V CC =2.7V-3.6V.5. Refer to Table 4 for valid D IN during a write operation.6. Never hold OE# low and WE# low at the same timing.7. Refer to Appendix of LH28F640BF series for more information about query code.Table 3.Bus Operation (1, 2)Mode Notes RST#CE#OE#WE#Address DQ 0-15Read Array 6V IH V IL V IL V IH X D OUT Output Disable V IH V IL V IH V IH X High Z Standby V IH V IH X X X High Z Reset3V IL X X X X High Z Read Identifier Codes/OTP 6V IH V IL V IL V IH See Table 2See Table 2Read Query 6,7V IH V IL V IL V IH See AppendixSee Appendix Write4,5,6V IHV ILV IHV ILXD INNOTES:1. Bus operations are defined in Table 3.2. The address which is written at the first bus cycle should be the same as the address which is written at the second bus cycle.X=Any valid address within the device.IA=Identifier codes address (See Table 2).QA=Query codes address. Refer to Appendix of LH28F640BF series for details.BA=Address within the block being erased, set/cleared block lock bit or set block lock-down bit.WA=Address of memory location for the Program command or the first address for the Page Buffer Program command.OA=Address of OTP block to be read or programmed (See Figure 3).3. ID=Data read from identifier codes. (See Table 2).QD=Data read from query database. Refer to Appendix of LH28F640BF series for details.SRD=Data read from status register. See Table 7 and Table 8 for a description of the status register bits.WD=Data to be programmed at location WA. Data is latched on the rising edge of WE# or CE# (whichever goes high first) during command write cycles.OD=Data within OTP block. Data is latched on the rising edge of WE# or CE# (whichever goes high first) during command write cycles.N-1=N is the number of the words to be loaded into a page buffer.4. Following the Read Identifier Codes/OTP command, read operations access manufacturer code, device code, block lock configuration code, and the data within OTP block (See Table 2).The Read Query command is available for reading CFI (Common Flash Interface) information.5. Block erase, full chip erase or (page buffer) program cannot be executed when the selected block is locked. Unlocked block can be erased or programmed when RST# is V IH .6. Either 40H or 10H are recognized by the CUI (Command User Interface) as the program setup.7. Following the third bus cycle, inputs the program sequential address and write data of "N" times. Finally, input the any valid address within the target block to be programmed and the confirm command (D0H). Refer to Appendix of LH28F640BF series for details.8. Full chip erase and OTP program operations can not be suspended. The OTP Program command can not be acceptedTable mand Definitions (10)CommandBusCycles Req ’d Notes First Bus CycleSecond Bus Cycle Oper (1)Addr (2)Data Oper (1)Addr (2)Data (3)Read Array1Write X FFH Read Identifier Codes/OTP ≥ 24Write X 90H Read IA or OA ID or OD Read Query ≥ 24Write X 98H Read QA QD Read Status Register 211Write BA or WA70H ReadBA or WASRDClear Status Register 1Write X 50H Block Erase 25Write BA 20H Write BA D0H Full Chip Erase 25,8Write X 30H Write X D0H Program25,6Write WA 40H or 10H Write WA WD Page Buffer Program ≥ 45,7Write WA E8H WriteWAN-1Block Erase and (Page Buffer) Program Suspend18Write BA or WA B0H Block Erase and (Page Buffer) Program Resume 18Write BA or WA D0H Set Block Lock Bit 2Write BA 60H Write BA 01H Clear Block Lock Bit 29Write BA 60H Write BA D0H Set Block Lock-down Bit 2Write BA 60H Write BA 2FH OTP Program28WriteOAC0HWriteOAODwhile the block erase operation is being suspended.9. Following the Clear Block Lock Bit command, the selected block is unlocked regardless of lock-down configuration.10. Commands other than those shown above are reserved by SHARP for future device implementations and should not be used.11. When the status register data is read, input the address to which the erase or program operation is executed.NOTES:1. DQ 0=1: a block is locked; DQ 0=0: a block is unlocked.DQ 1=1: a block is locked-down; DQ 1=0: a block is not locked-down.2. Erase and program are general terms, respectively, to express: block erase, full chip erase and (page buffer) program operations.3. At power-up or device reset, all blocks default to locked state and are not locked-down, that is,[01] regardless of the states before power-off or reset operation.4. OTP (One Time Program) block has the lock function which is different from those described above.NOTES:1. "Set Lock" means Set Block Lock Bit command, "Clear Lock" means Clear Block Lock Bit command and "Set Lock-down" means Set Block Lock-Down Bit command.2. When the Set Block Lock-Down Bit command is written to the unlocked block (DQ 0=0), the corresponding block is locked-down and automatically locked at the same time.3. "No Change" means that the state remains unchanged after the command written.Table 5.Functions of Block Lock (4) and Block Lock-DownCurrent StateErase/Program Allowed (2)State DQ 1(1)DQ 0(1)State Name [00]00Unlocked Yes [01](3)01Locked No [10]10Unlocked Yes [11]11LockedNoTable 6.Block Locking State Transitions upon Command Write Current State Result after Lock Command Written (Next State)State DQ 1DQ 0Set Lock (1)Clear Lock (1)Set Lock-down (1)[00]00[01]No Change (3)[11](2)[01]01No Change [00][11][10]10[11]No Change [11](2)[11]11No Change[10]No ChangeTable 7.Status Register DefinitionR R R R R R R R 15141312111098 WSMS BESS BEFCES PBPOPS R PBPSS DPS R 76543210SR.15 - SR.8 = RESERVED FOR FUTUREENHANCEMENTS (R)SR.7 = WRITE STATE MACHINE STATUS (WSMS)1 = Ready0 = BusySR.6 = BLOCK ERASE SUSPEND STATUS (BESS)1 = Block Erase Suspended0 = Block Erase in Progress/CompletedSR.5 = BLOCK ERASE AND FULL CHIP ERASESTATUS (BEFCES)1 = Error in Block Erase or Full Chip Erase0 = Successful Block Erase or Full Chip EraseSR.4 = (PAGE BUFFER) PROGRAM ANDOTP PROGRAM STATUS (PBPOPS)1 = Error in (Page Buffer) Program or OTP Program0 = Successful (Page Buffer) Program or OTP Program SR.3 = RESERVED FOR FUTURE ENHANCEMENTS (R) SR.2 = (PAGE BUFFER) PROGRAM SUSPENDSTATUS (PBPSS)1 = (Page Buffer) Program Suspended0 = (Page Buffer) Program in Progress/CompletedSR.1 = DEVICE PROTECT STATUS (DPS)1 = Erase or Program Attempted on aLocked Block, Operation Abort0 = UnlockedSR.0 = RESERVED FOR FUTURE ENHANCEMENTS (R)NOTES:Check SR.7 to determine block erase, full chip erase, (page buffer) program or OTP program completion. SR.6 - SR.1 are invalid while SR.7="0".If both SR.5 and SR.4 are "1"s after a block erase, full chip erase, (page buffer) program, set/clear block lock bit, set block lock-down bit, attempt, an improper command sequence was entered.SR.1 does not provide a continuous indication of block lock bit. The WSM interrogates the block lock bit only after Block E rase, Full Chip E rase, (Page Buffer) Program or OTP Program command sequences. It informs the system, depending on the attempted operation, if the block lock bit is set. Reading the block lock configuration codes after writing the Read Identifier Codes/OTP command indicates block lock bit status.SR.15 - SR.8, SR.3 and SR.0 are reserved for future use and should be masked out when polling the status register.Table 8.Extended Status Register DefinitionR R R R R R R R 15141312111098 SMS R R R R R R R 76543210XSR.15-8 = RESERVED FOR FUTUREENHANCEMENTS (R)XSR.7 = STATE MACHINE STATUS (SMS)1 = Page Buffer Program available0 = Page Buffer Program not availableXSR.6-0 = RESERVED FOR FUTURE ENHANCEMENTS (R)NOTES:After issue a Page Buffer Program command (E8H), XSR.7="1" indicates that the entered command is accepted. If XSR.7 is "0", the command is not accepted and a next Page Buffer Program command (E8H) should be issued again to check if page buffer is available or not.XSR.15-8 and XSR.6-0 are reserved for future use and should be masked out when polling the extended status register.1 Electrical Specifications 1.1 Absolute Maximum Ratings *Operating TemperatureDuring Read, Erase and Program......0°C to +70°C (1)Storage TemperatureDuring under Bias...............................-10°C to +80°C During non Bias................................-65°C to +125°C V oltage On Any Pin(except V CC )............................-0.5V to V CC +0.5V (2)V CC Supply V oltage...........................-0.2V to +3.9V (2)Output Short Circuit Current...........................100mA (3)*WARNING: Stressing the device beyond the "AbsoluteMaximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.NOTES:1. Operating temperature is for commercial temperature product defined by this specification.2. All specified voltages are with respect to GND.Minimum DC voltage is -0.5V on input/output pins and -0.2V on V CC pins. During transitions, this level may undershoot to -2.0V for periods <20ns. Maximum DC voltage on input/output pins is V CC +0.5V which,during transitions, may overshoot to V CC +2.0V for periods <20ns.3. Output shorted for no more than one second. No more than one output shorted at a time.1.2 Operating ConditionsNOTES:1. See DC Characteristics tables for voltage range-specific specification.ParameterSymbol Min.Typ.Max.Unit NotesOperating Temperature T A 0+25+70°C V CC Supply Voltage V CC2.73.03.6V 1Main Block Erase Cycling 100,000Cycles Parameter Block Erase Cycling100,000Cycles1.2.3 DC CharacteristicsNOTES:1. All currents are in RMS unless otherwise noted. Typical values are the reference values at V CC =3.0V and T A =+25°C unless V CC is specified.2. I CCWS and I CCES are specified with the device de-selected. If read or (page buffer) program is executed while in block erase suspend mode, the device ’s current draw is the sum of I CCES and I CCR or I CCW . If read is executed while in (page buffer) program suspend mode, the device ’s current draw is the sum of I CCWS and I CCR .3. Block erase, full chip erase, (page buffer) program and OTP program are inhibited when V CC ≤V LKO , and not guaranteed outside the specified voltage.4. The Automatic Power Savings (APS) feature automatically places the device in power save mode after read cycle completion. Standard address access timings (t AVQV ) provide new data when addresses are changed.5. Sampled, not 100% tested.V CC =2.7V-3.6VSymbol ParameterNotes Min.Typ.Max.Unit Test Conditions I LI Input Load Current 1-1.0+1.0µA V CC =V CC Max.,V IN /V OUT =V CC or GND I LO Output Leakage Current 1-1.0+1.0µA I CCS V CC Standby Current1625µAV CC =V CC Max.,CE#=RST#= V CC ±0.2V I CCAS V CC Automatic Power Savings Current 1,4420µA V CC =V CC Max.,CE#=GND±0.2V I CCDV CC Reset Power-Down Current 1420µA RST#=GND±0.2V I CCRAverage V CC Read CurrentNormal Mode11525mAV CC =V CC Max.,CE#=V IL ,OE#=V IH ,f=5MHzAverage V CC ReadCurrentPage Mode8 Word Read 1510mA I CCW V CC (Page Buffer) Program Current 1,52060mA I CCE V CC Block Erase, Full Chip Erase Current1,51030mA I CCWS I CCES V CC (Page Buffer) Program or Block Erase Suspend Current 1,215210µA CE#=V IHV IL Input Low Voltage 5-0.40.4V V IH Input High V oltage 5 2.4V CC + 0.4V V OL Output Low V oltage 50.2V V CC =V CC Min.,I OL =100µA V OH Output High V oltage 5V CC -0.2V V CC =V CC Min.,I OH =-100µAV LKOV CC Lockout Voltage31.5V1.2.4 AC Characteristics - Read-Only Operations(1)V CC=2.7V-3.6V, T A=0°C to +70°CSymbol Parameter Notes Min.Max.Unit t AV AV Read Cycle Time90ns t AVQV Address to Output Delay90ns t ELQV CE# to Output Delay390ns t APA Page Address Access Time35ns t GLQV OE# to Output Delay320ns t PHQV RST# High to Output Delay150ns t EHQZ, t GHQZ CE# or OE# to Output in High Z, Whichever Occurs First220ns t ELQX CE# to Output in Low Z20ns t GLQX OE# to Output in Low Z20ns t OH Output Hold from First Occurring Address, CE# or OE# change20ns NOTES:1. See AC input/output reference waveform for timing measurements and maximum allowable input slew rate.2. Sampled, not 100% tested.3. OE# may be delayed up to t ELQV t GLQV after the falling edge of CE# without impact to t ELQV.1.2.5 AC Characteristics - Write Operations (1), (2)NOTES:1. The timing characteristics for reading the status register during block erase, full chip erase, (page buffer) program and OTP program operations are the same as during read-only operations. Refer to AC Characteristics for read-only operations.2. A write operation can be initiated and terminated with either CE# or WE#.3. Sampled, not 100% tested.4. Write pulse width (t WP ) is defined from the falling edge of CE# or WE# (whichever goes low last) to the rising edge of CE# or WE# (whichever goes high first). Hence, t WP =t WLWH =t ELEH =t WLEH =t ELWH .5. Write pulse width high (t WPH ) is defined from the rising edge of CE# or WE# (whichever goes high first) to the falling edge of CE# or WE# (whichever goes low last). Hence, t WPH =t WHWL =t EHEL =t WHEL =t EHWL .6. t WHR0 (t EHR0) after the Read Query or Read Identifier Codes/OTP command=t A VQV +100ns.7. Refer to Table 4 for valid address and data for block erase, full chip erase, (page buffer) program, OTP program or lock bit configuration.V CC =2.7V-3.6V, T A =0°C to +70°CSymbol ParameterNotesMin.Max.Unit t AV AVWrite Cycle Time90ns t PHWL (t PHEL )RST# High Recovery to WE# (CE#) Going Low 3150ns t ELWL (t WLEL )CE# (WE#) Setup to WE# (CE#) Going Low 40ns t WLWH (t ELEH )WE# (CE#) Pulse Width460ns t DVWH (t DVEH )Data Setup to WE# (CE#) Going High 740ns t AVWH (t AVEH )Address Setup to WE# (CE#) Going High 750ns t WHEH (t EHWH )CE# (WE#) Hold from WE# (CE#) High 0ns t WHDX (t EHDX )Data Hold from WE# (CE#) High 0ns t WHAX (t EHAX )Address Hold from WE# (CE#) High 0ns t WHWL (t EHEL )WE# (CE#) Pulse Width High 530ns t WHGL (t EHGL )Write Recovery before Read 30ns t WHR0 (t EHR0)WE# (CE#) High to SR.7 Going "0"3, 6t A VQV +50ns1.2.7 Block Erase, Full Chip Erase, (Page Buffer) Program and OTP Program Performance (3)NOTES:1. Typical values measured at V CC =3.0V and T A =+25°C. Assumes corresponding lock bits are not set. Subject to change based on device characterization.2. Excludes external system-level overhead.3. Sampled, but not 100% tested.4. A latency time is required from writing suspend command (WE# or CE# going high) until SR.7 going "1".5. If the interval time from a Block Erase Resume command to a subsequent Block Erase Suspend command is shorter than t ERES and its sequence is repeated, the block erase operation may not be finished.V CC =2.7V-3.6V, T A =0°C to +70°CSymbolParameterNotes Page BufferCommand is Used or not Used Min.Typ.(1)Max.(2)Unitt WPB 4K-Word Parameter Block Program Time 2Not Used 0.050.3s 2Used 0.030.12s t WMB 32K-Word Main Block Program Time 2Not Used 0.38 2.4s 2Used 0.24 1.0s t WHQV1/t EHQV1Word Program Time 2Not Used 11200µs 2Used 7100µs t WHOV1/t EHOV1OTP Program Time 2Not Used36400µs t WHQV2/t EHQV24K-Word Parameter Block Erase Time2-0.34s t WHQV3/t EHQV332K-Word Main Block Erase Time2-0.65s Full Chip Erase Time280700s t WHRH1/t EHRH1(Page Buffer) Program Suspend Latency Time to Read 4-510µs t WHRH2/t EHRH2Block Erase Suspend Latency Time to Read 4-520µst ERESLatency Time from Block Erase Resume Command to Block Erase Suspend Command5-500µs2 Related Document Information(1)Document No.Document NameFUM00701 LH28F640BF series AppendixNOTE:1. International customers should contact their local SHARP or distribution sales offices.A-1.1.1 Rise and Fall TimeSymbol Parameter Notes Min.Max.Unit t VR V CC Rise Time10.530000µs/V t R Input Signal Rise Time1, 21µs/V t F Input Signal Fall Time1, 21µs/VNOTES:1. Sampled, not 100% tested.2. This specification is applied for not only the device power-up but also the normal operations.A-2 RELATED DOCUMENT INFORMATION(1)Document No.Document Name AP-001-SD-E Flash Memory Family Software DriversAP-006-PT-E Data Protection Method of SHARP Flash Memory AP-007-SW-E RP#, V PP Electric Potential Switching CircuitNOTE:1. International customers should contact their local SHARP or distribution sales office.。

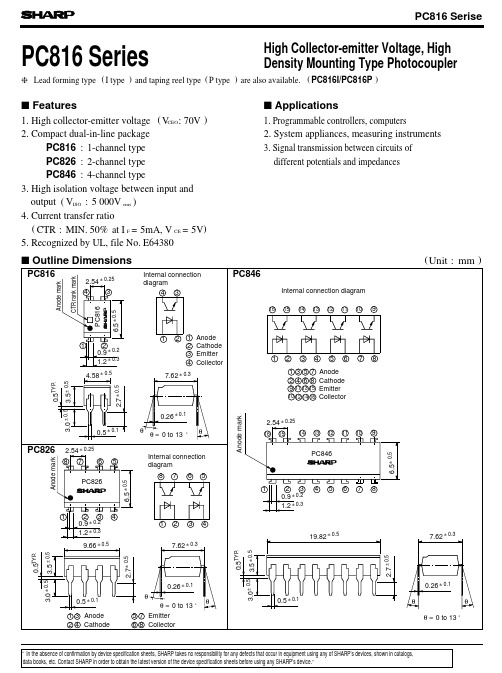

PC816AB中文资料

PC816 Seriess Featuress Applicationsdifferent potentials and impedancess Outline Dimensions(Unit :mm )ISO 2. Compact dual-in-line package 3. High isolation voltage between input and 4. Current transfer ratio(CTR :MIN. 50% at I F =5mA, V CE =5V ) 1. Programmable controllers, computers2. System appliances, measuring instruments3. Signal transmission between circuits of High Collector-emitter Voltage, High Density Mounting Type PhotocouplerPC816:1-channel type PC826:2-channel type PC846:4-channel typeCEO 1. High collector-emitter voltage (V : 70V ) output (V 5. Recognized by UL, file No. E64380g Lead forming type (I type ) and taping reel type (P type ) are also available. (PC816I/PC816P ):5 000V rms )Fig. 3 Peak Forward Current vs. Duty RatioC o l l e c t o r c u r r e n t I C (m A )Collector-emitter voltage V CE (V )Ambient temperature T a (˚C )F (m A )010020050150Ambient TemperatureC (m W )-Fig. 2 Collector Power Dissipation VS.C o l l e c t o r p o w e r d i s s i p a t i o n P F o r w a r d c u r r e n t I 2510205010020050010-300.020204060801000.040.060.080.100.120.140.16200406080555555100Fig. 9 Collector Dark Current vs. Ambient TemperatureFig.11 Frequency ResponseFrequency f (kHz )0125105002001005020R L =10k Ω1k Ω100Ω0.5C E (s a t ) (V )Ambient temperature T a (˚C )C o l l e c t o r d a r k c u r r e n t IC E O (A )Ambient temperature T a (˚C )V o l t a g e g a i n A v (dB )L (k Ω)0.20.10.5120.010.111050R e s p o n s e t i m e (µs )5102050100200500C o l l e c t o r -e m i t t e r s a t u r a t i o n v o l t a g e V C E (s a t ) (V )Forward current I F (mA )123456Fig.12 Collector-emitter Saturation Voltage vs. Forward CurrentTest Circuit for Response TimeInputOutputTest Circuit for Frepuency ResponseFig. 8 Collector-emitter Saturation Voltage vs. Ambient TemperatureC o l l e c t o r -e m i t t e r s a t u r a t i o n v o l t a g e V -3010-1110-1010-910-810-710-610-5-20-10I F =20mA I C =1mAt rt ft dt sV CE =2V I C =2mAT a =25˚C V CE =5V I C =2mA T a =25˚CV CE =20VPlease refer to the chapter “Precautions for Use ”Fig.10 Response Time vs. Load ResistanceLoad resistance R qApplication CircuitsNOTICEq The circuit application examples in this publication are provided to explain representative applications of SHARP devices and are not intended to guarantee any circuit design or license any intellectual property rights. SHARP takes no responsibility for any problems related to any intellectual property right of a third party resulting from the use of SHARP's devices.q Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device.SHARP reserves the right to make changes in the specifications, characteristics, data, materials, structure, and other contents described herein at any time without notice in order to improve design or reliability. Manufacturing locations are also subject to change without notice.q Observe the following points when using any devices in this publication. SHARP takes no responsibility for damage caused by improper use of the devices which does not meet the conditions and absolute maximum ratings to be used specified in the relevant specification sheet nor meet the following conditions:(i) The devices in this publication are designed for use in general electronic equipment designs such as:--- Personal computers--- Office automation equipment--- Telecommunication equipment [terminal]--- Test and measurement equipment--- Industrial control--- Audio visual equipment--- Consumer electronics(ii)Measures such as fail-safe function and redundant design should be taken to ensure reliability and safety when SHARP devices are used for or in connection with equipment that requires higher reliability such as:--- Transportation control and safety equipment (i.e., aircraft, trains, automobiles, etc.)--- Traffic signals--- Gas leakage sensor breakers--- Alarm equipment--- Various safety devices, etc.(iii)SHARP devices shall not be used for or in connection with equipment that requires an extremely high level of reliability and safety such as:--- Space applications--- Telecommunication equipment [trunk lines]--- Nuclear power control equipment--- Medical and other life support equipment (e.g., scuba).q Contact a SHARP representative in advance when intending to use SHARP devices for any "specific"applications other than those recommended by SHARP or when it is unclear which category mentioned above controls the intended use.q If the SHARP devices listed in this publication fall within the scope of strategic products described in the Foreign Exchange and Foreign Trade Control Law of Japan, it is necessary to obtain approval to export such SHARP devices.q This publication is the proprietary product of SHARP and is copyrighted, with all rights reserved. Under the copyright laws, no part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, in whole or in part, without the express written permission of SHARP. Express written permission is also required before any use of this publication may be made by a third party.q Contact and consult with a SHARP representative if there are any questions about the contents of this publication.。

L816BSRD中文资料

PAGE: 2 OF 5

元器件交易网

Absolute Maximum Ratings at T)=25°C °

Par am et er Power dissipation DC Forward Current VF=14V Reverse Voltage Operating Temperature Storage Temperature Lead Soldering Temperature [1]

Yellow L816BYD

Super Bright Red L816BSRD/B,L816SRC/B

SPEC NO: DSAA4471 APPROVED: J.Lu

REV NO: V.1 CHECKED:

DATE: OCT/10/2001 DRAWN: X.H.Fu

PAGE: 5 OF 5

Notes: 1. θ1/2 is the angle from optical centerline where the luminous intensity is 1/2 the optical centerline value.

Electrical / Optical Characteristics at T)=25°C °

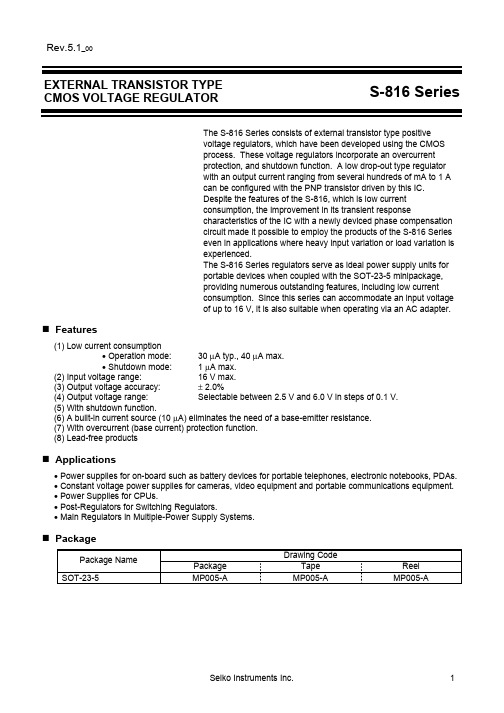

BULIT-IN BLINKING IC.

!OPERATION VOLTAGE FROM 3.5V to 14V. !BLINKING FREQUENCY FROM 3.0Hz to 1.5Hz.

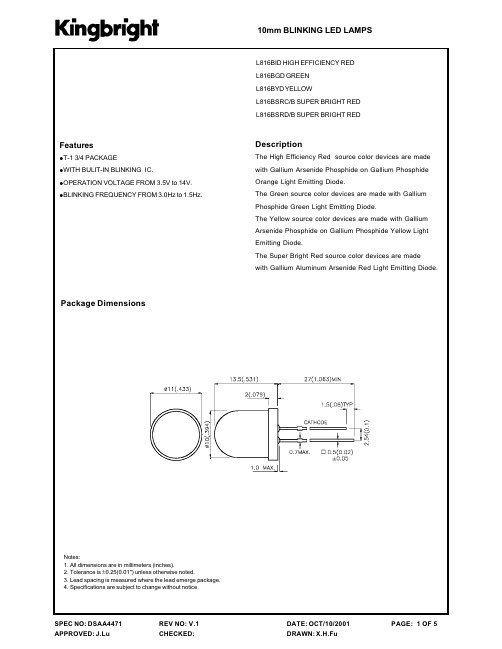

Package Dimensions

Notes: 1. All dimensions are in millimeters (inches). 2. Tolerance is ±0.25(0.01") unless otherwise noted. 3. Lead spacing is measured where the lead emerge package. 4. Specifications are subject to change without notice.

B5S162861TTR;中文规格书,Datasheet资料

1/9February 2003sHIGH SPEED:t PD =1.25ns (MAX.)at V CC =4.5V T A =85°CsON RESISTANCE BETWEEN TWO PORT:25Ω (TYP)at V CC =5.0V T A =25°C sLOW POWER DISSIPATION:I CC =1uA(MAX.)at T A =25°CsCOMPATIBLE WITH TTL OUTPUTS:V IH =2V(MIN),V IL =0.8V(MAX)sPOWER DOWN PROTECTION ON INPUTS AND OUTPUTSsOPERATING VOLTAGE RANGE:V CC (OPR)=4V to 5.5VsPIN AND FUNCTION COMPATIBLE WITH 74SERIES 16861s IMPROVED LATCH-UP IMMUNITY sESD PERFORMANCE:HBM >2000V (MIL STD 883method 3015);MM >200VDESCRIPTIONThe B5S162861is an advanced high-speed CMOS 20-BIT TWO PORT BUS SWITCH fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS tecnology.It is ideal for 4V to 5.5V V CC operations and ultra-low power and low noise applications,typically notebook and docking station.Any nG output control governs two 10-bit BUS SWITCHES.Output Enable inputs (nG)tied together gives full 20-bit operations.When nG is LOW,the switches are on.When nG is HIGH,the switches are in high impedance state.It has ultra high-speed performance at 5V near zero delay with low ON resistance and include 25Ωseries resistor to reduce noise resulting from reflections,thus eliminating the need for an external terminating resistor.All inputs and outputs are equipped with protection circuits against static discharge,giving them 2KV ESD immunity and transient excess voltage.B5S16286120-BIT TWO PORT BUS SWITCH WITH 25ΩSERIES RESISTOR IN OUTPUTThis is preliminary information on a new product now in development are or undergoing evaluation.Details subject to change withoutnotice.ORDER CODESPACKAGE T &RTSSOP48B5S162861TTRPRELIMINARY DATAPIN CONNECTIONOb so l e t ePr od u c t (s ) -d u c t (s)Ob so l e t ePr od u c t (s ) -B5S1628612/9INPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEn:0to 9X:"H"or "L"Z:High ImpedanceSCHEMATIC DIAGRAMPIN No SYMBOL NAME QND FUNCTION 1,13NCNot Connected2,3,4,5,6,7,8,9,10,111A0to 1A9Data Inputs 14,15,16,17,18,19,20,21,22,232A0to 2A9Data Inputs34,33,32,31,30,29,28,27,26,252B0to 2B9Data Outputs46,45,44,43,42,41,40,39,38,371B0to 1B9Data Outputs 47,351G ,2G Bus Enable Input(Active Low)12,24GND Ground (0V)36,48V CCPositive Supply VoltageINPUTOUTPUT nG 1An,2An1Bn,2Bn LXBus ON HXZOb so l e t ePr od u c t (s ) -O bs o l e t eP r od u c t (s) B5S1628613/9ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Rating are those value beyond which damage to the device may occour.Functional operation under these condition isnot implied1)I O absolute maximum rating must be observed 2)V O <GND,V O >V CC3)Not more than one output should be tested at one time.Duration of the test should not exceed one second.RECOMMENDED OPERATING CONDITIONS1)V IN from 0.8V to 2V at V CC =3.0VSymbol Parameter²Value Unit V CC Supply Voltage-0.5to +7.0V V I DC Switch and Control Pin Voltage -0.5to +7.0V V O DC Output Voltage (V CC =0V)(note 1)-0.5to +7.0V V O DC Output Voltage (V I/O =Gnd)-0.5to +7.0V I IK DC Input Diode Current (V I/O <0V)-50mA I OK DC Output Diode Current (note 2)-50mA I ODC Output Current (note 3)128mA I CC or I GND DC V CC or Ground Current per Supply Pin±100mA T stgStorage Temperature -65to +150°C T LLead Temperature (10sec)300°CSymbol ParameterValueUnitV CC Supply Voltage 4to 5.5V V I Input Voltage0to 5.5V V O Output Voltage (V CC =0V)0to 5.5V V O Output Voltage 0to 5.5V T op Operating Temperqture-55to 125°Cdt/dv Switch Input Rise and Fall Time0to DCns/V dt/dvControl Input Rise and Fall Time (note 1)0to 10ns/VOb so l e t ePr od u c t (s ) -O bs o l e t eP r od u c t (s) B5S1628614/9DC SPECIFICATION1)This current applies to the control inputs only and represent the current required to switch internal capacitance at the specified frequency.The 1An and 2An inputs generate no significant AC or DC currents as they transition.This parameter is not tested,but is guaranteed by design.AC ELECTRICAL CHARACTERISTICS1)Parameter guaranteed by design 2)X=1,2;n=0..9.SymbolParameterTest ConditionValue UnitV CC (V)T A =25°C-40to 85°C-55to 125°CMin.Typ.Max.Min.Max.Min.Max.V IH High Level Input Voltage 4to 5.5222V V IL Low Level Input Voltage 4to 5.50.80.80.8V V H Input Hysteresis at Con-trol pin4.5to5.5150mVR ONSwitch ON Resistance4.5I ON =64mA V I =0V 2040Ω4.5I ON =48mA V I =0V 2820404.5I ON =15mA V I =2.4V 3520484.0I ON =15mA V I =2.4V2048I I Input Leakage Current0to 5.5V I =5.5V orGND±0.1±1.0±2.0µA I OZ High Impedance Leakage Current 4.5to 5.5V I/O =5.5Vto GND ±1.0±2.0µA V IK Clamp Diode Voltage 4.0to 5.5I I =-18mA -0.7-1.2-1.2V I CC Quiescent Supply Current 5.5V I =V CC orGND 0.11.03.010.0µAI CCDSupply Current per Con-trol Input per MHz (1)5.5V I/O =Open nG=GND;Control Input Toggling 50%Duty Cycle 0.25mA/MHz∆I CC I CC incr.per Input5.5V IC =V CC -2.1V2.5mASymbolParameterTest ConditionValueUnitV CC (V)C L (pF)R L (Ω)t s =t r (ns)-40to 85°C -55to 125°C Min.Max.Min.Max.t PLH t PHL Propagation Delay Time (1)xAn to xBn,xBn to xAn(2) 4.5to 5.550500 2.5 1.25ns t PZL t PZH Output Enable Time 50500 2.5 1.5 5.5ns t PLZ t PHZOutput Disable Time505002.51.55.5nsOb so l e t ePr od u c t (s )- O bs o B5S1628615/9CAPACITANCE CHARACTERISTICSTEST CIRCUITC L =50pF or equivalent (includes jig and probe capacitance)R L =R 1=500Ωor equivalentR T =Z OUT of pulse generator (typically 50Ω)SymbolParameterTest ConditionValue UnitV CC (V)T A =25°C Min.Typ.Max.C IN Input Capacitance at Control Pin4pF C I/OInput Capacitance at I/O Pin5.0nG=V CC5.5pF TESTSWITCH t PLH ,t PHL Open t PZL ,t PLZ 7V t PZH ,t PHZOpenB5S162861WAVEFORM1:PROPAGATION DELAY(f=1MHz;50%duty cycle)WAVEFORM2:OUTPUT ENABLE AND DISABLE TIME(f=1MHz;50%duty cycle)6/9O b s ol e te Pr o du ct(s)-O bs ol e te Pr o du ct(s)B5S1628619/9Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2003 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.© 分销商库存信息: STMB5S162861TTR。

GS8161FZ18BD-6.5中文资料