227543_XILINX_XCF04S

XCF04S中文资料

Data

and

Memory

JTAG Interface

Address

Data

Serial Interface

TDO

CEO

DATA (D0) Serial Mode

CF

Figure 1: XCFxxS Platform Flash PROM Block Diagram

ds123_01_30603

FI

CLK

• Endurance of 20,000 Program/Erase Cycles

• Operation over Full Industrial Temperature Range (–40°C to +85°C)

• IEEE Standard 1149.1/1532 Boundary-Scan (JTAG) Support for Programming, Prototyping, and Testing

When the FPGA is in Slave Serial mode, the PROM and the FPGA are both clocked by an external clock source, or optionally, for the XCFxxP PROM only, the PROM can be used to drive the FPGA’s configuration clock.

元器件交易网

<BL Blue>

R

DS123 (v2.9) May 09, 2006

0

Features

• In-System Programmable PROMs for Configuration of Xilinx FPGAs

赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明

赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。

3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF文件,最后再经过实现后生成PCF 文件。

UCF文件是ASC 2码文件,描述了逻辑设计的约束,可以用文本编辑器和Xilinx约束文件编辑器进行编辑。

NCF约束文件的语法和UCF文件相同,二者的区别在于:UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。

PCF文件可以分为两个部分:一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。

一般情况下,用户约束都应在UCF文件中完成,不建议直接修改NCF文件和PCF文件。

约束文件的后缀是.ucf,所以一般也被称为UCF文件。

创建约束文件有两种方法,一种是通过新建方式,另一种则是利用过程管理器来完成。

第一种方法:新建一个源文件,在代码类型中选取ImplementaTIon Constrains File,在File Name中输入约束文件的名称。

单击Next按键进入模块选择对话框,选择要约束的模块,然后单击Next进入下一页,再单击Finish按键完成约束文件的创建。

第二种方法:在工程管理区中,将Source for设置为Synthesis/ImplementaTIon。

Constrains Editor是一个专用的约束文件编辑器,双击过程管理区中User Constrains下的Create TIming Constrains就可以打开Constrains Editor。

需要注意的是,UCF文件是大小敏感的,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。

OXuPCI954_DS

External—Free ReleaseOxford Semiconductor, Inc.1900 McCarthy Boulevard, Suite 210 © Oxford Semiconductor, Inc. 2007F EATURES• Four 16C950 High performance UART channels • 8-bit Pass-through Local Bus (PCI Bridge )• IEEE1284 Compliant SPP/EPP/ECP parallel port (with external transceiver)• Efficient 32-bit, 33 MHz, multi-function target-only PCIcontroller, fully compliant to PCI Local Bus Specification 3.0 and PCI Power Management Specification 1.1 • Software compatible with OXmPCI954• UARTs fully software compatible with 16C550-type devices • UART operation up to 60 MHz via external clock source. Up to 20 MHz with the crystal oscillator• Baud rates up to 60 Mbps in external 1x clock mode and 15 Mbps in asynchronous mode• 128-byte deep FIFO per transmitter and receiver • Flexible clock prescaler, from 1 to 31.875• Automated in-band flow control using programmable Xon/Xoff in both directions•Automated out-of-band flow control using CTS#/RTS# and/or DSR#/DTR#• Programmable RS485 turnaround delay• Arbitrary trigger levels for receiver and transmitter FIFO interrupts and automatic in-band and out-of-band flow control• Infra-red (IrDA) receiver and transmitter operation • 9-bit data framing, as well as 5, 6, 7, and 8 bits • Detection of bad data in the receiver FIFO• Global Interrupt Status and readable FIFO levels to facilitate implementation of efficient device drivers.• Local registers to provide status/control of device functions • 11 multi-purpose I/O pins, which can be configured as input interrupt pins or ‘wake-up’• Auto-detection of a wide range of optional MICROWIRE TM compatible EEPROMs, to re-configure device parameters • Function access , to pre-configure each function prior to handover to generic device drivers • Operation via I/O or memory mapping• 3.3 V or 5 V operation (PCI Universal Voltage)• Extended operating temperature range: -40° C to 85° C •176-pin LQFP packageD ESCRIPTIONThe OXuPCI954 is a single chip solution for PCI-based serial and parallel expansion add-in cards. It is a dual function PCI device, where function 0 offers four ultra-high performance OX16C950 UARTs, and function 1 is configurable either as an 8-bit local bus or a bi-directional parallel port.Each UART channel in the OXuPCI954 is the fastest available PC-compatible UART, offering data rates up to 15 Mbps and 128-byte deep transmitter and receiver FIFOs. The deep FIFOs reduce CPU overhead and allow utilization of higher data rates. Each UART channel is software compatible with the widely used industry-standard 16C550 devices (and compatibles), as well as the OX16C95x family of high performance UARTs. In addition to increased performance and FIFO size, the UARTs also provide the full set of OX16C95x enhanced features including automated in-band flow control, readable FIFO levels, etc.To enhance device driver efficiency and reduce interrupt latency, internal UARTs have multi-port features such as shadowed FIFO fill levels, a global interrupt source register and Good-Data Status, readable in four adjacent DWORD registers visible to logical functions in I/O space and memory space.Expansion of serial ports beyond four channels is possible using the 8-bit pass-through Local Bus function. This provides a general address/data bus and interrupt capability to a discrete UART part, such as the Oxford SemiconductorOX16C954. Other controllers could be used to provide capabilities beyond additional UART ports. The addressable space provided by the Local Bus can be increased up to 256 bytes, and divided into four chip-select regions. This flexible expansion scheme caters for cards with up to 20 serial ports using external 16C950, 16C954 or compatible devices, or composite applications such as combined serial and parallel port expansion cards. Serial port cards with up to 20 ports (or with 4 serial ports and a parallel port) can be designed without redefining any device or timing parameters.The parallel port is an IEEE 1284 compliant SPP/EPP/ECP parallel port that fully supports the existing Centronics interface. The parallel port can be enabled in place of the local bus. A n external bus transceiver is required for 5V parallel port operation if device is 3.3V sourced.For full flexibility, all the default configuration register values can be overwritten using an optional M ICROWIRE compatibleserial EEPROM. This EEPROM can also be used to provide function access to pre-configure devices on the local bus/parallel port, prior to any PCI configuration accesses and before control is handed to (generic) device drivers.The OXuPCI954 can be used to replace the OXmPCI954 in a PCI application where quad UARTs and a local bus/parallel port functionality are required.OXuPCI954 DATA SHEETIntegrated High Performance Quad UARTs,8-bit Local Bus/Parallel Port,3.3 V and 5 V (Universal Voltage) PCI Interface .Improvements of the OXuPCI954 over Discrete SolutionsHigher degree of integrationThe OXuPCI954 device offers four internal 16C950 high-performance UARTs and an 8-bit local bus or abi-directional parallel port.Multi-function deviceThe OXuPCI954 is a multi-function device to enable users to load individual device drivers for the internal serial ports, drivers for the peripheral devices connected to the local bus or drivers for the internal parallel port.Quad Internal OX16C950 UARTsThe OXuPCI954 device contains four ultra-high performance UARTs, which can increase driver efficiency by using features such as the 128-byte deep transmitter and receiver FIFOs, flexible clock options, automatic flow control, programmable interrupt and flow control trigger levels and readable FIFO levels. Data rates are up to 60 Mbps.Improved access timingAccess to the internal UARTs require zero or one PCI wait state. A PCI read transaction from an internal UART can complete within five PCI clock cycles and a write transaction to an internal UART can complete within four PCI clock cycles. Reduces interrupt latencyThe OXuPCI954 device offers shadowed FIFO levels and Interrupt status registers on the internal UARTs and the MIO pins. This reduces the device driver interrupt latency. Power managementThe OXuPCI954 device complies with the PCI Power Management Specification 1.1 and the Microsoft Communications Device-class Power Management Specification 2.0 (2000). Both functions offer the extended capabilities for Power Management. This achieves significant power savings by enabling device drivers to power down the PCI functions. For function 0, this is through switching off the channel clock, in power state D3. Wake-up (PME# generation) can be requested by either functions. For function 0, this is via the RI# inputs of the UARTs in the power-state D3 or any modem line and SIN inputs of the UARTs in power-state D2. For function 1, this is via the MIO[2] input.Optional EEPROMThe OXuPCI954 device can be reconfigured from an external EEPROM to the end-user’s requirements. However, this is not required in many applications as the default values are sufficient for typical applications. An overrun detection mechanism built into the EEPROM controller prevents the PCI system from ‘hanging’ due to an incorrectly programmed EEPROM.R EVISION H ISTORYRevision Modification May 2007 First publication.Sep 2007 Feature revision, including removal of D3coldT ABLE OF C ONTENTS1OXuPCI954 Device Modes (6)2Block Diagram (7)3Pin Information—176-Pin LQFP (8)3.1Mode ‘0’ Quad UARTs + 8-bit Local Bus (8)3.1.1Mode ‘1’ : Quad UARTs + Parallel Port (9)3.2Pin Descriptions (10)4Configuration and Operation (16)5PCI Target Controller (17)5.1Operation (17)5.2Configuration Space (17)5.2.1PCI Configuration Space Register Map (18)5.3Accessing Logical Functions (20)5.3.1PCI Access to Internal UARTs (21)5.3.2PCI Access to 8-bit Local Bus (22)5.3.3PCI Access to Parallel Port (22)5.4Accessing Local Configuration Registers (23)5.4.1Local Configuration and Control Register ‘LCC’ (Offset 0x00) (23)5.4.2Multi-purpose I/O Configuration Register ‘MIC’ (Offset 0x04) (24)5.4.3Local Bus Timing Parameter Register 1 ‘LT1’ (Offset 0x08) (26)5.4.4Local Bus Timing Parameter Register 2 ‘LT2’ (Offset 0x0C) (27)5.4.5UART Receiver FIFO Levels ‘URL’ (Offset 0x10) (28)5.4.6UART Transmitter FIFO Levels ‘UTL’ (Offset 0x14) (29)5.4.7UART Interrupt Source Register ‘UIS’ (Offset 0x18) (29)5.4.8Global Interrupt Status and Control Register ‘GIS’ (Offset 0x1C) (30)5.5PCI Interrupts (31)5.6Power Management (32)5.6.1Power Management of Function 0 (32)5.6.2Power Management of Function 1 (33)5.6.3Universal Voltage (34)5.7Unique Bar Option – for Function 0 (35)6Internal OX16C950 UARTs (36)6.1Operation – Mode Selection (36)6.1.1450 Mode (36)6.1.2550 Mode (36)6.1.3Extended 550 Mode (36)6.1.4750 Mode (36)6.1.5650 Mode (36)6.1.6950 Mode (37)6.2Register Description Tables (38)6.3UART Reset Configuration (41)6.3.1Hardware Reset (41)6.3.2Software Reset (41)6.4Transmitter and Receiver FIFOs (42)6.4.1FIFO Control Register ‘FCR’ (42)6.5Line Control and Status (43)6.5.1False Start Bit Detection (43)6.5.2Line Control Register ‘LCR’ (43)6.5.3Line Status Register ‘LSR’ (44)6.6Interrupts and Sleep Mode (45)6.6.1Interrupt Enable Register ‘IER’ (45)6.6.2Interrupt Status Register ‘ISR’ (46)6.6.3Interrupt Description (46)6.6.4Sleep Mode (47)6.7Modem Interface (47)6.7.1Modem Control Register ‘MCR’ (47)6.7.2Modem Status Register ‘MSR’ (48)6.8Other Standard Registers (48)6.8.1Divisor Latch Registers ‘DLL and DLM’ (48)6.8.2Scratch Pad Register ‘SPR’ (48)6.9Automatic Flow Control (49)6.9.1Enhanced Features Register ‘EFR’ (49)6.9.2Special Character Detection (50)6.9.3Automatic In-band Flow Control (50)6.9.4Automatic Out-of-band Flow Control (50)6.10Baud Rate Generation (51)6.10.1General Operation (51)6.10.2Clock Prescaler Register ‘CPR’ (51)6.10.3Times Clock Register ‘TCR’ (51)6.10.4External 1x Clock Mode (53)6.10.5Crystal Oscillator Circuit (53)6.11Additional Features (54)6.11.1Additional Status Register ‘ASR’ (54)6.11.2FIFO Fill Levels ‘TFL and RFL’ (54)6.11.3Additional Control Register ‘ACR’ (54)6.11.4Transmitter Trigger Level ‘TTL’ (55)6.11.5Receiver Interrupt. Trigger Level ‘RTL’ (55)6.11.6Flow Control Levels ‘FCL’ and ‘FCH’ (56)6.11.7Device Identification Registers (56)6.11.8Clock Select Register ‘CKS’ (56)6.11.9Nine-bit Mode Register ‘NMR’ (57)6.11.10Modem Disable Mask ‘MDM’ (57)6.11.11Readable FCR ‘RFC’ (58)6.11.12Good-data Status Register ‘GDS’ (58)6.11.13Port Index Register ‘PIX’ (58)6.11.14Clock Alteration Register ‘CKA’ (58)6.11.15RS485 Delay Enable ‘RS485_DLYEN’ (58)6.11.16RS485 Delay Count ‘RS485_DLYCNT’ (59)7Local bus (60)7.1Overview (60)7.2Operation (60)7.3Configuration and Programming (61)8Bidirectional Parallel Port (62)8.1Operation and Mode Selection (62)8.1.1SPP Mode (62)8.1.2PS2 Mode (62)8.1.3EPP Mode (62)8.1.4ECP Mode (62)8.2Parallel Port Interrupt (63)8.3Register Description (63)8.3.1Parallel Port Data Register ‘PDR’ (64)8.3.2ECP FIFO Address / RLE (64)8.3.3Device Status Register ‘DSR’ (64)8.3.4Device Control Register ‘DCR’ (64)8.3.5EPP Address register ‘EPPA’ (65)8.3.6EPP Data Registers ‘EPPD1-4’ (65)8.3.7ECP Data FIFO (65)8.3.8Test FIFO (65)8.3.9Configuration A Register (65)8.3.10Configuration B Register (65)8.3.11Extended Control Register ‘ECR’ (65)9Serial EEPROM (66)9.1Specification (66)9.1.1Zone 0: Header (67)9.1.2Zone 1: Local Configuration Registers (68)9.1.3Zone 2: Identification Registers (69)9.1.4Zone 3: PCI Configuration Registers (69)9.1.5Zone 4: Power Management DATA (and DATA_SCALE Zone) (70)9.1.6Zone 5: Function Access (70)10Operating Conditions (72)10.1DC Electrical Characteristics (72)11AC Electrical Characteristics (76)11.1PCI Bus Timings (76)11.2Local Bus (77)11.3Serial Ports (79)12Timing Waveforms (80)13Package Information (95)13.1176-Pin LQFP (95)14Ordering Information (96)1OX U PCI954D EVICE M ODESThe OXuPCI954 supports two modes of operation. These modes are summarized in the following table.Device Mode Mode Pin Selection Functionality0 MODE = 0 Function 0 : Quad UARTs Function 1 : 8-bit local bus1 MODE = 1 Function 0 : Quad UARTs Function 1 : Parallel Port* The OXuPCI954 is not pin-compatible with the OX16PCI954 or the OXmPCI954, but is the same in all other aspects.2B LOCK D IAGRAMFIFOSELMODEAD[31:0]C/BE[3:0]#PCI_CLKFRAME#DEVSEL#IRDY#TRDY#STOP#PARPERR#IDSELRST#INTA#PME#XTLIXTLOUART_Clk_Out Local_Bus ClkEE_DIEE_CSEE_CKEE_DOSOUT[3:0]SIN[3:0]RTS[3:0]DTR[3:0]CTS[3:0]DSR[3:0]DCD[3:0]RI[3:0]MIO[10:0]PD[7:0]ACK#PEBUSYSLCTERR#SLIN#INIT#AFD#STB#LBA[7:0]LBD[7:0]LBCS[3:0]LBWR#LBRD#LBRSTDATA_DIR OXuPCI954 Block DiagramOSCDIS XTLSEL3P IN I NFORMATION—176-P IN LQFP 3.1Mode ‘0’ Quad UARTs + 8-bit Local Bus7 NC. Do not connect these pins:23, 40, 41, 136, 137, 138, 1393.1.1Mode ‘1’ : Quad UARTs + Parallel Port15 NC. Do not connect these pins:23, 40, 41, 74, 112, 113, 114, 115, 116, 117, 124, 136, 137, 138, 1393.2Pin DescriptionsFor the actual pinouts of the OXuPCI954 device (for the various modes), refer to the Section 3, Pin Information. The I/O direction key table is on page 15.PCI Interface – All ModesPin Dir1Name Description149, 150, 151, 154, 155,157, 158, 160, 164, 165,167, 168, 169, 170, 171,174, 13, 14, 15, 17, 18, 20,24, 25, 27, 28, 31, 32, 33,34, 35, 39P_I/O AD[31:0] Multiplexed PCI Address/Data bus161, 175, 12, 26 P_I C/BE[3:0]# PCI Command/Byte enable146 P_I CLK PCI system clock (33MHz)176 P_IFRAME#CycleFrame5 P_ODEVSEL#DeviceSelect1 P_IIRDY#Initiatorready2 P_OTRDY#Targetready6 P_O STOP# Target Stop request10 P_I/OPAR Parity8 P_OSERR#Systemerror7 P_I/OPERR#Parityerror163 P_I IDSEL Initialization device select144 P_I RST# PCI system reset142 P_ODINTA# PCIinterrupt147 P_OD PME# Power management eventSerial Port Pins – All ModesPin Dir1Name Description50 I FIFOSEL FIFO select. For backward compatibility with 16C550,16C650 and 16C750 devices the UARTs’ FIFO depth is 16when FIFOSEL is low. The FIFO size is increased to 128when FIFOSEL is high. The unlatched state of this pin isreadable by software. The FIFO size may also be set to 128by setting FCR[5] when LCR[7] is set, or by putting thedevice into Enhanced mode.82, 81, 63, 62 O(h)SOUT[3:0]IrDA_Out[3:0] These four pins are present in all modes but they can serve one of two functions, as follows:UART serial data outputs.UART IrDA data output when MCR[6] of the corresponding channel is set in Enhanced mode.91, 73, 72, 55I(h) I(h) SIN[3:0]IrDA_In[3:0]These four pins are present in all modes but they can serveone of two functions, as follows:UART serial data inputs.UART IrDA data input when IrDA mode is enabled (seeabove).Serial Port Pins – All ModesPin Dir1Name Description89, 76, 71, 57 I(h) DCD[3:0]# Active-low modem data-carrier-detect input 84, 79, 65, 60O(h) O(h) O(h) DTR[3:0]#485_En[3:0]Tx_Clk_Out[3:0]These four pins are present in all modes but they can serveone of three functions, as follows:Active-low modem data-terminal-ready output. If automatedDTR# flow control is enabled, the DTR# pin is asserted anddeasserted if the receiver FIFO reaches or falls below theprogrammed thresholds, respectively.In RS485 half-duplex mode, the DTR# pin may beprogrammed to reflect the state of the transmitter empty bitto automatically control the direction of the RS485transceiver buffer (see register ACR[4:3]).Transmitter 1x clock (baud rate generator output). Forisochronous applications, the 1x (or Nx) transmitter clockmay be asserted on the DTR# pins (see register CKS[5:4]).83, 80, 64, 61 O(h) RTS[3:0]# Active-low modem request-to-send output. If automatedRTS# flow control is enabled, the RTS# pin is deassertedand reasserted whenever the receiver FIFO reaches or fallsbelow the programmed thresholds, respectively.85, 78, 67, 59 I(h) CTS[3:0]# Active-low modem clear-to-send input. If automated CTS#flow control is enabled, upon deassertion of the CTS# pin,the transmitter will complete the current character and enterthe idle mode until the CTS# pin is reasserted. Note: any in-band flow control characters are transmitted regardless ofthe state of the CTS# pin.86, 77, 66, 58I(h) I(h) DSR[3:0]#Rx_Clk_In[3:0]These four pins are present in all modes but they can serveone of two functions, as follows:Active-low modem data-set-ready input. If automated DSR#flow control is enabled, upon deassertion of the DSR# pin,the transmitter will complete the current character and enterthe idle mode until the DSR# pin is reasserted. Note: any in-band flow control characters are transmitted regardless ofthe state of the DSR# pin.External receiver clock for isochronous applications. TheRx_Clk_In is selected when CKS[1:0] = ‘01’.90, 75, 70, 56 I(h)I(h) RI[3:0]#Tx_Clk_In[3:0]Active-low modem Ring-Indicator inputExternal transmitter clock. This clock can be used by thetransmitter (and indirectly by the receiver) when CKS[6]=’1’.Clock Interface Pins – All ModesPin Dir 1 Name Description49 I/OXTLOCrystal oscillator output when OSCDIS = ‘0’.External clock source input when OSCDIS = ‘1’48 I XTLI Crystal oscillator input when OSCDIS = ‘0’, up to 20MHz.N/C when OSCDIS = ‘1’45 I OSCDIS Oscillator disable.When 0, the internal crystal oscillator is enabled and a crystal needs to be attached to XTLI/XTLO.XTLSEL must be set according to the crystal frequency that is used (up to 20Mhz).When 1, the internal crystal oscillator is disabled and an external oscillator source (up to 60MHz) can be input to XTLO. XTLI is N/C and XTLSEL must be 0130 I XTLSEL Defines the frequency of the crystal attached to XTLI/XTLO(when OSCDIS = ‘0’)0 = 1 MHz – 12 MHz 1 = 12 MHz – 20 MHz8-bit Local Bus – Mode 0Pin Dir 1 Name Description 111O UART_CLK_Out Buffered crystal output. This clock can drive external UARTsconnected to the local bus. Can be enabled / disabled by software.123 O(h) LBRST Local bus active-high reset. 124 O LBRST# Local bus active-low reset. 104 O LBDOUT Local bus data out enable. This pin can be used by externaltransceivers; it is high when LBD[7:0] are in output mode and low when they are in input mode.74 O LBCLK Buffered PCI clock. Can be enabled / disabled by software. 114, 115, 116, 117 O(h) O(h) LBCS[3:0]# LBDS[3:0]# Local bus active-low Chip-Select (Intel mode).Local bus active-low Data-Strobe (Motorola mode).112 O O LBWR# LBRDWR# Local bus active-low write-strobe (Intel mode).Local bus Read-not-Write control (Motorola mode).113 O Z LBRD# Hi-Z Local bus active-low read-strobe (Intel mode).Permanent high impedance (Motorola mode).105, 106, 108, 109 118, 119, 120, 122 O(h) LBA[7:0] Local bus address signals. 96, 97, 98, 99 100, 101, 102, 103I/O(h) LBD[7:0] Local bus data signals.Parallel Port – Mode 1Pin Dir 1 NameDescription123 I(h) I(h) ACK#INTR#Acknowledge (SPP mode). ACK# is asserted (low) by the peripheral to indicate that a successful data transfer has taken place.Identical function to ACK# (EPP mode).122 I(h) PEPaper Empty. Activated by printer when it runs out of paper. 120 I(h) I(h) BUSYWAIT#Busy (SPP mode). BUSY is asserted (high) by the peripheral when it is not ready to accept data.Wait (EPP mode). Handshake signal for interlocked IEEE 1284 compliant EPP cycles.109 OD(h) O(h) SLIN#ADDRSTB#Select (SPP mode). Asserted by host to select the peripheral.Address strobe (EPP mode) provides address read and write strobe.119 I(h) SLCT Peripheral selected. Asserted by peripheral when selected. 118 I(h) ERR#Error. Held low by the peripheral during an error condition. 108 OD(h) O(h) INIT#INIT#Initialize (SPP mode). Commands the peripheral to initialize.Initialize (EPP mode). Identical function to SPP mode. 106 OD(h) O(h) AFD#DATASTB# Auto Feed (SPP mode, open-drain).Data strobe (EPP mode) provides data read and write strobe.105 OD(h) O(h) STB#WRITE#Strobe (SPP mode). Used by peripheral to latch data currently available on PD[7:0].Write (EPP mode). Indicates a write cycle when low and a read cycle when high . 96, 97, 98, 99, 100, 101, 102, 103I/O(h) PD[7:0] Parallel data bus.104OPDOUTParallel port data out enable. This pin should be used by external transceivers for 5 V signaling; it is high when PD[7:0] are in output mode and low when they are in input mode.Multi-purpose and External Interrupt Pins – All ModesPin Dir1Name DescriptionMODE0 1135 --135I/O(h)OMIO0NCMulti-purpose I/O 0. Can drive high or low, or assert a PCIinterrupt.Output Driving ‘0’. Can be left as a No-connect.134 134 134134I/O(h)MIO1NCMulti-purpose I/O 1. Can drive high or low, or assert a PCIinterrupt (as long as LCC[6:5] = “00”).Output Driving ‘0’ (when LCC[6:5] ≠ ‘00’)Can be left as a No-Connect.133 133 133133I/O(h)IMIO2PME_InMulti-purpose I/O 2. When LCC[7] = 0, this pin can drive highor low, or assert a PCI interrupt.Input power management event. When LCC[7] is set thisinput pin can assert a function 1 PME#.93, 94, 95, 125, 126, 127, 128, 132 I/O(h) MIO[10:3] Multi-purpose I/O pins. Can drive high or low, or assert a PCIinterrupt.EEPROM Pins – All ModesPin Dir1Name Description53 OEE_CKEEPROMclock.52 O EE_CS EEPROM active-high Chip Select.54 IU(h) EE_DI EEPROM data in, with internal pull-up.When the serial EEPROM is connected, this pin should bepulled up using a 1-10k resistor. When the EEPROM is notused the internal pull-up is sufficient.Pin to be connected to the external EEPROM’s EE_DO pin(if used).51 O EE_DO EEPROM data out.Pin to be connected to the external EEPROM’s EE_DI pin(if used).Table 1: Pin DescriptionsI/O Direction Key P_I PCI input 3.3 V Only P_O PCI output / PCITristates 3.3 V Only P_I/O PCI bi-directional 3.3 V Only P_OD PCI open drain 3.3 V OnlyI Input LVTTL level I(h) Input LVTTL level, 5 V tolerant IU(h) Input with internal pull-up LVTTL level, 5 V tolerant I/O(h) Bi-Directional LVTTL level, 5 V tolerantO Output Standard Output O(h) Output 5 V tolerant (High Voltage BI-Direct in output mode) OD Open drain Standard Open-drain Output OD(h) Open drain 5 V tolerant (High Voltage BI-Direct in open-drain mode) NC No connectG Ground V VoltageMiscellaneous PinsPin Dir 1 NameDescription44 IMODEMode selector Pin0 : Function 0 : Quad UART. Function 1 : 8-bit local bus.1 : Function 0 : Quad UART. Function 1 : Parallel port.Power and GroundPinType Name Description19, 42, 47, 69, 88, 107, 131, 148VVDDPower Supply (3.3 V)11, 22, 36, 140, 156, 162, 173 V VIOPCI I/O Universal VoltageDefines the (clamping) voltage of the PCI I/O Buffers.To be connected to the VIO pin of the PCI connector. 3, 4, 9, 16, 21, 29, 30, 37, 38, 43, 46, 68, 87, 92, 110, 121, 129, 141, 143, 145, 152, 153, 159, 166, 172G GNDPower Supply Ground (0 V)4C ONFIGURATION AND O PERATIONThe OXuPCI954 is a multi-function, target-only PCI device, compliant with the PCI Local Bus Specification, Revision 3.0 and the PCI Power Management Specification, Revision 1.1.The OXuPCI954 affords maximum configuration flexibility by treating the internal UARTs, the local bus and the parallel port as separate logical functions. Each function has its own configuration space and is therefore recognized and configured by the PCI BIOS separately. The functions used are configured by the Mode Selection Pin as shown in Section 1 OXuPCI954 Device Modes.The OXuPCI954 is configured by system start-up software during the bootstrap process that follows bus reset. The system scans the bus and reads the vendor and device identification codes from any devices it finds. It then loads device-driver software according to this information and configures the I/O, memory and interrupt resources. Device drivers can then access the functions at the assigned addresses in the usual fashion, with the improved data throughput provided by PCI.Each function operates as though it was a separate device. However there are a set of Local Configuration Registers that can be used to enable signals and interrupts, configure timings, and improve the efficiency of multi-port drivers. This architecture enables separate drivers to be installed for each function. Generic port drivers can be hooked to use the functions individually, or more efficient multi-port drivers can hook both functions, accessing the Local Configuration Registers from either.All registers default after reset to suitable values for typical applications such a 4/8 port serial, or combo 4-port serial/1-port parallel add-in cards. However, all identification, control and timing registers can be redefined using an optional serial EEPROM.5PCI T ARGET C ONTROLLER5.1OperationThe OXuPCI954 responds to the following PCI transactions:-•Configuration access: The OXuPCI954 responds to type 0 configuration reads and writes if the IDSELsignal is asserted and the bus address is selecting theconfiguration registers for function 0 or 1. The devicewill respond to the configuration transaction by asserting DEVSEL#. Data transfer then follows. Anyother configuration transaction will be ignored by theOXuPCI954.•I/O reads/writes: The address is compared with the addresses reserved in the I/O Base Address Registers(BARs). If the address falls within one of the assignedranges, the device will respond to the I/O transactionby asserting DEVSEL#. Data transfer follows thisaddress phase. For the UARTs and 8-bit local buscontroller, only byte accesses are possible. For I/Oaccesses to these regions, the controller comparesAD[1:0] with the byte-enable signals as defined in thePCI specification. The access is always completed;however if the correct BE signal is not present thetransaction will have no effect.•Memory reads/writes: These are treated in the same way as I/O transactions, except that the memoryranges are used. Memory access to single-byte regions is always expanded to DWORDs in theOXuPCI954. In other words, OXuPCI954 reserves aDWORD per byte in single-byte regions. The deviceallows the user to define the active byte lane usingLCC[4:3] so that in Big-Endian systems the hardwarecan swap the byte lane automatically. For Memorymapped access in single-byte regions, the OXuPCI954 compares the asserted byte-enable withthe selected byte-lane in LCC[4:3] and completes theoperation if a match occurs, otherwise the access willcomplete normally on the PCI bus, but it will have noeffect on either the internal UARTs or the local buscontroller.•All other cycles (64-bit, special cycles, reserved encoding etc.) are ignored.The OXuPCI954 will complete all transactions as disconnect-with-data, i.e. the device will assert the STOP# signal alongside TRDY#, to ensure that the Bus Master does not continue with a burst access. The exception to this is Retry, which will be signaled in response to any access while the OXuPCI954 is reading from the serial EEPROM.The OXuPCI954 performs medium-speed address decoding as defined by the PCI specification. It asserts the DEVSEL# bus signal two clocks after FRAME# is first sampled low on all bus transaction frames which address the chip. The internal UARTs are accessed with zero wait states inserted. Fast back-to-back transactions are supported by the OXuPCI954 as a target, so a bus master can perform faster sequences of write transactions to the UARTs or local bus when an inter-frame turn-around cycle is not required.The device supports any combination of byte-enables to the PCI Configuration Registers and the Local Configuration Registers. If a byte-enable is not asserted, that byte is unaffected by a write operation and undefined data is returned upon a read.The OXuPCI954 performs parity generation and checking on all PCI bus transactions as defined by the standard. Note this is entirely unrelated to serial data parity which is handled within the UART functional modules themselves. If a parity error occurs during the PCI bus address phase, the device will report the error in the standard way by asserting the SERR# bus signal. However if that address/command combination is decoded as a valid access, it will still complete the transaction as though the parity check was correct.The OXuPCI954 does not support any kind of caching or data buffering in addition to that already provided within the UARTs by the transmit and receive data FIFOs. In general, registers in the UARTs and on the local bus can not be pre-fetched because there may be side-effects on read.5.2Configuration SpaceThe OXuPCI954 is a dual-function device, where each logical function has its own configuration space. All required fields in the standard header are implemented, plus the Power Management Extended Capability register set. The format of the configuration space is shown in the following tables.In general, writes to any registers that are not implemented are ignored, and all reads from unimplemented registers return 0.。

XilinxFPGA的嵌入式系统开发过程

Xilinx FPGA的嵌入式系统开发过程由创新网小编于星期四, 01/10/2013 - 11:03 发表随着FPGA 技术的迅速发展,可编程片上系统(SOPC)作为一种特殊的嵌入式微处理器系统,融合了SoC和FPGA 各自的优点,并具备软硬件在系统可编程、可裁减、可扩充、可升级的功能,已逐渐成为一个新兴的技术方向。

SOPC的核心是在FPGA上实现的嵌入式微处理器核,目前主要有Xilinx公司集成的32位软核MicroBlaze[1] ,32位PowerPC系列处理器硬核PowerPC405、PowerPC440,ARM公司的CortexA9,以及Altera公司的Nios系列微处理器软核等。

本文主要介绍Xilinx公司的MicroBlaze 软核结构,对其体系结构、设计流程和相关开发工具一一进行介绍,并在实际的无线电监测系统[2]中采用此方案,构建了一个小型化、智能化、网络化的软件无线电处理平台。

1 MicroBlaze处理器结构MicroBlaze软核处理器是可配置的精简指令集(RISC)32位CPU,该RISC核针对Xilinx公司的FPGA芯片进行了优化。

设计人员可以根据设计定制处理器的可选配置,根据版本的不同,配置不同的选项。

该软核处理器具有以下几个方面的特征:◆32个32位通用寄存器;◆32位3个操作数的指令字,指令字有2种寻址模式;◆分离的32位地址总线和数据总线;◆具有高速的指令和数据缓存,3级和5级流水线操作;◆灵活的总线结构,支持LMB、OPB、PLB、XCL、FSL片上总线接口等,新推出的系列还支持AXI总线接口;◆支持MMU存储管理、FPU浮点单元、高速缓存、异常处理和调试逻辑等可根据性能需求和逻辑区域成本任意裁减的高级特性。

MicroBlaze的这些特性极大地扩展了其应用范围,MicroBlaze处理器的内核仍在不断更新之中,目前使用的版本MicroBlaze v7.1,其内部架构如图1所示。

XILINX ISE 14.5设计教程

点击“按钮”,直到出现窗口波形

仿真波形窗口

基于VHDL语言的ISE设计流程

--对该设计进行行为仿真

可以在控制台窗口,输入命令控制仿真的运行

输入run 1ms, 控制仿真运行时间到1ms

关闭整个仿真窗口,继续下面的设计, 为了将来在硬件上看到灯的变化所反映 的计数器的工作状态,需要在top.vhd设计文件,添加分频时钟部分代码,

FPGA硅片布局

基于VHDL语言的ISE设计流程

--查看布局布线后结果

CLB

连线

Slice 双击,展 开Slice

基于VHDL语言的ISE设计流程

--查看布局布线后结果

关闭FPGA Editor界面

基于VHDL语言的ISE设计流程

--下载设计到FPGA芯片

准备工作:

• 将HEP的USB-JTAG电缆分别和计算机USB接口及EXCD-1目标

点击“Next”按钮

基于VHDL语言的ISE设计流程

--创建一个新的设计文件

添加代码到top.vhd文件中

生成的top.vhd文件

基于VHDL语言的ISE设计流程

--创建一个新的设计文件

此处添加两条库调用语句

基于VHDL语言的ISE设计流程

--创建一个新的设计文件

此处添加端口声明语句

基于VHDL语言的ISE设计流程

基于VHDL语言的ISE设计流程

--对该设计继续添加代码

选中Implementation

选中top.vhd, 并点击打开该文件 ,准备添加代码

基于VHDL语言的ISE设计流程

--对该设计继续添加代码

添加内部信号量声明部分

添加分频时钟映射部分

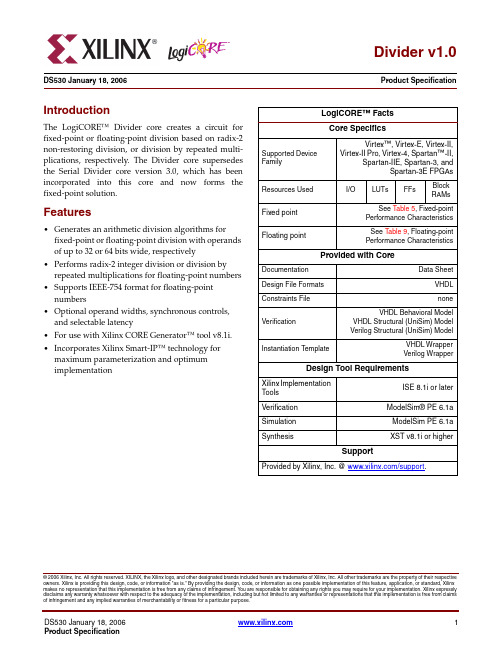

Xilinx ISE自带的除法器IP核数据手册

© 2006 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners. Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. Y ou are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claimsof infringement and any implied warranties of merchantability or fitness for a particular purpose.IntroductionThe LogiCORE™ Divider core creates a circuit for fixed-point or floating-point division based on radix-2non-restoring division, or division by repeated multi-plications, respectively. The Divider core supersedes the Serial Divider core version 3.0, which has been incorporated into this core and now forms the fixed-point solution.Features•Generates an arithmetic division algorithms for fixed-point or floating-point division with operands of up to 32 or 64 bits wide, respectively •Performs radix-2 integer division or division by repeated multiplications for floating-point numbers •Supports IEEE-754 format for floating-point numbers •Optional operand widths, synchronous controls, and selectable latency •For use with Xilinx CORE Generator™ tool v8.1i. •Incorporates Xilinx Smart-IP™ technology for maximum parameterization and optimum implementationDivider v1.0DS530 January 18, 2006Product SpecificationLogiCORE™ Facts Core SpecificsSupported Device FamilyVirtex™, Virtex-E, Virtex-II,Virtex-II Pro, Virtex-4, Spartan™-II,Spartan-IIE, Spartan-3, andSpartan-3E FPGAsResources UsedI/OLUTsFFsBlock RAMsFixed point See Table 5,Fixed-point Performance Characteristics Floating pointSee T able 9,Floating-point Performance CharacteristicsProvided with CoreDocumentation Data SheetDesign File Formats VHDL Constraints File noneVerificationVHDL Behavioral ModelVHDL Structural (UniSim)Model Verilog Structural (UniSim)ModelInstantiation TemplateVHDL Wrapper Verilog WrapperDesign Tool RequirementsXilinx Implementation Tools ISE 8.1i or later Verification ModelSim®PE 6.1a Simulation ModelSim PE 6.1a SynthesisXST v8.1i or higherSupportProvided by Xilinx, Inc. @ /support .OverviewThe Divider core selects an implementation depending on the algorithm_type parameter. Currently,the following two division implementations are supported:•Fixed-point. Radix-2, non-restoring integer division using fixed-point operands, allowing a remainder to be generated.•Floating-point. Division by repeated multiplications. Works on normalized operands; in effect, a floating-point implementation.A detailed explanation of each implementation is provided in a later section of this data sheet.ApplicationsDivision is the most complex of the four basic arithmetic operations. Because hardware solutions arecorrespondingly larger and more complex than the solutions for the other operations, it is best to min-imize the number of divisions in any algorithm. There are many forms of division implementation,which can be separated into two broad categories: fixed-point algorithms and floating-point algo-rithms. This core provides one example of each category.The radix-2 non-restoring algorithm solves one bit of the quotient per cycle using addition and subtrac-tion. For this reason, it can achieve very high clock speeds at the expense of relatively high latency.However, the design is fully pipelined, so can achieve a throughput of one division per clock cycle. Theresulting circuit is relatively large, however, so if the throughput is smaller, the divisions per clockparameter allows compromises of throughput and resource use. This algorithm naturally generates aremainder, so is the choice for applications requiring remainders or modulus results.The repeated multiplications algorithm is an iterative method using successive approximations to thereciprocal of the denominator. The number of bits of the quotient solved doubles per iteration, so thisalgorithm is well suited to applications requiring precise results. Also, because this core makes use ofembedded multipliers, the overall resource use is less than that for the radix-2 algorithm. Again, thedesign is fully pipelined to allow a throughput of one division per clock cycle. This algorithm does notnaturally yield a remainder.2DS530 January 18, 2006Generic XCO and VHDL ParametersThe descriptions below refer to generic VHDL parameters. Table2 defines the parameters, legal values,and meaning of the XCO parameters and VHDL generics, which are broadly equivalent.•c_family (string) and c_xdevicefamily (string): Together, these generics identify the specific FPGA device family the core is targeting. Table1 the values for each of the supported families.T able 1: Relationship between Target FPGA Family, c_family and c_xdevicefamilyTarget FPGA Family c_family c_xdevicefamily Virtex/Virtex-E"virtex""virtex"Spartan-II/Spartan-II E"virtex""spartan2"Virtex-II"virtex2""virtex2"Virtex-II Pro"virtex2p""virtex2p"Spartan-3"spartan3""spartan3"Spartan-3E"spartan3""spartan3e"Virtex-4"virtex4""virtex4"•algorithm_type (integer): Specifies the division algorithm to use. The choice is 1 for radix-2(fixed-point notation) or 2 for division by repeated multiplications (floating-point notation).•signed_b (integer): 0 for unsigned operands, 1 for signed (2’s complement) operands. Applies to fixed-point notation only.•fractional_b (integer): 0 (no remainder) or 1 (has remainder). Applies to fixed-point only.•dividend_width (integer): 2 to 32 (fixed). Specifies the width of both dividend and quotient.•fractional_width (integer): 2 to 32 (fixed-point only).•c_has_ce (integer): 0 (no ce), or 1 (has ce).•c_has_aclr (integer): 0 (no ce), or 1 (has ce).•c_has_sclr (integer): 0 (no ce), or 1 (has ce).•divclk_sel (integer): 1, 2, 4, or 8. Specifies the number of clocks between division results for the fixed-point case only. A higher number results in lower-circuit area at the cost of lower throughput.•latency (integer): 1 to 99(float only). Specifies the circuit latency in terms of enabled clock (ce) cycles.•divisor_width (integer):2 to 32 (fixed)•bias (integer): Specifies the bias on the exponent, according to IEEE-754 format. A value of -1 results in a bias value in the mid-point of the exponent range.•mantissa_width (integer): 2 to 64. Specifies the width of the mantissae of all operands (floating-point only).•exponent_width (integer): 2 to 16. Specifies the width of the exponents of all operands (floating-point only).4DS530 January 18, 2006T able 2: Common Generic Parameters XCO ParameterXCO ValuesGeneric VHDL Parameter Generic ValuesDescriptionCommon GenericsAlgorithm T ype Fixed, Float algorithm_type (1),21 = fixed-point division (radix-2)2 = floating-point division CE false, true c_has_ce (0),10 = no CE 1 = has CE ACLR false, true c_has_aclr (0),10 = no ACLR 1 = has ACLR SCLRfalse, true c_has_sclr(0),10 = no SCLR 1 = has SCLRSCLR/CE Priority SCLR_overrides _CE, CE_overrides_SCLRc_sync_enable (0),10 = SCLR overrides CE 1 = CE overrides SCLRSerial-divider Generics (Fixed-point)Dividend and Quotient width 2 to 32 (16)dividend_width 2 to 32(16)Width of dividend and quotient (fixed only)Divisor width 2 to 32 (16)divisor_width 2 to 32 (16)Width of divisor (fixed only)Remainder type remainder, fractional fractional_b 0,10 = remainder,1 = fractional Fractional width 2 to 32 (16)fractional_width 2 to 32 (16)Width of fraction (fractional only)Operand signunsigned, signedsigned_b0,10 = unsigned 1 = signedClocks per division 1,2,4,8divclk_sel (1),2,4,8Throughput (interval between input opportunities)Low-latency Generics (Floating-point)Mantissa width 2 to 64mantissa_width 2 to 64 (16)Width of mantissa Exponent width2 to 16exponent_width2 to 16 (8)Width of exponent Latency 1 to 99latency 1 to 99(1)Latency of division Bias-1 to 2^Exponent_width -1bias-1 to 2^exponent_width -1Exponent biasFeature Summary Fixed-point Solution•Divides dividend by divisor to provide the quotient with integer or fractional remainder •Pipelined architecture for increased throughput •Pipeline reduction for size versus throughput selections •Dividend width from 1 to 32 bits •Divisor width from 3 to 32 bits•Fractional remainder width from 3 to 32 bits•Independent dividend, divisor and fractional bit widths •Fully synchronous design using a single clock•Supports unsigned or two’s complement signed numbers •Can implement 1/X (reciprocal) function •Fully registered outputsOverview Fixed-point SolutionThis parameterized module divides an M-bit-wide variable dividend by an N-bit-wide variable divi-sor. The output consists of the quotient and either the integer remainder or the fractional result (quo-tient continued past the binary point). In the integer remainder case, the result of the division is an M-bit-wide quotient with an N-bit-wide integer remainder (Equation 1). In the fractional case, the result is an M-bit-wide quotient with an F-bit-wide fractional remainder (Equation 2). When both frac-tional and signed are selected, the top bit of the fractional result is a two’s complement sign bit, result-ing in one less bit of magnitude result (Equation 3). It is an efficient, high-speed, parallel implementation. The core can be configured for unsigned or signed data.Equation 1: Integer remainder case.Equation 2: F-bit-wide fractional remainder in the unsigned caseEquation 3: F-bit-wide fractional remainder in the signed caseNote that for signed mode with integer remainder, the sign of the quotient and remainder correspond exactly to Equation 1.Dividend = quotient * divisor + remainderFractRmd=IntRmd *2FDivisorFractRmd=IntRmd *2( F-1)DivisorThus6/-4 = -1 REMD 2whereas-6/4 = -1 REMD –2For signed mode with fractional remainder, the sign bit is present both in the quotient and the remain-der. For example, for a four-bit dividend, divisor and fractional remainder we have:-9/4 = 9/-4 = -(2 1/4)This corresponds to:(1)0111 / 0100 or 1001/1100Giving the result:Quotient = 1110 (= -2)Remainder = 1110 (= -1/4)For division by zero, the quotient, remainder, and fractional results are undefined.The design is highly pipelined. The amount of pipelining can be reduced to decrease the area of thedesign at the expense of throughput. In the fully pipelined mode the design outputs the result of onedivision operation per clock cycle after an initial latency. The design also supports the options of 2, 4,and 8 clock cycles per division after an initial latency, as shown in Table4.The dividend and divisor bit widths can be set independently. The bit width of the quotient is equal tothe bit width of the dividend. The bit width of the integer remainder is equal to the width of the divisor.For fractional output, the remainder bit width is also independent of the dividend and divisor. The corewill handle data ranges of 3 to 32 bits for the dividend, divisor and fractional output.The divider can be used to implement the 1/X function; that is, the reciprocal of the variable X. To dothis, the dividend bit width is set to 1 for unsigned or 2 for signed data and fractional mode is selected.The dividend input is tied high within the user’s design.6DS530 January 18, 2006Pinout of Fixed-point SolutionThe fixed-point core pinout and signal names are shown in Figure 1 and defined in Table 3.Figure 1: Core Pinout DiagramTable 3: Fixed-point Signal PinoutSignalDirectionDescriptionDIVIDEND[Dividend Width-1:0]Input Dividend (parallel data in). Data bit width determined by the Dividend width generic or XCO parameter.DIVISOR[Divisor Width -1:0]InputDivisor (parallel data in). Data bit width determined by the Divisor width generic or XCO parameter.CLK InputClock . With the exception of ACLR, control and data inputs are captured and new output data formed on rising clock transitions.ACLRInput (optional)Asynchronous Clear (ACLR). Optional input pin. All control signals are synchronous to the rising edge of CLK except ACLR. When ACLR is asserted (High), all the core flip-flops are asynchronously initialized. The core remain in this state until ACLR is negated.SCLRInput (optional)Synchronous Clear (SCLR). Optional input pin. When asserted (high), all the core flip-flops are synchronously initialized (synchronous to the clock). The core remains in this state until SCLR is deasserted. When both SCLR and CE exist, the sync_enable parameter determines whether SCLR is qualified by CE or whether SCLR overrides CE (that is, will clear the module on the clock edge even if CE is deasserted).CEInput (optional)Clock Enable (CE). Optional input pin. When deasserted (low), all the synchronous inputs are ignored and the core remains in its current state.8DS530 January 18, 2006Following a power-on reset, SCLR , or ACLR , the outputs QUOTIENT and REMAINDER output all zeroes until new results appear.Waveforms of Fixed-point SolutionThe total latency (number of clocks required to get the first output) is a function of the bit width of the dividend. If fractional output is required, the latency is also a function of the fractional bit width. If clock enable is selected, latency is in terms of enabled clock cycles.When ‘clocks per division’ is set to 2, 4, or 8, the RFD output indicates the cycle in which input data is sampled (Figure 2), and therefore from when latency is measured. Ready for data should be qualified by clock enable if used externally.In general:Latency is of the order M for integer remainder dividers Latency is of the order M + F for fractional remainder dividersRFDOutputReady for Data (RFD). An output that indicates the cycle in which input data is sampled by the core. This is only applicable to cores where divclk_sel is not 1. For the case of divclk_sel = 1 the core is fully pipelined and samples the inputs on every enabled clock rising edge; hence, RFD will always be high.When divclk_sel = 2, 4 or 8, the core only samples data on every 2nd, 4th or 8th enabled clock rising edge respectively. The cycle on which data is sampled isimportant for the definition of latency, as shown in figure3. RFD will only change on enabled (CE input) clock rising edges for a core that has CE input (has_ce = True).QUOTIENT[Dividend width-1:0]OutputQuotient . The result of the integer division of dividend by divisor (dividend DIV divisor). The bit width of the quotient is equal to the dividend. For signed operation, the quotient is in two’s complement form. Parallel data out. Data bit width determined by the dividend width generic or XCO parameter.REMAINDER[n:0]REMAINDER[f:0]OutputRemainder . The integer remainder of the integer division of dividend by divisor (dividend MOD divisor) when the core is not fractional. For a fractional core, this output is the fractional part of the division result.For either case, if the core is signed, the output is in two’s complement form.• Integer Remainder. Result data bit width determined by divisor width generic or XCO parameter.• Fractional Remainder. Result data bit width determined by Fractional Width generic or XCO parameter.Table 3: Fixed-point Signal Pinout (Continued)SignalDirectionDescriptionTable 4 provides a list of the latency formula for divider selections and Figure 2 illustrates how latency is defined. Latency is expressed in clock cycles for dividers with no clock enable input and otherwise in enabled clock cycles.The divclk_sel parameter allows a range of choices of throughput versus area. With divclk_sel = 1, the core is fully pipelined, so it will have maximal throughput of one division per clock cycle, but will occupy the most area. The divclk_sel selections of 2, 4 and 8 reduce the throughput by those respective factors for smaller core sizes.Figure 2: Latency Example (Clocks per Division = 4)T able 4: Latency of Fixed-point Solution Based on Divider ParametersSignedFractionalClks/DivLatencyFalse False 1M+2False False >1M+3False True 1M+F+2False True >1M+F+3True False 1M+4True False >1M+5True True 1M+F+4TrueTrue>1M+F+5Note: M=dividend width, F=fractional remainder width.clk dividend divisorrfd quot remda ba divb a rem blatencyce c div d c rem dc de f10DS530 January 18, 2006Performance Characteristics of Fixed-point SolutionTable 5 defines performance characteristics for cases run on a Virtex-4, speed grade 10 device, and are intended to provide an indication of resources used and achievable clock speed. Generics not specified are at their default values.T able 5: Fixed-point Performance CharacteristicsDivisor WidthDividend WidthDivclk_selSlices usedSpeed (MHz)DSP48s usedBlock Memories881129385008821002850088475322008886233000323211666203Feature Summary Floating-point Solution•Performs division by repeated multiplications for floating-point numbers•Supports IEEE-754 format for floating-point numbers•Optional operand widths, synchronous controls, selectable latencyOverview Floating-point SolutionThe floating-point implementation performs division by repeated multiplications. The design is fully pipelined for maximal throughput. The two operands, divisor and dividend, are entered in sign-man-tissa-exponent form. A single sign bit per operand determines the sign of the mantissa. The mantissa width is configurable, as is the exponent width. The bias of the exponent is also configurable. Following IEEE754, certain combinations of exponent and mantissa are interpreted as zero, infinity and NaN (not a number). The result is expressed in the same form as the inputs. Overflow and underflow outputs are given for those results whose magnitudes lie above or below (respectively) the range which can be expressed with the specified mantissa and exponent widths.The format of number representation follows IEEE754. The mantissas, both on input and output have an implicit leading ’1.’ The mantissa describes a number in the range 0.5(inclusive) to 1.0(not inclusive). For example, the number 0.75 is 0.11000... in binary. The mantissa to describe this would be 10000... (to the specified width). The leading 1 indicates the number is in the range 0.5 to just less than 1.0. Since the number representation requires this normalization the leading 1 is not required as an input since it car-ries no information.The underflow and overflow outputs are provided to show if the result of a calculation resulted in and exponent outside the range allowed by the width of the exponent, that is, <0 or >2^exponent_width. Table6 defines special values recognized by the core.T able 6: Special ValuesExponent Mantissa Special ValueAll ’1’s Not all ’0’s Not a Number (NaN)All ’1’s All ’0’s InfinityAll ’0’s All ’0’s ZeroTable7 defines division results involving any of the special values described in Table6.T able 7: Division Results Involving Special ValuesDividend Divisor QuotientNaN Any Value NaNAny Value NaN NaNInfinity Infinity NaNZero Zero NaNAny value Infinity Zero12DS530 January 18, 2006Pinout of Floating-point SolutionThe floating-point core pinout and signal names are displayed in Figure 3 and defined in Table 8.Any Value Zero Infinity Zero Any Value Zero InfinityAny ValueInfinityFigure 3: Floating-point Schematic SymbolTable 8: Pinout of Floating-point SolutionSignalDirectionDescriptionCLK Input Clock. Rising edge clock signal CE Input (optional)Clock Enable ACLR Input (optional)Asynchronous Clear SCLRInput (optional)Synchronous Clear DIVIDEND _MANTISSA [Mantissa Width-1:0]Input Dividend mantissa DIVISOR _MANTISSA [Mantissa Width-1:0]Input Divisor mantissaDIVISOR_SIGNInputSign of Divisor mantissa (0 for +ve, 1 for -ve)T able 7: Division Results Involving Special Values (Continued)DividendDivisorQuotientWaveforms of Floating-point SolutionThe functional timing characteristics of the floating-point solution are very simple. Because the design has a throughput of one division per clock cycle, no handshaking signals (Ready for Data, New Data,output Ready) are required. Latency is selectable and is defined in the same manner as for the fixed-point solution. For this reason, outputs occur following the n th enabled rising clock edge after the inputs, where n is the latency value.Performance Characteristics of Floating-point SolutionTable 9 defines performance characteristics for cases run on a Virtex-4, speed grade 10 device and are intended to provide an indication of resources used and achievable clock speed. Generics not specified are at their default values.Note that when the core does not have asynchronous clear nor synchronous clear, use can be made of SRL16 primitives, leading to a substantial reduction in circuit size. For this reason, the use of SCLR or ACLR is not recommended.DIVIDEND_SIGNInput Sign of Dividend mantissa (0 for +ve, 1 for -ve)DIVISOR _EXPONENT [Exponent Width-1:0]Input Exponent of Divisor DIVIDEND _EXPONENT [Exponent Width-1:0]Input Exponent of Dividend QUOTIENT _MANTISSA [Mantissa Width-1:0]Output Quotient mantissa QUOTIENT_SIGNOutput Sign of Quotient QUOTIENT _EXPONENT [Exponent Width-1:0]Output Exponent of Quotient OVERFLOW Output Float overflow indication UNDERFLOWOutputFloat underflow indicationNoteAll control inputs are Active High. If an Active Low input is required for a particular control pin, an inverter must be placed in the path to the pin. The inverter will be absorbed appropriately during synthesis and/or mapping.T able 9: Floating-point Performance CharacteristicsMantissa WidthExponent WidthLatencySlices usedSpeed (MHz)DSP48s usedBlock Memories1581842510115810231941011583027227610124826(no SCLR)399283101Table 8: Pinout of Floating-point Solution (Continued)SignalDirectionDescription14DS530 January 18, 2006Generating the CoreThe Divider core can be included in your design in two ways: Using the CORE Generator graphical user interface (GUI), or using direct instantiation.Method 1: GUIThe CORE Generator system produces several files when a core is generated. Instructions about how to instantiate a core using this method are automatically produced in the .vho file. An example of a section of a .vho file is provided below:-- The following code must appear in the VHDL architecture header:------------- Begin Cut here for COMPONENT Declaration ------ COMP_TAG component div_gen_v1_0 port (clk: IN std_logic;...(other ports));end component;-- COMP_TAG_END ------ End COMPONENT Declaration -- The following code must appear in the VHDL architecture -- body. Substitute your own instance name and net names.------------- Begin Cut here for INSTANTIATION Template ----- INST_TAG your_instance_name : div_gen_v1_0 port map ( clk => clk, q => q);-- INST_TAG_END ------ End INSTANTIATION Template -- You must compile the wrapper file counter.vhd when simulating24826(with SCLR)720310101428157388821142845937211211T able 9: Floating-point Performance Characteristics (Continued)Mantissa WidthExponent WidthLatencySlices usedSpeed (MHz)DSP48s usedBlock Memories-- the core, counter. When compiling the wrapper file, be-- sure to reference the XilinxCoreLib VHDL simulation-- library. For detailed-- instructions, please see the CORE Generator User Guide.Method 2: Direct InstantiationThe CORE Generator now allows cores to be directly instantiated into user code. To do this, add the fol-lowing lines to the head of your VHDL file:Library Xilinxcorelib;Use Xilinxcorelib.div_gen_v1_0_comp.all;and instantiate the Divider core with appropriate values for the generics and your local signals:i_instance: div_gen_v1_0generic map(c_dividend_width => 16,c_has_ce => 1etc.);port map(clk => clk ,sclr => sclr ,quotient => output);Note that generics do not need to be specified if the default value suits your application.CORE Generator Parameter ScreensThe Divider core GUI provides three screens for selecting core parameters.•Main screen. Describes parameters common to both implementations, such as SCLR and CE, and allows the selection of the divider implementation.•Fixed-point implementation options. Provides configuration options for the fixed-point divider configuration. Note that this screen is displayed only if Fixed-point is selected on the main screen. •Floating-point implementation options. Provides configuration options for the floating-point divider configuration. Note that this screen is displayed only if Floating-point is selected on the main screen.16DS530 January 18, 2006Main Screen•Component Name. The base name of the output files generated for the core. Names must begin with a letter and be composed of any of the following characters: a to z, 0 to 9 and “_”.Figure 4: Main ScreenFixed-point Implementation OptionsFloating-point Implementation OptionsFigure 5: Fixed-point Implementation OptionsFigure 6: Floating-Point Implementation OptionsVerificationThe Divider core is supplied with a VHDL functional behavioral model, and the CORE Generator canalso produce a UniSim-based Verilog model if desired.SimulationWhen the Divider core is generated using the CORE Generator, a VHDL functional behavioral model is alsogenerated. The VHDL behavioral model is a pre-defined, parameterized model of the core, which is copiedto the project directory. A Verilog wrapper is also provided for the VHDL model for mixed-language simu-lation. If a Verilog model is selected, the CORE Generator produces a UniSim-based model of the core.Important Note: The VHDL Behavioral model provided for the floating-point solution does not exactlyreproduce the behavior of the synthesized core. The models quotients may differ by the least significant bitof the mantissa. For an exact match, the structural (UniSim) behavioral model must be used.References"Computer Arithmetic Algorithms and Hardware Designs," Behrooz Parhami. Oxford Press © 2000.LicensingThe Divider core does not require a license.Ordering InformationThis core may be downloaded from the Xilinx IP Center for use with the Xilinx CORE Generator systemv8.1i and higher. The Xilinx CORE Generator system is bundled with the ISE Foundation software at noadditional charge. To inquire about other Xilinx products, contact your local Xilinx sales representative.SupportXilinx provides technical support for this LogiCORE product when used as described in the productdocumentation. Xilinx cannot guarantee timing, functionality, or support of product if implemented indevices not listed in the documentation, or if customized beyond that allowed in the productdocumentation, or if any changes are made in sections of design marked as DO NOT MODIFY.Related InformationXilinx products are not intended for use in life-support appliances, devices, or systems. Use of a Xilinxproduct in such application without the written consent of the appropriate Xilinx officer is prohibited.Revision HistoryDate Version Revision1/18/06 1.0Initial Xilinx release.18DS530 January 18, 2006。

c_oflag参数

c_oflag参数

c_oflag是控制终端输出的参数,用于控制终端的输出方式。

它的一些参数包括:

1. CREAD:使用接收器,控制终端是否能够接收数据。

2. CSIZE:字符长度,取值范围为CS5、CS6、CS7或CS8,控制终端输出的字符长度。

3. CSTOPB:设置两个停止位,控制终端输出的停止位的数量。

4. PARENB:使用奇偶校验,控制终端是否使用奇偶校验。

5. PARODD:对输入使用奇偶校验,对输出使用偶校验,控制终端的奇偶校验设置。

6. CRTSCTS:使用RTS/CTS流控制,控制终端是否使用硬件流控制。

这些参数可以通过编程方式设置,以控制终端的输出方式和特性。

XilinxSDK使用教程

XilinxSDK使⽤教程本⽂参考 Xilinx SDK软件内置的教程,打开⽅法:打开SDK->Help->Cheet Sheets...->Xilinx SDK Tutorials,这⾥有6篇⽂档。

本⽂详细介绍其中的4篇(与Application相关)如何创建⼀个新的软件应⽤1.打开SDK,切换到c/c++界⾯下。

(有两个界⾯,还有⼀个是Debug界⾯,在软件右上⾓处切换)2.指定⼀个新的硬件平台项⽬在SDK开发软件时,需要指定硬件平台。

(如果你打开⼀个现成的SDK⼯作空间,这⼀步可以省略)如果SDK⼯作空间中没有指定,BSP 新建窗⼝会弹出,询问你硬件平台。

---File > New > Other > Xilinx > Hardware Platform Specification---Next, 显⽰新的硬件项⽬对话框。

---设定项⽬名称,以及由Vivado产⽣的硬件平台。

---Finish.3.创建⼀个独⽴的板级⽀持包(Board Support Package <BSP>)---File > New > Board Support Package,打开对话框。

---指定新项⽬的名字(已初始⼀个默认的名称)---从CPU下拉列表中,选择⽬标处理器---从BSP OS下拉列表中,选择操作系统,默认是standalone(没有操作系统)---Finish.弹出BSP设置对话框---配置参数,⽣成⼀个BSP---OK4.创建应⽤项⽬---File > New > Application Project---指定项⽬名称---选择OS---选择⽬标硬件平台---选择⽬标处理器---选择编程语⾔---选择⼀个现有的BSP,或者新建⼀个---Next---选择⼀个模板,⽣成⼀个可直接运⾏的软件⼯程---Finish如何调试⼀个软件应⽤1.配置⽬标连接如果你想⽤本地设备,你可以跳过这个步骤。

zynq 除法

zynq 除法摘要:本文将介绍Zynq 除法,这是一种基于Xilinx Zynq 处理器的快捷、灵活的数字设计方法。

我们将讨论Zynq 除法的基本原理、优势以及如何在实际项目中应用这种方法。

一、引言随着数字化技术的不断发展,越来越多的工程设计人员开始使用FPGA(现场可编程门阵列)来满足高性能、低功耗的应用需求。

Xilinx Zynq 处理器是一款集成ARM Cortex-A 处理器的FPGA,提供了丰富的逻辑资源和高性能的处理能力。

在这篇文章中,我们将介绍一种基于Zynq 的除法算法——Zynq 除法,以及它在实际项目中的应用。

二、Zynq 除法的基本原理Zynq 除法是一种基于查找表(LUT)和乘法器的快捷除法算法。

它主要包括两个主要步骤:预处理和主处理。

1. 预处理:在预处理阶段,我们将被除数和除数转换为二进制形式。

然后,我们将除数分为两个部分:商的第一位和除数的其余部分。

接下来,我们计算商的第一位,即被除数除以除数的第一部分的结果。

这个过程可以使用查找表来实现,从而减少了乘法器的数量。

2. 主处理:在主处理阶段,我们将被除数除以除数的剩余部分。

这个过程与预处理类似,但不需要计算商的第一位。

我们同样可以使用查找表来实现这个过程,从而进一步提高除法器的性能。

三、Zynq 除法的优势Zynq 除法具有以下优势:1. 高性能:Zynq 除法利用查找表和乘法器实现了快捷的除法算法。

与基于硬宏的除法器相比,Zynq 除法具有更高的性能。

2. 低功耗:由于查找表和乘法器的面积较小,Zynq 除法具有较低的功耗。

此外,Zynq 处理器采用了先进的工艺技术,进一步降低了功耗。

3. 灵活性:Zynq 除法可以轻松地应用于不同的项目和需求。

通过调整查找表的内容,可以轻松实现不同的除法和取模功能。

四、实际项目中的应用在实际项目中,我们可以将Zynq 除法应用于以下场景:1. 通信系统:在通信系统中,我们需要对接收的数据进行除法运算,以确定数据包的起始位置。

FPGA可编程逻辑器件芯片XC4VFX140-11FF1517I中文规格书

XC5VTX150T: GTX_DUAL_X1Y3

AF4 AF3

AH1 AG1

AE1 AF1

AJ2 AH2

AD2 AE2

MGTREFCLKP_118 MGTREFCLKN_118

MGTRXP1_118 MGTRXN1_118

MGTRXP0_118 MGTRXN0_118

MGTTXP1_118 MGTTXN1_118

PMA_TX_CFG_0

PMA_RX_CFG_1

PMA_RX_CFG_0

PMA_COM_CFG

PMA_CDR_SCAN_1

PLL_TXDIVSEL_OUT_0 PLL_TXDIVSEL_OUT_1

PLL_LKDET_CFG PMA_CDR_SCAN_0

PLL_TDCC_CFG[2:0]

Table D-2: DRP Address by Attribute (Cont’d)

CHAN_BOND_SEQ_LEN_0 CHAN_BOND_SEQ_LEN_1

Integer

Defines the length in bytes of the channel bonding sequence that the transceiver matches to detect opportunities for channel bonding.

21

45<9> 0a<6> 5<8> 49<7> 6<8>

20

45<8> 0a<7> 4a<7> 49<6> 6<9>

19

45<7> 0a<8> 3a<6> 49<5> 6<10>

基于Xilinx

基于Xilinx Kintex-7 FPGA K7 XC7K325T PCIeX8 四路光纤

卡

基于Xilinx Kintex-7 FPGA K7 XC7K325T PCIeX8 四路光纤卡

1. 板卡概述

板卡主芯⽚采⽤Xilinx公司的XC7K325T-2FFG900 FPGA,pin_to_pin兼容FPGAXC7K410T-2FFG900,

⽀持8-Lane PCIe、64bit DDR3、四路SFP+连接器、四路SATA接⼝、内嵌16个⾼速串⾏收发器RocketIO

GTX,软件具有windows驱动。

⼆、功能和技术指标:

• 8-Lane PCIe可实现5Gbps/lane*8=40Gbps的⾼速数据传输;

• 使⽤4个16bit DDR3颗粒组成64bit DDR3,总存储容量可达1GByte;

• 4个SFP+接⼝与4个RocketIO GTX收发器连接,可⽤作万兆以太⽹接⼝;

• 4个SATA接⼝与4个RocketIO GTX收发器连接,可实现⾼速串⾏存储;

• 20对LVDS差分信号,通过连接器J6与FPGA连接,时钟频率为100MHz;

• 8个⽤户LED指⽰灯;

• 1个复位按钮;

• 所有器件可同时⽀持商业级和⼯业级。

三、软件功能:

• ⽀持DDR3 IP,PCIe IP,GTX IP开发;

• ⽀持Windows驱动,

四、应⽤领域

•软件⽆线电处理平台

•图形图像硬件加速器

• Net FPGA

•万兆⽹络

北京太速科技有限公司

在线客服:QQ:448468544

淘宝⽹站:/?

阿⾥巴巴:/

商务⽀持与服务邮箱:448468544@。

XCF04SVOG20C

XCF04SVOG20CCopyright 2009 Xilinx, Inc. All Rights Reserved. XILINX, the Xilinx logo, the Brand Window and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.XCN09029 (v1.0) October 26, 2009 1XCN09029 (v1.0) October 26, 2009 Customer Notification – For Your Information OverviewThe purpose of this notification is to communicate some revisions to the Platform Flash PROM DS123, v2.17, data sheet and UG161, v1.5, user guide. The Platform Flash PROM family includes the XCF01S, XCF02S, XCF04S, XCF08P, XCF16P, and XCF32P devices. There is no change to the form, fit, or function of these devices.Note that this notification applies to Commercial (C) grade XCFxxS and XCFxxP PROM products only. This notification does not apply to the Platform Flash XL (XCF128X) device or Military XQF32PVO48M grade device.DescriptionThe Platform Flash PROM DS123 data sheet and UG161 user guide have been revised according to Xilinx product documentation standards such that the DS123 data sheet is the primary location for product specifications and the UG161 user guide is the primary location for product usage information. These revisions also include clarifications for additional product support and usage. The details of the key revisions are listed below to insure identification of information that has changed locations, has been clarified, or has been listed as important. All the revisions are also listed within the Revision History sections of DS123 data sheet and UG161 user guide. There is no change to the form, fit, or function of these devices. Key revisions in DS123, Platform Flash In-System Programmable Configuration PROMs data sheet, v2.17:Removed empty placeholders for XCFxxP VCCO AC/DC Characteristics at 1.5V operation. Althoughthe product plans included extension of the VCCO operation down to 1.5V, the characteristics of XCFxxP VCCO operation at 1.5V were never specified and the empty specification placeholders have been removed along with all references to XCFxxP VCCO operation at 1.5V.Moved product user guidance table of “Xilinx FPGAs and Compatible Platform Flash PROMs” fromthe DS123 data sheet to the UG161 user guide.Removed “PROM to FPGA Configuration Mode and Connections Summary” section that was aredundant and less complete form of the information contained in the UG161 user guide and the FPGA configuration user guides.Removed “Configuration PROM-to-FPGA Device Interface Connection Diagrams” that were aredundant and a less complete set of reference schematics contained in the UG161 user guide.Key revisions in UG161, Platform Flash PROM User Guide, v1.5:Removed references to the never-specified XCFxxP VCCO operation at 1.5V. See the “Removedempty placeholders for XCFxxP VCCO AC/DC Characteristics at 1.5V operation” item in the DS123data sheet revision list, above.Added product user guidance table of “Xilinx FPGAs and Compatible Platform Flash PROMs” thatwas moved from the DS123 data sheet to the UG161 user guide.Added Spartan-6 and Virtex-6 FPGAs to the table of “Xilinx FPGAs and Compatible Platform FlashPROMs”.Replaced example third-party voltage regulator part number with reference to Xilinx Power Solutionswebsite (/doc/441cc0d83868011ca300a6c30c2259010302f349.html /power) for access to a wider range of applicable voltage regulator solutions.Updated software flows to ISE? software 11.x.找FPGA和CPLD上宇航军⼯Platform Flash PROM Data Sheet (DS123) and User Guide (UG161) Revisions 2 XCN09029 (v1.0) October 26, 2009 Miscellaneous usage clarifications:o Clarified XCFxxP PROM internal 40 MHz clock feature is valid with only the XCFxxP PROMdecompression feature that divides the internal clock frequency in half before driving theCLKOUT pin. This has always been true based on the related timing specifications (TCCDand FF) in the DS123 data sheet.o Clarified that third-party programmers require PROM MCS formatted file for input PROMdata. This has always been true but was not clearly specified on some third-partyprogrammers.Products AffectedThis notice applies to the Platform Flash PROM devices named in the DS123 data sheet. The DS123 data sheet changes do not affect the Platform Flash XL (XCF128X) or Military (XQF32PVO48M) grade devices which are specified in separate data sheets. Affected part numbers are included in the following table: Table 1: Affected Product Ordering Codes XCF01SVO20C XCF02SVO20C XCF04SVO20CXCF01SVO20C0100XCF02SVO20C0100XCF04SVO20C0100XCF01SVO20C0936 XCF02SVO20C0936 XCF04SVO20C0936XCF01SVOG20C XCF02SVOG20C XCF04SVOG20CXCF01SVOG20C0100XCF02SVOG20C0100XCF04SVOG20C0100XCF01SVOG20C0936 XCF02SVOG20C0936 XCF04SVOG20C0936XCF08PFS48C XCF16PFS48C XCF32PFS48CXCF08PFS48C0973XCF16PFS48C0973XCF32PFS48C0973XCF08PFSG48C XCF16PFSG48C XCF32PFSG48CXCF08PVO48C XCF16PVO48C XCF32PVO48CXCF08PVO48C0973XCF16PVO48C0973XCF32PVO48C0973XCF08PVOG48C XCF16PVOG48C XCF32PVOG48CPlatform Flash PROM Family Ordering CodesKey DatesThis notification applies to the documentation revisions shown in Table 2: Table 2: Key DatesDocumentNumberDocument Title Document Revision Publication Date DS123Platform Flash In-System Programmable Configuration PROMs v2.1710/26/09UG161 Platform Flash PROM User Guidev1.510/26/09Platform Flash PROM Data Sheet (DS123) and User Guide (UG161) Revisions XCN09029 (v1.0) October 26, 2009/doc/441cc0d83868011ca300a6c30c2259010302f349.html 3 ResponseNo response is required. For additional information or questions, please contact Xilinx Technical Support . Important Notice : Xilinx Customer Notifications (XCNs, XDNs, and Quality Alerts) can be delivered viae-mail alerts sent by the MySupport website (). Register today and personalize your “MyAlerts” area to include Customer Notifications. This change provides many benefits, including the ability to receive alerts for new and updated information about specific products, as well as alerts for other publications such as data sheets, errata, application notes, etc. For information on how to sign up, refer to Xilinx Answer Record 18683.Revision History The following table shows the revision history for this document. Date Version Revision10/26/09 1.0 Initial release.。

基于Xilinx V5的DDR2数据解析功能实现

基于Xilinx V5的DDR2数据解析功能实现

唐岚

【期刊名称】《电子设计工程》

【年(卷),期】2014(22)9

【摘要】介绍了一种基于Xilinx V5芯片的硬件板卡上,利用Verilog硬件编程语言,来实现DDR2对数据文件解析的目的:分析了CPCI总线与FPGA之间的通信特点;然后根据收到的数据文件要求,介绍了DDR2的使用方法;最后介绍了对信号波形进行验证的方法.可利用示波器对解析过程中的信号波形进行监测,以验证解析结果.经过实践证明,解析出的数据信号波形信号严格按照文件中的参数要求生成,该信号波形相位稳定,延时准确.能广泛应用于雷达模拟器以及雷达信号处理领域.

【总页数】4页(P124-126,130)

【作者】唐岚

【作者单位】北方工业大学北京100144

【正文语种】中文

【中图分类】TN80

【相关文献】

1.基于EMS V5s能源管理系统的医院能耗监测平台应用实践 [J], 胡晓妍;胡铖;陈峰;冉懋君;王道雄

2.Xilinx DDR2 IP核控制器设计 [J], 邹连英;余峰

3.XILINX推出业界第一款667 Mbps DDR2 SDRAM接口解决方案 [J],

4.Xilinx FPGA处理器解决方案为嵌入式系统设计人员提供强大的性能优势独立测

试结果再次肯定了Xilinx业界最全面的基于FPGA的32位嵌入式处理解决方案的领先地位 [J],

5.Xilinx的V5新增FXT家族,FPGA嵌入PowerPC440 [J], 迎九

因版权原因,仅展示原文概要,查看原文内容请购买。

漫谈xilinx FPGA 配置电路

漫谈xilinx FPGA 配置电路这里要谈的时xilinx的spartan-3系列FPGA的配置电路。

当然了,其它系列的FPGA配置电路都是大同小异的,读者可以类推,重点参考官方提供的datasheet,毕竟那才是最权威的资料。

这里特权同学只是结合自己的理解,用通俗的语言作一点描述。

所谓典型,这里要列出一个市面上最常见的spartan-3的xc3s400的配置电路。

所有spartan-3的FPGA配置电路的链接方式都是一样的。

Xc3s400是40万门FPGA,它的ConfigurationBitstream虽然只有1.699136Mbit,但是它还是需要2Mbit的配置芯片XCF02S,不能想当然的以为我的设计简单,最多用到1Mbit,那么我选XCF01S(1Mbit)就可以了。

事实并非如此,即使你只是用xc3s400做一个流水灯的设计,那么你下载到ROM(XCF02S)里的数据也是1.699136Mbit的,所以对于FPGA的配置ROM的选择宜大不宜小。

配置电路无非有下面五种:主串,从串,主并,从并,JTAG。

前四种是相对于下载到PROM而言的(串并是相对于不同配置芯片是串口和时并口协议和FPGA 通讯区分的),只有JTAG是相对于调试是将配置下载到FPGA的RAM而言的(掉电后丢失)。

FPGA和CPLD相比,CPLD是基于ROM型的,就是在数据下载到CPLD 上,掉电后不丢失。

而FPGA则是基于RAM的,如果没有外部ROM存储配置数据,那么掉电后就丢失数据。

所以FPGA都需要外接有配置芯片(当然现在也有基于FLASH的FPGA出现)。

那么我们就来看一下主串模式下FPGA的配置电路的连接。

官方的硬件连接如下:为了增加配置电路的可靠性,通常我们我们增加一些抗干扰的设计(如增加滤波电容、匹配电阻):先看PROM芯片的各个管脚吧。

18,19,20脚就不谈了,根据datasheet给供相对应的电平;3脚CLK是接了FPGA的CCLK,数据通信的同步就是通过FPGA 的CCLK产生的时钟进行的;因为使用的芯片时串行的配置芯片,所以只有一个数据信号口DO,连接到FPGA的DIN口(上图没有画出),和上面的时钟信号协同工作完成串行数据传输,每当CLK的上升沿锁存数据,同时PROM内部的地址计数器自动增加;另外还有两条控制信号线时INIT(连接PROM的OE/RESET)和DONE(连接PROM的CE),OE/RESET是为了确保每次重新配置前PROM的地址计数器复位;关于CE脚,官方资料说得也不是很详细,以我个人的理解,CE应该是chip enable的缩写,从它和FPGA的DONE脚连接我们不难推断出,FPGA未配置完成时DONE=0,那么配置芯片PROM处于片选状态,而一旦配置完成DONE=1,那么PROM就不再被选通,同时datasheet也说到这个管脚可以直接接地,就是一直片选中,但是这样会使DATA口有持续的数据信号输出,同时导致不必要的电流消耗;CEO脚这里不接,因为它在多个PROM的配置电路中时作为下一个PROM 的OE端信号连接用的;CF信号时连接FPAG的PROG_B接口的,它的作用就是产生开始配置信号,它连接了一个上拉电阻,如果PROG_B产生低电平脉冲则PROM 会重新开始一次配置,所以我们会在这条线上接一个按键到地,如果按键按下那么就会使能PROM重新配置FPGA;还有几个信号接口TDI,TCK,TMS,TDO都是PROM 和PC连接的信号,PC通过这些电路(通常接一片驱动隔离芯片后通过并口通信,这里不重点介绍了)下载数据到PROM中。

Xilinx滤波器IP核的延时问题

Xilinx滤波器IP核的延时问题

前一段时间一直在研究通信系统,必然就会和各种滤波器打交道,同样也遇到了一些问题。

比如说本文的主要内容,滤波器的延时问题。

在生成滤波器IP核之前需要产生抽头系数,这个抽头系数的阶数是自己设定的,阶数越高代表滤波器乘累加运算越多,但是阶数大小的选择要看是否满足自己的设计要求(例如衰减db是否满足要求)。

同时,生成的滤波器抽头系数的值是与自己设计滤波器的各种参数确定的,如数据采样速率,通带截止频率、阻带起始频率(低通)、滤波器类型等。

这些抽头系数可以用MATLAB生成,MATLAB中有一个FDATool的工具,以图形化的方式供使用者产生所需的滤波器,然后将系数导出(以coe格式),这样我们在ISE中新建FIR IP核之后就可以直接导入刚刚产生的抽头系数表,非常方便。

下面直接开始用MATLAB生成抽头系数表:

1、利用matlab 的FDATool,产生需要的滤波器系数,打开【FDATool】

2、滤波器参数设置

注意:

Order数=滤波器阶数-1

尽量设计偶数阶滤波器,偶数阶滤波器乘法器利用率高。

3、滤波器系数量化

一般量化位数在12-16之间,量化位数越低乘法器消耗的资源越少,需要设计者权衡资源与精度。

对于FIR Compiler,他使用的是DSP48 slices,经测试14位输入时16位量化位数与16位量化位数消耗相同资源,应选择16位系数。

(至于为什么消耗相同的资源,是因为FPGA内部的DSP48E1硬核乘法器是25*18的,所以无论是16位还是14位都会占。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Parallel Config.

Design Revisioning

Compression

✓ ✓ ✓

✓

✓

✓

✓

✓

✓

✓

✓

✓

✓

✓

✓

✓

✓

✓

© 2003–2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm. PowerPC is a trademark of IBM, Inc. All other trademarks are the property of their respective owners. All specifications are subject to change without notice.

the PROMs DATA (D0-D7) pins. New data is available a short access time after each rising clock edge. The data is clocked into the FPGA on the following rising edge of the CCLK. A free-running oscillator can be used in the Slave Parallel/Slave SelecMAP mode.

<BL Blue>

R

Platform Flash In-System Programmable

Configuration PROMs

DS123 (v2.11.1) March 30, 2007 0

Features

• In-System Programmable PROMs for Configuration of Xilinx FPGAs

Description

Xilinx introduces the Platform Flash series of in-system programmable configuration PROMs. Available in 1 to 32 Megabit (Mbit) densities, these PROMs provide an easy-to-use, cost-effective, and reprogrammable method for storing large Xilinx FPGA configuration bitstreams. The Platform Flash PROM series includes both the 3.3V XCFxxS PROM and the 1.8V XCFxxP PROM. The XCFxxS version includes 4-Mbit, 2-Mbit, and 1-Mbit PROMs that

support Master Serial and Slave Serial FPGA configuration modes (Figure 1, page 2). The XCFxxP version includes 32-Mbit, 16-Mbit, and 8-Mbit PROMs that support Master Serial, Slave Serial, Master SelectMAP, and Slave SelectMAP FPGA configuration modes (Figure 2, page 2). A summary of the Platform Flash PROM family members and supported features is shown in Table 1.

(VCCJ) • I/O Pins Compatible with Voltage Levels Ranging From

1.5V to 3.3V • Design Support Using the Xilinx Alliance ISE™ and

Foundation ISE Series Software Packages

DS123 (v2.11.1) March 30, 2007

Product Specification

1

R

Platform Flash In-System Programmable Configuration PROMs

CLK CE

OE/RESET

TCK

TMS TDI

Control

Data

and

ห้องสมุดไป่ตู้

Memory

JTAG Interface

Address

Data

Serial Interface

TDO

CEO

DATA (D0) Serial Mode

CF

Figure 1: XCFxxS Platform Flash PROM Block Diagram

ds123_01_30603

FI

CLK

1.5V – 3.3V 2.5V – 3.3V

VO20/VOG20

VO20/VOG20

VO20/VOG20

VO48/VOG48 FS48/FSG48

VO48/VOG48 FS48/FSG48

VO48/VOG48 FS48/FSG48

Program In-system via JTAG

✓

✓

✓

Serial Config.

Support for Programming, Prototyping, and Testing • JTAG Command Initiation of Standard FPGA

Configuration • Cascadable for Storing Longer or Multiple Bitstreams • Dedicated Boundary-Scan (JTAG) I/O Power Supply

The XCFxxP version of the Platform Flash PROM provides additional advanced features. A built-in data decompressor supports utilizing compressed PROM files, and design revisioning allows multiple design revisions to be stored on a single PROM or stored across several PROMs. For design revisioning, external pins or internal control bits are used to select the active design revision.

When the FPGA is in Slave Serial mode, the PROM and the FPGA are both clocked by an external clock source, or optionally, for the XCFxxP PROM only, the PROM can be used to drive the FPGA’s configuration clock.

• XCF08P/XCF16P/XCF32P ♦ 1.8V supply voltage ♦ Serial or parallel FPGA configuration interface (up to 33 MHz) ♦ Available in small-footprint VO48, VOG48, FS48, and FSG48 packages ♦ Design revision technology enables storing and accessing multiple design revisions for configuration ♦ Built-in data decompressor compatible with Xilinx advanced compression technology

• Low-Power Advanced CMOS NOR FLASH Process • Endurance of 20,000 Program/Erase Cycles • Operation over Full Industrial Temperature Range

(–40°C to +85°C) • IEEE Standard 1149.1/1532 Boundary-Scan (JTAG)

CE

EN_EXT_SEL

OE/RESET BUSY

OSC

TCK TMS TDI TDO

Control and JTAG

Interface

Data Address

Memory

Data

Decompressor

Serial or

Parallel Interface

CLKOUT

CEO

DATA (D0) (Serial/Parallel Mode)

XCF32P 32 Mbit

3.3V 3.3V 3.3V 1.8V

1.8V

1.8V

1.8V – 3.3V 2.5V – 3.3V 1.8V – 3.3V 2.5V – 3.3V 1.8V – 3.3V 2.5V – 3.3V 1.5V – 3.3V 2.5V – 3.3V

1.5V – 3.3V 2.5V – 3.3V

Product Specification