AD402M182VCA-5中文资料

DMD402_DMD402A使用手册

⑥ ⑤ ④ ③

4 线电机

⑥ ⑤ ④ ③

8 线电机(并联)

控 制 器

VCC

Com R Pul

270Ω

15mA±20%

驱 动 器

脉冲信号

270Ω

R

方向信号

Dir

330Ω

⑥ ⑤ ④ ③

8 线电机(串联)

⑥ ⑤ ④ ③

6 线电机(高扭矩)

使能信号

R

Ena

VCC值为5V时,R短路; VCC值为12V时,R=1KΩ(≥1/8W); VCC值为24V时,R=2KΩ(≥1/8W)。

DMD402/DMD402A 使用手册

DMD402/DMD402A 使用手册

1、简

介

DMD402、DMD402A 是我公司自主研发的步进电机细分驱动器,它 们具有高性能、 低价格的特点, 适合驱动两相或四相混合式步进电机。 由于采用新型的双极性恒流斩波驱动技术, 使用同样的电机时可以比 其它驱动方式输出更大的功率。其细分功能使步进电机低频振动减 小,噪声降低,同时有助于运转精度提高。

8

9

DMD402/DMD402A 使用手册

DMD402/DMD402A 使用手册

6.2 设定输出电流

7、 电 源 供 给

电源电压在 DC14V ~DC40V 之间都可以正常工作,本驱动器 最好采用非稳压型直流电源供电,也可以自己采用变压器降压+ 桥式整流+电容滤波,电容可取 6800μ F或 10000μ F。但注意应使 整流后电压纹波峰值不超过 40V,避免电网波动超过驱动器电压

A向

95

保存温度

24

重量

10 11.5

4—Φ4

33

5

M218控制器

• •

第一章 产品简介-编程软件 产品简介M218控制器的可编程开发软件: M218控制器的可编程开发软件:SoMachine V2.0 控制器的可编程开发软件 SoMachine是一个专业的 高效的,开放的OEM解决方案软件, 是一个专业的, OEM解决方案软件 SoMachine是一个专业的,高效的,开放的OEM解决方案软件,可 以在单个环境中组态和调试整个机器. 以在单个环境中组态和调试整个机器. – HMI控制器 HMI控制器 • HMI控制器 控制器; Magelis XBT GC HMI控制器; • 控制器; XBT GT/GK CANopen HMI 控制器; – 逻辑控制器 • 逻辑控制器; Modicon M218 逻辑控制器; • 逻辑控制器; Modicon M238 逻辑控制器; • 逻辑控制器; Modicon M258 逻辑控制器; – 运动控制器 • LMC058 – 传动控制器 • ATV IMC

技术参数-继电器输出特征 第二章 技术参数-继电器输出特征

输出供电 额定电流值

额定电压 供电范围

24VDC 5V~ 5V~30VDC 2A/通道 2A/通道 4A 0.1Hz 5Hz 否 继电器线圈 20,000,000次 20,000,000次 非屏蔽30m 非屏蔽30m

220VAC 100VAC~ 100VAC~250VAC

电流/ (4通道) 电流/组(4通道) 通道 最大输出频率 防短路 输出类型 机械寿命 电缆长度 最大负载 无负载

技术参数-模拟量输入特征 第二章 技术参数-模拟量输入特征

输入类型 最大输入通道数 输入类型 输入范围 输入阻抗 I/O端子类型 I/O端子类型 采样时间 总输入传输时间 输入误差 输入精度 允许的过载电压 保护类型 极性接反 电缆长度 电缆类型 -10VDC~10VDC 10VDC~ 0~10VDC >1MΩ 可插拔端子 10ms/通道+1扫描周期 10ms/通道+1扫描周期 通道+1 20ms+1扫描周期 20ms+1扫描周期 +1% 12位 12位,包含符号位 +30VDC 输入和内部电路之间的光耦隔离 保护 最大屏蔽电缆3 最大屏蔽电缆3米 屏蔽电缆 电压输入 2 单端输入 0~20mA 4~20mA <250Ω 电流输入

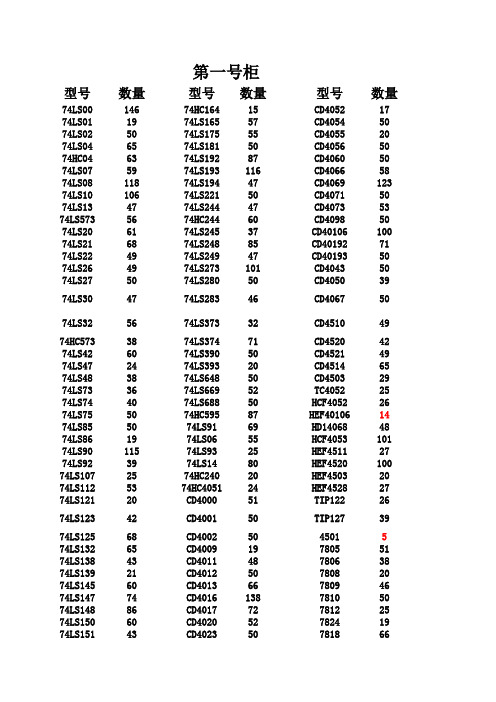

元器件清单

第一号柜型号数量型号数量型号数量74LS0014674HC16415CD405217 74LS011974LS16557CD405450 74LS025074LS17555CD405520 74LS046574LS18150CD405650 74HC046374LS19287CD406050 74LS075974LS193116CD406658 74LS0811874LS19447CD4069123 74LS1010674LS22150CD407150 74LS134774LS24447CD407353 74LS5735674HC24460CD409850 74LS206174LS24537CD40106100 74LS216874LS24885CD4019271 74LS224974LS24947CD4019350 74LS264974LS273101CD404350 74LS275074LS28050CD405039 74LS304774LS28346CD406750 74LS325674LS37332CD451049 74HC5733874LS37471CD452042 74LS426074LS39050CD452149 74LS472474LS39320CD451465 74LS483874LS64850CD450329 74LS733674LS66952TC405225 74LS744074LS68850HCF405226 74LS755074HC59587HEF4010614 74LS855074LS9169HD1406848 74LS861974LS0655HCF4053101 74LS9011574LS9325HEF451127 74LS923974LS1480HEF4520100 74LS1072574HC24020HEF450320 74LS1125374HC405124HEF452827 74LS12120CD400051TIP12226 74LS12342CD400150TIP12739 74LS12568CD40025045015 74LS13265CD400919780551 74LS13843CD401148780638 74LS13921CD401250780820 74LS14560CD401366780946 74LS14774CD4016138781050 74LS14886CD401772781225 74LS15060CD402052782419 74LS15143CD402350781866 74LS15373CD402448790572 74LS15464CD402648790647 74LS15550CD40275079084774LS16069CD40305079093874LS161103CD40404679124274LS163135CD40463079153574LS16437CD405144792419 LM31736LM33757第三号柜型号数量型号数量型号数量晶振(1M)6347P60左右电容683180左右455K1750P200左右1041500左右32.678K7556P160左右224150左右6M6162P150左右33480左右4M2675P120左右474220左右8M8682P180左右10520左右10M27电容101150左右272500左右11.0592M54105100左右9051(NPN)150左右12M53201150左右9011(NPN)80左右20M56221200左右9012(PNP)50左右14.318M6918180左右9013(NPN)100左右24M45271100左右9014(NPN)60左右40M90左右301150左右8550(PNP)100左右10.245M50左右331200左右9018(NPN)100左右80M18391100左右8050(NPN)120左右3.57954523471250左右发光二级管(红)110左右30M有源25501600左右发光二级管(绿)100左右36M有源38511180左右光敏二极管13电容(12P)67561100左右FR307二极管50左右15P50左右681200左右可调电容25-36P70左右3P100左右1021000左右发光二级管(黄)220左右4P100左右821250左右白发红光二极管200左右2.2P100左右122300左右红外发射208P100左右15270左右红外接收29 1P40左右202100左右发光二级管(白)20左右1.5P150左右222160左右发光二级管(双色)80左右5.6P/5.1P100左右302400左右IN60366P/6.8P100左右332180左右稳压二极管2.7V957P/8.2P80左右392100左右稳压二极管2.4V105 9P100左右472180左右IN4732101 10P200左右502120左右IN473049 18P250左右562150左右IN472842 20P180左右682250左右IN472998 22P800左右822150左右IN473395 27P180左右1031500左右IN4734125 30P700左右223200左右IN474429 33P1000左右333300左右IN47354239P750左右473350左右IN414876 IN40010IN4007270左右IN91458第五号柜型号数量型号数量型号数量MSP430F2TPS78001D2THS7001CPWP2 TLC0820AIN27THS4271D22TPS62100D22 AD60313INA137PA2DAC902E31 TLC082IP20DAC781114CX20106A20 OPA2822U40DAC782122MRR2045CTG40 INA213A20CE8301282DW23431 ADS1158202720120TPS6106220 UCC28600D20OPA355UA21117-3.346 TLV5636ID30TPS5416021117-1.830 VCA822ID30PGA113A62390nH100 INA333A82TPS601102470nH80 INA133UA20TPS612002X9312WP36 TLV2462A25TPS601002X9312TP30 ADS828E20ADS788222绕线电阻-36欧10 OPA691ID19ADS523720绕线电阻-30欧6 THS3001ID20VFC32KP22TPS6107020 TPS60310DGS2VCA81037激光二极管40 INA2134PA30INA28220激光接收管10 OPA2134PA35LP2950-33120聚焦透镜10 OPA234020TPS543020ADS111520TPS54331D20CSD17505Q5A15TPS6040020第七号柜型号数量型号数量型号数量AD83512BQ2402517MC337220 ADS834422AT25F51212MC159617 AD836919BUF301200MC164817 ADS850712CNY17-220FDS943120 ADS781820CSI5112PI0MPY6348 AD831020CXA1545AS14MUR15109 AD63716CXA1587S14NCP105020 AD99542CXA169129LM267620 AD71229ATHE8A3260LM290420 AD81130DAC855217LVC424572 AD83424DAC855524KMZ4125 ADS788619DAC900U15HS003819 AD832019DAC902E21LM388610AD84124DAC761116THS450335 AD83024DM9000AE9TL311622 AD84419EXB84115TLC22129 LF412CN35ispPAC805TLC37237 LF35750IR210330MLT0424 74HC57420IR211034MT888018 INA27130MC283328MOC306322 BTA41700B20MC336130MUR166030 BUF634722MC1450770IRF954040 INA12890MC14516323IRF54042 INA15919MC100LVEL6D20TIP32A0 INA233126MC908GP325TIP32C75 INA27034MC1202219IRF530N33 INA233224MAC97A680左右IRF9530N46 BUP30411MC336230IRF63031IRF64046第九号柜型号数量型号数量型号数量CBB102/100V100左右220uF/16V80左右V147-371015490.1uF/630V100左右220uF/250V10V147-391015416 0.47uF/630V100左右47uF/63V50左右二极管SA12A50 220uF/16V50左右47uF/100V100左右P6KE91120 103K/630V100左右100uF/16V120左右IN581752 CD100uF/25V120左右100uF/50V100左右IN582263 100uF/100V80左右330uF/16V80左右贴片9012100左右4.7uF/25V120左右470uF/16V50左右9013100左右4.7uF/50V110左右33uF/250V80左右8050150左右0.1uF/50V30左右47uF/16V100左右8550100左右0.1uF/160V120左右470uF/25V30左右磁环122.2uF/50V80左右1000uF/25V30左右贴片电阻1021500左右3.3uF/16V50左右1000uF/50V100左右贴片电阻0欧100左右4.7uF/250V50左右2200uF/16V60左右软键盘710uF/25V50左右4700uF/16V100左右太阳能控制板147uF/50V100左右2200uF/25V60左右贴片901880左右1uF/50V80左右C92-02恢复二极管30左右1000uF/100V20 100uF/50V30左右D92-02恢复二极管242200uF/100V2010uF/50V15左右变容二极管0-20P30470uF/50V1522uF/25V100左右变容二极管40-75P302200uF/50V2122uF/50V60左右变容二极管400-850P304700uF/50V2322uF/100V23二极管P6KE20020继电器943-1C-6DS2633uF/25V60左右P6KE120105继电器G5RL-1A-E1522uF/250V100左右P6KE15020220uF/450V20第二号柜型号数量型号数量型号数量电位器10126ADS77418OP2745电位器102177AD62029OP3744电位器103107AD770533TL08264电位器104161DAC083233TL08438电位器201150AD65024TL49475电位器202185AD66920TL384210电位器203218AD67719HA1732437电位器204194AD722820CA314058电位器501100AD985124N2567电位器502305AD985274N3551电位器503109MC1403496N13667电位器50448MC1444246N13750电位器253210MC148934P52137拨码开关4P28MC1406035MOC302053拨码开关8P52MC1451649PC81740电机驱动L29725MC1452673NEC2501121电机驱动L29826MC1443320高桥/10A20 BT15118MC14502723LF351116 BT113640MC348631LF35356 D827935NE555116LF35683 82C2920NE55647LF34725 TLP52150NE56461LF39854 D825321NE56769PT226235 D815540NE553292PT227216 80301NE553469ULN200324 80512MICRF002B5ULN280320 AT89C51103MC149622TLC154328 AT89S5117LM3552TLC254328 AT89S5212LM311144TLC551026 AT89C526LM32423TLS752820 AT89C205158LM336(5V)117TLE202219 HY626435LM336(2.5V)50TLV561625 HM6225639LM33928TEB403331 HM61166LM35850TDA282264 M27C12819LM38639TDA705010 GAL20V8B21LM39348HD727910 PIC16C57C6LF56759ST288A48 PIC12C508A16LM741101CH3412 24LC08B35LM187567ICL803840 74HC29524LM290430NB72329 ADC080930LM181217TL07250 ADC083267LM31926TLV246030 AD775123LM33148AD54524ISD256017AD53640ISD25902AD57030FR60722AD57420OP0755AD52618第四号柜型号数量型号数量型号数量C2073(功率管)16ST-ICL319一体化超声波传感器3 3DA87CJ48C181520QM-YT11 3DG800TA7267BP2310214 3DG130DJ107SP203910134 A94020晶闸管1A单硅1810432 KSP290750晶闸管1A双硅1547324 IRF84024EPM72181520442 TIP41C27EP1KTC144220237 TIP42C32EPC2LI20520366 KSP2222A80左右SHT11750240 TL431AC178XF-18D4250143 2DW2331USB转接器150433 2N540150左右热敏电阻75S10KBP31041 2N555140左右NTC10K(+/-)1%9KBPC80855 3D0175左右MYG7K33029KBPC21012 K112035ORD9216302W1013 3DV3330TA122DB106G41 2SC328020热敏电阻10K40左右E623203 DS18B2033C0412直流电机3470K15 BT33P0BPW410光敏电阻34B50K24 BT33FJ40杜邦-IP大量B100K10 DG20135小按键60左右2SK-24118 BBP1020拨码开关50左右K147120 B83472510-2P连接器40左右K51410 D88018人体感应模块163DU3388HM1温度模块149E70518温度传感器73DU310HS1101293DU320HTS11110AN5035C290120CS5125C197020CB35520BB639202SA130125BB11230TDA203023MQ-23ST251C123HY3011RE20015EL-1KL20LM3357SP-1KL0AD59026PT-23F13TCRT500015第六号柜型号数量型号数量型号数量C20790MAX43730MAX76430 C9450MAX50320MAX602920 JGX-5113F3MAX54223OPA12922 nRF24015MAX75632OPA13234 TL07113MAX76526OPA13430 ISD142020MAX80941OPA642u16 CSI511212MAX87431OPA335582SC3423-Y10MAX162620OPA300142SA1360-Y30MAX260120OPA36548 MAX03818MAX26212OPA56136 MAX19517MAX261120OPA60420 MAX20245MAX41065OPA63727 MAX23234MAX740120OPA69016 MAX29120MAX742119OPA222719 MAX323238磁壳绕线电阻器17OPA2270 MAX30620MAX29731OPA22822 MAX40018MAX30927OPA33322编码器2MCR100-630OPA54812 C0721763DG6C20OPA82034 2460C783DG8D20OPA84243射频线3DG182C193CG15C20 OPA656203DG7A20ADS114620第八号柜型号数量型号数量型号数量TL0459TRF37506MCR100-60 TL05230TSAC620022SC520020 TLC08379TLC7135732SC17909 TLC08546TDS2285102SC945100左右TPS7590122THS3091162SC19710 TLV246318安规电容0.1uF80左右应力传感器8 TLV154410安规电容1000pF40左右IN5401100左右SF56208UA73330直流电机30r/分7 MSP430F20027UCC2801926直流电机100r/分0 MSP430F22745UCC38C4322语音编程器2 MSP430F427010UGN35035语音操作WT588D-2010 PM30SSJ06010THS461315超声波发射36 RHRG301200409440超声波接受36SN65LBC184D10C9231282SA194318 SG352520SCA60C-N10000602霍尔开关FQZ-F-NK203 SP322029LM717115中周HGTF10-116 ST18820图像传感器T001P128中周HGTF10-213 ST27817智能控制器2交流接触器1 TPS73301474F15720电机驱动器BAL-352 TPS733335MQ-416电机驱动器DMD402A1 RF2317202SC190644固态继电器SSR-800 TPS3803202SC17910接近开关TK-SN5C3 ADE775517KS10A3 SMA射频插头磁珠29光电探测器10电源变压器19 1W高亮LED50第十号柜型号数量型号数量型号数量数码管LG3641BH38钽电容6.8uF40左右各种DIP座大量TOS-5101BH-B57钽电容22uF80左右LG3641AH23330uH90左右蜂鸣器50左右1uH150左右扬声器0 3.3uH100左右电源插头3210uH80左右9针串口头50左右33uH150左右9孔串口头23贴片68nH80左右电感120uH60左右贴片82nH80左右100uH100贴片0.22uH80左右220uH80左右贴片0.27uH80左右6.8uH/400V250左右 6.8mH110左右470uH120左右 4.7mH120左右680uH100左右10mH25左右12uH110左右100mH50左右15uH100左右色环1mH90左右47uH80左右立式电感1mH80左右56uH100左右立式电感33mH70左右3.3uF/150V50左右排针排座大量100uF/100V50左右IDC座大量10mH100左右连接器大量22uH65左右转接板大量钽电容10uF/25V40左右各种电阻大量钽电容22uF/16V5010000uF/63V20。

EUP40D-2HMC-0 无线调光LED驱动器 电源参数手册说明书

220VAC-240VAC 50/60Hz87%@230VAC,Full load ≥0.95@230VAC,Full load Cold start,12A(twidth=50us measured at 50% Ipeak)@230VAC 0.2Amax@230VAC 137*82*31mm (L*W*H )IP20-20℃~50℃-40℃~85℃, 20-90%RH 90℃PC 50,000h@tc:75℃0.1%-100% Dimming to off ±5%<3%DALI-2>100,000 times2600mA/9-42VDC/25.2W 700mA/9-42VDC/29.4W800mA/9-42VDC/33.6W<15%@230VAC, Full load EUP40D-2HMC-0tc LifetimeMaterialBrightness Range 3000-6000KColor Temperature DimensionNet weight: 225g±5%/PCS; 50PCS/Carton;11.75kg±5%/Carton; Carton Size: 517*337*179mm(L*W*H)Packing(weight)IP Rating Working Temp.Storage Temp., Humidity Dimming TypeSwitch Cycle 5 years Warranty Condition No load output voltage 50VDC Efficiency AC Current(max)<0.5WStandby power Inrush Current(max)THD(full load)Current(mA)/Voltage (VDC) Power(W)Output Lf Current Ripple(<120hz)Channel Current Tolerance VoltageFrequency Range(Hz)Power Factor Short Circuit Over TemperatureOver load Close output ,recovers automatically after fault removed Hiccup, when the output power exceeds the rated power of 100~120%,then,recoversautomatically after fault removed When tc exceeds 105℃,shut down the output, recoversautomatically , when temp. back to 85℃OthersFunctionModelOutputInputProtectionSummaryProduct Features·Meet DALI Protocol IEC 62386 DT8, Support DALI-2 Dimming ·SELV. Full protective plastic housing ·High efficiency up to 87 %·Built-in active PFC function·Dimming effect smooth, no flicker·Protections: Short circuit, over load, over temperature ·The positive output of the two channels is common·Supports adjustment of brightness and colour temperature.EUP40D-2HMC-0 is a LED controller that provides two channels outputs.The user can select the total output current via DIP switch.It supports DALI standard protocol and adjustment of brightness and colour temperature.EUP40D-2HMC-0(Product No.:102100860101)Dimension(mm)Technical ParamatersApplicationDownlight Panel Light Flood LightSpotlight Ceiling Light Floor LightDecorative LightDALI Wiring※ The contents of this manual are updated without prior notice. If the function of the product you are using is inconsistent with the instructions, the function of the product shall prevail.Please contact us if you have any questions .Cautions1.This product should be installed by qualified personnel.2.This product is non waterproof, need to avoid sun and rain.In case of outdoor use, please ensure it is mounted in a water proof enclosure.3.Good heat dissipation conditions extend product life.Please install the product in a well-ventilated environment.4.Please make sure LED power supply output voltage,current is used to meet the product requirements.5.Due to safety concerns, cables for input and output terminal(s) must meet the following requirements : Ensure all wire connections and polarities are correct before applying power to avoid any damages to the LED lights.6.The max quantity of drivers that connect to MCB type B16A is 80.7.In case of malfunction, do not repair it yourself.Note: When the DALI signal is not connected, the output power of WW (warm light) channel is full, while that of CW (cold light) channel is not.20406080100120DALI Dimming LevelO u t p u t C u r r e n t(%)Dimming CurveCurrent Selection TablePF vs load0.910.920.950.96Load(%)PFTHD vs Load468Load(%)T H D (%)Derating CurveAmbient Temperature(℃)-20020406080100L o a d (%)-10102030405060600mA 700mA 800mA ON OFF ONON OFF ONOFF ON ONOFF ON ONCurrent CW-1CW-2WW-1WW-2Push DIM(Touch DIM) DiagramPush DIM/Coloer Switch1. Press and hold the push DIM switch for 8s or more to enter the push dimming mode.2. Press the push DIM switch briefly to turn on or off the lamp and return to the last memory state.3. Press and hold the push DIM switch for dimming, stop at the current brightness when releasing, and adjust in the opposite direction every time, with the dimming range of 5% - 100%4. Double click the push DIM switch to turn on the lamp to the brightest and cool light (this function is also used to adjust the consistency of multiple power supplies in the same circuit)5. Colour switch is valid only after entering push DIM mode.6. Press colour SWITCH briefly to set the color temperature mode, with 9 values between 2,700 and 6,500K.7. Long press Colour SWITCH can continuously adjust the color temperature. Every long press, the color temperature will be adjusted in the opposite direction, with the color temperature range of 2700-6500K 。

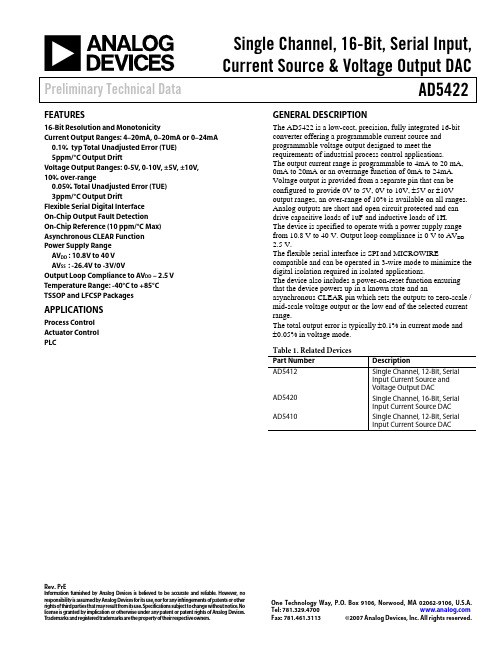

AD5422中文资料

Single Channel, 16-Bit, Serial Input,Current Source & Voltage Output DAC Preliminary Technical Data AD5422Rev. PrEInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, M A 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.FEATURES16-Bit Resolution and MonotonicityCurrent Output Ranges: 4–20mA, 0–20mA or 0–24mA 0.1% typ Total Unadjusted Error (TUE)5ppm/°C Output DriftVoltage Output Ranges: 0-5V, 0-10V, ±5V, ±10V,10% over-range0.05% Total Unadjusted Error (TUE)3ppm/°C Output DriftFlexible Serial Digital InterfaceOn-Chip Output Fault DetectionOn-Chip Reference (10 ppm/°C Max)Asynchronous CLEAR FunctionPower Supply RangeAV DD : 10.8V to 40 VAV SS : -26.4V to -3V/0VOutput Loop Compliance to AV DD – 2.5 V Temperature Range: -40°C to +85°CTSSOP and LFCSP PackagesAPPLICATIONSProcess ControlActuator ControlPLC GENERAL DESCRIPTIONThe AD5422 is a low-cost, precision, fully integrated 16-bit converter offering a programmable current source and programmable voltage output designed to meet the requirements of industrial process control applications.The output current range is programmable to 4mA to 20 mA,0mA to 20mA or an overrange function of 0mA to 24mA. Voltage output is provided from a separate pin that can be configured to provide 0V to 5V, 0V to 10V, ±5V or ±10V output ranges, an over-range of 10% is available on all ranges. Analog outputs are short and open circuit protected and can drive capacitive loads of 1uF and inductive loads of 1H.The device is specified to operate with a power supply range from 10.8 V to 40 V. Output loop compliance is 0 V to AV DD – 2.5 V.The flexible serial interface is SPI and MICROWIRE compatible and can be operated in 3-wire mode to minimize the digital isolation required in isolated applications.The device also includes a power-on-reset function ensuring that the device powers up in a known state and an asynchronous CLEAR pin which sets the outputs to zero-scale / mid-scale voltage output or the low end of the selected current range.The total output error is typically ±0.1% in current mode and ±0.05% in voltage mode.Table 1. Related DevicesPart Number DescriptionAD5412 Single Channel, 12-Bit, SerialInput Current Source andVoltage Output DACAD5420 Single Channel, 16-Bit, SerialInput Current Source DACAD5410 Single Channel, 12-Bit, SerialInput Current Source DACAD5422Preliminary Technical DataRev. PrE | Page 2 of 37TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 General Description.........................................................................1 Revision History...............................................................................2 Functional Block Diagram..............................................................3 Specifications.....................................................................................4 AC Performance Characteristics................................................7 Timing Characteristics................................................................8 Absolute Maximum Ratings..........................................................10 ESD Caution................................................................................10 Pin Configuration and Function Descriptions...........................11 Typical Performance Characteristics Voltage output ...............13 Typical Performance Characteristics current output ...............17 Typical Performance Characteristics general ............................20 Terminology....................................................................................22 Theory of Operation......................................................................24 Architecture.................................................................................24 Serial Interface............................................................................24 Default configuration.................................................................28 Transfer Function.......................................................................28 Data Register...............................................................................29 Control Register..........................................................................29 RESET register............................................................................29 Status register..............................................................................30 Features............................................................................................31 fault alert......................................................................................31 voltage output short circuit protection....................................31 Asynchronous Clear (CLEAR).................................................31 Internal Reference......................................................................31 External current setting resistor...............................................31 Voltage ouTput over-range........................................................31 Digital Power Supply..................................................................31 External boost function.............................................................31 digital Slew rate control.............................................................32 I OUT Filtering Capacitors............................................................32 Applications Information..............................................................33 driving inductive loads..............................................................33 Transient voltage protection.....................................................33 Layout Guidelines.......................................................................33 Galvanically Isolated Interface.................................................33 Microprocessor Interfacing.......................................................33 Thermal and supply considerations.........................................34 Outline Dimensions.......................................................................35 Ordering Guide.. (35)REVISION HISTORYPrE – Preliminary Version, November 22, 2007Preliminary Technical DataAD5422Rev. PrE | Page 3 of 37FUNCTIONAL BLOCK DIAGRAMV OUT I OUT LATCH SCLK SDIN SDOCCAGND CLEAR FAULT BOOSTREFOUT REFIN SENSESENSECLEAR SELECT R SET DV CC C COMP2C COMP1DGND**LFCSP PackageFigure 1.AD5422Preliminary Technical DataRev. PrE | Page 4 of 37SPECIFICATIONSAV DD = 10.8V to 40V , AV SS = -26.4V to -3V/0V , AV DD + |AV SS | < 52.8V , AGND = DGND = 0 V , REFIN= +5 V external; DV CC = 2.7 V to 5.5 V , V OUT : R L = 2 kΩ, C L = 200 pF, I OUT : R L = 300Ω, H L = 50mH; all specifications T MIN to T MAX , ±10 V / 0 to 24 mA range unless otherwise noted. Table 2.Parameter Value 1 Unit Test Conditions/CommentsVOLTAGE OUTPUTOutput Voltage Ranges 0 to 5 V 0 to 10 V -5 to +5 V -10 to +10 V ACCURACY Output unloaded Bipolar Output Resolution 16 Bits Total Unadjusted Error (TUE) 0.1 % FSR max Over temperature, supplies, and time, typically 0.05%FSRTUE TC 2 ±3 ppm typ Relative Accuracy (INL) ±0.012 % FSR max Differential Nonlinearity (DNL) ±1 LSB max Guaranteed monotonic Bipolar Zero Error ±5 mV max @ 25°C, error at other temperatures obtained usingbipolar zero TCBipolar Zero TC 2±3 ppm FSR/°C max Zero-Scale Error ±1 mV max @ 25°C, error at other temperatures obtained using zeroscale TCZero-Scale TC 2±3 ppm FSR/°C max Gain Error ±0.05 % FSR max @ 25°C, error at other temperatures obtained using gainTCGain TC 2 ±8 ppm FSR/°C max Full-Scale Error 0.05 % FSR max @ 25°C, error at other temperatures obtained using gainTCFull-Scale TC 2 ±3 ppm FSR/°C max Unipolar Output AV SS = 0 V Resolution 16 Bits Total Unadjusted Error (TUE) 0.1 % FSR max Over temperature, supplies, and time, typically 0.05%FSRRelative Accuracy (INL) ±0.012 % FSR max Differential Nonlinearity (DNL) ±1 LSB max Guaranteed monotonic (at 16 bit-resolution) Zero Scale Error +10 mV max @ 25°C, error at other temperatures obtained using gainTCZero Scale TC 2±3 ppm FSR/°C max Offset Error ±10 mV max Gain Error ±0.05 % FSR max @ 25°C, error at other temperatures obtained using gainTCGain TC 2±3 ppm FSR/°C max Full-Scale Error 0.05 % FSR max @ 25°C, error at other temperatures obtained using gainTCFull-Scale TC 2±3 ppm FSR/°C maxOUTPUT CHARACTERISTICS 2eadroom 0.8 V max 0.5 V typ Output Voltage TC ±3 ppm FSR/°C max Output Voltage Drift vs. Time ±12 ppm FSR/500 hr typ Vout = ¾ of Full-Scale ±15 ppm FSR/1000 hr typ Short-Circuit Current 12 mA typPreliminary Technical DataAD5422Rev. PrE | Page 5 of 37Parameter Value 1 Unit Test Conditions/Comments Load 2 kΩ min For specified performance Capacitive Load Stability R L = ∞ 20 nF max R L = 2 kΩ TBD nF max R L = ∞ 1 µF max External compensation capacitor of 4nF connected. DC Output Impedance 0.3 Ω typ Power-On Time 10 µs typ DC PSRR TBD µV/VCURRENT OUTPUTOutput Current Ranges 0 to 24 mA 0 to 20 mA 4 to 20 mA ACCURACY Resolution 16 Bits Total Unadjusted Error (TUE) ±0.3 % FSR max Over temperature, supplies, and time, typically 0.1% FSR TUE TC 2 ±5 ppm/°C typ Relative Accuracy (INL) ±0.012 % FSR max Differential Nonlinearity (DNL) ±1 LSB max Guaranteed monotonic Offset Error ±0.05 % FSR max Offset Error Drift ±5 µv/°C typ Gain Error ±0.02 % FSR max @ 25°C, error at other temperatures obtained using gainTCGain TC 2 ±8 ppm FSR/°C max Full-Scale Error 0.05 % FSR max @ 25°C, error at other temperatures obtained using gainTCFull-Scale TC 2 ±8 ppm FSR/°COUTPUT CHARACTERISTICS 2Current Loop Compliance Voltage AVDD - 2.5 V max Output Current Drift vs. Time TBD ppm FSR/500 hr typ TBD ppm FSR/1000 hr typ Resistive Load TBD Ω max Inductive Load 1 H max DC PSRR 10 µA/V max Output Impedance 50 MΩ typREFERENCE INPUT/OUTPUTReference Input 2 Reference Input Voltage 5 V nom ±1% for specified performance DC Input Impedance 30 kΩ min Typically 40 kΩ Reference Range 4 to 5 V min to V max Reference Output Output Voltage 4.998 to 5.002 V min to V max @ 25°C Reference TC ±10 ppm/°C max Output Noise (0.1 Hz to 10 Hz)2 18 µV p-p typNoise Spectral Density 2120 nV/√Hz typ @ 10 kHz Output Voltage Drift vs. Time 2 ±40 ppm/500 hr typ ±50 ppm/1000 hr typ Capacitive Load TBD nF max Load Current 5 mA typ Short Circuit Current 7 mA typ Line Regulation 2 10 ppm/V typLoad Regulation 2TBD ppm/mA Thermal Hysteresis 2 TBD ppmAD5422 Preliminary Technical Data1 Temperature range: -40°C to +85°C; typical at +25°C.2 Guaranteed by characterization. Not production tested.Rev. PrE | Page 6 of 37Preliminary Technical DataAD5422Rev. PrE | Page 7 of 37AC PERFORMANCE CHARACTERISTICSAV DD = 10.8V to 40V , AV SS = -26.4V to -3V/0V , AV DD + |AV SS | < 52.8V , AGND = DGND = 0 V , REFIN= +5 V external; DV CC = 2.7 V to 5.5 V , V OUT : R L = 2 kΩ, C L = 200 pF, I OUT : R L = 300Ω, H L = 50mH; all specifications T MIN to T MAX , ±10 V / 0 to 24 mA range unless otherwise noted. Table 3.Parameter 1 Unit Test Conditions/Comments DYNAMIC PERFORMANCEVOLTAGE OUTPUTOutput Voltage Settling Time 8 µs typ Full-scale step (10 V) to ±0.03% FSR 10 µs max 5 µs max 512 LSB step settlingOutput Current Settling Time 10 µs max To 0.1% FSR Slew Rate 1 V/µs typ Power-On Glitch Energy 10 nV-sec typ Digital-to-Analog Glitch Energy 10 nV-sec typ Glitch Impulse Peak Amplitude 20 mV typ Digital Feedthrough 1 nV-sec typ Output Noise (0.1 Hz to 10 Hz Bandwidth) 0.1 LSB p-p typ Output Noise (100 kHz Bandwidth) 80 µV rms max 1/f Corner Frequency 1 kHz typ Output Noise Spectral Density 100 nV/√Hz typ Measured at 10 kHz AC PSRR TBD dB 200mV 50/60Hz Sinewavesuperimposed on power supply voltage.CURRENT OUTPUTOutput Current Settling Time TBD µs typ To 0.1% FSR , L = 1H TBD µs typ To 0.1% FSR , L < 1mH1Guaranteed by characterization, not production tested.AD5422Preliminary Technical DataRev. PrE | Page 8 of 37TIMING CHARACTERISTICSAV DD = 10.8V to 40V , AV SS = -26.4V to -3V/0V , AV DD + |AV SS | < 52.8V , AGND = DGND = 0 V , REFIN= +5 V external; DV CC = 2.7 V to 5.5 V , V OUT : R L = 2 kΩ, C L = 200 pF, I OUT : R L = 300Ω, H L = 50mH; all specifications T MIN to T MAX , ±10 V / 0 to 24 mA range unless otherwise noted. Table 4.Parameter 1, 2, 3 Limit at T MIN , T MAX Unit DescriptionWrite Modet 1 33 ns min SCLK cycle time t 2 13 ns min SCLK low time t 3 13 ns min SCLK high time t 4 13 ns min LATCH delay time t 5 40 ns min LATCH high time t 5 5 µs min LATCH high time (After a write to the CONTROL register) t 6 5 ns min Data setup time t 7 5 ns min Data hold time t 8 40 ns min LATCH low time t 9 20 ns min CLEAR pulsewidth t 10 5 µs max CLEAR activation timeReadback Modet 11 82 ns min SCLK cycle time t 12 33 ns min SCLK low time t 13 33 ns min SCLK high time t 14 13 ns min LATCH delay time t 15 40 ns min LATCH high time t 16 5 ns min Data setup time t 17 5 ns min Data hold time t 18 40 ns min LATCH low time t 19 40 ns max Serial output delay time (C L SDO 4 = 15pF) t 20 33 ns max LATCH rising edge to SDO tri-stateDaisychain Modet 21 82 ns min SCLK cycle time t 22 33 ns min SCLK low time t 23 33 ns min SCLK high time t 24 13 ns min LATCH delay time t 25 40 ns min LATCH high time t 26 5 ns min Data setup time t 27 5 ns min Data hold time t 28 40 ns min LATCH low time t 29 40 ns max Serial output delay time (C L SDO 4 = 15pF)1 Guaranteed by characterization. Not production tested.2All input signals are specified with t R = t F = 5 ns (10% to 90% of DV CC ) and timed from a voltage level of 1.2 V. 3See Figure 2, Figure 3, and Figure 4. 4C L SDO = Capacitive load on SDO output.Preliminary Technical DataAD5422Rev. PrE | Page 9 of 37SCLK LATCHSDINCLEAROUTPUTFigure 2. Write Mode Timing DiagramSCLKLATCHSDINSDOSELECTED REGISTER DATA CLOCKED OUTFIRST 8 BITS ARE DON’T CARE BITSFigure 3. Readback Mode Timing DiagramSCLKSDINSDOLATCHFigure 4. Daisychain Mode Timing DiagramAD5422Preliminary Technical DataRev. PrE | Page 10 of 37ABSOLUTE MAXIMUM RATINGST A = 25°C unless otherwise noted.Transient currents of up to 100 mA do not cause SCR latch-up. Table 5.Parameter Rating AV DD to AGND, DGND −0.3V to 48V AV SS to AGND, DGND +0.3 V to −48 V AV DD to AV SS -0.3V to 60V DV CC to AGND, DGND −0.3 V to +7 V Digital Inputs to AGND, DGND −0.3 V to DV CC + 0.3 V or 7 V(whichever is less)Digital Outputs to AGND, DGND −0.3 V to DV CC + 0.3 V or 7V(whichever is less)REFIN/REFOUT to AGND, DGND −0.3 V to +7 V V OUT to AGND, DGND AV SS to AV DD I OUT to AGND, DGND −0.3V to AV DD AGND to DGND -0.3V to +0.3V Operating Temperature Range Industrial −40°C to +851°C Storage Temperature Range −65°C to +150°C Junction Temperature (T J max) 125°C 24-Lead TSSOP Package θJA Thermal Impedance 42°C/W 40-Lead LFCSP Package θJA Thermal Impedance 28°C/W Power Dissipation (T J max – T A )/ θJA Lead Temperature JEDEC Industry StandardSoldering J-STD-020Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.ESD CAUTION1Power dissipated on chip must be de-rated to keep junction temperature below 125°C. Assumption is max power dissipation condition is sourcing 24mA into Ground from AV DD with a 3mA on-chip current.PIN CONFIGURATION AND FUNCTION DESCRIPTIONSAGND SDOAV SSSENSE GNDLATCH CLEAR CLEAR SELECT REFIN SELECT SCLK SDIN GND R SETOUTBOOST C COMP1REFOUT DV CC C COMP2I OUTSENSEAV DDDV CCD G N G N A V S CA V S SA V D D N CN CV S E N S EV C CNCNC DV CC SELECT V S E N S EO U TBOOST C COMP1C COMP2I OUT N R S E NC A G N CN N R E F I R E F O U CAP2CAP1Figure 5. TSSOP Pin ConfigurationFigure 6. LFCSP Pin ConfigurationTSSOP Pin No. LFCSP Pin No. Mnemonic Descriptionoutputpin.19 26 I OUT Current20 27 BOOSTOptional external transistor connection. Connecting an external transistor will reducethe power dissipated in the AD5422. Refer to the features section.N/A 28 CAP1 Connection for optional output filtering capacitor. Refer to Features section.N/A 29 CAP2 Connection for optional output filtering capacitor. Refer to Features section.21 32 V OUT Buffered Analog Output Voltage. The output amplifier is capable of directly driving a 2kΩ, 2000 pF load.22 33 +V SENSE Sense connection for the positive voltage output load connection.23 34 -V SENSE Sense connection for the negative voltage output load connection.24 36 AV DD Positive Analog Supply Pin. Voltage ranges from 10.8V to 60V.Paddle Paddle AV SS Negative Analog Supply Pin. Voltage ranges from –3 V to –24 V. This pin can beconnected to 0V if output voltage range is unipolar.TYPICAL PERFORMANCE CHARACTERISTICSVOLTAGE OUTPUTFigure 7. Integral Non Linearity Error vs DAC Code (Four Traces)Figure 8. Differential Non Linearity Error vs. DAC Code (Four Traces)Figure 9. Total Unadjusted Error vs. DAC Code (Four Traces)Figure 10. Integral Non Linearity vs. Temperature (Four Traces)Figure 11. Differential Non Linearity vs. Temperature (Four Traces)Figure 12. Integral Non Linearity vs. Supply Voltage (Four Traces)Figure 13.Differential Non Linearity Error vs. Supply Voltage (Four Traces)Figure 14. Integral Non Linearity Error vs. Reference Voltage (Four traces)Figure 15. Differential Non Linearity Error vs. Reference Voltage (Four Traces)Figure 16. Total Unadjusted Error vs.Reference Voltage (Four Traces)Figure 17. Total Unadjusted Error vs. Supply Voltage (Four Traces)Figure 18. Offset Error vs.TemperatureFigure 19. Bipolar Zero Error vs. TemperatureFigure 20. Gain Error vs. TemperatureFigure 21. Source and Sink Capability of Output AmplifierFull-Scale Code LoadedFigure 22. Source and Sink Capability of Output AmplifierZero-Scale LoadedFigure 23.Full-Scale Positive StepFigure 24. Full-Scale Negative StepFigure 25. Digital-to-Analog Glitch EnergyFigure 26. Peak-to-Peak Noise (0.1Hz to 10Hz Bandwidth)Figure 27. Peak-to-Peak Noise (100kHz Bandwidth)Figure 28. V OUT vs. Time on Power-upFigure 29. V OUT vs, Time on Output EnabledTYPICAL PERFORMANCE CHARACTERISTICS CURRENT OUTPUTFigure 30. Integral Non Linearity vs. CodeFigure 31.Differential Non Linearity vs. CodeFigure 32. Total Unadjusted Error vs. CodeFigure 33. Integral Non Linearity vs. TemperatureFigure 34. Differential Non Linearity vs. TemperatureFigure 35. Integral Non Linearity vs. SupplyFigure 36. Differential Non Linearity vs. Supply VoltageFigure 37. Integral Non Linearity vs. Reference VoltageFigure 38. Differential Non Linearity vs. Reference VoltageFigure 39. Total Unadjusted Error vs. Reference VoltageFigure 40. Total Unadjusted Error vs. Supply VoltageFigure 41. Offset Error vs. TemperatureFigure 42. Gain Error vs. TemperatureFigure 43. Voltage Compliance vs. TemperatureFigure 44. I OUT vs. Time on Power-upFigure 45. I OUT vs. Time on Output EnabledTYPICAL PERFORMANCE CHARACTERISTICS GENERALFigure 46. DI CC vs.Logic Input VoltageFigure 47. AI DD /AI SS vs AV DD /AV SSFigure 48. AI DD vs AV DDFigure 49. DVCC Output Voltage vs. DI CC Load CurrentFigure 50. Refout Turn-on TransientFigure 51. Refout Output Noise (0.1Hz to 10Hz Bandwidth)Figure 52. Refout Output Noise (100kHz Bandwidth)Figure 53. Refout Line TransientFigure 54. Refout Load TransientFigure 55. Refout Histogram of Thermal HysteresisFigure 56. Refout Voltage vs. Load CurrentTERMINOLOGYRelative Accuracy or Integral Nonlinearity (INL)For the DAC, relative accuracy, or integral nonlinearity (INL), is a measure of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function. A typical INL vs. code plot can be seen in Figure 7. Differential Nonlinearity (DNL)Differential nonlinearity (DNL) is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of ±1 LSB maximum ensures monotonicity. This DAC is guaranteed monotonic by design. A typical DNL vs. code plot can be seen in Figure 10.MonotonicityA DAC is monotonic if the output either increases or remains constant for increasing digital input code. The AD5724R/AD5734R/AD5754R are monotonic over their full operating temperature range.Bipolar Zero ErrorBipolar zero error is the deviation of the analog output from the ideal half-scale output of 0 V when the DAC register is loaded with 0x8000 (straight binary coding) or 0x0000 (twos complement coding). A plot of bipolar zero error vs. temperature can be seen in Table TBD.Bipolar Zero TCBipolar zero TC is a measure of the change in the bipolar zero error with a change in temperature. It is expressed in ppm FSR/°C.Full-Scale ErrorFull-Scale error is a measure of the output error when full-scale code is loaded to the DAC register. Ideally, the output should be full-scale − 1 LSB. Full-scale error is expressed in percent offull-scale range (% FSR).Negative Full-Scale Error/Zero-Scale ErrorNegative full-scale error is the error in the DAC output voltage when 0x0000 (straight binary coding) or 0x8000 (twos complement coding) is loaded to the DAC register. Ideally, the output voltage should be negative full-scale− 1 LSB. A plot of zero-scale error vs. temperature can be seen in Table TBD Zero-Scale TCThis is a measure of the change in zero-scale error with a change in temperature. Zero-scale error TC is expressed in ppm FSR/°C. Output Voltage Settling TimeOutput voltage settling time is the amount of time it takes for the output to settle to a specified level for a full-scale input change. A plot of settling time can be seen in Table TBD Slew RateThe slew rate of a device is a limitation in the rate of change of the output voltage. The output slewing speed of a voltage-output D/A converter is usually limited by the slew rate of the amplifier used at its output. Slew rate is measured from 10% to 90% of the output signal and is given in V/µs.Gain ErrorThis is a measure of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from ideal expressed in % FSR. A plot of gain error vs. temperature can be seen in Table TBDGain TCThis is a measure of the change in gain error with changes in temperature. Gain Error TC is expressed in ppm FSR/°C. Total Unadjusted ErrorTotal unadjusted error (TUE) is a measure of the output error taking all the various errors into account, namely INL error, offset error, gain error, and output drift over supplies, temperature, and time. TUE is expressed in % FSR.Current Loop Voltage ComplianceThe maximum voltage at the I OUT pin for which the output currnet will be equal to the programmed value.Power-On Glitch EnergyPower-on glitch energy is the impulse injected into the analog output when the AD5422 is powered-on. It is specified as the area of the glitch in nV-sec. See Table TBDDigital-to-Analog Glitch ImpulseDigital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state, but the output voltage remains constant. It is normally specified as the area of the glitch in nV-sec and is measured when the digital input code is changed by 1 LSB at the major carry transition (0x7FFF to 0x8000). See Table TBDGlitch Impulse Peak AmplitudeGlitch impulse peak amplitude is the peak amplitude of the impulse injected into the analog output when the input code in the DAC register changes state. It is specified as the amplitude of the glitch in mV and is measured when the digital input code is changed by 1 LSB at the major carry transition (0x7FFF to0x8000). See Table TBD.Digital FeedthroughDigital feedthrough is a measure of the impulse injected into the analog output of the DAC from the digital inputs of the DAC, but is measured when the DAC output is not updated. It is specified in nV-sec and measured with a full-scale code change on the data bus.Power Supply Rejection Ratio (PSRR)PSRR indicates how the output of the DAC is affected by changes in the power supply voltage.Reference TCReference TC is a measure of the change in the reference output voltage with a change in temperature. It is expressed in ppm/°C. Line RegulationLine regulation is the change in reference output voltage due to a specified change in supply voltage. It is expressed in ppm/V. Load RegulationLoad regulation is the change in reference output voltage due to a specified change in load current. It is expressed in ppm/mA. Thermal HysteresisThermal hysteresis is the change of reference output voltage after the device is cycled through temperatures from +25°C to −40°C to +85°C and back to +25°C. This is a typical value from a sample of parts put through such a cycle. See Table TBDfor a histogram of thermal hysteresis.TCOOHYSOVVV__C)25(−°=6__10C)25(C)25()(×°−°=OTCOOHYSO VVVppmVwhere:V O(25°C) = V O at 25°CV O_TC = V O at 25°C after temperature cycleTHEORY OF OPERATIONThe AD5422 is a precision digital to current loop and voltage output converter designed to meet the requirements of industrial process control applications. It provides a high precision, fully integrated, low cost single-chip solution for generating current loop and unipolar/bipolar voltage outputs. The current ranges available are; 0 to 20mA, 0 to 24mA and 4 to 20mA, the voltage ranges available are; 0 to 5V , ±5V , 0 to 10V and ±10V , the current and voltage outputs are available onseparate pins and only one is active at any one time. The desired output configuration is user selectable via the CONTROL register.ARCHITECTUREThe DAC core architecture of the AD5422 consists of two matched DAC sections. A simplified circuit diagram is shown in Figure 57. The 4 MSBs of the 16-bit data word are decoded to drive 15 switches, E1 to E15. Each of these switches connects 1 of 15 matched resistors to either ground or the reference buffer output. The remaining 12 bits of the data-word drive switches S0 to S11 of a 12-bit voltage mode R-2R ladder network.V REFV OUT12-BIT R-2R LADDE RFOUR MSBs DECODED INTO 15 EQUAL SEGMENTSFigure 57. DAC Ladder StructureThe voltage output from the DAC core is either converted to a current (see diagram, Figure 58) which is then mirrored to the supply rail so that the application simply sees a current source output with respect to ground or it is buffered and scaled to output a software selectable unipolar or bipolar voltage range (See diagram, Figure 59). The current and voltage are output onseparate pins and cannot be output simultaneously.I OUTFigure 58. Voltage to Current conversion circuitryREFINL1Figure 59. Voltage OutputVoltage Output AmplifierThe voltage output amplifier is capable of generating both unipolar and bipolar output voltages. It is capable of driving a load of 2 kΩ in parallel with 1 µF to AGND. The source and sink capabilities of the output amplifier can be seen in Figure TBD. The slew rate is 1 V/µs with a full-scale settling time of 10 µs, (10V step). Figure 59 shows the voltage output drving a load, R L on top of a common mode voltage of up to ±3V .In output module applications where a cable could possibly become disconnected from +V SENSE resulting in the amplifier loop being broken and most probably resulting in largedestructive voltages on V OUT , a resistor, R 1, of value 2k Ω to 5k Ω should be included as shown to ensure the amplifier loop is kept closed.Driving Large Capacitive LoadsThe voltage output amplifier is capable of driving capacitive loads of up to 1uF with the addition of a non-polarised 4nF compensation capacitor between the C COMP1 and C COMP2 pins. Without the compensation capacitor, up to 20nF capacitive loads can be driven.Reference BuffersThe AD5422 can operate with either an external or internal reference. The reference input has an input range of 4 V to 5 V , 5 V for specified performance. This input voltage is then buffered before it is applied to the DAC.SERIAL INTERFACEThe AD5422 is controlled over a versatile 3-wire serial interface that operates at clock rates up to 30 MHz. It is compatible with SPI®, QSPI™, MICROWIRE™, and DSP standards.Input Shift RegisterThe input shift register is 24 bits wide. Data is loaded into the device MSB first as a 24-bit word under the control of a serial clock input, SCLK. Data is clocked in on the rising edge of SCLK. The input register consists of 8 control bits and 16 data bits as shown in Table 7. The 24 bit word is unconditionally latched on the rising edge of LATCH. Data will continue to be clocked in irrespective of the state of LATCH, on the rising edge of LATCH the data that is present in the input register will be latched, in other words the last 24 bits to be clocked in before。

Emulex CN4052S 和 CN4054S 10Gb VFA5.2 适配器商品说明说明书

Emulex CN4052S and CN4054S 10Gb VFA5.2 Adapters for Flex SystemProduct GuideThe CN4054S 4-port and CN4052S 2-port 10Gb Virtual Fabric Adapters are VFA5.2 adapters that are supported on ThinkSystem and Flex System compute nodes.The CN4052S can be divided into up to eight virtual NIC (vNIC) devices per port (for a total of 16 vNICs) and the CN4054S can be divided in to four vNICs (for a total of 16 vNICs). Each vNIC can have flexible bandwidth allocation. These adapters also feature RDMA over Converged Ethernet (RoCE) capability, and support iSCSI, and FCoE protocols, either as standard or with the addition of a Features on Demand (FoD) license upgrade.The adapters are shown in the following figure. The CN4054S and CN4052S look the same.Figure 1. Flex System CN4054S and CN4052S 10Gb Virtual Fabric AdaptersDid you know?The CN4054S and CN4052S are based on the new Emulex XE100-P2 "Skyhawk P2" ASIC which enables better performance, especially with the new RDMA over Converged Ethernet v2 (RoCE v2) support. In addition, these adapters are supported by Lenovo XClarity Administrator, which allows you to deploy adapter settings easier and incorporate the adapters in configuration patterns.The CN4052S adapter now supports 8 vNICs per port using UFP or vNIC2 and with adapter firmware 10.6 or later. This means a total of 16 vNICs are supported. The CN4054S still supports 4 vNICs per port.Click here to check for updatesIn pNIC mode, an adapter with the FoD upgrade applied operates in traditional Converged Network Adapter (CNA) mode with four ports (CN4054S) or two ports (CN4052S) of Ethernet and four ports (CN4054S) or two ports (CN4052S) of iSCSI or FCoE available to the operating system.Server supportThe following table lists the ThinkSystem and Flex System compute nodes that support the adapters. Table 2. Support for Flex System compute nodesPartnumber DescriptionAdapters - ThinkSystem and Flex System compute nodes01CV780Flex System CN4052S 2-port 10Gb Virtual FabricAdapter AdvancedN N Y Y Y Y Y Y Y Y00AG540Flex System CN4052S 2-port 10Gb Virtual FabricAdapterN N Y Y Y N Y Y Y Y00AG590Flex System CN4054S 4-port 10Gb Virtual FabricAdapterY Y Y Y Y Y Y Y Y Y Features on Demand upgrades - Flex System compute nodes only00JY804Flex System CN4052 Virtual Fabric Adapter SWUpgrade (FoD)Y Y Y Y Y Y Y N N N00AG594Flex System CN4054S 4-port 10Gb Virtual Fabric Adapter SW Upgrade (FoD)Y Y Y Y Y Y Y N N N x24(8737,E5-26v2)x24(7162)x24M5(9532,E5-26v3)x24M5(9532,E5-26v4)x44(7167)x88/x48/x28X6(793)x28/x48/x88X6(7196)SN55(7X16)SN85(7X15)SN55V2(7Z69)I/O module supportThese adapters can be installed in any I/O adapter slot of a supported Flex System compute node. One or two compatible 1 Gb or 10 Gb I/O modules must be installed in the corresponding I/O bays in the chassis. The following table lists the switches that are supported. When connected to the 1 Gb switch, the adapter will operate at 1 Gb speeds. When connected to the 40 Gb switch, the adapter will operate at 10 Gb speeds.To maximize the number of adapter ports usable, you may also need to order switch upgrades to enable additional ports. Alternatively, for CN4093, EN4093R, and SI4093 switches, you can use Flexible Port Mapping (FPM), a feature of Networking OS 7.8 or later, that allows you to minimize the number of upgrades needed.See the Product Guides for the Flex System switches for more details about switch upgrades and FPM: https:///servers/blades/networkmoduleThe table below specifies how many ports the adapters contain. For the CN4054S, to enable all 4 adapter ports, either upgrade the switch or use Flexible Port Mapping. Switches should be installed in pairs to maximize the number of ports enabled and to provide redundant network connections.Table 3. I/O modules supportedPartnumber Description CN4052Sports†CN4054Sports†4SG7A08868Lenovo ThinkSystem NE2552E Flex Switch2400FM514Lenovo Flex System Fabric EN4093R 10Gb Scalable Switch24**00FM510Lenovo Flex System Fabric CN4093 10Gb Converged Scalable Switch24**00FE327Lenovo Flex System SI4091 10Gb System Interconnect Module2200FM518Lenovo Flex System Fabric SI4093 System Interconnect Module24**90Y9346Flex System EN6131 40Gb Ethernet Switch2288Y6043Flex System EN4091 10Gb Ethernet Pass-thru2249Y4294Flex System EN2092 1Gb Ethernet Scalable Switch24**94Y5350Cisco Nexus B22 Fabric Extender for Flex System2200D5823*Flex System Fabric CN4093 10Gb Converged Scalable Switch24**95Y3309*Flex System Fabric EN4093R 10Gb Scalable Switch24**49Y4270*Flex System Fabric EN4093 10Gb Scalable Switch24**95Y3313*Flex System Fabric SI4093 System Interconnect Module24**94Y5212*Flex System EN4023 10Gb Scalable Switch24*** Withdrawn from marketing† This is the number of adapter ports that will be enabled per adapter, and requires that two switches be installed in the chassis.** The use of 4 ports will require either a switch upgrade to enable additional ports or the use of Flexible Port Mapping to reconfigure the active portsThe following table shows the connections between adapters installed in the compute nodes and the switch bays in the chassis.Table 4. Adapter to I/O bay correspondenceI/O adapter slot in the server Port on the adapter Corresponding I/O module bayin the chassisSlot 1Port 1Module bay 1Port 2Module bay 2Port 3*Module bay 1Port 4*Module bay 2 Slot 2Port 1Module bay 3Port 2Module bay 4Port 3*Module bay 3Port 4*Module bay 4Slot 3(full-wide compute nodes only)Port 1Module bay 1 Port 2Module bay 2 Port 3*Module bay 1 Port 4*Module bay 2Slot 4(full-wide compute nodes only)Port 1Module bay 3 Port 2Module bay 4 Port 3*Module bay 3 Port 4*Module bay 4* Ports 3 and 4 (CN4054S only) require Upgrade 1 of the selected switch, where applicable. 14-port modules such as the EN4091 Pass-thru, SI4091 switch, and Cisco B22 only support ports 1 and 2 (and only when two I/O modules are installed).The following figure shows the internal layout of the CN4054S, with how the adapter ports are routed to the I/O module internal ports.Note: INTD1 is not available on any currently shipping Flex System I/O modules.Figure 2. Internal layout of the CN4054S adapter portsThe following figure shows the internal layout of the CN4052S, and how the adapter ports are routed to the I/O module internal ports.Note: INTD1 is not available on any currently shipping Flex System I/O modules.Figure 3. Internal layout of the CN4052S adapter portsThe connections between the adapters installed in the compute nodes to the switch bays in the chassis are shown diagrammatically in the following figure. The figure shows half-wide servers (such as the x240 M5 with two adapters) and full-wide servers (such as the x440 with four adapters).Figure 4. Logical layout of the interconnects between I/O adapters and I/O modulesSUSE Linux Enterprise Server 12 SP2N N N Y Y Y Y Y SUSE Linux Enterprise Server 12 SP2 with Xen N N N Y Y Y Y Y SUSE Linux Enterprise Server 12 SP3N N N Y Y Y Y Y SUSE Linux Enterprise Server 12 SP3 with Xen N N N Y Y Y Y Y SUSE Linux Enterprise Server 12 SP4N Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP4 with Xen N Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP5Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP5 with Xen Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 15N Y Y Y Y Y Y N SUSE Linux Enterprise Server 15 SP1N Y Y Y Y Y Y N SUSE Linux Enterprise Server 15 SP1 with Xen N Y Y Y Y Y Y N SUSE Linux Enterprise Server 15 SP2Y Y Y Y Y Y Y N SUSE Linux Enterprise Server 15 SP2 with Xen Y Y Y Y Y Y Y N SUSE Linux Enterprise Server 15 SP3Y Y Y Y Y N N N SUSE Linux Enterprise Server 15 SP3 with Xen Y Y Y Y Y N N N SUSE Linux Enterprise Server 15 SP4Y Y Y Y Y N N N SUSE Linux Enterprise Server 15 SP4 with Xen Y Y Y Y Y N N N SUSE Linux Enterprise Server 15 SP5Y Y Y Y Y N N N SUSE Linux Enterprise Server 15 SP5 with Xen Y Y Y Y Y N N N SUSE Linux Enterprise Server 15 with Xen N Y Y Y Y Y Y N Ubuntu 18.04.5 LTSY N N N N N N N VMware vSphere Hypervisor (ESXi) 5.5N N N N N Y N Y VMware vSphere Hypervisor (ESXi) 6.0 U3N N N Y Y Y N Y VMware vSphere Hypervisor (ESXi) 6.5N N N Y Y Y Y N VMware vSphere Hypervisor (ESXi) 6.5 U1N N N Y Y Y Y N VMware vSphere Hypervisor (ESXi) 6.5 U2N Y Y Y Y Y Y N VMware vSphere Hypervisor (ESXi) 6.5 U3N Y Y Y Y Y Y N VMware vSphere Hypervisor (ESXi) 6.7N N N Y Y Y N N VMware vSphere Hypervisor (ESXi) 6.7 U1N Y Y Y Y Y N N VMware vSphere Hypervisor (ESXi) 6.7 U2N Y Y Y Y Y N N VMware vSphere Hypervisor (ESXi) 6.7 U3Y Y Y Y Y Y N N VMware vSphere Hypervisor (ESXi) 7.0N Y Y Y Y N N N VMware vSphere Hypervisor (ESXi) 7.0 U1N Y Y Y Y N N N VMware vSphere Hypervisor (ESXi) 7.0 U2Y Y Y Y Y N N NOperating systemsS N 550 V 2S N 550 (X e o n G e n 2)S N 850 (X e o n G e n 2)S N 550 (X e o n G e n 1)S N 850 (X e o n G e n 1)x 240 M 5 (9532)x 280/x 480/x 880 X 6 (719x 440 (7167)VMware vSphere Hypervisor (ESXi) 7.0 U3Y Y Y Y Y N N NOperating systemsTable 6. Operating system support for Flex System CN4054S 4-port 10Gb Virtual Fabric Adapter, 00AG590Operating systemsMicrosoft Windows Server 2012N N N N N Y Y Y N Y Y Y Microsoft Windows Server 2012 R2N N N Y Y Y Y Y N Y Y Y Microsoft Windows Server 2016Y Y Y Y Y Y N Y N Y Y N Microsoft Windows Server 2019Y Y Y Y Y N N Y N N N N Microsoft Windows Server 2022Y Y Y Y Y N N N N N N N Microsoft Windows Server version 1709N N N Y Y N N Y Y N Y N Microsoft Windows Server version 1803N N N Y N N N N N N N N Red Hat Enterprise Linux 6.10N N N Y Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 6.9N N N Y Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 7.3N N N Y Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 7.4N N N Y Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 7.5N N N Y Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 7.6N Y Y Y Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 7.7N Y Y Y Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 7.8N Y Y Y Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 7.9Y Y Y Y Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 8.0N Y Y Y Y N N N N N N N Red Hat Enterprise Linux 8.1N Y Y Y Y N N N N N N N Red Hat Enterprise Linux 8.2Y Y Y Y Y N N N N N N N Red Hat Enterprise Linux 8.3Y Y Y Y Y N N N N N N N Red Hat Enterprise Linux 8.4Y Y Y Y Y N N N N N N N Red Hat Enterprise Linux 8.5Y Y Y Y Y N N N N N N N Red Hat Enterprise Linux 8.6Y Y Y Y Y N N N N N N N Red Hat Enterprise Linux 8.7Y Y Y Y Y N N N N N N NS N 550 V 2S N 550 (X e o n G e n 2)S N 850 (X e o n G e n 2)S N 550 (X e o n G e n 1)S N 850 (X e o n G e n 1)x 240 M 5 (9532)x 280/x 480/x 880 X 6 (719x 440 (7167)S N 550 V 2S N 550 (X e o n G e n 2)S N 850 (X e o n G e n 2)S N 550 (X e o n G e n 1)S N 850 (X e o n G e n 1)x 240 (8737, E 5 v 2)x 240 (7162)x 240 M 5 (9532)x 280/x 480/x 880 X 6 (7196)x 280/x 480/x 880 X 6 (7903)x 440 (7167)x 440 (7917)SUSE Linux Enterprise Server 11 SP4N N N Y Y Y Y Y N Y Y Y SUSE Linux Enterprise Server 11 SP4 with Xen N N N Y Y Y Y Y N Y Y Y SUSE Linux Enterprise Server 11 for x86N N N N N N Y N N N Y N SUSE Linux Enterprise Server 12 SP2N N N Y Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP2 with Xen N N N Y Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP3N N N Y Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP3 with Xen N N N Y Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP4N Y Y Y Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP4 with Xen N Y Y Y Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP5Y Y Y Y Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP5 with Xen Y Y Y Y Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 15N Y Y Y Y N N Y Y N N N SUSE Linux Enterprise Server 15 SP1N Y Y Y Y N N Y Y N N N SUSE Linux Enterprise Server 15 SP1 with Xen N Y Y Y Y N N Y Y N N N SUSE Linux Enterprise Server 15 SP2Y Y Y Y Y N N Y Y N N N SUSE Linux Enterprise Server 15 SP2 with Xen Y Y Y Y Y N N Y Y N N N SUSE Linux Enterprise Server 15 SP3Y Y Y Y Y N N N N N N N SUSE Linux Enterprise Server 15 SP3 with Xen Y Y Y Y Y N N N N N N N SUSE Linux Enterprise Server 15 SP4Y Y Y Y Y N N N N N N N SUSE Linux Enterprise Server 15 SP4 with Xen Y Y Y Y Y N N N N N N N SUSE Linux Enterprise Server 15 SP5Y Y Y Y Y N N N N N N N SUSE Linux Enterprise Server 15 SP5 with Xen Y Y Y Y Y N N N N N N N SUSE Linux Enterprise Server 15 with Xen N Y Y Y Y N N Y Y N N N Ubuntu 18.04.5 LTSY N N N N N N N N N N N VMware vSphere Hypervisor (ESXi) 5.5N N N N N Y Y Y N Y Y Y VMware vSphere Hypervisor (ESXi) 6.0 U3N N N Y Y Y Y Y Y Y Y Y VMware vSphere Hypervisor (ESXi) 6.5N N N Y Y Y N Y Y Y N N VMware vSphere Hypervisor (ESXi) 6.5 U1N N N Y Y Y N Y Y Y N N VMware vSphere Hypervisor (ESXi) 6.5 U2N Y Y Y Y Y N Y Y Y N N VMware vSphere Hypervisor (ESXi) 6.5 U3N Y Y Y Y Y N Y Y Y N N VMware vSphere Hypervisor (ESXi) 6.7N N N Y Y N N Y N N N N VMware vSphere Hypervisor (ESXi) 6.7 U1N Y Y Y Y N N Y N N N N VMware vSphere Hypervisor (ESXi) 6.7 U2N Y Y Y Y N N Y N N N N VMware vSphere Hypervisor (ESXi) 6.7 U3Y Y Y Y Y N N Y N N N NOperating systemsS N 550 V 2S N 550 (X e o n G e n 2)S N 850 (X e o n G e n 2)S N 550 (X e o n G e n 1)S N 850 (X e o n G e n 1)x 240 (8737, E 5 v 2)x 240 (7162)x 240 M 5 (9532)x 280/x 480/x 880 X 6 (719x 280/x 480/x 880 X 6 (790x 440 (7167)x 440 (7917)VMware vSphere Hypervisor (ESXi) 7.0N Y Y Y Y N N N N N N N VMware vSphere Hypervisor (ESXi) 7.0 U1N Y Y Y Y N N N N N N N VMware vSphere Hypervisor (ESXi) 7.0 U2Y Y Y Y Y N N N N N N N VMware vSphere Hypervisor (ESXi) 7.0 U3Y Y Y Y Y N N N N N N NOperating systemsTable 7. Operating system support for Flex System CN4052S 2-port 10Gb Virtual Fabric Adapter Advanced,01CV780Operating systemsMicrosoft Windows Server 2012N N N N N Y Y Y Y Microsoft Windows Server 2012 R2N N N Y Y Y Y Y Y Microsoft Windows Server 2016Y Y Y Y Y Y Y Y N Microsoft Windows Server 2019Y Y Y Y Y Y N N N Microsoft Windows Server 2022Y Y Y Y Y N N N N Microsoft Windows Server version 1709N N N Y Y Y Y N N Microsoft Windows Server version 1803N N N Y N N N N N Red Hat Enterprise Linux 6.10N N N Y Y Y Y Y Y Red Hat Enterprise Linux 6.9N N N Y Y Y Y Y Y Red Hat Enterprise Linux 7.3N N N Y Y Y Y Y Y Red Hat Enterprise Linux 7.4N N N Y Y Y Y Y Y Red Hat Enterprise Linux 7.5N N N Y Y Y Y Y Y Red Hat Enterprise Linux 7.6N Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 7.7N Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 7.8N Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 7.9Y Y Y Y Y Y Y Y Y Red Hat Enterprise Linux 8.0N Y Y Y Y N N N N Red Hat Enterprise Linux 8.1N Y Y Y Y N N N N Red Hat Enterprise Linux 8.2Y Y Y Y Y N N N N Red Hat Enterprise Linux 8.3Y Y Y Y Y N N N NS N 550 V 2S N 550 (X e o n G e n 2)S N 850 (X e o n G e n 2)S N 550 (X e o n G e n 1)S N 850 (X e o n G e n 1)x 240 (8737, E 5 v 2)x 240 (7162)x 240 M 5 (9532)x 280/x 480/x 880 X 6 (719x 280/x 480/x 880 X 6 (790x 440 (7167)x 440 (7917)S N 550 V 2S N 550 (X e o n G e n 2)S N 850 (X e o n G e n 2)S N 550 (X e o n G e n 1)S N 850 (X e o n G e n 1)x 240 M 5 (9532)x 280/x 480/x 880 X 6 (7196)x 280/x 480/x 880 X 6 (7903)x 440 (7917)Red Hat Enterprise Linux 8.4Y Y Y Y Y N N N N Red Hat Enterprise Linux 8.5Y Y Y Y Y N N N N Red Hat Enterprise Linux 8.6Y Y Y Y Y N N N N Red Hat Enterprise Linux 8.7Y Y Y Y Y N N N N SUSE Linux Enterprise Server 11 SP4N N N Y Y Y Y Y Y SUSE Linux Enterprise Server 11 SP4 with Xen N N N Y Y Y Y Y Y SUSE Linux Enterprise Server 11 for x86N N N N N N Y N N SUSE Linux Enterprise Server 12 SP2N N N Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP2 with Xen N N N Y Y N Y Y Y SUSE Linux Enterprise Server 12 SP3N N N Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP3 with Xen N N N Y Y N Y Y Y SUSE Linux Enterprise Server 12 SP4N Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP4 with Xen N Y Y Y Y N Y Y Y SUSE Linux Enterprise Server 12 SP5Y Y Y Y Y Y Y Y Y SUSE Linux Enterprise Server 12 SP5 with Xen Y Y Y Y Y N Y Y Y SUSE Linux Enterprise Server 15N Y Y Y Y Y Y N N SUSE Linux Enterprise Server 15 SP1N Y Y Y Y Y Y N N SUSE Linux Enterprise Server 15 SP1 with Xen N Y Y Y Y Y Y N N SUSE Linux Enterprise Server 15 SP2Y Y Y Y Y Y Y N N SUSE Linux Enterprise Server 15 SP2 with Xen Y Y Y Y Y Y Y N N SUSE Linux Enterprise Server 15 SP3Y Y Y Y Y N N N N SUSE Linux Enterprise Server 15 SP3 with Xen Y Y Y Y Y N N N N SUSE Linux Enterprise Server 15 SP4Y Y Y Y Y N N N N SUSE Linux Enterprise Server 15 SP4 with Xen Y Y Y Y Y N N N N SUSE Linux Enterprise Server 15 SP5Y Y Y Y Y N N N N SUSE Linux Enterprise Server 15 SP5 with Xen Y Y Y Y Y N N N N SUSE Linux Enterprise Server 15 with Xen N Y Y Y Y Y Y N N Ubuntu 18.04.5 LTSY N N N N N N N N VMware vSphere Hypervisor (ESXi) 5.5N N N N N Y Y Y Y VMware vSphere Hypervisor (ESXi) 6.0 U3N N N Y Y Y Y Y Y VMware vSphere Hypervisor (ESXi) 6.5N N N Y Y Y Y Y N VMware vSphere Hypervisor (ESXi) 6.5 U1N N N Y Y Y Y Y N VMware vSphere Hypervisor (ESXi) 6.5 U2N Y Y Y Y Y Y Y N VMware vSphere Hypervisor (ESXi) 6.5 U3N Y Y Y Y Y Y Y NOperating systems S N 550 V 2S N 550 (X e o n G e n 2)S N 850 (X e o n G e n 2)S N 550 (X e o n G e n 1)S N 850 (X e o n G e n 1)x 240 M 5 (9532)x 280/x 480/x 880 X 6 (719x 280/x 480/x 880 X 6 (790x 440 (7917)TrademarksLenovo and the Lenovo logo are trademarks or registered trademarks of Lenovo in the United States, other countries, or both. A current list of Lenovo trademarks is available on the Web athttps:///us/en/legal/copytrade/.The following terms are trademarks of Lenovo in the United States, other countries, or both:Lenovo®Flex SystemServerProven®System x®ThinkSystem®VMready®XClarity®The following terms are trademarks of other companies:Xeon® is a trademark of Intel Corporation or its subsidiaries.Linux® is the trademark of Linus Torvalds in the U.S. and other countries.Microsoft®, Hyper-V®, SQL Server®, SharePoint®, Windows Server®, and Windows® are trademarks of Microsoft Corporation in the United States, other countries, or both.Other company, product, or service names may be trademarks or service marks of others.Emulex CN4052S and CN4054S 10Gb VFA5.2 Adapters for Flex System21。

(产品管理)万能式断路器产品说明书

断路器应按使用说书的要求进行安装,断路器的垂直倾斜度不超过5°。

☆断路器的额定电流见表1表1

壳架等级额定电流Inm(A)

额定电流In( A )

2000

400、630、800、1000、1250、1600、2000

3200

2000、2500、3200

4000

3200、4000

☆断路器的额定短路分断能力及短时耐受电流见表2

◇智能脱扣器

BYW45可提供多种不同功能的智能脱扣器,以满足用户的需求。

正常工作条件

☆周围空气温度

上限值不超过+40℃。

下限值一般不低于-5℃。

24小时的平均值不超过+35℃。

注:①下限值为-10℃或-25℃的工作条件在订货时用户需向本公司申明。

②上限值超过+40℃或下限值低于-25℃的工作条件,用户需与本公司协商。

支持多种开放性通讯协议,便于实现配电控制自动化。

控制器型号选择说明

用途

配电或电机保护

发电机保护△

型号

H型 (通讯型 )

M型 (标准型)

通讯接口:

提供准RS485接口,多协议数据传输功能(内部集成一种通讯协议Modbus协议)

位置锁:

可选设置、本地和遥控三种位置状态

L型 (经济型 )

●功能表功能△

此功能测量和显示:电压、频率、功率因数、有功功率、有功电度

◇具有较高的极限短路分断能力和额定短时耐受电流

断路器采用MCR和模拟脱扣功能,每相触头安装在绝缘小室内,触头系统采用多片触头并联型式的结构,减小了触头系统的惯性,保证了断路器的高分断能力和经受较高的短时耐受电流。

◇操作机构

安装于断路器中央,与主电路隔离;断路器由弹簧储能机构进行闭合操作,闭合速度快。

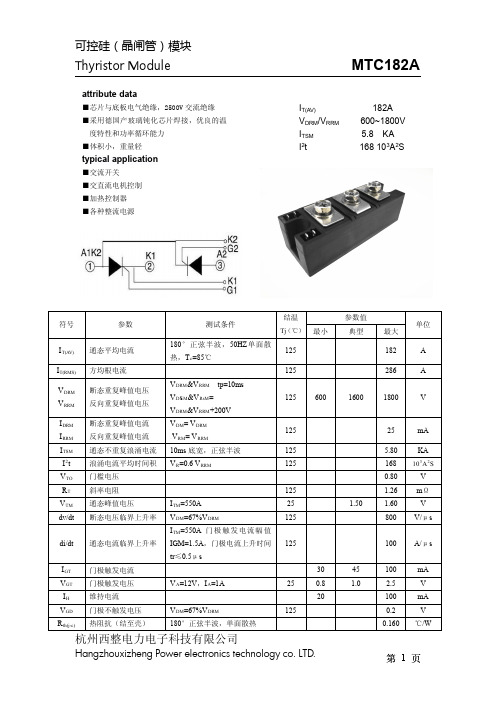

晶闸管模块MTC182A

B

绝缘电压

F mB

B

T sbg B

B

W tB B

Outline

安装扭矩(M5) 安装扭矩(M6) 储存温度 质量(约)

180°正弦半波,单面散热

50HZ , R.M.S , t=1min

IBiso

:1mA

B

(ma

x)

与散热器固定

M234

MTC182A

0.08 ℃/W

2500

V

4.0±15%

5.0±15%

-40

125

205

N·m N·m

℃

g

杭州西整电力电子科技有限公司

Hangzhouxizheng Power electronics technology co. LTD.

第2页

可控硅(晶闸管)模块 Thyristor Module

MTC182A

杭州西整电力电子科技有限公司

Hangzhouxizheng Power electronics technology co. LTD.

可控硅(晶闸管)模块 Thyristor Module

MTC182A

matters needing attention: 1、模块实际负载电流大于 5A 时务必要加装散热器,需提供良好的通风条件。 2、工作环境温度高于 40℃时,应优化散热通风条件。 3、模块工作后会发热,在设备未断电及模块未完全冷却降温之前,严禁用手触摸模块

B

DRM B

B

RBth(j-c)B

热阻抗(结至壳)

180°正弦半波,单面散热

杭州西整电力电子科技有限公司

30

25

0.8

20

125

Hangzhouxizheng Power electronics technology co. LTD.

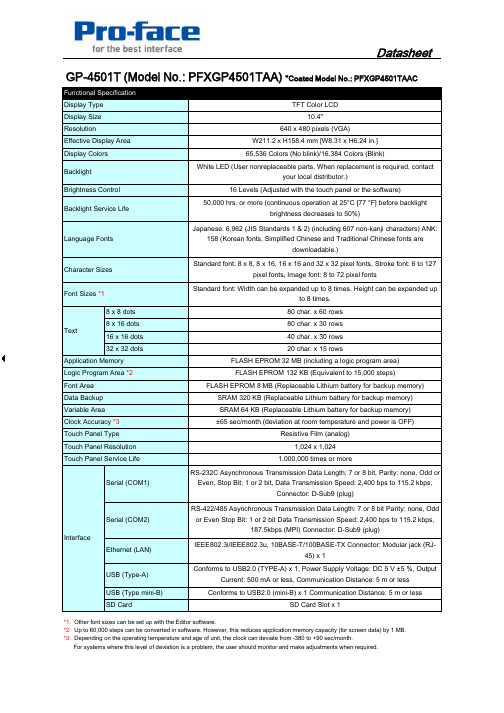

W211.2 TFT Color LCD 10.4英寸商品说明书

40h 30Text Language Fonts 16 Levels (Adjusted with the touch panel or the software)Brightness Control Display Type Display Size Resolution Effective Display Area Backlight Service Life 8 x 8 dots 8 x 16 dots 1616d t 80 char. x 60 rows 80 char. x 30 rows Display Colors Backlight 640 x 480 pixels (VGA)W211.2 x H158.4 mm [W8.31 x H6.24 in.]65,536 Colors (No blink)/16,384 Colors (Blink)White LED (User nonreplaceable parts. When replacement is required, contact your local distributor.)TFT Color LCD 10.4"50,000 hrs. or more (continuous operation at 25°C [77 °F] before backlight brightness decreases to 50%)Japanese: 6,962 (JIS Standards 1 & 2) (including 607 non-kanji characters) ANK:158 (Korean fonts, Simplified Chinese and Traditional Chinese fonts are downloadable.)Character Sizes Standard font: 8 x 8, 8 x 16, 16 x 16 and 32 x 32 pixel fonts, Stroke font: 6 to 127pixel fonts, Image font: 8 to 72 pixel fonts Font Sizes *1Standard font: Width can be expanded up to 8 times. Height can be expanded up to 8 times.GP-4501T (Model No.: PFXGP4501TAA) *Coated Model No.: PFXGP4501TAAC *3: Depending on the operating temperature and age of unit, the clock can deviate from -380 to +90 sec/month.For systems where this level of deviation is a problem, the user should monitor and make adjustments when required.Conforms to USB2.0 (mini-B) x 1 Communication Distance: 5 m or lessSD Card Slot x 140 char. x 30 rows *1: Other font sizes can be set up with the Editor software.*2: Up to 60,000 steps can be converted in software. However, this reduces application memory capacity (for screen data) by 1 MB.Clock Accuracy *3RS-232C Asynchronous Transmission Data Length: 7 or 8 bit, Parity: none, Odd orEven, Stop Bit: 1 or 2 bit, Data Transmission Speed: 2,400 bps to 115.2 kbps,Connector: D-Sub9 (plug)IEEE802.3i/IEEE802.3u, 10BASE-T/100BASE-TX Connector: Modular jack (RJ-45) x 1RS-422/485 Asynchronous Transmission Data Length: 7 or 8 bit Parity: none, Oddor Even Stop Bit: 1 or 2 bit Data Transmission Speed: 2,400 bps to 115.2 kbps,187.5kbps (MPI) Connector: D-Sub9 (plug)20 char. x 15 rows±65 sec/month (deviation at room temperature and power is OFF)SRAM 64 KB (Replaceable Lithium battery for backup memory)Resistive Film (analog)1,024 x 1,0241,000,000 times or more16 x 16 dots 32 x 32 dots Variable Area Conforms to USB2.0 (TYPE-A) x 1, Power Supply Voltage: DC 5 V ±5 %, OutputCurrent: 500 mA or less, Communication Distance: 5 m or lessInterfaceTouch Panel Resolution Touch Panel Type Touch Panel Service Life USB (Type mini-B)SD Card Ethernet (LAN)Serial (COM1)USB (Type-A)Serial (COM2)Data Backup SRAM 320 KB (Replaceable Lithium battery for backup memory)Application Memory FLASH EPROM 32 MB (including a logic program area)Logic Program Area *2FLASH EPROM 132 KB (Equivalent to 15,000 steps)Font Area FLASH EPROM 8 MB (Replaceable Lithium battery for backup memory)Pollution Degree Atmosphere Voltage Endurance Storage Humidity International Safety Standards-20 to 60 °C [-4 to 140 °F]Allowable Voltage Drop In-Rush Current Surrounding Air Temperature Power Consumption 0 to 55 °C [32 to 131 °F]Storage Temperature Rated Input Voltage AC 100 to 240 V Insulation Resistance AC 85 to 264 V 1 cycle or less(Voltage drop interval must be 1 second or more.)30 A or less Input Voltage Limits 100 Vac: 44 VA or less 240 Vac: 58 VA or less DC 500 V, 10 MΩ or more (between charging and FG terminals)AC 1,500 V, 20 mA for 1 min (between charging and FG terminals)10 to 90 % RH (Wet bulb temperature: 39 °C [102.2 °F] or less - no condensation.)IEC/EN61131-2 compliant 147 m/s², X, Y, Z directions for 3 times Vibration Resistance Air Pressure (altitude range)800 to 1,114 hPa (2,000 m above sea level or less)0.1 mg/m³ (10-7 oz/ft³) or less (non-conductive levels)For use in Pollution Degree 2 environment Ambient Humidity Dust Free of corrosive gases IEC/EN61131-2 compliant, 5 to 9 Hz Single amplitude 3.5 mm [0.14 in.], 9 to 150Hz Fixed acceleration: 9.8 m/s², X, Y, Z directions for 10 cycles (approx. 100 min)Concussion Resistance *1:*2:External Dimensions Panel Cut Dimensions *2W259 x H201 mm [W10.2 x H7.91 in.], Panel thickness area: 1.6 to 5 mm [0.06 to0.2 in.]2 kg [4.4 lb] or less (display unit only)Contact Discharge Method: 6 kV (IEC/EN61000-4-2 Level 3)W272.5 x H214.5 x D57 mm [W10.73 x H8.44 x D2.24 in.]Cooling Method Weight Approx.Grounding Functional grounding: Grounding resistance of 100Ω, 2mm² (AWG 14) or thicker wire, or your country's applicable standard. (Same for FG and SG terminals)Structure *1Natural air circulationNoise Voltage: 1,500 Vp-p, Pulse Duration: 1 µs, Rise Time: 1 ns (via noisesimulator)Noise Immunity IP65f NEMA #250 TYPE 4X/13 (on the front panel when properly installed in anenclosure)Electrostatic Discharge Immunity The front face of the GP unit, installed in a solid panel, has been tested using conditions equivalent to the standards shown in thespecification. Even though the GP unit's level of resistance is equivalent to these standards, oils that should have no effect on the GP can possibly harm the unit. This can occur in areas where either vaporized oils are present, or where low viscosity cutting oils are allowed to adhere to the unit for long periods of time. If the GP's front face protection sheet becomes peeled off, these conditions can lead to the ingress of oil into the GP and separate protection measures are suggested. Also, if non-approved oils are present, it may causedeformation or corrosion of the front panel's plastic cover. Therefore, prior to installing the GP unit, be sure to confirm the type of conditions that will be present in the GP's operating environment. If the installation gasket is used for a long period of time, or if the unit and its gasket http://www pro face com/product/hmi/gp4000html Pro face's GP4000Series website Regarding dimensional tolerance, everything +1/-0 mm [+0.04/-0 in.] and R in angle are below R3 [R0.12 in.]./product/hmi/gp4000.html Pro-face's GP4000 Series website Copyright (C) 2011 Digital Electronics Corporation. All rights reserved. Specifications may change without notice.2012.1 Rev.1。

FPC402 四端口口控制器数据手册说明书

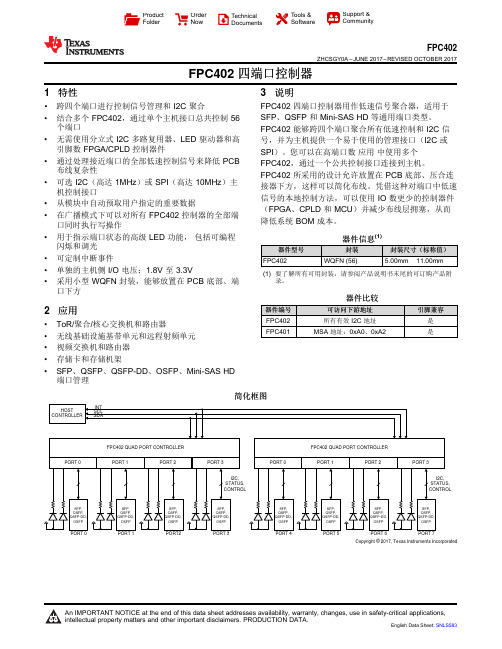

Copyright © 2017, Texas Instruments IncorporatedProduct Folder Order Now Technical Documents Tools &SoftwareSupport &CommunityFPC402ZHCSGY0A –JUNE 2017–REVISED OCTOBER 2017FPC402四端口控制器1特性•跨四个端口进行控制信号管理和I2C 聚合•结合多个FPC402,通过单个主机接口总共控制56个端口•无需使用分立式I2C 多路复用器、LED 驱动器和高引脚数FPGA/CPLD 控制器件•通过处理接近端口的全部低速控制信号来降低PCB 布线复杂性•可选I2C (高达1MHz )或SPI (高达10MHz )主机控制接口•从模块中自动预取用户指定的重要数据•在广播模式下可以对所有FPC402控制器的全部端口同时执行写操作•用于指示端口状态的高级LED 功能,包括可编程闪烁和调光•可定制中断事件•单独的主机侧I/O 电压:1.8V 至3.3V•采用小型WQFN 封装,能够放置在PCB 底部、端口下方2应用•ToR/聚合/核心交换机和路由器•无线基础设施基带单元和远程射频单元•视频交换机和路由器•存储卡和存储机架•SFP 、QSFP 、QSFP-DD 、OSFP 、Mini-SAS HD 端口管理3说明FPC402四端口控制器用作低速信号聚合器,适用于SFP 、QSFP 和Mini-SAS HD 等通用端口类型。

FPC402能够跨四个端口聚合所有低速控制和I2C 信号,并为主机提供一个易于使用的管理接口(I2C 或SPI )。

您可以在高端口数应用中使用多个FPC402,通过一个公共控制接口连接到主机。

FPC402所采用的设计允许放置在PCB 底部、压合连接器下方,这样可以简化布线。

凭借这种对端口中低速信号的本地控制方法,可以使用IO 数更少的控制器件(FPGA 、CPLD 和MCU )并减少布线层拥塞,从而降低系统BOM 成本。

AD8005中文资料

TMIN to TMAX Offset Drift +Input Bias Current TMIN to TMAX –Input Bias Current Input Bias Current Drift (± ) Open-Loop Transimpedance INPUT CHARACTERISTICS Input Resistance Input Capacitance Input Common-Mode Voltage Range Common-Mode Rejection Ratio OUTPUT CHARACTERISTICS Output Voltage Swing Output Current Short Circuit Current POWER SUPPLY Quiescent Current Power Supply Rejection Ratio OPERATING TEMPERATURE RANGE

元器件交易网

a

FEATURES Ultralow Power 400 A Power Supply Current (4 mW on ؎5 VS) Specified for Single Supply Operation High Speed 270 MHz, –3 dB Bandwidth (G = +1) 170 MHz, –3 dB Bandwidth (G = +2) 280 V/ s Slew Rate (G = +2) 28 ns Settling Time to 0.1%, 2 V Step (G = +2) Low Distortion/Noise –63 dBc @ 1 MHz, V O = 2 V p-p –50 dBc @ 10 MHz, VO = 2 V p-p 4.0 nV/√Hz Input Voltage Noise @ 10 MHz Good Video Specifications (RL = 1 k⍀, G = +2) Gain Flatness 0.1 dB to 30 MHz 0.11% Differential Gain Error 0.4؇ Differential Phase Error APPLICATIONS Signal Conditioning A/D Buffer Power-Sensitive, High-Speed Systems Battery Powered Equipment Loop/Remote Power Systems Communication or Video Test Systems Portable Medical Instruments PRODUCT DESCRIPTION

AD404M82VTA-5中文资料