LTC3539EDCB-2-PBF中文资料

LTC3537EUD-PBF中文资料

13537faT YPICAL APPLICATIONF EATURESA PPLICATIONSD ESCRIPTION Synchronous Step-Up DC/DC Converter and 100mA LDOThe L TC ®3537 combines a high effi ciency, 2.2MHz step-upDC/DC converter with an idependent 100mA low dropout regulator (LDO). The step-up converter starts from an input voltage as low as 0.68V and contains an internal 0.4Ω switch and a 0.6Ω synchronous rectifi er that disconnects from the output when disabled in shutdown.A switching frequency of 2.2MH z minimizes solution footprint by allowing the use of tiny, low profi le inductors and ceramic capacitors. The current mode PWM design is internally compensated, reducing external parts count. Fixed frequency switching is maintained until a light load current is sensed, at which point Burst Mode ® operation is engaged to maximize effi ciency. For low noise operation, Burst Mode Operation can be disabled. Anti-ring circuitry reduces EMI by damping the inductor in discontinuous mode. Additional features include a low shutdown current of under 1μA and thermal overload protection.The integrated LDO regulator provides a very low noise, programmable low dropout supply.nHigh Effi ciency Step-Up DC/DC Converter and LDO Step-Upn V IN: 0.68V to 5V , V OUT : 1.5V to 5.25V I OUT : 100mA at 3.3V , V IN >0.8V n 2.2MHz Fixed Frequency Operation n Synchronous Rectifi er with Output Disconnect n Burst Mode Operation (Pin Selectable)Linear LDO Regulator n V IN : 1.8V to 5.5V , V OUT : 0.6V to 5V I OUT : 100mAn 100mV Dropout Voltage at 50mA n 24dB Ripple Rejection at f SW Combinedn Power Good Indicators n Low-Battery Comparator n 30μA I Q n Low Profi le 3mm × 3mm × 0.75mm PackagenWireless Microphonesn Portable Medical instrumentsn Noise Cancelling/Portable Headsets n RF and Audio PowerL , L T , L TC, L TM and Burst Mode are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.Effi ciency and Power Lossvs Load CurrentLOAD CURRENT (mA)0.01E F F I C I E N C Y (%)POWER LOSS (mW)10080906020304070501001000100.111000.01100.13537 TA01b10001100ALKALINE0.8V TO 1.6VV OUTB 3.3V V OLDO 3V23537faP IN CONFIGURATIONA BSOLUTE MAXIMUM RATINGS V INB and V INL Voltage ...................................–0.3V to 6V SW DC Voltage .............................................–0.3V to 6V SW Pulsed (<100ns) Voltage .......................–0.3V to 7V FBB, FBL, PGDB, PGDL Voltage ...................–0.3V to 6V MODE, ENBST , ENLDO Voltage ...................–0.3V to 6V LBI and LBO Voltage ....................................–0.3V to 6V V OUTB , V OLDO ...............................................–0.3V to 6V Operating Temperature (Notes 2, 5) .........–40°C to 85°C Junction Temperature ...........................................125°C Storage Temperature Range ...................–65°C to 125°C(Note 1)161514135678TOP VIEWUD PACKAGE16-LEAD (3mm s 3mm) PLASTIC QFN 9171011124321MODE LBI SGND V INB V INLV OLDO FBL FBBL B OP G N D S WV O U T BP G D BE N B S TP G D LE N L D OT JMAX = 125°C, θJA = 68°C/W (Note 6)EXPOSED PAD (PIN 17) IS GND, MUST BE SOLDERED TO PCBO RDER INFORMATION LEAD FREE FINISH TAPE AND REEL PART MARKING PACKAGE DESCRIPTIONTEMPERATURE RANGE L TC3537EUD#PBFL TC3537EUD#TRPBFLDBD16-Lead (3mm × 3mm) Plastic QFN–40°C to 85°CConsult L TC Marketing for parts specifi ed with wider operating temperature ranges.Consult L TC Marketing for information on non-standard lead based fi nish parts.For more information on lead free part marking, go to: http://www.linear .com/leadfree/ For more information on tape and reel specifi cations, go to: http://www.linear .com/tapeandreel/E LECTRICAL CHARACTERISTICS The l denotes the specifi cations which apply over the full operatingtemperature range, otherwise specifi cations are at T A = 25°C. V INB = 1.2V , V OUTB = 3.3V , unless otherwise noted.SYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITSBoost ConverterV INMIN Minimum Start-Up Voltage I LOAD = 1mA0.680.8V V OUTB Output Voltage Range l 1.5 5.25V V FBB Feedback Voltage l1.1791.21 1.240V I FBB Feedback Input Current 150nA I QSHDN Quiescent Current - Shutdown V ENBST = V ENLDO = 0V , Not Including SW Leakage,V OUTB = 0V0.021μA I QACTIVE Quiescent Current - Active Measured on V OUTB , Nonswitching, MODE = 1.2V , V ENLDO = 0V300500μA I QBURST Quiescent Current - BurstMeasured on V OUTB , FBB >1.24V , MODE = 1.2V , V ENLDO = 0V 15μAI NLEAK NMOS Switch Leakage Current V SW = 5V0.15μA I PLEAKPMOS Switch Leakage Current V SW = 5V , V OUTB = 0V0.110μA33537faE LECTRICAL CHARACTERISTICS The l denotes the specifi cations which apply over the full operatingtemperature range, otherwise specifi cations are at T A = 25°C. V INB = 1.2V , V OUTB = 3.3V , unless otherwise noted.SYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITSR NMOSNMOS Switch On ResistanceV OUTB = 1.8VV OUTB = 3.3V V OUTB = 5V 0.80.40.3ΩΩΩR PMOSPMOS Switch On ResistanceV OUTB = 1.8V V OUTB = 3.3V V OUTB = 5V 10.60.4ΩΩΩI LIM NMOS Current Limit (Note 4)l600750mA t LIMDELAYCurrent Limit Delay Time to Output (Note 3)40ns Max Duty Cycle V FBB = 1.15V l 8792%Min Duty CycleV FBB = 1.3Vl 0%f SW Switching Frequency l 2 2.22.4MHz V ENBSTH ENBST Input High Voltage 0.8V V ENBSTL ENBST Input Low Voltage 0.3V I ENBSTIN ENBST Input Current V ENBST = 5.5V1.5μA V MODEH MODE Input High Voltage 0.8VV MODEL MODE Input Low Voltage 0.3V I MODEIN MODE Input Current V MODE = 5.5V 1.5μA t SS Soft-Start Time 0.5ms V FBLBI LBI Feedback Voltage Falling Threshold 530553575mV LBI Hysteresis Voltage 35mV I LBIIN LBI Input Current V LBI = 1V 1050nA V LBOLOW LBO Voltage Low I LBO = 5mA 200mV I LBOLEAK LBO Leakage Current V LBO = 5.5V 0.011μA V PGDBLOW PGDB Voltage Low I PGDB = 5mA 200mV I PGDBLEAKPGDB Leakage Current V PGDB = 5.5V 0.011μA PGDB T rip Point Voltage V FBB Rising 94% V OUTBPGDB Hysteresis6%SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITSLDO RegulatorV INL Input Voltage Range 1.8 5.5V V OLDO Output Voltage Range I LOAD = 100mAV FBL 5V I OUTMAX Max Output Current l 100mA V FBLFeedback Voltage l590600610mV Line Regulation V INL = 1.8V to 5.5V 0.1%Load RegulationI LOAD = 10mA to 90mA 0.4%V DROPOUTDropout VoltageI O = 50mA 100mVThe l denotes the specifi cations which apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. V INL = 3.3V , V OLDO = 3V , unless otherwise noted.43537faNote 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: The L TC3537 is guaranteed to meet performance specifi cations from 0°C to 85°C. Specifi cations over the –40°C to 85°C operatingtemperature range are assured by design, characterization and correlation with statistical process controls.Note 3: Specifi cation is guaranteed by design and not 100% tested in production.E LECTRICAL CHARACTERISTICS The l denotes the specifi cations which apply over the full operatingtemperature range, otherwise specifi cations are at T A = 25°C. V INL = 3.3V, V OLDO = 3V, unless otherwise noted.SYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITS PSRR Ripple Rejection f = 2.2MHz at I LOAD = 100mA (Note 3)24dB I SHORT Short Circuit Current Limit V OLDO = 0Vl110150mA V ENLDOH ENLDO Input High Voltage 0.8VV ENLDOL ENLDO Input Low Voltage 0.3V I ENLDO ENLDO Input Current V ENLDO = 5.5V 1.5μA V PGDLLOW PGDL Voltage Low I PGDL = 5mA 200mV I PGDLLEAKPGDL Leakage Current V PGDL = 5.5V 0.011μA PGDL T rip Point V FBL Rising96% V OLDOPGDL Hysteresis3%Note 4: Current measurements are made when the output is not switching.Note 5: This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specifi ed maximum operating junction temperature may result in device degradation or failure.Note 6: Failure to solder the exposed backside of the package to the PC board ground plane will result in a thermal resistance much higher than 68°C/W .53537faT YPICAL PERFORMANCE CHARACTERISTICS Effi ciency vs Load Current and V INB for V OUTB = 5VMaximum Output Current vs V INBMinimum Load Resistance During Start-Up vs V INBStart-Up Delay Time vs V INBBurst Mode Threshold Current vs V INBBurst Mode Threshold Current vs V INBEffi ciency vs Load Current andV INB for V OUTB = 1.8VEffi ciency vs Load Current and V INB for V OUTB = 3.3VNo-Load Input Current vs V INBT A = 25°C unless otherwise noted.LOAD CURRENT (mA)0.01E F F I C I E N C Y (%)POWER LOSS (mW)10080906020304070501001000100.111000.01100.13537 G0110001100LOAD CURRENT (mA)0.01E F F I C I E N C Y (%)POWER LOSS (mW)10080906020304070501001000100.111000.01100.13537 G0210001100V INB (V)0.5I I N(μA )100809060304050702010 2.51.53537 G033.5213LOAD CURRENT (mA)0.01E F F I C I E N C Y (%)POWER LOSS (mW)10080906020304070501001000100.111000.01100.13537 G0410001100V INB (V)0.5L O A D C U R R E N T (m A )10008009006002003004007005001000 3.532.51.53537 G054.5214V INB (V)0.8L O A D (Ω)1000100101.61.51.41.31.213537 G061.81.10.91.7V INB(V)1D E L A Y (μs )60302010504004.543.5323537 G0752.51.5V INB (V)0.8L O A D C U R R E N T (m A )35301510525200 1.41.31.213537 G081.51.10.9V INB (V)0.8L O A D C U R R E N T (m A )454035301510525200 1.81.61.43537 G0921.2163537faTYPICAL PERFORMANCE CHARACTERISTICSVoltage Feedback Change vs TemperatureStart-Up Voltage vs TemperatureBurst Mode Quiescent Current vs V OUTBT A = 25°C unless otherwise noted.TEMPERATURE (°C)–40V O L T A G E C H A N G E (%)0.050.00–0.10–0.15–0.20–0.25–0.3040602003537 G1680–20TEMPERATURE (°C)–40V I N B (V )0.800.750.700.650.600.550.5040602003537 G1780–20V OUTB (V)1.8I Q (μA )605030402010 3.84.33.32.83537 G184.82.3R DS(ON) vs V OUTBOscillator Frequency Change vs TemperatureR DS(ON) Change vs TemperatureV OUTB (V)1.5R D S (O N )(Ω)1.00.90.80.70.60.50.30.40.2 3.544.532.53537 G1352TEMPERATURE (°C)–40F R E Q U E N C Y C H A NG E (%)1–1–2–3–440602003537 G1480–20TEMPERATURE (°C)–40R D S (O N ) C H A N G E (%)3020100–10–20–3040602003537 G1580–20Burst Mode Threshold Current vs V INBBurst Mode Threshold Current vs V INBOscillator Frequency Change vs V OUTBV INB (V)0.8L O A D C U R R E N T (m A )6050403020100 2.31.83537 G101.3V INB (V)0.8L O A D C U R R E N T (m A )120100806040200 2.8 3.3 3.82.31.83537 G114.31.3V OUTB (V)1.5F R E Q U E N C Y C H A NG E (%)10–1–2–3–5–4–6 3.54 4.532.53537 G125273537faFixed Frequency SwitchingWaveform and VOUTBRippleBurst Mode WaveformsV OUTB and I INB During Soft-StartT YPICAL PERFORMANCE CHARACTERISTICS Load Current Step Response (from Burst Mode Operation)Load Current Step Response (Fixed Frequency)Load Current Step Response (Fixed Frequency)Load Current Step Response (from Burst Mode Operation)LDO Dropout Voltage vs Load CurrentT A = 25°C unless otherwise noted.LOAD CURRENT (mA)D R O P O U T V O L T A GE (m V )1401201008040602080706050409030203537 G2610010V OUTB 20mV/DIVI L10mA/DIVV INB = 2.4V V OUTB = 3.3V C OUTB = 4.7μF3537 G2010μs/DIVVINB = 2.4V V OUTB = 3.3V C OUT = 4.7μF3537 G22V OUTB 100mV/DIV I LOAD 100mA/DIV 100μs/DIVV INB = 2.4V V OUTB = 3.3V C OUT = 4.7μF3537 G23I LOAD 100mA/DIVV OUTB 100mV/DIV100μs/DIVV INB = 3.6V V OUTB = 5V C OUTB = 4.7μF3537 G24I LOAD 100mA/DIVV OUTB 100mV/DIV100μs/DIVV INB = 3.6V V OUTB = 5V C OUTB = 4.7μF3537 G25I LOAD 100mA/DIVV OUTB 100mV/DIV100μs/DIVV INB = 2.4V V OUTB = 3.3V C OUTB = 4.7μF3537 G19200ns/DIVSW 2V/DIVV OUTB 20mV/DIVENBSTV OUTB 2V/DIVI VINB 200mA/DIVV INB = 1.2V V OUTB = 3.3V C OUTB = 4.7μF I LOAD = 10mA3537 G21100μs/DIVLDO Input Ripple Rejection vs FrequencyFREQUENCY (kHz)A T T E N U A T I O I N (dB )3537 G2960504030201000.010.111010083537faTYPICAL PERFORMANCE CHARACTERISTICSLDO Load Current Step ResponseLDO Load Current Step Response LDO Load Current Step ResponseT A = 25°C unless otherwise noted.V INL = 5V V OLDO = 3V C OUT = 1μF3537 G32I LOAD 100mA/DIV V OLDO 100mV/DIV100μs/DIVV INL = 3.3V V OLDO = 3V C OUT = 1μF3537 G31I LOAD 100mA/DIVV OLDO 100mV/DIV100μs/DIVV INL = 5V V OLDO = 1.8V C OUT = 1μF3537 G33I LOAD 100mA/DIVV OLDO 100mV/DIV100μs/DIVLDO Current Limit vs TemperatureTEMPERATURE (°C)–40L O A D C U R R E N T (%)7654231–10–260402003537 G3080–20P IN FUNCTIONSMODE (Pin 1): Logic Controlled Input for the Auto-Burst Mode Feature.MODE = High: PWM operation with Burst ModeOperationMODE = Low: PWM operation onlyLBI (Pin 2): Low-Battery Comparator Non-Inverting Input. (Comparator enabled with ENBST or ENLDO)SGND (Pin 3): Signal Ground. Provide a short direct PCB path between GND and the (–) side of the input and output capacitors.V INB (Pin 4): Input Supply for the Step-Up Converter. Connect a minimum of 1μF ceramic decoupling capacitor from this pin to ground.PGDB (Pin 5): Power Good Indicator for the Boost Con-verter. This is an open-drain output that sinks current when V OUTB is greater than 94% of the programmed voltage. ENBST (Pin 6): Logic controlled shutdown input for the boost converter.ENBST = High: Normal operationENBST = Low: ShutdownPGDL (Pin 7): Power Good Indicator for the LDO Regulator. This is an open-drain output that sinks current when V OLDO is greater than 96% of the programmed voltage. ENLDO (Pin 8): Logic Controlled Shutdown Input for the LDO Regulator.ENLDO = High: Normal operationENLDO = Low: Shutdown FBB (Pin 9): Feedback Input to the g m Error Amplifi er of the Boost Converter. Connect resistor divider tap to this pin. The output voltage can be adjusted from 1.5V to 5.25V by:V OUTB = 1.2V • [1 + (R2/R1)]FBL (Pin 10): Feedback Input to the g m Error Amplifi er of the LDO. Connect resistor divider tap to this pin. The output voltage can be adjusted from 0.6V (typical) to 5V by:V OLDO = 0.6V • [1 + (R4/R3)]V OLDO (Pin 11): LDO Regulator Output. PCB trace from V OLDO to the output fi lter capacitor (1μF minimum) should be as short and as wide as possible.V INL (Pin 12): Input Supply for the LDO Regulator.V OUTB (Pin 13): Output Voltage Sense Input and Drain of the Internal Synchronous Rectifi er. PCB trace length from V OUTB to the output fi lter capacitor (4.7μF minimum) should be as short and wide as possible.SW (Pin 14): Switch Pin. Connect the inductor between SW and V INB. Keep these PCB trace lengths as short and wide as possible to reduce EMI. If the inductor current falls to zero or ENBST is low, an internal anti-ringing switch is connected from SW to V INB to minimize EMI.PGND (Pin 15): Power Ground. Provide a short direct PCB path between GND and the (–) side of the input and output capacitors.LBO (Pin 16): Low-Battery Comparator Output. (Open-Drain)Exposed Pad (Pin 17): Power Ground. The Exposed Pad must be soldered to the PCB.93537faBLOCK DIAGRAM103537faO PERATIONThe L TC3537 is a 2.2MHz synchronous step-up (boost) converter and LDO regulator housed in a 16-lead 3mm × 3mm QFN package. Included with the ability to startup and operate from inputs less than 0.7V, the L TC3537 features fi xed frequency, current mode PWM control for exceptional line and load regulation.The current mode architecture with adaptive slope com-pensation provides excellent transient load response, requiring minimal output fi ltering. Internal soft-start and loop compensation simplifi es the design process while minimizing the number of external components. With its low R DS(ON) and low gate charge internal N-channel MOSFET switch and P-channel MOSFET synchronous rectifi er, the L TC3537 achieves high effi ciency over a wide range of load currents. Automatic Burst Mode operation maintains high effi ciency at very light loads, reducing the quiescent current to just 30μA. Operation can be best understood by referring to the Block Diagram.LOW VOL TAGE START-UPThe L TC3537 step-up converter includes an independent start-up oscillator designed to operate at an input voltage of 0.68V (typical). Soft-start and inrush current limiting are provided during start-up, as well as normal mode. When either V INB or V OUTB exceeds 1.4V typical, the IC enters normal operating mode. When the output voltage exceeds the input by 0.24V, the IC powers itself from V OUTB instead of V INB. At this point the internal circuitry has no dependency on the V INB input voltage, eliminating the requirement for a large input capacitor. The input voltage can drop as low as 0.5V after start-up is achieved. The limiting factor for the application becomes the availability of the power source to supply suffi cient energy to the output at low voltages, and maximum duty cycle, which is clamped at 92% typical. Note that at low input voltages, small voltage drops due to series resistance become critical, and greatly limit the power delivery capability of the converter.LOW NOISE FIXED FREQUENCY OPERATIONSoft-StartThe L TC3537 contains internal circuitry to provide soft-start operation. The soft-start circuitry slowly ramps the peak inductor current from zero to its peak value of 750mA (typical) in approximately 0.5ms, allowing start-up into heavy loads. The soft-start circuitry is reset in the event of a shutdown command or a thermal shutdown. OscillatorAn internal oscillator sets the switching frequency to 2.2MHz.ShutdownShutdown of the boost converter is accomplished by pulling ENBST below 0.3V and enabled by pulling ENBST above 0.8V. Note that ENBST can be driven above V INB or V OUTB, as long as it is limited to less than the absolute maximum rating.Boost Error Amplifi erThe non-inverting input of the transconductance error amplifier is internally connected to the 1.2V reference and the inverting input is connected to FBB. Clamps limit the minimum and maximum error amp output voltage for improved large-signal transient response. Power converter control loop compensation is provided internally. An exter-nal resistive voltage divider from V OUTB to ground programs the output voltage via FBB from 1.5V to 5.25V.V OUTB=1.2V1+R2R1⎛⎝⎜⎞⎠⎟Boost Current SensingLossless current sensing converts the peak current signal of the N-channel MOSFET switch into a voltage that is summed with the internal slope compensation. The summed signal is compared to the error amplifi er output to provide a peak current control command for the PWM.113537faO PERATIONBoost Current LimitThe current limit comparator shuts off the N-channel MOSFET switch once its threshold is reached. The cur-rent limit comparator delay to output is typically 40ns. Peak switch current is limited to approximately 750mA, independent of input or output voltage, unless V OUTB falls below 0.8V, in which case the current limit is cut in half. Boost Zero Current ComparatorThe zero current comparator monitors the inductor cur-rent to the output and shuts off the synchronous rectifi er when this current reduces to approximately 30mA. This prevents the inductor current from reversing in polarity, improving effi ciency at light loads.Boost Synchronous Rectifi erTo control inrush current and to prevent the inductor cur-rent from running away when V OUTB is close to V INB, the P-channel MOSFET synchronous rectifi er is only enabled when V OUTB > (V INB + 0.24V).Boost Anti-Ringing ControlThe anti-ringing control connects a resistor across the inductor to prevent high frequency ringing on the SW pin during discontinuous current mode operation. Although the ringing of the resonant circuit formed by L and C SW (capacitance on SW pin) is low energy, it can cause EMI radiation.Boost Output DisconnectThe L TC3537 is designed to allow true output disconnect by eliminating body diode conduction of the internal P-channel MOSFET synchronous rectifi er. This allows V OUTB to go to zero volts during shutdown, drawing no current from the input source. It also allows inrush current limit-ing at turn-on, minimizing surge currents seen by the input supply. Note that to obtain the advantages of output disconnect, there cannot be an external Schottky diode connected between the SW pin and V OUTB. The output disconnect feature also allows V OUTB to be pulled high, above the nominal regulation voltage, without any reverse current into the power source connected to V INB.Thermal Overload ProtectionIf the die temperature exceeds 160°C typical, the L TC3537 boost converter will shut down. All switches will be off and the soft-start capacitor will be discharged. The boost converter will be enabled when the die temperature drops by approximately 15°C.BOOST BURST MODE OPERATIONWhen enabled (MODE pin high), the L TC3537 will auto-matically enter Burst Mode operation at light load current and return to fi xed frequency PWM mode when the load increases. Refer to the Typical Performance Characteristics to see the Burst Mode Threshold Current vs V INB. The load current at which Burst Mode operation is entered can be changed by adjusting the inductor value. Raising the inductor value will lower the load current at which Burst Mode operation is entered.In Burst Mode operation, the L TC3537 still switches at a fi xed frequency of 2.2MHz, using the same error amplifi er and loop compensation for peak current mode control. This control method eliminates any output transient when switching between modes. In Burst Mode operation, en-ergy is delivered to the output until it reaches the nominal voltage regulation value, then the L TC3537 transitions to sleep mode where the outputs are off and the L TC3537 consumes only 30μA of quiescent current from V OUTB including the current required to keep the LDO enabled. When the output voltage droops slightly, switching re-sumes. This maximizes effi ciency at very light loads by minimizing switching and quiescent losses. Burst Mode output voltage ripple, which is typically 1% peak-to-peak, can be reduced by using more output capacitance (10μF or greater), or with a small capacitor (10pF to 50pF) con-nected between V OUTB and FBB.As the load current increases, the L TC3537 will automati-cally leave Burst Mode operation. Note that larger output capacitor values may cause this transition to occur at lighter loads. Once the L TC3537 has left Burst Mode operation and returned to normal operation, it will remain there until the output load is reduced below the burst threshold.123537fa133537faOPERATIONBurst Mode operation is inhibited during start-up and soft-start and until V OUTB is at least 0.24V greater than V INB .The L TC3537 will operate at a continuous PWM frequency of 2.2MH z by connecting MODE to GND. At very light loads, the L TC3537 will exhibit pulse-skip operation.LDO REGULATOR OPERATIONThe L TC3537 includes an independent 100mA low dropout linear regulator (LDO). The V INL pin can be connected to an independent source or connected to the output of the boost regulator . An input capacitor on V INL is optional, but it will help to improve transient responses. The LDO willoperate with a V INL down to 1.5V , but specifications are guaranteed with V INL from 1.8V to 5.5V .ShutdownShutdown of the LDO is accomplished by pulling ENLDO below 0.3V and enabled by pulling ENLDO above 0.8V . Note that ENLDO can be driven above V INL or V OLDO , as long as it is limited to less than the absolute maximum rating. In the event that the LDO output voltage is held above the input voltage, the LDO goes in to shutdown until the output drops back below the input voltage. In shutdown the LDO will block reverse current from V OLDO to V INL .LDO Error Amplifi erThe non-inverting input of the transconductance error amplifi er is internally connected to a 0.6V reference and the inverting input is connected to FBL. The control loop compensation is provided internally. An external resistive voltage divider from V OLDO to ground programs the output voltage via FBL from 0.6V to 5V .V OLDO =0.6V 1+R4R3⎛⎝⎜⎞⎠⎟LDO Current Sensing and LimitingCurrent is sensed across an internal resistor . The guaran-teed minimum output current is 100mA.LOW-BATTERY INDICATORThe L TC3537 includes a low-battery comparator . The non-inverting input of the comparator is internally connected to a 0.6V reference and the inverting input is connected to LBI. An external resistive voltage divider from V INL to ground programs the threshold voltage. When the volt-age at LBI drops below 0.6V , the open-drain N-channel MOSFET will turn on. The N-channel MOSFET device is forced off when both the step-up converter and LDO are in shutdown.V LBI =0.6V 1+R6R5⎛⎝⎜⎞⎠⎟BOOST POWER-GOOD INDICATORThe L TC3537 includes a power-good comparator for the step-up converter . The non-inverting input of the compara-tor is internally connected to a 1.08V reference and the inverting input is connected to the FBB pin. The open-drain MOSFET on PGDB will turn on when the output voltage is typically within 6% of the programmed output voltage.Output sequencing can be achieved by connecting PGDB to the LDO enable pin (ENLDO). This would allow the user to keep the LDO off until the step-up converter is regulating. The N-channel MOSFET is forced on in shutdown.LDO POWER-GOOD INDICATORThe L TC3537 includes a power-good comparator for the LDO. The non-inverting input of the comparator is internally connected to a 540mV reference and the inverting input is connected to the FBL pin. The open-drain MOSFET on the PGDL pin will turn on when the output voltage is typically within 4% of the programmed output voltage.Output sequencing can be achieved by connecting PGDL to the boost enable pin (ENBST). This would allow the user to keep the step-up converter off until the LDO is regulating. The N-channel MOSFET is forced on in shutdown.143537faA PPLICATIONS INFORMATION V INB > V OUTB OPERATIONThe L TC3537 step-up converter will maintain voltage regu-lation even when the input voltage is above the desired output voltage. Note that the effi ciency is much lower in this mode, and the maximum output current capability will be less. Refer to the Typical Performance Characteristics.STEP-UP SHORT-CIRCUIT PROTECTIONThe L TC3537 output disconnect feature provides output short circuit protection. To reduce power dissipation under short-circuit conditions, the peak switch current limit is reduced to 400mA (typical).SCHOTTKY DIODEAlthough it is not required, adding a Schottky diode fromSW to V OUTB will improve efficiency by about 4%. Note that this defeats the output disconnect and short-circuit protection features.PCB LAYOUT GUIDELINESThe high speed operation of the L TC3537 demands careful attention to board layout. A careless layout will result in reduced performance. Figure 1 shows the recommended component placement. A large ground pin copper areawill help to lower the die temperature. A multilayer board with a separate ground plane is ideal, but not absolutely necessary.COMPONENT SELECTION Inductor SelectionThe L TC3537 can utilize small surface mount chip induc-tors due to its fast 2.2MHz switching frequency. Inductor values between 1μH and 4.7μH are suitable for most ap-plications. Larger values of inductance will allow slightly greater output current capability (and lower the Burst Mode threshold) by reducing the inductor ripple current. Increasing the inductance above 10μH will increase size while providing little improvement in output current capa-bility. The minimum inductance value is given by: L >V INB(MIN)•V OUTB(MAX)−V INB(MIN)()Ripple •V OUTB(MAX)where:Ripple = Allowable inductor current ripple (amps peak-peak)V INB(MIN) = Minimum converter input voltage V OUTB(MAX) = Maximum output voltageThe inductor current ripple is typically set for 20% to 40% of the maximum inductor current. High frequency ferrite core inductor materials reduce frequency dependent power losses compared to cheaper powdered iron types, improving effi ciency. The inductor should have low ESR (series resistance of the windings) to reduce the I 2R power losses, and must be able to support the peak inductor current without saturating. Molded chokes and some chip inductors usually do not have enough core area to support the peak inductor currents of 750mA seen on the L TC3537. To minimize radiated noise, use a shielded inductor . See Table 1 for suggested components and suppliers.Figure 1TO INNER GROUND LAYERS。

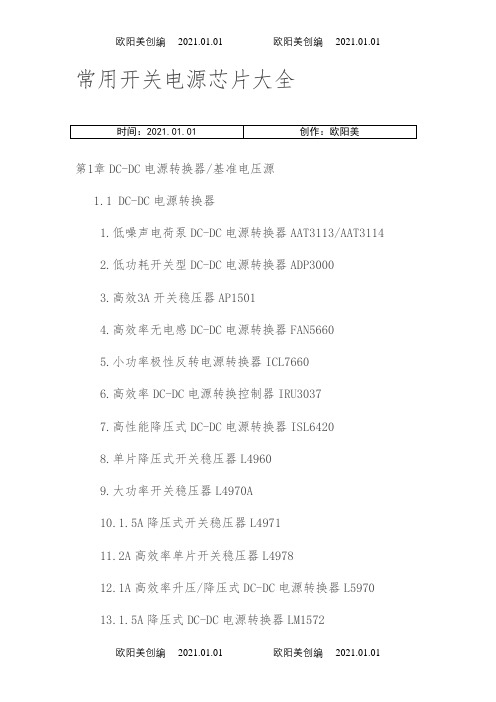

ltc2954的用法

ltc2954的用法摘要:1.简介2.特性3.应用领域4.使用方法4.1 接线4.2 配置4.3 操作5.常见问题及解决方案6.总结正文:【简介】LTC2954 是德州仪器(Texas Instruments)公司生产的一款高精度、低漂移的电压基准芯片,具有4 路输出,广泛应用于各种电子设备中,提供精确稳定的电压参考。

【特性】LTC2954 具有以下特性:1.4 路输出,输出电压分别为2.5V、1.25V、0.625V 和0.313V;2.低漂移,典型值为±2ppm/°C;3.高精度,典型值为±0.02%;4.低噪声,典型值为1μVp-p;5.宽工作电压范围,1.8V 至5.5V;6.紧凑型5 引脚SC70 封装。

【应用领域】LTC2954 电压基准芯片广泛应用于通信、工业控制、医疗设备、仪器仪表等领域,为这些设备提供精确稳定的电压参考。

【使用方法】【接线】使用时,将LTC2954 的VCC 引脚连接到1.8V 至5.5V 电源,GND 引脚连接到地,然后将输出引脚连接到需要提供电压参考的电路。

【配置】LTC2954 无需外部元件即可工作,但在某些应用场景下,可以通过外接电阻调整输出电压。

例如,通过连接一个电阻到OUT1 引脚,可以调整OUT1 的输出电压。

【操作】LTC2954 在接通电源后即可正常工作,无需额外的操作。

但在实际应用中,建议对电路进行适当的设计和布局,以降低噪声和干扰。

【常见问题及解决方案】1.输出电压不准确:可能是由于电源电压波动或负载电流变化导致的,可以通过使用稳压电源和使用合适的负载电阻来解决;2.温度漂移较大:可能是由于环境温度变化或电路布局不合理导致的,可以通过改善电路散热条件或使用散热片来解决。

【总结】LTC2954 是一款性能优异的电压基准芯片,具有高精度、低漂移、低噪声等优点,广泛应用于各种电子设备中。

BF992中文资料

1

VG2-S = 4 V; Tj = 25 °C.

VDS = 10 V; Tj = 25 °C.

Fig.3 Output characteristics; typical values.

Fig.4 Transfer characteristics; typical values.

handbook, halfpage

1999 Aug 11

2

元器件交易网

Philips Semiconductors

Product specification

Silicon N-channel dual gate MOS-FET

LIMITING VALUES In accordance with the Absolute Maximum Rating System (IEC 134). SYMBOL VDS ID IG1 IG2 Ptot Tstg Tj Note 1. Device mounted on a ceramic substrate, 8 mm × 10 mm × 0.7 mm. PARAMETER drain-source voltage drain current gate 1 current gate 2 current total power dissipation storage temperature operating junction temperature Tamb ≤ 60 °C; see Fig.2; note 1 CONDITIONS − − − − − −65 − MIN. MAX. 20 40 ±10 ±10 200 +150 150

VDS = 10 V; VG2-S = 4 V; ID = 15 mA; Tamb = 25 °C.

逆变器用到的IC

KA5H0165RN 原装正品 06年份 FSC 4000 现货

FSDM0265RNB 原装正品 06年份 FSC 40000 香港现货

FSDL0165RN 原装正品 06年份 FSC 9000 香港现货

FSDH321 原装正品 06年份 FSC 12000 香港现货

STP10NK60 原装正品 04年份 ST 10000 现货

IRF640B 原装正品 04年份 FSC 3800 现货

IRF630B 原装正品 06年份 FSC 2000 现货

FDP2532 原装正品 06年份 FSC 4200 现货

FQP50N06 原装正品 07年份 FSC 20000 现货

SSH70N10A 原装正品 07年份 FSC 480 香港现货

FQA160N08 原装正品 06年份 FSC 1300 现货

FQA40N25 原装正品 05年份 FSC 340 现货

FQA16N50 原装正品 04年份 FSC 2600 现货

FQPF10N60C 原装正品 07年份 FSC 6000 现货

FQPF12N60C 原装正品 07年份 FSC 550 现货

KA5L0380RYDTU 原装正品 07年份 FSC 10000 香港现货

FQPF8N60C 原装正品 07年份 FSC 20000 香港现货

2SK2645 原装正品 06年份 FUJI 5400 现货

2SK2765 原装正品 06年份 FUJI 2500 现货

FQA90N15 原装正品 06年份 FSC 500 现货

IRFP460C 原装正品 06.07年份 FSC 5600 香港现货

LTC4213 1 4213f 电子电路保护器说明书

2µs/DIV4213 TA01b124213fBias Supply Voltage (V CC )...........................–0.3V to 9V Input VoltagesON, SENSEP, SENSEN.............................–0.3V to 9V I SEL ..........................................–0.3V to (V CC + 0.3V)Output VoltagesGATE .....................................................–0.3V to 15V READY.....................................................–0.3V to 9V Operating Temperature RangeLTC4213C ...............................................0°C to 70°C LTC4213I.............................................–40°C to 85°C Storage Temperature Range.................–65°C to 150°C Lead Temperature (Soldering, 10sec)...................300°CORDER PART NUMBER DDB PART*MARKING T JMAX = 125°C, θJA = 250°C/WEXPOSED PAD (PIN 9)PCB CONNECTION OPTIONALConsult LTC Marketing for parts specified with wider operating temperature ranges.*The temperature grade is identified by a label on the shipping container.LBHVLTC4213CDDB LTC4213IDDB ABSOLUTE AXI U RATI GSW W WU PACKAGE/ORDER I FOR ATIOUUW (Note 1)ELECTRICAL CHARACTERISTICSThe ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V CC = 5V, I SEL = 0 unless otherwise noted. (Note 2)SYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITSV CC Bias Supply Voltage ● 2.36V V SENSEP SENSEP Voltage ●06V I CC V CC Supply Current●1.63mA V CC(UVLR)V CC Undervoltage Lockout Release V CC Rising● 1.8 2.07 2.23V ∆V CC(UVHYST)V CC Undervoltage Lockout Hysteresis ●30100160mV I SENSEP SENSEP Input Current V SENSEP = V SENSEN = 5V, Normal Mode 154080µA V SENSEP = V SENSEN = 0, Normal Mode –1±15µA I SENSENSENSEN Input CurrentV SENSEP = V SENSEN = 5V, Normal Mode 154080µA V SENSEP = V SENSEN = 0, Normal Mode –1±15µA V SENSEP = V SENSEN = 5V,50280µAReset Mode or Fault ModeV CBCircuit Breaker Trip Voltage I SEL = 0, V SENSEP = V CC●22.52527.5mV V CB = V SENSEP – V SENSEN I SEL = Floated, V SENSEP = V CC ●455055mV I SEL = V CC, V SENSEP = V CC ●90100110mV V CB(FAST)Fast Circuit Breaker Trip Voltage I SEL = 0, V SENSEP = V CC●63100115mV V CB(FAST)= V SENSEP – V SENSEN I SEL = Floated, V SENSEP = V CC ●126175200mV I SEL = V CC, V SENSEP = V CC ●252325371mV I GATE(UP)GATE Pin Pull Up Current V GATE = 0V●–50–100–150µA I GATE(DN)GATE Pin Pull Down Current ∆V SENSEP – V SENSEN = 200mV, V GATE = 8V ●1040mA ∆V GSMAX External N-Channel Gate Drive V SENSEN = 0, V CC ≥ 2.97V, I GATE = –1µA ● 4.8 6.58V V SENSEN = 0, V CC = 2.3V, I GATE = –1µA ● 2.65 4.38V ∆V GSARMV GS Voltage to Arm Circuit BreakerV SENSEN = 0, V CC ≥ 2.97V ● 4.4 5.47.6V V SENSEN = 0, V CC = 2.3V●2.53.57VTOP VIEWDDB PACKAGE8-LEAD (3mm × 2mm) PLASTIC DFN567894321READY ON I SEL GND V CC SENSEP SENSEN GATE34213f∆V GSMAX – ∆V GSARM Difference Between ∆V GSMAX and V SENSEN = 0, V CC ≥ 2.97V ●0.3 1.1V ∆V GSARMV SENSEN = 0, V CC = 2.3V●0.150.8VV READY(OL)READY Pin Output Low Voltage I READY = 1.6mA, Pull Down Device On ●0.20.4V I READY(LEAK)READY Pin Leakage Current V READY = 5V, Pull Down Device Off ●0±1µA V ON(TH)ON Pin High Threshold ON Rising, GATE Pulls Up ●0.760.80.84V ∆V ON(HYST)ON Pin Hysteresis ON Falling, GATE Pulls Down104090mV V ON(RST)ON Pin Reset Threshold ON Falling, Fault Reset, GATE Pull Down ●0.360.40.44V I ON(IN)ON Pin Input Current V ON = 1.2V●0±1µA ∆V OV Overvoltage Threshold ●0.410.7 1.1V ∆V OV = V SENSEP – V CCt OVOvervoltage Protection Trip Time V SENSEP = V SENSEN = Step 5V to 6.2V 2565160µs t FAULT(SLOW)V CB Trips to GATE Discharging ∆V SENSE Step 0mV to 50mV,●71627µs V SENSEN Falling, V CC = V SENSEP = 5V t FAULT(FAST)V CB(FAST) Trips to GATE Discharging ∆V SENSE Step 0V to 0.3V, V SENSEN Falling,●12.5µs V SENSEP = 5Vt DEBOUNCE Startup De-Bounce Time V ON = 0V to 2V Step to Gate Rising,2760130µs (Exiting Reset Mode)t READY READY Delay Time V GATE = 0V to 8V Step to READY Rising,2250115µs V SENSEP = V SENSEN = 0t OFF Turn-Off Time V ON = 2V to 0.6V Step to GATE Discharging 1.5510µs t ON Turn-On Time V ON = 0.6V to 2V Step to GATE Rising,4816µs (Normal Mode)t RESETReset TimeV ON Step 2V to 0V2080150µsNote 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.ELECTRICAL CHARACTERISTICSThe ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V CC = 5V, I SEL = 0 unless otherwise noted. (Note 2)SYMBOLPARAMETERCONDITIONSMIN TYP MAX UNITSNote 2: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.4564213ft RESET vs Temperaturet FAULT(SLOW) vs V CCt FAULT(SLOW) vs Temperaturet FAULT(FAST) vs V CCt FAULT(FAST) vs TemperatureTYPICAL PERFOR A CE CHARACTERISTICSU WSpecifications are at T A = 25°C. V CC = 5Vunless otherwise noted.t F A U L T (F A S T ) (µs )4213 G230.90.80.71.01.11.21.3TEMPERATURE (°C)–50050100125–252575BIAS SUPPLY VOLTAGE (V)2.010t F A U L T (S L O W ) (µs )14121618 3.0 4.0 5.0 6.04213 G202022 2.53.54.55.5TEMPERATURE (°C)–500501001254213 G21–25257510t F A U L T (S L O W ) (µs )141216182022TEMPERATURE (°C)–500501001254213 G19–252575t R E S E T (µs )60708090100BIAS SUPPLY VOLTAGE (V)2.0t F A U L T (F A S T ) (µs )3.04.05.06.04213 G222.53.54.55.50.90.80.71.01.11.21.374213fPI FU CTIO SU U UREADY (Pin 1): READY Status Output. Open drain output that goes high impedance when the external MOSFET is on and the circuit breaker is armed. Otherwise this pin pulls low.ON (Pin 2): ON Control Input. The LTC4213 is in reset mode when the ON pin is below 0.4V. When the ON pin increases above 0.8V, the device starts up and the GATE pulls up with a 100µA current source. When the ON pin drops below 0.76V, the GATE pulls down. To reset a circuit breaker fault, the ON pin must go below 0.4V.I SEL (Pin 3): Threshold Select Input. With the I SEL pin grounded, float or tied to V CC the V CB is set to 25mV, 50mV or 100mV, respectively. The corresponding V CB(FAST)values are 100mV, 175mV and 325mV.GND (Pin 4): Device Ground.GATE (P in 5): GATE D rive Output. An internal charge pump supplies 100µA pull-up current to the gate of the external N-channel MOSFET. Internal circuitry limits thevoltage between the GATE and SENSEN pins to a safe gate drive voltage of less than 8V. When the circuit breaker trips, the GATE pin abruptly pulls to GND.SENSEN (Pin 6): Circuit Breaker Negative Sense Input.Connect this pin to the source of the external MOSFET.During reset or fault mode, the SENSEN pin discharges the output to ground with 280µA.SENSEP (P in 7): Circuit Breaker Positive Sense Input.Connect this pin to the drain of external N-channel MOSFET.The circuit breaker trips when the voltage across SENSEP and SENSEN exceeds V CB . The input common mode range of the circuit breaker is from ground to V CC + 0.2V when V CC < 2.5V. For V CC ≥ 2.5V, the input common mode range is from ground to V CC + 0.4V.V CC (Pin 8): Bias Supply Voltage Input. Normal operation is between 2.3V and 6V. An internal under-voltage lockout circuit disables the device when V CC < 2.07V.Exposed Pad (Pin 9): Exposed pad may be left open or connected to device ground.8910114213fsupply transient dips below 1.97V of less than 80µs are ignored.ON FunctionWhen V ON is below comparator COMP1’s threshold of 0.4V for 80µs, the device resets. The system leaves reset mode if the ON pin rises above comparator COMP2’s threshold of 0.8V and the UVLO condition is met. Leaving reset mode, the GATE pin starts up after a t DEBOUNCE delay of 60µs. When ON goes below 0.76V, the GATE shuts off after a 5µs glitch filter delay. The output is discharged by the external load when V ON is in between 0.4V to 0.8V. At this state, the ON pin can re-enable the GATE if V ON exceeds 0.8V for more than 8µs. Alternatively, the device resets if the ON pin is brought below 0.4V for 80µs. Once reset, the GATE pin restarts only after the t DEBOUNCE 60µs delay at V ON rising above 0.8V. To protect the ON pin from overvoltage stress due to supply transients, a series resistor of greater than 10k is recommended when the ON pin is connected directly to the supply. An external resis-tive divider at the ON pin can be used with COMP2 to set a supply undervoltage lockout value higher than the inter-nal UVLO circuit. An RC filter can be implemented at the ON pin to increase the powerup delay time beyond the internal 60µs delay.Gate FunctionThe GATE pin is held low in reset mode. 60µs after leaving reset mode, the GATE pin is charged up by an internal 100µA current source. The circuit breaker arms when V GATE > V SENSEN + ∆V GSARM . In normal mode operation,the GATE peak voltage is internally clamped to ∆V GSMAX above the SENSEN pin. When the circuit breaker trips, an internal MOSFET shorts the GATE pin to GND, turning off the external MOSFET.READY StatusThe READY pin is held low during reset and at startup. It is pulled high by an external pullup resistor 50µs after the circuit breaker arms. The READY pin pulls low if the circuit breaker trips or the ON pin is pulled below 0.76V, or V CC drops below undervoltage lockout.∆V GSARM and V GSMAXEach MOSFET has a recommended V GS drive voltage where the channel is deemed fully enhanced and R DSON is minimized. Driving beyond this recommended V GS volt-age yields a marginal decrease in R DSON . At startup, the gate voltage starts at ground potential. The GATE ramps past the MOSFET threshold and the load current begins to flow. When V GS exceeds ∆V GSARM , the circuit breaker is armed and enabled. The chosen MOSFET should have a recommended minimum V GS drive level that is lower than ∆V GSARM . Finally, V GS reaches a maximum at ∆V GSMAX.Trip and Reset Circuit BreakerFigure 2 shows the timing diagram of V GATE and V READY after a fault condition. A tripped circuit breaker can be reset either by cycling the V CC bias supply below UVLO thresh-old or pulling ON below 0.4V for >t RESET . Figure 3 shows the timing diagram for a tripped circuit breaker being reset by the ON pin.Calculating Current LimitThe fault current limit is determined by the R DSON of the MOSFET and the circuit breaker voltage V CB .I V R LIMIT CB DSON=()2The R DSON value depends on the manufacturer’s distribu-tion, V GS and junction temperature. Short Kelvin-sense connections between the MOSFET drain and source to the LTC4213 SENSEP and SENSEN pins are strongly recommended.For a selected MOSFET, the nominal load limit current is given by:I V R LIMIT NOM CB NOM DSON NOM ()()()()=3The minimum load limit current is given by:I V R LIMIT MIN CB MIN DSON MAX ()()()()=4APPLICATIO S I FOR ATIOW UUU1213144213fOperating temperature of 0° to 70°C.R DSON @ 25°C = 100%R DSON @ 0°C = 90%R DSON @ 70°C = 120%MOSFET resistance variation:R DSON(NOM) = 15m • 0.82 = 12.3m ΩR DSON(MAX) = 15m • 1.333 • 0.93 • 1.2 = 15m • 1.488= 22.3m ΩR DSON(MIN) = 15m • 0.667 • 0.80 • 0.90 = 15m • 0.480= 7.2m ΩV CB variation:NOM V CB = 25mV = 100%MIN V CB = 22.5mV = 90%MAX V CB = 27.5mV = 110%The current limits are:I LIMIT(NOM) = 25mV/12.3m Ω = 2.03A I LIMIT(MIN) = 22.5mV/22.3m Ω = 1.01A I LIMIT(MAX) = 27.5mV/7.2m Ω = 3.82AFor proper operation, the minimum current limit must exceed the circuit maximum operating load current with margin. So this system is suitable for operating load current up to 1A. From this calculation, we can start with the general rule for MOSFET R DSON by assuming maxi-mum operating load current is roughly half of the I LIMIT(NOM). Equation 7 shows the rule of thumb.I V R OPMAX CB NOM DSON NOM =()()•()27Note that the R DSON(NOM) is at the LTC4213 nominal operating ∆V GSMAX rather than at typical vendor spec.Table 1 gives the nominal operating ∆V GSMAX at the various operating V CC . From this table users can refer to the MOSFET’s data sheet to obtain the R DSON(NOM) value.Table 1. Nominal Operating ∆V GSMAX for Typical Bias Supply VoltageV CC (V)∆V GSMAX (V)2.3 4.32.5 5.02.7 5.63.0 6.53.37.05.07.06.07.0Load Supply Power-Up after Circuit Breaker Armed Figure 4 shows a normal power-up sequence for the circuit in Figure 1 where the V IN load supply power-up after circuit breaker is armed. V CC is first powered up by an auxiliary bias supply. V CC rises above 2.07V at time point 1. V ON exceeds 0.8V at time point 2. After a 60µs debounce delay, the GATE pin starts ramping up at time point 3. The external MOSFET starts conducting at time point 4. At time point 5, V GATE exceed ∆V GSARM and the circuit breaker is armed. After 50µs (t READY delay), READY pulls high by an external resistor at time point 6. READY signals the V IN load supply module to start its ramp. The load supply begins soft-start ramp at time point 7. The load supply ramp rate must be slow to prevent circuit breaker tripping as in equation (8).∆∆V t I I C IN OPMAX LOADLOAD<−()8Where I OPMAX is the maximum operating current defined by equation 7.For illustration, V CB = 25mV and R DSON = 3.5m Ω at the nominal operating ∆V GSMAX . The maximum operating current is 3.5A (refer to equation 7). Assuming the load can draw a current of 2A at power-up, there is a margin of 1.5A available for C LOAD of 100µF and V IN ramp rate should be <15V/ms. At time point 8, the current through the MOSFET reduces after C LOAD is fully charged.APPLICATIO S I FOR ATIOW UUU1516174213fThe selected MOSFET V GS absolute maximum rating should meet the LTC4213 maximum ∆V GSMAX of 8V.Other MOSFET criteria such as V BDSS , I DMAX , and R DSON should be reviewed. Spikes and ringing above maximum operating voltage should be considered when choosing V BDSS . I DMAX should be greater than the current limit. The maximum operating load current is determined by the R DSON value. See the section on “Calculating Current Limit” for details.Supply RequirementsThe LTC4213 can be powered from a single supply or dual supply system. The load supply is connected to the SENSEP pin and the drain of the external MOSFET. In the single supply case, the V CC pin is connected to the load supply, preferably with an RC filter. With dual supplies,V CC is connected to an auxiliary bias supply V AUX where V AUX voltage should be greater or equal to the load supply voltage. The load supply voltage must be capable of sourcing more current than the circuit breaker limit. If the load supply current limit is below the circuit breaker trip current, the LTC4213 may not react when the output overloads. Furthermore, output overloads may trigger UVLO if the load supply has foldback current limit in a single supply system.V IN Transient and Overvoltage ProtectionInput transient spikes are commonly observed whenever the LTC4213 responds to overload. These spikes can be large in amplitude, especially given that large decoupling capacitors are absent in hot swap environments. These short spikes can be clipped with a transient suppressor of adequate voltage and power rating. In addition, the LTC4213can detect a prolonged overvoltage condition. WhenAPPLICATIO S I FOR ATIOW UUU point 6 should be within the circuit breaker limits. Other-wise, the system fails to start and the circuit breaker trips immediately after arming. In most applications additional external gate capacitance is not required unless C LOAD is large and startup becomes problematic. If an external gate capacitor is employed, its capacitance value should not be excessive unless it is used with a series resistor. This is because a big gate capacitor without resistor slows down the GATE turn off during a fault. An alternative method would be a stepped I SEL pin to allow a higher current limit during startup.In the event of output short circuit or a severe overload, the load supply can collapse during GATE ramp up due to load supply current limit. The chosen MOSFET must withstand this possible brief short circuit condition before time point 6 where the circuit breaker is allowed to trip. Bench short circuit evaluation is a practical verification of a reliable design. To have current limit while powering a MOSFET into short circuit conditions, it is preferred that the load supply sequences to turn on after the circuit breaker is armed as described in an earlier section.Power-Off CycleThe system can be powered off by toggling the ON pin low.When ON is brought below 0.76V for 5µs, the GATE and READY pins are pulled low. The system resets when ON is brought below 0.4V for 80µs.MOSFET SelectionThe LTC4213 is designed to be used with logic (5V) and sub-logic (3V) MOSFETs for V CC potentials above 2.97V with ∆V GSMAX exceeding 4.5V. For a V CC supply range between 2.3V and 2.97V, sub-logic MOSFETs should be used as the minimum ∆V GSMAX is less than 4.5V.1819Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.201630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX: (408) 434-0507 ● © LINEAR TECHNOLOGY CORPORA TION 2005LT/TP 0405 500 • PRINTED IN USA。

LTC5509 RF电源检测器演示板快速使用指南说明书

February 14, 2003DC539B DEMO BOARD QUICK START GUIDEINTRODUCTIONThe DC539B demo board is used to evaluate the LTC5509, RF power detector with integrated output buffer and voltage reference. The LTC5509 converts an RF input signal at pin 6 (RF) to a DC voltage at pin 3 (Vout). The RF input frequency range is 300 MHz to 3000 MHz. Maximum input power is8 dBm. The output voltage at Vout will start at an initial DC value of typically 250mV. When the RF signal is applied the output voltage will increase.The optional 68Ω (R1) termination resistor is not placed on PCB. The optional C5 shunt capacitor is not installed. R2 and C5 form a low pass filter at Vout. Capacitor C1 is 33 pF for high frequency tests and evaluations at 1000 to 3000 MHz. For frequencies at 300 to 1000 MHz a 51 pF value is suggested.A logic high at pin 1 enables the part. It is controlled by a jumper JP1.The DC539B demo board is easily set up for evaluating the LTC5509 RF power detector performance. Follow the procedures outlined below and connections on the attached diagram for proper operation. 1.Connect the input DC power supply (2.7V to 6V) to Vcc pin (E1). Connect the power supply groundto ground pin (E3 or E5). Connect RF input (SMA connector J1) to the RF signal generator output via coaxial cable. It is common practice to include a 3dB pad at the RF input of the demo board to minimize reflections back into the signal generator.2.The part can be shutdown via jumper switch JP1. When JP1 is connected to ground the part will bein shutdown. When JP1 is connected to VCC via the 22k resistor the part will be enabled. The shutdown terminal E4 can also be controlled externally by a pulse from function generator, tocharacterize enable times from the shutdown state. When external shutdown signal is used, set JP1 to the enable position. External 50Ω termination from E4 to ground is recommended for timing measurements when signal source with 50Ω output impedance is used. Connect a pulse generator to E4 via a coaxial cable.3.With JP1 set to the enable position, apply an RF input signal (-35 to +9dBm) and measure the VoutDC voltage at E2.DC539B Demo Board Connection Diagram。

利特尔比特ltc4059 ltc4059a-900ma-线性锂离子电池充电器用热控制在2-2 dfn

124059fbInput Supply Voltage (V CC )...................... –0.3V to 10V BAT, PROG, EN, Li CC, ACPR ................... –0.3V to 10V BAT Short-Circuit Duration...........................Continuous BAT Pin Current............................................... 1000mA PROG Pin Current............................................. 1000µA Junction Temperature.......................................... 125°C Operating Temperature Range (Note 2)..–40°C to 85°C Storage Temperature Range.................–65°C to 125°CORDER PART NUMBER Consult LTC Marketing for parts specified with wider operating temperature ranges.LTC4059EDC LTC4059AEDC ABSOLUTE AXI U RATI GSW W WU PACKAGE/ORDER I FOR ATIOUUW (Note 1)T JMAX = 125°C, θJA = 60°C/W TO 85°C/W (NOTE 3)*Li CC PIN 2 ON LTC4059EDC,ACPR PIN 2 ON LTC4059AEDC EXPOSED PAD (PIN 7) IS GND MUST BE SOLDERED TO PCBTOP VIEW7DC6 PACKAGE6-LEAD (2mm × 2mm) PLASTIC DFN456321GND BAT EN PROG V CCLi CC/ACPR*DC6 PART MARKING LAFU LBJHELECTRICAL CHARACTERISTICSThe ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V CC = 5V unless otherwise noted.SYMBOL PARAMETERCONDITIONSMIN TYP MAX UNITSV CC V CC Supply Voltage●3.758V I CC Quiescent V CC Supply Current V BAT = 4.5V (Forces I BAT and I PROG = 0)●2560µA I CCMS V CC Supply Current in Shutdown V EN = V CC●1025µA I CCUV V CC Supply Current in Undervoltage V CC < V BAT ; V CC = 3.5V, V BAT = 4V ●410µA LockoutV FLOAT V BAT Regulated Output Voltage I BAT = 2mA4.175 4.2 4.225V 4.5V < V CC < 8V, I BAT = 2mA● 4.158 4.2 4.242V I BAT BAT Pin CurrentR PROG = 2.43k, Current Mode, V BAT = 3.8V ●475500525mA R PROG = 12.1k, Current Mode, V BAT = 3.8V ●94100106mA I BMS Battery Drain Current in Shutdown V EN = V CC , V CC > V BAT ●0±1µA I BUV Battery Drain Current in Undervoltage V CC < V BAT , V BAT = 4V●014µA LockoutV UV V CC – V BAT Undervoltage Lockout V CC from Low to High, V BAT = 3.7V ●100150200mV ThresholdV CC from High to Low, V BAT = 3.7V ●03580mV V PROG PROG Pin VoltageR PROG = 2.43k, I PROG = 500µA ● 1.18 1.21 1.24V R PROG = 12.1k, I PROG = 100µA ● 1.18 1.21 1.24V V MS Manual Shutdown Threshold V EN Increasing ●0.30.92 1.2V V MSHYS Manual Shutdown Hysteresis V EN Decreasing 85mV R EN EN Pin Input ResistanceV EN = 5V●1 1.853M ΩV Li CC Voltage Mode Disable Threshold V Li CC Increasing (LTC4059 Only)●0.30.92 1.2V V Li CCHYS Voltage Mode Disable Hysteresis V Li CC Decreasing (LTC4059 Only)85mV V ACPR ACPR Pin Output Low Voltage I ACPR = 300µA (LTC4059A Only)0.250.5V t LIM Junction Temperature In Constant 115°C Temperature ModeR ONPower FET “ON” Resistance I BAT = 150mA (Note 4)8001200m Ω(Between V CC and BAT)Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.Note 2: The LTC4059E/LTC4059AE are guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the –40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.Note 3: Failure to solder the exposed backside of the package to the PC board ground plane will result in a thermal resistance much higher than 60°C/W.Note 4: The FET on-resistance is guaranteed by correlation to wafer level measurements.3454059fbPI FU CTIO SU U UGND (P ins 1, 7): Ground/Exposed Pad. The exposed package pad is ground and must be soldered to the PC board for maximum heat transfer.Li CC (Pin 2, LTC4059): Li-Ion/Constant Current Input Pin. Pulling this pin above V Li CC disables voltage mode thereby providing a constant current to the BAT pin. This feature is useful for charging Nickel chemistry batteries.Tie to GND if unused.ACP R (P in 2, LTC4059A): Open-Drain Power Supply Status Output. When V CC is greater than the undervoltage lockout threshold, the ACPR pin will pull to ground;otherwise the pin is forced to a high impedance state.BAT (P in 3): Charge Current Output. Provides charge current to the battery and regulates the final float voltage to 4.2V. An internal precision resistor divider from this pin sets this float voltage and is disconnected in shutdown mode.V CC (P in 4): Positive Input Supply Voltage. This pin provides power to the charger. V CC can range from 3.75V to 8V. This pin should be bypassed with at least a 1µF capacitor. When V CC is within 35mV of the BAT pin voltage, the LTC4059 enters shutdown mode, dropping I BAT to less than 4µA.PROG (Pin 5): Charge Current Program and Charge Cur-rent Monitor Pin. Connecting a resistor, R PROG , to ground programs the charge current. When charging in constant-current mode, this pin servos to 1.21V. In all modes, the voltage on this pin can be used to measure the charge current using the following formula:I V R BAT PROGPROG=•1000EN (Pin 6): Enable Input Pin. Pulling this pin above the manual shutdown threshold (V MS is typically 0.92V) puts the LTC4059 in shutdown mode, thus terminating a charge cycle. In shutdown mode, the LTC4059 has less than 25µA supply current and less than 1µA battery drain current.Enable is the default state, but the pin should be tied to GND if unused.674059fbOPERATIOUThe LTC4059/LTC4059A are linear battery chargers de-signed primarily for charging single cell lithium-ion bat-teries. Featuring an internal P-channel power MOSFET,the chargers use a constant-current/constant-voltage charge algorithm with programmable current. Charge current can be programmed up to 900mA with a final float voltage accuracy of ±0.6%. No blocking diode or external sense resistor is required; thus, the basic charger circuit requires only two external components. The ACPR pin (LTC4059A) monitors the status of the input voltage with an open-drain output. The Li C C pin (LTC4059) disables constant-voltage operation and turns the LTC4059 into a precision current source capable of charging Nickel chem-istry batteries. Furthermore, the LTC4059/LTC4059A are designed to operate from a USB power source.An internal thermal limit reduces the programmed charge current if the die temperature attempts to rise above a preset value of approximately 115°C. This feature protects the LTC4059/LTC4059A from excessive temperature, and allows the user to push the limits of the power handling capability of a given circuit board without risk of damaging the LTC4059/LTC4059A or external components. Anotherbenefit of the thermal limit is that charge current can be set according to typical, not worst-case, ambient tempera-tures for a given application with the assurance that the charger will automatically reduce the current in worst-case conditions.The charge cycle begins when the voltage at the V CC pin rises approximately 150mV above the BAT pin voltage, a program resistor is connected from the PROG pin to ground, and the EN pin is pulled below the shutdown threshold (typically 0.92V).If the BAT pin voltage is below 4.2V, or the Li CC pin is pulled above V Li CC (LTC4059 only), the LTC4059 will charge the battery with the programmed current. This is constant-current mode. When the BAT pin approaches the final float voltage (4.2V), the LTC4059 enters constant-voltage mode and the charge current begins to decrease.To terminate the charge cycle the EN should be pulled above the shutdown threshold. Alternatively, reducing the input voltage below the BAT pin voltage will also terminate the charge cycle.APPLICATIO S I FOR ATIOW UUU Programming Charge CurrentThe charge current is programmed using a single resistor from the PROG pin to ground. The battery charge current is 1000 times the current out of the PROG pin. The program resistor and the charge current are calculated using the following equations:R V I I VR PROG CHG CHG PROG==10001211000121•.,•.For best stability over temperature and time, 1% metal-film resistors are recommended.The charge current out of the BAT pin can be determinedat any time by monitoring the PROG pin voltage and using the following equation:I V R BAT PROGPROG=•1000Undervoltage Lockout (UVLO)An internal undervoltage lockout circuit monitors the input voltage and keeps the charger in undervoltage lockout until V CC rises approximately 150mV above the BAT pin voltage.The UVLO circuit has a built-in hysteresis of 115mV. If the BAT pin voltage is below approximately 2.75V, then the charger will remain in undervoltage lockout until V CC rises above approximately 3V. During undervoltage lockout conditions, maximum battery drain current is 4µA.Power Supply Status Indicator (ACPR, LTC4059A Only)The power supply status output has two states: pull-down and high impedance. The pull-down state indicates that V CC is above the undervoltage lockout threshold (see Undervoltage Lockout). When this condition is not met,the ACPR pin is high impedance indicating that the LTC4059A is unable to charge the battery.894059fbPower DissipationThe conditions that cause the LTC4059/LTC4059A to reduce charge current through thermal feedback can be approximated by considering the power dissipated in the IC. For high charge currents, the LTC4059 power dissipa-tion is approximately:P D = (V CC – V BAT ) • I BATwhere P D is the power dissipated, V CC is the input supply voltage, V BAT is the battery voltage and I BAT is the charge current. It is not necessary to perform any worst-case power dissipation scenarios because the LTC4059/LTC4059A will automatically reduce the charge current to maintain the die temperature at approximately 115°C.However, the approximate ambient temperature at which the thermal feedback begins to protect the IC is:T A = 115°C – P D θJAT A = 115°C – (V CC – V BAT ) • I BAT • θJAExample: Consider an LTC4059 operating from a 5V wall adapter providing 900mA to a 3.7V Li-Ion battery. The ambient temperature above which the LTC4059/LTC4059A begin to reduce the 900mA charge current is approximately:T A = 115°C – (5V – 3.7V) • (900mA) • 50°C/W T A = 115°C – 1.17W • 50°C/W = 115°C – 59°C T A = 56°CThe LTC4059 can be used above 56°C, but the charge current will be reduced from 900mA. The approximate current at a given ambient temperature can be calculated:I C T V V BAT A CC BAT JA=°()115––•θUsing the previous example with an ambient temperature of 65°C, the charge current will be reduced to approximately:I C C V V C W CC AI mABAT BAT =°°()°=°°=11565537505065770––.•//F urthermore, the voltage at the PROG pin will change proportionally with the charge current as discussed in the Programming Charge Current section.It is important to remember that LTC4059/LTC4059A applications do not need to be designed for worst-case thermal conditions since the IC will automatically reduce power dissipation when the junction temperature reaches approximately 115°C.Board Layout ConsiderationsIn order to be able to deliver maximum charge current under all conditions, it is critical that the exposed metal pad on the backside of the LTC4059/LTC4059A package is soldered to the PC board ground. Correctly soldered to a 2500mm 2 double sided 1oz copper board the LTC4059/LTC4059A have a thermal resistance of approximately 60°C/W. F ailure to make thermal contact between the exposed pad on the backside of the package and the copper board will result in thermal resistances far greater than 60°C/W. As an example, a correctly soldered LTC4059/LTC4059A can deliver over 900mA to a battery from a 5V supply at room temperature. Without a backside thermal connection, this number could drop to less than 500mA.Stability ConsiderationsThe LTC4059 contains two control loops: constant voltage and constant current. The constant-voltage loop is stable without any compensation when a battery is connected with low impedance leads. Excessive lead length, how-ever, may add enough series inductance to require a bypass capacitor of at least 1µF from BAT to GND. Further-more, a 4.7µF capacitor with a 0.2Ω to 1Ω series resistor from BAT to GND is required to keep ripple voltage low when the battery is disconnected.High value capacitors with very low ESR (especially ce-ramic) reduce the constant-voltage loop phase margin.Ceramic capacitors up to 22µF may be used in parallel with a battery, but larger ceramics should be decoupled with 0.2Ω to 1Ω of series resistance.I n constant-current mode, the PROG pin is in the feedback loop, not the battery. Because of the additional pole created by PROG pin capacitance, capacitance on this pin must be kept to a minimum. With no additional capaci-tance on the PROG pin, the charger is stable with program resistor values as high as 12k. However, additional ca-pacitance on this node reduces the maximum allowedAPPLICATIO S I FOR ATIOW UUUFigure 5. Photo of Typical Circuit (2.5mm × 2.7mm) 1011Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.121630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX: (408) 434-0507 ● © LINEAR TECHNOLOGY CORPORA TION 2003LT/LT 0505 REV B • PRINTED IN USA。

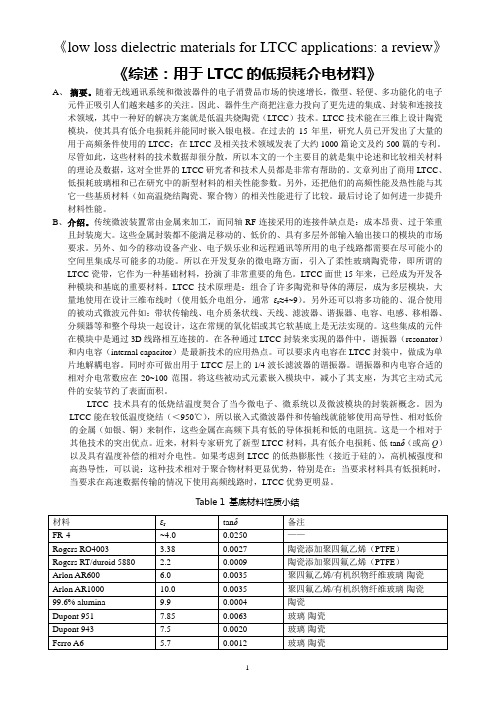

综述:用于LTCC的低损耗介电材料

《low loss dielectric materials for LTCC applications: a review》《综述:用于LTCC的低损耗介电材料》A、摘要。

随着无线通讯系统和微波器件的电子消费品市场的快速增长,微型、轻便、多功能化的电子元件正吸引人们越来越多的关注。

因此、器件生产商把注意力投向了更先进的集成、封装和连接技术领域,其中一种好的解决方案就是低温共烧陶瓷(LTCC)技术。

LTCC技术能在三维上设计陶瓷模块,使其具有低介电损耗并能同时嵌入银电极。

在过去的15年里,研究人员已开发出了大量的用于高频条件使用的LTCC;在LTCC及相关技术领域发表了大约1000篇论文及约500篇的专利。

尽管如此,这些材料的技术数据却很分散,所以本文的一个主要目的就是集中论述和比较相关材料的理论及数据,这对全世界的LTCC研究者和技术人员都是非常有帮助的。

文章列出了商用LTCC、低损耗玻璃相和已在研究中的新型材料的相关性能参数。

另外,还把他们的高频性能及热性能与其它一些基质材料(如高温烧结陶瓷、聚合物)的相关性能进行了比较。

最后讨论了如何进一步提升材料性能。

B、介绍。

传统微波装置常由金属来加工,而同轴RF连接采用的连接件缺点是:成本昂贵、过于笨重且封装庞大。

这些金属封装都不能满足移动的、低价的、具有多层外部输入输出接口的模块的市场要求。

另外、如今的移动设备产业、电子娱乐业和远程通讯等所用的电子线路都需要在尽可能小的空间里集成尽可能多的功能。

所以在开发复杂的微电路方面,引入了柔性玻璃陶瓷带,即所谓的LTCC瓷带,它作为一种基础材料,扮演了非常重要的角色。

LTCC面世15年来,已经成为开发各种模块和基底的重要材料。

LTCC技术原理是:组合了许多陶瓷和导体的薄层,成为多层模块,大量地使用在设计三维布线时(使用低介电组分,通常εr≈4~9)。

另外还可以将多功能的、混合使用的被动式微波元件如:带状传输线、电介质条状线、天线、滤波器、谐振器、电容、电感、移相器、分频器等和整个母块一起设计,这在常规的氧化铝或其它软基底上是无法实现的。

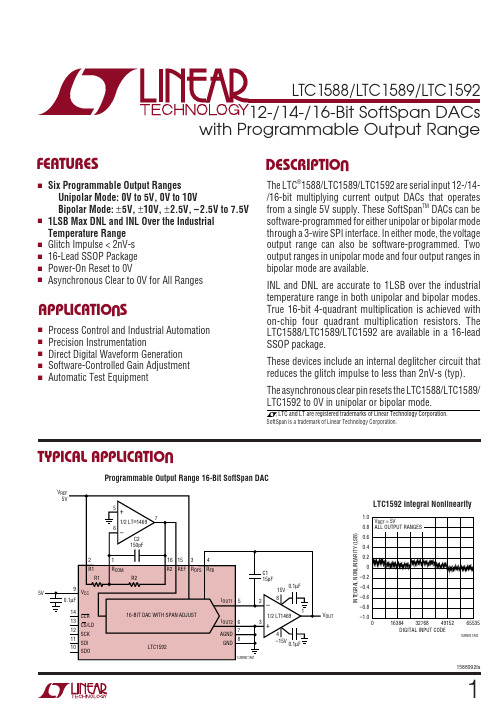

LTC1592资料

1.0 0.8 0.6 0.4 0.20–0.2–0.4–0.6–0.8–1.0V REF = 5VALL OUTPUT RANGES1LTC1588/LTC1589/LTC159223LTC1588/LTC1589/LTC159245LTC1588/LTC1589/LTC15921588992faTYPICAL PERFOR A CE CHARACTERISTICSU W(LTC1588)Integral NonlinearityDifferential NonlinearityDIGITAL INPUT CODEI N T E G R A L N O N L I N E A R I T Y (L S B )0.20.61.01588992 G11–0.2–0.600.40.8–0.4–0.8–1.08001600240032004095DIGITAL INPUT CODED I F FE R E N T I A L N O N L I N E A R I T Y (L S B )0.20.61.01588992 G12–0.2–0.600.40.8–0.4–0.8–1.08001600240032004095(LTC1589)Integral NonlinearityDifferential NonlinearityDIGITAL INPUT CODEI N T E G R A L N O N L I N E A R I T Y (L S B )0.20.61.01588992 G13–0.2–0.600.40.8–0.4–0.8–1.0411282241233616383DIGITAL INPUT CODED I F FE R E N T I A L N O N L I N E A R I T Y (L S B )0.20.61.01588992 G14–0.2–0.600.40.8–0.4–0.8–1.0411282241233616383Integral Nonlinearity vs Reference Voltage in Unipolar ModeREFERENCE VOLTAGE (V)–10I N T E G R A L N O N L I N E A R I T Y (L S B )0.20.61.061588992 G05–0.2–0.600.40.8–0.4–0.8–1.0–6–22–88–40410Integral Nonlinearity (INL)DIGITAL INPUT CODE–1.0I N T E G R A L N O N L I N E A R I T Y (L S B )–0.8–0.4–0.201.00.416384327681588992 G01–0.60.60.80.24915265535DIGITAL INPUT CODE–1.0D I F FE R E N T I A L N O N L I N E A R I T Y (L S B )–0.8–0.4–0.201.00.416384327681588992 G02–0.60.60.80.24915265535Differential Nonlinearity (DNL)(LTC1592)6LTC1588/LTC1589/LTC15921588992faREFERENCE VOLTAGE (V)–10I N T E G R A L N O N L I N E A R I T Y (L S B )0.20.61.061588992 G06–0.2–0.600.40.8–0.4–0.8–1.0–6–22–88–40410Integral Nonlinearityvs Reference Voltage in Bipolar ModeDifferential Nonlinearity vs Reference Voltage in Unipolar ModeREFERENCE VOLTAGE (V)–10D I F F E R E N T I A L N O N L I N E A R I T Y (L S B )0.20.61.061588992 G07–0.2–0.600.40.8–0.4–0.8–1.0–6–22–88–40410TYPICAL PERFOR A CE CHARACTERISTICS U WDifferential Nonlinearity vs Reference Voltage in Bipolar ModeREFERENCE VOLTAGE (V)–10D I F F E R E N T I A L N O N L I N E A R I T Y (L S B )0.20.61.061588992 G08–0.2–0.600.40.8–0.4–0.8–1.0–6–22–88–40410(LTC1592)U U UPI FU CTIO SR COM (Pin 1): Center Tap Point of the Two Bipolar Resis-tors R1 and R2. Normally tied to the inverting input of an external amplifier. When these resistors are not used,connect this pin to ground. The absolute maximum volt-age range on this pin is –0.3V to 12V.R1 (Pin 2): Bipolar Resistor R1. The main reference input V REF , typically 5V. Accepts up to ±15V. Normally tied to R OFS (Pin 3) and the reference input voltage V REF (5V).When not used connect this pin to ground.R OFS (Pin 3): Bipolar Offset Network. This pin provides the offset of the output voltage range for bipolar modes.Accepts up to ±15V. Normally tied to R1 and the reference input voltage V REF (5V). Alternatively, this pin may be driven from a different voltage than V REF .R FB (Pin 4): Feedback Network. Normally tied to the output of the current to voltage converter op amp. Range limited to ±15V.Full-Scale Settling WaveformGATED SETTLING WAVEFORM 500µV/DIVLD PULSE 5V/DIV 500ns/DIV1592 G04USING LT1468 OP AMP C FEEDBACK = 20pF 0V TO 10V STEP7LTC1588/LTC1589/LTC159289LTC1588/LTC1589/LTC15921588992faOPERATIOUSerial InterfaceWhen the CS/LD is brought to a logic low, the data on the SDI input is loaded into the shift register on the rising edge of the clock. A 4-bit command word (C3 C2 C1 C0),followed by four “don’t care” bits and 16 data bits (MSB-first) is the minimum loading sequence required for the LTC1588/LTC1589/LTC1592. When the CS/LD is brought to a logic high, the clock is disabled internally and the command word is executed.If no daisy-chaining is required, the input stream can be 24-bit wide as shown in Figure 1a. The first four bits are the command word, followed by four “don’t care” bits, then a 16-bit data word. The last four bits (LSBs) of this 16-bit data word are don’t cares for the LTC1588. For the LTC1589, the last 2 bits of the 16-bit data word are don’t cares.If daisy-chaining is required or the input needs to be written in two 16-bit wide segments, then the input stream must be 32-bit wide and the first 8 bits loaded are “don’t care” bits. The remaining bits work the same as a 24-bit stream which is described in the previous paragraph. The output of the internal 32-bit shift register is available on the SDO pin 32 clock cycles later.Multiple LTC1588/LTC1589/LTC1592s may be daisy-chained together by connecting the SDO pin to the SDI pin of the next IC. The clock and CS/LD signals should remain common to all ICs in the daisy-chain. The serial data isclocked to all ICs, then the CS/LD signal is pulled high to update all of them simultaneously.Power-On Reset and ClearWhen the power supply is first turned on, the LTC1588/LTC1589/LTC1592 will power up in 5V unipolar mode (C3C2 C1 C0 = 1000). All the internal registers are set to zeros and the DAC is set to zero code.The LTC1588/LTC1589/LTC1592 must first be pro-grammed in either unipolar or bipolar mode. There are six operating modes available and can be software-pro-grammed by the command word. When a CLR signal is brought to low, it clears all internal registers to zero. The DAC output voltage goes to zero volts. If an update DAC command (C3 C2 C1 C0 = 0001) is issued immediately after the CLR signal, the DAC output remains at zero volts.If a CLR signal is given within a 100ns interval immediately after CS/LD goes high, the user should reload the output range.Output Range ProgrammingThere are two output ranges available in unipolar mode and four output ranges available in bipolar mode. See Function Table for details. All output ranges are with re-spect to a 5V reference input. When changing the LTC1588/LTC1589/LTC1592 to a new mode, the command word and data are given at the same time (24 or 32 bit). WhenC3COMMAND DON’T CARE DATA (16 BITS)C2C1C0XXXXD13D14D15D12D11D10D9D8D7D6D5D4D3D2D1D01588992 TD2MSBLSBC3COMMAND DON’T CARE DATA (14 BITS + 2 DON’T-CARE BITS)C2C1C0XXXXD13D12D11D10D9D8D7D6D5D4D3D2D1D0X X1588992 TD3MSBLSBC3COMMAND DON’T CARE DATA (12 BITS + 4 DON’T-CARE BITS)C2C1C0XXXXD11D10D9D8D7D6D5D4D3D2D1D0XXXX1588992 TD4MSBLSBINPUT WORD (LTC1592)INPUT WORD (LTC1589)INPUT WORD (LTC1588)LTC1588/LTC1589/LTC1592101112LTC1588/LTC1589/LTC15921588992faWhile not directly addressed by the simple equations in Tables 2 and 3, temperature effects can be handled just as easily for unipolar and bipolar applications. First, consult an op amp’s data sheet to find the worst-case V OS and I B over temperature. Then, plug these numbers in the V OS and I B equations from Table 3 and calculate the tempera-ture induced effects.For applications where fast settling time is important, Appli-cation Note 74, entitled “Component and MeasurementAdvances Ensure 16-Bit DAC Settling Time ,” offers a thor-ough discussion of 16-bit DAC settling time and op amp selection.Precision Voltage Reference Considerations Much in the same way selecting an operational amplifier for use with the LTC1592 is critical to the performance of the system, selecting a precision voltage reference also requires due diligence. The output voltage of the LTC1592is directly affected by the voltage reference; thus, any voltage reference error will appear as a DAC output voltage error.There are three primary error sources to consider when selecting a precision voltage reference for 16-bit applica-tions: output voltage initial tolerance, output voltage tem-perature coefficient and output voltage noise.Initial reference output voltage tolerance, if uncorrected,generates a full-scale error term. Choosing a referenceAPPLICATIO S I FOR ATIOW UUU Table 4. Partial List of LTC Precision Amplifiers Recommended for Use with the LTC1588/LTC1589/LTC1592,with Relevant SpecificationsAMPLIFIER SPECIFICATIONSVOLTAGE CURRENT SLEW GAIN BANDWIDTHt SETTLING POWER V OS I B A OL NOISE NOISE RATE PRODUCT with LTC1592DISSIPATIONAMPLIFIER µV nA V/mV nV/√Hz pA/√Hz V/µs MHzµsmWLT1001252800100.120.250.812046LT1097500.351000140.0080.20.712011LT1112 (Dual)600.251500140.0080.160.7511510.5/Op Amp LT1124 (Dual)70204000 2.70.3 4.512.51969/Op Amp LT14687510500050.62290 2.5117LT1469 (Dual)12510200050.622902.5123/Op Amp()5VVREF ()5VVREF ()16.5kAVOL1OP AMPV OS1 (mV)I B1 (nA)A VOL1 (V/V)V OS2 (mV)I B2 (mV)A VOL2 (V/V)V OS1 • 2.4 • I B1 • 0.0003 • A1 • 0 0 0INL (LSB)()5VVREF ()5VVREF ()1.5k AVOL1()66k A VOL2()131k A VOL1()131kA VOL1()131kA VOL2()131k A VOL2V OS1 • 0.6 • I B1 • 0.00008 • A2 • 0 0 0DNL (LSB)()5VVREF ()5VVREF V OS1 • 13.2 • I B1 • 0.13 •0 0 0UNIPOLAR OFFSET (LSB)()5VVREF()5V V REF ()5V V REF V OS1 • 13.2 • I B1 • 0.0018 • A5 •V OS2 • 26.2 •I B2 • 0.1 •BIPOLAR GAIN ERROR (LSB)()5V V REF ()5VV REF()()()5V V REF ()5V V REF A3 • V OS1 • 19.8 • I B1 • 0.01 • 0 A4 • V OS2 • 13.1 •A4 • I B2 • 0.05 • A4 • BIPOLAR ZERO ERROR (LSB)UNIPOLAR GAIN ERROR (LSB)()5V V REF ()5V V REF ()5V V REF ()5VV REF()5VV REFV OS1 • 13.2 • I B1 • 0.0018 • A5 •V OS2 • 26.2 •I B2 • 0.1 • Table 3. Easy-to-Use Equations Determine Op Amp Effects on DAC Accuracy in All Output RangesTable 2. Variables for Each Output Range That Adjust the Equations in Table 3OUTPUT RANGEA1A2A3A4A55V 1.12110V 2.23 1.5±5V 22 1.21 1.5±10V 44 1.21 2.5±2.5V 11 1.611–2.5V to 7.5V1.9310.51.513LTC1588/LTC1589/LTC15921588992faAPPLICATIO S I FOR ATIOW UUU with low output voltage initial tolerance, like the LT1236(±0.05%), minimizes the gain error caused by the refer-ence; however, a calibration sequence that corrects for system zero- and full-scale error is always recommended.A reference’s output voltage temperature coefficient af-fects not only the full-scale error, but can also affect the circuit’s INL and DNL performance. If a reference is chosen with a loose output voltage temperature coeffi-cient, then the DAC output voltage along its transfer characteristic will be very dependent on ambient condi-tions. Minimizing the error due to reference temperature coefficient can be achieved by choosing a precision reference with a low output voltage temperature coeffi-cient and/or tightly controlling the ambient temperature of the circuit to minimize temperature gradients.As precision DAC applications move to 16-bit and higher performance, reference output voltage noise may contrib-ute a dominant share of the system’s noise floor. This in turn can degrade system dynamic range and signal-to-noise ratio. Care should be exercised in selecting a voltage reference with as low an output noise voltage as practical for the system resolution desired. Precision voltage refer-ences, like the LT1236, produce low output noise in the 0.1Hz to 10Hz region, well below the 16-bit LSB level in 5V or 10V full-scale systems. However, as the circuit band-widths increase, filtering the output of the reference may be required to minimize output noise.Table 5. Partial List of LTC Precision References Recommended for Use with the LTC1588/LTC1589/LTC1592 with Relevant SpecificationsINITIAL TEMPERATURE0.1Hz to 10Hz REFERENCE TOLERANCE DRIFT NOISE LT1019A-5,±0.05%5ppm/°C 12µV P-P LT1019A-10LT1236A-5,±0.05%5ppm/°C 3µV P-P LT1236A-10LT1460A-5,±0.075%10ppm/°C 20µV P-P LT1460A-10LT1790A-2.5±0.05%10ppm/°C12µV P-PGroundingAs with any high resolution converter, clean grounding is important. A low impedance analog ground plane and star grounding techniques should be used. I OUT2 must be tied to the star ground with as low a resistance as possible.When it is not possible to locate star ground close to I OUT2,a low resistance trace should be used to route this pin to star ground. This minimizes the voltage drop from this pin to ground caused by the code dependent current flowing to ground. When the resistance of this circuit board trace becomes greater than 1Ω, a force/sense amplified con-figuration should be used to drive this pin (see Figure 2).This preserves the excellent accuracy (1LSB INL and DNL)of the LTC1588/LTC1589/LTC1592.An Isolated 16-Bit Subsystem Using the LTC1592The circuit in Figure 4 is a complete example of an optically isolated analog output subsystem that supports most of the legacy ranges that are still common in industrial environments. This circuit uses only two optoisolators,the load pulse (CS/LD) being derived from a series of transitions on the data line (SDI) after the clock (SCK) is halted high. If a single chip microcontroller with an auto-mated SPI interface is to be used, the SPI port can transfer the 24 bits as three bytes. Subsequently, the data output port pin can be reassigned to general purpose port opera-tion and exercised to produce a number of transitions to generate the load pulse. Alternatively, the entire sequence can be programmed bit by bit with a general purpose port.Figure 5 shows the timing.The DC/DC converter, Figure 3 based on the LT ®3439ultralow noise transformer driver provides a compact means of powering this circuit, and allows the output to deliver output current that is only limited by the LT1468capabilities. The output capability of the DC/DC converter itself is 80mA at ±12V and is available as demo board DC511A. This circuit as shown requires approximately 130mA of the 5V supply (no load). The total surface area required is less than 2 square inches.LTC1588/LTC1589/LTC159214Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.1516LTC1588/LTC1589/LTC1592LT/TP 0503 1K REV A • PRINTED IN USA© LINEAR TECHNOLOGY CORPORATION 20011630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 q FAX: (408) 434-0507 q 。

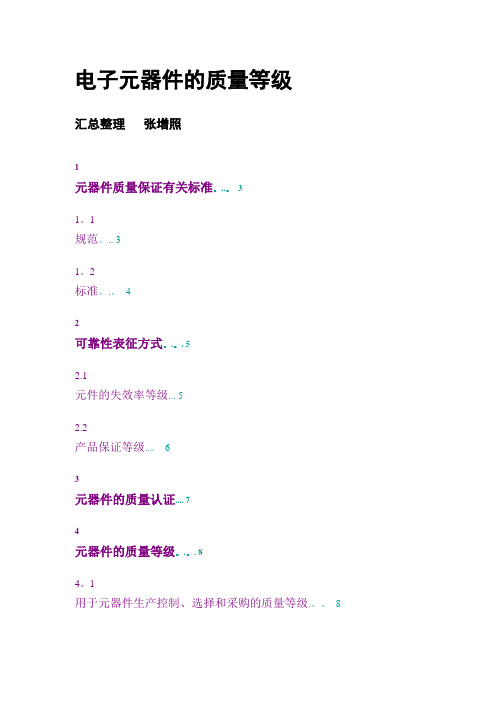

电子元器件的质量等级

电子元器件的质量等级汇总整理张增照1元器件质量保证有关标准。

..。

31。

1规范。

.. 31。

2标准。

.。

42可靠性表征方式。

.。

. 52.1元件的失效率等级 (5)2.2产品保证等级..。

63元器件的质量认证 (7)4元器件的质量等级。

.。

. 84。

1用于元器件生产控制、选择和采购的质量等级.。

84。

2用于电子设备可靠性预计的质量等级。

.。

104.3元器件两种质量等级的比较。

.. 105元器件的选用与质量标记。

(19)5。

1元器件的选用 (19)5.2质量标记.。

. 216结束语。

.。

. 22元器件质量保证有关标准为了保证军用元器件的质量,我国制订了一系列的元器件标准。

在七十年代末期制订的“七专”7905技术协议和八十年代初期制订的“七专"8406技术条件(以下统称“七专"条件),“七专"技术条件是建立我国军用元器件标准的基础,目前按“七专”条件或其加严条件控制生产的元器件仍是航天等部门使用的主要品种。

(注:“七专"指专人、专机、专料、专批、专检、专技、专卡)根据发展的趋势,“七专”条件将逐步向元器件的**军用标准(GJB)过渡。

因此,以下将主要介绍元器件**军用标准的有关情况。

从八十年代开始,我国军用标准化组织参照美国军用标准(MIL)体系建立了GJB 体系,其中元器件的标准有规范、标准、指导性技术文件三种形式:a。

规范-主要包括:元器件的总规范和详细规范,这两种规范统称产品规范。

b。

标准—主要包括:试验和测量标准、质量保证大纲和生产线认证标准、元器件材料和零件标准、型号命名标准、文字和图形符号标准等;c. 指导性技术文件—主要包括:指导正确选择和使用元器件的指南、用于电子设备可靠性预计的手册、元器件系列型谱等。

根据我国的具体情况,军标分为**军用标准、行业军用标准、企业军用标准三个级别。

下面对组成**军用元器件标准体系的三种形式:规范、标准和指导性技术文件分别举例作简要的介绍.1.1规范元器件规范主要包括:元器件的总规范(通用规范)和详细规范两个层次。

LTC1735CF资料

U W U PACKAGE/ORDER I FOR ATIO

TOP VIEW COSC 1 RUN/SS 2 ITH 3 FCB 4 SGND 5 VOSENSE 6 SENSE – 7 SENSE + 8 GN PACKAGE 16-LEAD NARROW PLASTIC SSOP 16 TG 15 BOOST 14 SW 13 VIN 12 INTVCC 11 BG 10 PGND 9 EXTVCC

元器件交易网

FEATURES

s s s s s s s s s

LTC1735 High Efficiency Synchronous Step-Down Switching Regulator DESCRIPTIO