可复用微处理器片上调试功能的设计与实现

嵌入式作业题答案

嵌入式系统原理及应用作业题答案第1章嵌入式系统概述1. 什么是嵌入式系统?嵌入式系统的组成?答:嵌入式系统是以应用为中心,以计算机技术为基础,并且软硬件可裁剪,适用于应用系统对功能、可靠性、成本、体积、功耗有严格要求的专用计算机系统。

组成:嵌入式处理器、外围设备、操作系统、应用软件。

2. 典型的嵌入式处理器有哪些?3. 答:微处理器、微控制器、DSP处理器、片上系统SOC。

4. 典型的RTOS操作系统有哪些?5. 答:嵌入式LinUX、卩CLinUX、WindoWS Embedded CE、WindoWS Embedded ComPaCt 7 > μC/OS-II > μC/OS-III、VXWorks、eCos 等。

6. 列举身边的嵌入式应用产品?7. 嵌入式系统的设计可以分成四个阶段:需求分析、架构设计和概要设计、详细设计和开发、测试反馈。

第2章COrteX-M体系结构8. ARM COrteX系统的处理器分为: A 、__________ R ____ 、____ M ____ 。

9. ARM COrteX-M3为32位微控制器,请问32位指的是CPlJ字长。

10. 3、COrteX-M3处理器能够以小端格式或大端格式访问存储器中的数据字,而访问代码时始使用小端格式______11. ARM COrteX-M3体系结构采用哈佛总线结构,拥有独立的指令总线和数据总线,可以让取指与数据访问并行进行。

12. CM3寄存器分为通用寄存器,包括R0~R15和特殊功能寄存器,包括程序状态寄存器、异常屏蔽寄存器、控制寄存器。

13. 寄存器R13是堆栈指针寄存器。

14. 寄存器R14是程序连接寄存器。

15. 寄存器R15是程序PG16. CM3的堆栈指针分为__MSP__ _=PSP r O存储器堆栈堆栈分为:向上生长(即向高地址方向生长)的递增堆栈;向下生长(即向低地址方向生长),称为递减堆栈。

(完整word版)嵌入式系统模拟试题及答案

学习中心/函授站_姓名学号西安电子科技大学网络与继续教育学院2014学年下学期《嵌入式系统》期末考试试题(综合大作业)考试说明:1、大作业于2014年12月25日下发,2015年1月10日交回;2、考试必须独立完成,如发现抄袭、雷同均按零分计;3、答案须手写完成,要求字迹工整、卷面干净。

一、问题简述(每小题4分,共20分)1、简述嵌入式系统的定义和组成结构。

答:嵌入式系统是以应用为中心,以计算机技术为基础,并软硬件可剪裁、功能、,可靠性、体积、重量、成本、功耗、成本、安装方式等方面符合要求的专用计算机系统。

嵌入式系统一般由嵌入式微处理器、存储与I/O部分、外设与执行部分、嵌入式软件等四个部分组成.2、简单说明ARM微处理器的特点。

答:(1) 体积小、低功耗、低成本、高性能。

(2)支持Thumb(16位)/ARM(32位)双指令集,能很好地兼容8位/16位器件。

(3)大量使用寄存器,指令执行速度更快。

(4)大多数数据操作都在寄存器中完成,通过Load/Store结构在内存和寄存器之间批量传递数据。

(5)寻址方式灵活简单,执行效率高。

(6) 指令长度固定.3、简述嵌入式系统产品的设计和开发过程。

答:①在嵌入式系统的开发过程中,一般采用的方法是首先在通用PC机上的集成开发环境中编程;②然后通过交叉编译和链接,将程序转换成目标平台(嵌入式系统)可以运行的二进制代码;③接着通过嵌入式调试系统调试正确;④最后将程序下载到目标平台上运行。

要强调,选择合适的开发工具和调试工具,对整个嵌入式系统的开发都非常重要。

4、简述嵌入式系统设计中要考虑的因素。

答:在嵌入式系统的开发过程中,要考虑到实时性、可靠性、稳定性、可维护性、可升级、可配置、易于操作、接口规范、抗干扰、物理尺寸、重量、功耗、成本、开发周期等多种因素。

5、什么是BootLoader,了解其在嵌入式系统中作用。

答:就是启动载入或引导加载又叫自举装载.由于系统加电后需要首先运行BootLoader这段程序,因此它需要放在系统加电后最先取指令的地址上。

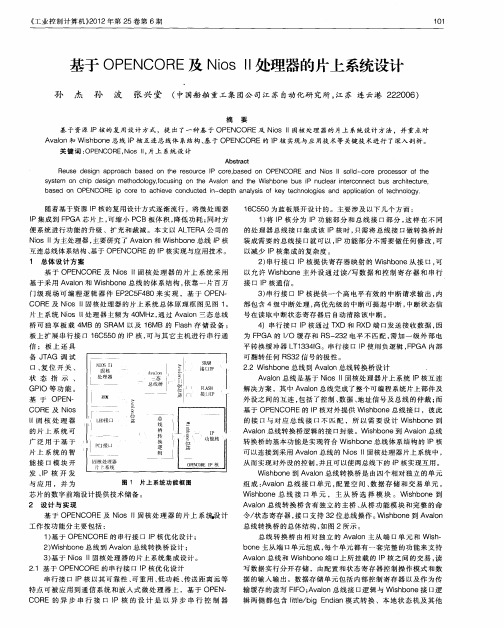

基于OPENCORE及NiosⅡ处理器的片上系统设计

桥可 独享板 载 4 MB 的 S A 以 及 1 MB 的 Fa h存 储 设 备 ; RM 6 ls 板 上 扩 展 串行 接 口 1 C 5 6 5 O的 I P核 , 与 其 它 主 机 进 行 串行 通 可

信 ;板 上 还 具 备 J AG 调 试 T

随着 基 于 资 源 I 的 复用 设 计 方 式逐 渐 流 行 ,将 微 处 理器 P核

1C 5 6 5 0为 蓝板 展 开 设 计 的 。 主要 涉 及 以下 几 个 方 面 :

I 成 到 F GA 芯 片 上 , 缩 小 P P集 P 可 CB板 体 积 , 降低 功 耗 ; 时方 同 便 系 统 进 行 功 能 的 升 级 、扩 充 和 裁减 。本 文 以 A T R L E A公 司 的

Ni l 主处 理 器 , 要研 究 了 A ao o l s 为 主 v ln和 Wi b n s o e总线 I h P核

1 将 I 分 为 J 能 部 分 和 总 线 接 口部 分 , 样 在 不 同 ) P核 P功 这

的处 理 器 总 线 接 口集 成 该 I 时 , 需 将 总线 接 口做 转 换 桥 封 P核 只

Ab ta t s rc

Reu e esgn s d i ap o ch as d pr a b e on h r o c I t e es ure P cor b e on PENCORE e,as d O an Ni l s i d os l ol d—c e r c s r o h or p o es o f t e

4 )串行 接 口 l 通 过 T D 和 R D 端 口发 送 接 收 数 据 , P核 x X 因

芯片设计中的片上系统设计方法研究与实现

芯片设计中的片上系统设计方法研究与实现随着信息技术的快速发展,芯片设计变得越来越重要。

在芯片设计过程中,片上系统设计方法是一项关键任务。

本文将探讨片上系统设计方法的研究与实现,在不设计政治的前提下,深入介绍相关概念、方法和实践。

1. 片上系统设计方法概述片上系统(System on Chip,SoC)是一种将多个功能集成在一个芯片上的设计方法。

片上系统设计方法旨在实现高度集成、高性能、低功耗、低成本的芯片。

其设计是将处理器核、外围设备、存储器等功能模块集成在一个芯片上,实现功能的同时尽可能减小功耗和占用面积。

2. 黑箱设计与白箱设计在片上系统设计中,存在两种主要的设计方法:黑箱设计和白箱设计。

黑箱设计是一种模块化的设计方法,各功能模块相互独立,通过接口进行连接。

在黑箱设计中,各模块的实现细节对其他模块来说是透明的,只关注功能的输入和输出。

这种设计方法简化了设计过程,提高了设计效率,但在整合时可能出现接口不兼容等问题。

白箱设计是一种更细粒度的设计方法,将各模块的实现细节考虑在内。

在白箱设计中,设计者需要深入了解各个模块的实现,并在设计过程中进行优化和调整。

这种设计方法可以提高整体性能和灵活性,但对设计者的要求更高,也更加复杂。

3. 片上系统设计流程片上系统设计流程包括需求分析、体系结构设计、功能模块设计、验证和调试等环节。

需求分析阶段,设计者根据芯片功能的需求,进行功能和性能的分析。

这一阶段需要考虑功耗、面积、性能等要素,确定整体设计的目标和约束条件。

体系结构设计阶段,设计者将整体结构分成多个功能模块,确定各个模块之间的连接方式。

这一阶段需要对芯片功能的实现方式进行抽象和细化,确定各个模块的功能和接口。

功能模块设计阶段,每个模块的实现细节被具体化。

设计者需要设计各个模块的电路、逻辑和物理布局,确保每个模块的功能和性能达到预期。

验证和调试阶段,设计者对设计的芯片进行功能和性能的验证,并进行调试和优化。

用于8051微控制器的片上调试系统的硬件设计

武汉 407) 3 0 4 ( 中科 技大 学 电 子科 学 与 技术 系 华

摘

要

为工业用 8 5 0 1微控制器设计 了一个片上调试 系统 , 将调试功 能集 成到单片机芯片 内部 。该 系统基于专用集

成 电路 的设 计流程设 计 , 不仅具有控制 85 0 1单片机挂 起 、 正常运行 、 步运行 和指令跳 转 的能力 , 单 而且能够 读写 片 内寄存

sa d r TAG.I sv rf d o l xSx 3 4 0 F tn adJ twa e ie n Xin ’ c sቤተ መጻሕፍቲ ባይዱ0 PGA n R t M I . 8, tc n lg irr . s l h ws i i a dP& wihS C 0 1 / m eh oo yl a y Re ut s o b s

( p r me to e to isS in e a d Te h o o y De a t n fElc r n c c e c n c n lg ,H u z o g Un v r i fS in e a d Te h o o y,W u a 4 0 7 ) a h n ie st o ce c n c n l g y hn 3 0 4

常见嵌入式微处理器调试技术综述

关 键词 : 片上调 试 ; 处理 器 ; 界 扫描 微 边

D I 码 :0 3 6 / .s . 0 2— 2 9 2 1 .4 0 5 O 编 1 . 9 9 ii n 1 0 2 7 . 0 0 .0 s 1

中图分 类号 :P 3 章 编号 :0 2— 2 9 2 1 )4—0 1 0 10 2 7 (0 10 06— 5

同时极 大增加 了设 计难 度 和复 杂度 。如果在 设计 使 用 中 出现硬件 或 者 软 件 的错 误 , 需 要 通 过 各种 手 就

段对 微 处理 器 进 行 调 试 ( e u ) 以发 现 导 致 错 误 D bg ,

D b gO D 。在线仿真器采用仿真头取代 目标板 eu , C ) 上的处理器 , 以完全仿 真微处理器芯 片的运行。 可 片上调 试是 在处 理 器 内部 嵌 入 额 外 的控 制 模块 , 以 交叉调试的方式令调试主机可 以通过特定的通信接 口访 问处理 器 的 内部 资源 ( 寄存 器 、 储 器等 ) 执 存 并

NO 4 .

微

处

理

机

第 4期

2 1 年 8月 01

A g 2 1 u ., 01

MI CR0PR0C S ES 0RS

常 见嵌 人 式 微 处 理 器 调试 技 术 综 述

刘 鹏 , 立新 , 于 覃 辉 , 海 洋 周

( 北京 微 电子技 术研 究所 , 北京 10 7 ) 0 0 6

t n a o a io i nd c mp rs n. o

Ke y wor ds: On —Ch p De g; c o r c so s; u ay S a i bu Mir p o e s r Bo nd r c n

计算机三级(嵌入式系统开发技术)机试模拟试卷13(题后含答案及解析)

计算机三级(嵌入式系统开发技术)机试模拟试卷13(题后含答案及解析)题型有:1. 选择题 2. 填空题 3. 综合题选择题1.下列产品中不属于嵌入式系统的是( )。

A.有线电视机顶盒B.服务器C.电饭煲D.路由器正确答案:B解析:广义上讲,凡是带有微处理器的专用软硬件系统都可称为嵌入式系统。

狭义上讲,嵌入式系统强调那些使用嵌入式微处理器构成的具有自己的操作系统和特定功能、用于特定场合的独立系统。

嵌入式系统以应用为中心、以计算机技术为基础、软硬件可裁剪、功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

选项中A、C、D均属于嵌入式系统;而服务器是网络环境中的高性能计算机,不属于嵌入式系统。

故本题选择B。

2.下面关于嵌入式系统逻辑组成的叙述中,错误的是( )。

A.嵌入式系统由硬件和软件两部分组成B.嵌入式系统硬件的主体是中央处理器(CPU)和存储器C.嵌入式系统的CPU比通用计算机简单得多,它们都是8位字长的处理器D.嵌入式系统通过输入输出(I/O)接口和输入/输出设备与外部世界进行联系正确答案:C解析:嵌入式系统与通用计算机一样,也由硬件和软件两部分组成。

硬件的主体是CPU和存储器,它们通过I/O接口和I/O设备与外部世界联系。

现在嵌入式系统中使用最多的还是8位和16位CPU,但32位是技术发展的主流。

故本题选择C。

3.按照软硬件技术的复杂程度嵌入式系统分为低端系统、中端系统和高端系统三大类,下面有关低端系统的叙述中错误的是( )。

A.硬件大多采用4位或8位单片机B.由监控程序对系统进行控制,不使用操作系统C.家用洗衣机、吸尘器、电磁炉等属于低端嵌入式应用系统D.它们正在被32位的高端系统所取代正确答案:D解析:嵌入式系统的分类有多种。

按系统的软硬件技术复杂度,嵌入式系统分为低端系统、中端系统和高端系统。

其中低端系统硬件大多采用4位或8位单片机,不使用操作系统,由监控程序对系统进行控制,在工控领域和白色家电领域占主导地位。

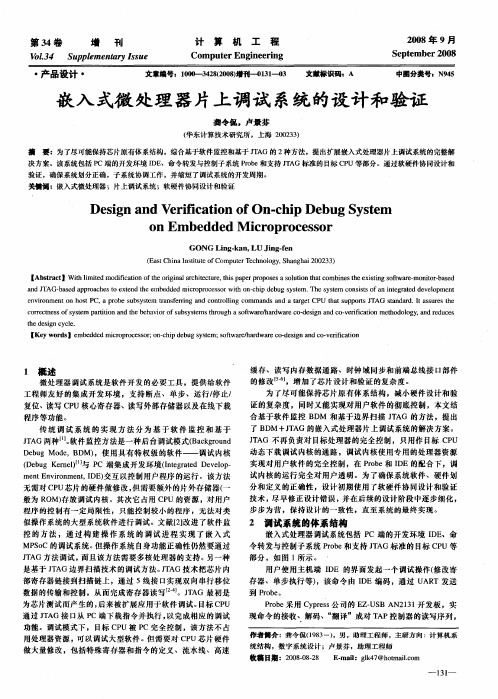

嵌入式微处理器片上调试系统的设计和验证

De i n a d Ve i c to f n c i b g S s e sg n rf a i n 0 — h p De u y t m i O

0 Em be n dde M i r pr e s r d c o oc s o

片上系统(SOC)设计与EDA

片上系统(SOC)设计与EDA摘要:利用EDA工具和硬件描述语言(HDL),根据产品的特定要求设计性能价格比高的片上系统,是目前国际上广泛使用的方法。

与传统的设计方法不同,在设计开始阶段并不一定需要具体的单片微控制器(MCU)和开发系统(仿真器)以及带有外围电路的线路板来进行调试,所需要的只是由集成电路制造厂家提供的用HDL描述的MCU核和各种外围器件的HDL模块。

设计人员在EDA工具提供的虚拟环境下,不但可以编写和调试汇编程序,也可以用HDL设计、仿真和调试具有自己特色的快速算法电路和接口,并通过综合和布线工具自动转换为电路结构,与制造厂家的单元库、宏库及硬核对应起来,通过仿真验证后,即可投片制成专用的片上系统(SOC)集成电路。

关键词:片上系统(SOC) EDA 硬件描述语言(HDL)单片机一、芯片设计和制造是电子工业发展的基础近10年来我国的电子工业取得了很大的进步,无论在消费类产品如电视、录像机还是在通信类产品如电话、网络设备方面,产品的档次和产量都有快速的提高。

但这些产品的核心部件——芯片,大多需要进口,每年需要花费大量外汇来购买。

许多产品技术档次的提高也受制于芯片。

由于高档产品使用的新芯片价格昂贵,研制能在国际高档产品市场竞争的电子产品和设备非常困难。

我国目前能在国际市场上竞争的电子产品大多数还是中低档的。

由于核心芯片大多需要进口,因此利润非常低,主要依靠我国相对较廉价的劳动力才能在市场中生存。

在21世纪的头5年中,如果我们还不能掌握核心芯片的设计和制造技术,电子工业很难在20年内赶上国际先进水平。

核心芯片的设计是高级技术,但并非每一种核心芯片都是非常难设计和制造的,大多数中低档电子产品中的片上系统SOC(System on Chip)并不复杂。

目前,我国许多电子工程师已掌握了传统的微控制器系统开发手段:编写汇编程序,利用开发系统进行仿真来调试汇编程序和接口信号。

在这一基础上,如果掌握一些常用的EDA工具,了解复杂数字系统的设计思路并能主动深入地学习HDL语言,不但能设计出具有自己知识产权的微控制器和线路板,甚至能设计出几万门甚至几百万门的专用数字信号处理芯片和片上系统。

synopsys ic compiler 介绍、安装、调试和设计流程

synopsys ic compiler 介绍、安装、调试和设计流程加入该小组相关分类:petery (组长) 2007/9/23 顶楼举报一、介绍synopsys ic compiler (v2005.linux)是基于Galaxy设计平台开发的产品。

主要的工具有:LEDALEDA是可编程的语法和设计规范检查工具,它能够对全芯片的VHDL和Verilog描述、或者两者混合描述进行检查,加速SoC的设计流程。

LEDA预先将IEEE可综合规范、可仿真规范、可测性规范和设计服用规范集成,提高设计者分析代码的能力VCSVCS是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言、PLI和SDF。

VCS具有目前行业中最高的模拟性能,其出色的内存管理能力足以支持千万门级的ASIC设计,而其模拟精度也完全满足深亚微米ASIC Sign-Off 的要求。

VCS结合了节拍式算法和事件驱动算法,具有高性能、大规模和高精度的特点,适用于从行为级、RTL到Sign-Off等各个阶段。

VCS已经将CoverMeter 中所有的覆盖率测试功能集成,并提供VeraLite、CycleC等智能验证方法。

VCS 和Scirocco也支持混合语言仿真。

VCS和Scirocco都集成了Virsim图形用户界面,它提供了对模拟结果的交互和后处理分析。

SciroccoScirocco是迄今为止性能最好的VHDL模拟器,并且是市场上唯一为SoC验证度身定制的模拟工具。

它与VCS一样采用了革命性的模拟技术,即在同一个模拟器中把节拍式模拟技术与事件驱动的模拟技术结合起来。

Scirocco的高度优化的VHDL编译器能产生有效减少所需内存,大大加快了验证的速度,并能够在一台工作站上模拟千万门级电路。

这一性能对要进行整个系统验证的设计者来说非常重要。

VeraVera验证系统满足了验证的需要,允许高效、智能、高层次的功能验证。

基于ARM_Cortex-M3的SoC系统设计_

核发出中断请求信号,包含最多240个中断请求,以及1个不可屏蔽中断。

NVIC是与CPU紧密耦合的,它还包含了若干个系统控制寄存器。

2.2.3 总线系统总线系统用于将Cortex-M3内部的各个功能部件连接在一起。

总线系统包括:①内部总线系统;②处理器核内部的数据通道;③AHB Lite接口单元。

2.2.4 调试子系统作为Cortex-M3处理器重要的一部分,调试子系统提供下面的功能。

①管理调试控制、程序断点、以及数据监控点。

②当产生调试事件时,它将处理器核设置为停止状态。

此时,可以在该点分析处理器的状态,如寄存器值和标志。

2.3 异常处理与中断向量表设计Cortex-M3在内核水平上搭载了一个异常响应系统,支持为数众多的系统异常和外部中断。

向量中断控制器(NVIC)以存储器映射的方式来访问,除了包含控制寄存器和中断处理的控制逻辑之外,NVIC还包含了MPU的控制寄存器、SysTick定时器以及调试控制。

2.4 地址译码器和多路复用器设计本系统基于AHB-Lite所构建的Cortex-M3 SoC系统设计包含了地址译码器和多路复用器。

在系统中,来自不同从设备的响应信号,包括:HRDATA、HREADY和HRESP连接到多路复用器的输入,根据地址译码器所生成的选择信号,多路复用器将选择的从设备响应信号送给主设备。

其中HRDATA[31:0]是来自多路复用器到主设备的读数据,由多路复用器指向主设备;HREADY是来自多路复用器到主设备的准备信号,由多路复用器指向主设备和从设备,当该位为高时,该信号表示到主设备和先前完成传输的所用从设备。

2.5 APB子系统该APB子系统的顶层是AHB-Lite总线接口,可以与内核的AHB总线进行连接。

子系统内部包括的外设有定时器、UART、双输入定时器、看门狗电路、AHB到APB的桥接器、异步中断信号等。

表2为APB系统IRQ分配表。

表2 APB系统IRQ分配IRQ Device0UART 0 receive interrupt1UART 0 transmit interrupt2UART 1 receive interrupt3UART 1 transmit interrupt4UART2 receive interrupt5UART 2 transmit interrupt8Timer 09Timer 110Dual-input timer11Not used12UART 0 overflow interrupt13UART1 overflow interrupt14UART 2 overflow interrupt15Not used in APB subway16-31Not used in APB subway a: Reserved for GPIO in AHBb: Reserved for DMA2.6 时钟和复位电路设计本系统片上SoC系统主要包含HCLK、PCLK、PCLKG等三个时钟,HCLK时钟主要用于内核的工作时钟以及驱动片内高性能总线上挂载的外设。

SOC片上嵌入式微处理器核的可测试性技术

Ke wo d :S y r s OC;e b d e co r c s o o e e tn e i m o t r- a e e ̄ts ;had r- a e e ̄ts m e d d mir p o e s rc r ;tsi gd sg s fwa e b s d s l e t r wa e b s d s l e t

Te tn e h o o y o OCi g t c n l g fS e e de c 0 r c s 0 o e

L i i Ya n e g e Ja n Yu fn

( c o l fElcrncE gn e ig S h o e to i n ie rn ,Gul n v ri f lcrnctc n lg o in u iest o e to i e h oo y,Gul 4 0 4 i y e in5 1 0 ) i

t ie e in f rt sig crut n t e mir p o e s rc r s tc ud dvd h s e h d n oh r wa eb s ds l t s an d d sg o e t ic isi h co r c s o o e ,i o l iiet e em t o sit a d r - a e ef e t n - m eh d lg n o t r- a e e ̄ts e h d lg . Th o t ru e i d fd sg o e tn eh d lg O t s t o oo ya d s fwa eb s d s l e tm t o oo y efs e s d k n s o e in f rts ig m t o oo y t e t t emir p o e s rc r s tc n an d t e me h d t a n e td kn so h co r c s o o e ,i o ti e h t o h tis re id fDFT e tn ic i a d t e fncina e t g tsi g cru t n h u to lt si n m eh dt a sb s do h S tc n lg . e h a e a eat sig fa wo kw hc su e Ot s i l t o h twa a e nt eBI T e h oo y Th n t ep p rg v e tn r me r ihwa s d t e tasmp e 8 btp o e s rc r .Th o t r- a e e ̄ts e h o o y u e h n tu t n ft ep o e s rt o lt h ef i r c so o e es fwa e b s d s l e tt c n lg s d t ei sr ci so h r c s o Oc mp e et es l- o ts . The e ci e h dv n a e n ia v n a e ft e et y em eh d n o e a t dt ef t r f r cs et n wed s rb dt ea a tg sa d ds d a t g so h s wo tp t o sa d fr c se h u u eo o e — p

嵌入式处理器在片调试功能的设计与实现

中图法分类号

De i n a d I pl m e t to f On c i b g Fe t r s i s g n m e n a i n o - h p De u a u e n Em be d d Pr c s o d e o esr

Hu n in ’ a g Hal i Fa n r i Xu To g ’ Zh n fi Z e g B oin ’ C o Fe ’ Ch n Lin 3 n Do g u ’ n ’ uPe ge。 ’ h n aj a a i ’ e a g’

J l ,2 0 uy 0 6

嵌 入式 处 理器 在 片调 试 功 能 的设 计 与 实现

黄海林 范东睿” ຫໍສະໝຸດ 许 北京 103) 00 9

朱鹏飞。 郑保建” j 陈 亮 ’ 曹 } ’ 。

北京 10 8 ) 0 0 0

( 国科 学 院 计 算 技 术 研 究 所 系 统 结 构研 究 室 中 ( 国科 学 院研 究 生 院 中

维普资讯

第 1 8卷

第 7期

计 算机 辅 助设计 与 图形学 学报

J OURNAL OF COM P UTE AI D R— DE DES GN & C I OM P UTER APHI S GR C

V O . 8.NO. 11 7

20 0 6年 7月

( o ue ci c r L brtr ,I stt o mp t gT c nl y,C iee a e y0 c ne,B i n 10 8 ) C mp t Arht t e aoaoy nt ue fC r eu i o ui eh oo n g hns d m Ac ,Si cs e ig 0 0 0 e j ( a u t Unvr t C ie Ac e y Si cs e ig 10 3 ) Grd ae iesy i hns a m ce e,B i n 0 0 9 e d n j ( L CDeg .Ld , e ig 10 8 ) B X I s nC 。 t B i n 0 0 0 i o j

SOPC系统设计与实践-要点归纳

《现代电子设计技术》课程要点归纳第1章概述1 SOPC名词解释2 VHDL名词解释:Very-High-Speed Integrated Circuit HardwareDescription Language超高速集成电路硬件描述语言3 集成电路发展的6个阶段:晶体管,小规模集成电路(SSI),中规模集成电路(MSI),大规模集成电路(LSI),超大规模集成电路(VSLI),片上可编程系统(SOC)4 片上系统(SOC)基本概念:SoC (System on Chip,片上系统) 是ASIC(Application Specific IntegratedCircuits) 设计方法学中的新技术,是指以嵌入式系统为核心,以IP 复用技术为基础,集软、硬件于一体,并追求产品系统最大包容的集成芯片.狭意些理解,可以将它翻译为“系统集成芯片”,指在一个芯片上实现信号采集、转换、存储、处理和I/O 等功能,包含嵌入软件及整个系统的全部内容;广义些理解,可以将它翻译为“系统芯片集成”,指一种芯片设计技术,可以实现从确定系统功能开始,到软硬件划分,并完成设计的整个过程.5 SOC设计方法学中的系统集成芯片技术包括的三个方面:设计重用技术,软硬件协同设计技术,纳米级电路设计技术6 SOC设计重用技术的概念、特点、构成及要求:主要指的是IP重用技术,重用预先设计并经验证的模块(可从第三方获得),以达到缩短设计周期、加快投入市场的目的;它由IP的设计和IP的使用两个部分构成,要求所设计的IP可重用、可配置和可升级,目标是IP能即插即用。

7 软硬协同技术的概念及其构成:一般来说,面向SOC的软硬件协同设计理论是从一个给定的系统描述着手,通过有效地分析系统任务和所需的资源,采用一系列变换方法并遵循特定的准则自动生成符合系统功能要求、符合系统约束的硬件和软件架构。

软硬协同主要包括系统描述、软硬件划分、软硬件协同综合以及软硬件协同模拟与验证。

第四部分2:FPGA配置及片内调试技术

第四部分:FPGA设计基础(2)北京理工大学雷达技术研究所陈禾FPGA配置及片内调试技术{边界扫描原理{FPGA配置的基本方式{高级配置环境{基于嵌入式处理器的配置技术{基于Internet的可重构逻辑实现{ChipScope Pro片内调试系统边界扫描原理{IEEE Standard 1149.1 -Test Access Port and Boundary-Scan Architecturez JTAG是JOINT TEST ACTION GROUP组织最初提出的,最终由IEEE批准并且标准化的。

IEEE 1149.1一般也俗称JTAG调试标准。

z在JTAG调试标准当中,边界扫描(Boundary-Scan)是一个很重要的概念。

边界扫描技术的基本思想是在靠近芯片的输入输出管脚上增加一个移位寄存器单元。

因为这些移位寄存器单元都分布在芯片的边界上(周围),所以被称为边界扫描寄存器(Boundary-Scan Register Cell)。

边界扫描原理{当芯片处于调试状态的时候,这些边界扫描寄存器可以将芯片和外围的输入输出隔离开来。

通过这些边界扫描寄存器单元,可以实现对芯片输入输出信号的观察和控制。

{对于芯片的输入管脚,可以通过与之相连的边界扫描寄存器单元把信号(数据)加载到该管脚中去。

{对于芯片的输出管脚,也可以通过与之相连的边界扫描寄存器“捕获”(capture)该管脚上的输出信号。

边界扫描原理{在正常的运行状态下,这些边界扫描寄存器对芯片来说是透明的。

{芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。

{一般的芯片都会提供几条独立的边界扫描链,用来实现完整的测试功能。

边界扫描链可以串行的输入和输出,通过相应的时钟信号和控制信号,就可以方便的观察和控制处在调试状态下的芯片。

利用边界扫描链可以实现对芯片的输入输出进行观察和控制。

FT-2000+高性能通用微处理器数据手册说明书

FT-2000+高性能通用微处理器数据手册(V2.1)天津飞腾信息技术有限公司二零二零年五月版本历史以下为此文档释放过的更新版本版权所有©天津飞腾信息技术有限公司2019。

此文档用于指导用户的相关应用和开发工作。

天津飞腾信息技术有限公司对此文档内容拥有版权,并受法律保护。

目录目录 (4)1简介 (1)1.1技术指标 (1)1.2结构描述 (2)1.3产品形态 (4)1.4最大功耗 (5)2接口描述 (6)2.1DDR接口 (6)2.2PCIE接口 (6)2.2.1翻转说明 (6)2.2.2寄存器说明 (7)2.3LPC接口 (16)2.3.1寄存器说明 (16)2.4SPI接口 (20)2.4.1寄存器说明 (20)2.5UART接口 (28)2.5.1寄存器说明 (29)2.6I2C接口 (42)2.6.1寄存器说明 (42)2.7WDT接口 (57)2.7.1寄存器说明 (57)2.8GPIO接口 (59)2.8.1GPIO复用说明 (59)2.8.2GPIO寄存器说明 (62)2.9调测试接口 (65)3外设中断说明 (66)4电气特性 (67)4.1极限工作条件 (67)4.2工作电压范围 (67)4.3工作电流范围 (67)4.4通用引脚电气特性 (68)4.5PCIE引脚电气特性 (68)4.5.1发送引脚电气特性 (69)4.5.2接收引脚电气特性 (69)4.5.3时钟电气特性 (69)4.5.4参考电阻电气特性 (70)4.6DDR引脚电气特性 (70)5封装数据 (71)6装焊温度曲线 (72)7引脚描述 (74)7.1通用IO类引脚(123PIN) (74)7.2PCIE引脚(149PIN) (80)7.3DDR4引脚(1280PIN) (85)7.4电源引脚(2024PIN) (140)8产品标识 (147)1简介FT-2000+处理器芯片集成64个自主开发的ARMv8指令集兼容处理器内核FTC662,采用片上并行系统体系结构。

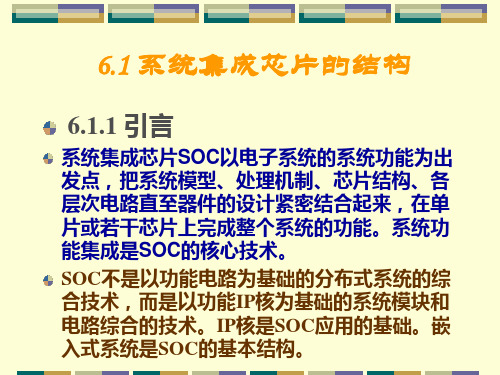

第6章SOC的体系结构

超流水线技术

提高流水线处理效率的另一个方法是缩短机器周期。 一般是将一个机器周期划分为若干个子周期,每个子 周期均发射一条新的指令,亦即每个机器周期发射多 条指令,从而提高计算机的性能。这种处理方式称为 超流水线处理技术。

取指1 取指2 译码 执行 存贮1 存贮2 检查标志 写结果 取指3 取指4 译码 执行 存贮3 存贮4 检查标志

(2) 可扩展性:所有的数据结构和接口应能方便加入新 的模块。

(3) 可综合性:处理器核的描述应该能够综合,以得到 实际电路的实现。

(4) 可测试性:处理器核的设计应该便于进行系统测试 和性能分析。

(5) 分布性:处理器的控制设计成分布式控制,便于指 令集扩展和处理器适应新的应用要求。分布式控制主要 负责流水级管理和每个流水级之间的状态通信。

微指令的结构限制了CISC CPU速度的进一步提 高。

CISC结构不利于并行处理方法。

6.1.3 嵌入式软件

有些SOC需要嵌入式实时操作系统(Real Time Operational System,简称为RTOS)的支持。

嵌入式实时操作系统是计算机操作系统的技术 和设计理念在嵌入式系统中的应用。

6.2 SOC中的嵌入式精简指令集处理 器RISC

CPU核

地址产生电路

运算电路

时序控制电路

指令译码 取指电路

DSP核

地址产生电路

运算电路

指令译码

CPU与DSP同指令流、同地址

CPU核

地址产生电路

运算电路

时序控制电路

指令译码 取指电路

DSP核 运算电路 指令译码

6.2.6 RISC核的设计

RISC核的设计原则:

(1) 模块化:若需加入新的指令,只需要修改相关的部 分,系统结构不应变化。

SoC介绍

3 SoPC

以往的SoC 设计依赖于固定的ASIC ASIC。 以往的SoC 设计依赖于固定的ASIC。其设计方法通常采用全定制和 半定制电路设计方法,设计完成后如果不能满足要求, 半定制电路设计方法,设计完成后如果不能满足要求,经常需要重 新设计再进行验证,这将导致开发周期变长,开发成本增加。另外, 新设计再进行验证,这将导致开发周期变长,开发成本增加。另外, 如果要对固定ASIC 的设计进行修改、升级, 如果要对固定ASIC 的设计进行修改、升级,也将花费昂贵的代价进 行重复设计。 比较,可编程逻辑器件(PLD) (PLD)的设计要灵活得 行重复设计。与ASIC 比较,可编程逻辑器件(PLD)的设计要灵活得 它不仅开发周期较短,而且规模效应具有成本优势。 多,它不仅开发周期较短,而且规模效应具有成本优势。 chip:片上可编程系统) SOPC (System on a programmable chip:片上可编程系统)是 Altera公司提出来的一种灵活 高效的解决方案,它将处理器、 公司提出来的一种灵活、 Altera公司提出来的一种灵活、高效的解决方案,它将处理器、存 储器、I/O口 LVDS、CDR等系统设计需要的东西集成到一个PLD器件 等系统设计需要的东西集成到一个PLD 储器、I/O口、LVDS、CDR等系统设计需要的东西集成到一个PLD器件 构建成一个可编程的片上系统,它所具有的灵活性、 上,构建成一个可编程的片上系统,它所具有的灵活性、低成本可 让系统设计者获益非浅。 让系统设计者获益非浅。 技术和可编程逻辑技术结合的产物, SoPC 是SoC 技术和可编程逻辑技术结合的产物,是一种特殊的嵌入 式系统。首先它是SoC SoC, 式系统。首先它是SoC,即可以由单个芯片完成整个系统的主要逻辑 功能;其次,它还是可编程系统,具有灵活的设计方式,可裁减、 功能;其次,它还是可编程系统,具有灵活的设计方式,可裁减、 可扩充、可升级,并具备一定的系统可编程功能。 可扩充、可升级,并具备一定的系统可编程功能。

TMS320系列DSP原理结构及应用

XINTF和并行I/O口; —标准的数学列表。 ◆时钟和系统控制

控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调 节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的 输入时钟频率。

引导模式选择见教材P248中表9.3-1。

第九章 TMS320F2833x系列DSC的硬件结构

9.3 TMS320F2833x 系列DSC的内核

3. F2833x的存储单元

5.存储器映射 F2833x DSC有两个独立的存储空间,即片内存储器和外部

存储器。片内存储器和外部存储器都可以用作数据存储空间和程 序存储空间。片内存储器的空间大小为128K×16,分为高16K 和低16K,包括256K×16位的FLASH,34K×16位的SRAM、 8K×16位的Boot ROM和1K×16位的OTP ROM。

DSC片内存储器与CPU之间数据读写和读取程序执行语句 的操作是通过三条总线(Memory Bus)完成。这三条总线分别 是程序读总线(PrgramRead Bus)、数据读总线(Data Read Bus)和数据写总线(Data Read Bus)。其中,程序读总线由 22根地址线和32位的数据总线组成。数据读和写总线是由32根 地址总线和32位的数据总线组成。32位的数据总线保证了每个周 期内进行32位的操作。

表9.3-2 Flash存储器块的地址分配

地址范围

0x300000-0x307FFF 0x308000-0x30FFFF 0x310000-0x317FFF 0x318000-0x31FFFF 0x320000-0x327FFF 0x328000-0x32FFFF 0x330000-0x337FFF 0x338000-0x337F7F 0x337F80-0x337FF5 0x337FF6-0x337FF7 0x337FF8-0x33FF7F

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

pr e s r oc s o

W a g Qi ,Ga n k 2 ,Hu i a g n ' o Yig e, ) aS l n ¨,Zh n eu ¨ ,W a g Do g u¨,a d H o a h a i a g Tij n n n h i n u Ch o u n

北 京

1 01 0) 0 9

( n q2 8@ m al. u a . c c ) wa g i0 is g c s a . n

摘 要 :为 了 方便 软 件 与 应 用 系 统 的开 发 与调 试 , 出一 种 可 复 用 的 微 处 理 器 片 上 调 试 方 法 . 过 设 计 通 用 的 调 试 提 通 指 令 集 和 增 加 调 试 模 块 , 扩 展 处 理 器 内核 功 能 , 现 了 断 点 设 置 与 取 消 、 核 运 行 的流 水 级 精 确 控 制 、 并 实 内 内核 资 源 访

第 2 4卷 第 1 O期 21 0 2年 1 O月

Байду номын сангаас计算 机辅 助设 计 与 图形学 学报

J u n l fCo u e— d dDein & Co u e a hc o r a mp tr Aie sg o mp trGr p is

Vo 4 NO 1 L2 . 0

0c . 2O1 t 2

pr gr m , e c T hi e ho s be n i plm e e he i e e de ty d sgn d Su r o a t. sm t d ha e m e nt d on t nd p n n l e i e pe V EF01 DSP.

积 仅 增 加 了 3 8 . .7

关 键 词 :片上 调试 ; 可复 用 ; 字 信 号 处 理 器 ; 步 数 单

中 图 法 分 类 号 :TP 6 38

De i n nd m p e e a i n f Re s b e s g a I l m nt to o u a l On- hi De u Fu c i n f r - p c b g n to s o M ir - c o-

c e;a c s i g t o e r s r e or c e sn hec r e ou c s;c le tn h t ts i p ca ve t t e n r e ur so o l c i g t e s a itcofs e i le n sbe we n a y p oc d e f3

问 、 意程 序段 运 行 中 特 殊 事 件 的 统 计 等 片 上 调 试 功 能 . 方 法 已 在 自主 研 发 的 S pr E 0 S 任 该 u eV— F 1D P上 实 现 . 在 C MOS9 m 工 艺 下 的 综合 结果 表 明 , 增 的 片 上调 试 功 能 不 影 响 S pr — F 1D P的 关键 路径 时 序 , 芯 片 总 面 0 n 新 u eV E 0 S 而

可 复 用 微 处 理 器 片 上 调 试 功 能 的 设 计 与 实 现

王 琪 , 高瑛珂 , 华斯亮” 张铁军 王东辉” 侯朝焕” , ,

,

”( 国 科 学 院 声 学 研 究 所 数 字 系 统 集 成 实 验 室 中

。( 国 科 学 院 研 究 生 院 ’中 北 京 1 0 4 ) 0 0 9

s t a di bug m o l nd e e i he f nc i ns o h r e s , t o l w i u to s a e e , d ng a de du e a xt nd ng t u to f t e p oc s or he f lo ng f nc i n r i pl m e e m e nt d:s t i g a d c nc li g br a oi t e tn n a e ln e kp n s;p e ie y r n tm e c t olo he p p lne s a e i he r c s l u — i on r ft i e i — t g n t

( r d a eU i e s y o hn s Ac d my o ce cs e i g 1 0 4 ) G a u t n v ri f C ie e a e S in e 。B i n 0 0 9 t f j

Ab t a t n t i pe ,a r us b eon c p de s r c :I h s pa r e a l — hi bug m e ho o r o— o e s s i o s d i r e o t d f r mic pr c s or s pr po e n o d rt f clt t o t r nd a lc ton s s e d v l pi nd d bu gi g.By e a iia e s f wa ea pp ia i y t m e e o ng a e g n mpl y ng a de g i t u to o i bu ns r c i n