MIW3034中文资料

MAALSS0034中文资料

Miniature Broadband Gain Stage 70 - 3000 MHzMAALSS0034V2CompliantFeatures• Low Noise Figure • High IP 3• Single +3 V to +5 V Supply Voltage • Lead-Free SOT-89 Package• 100% Matte Tin Plating over Copper • Halogen-Free “Green” Mold Compound• RoHS* Compliant and 260°C Re-flow CompatibleDescriptionM/A-COM’s MAALSS0034 broadband gain stage is a GaAs MMIC amplifier in a lead-free SOT-89 surface mount plastic package. It can be operated from a single 3 to 5 volt supply.The MAALSS0034 employs a monolithic single-stage self-biased design featuring a convenient 50-ohm input impedance that minimizes the number of external components required. The broadband design provides low noise figure and high IP3 from 70 to 3000 MHz.M/A-COM fabricates the MAALSS0034 using an E/D MESFET process to realize low noise and high dynamic range. The process features full passivation for performance and reliability.Pin ConfigurationPinPin NameDescription1 RF In RF Input2 GND Ground3RF Out/V DDRF Output & Voltage BiasOrdering Information 1Part NumberPackageMAALSS0034 Bulk Packaging MAALSS0034TR-3000 3000 piece reel MAALSS0034SMBSample Test Board1. Reference Application Note M513 for reel size information.Absolute Maximum Ratings 4,5ParameterAbsolute MaximumRF Output Power24 dBm Voltage6.0 volts Storage Temperature -65°C to +150°CJunction Temperature200°C* Restrictions on Hazardous Substances, European Union Directive 2002/95/EC. 4. Exceeding any one or combination of these limits may cause permanent damage to this device.5. M/A-COM does not recommend sustained operation near these survivability limits.Maximum Operating Conditions 2ParameterMaximumOperating ConditionRF Output Power23 dBm Junction Temperature 3 150°C Operating Temperature-40°C to +85°C2. Operating at or within these conditions will ensure MTTF > 1 x 106 hours.3. Typical thermal resistance (θjc) = 100°C/W.Functional Block DiagramPin 1RF InRF Out/V DDMiniature Broadband Gain Stage 70 - 3000 MHzMAALSS0034V2CompliantElectrical Specifications: Z 0 = 50 Ω, T A = 25 °C, V DD = +5 V (unless otherwise specified)ParameterTest ConditionsUnitsMin.Typ.Max.Gain0.9 GHz 1.9 GHz1.9 GHz (V DD = +3V)3.0 GHz dB dB dB dB — 11.0 10.5 — 14.5 12.0 11.5 9.20 — 13.0 13.0 — Noise Figure0.9 GHz 1.9 GHz1.9 GHz (V DD = +3V)3.0 GHz dB dB dB dB — — — — 1.55 1.60 1.50 1.70 — 2.0 2.0 — Input Return Loss0.9 GHz 1.9 GHz 3.0 GHzdB dB dB — — — 10 15 18 — — — Output Return Loss0.9 GHz 1.9 GHz 3.0 GHzdB dB dB — — — 9 14 18 — — — Output P1dB 0.9 GHz 1.9 GHz 3.0 GHzdBm dBm dBm — — — 22 23 23 — — — Output IP 3Two tone, -12 dBm/tone, 1 MHz spacing0.9 GHz 1.9 GHz 3.0 GHz dBm dBm dBm — — — 33 36 37 — — — CurrentV DD = +5 V V DD = +3 VmA mA50 3588 70110 100Component List 6, 500 - 3000 MHzPart Value Case StyleManufacturerPurposeC1,C2 39 pF 0402 Murata DC Block C3 0.1µF 0402 Murata RF Bypass L112 nH0402CoilcraftRF Choke/Tuning6. Please contact M/A-COM application group for lowerfrequency application circuitry.Handling ProceduresPlease observe the following precautions to avoid damage:Static SensitivityGallium Arsenide Integrated Circuits are sensitive to electrostatic discharge (ESD) and can be damaged by static electricity. Proper ESD control techniques should be used when handling these devices.Application SchematicRecommended PCB ConfigurationMiniature Broadband Gain Stage 70 - 3000 MHzMAALSS0034V2CompliantNoise FigureTypical Performance Curves, V DD = +5 VGainOutput Return LossInput Return LossOutput IP3, Input Power = -12 dBmOutput P1dB51015200.51.0 1.52.0 2.53.0+25°C-40°C +85°CFrequency (GHz)-25-20-15-10-500.51.01.52.02.53.0+25°C-40°C +85°CFrequency (GHz)253035400.51.0 1.52.0 2.53.0+25°C-40°C +85°CFrequency (GHz)0.51.01.52.02.50.51.0 1.52.0 2.53.0+25°C-40°C +85°CFrequency (GHz)-25-20-15-10-50.51.01.52.02.53.0+25°C-40°C +85°CFrequency (GHz)152025300.51.0 1.52.0 2.53.0+25°C-40°C +85°CFrequency (GHz)Miniature Broadband Gain Stage 70 - 3000 MHzMAALSS0034V2CompliantNoise FigureTypical Performance Curves, V DD = +3 VGainOutput Return LossInput Return LossOutput IP3, Input Power = -12 dBmOutput P1dB51015200.51.0 1.52.0 2.53.0+25°C-40°C +85°CFrequency (GHz)253035400.51.0 1.52.0 2.53.0+25°C-40°C +85°CFrequency (GHz)152025300.51.0 1.52.0 2.53.0+25°C-40°C +85°CFrequency (GHz)0.51.01.52.02.50.51.0 1.52.0 2.53.0+25°C-40°C +85°CFrequency (GHz)-25-20-15-10-500.51.01.52.02.53.0+25°C-40°C +85°CFrequency (GHz)-25-20-15-10-50.51.01.52.02.53.0+25°C-40°C +85°CFrequency (GHz)Miniature Broadband Gain Stage 70 - 3000 MHzMAALSS0034V2 CompliantLead-Free SOT-89†† Reference Application Note M538 for lead-free solder reflow recommendations.。

TDS3034C 数字荧光示波器技术规格使用说明书

使用 TDS3SDI 601串行数字视频模块,跟踪和识别 ITU-R BT.601 视频信号。

TDS3000C 系列为通信线路卡测试提供了突破性的测试速度。通 信 QUICKMENU 把所有常用的测试功能放在一个菜单上。

4 TDS3000C /oscilloscopes

使用 DRT 采样技术和 Sin(x)/x 内插功能 迅速调试和检定信号

DPO 可以更全面地查看复杂的信号

为解决问题,首先必需看到问题。 TDS3000C 系列提供了 3,600 wfms/s 的 连续波形捕获速率及实时辉度等级,使 您能够看到并解决问题。

快速连续波形捕获速率可以迅速揭示问 题特点,进而应用高级触发隔离问题,节 约大量的时间。

TDS3012C 100 MHz

3.5 ns 2

1.25 GS/s

20 MHz 4 ns-10 s

TDS3014C 100 MHz

3.5 ns

TDS3032C 300 MHz

1.2 ns

TDS3034C 300 MHz

1.2 ns

TDS3052C 500 MHz

0.7 ns

TDS3054C 500 MHz

主要特点和优点

主要性能指标 100 MHz, 300 MHz 和 500 MHz 带宽 2 条或 4 条通道 在所有通道上实现高达 5 GS/s 的实 时采样率 在所有通道上标配 10 k 记录长度 3,600 wfms/s 连续波形捕获速率 高级触发套件

简便易用功能 前面板 USB 主机端口,简便地存储 和传送测量数据 25 种自动测量功能 标配 FFT 多语言用户界面 WaveAlert® 异常波形自动检测 TekProbe® 接口支持有源探头、差 分探头和电流探头,自动定标和确 定单位

NCV33204中文资料

1

October, 2006 − Rev. 14

Publication Order Number: MC33201/D

MC33201, MC33202, MC33204, NCV33202, NCV33204

MC33201 All Case Styles

NC 1

8 NC

2

Inputs 3

7 VCC 6 Output

3

Inputs 3 9

Output 2 7

8 Output 3

(Top View)

Output 1 1

2 Inputs 1

3

VEE 4

8 VCC

7 Output 2 1

6

2

Inputs 2 5

(Top View)

VCC

VCC VCC

Vin −

Vin +

VEE

Vout VCC

VEE This device contains 70 active transistors (each amplifier). Figure 1. Circuit Schematic (Each Amplifier)

supply voltage range available. It is designed to work at very low supply voltages (± 0.9 V) yet can operate with a supply of up to +12 V and ground. Output current boosting techniques provide a high output

Characteristic

Figure Symbol

MIW4127中文资料

Dual OutputSingle OutputBlock DiagramMIW4100-Series power modules operate over inputvoltage ranges of 9-36VDC and 18-75VDC which provide precisely regulated output voltages of 3.3V, 5V, 12V, 15V, {5V, {12V and {15VDC.The -40] to +71] operating temperature range makes it ideal for data communication equipments, mobile battery driven equipments, distributed power systems, telecommunication equipments, mixed analog/digital subsystems, process/machine control equipments, computer peripheral systems and industrial robot systems.The modules have a maximum power rating of 6W and a typical full-load efficiency of 83%, continuous short circuit, EN55022 Class A conducted noise compliance minimize design-in time, cost and eliminate the need for external filtering.y Internal SMD Constructiony UL 94V-0 Package Material y Industry Standard Pinout y Temperature Performance -40] to +71]y Complies with EN55022 Class Ay Low Costy 4:1 Wide Input Range y MTBF > 1,000,000 Hours y 1500VDC Isolationy Efficiency up to 83%Key Features5-6W, Ultra-Wide Input Range DIP, Single & Dual Output DC/DC ConvertersMIW4100 Series82152{20{200{15MIW413783151{25{250{12MIW413678134{50{500{5MIW4135821524040015MIW4134831515050012MIW41337813410010005MIW413275151011012012003.348( 18 ~ 75 )MIW413182305{20{200{15MIW412783301{25{250{12MIW412678267{50{500{5MIW4125823054040015MIW4124833015050012MIW41237826710010005MIW412275202022012012003.324( 9 ~ 36 )MIW4121% (Typ.)mA (Typ.)mA (Typ.)mA (Typ.)mA mA VDC VDC@Max. Load @No Load @Max. Load Min.Max.EfficiencyReflected Ripple Current Input CurrentOutput CurrentOutput VoltageInput VoltageModel NumberModel Selection GuideEN55022 Class AConducted EMIFree-Air Convection Cooling %95---Humidity ]+125-40Storage Temperature ]+95-40CaseOperating Temperature ]+71-40Ambient Operating Temperature Unit Max.Min.Conditions ParameterEnvironmental SpecificationsExceeding the absolute maximum ratings of the unit could cause damage.These are not continuous operating ratings.mW2,500---Internal Power Dissipation]260---Lead Temperature (1.5mm from case for 10 Sec.)VDC 100-0.748VDC Input ModelsVDC 50-0.724VDC Input Models Input Surge Voltage( 1000 mS )Unit Max.Min.ParameterNotes :1. Specifications typical at Ta=+25], resistive load,nominal input voltage, rated output current unless otherwise noted.2. Transient recovery time is measured to within 1%error band for a step change in output load of 75%to 100%.3. Ripple & Noise measurement bandwidth is 0-20MHz.4. These power converters require a minimum output loading to maintain specified regulation.5. Operation under no-load conditions will not damage these modules; however, they may not meet all specifications listed.6. All DC/DC converters should be externally fused at the front end for protection.7. Other input and output voltage may be available,please contact factory.8. Specifications subject to change without notice.Absolute Maximum RatingsMIW4100 SeriesPi FilterInput FiltermW 3000------Short Circuit Input Power A 1------All Models Reverse Polarity Input Current 16------48V Input Models8.5------24V Input Models Under Voltage Shutdown 18161448V Input Models VDC 98724V Input Models Start VoltageUnitMax.Typ.Min.Model ParameterInput SpecificationsK Hours------1000MIL-HDBK-217F @ 25], Ground BenignMTBFKHz ---450---Switching Frequency pF 550350---100KHz,1VIsolation Capacitance M[------1000500VDC Isolation Resistance VDC ------1650Flash Tested for 1 SecondIsolation Voltage Test VDC ------150060 SecondsIsolation Voltage Unit Max.Typ.Min.Conditions ParameterGeneral SpecificationsContinuousOutput Short Circuit%/]{0.02{0.01---Temperature Coefficient %---{3---Transient Response Deviation uS 500300---25% Load Step Change Transient Recovery Time %350250110Over Power Protection mV rms 15------Ripple & Noise (20MHz)mV P-P 100------Over Line, Load & Temp.Ripple & Noise (20MHz)mV P-P 8050---Ripple & Noise (20MHz)%{1.0{0.5---Io=10% to 100%Load Regulation %{0.5{0.1---Vin=Min. to Max.Line Regulation %{2.0{0.5---Dual Output, Balanced LoadsOutput Voltage Balance %{2.0{0.5---Output Voltage Accuracy Unit Max.Typ.Min.ConditionsParameterOutput Specifications# For each outputuF100100100100100470470Maximum Capacitive Load Unit {15V #{12V #{5V #15V 12V 5V 3.3V Models by VoutCapacitive LoadMIW4100 Series750mA Slow-Blow type1000mA Slow-Blow type48V Input Models 24V Input Models Input Fuse Selection GuideInput Voltage Transient RatingMIW4100 SeriesTest ConfigurationsInput Reflected-Ripple Current Test SetupInput reflected-ripple current is measured with a inductor Lin (4.7uH) and Cin (220uF, ESR < 1.0[ at 100 KHz) to simulate source impedance.Capacitor Cin, offsets possible battery impedance.Current ripple is measured at the input terminals of the module, measurement bandwidth is 0-500 KHz.Peak-to-Peak Output Noise Measurement TestUse a Cout 0.47uF ceramic capacitor.Scope measurement should be made by using a BNC socket, measurement bandwidth is 0-20 MHz. Position the load between 50 mm and 75 mm from the DC/DC Converter.Design & Feature ConsiderationsMaximum Capacitive LoadThe MIW4100 series has limitation of maximum connected capacitance at the output.The power module may be operated in current limiting mode during start-up, affecting the ramp-up and the startup time.The maximum capacitance can be found in the data sheet.Overcurrent ProtectionTo provide protection in a fault (output overload) condition,the unit is equipped with internal current limiting circuitry and can endure current limiting for an unlimited duration. At the point of current-limit inception, the unit shifts from voltage control to current control. The unit operates normally once the output current is brought back into its specified range.Input Source ImpedanceThe power module should be connected to a low ac-impedance input source. Highly inductive source impedances can affect the stability of the power module.In applications where power is supplied over long lines and output loading is high, it may be necessary to use a capacitor at the input to ensure startup.Capacitor mounted close to the power module helps ensure stability of the unit, it is recommended to use a good quality low Equivalent Series Resistance (ESR < 1.0[ at 100KHz) capacitor of a 4.7uF for the 24V input devices and a 2.2uF for the 48V devices.A good quality low ESR capacitor placed as close as practicable across the load will give the best ripple and noise performance.To reduce output ripple, it is recommended to use 3.3uF capacitors at the output.MIW4100 SeriesMIW4100 Series Thermal ConsiderationsMany conditions affect the thermal performance of thepower module, such as orientation, airflow over the moduleand board spacing. To avoid exceeding the maximumtemperature rating of the components inside the powermodule, the case temperature must be kept below 90°C.The derating curves are determined from measurementsobtained in an experimental apparatus.The MIW4100 converter is encapsulated in a low thermal resistance molding compound that has excellent resistance/electrical characteristics over a wide temperature range or in high humidity environments.The encapsulant and unit case are both rated to UL 94V-0 flammability specifications.Leads are tin plated for improved solderability.NC: No Connection+Vin+Vin 23UL94V-0:Flammability+Vin +Vin 22Common -Vout 1617.3g :Weight +Vout +Vout 14-Vout NC 11Metal With Non-Conductive Baseplate :Case Material Common No Pin 9-Vin -Vin 3 1.25*0.80*0.40 inches-Vin -Vin 231.8*20.3*10.2 mm :Case Size Dual OutputSingle OutputPin Physical CharacteristicsPin ConnectionsConnecting Pin PatternsTop View ( 2.54 mm / 0.1 inch grids )Mechanical DimensionsMIW4100 Series。

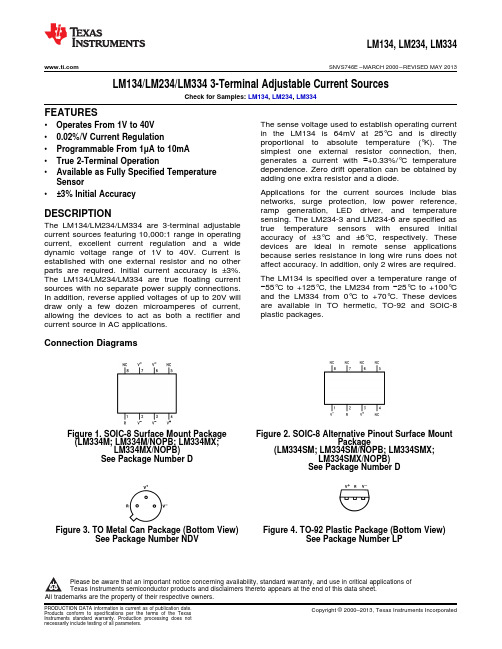

LM334中文资料_数据手册_参数

Absolute Maximum Ratings(1)(2)

V+ to V− Forward Voltage

V+ to V− Reverse Voltage R Pin to V− Voltage Set Current Power Dissipation ESD Susceptibility(3) Operating Temperature Range(4)

LM134, LM234, LM334

SNVS746E – MARCH 2000 – REVISED MAY 2013

Electrical Characteristics(1)

Parameter

Conditions

Set Current Error, V+=2.5V(2)

Ratio of Set Current to Bias Current

1mA < ISET ≤ 5mA

Temperature Dependence of Set Current(3) Effective Shunt Capacitance

(LM334SM; LM334SM/NOPB; LM334SMX; LM334SMX/NOPB)

See Petal Can Package (Bottom View) See Package Number NDV

Figure 4. TO-92 Plastic Package (Bottom View) See Package Number LP

ZL30120GGG中文资料

1A full Design Manual is available to qualified customers.To register, please send an email to TimingandSync@.Features•Synchronizes with standard telecom system references and synthesizes a wide variety of protected telecom line interface clocks that are compliant with Telcordia GR-1244-CORE, GR-253-CORE, ITU-T G.813, and compatible with ITU-T G.8261 (formerly G.pactiming)•Internal low jitter APLL provides SONET/SDHclocks including 6.48MHz, 19.44MHz, 38.88MHz, 51.84MHz and 77.76MHz, or 25MHz and 50MHz Synchronous Ethernet output clocks•Programmable output synthesizers (P0, P1)generate general purpose clock frequencies from any multiple of 8kHz up to 100MHz•Jitter performance of <8 ps RMS on the low jitter APLL outputs, and <20 ps RMS on the programmable synthesizer outputs.•Provides 8 reference inputs which support clock frequencies with any multiples of 8kHz up to 77.76MHz in addition to 2kHz•Provides two DPLLs which have independent modes of operation (locked, free-run, holdover) and optional hitless reference switching.•Flexible input reference monitoring automatically disqualifies references based on frequency and phase irregularities•Provides 3 sync inputs for output frame pulse alignment•Generates several styles of output frame pulses with selectable pulse width, polarity, and frequency •Configurable input to output delay, and output to output phase alignment•Supports IEEE 1149.1 JTAG Boundary ScanMay 2006Figure 1 - Block DiagramZL30120SONET/SDH/EthernetMulti-Rate Line Card SynchronizerData SheetOrdering InformationZL30120GGG 100 Pin CABGA Trays ZL30120GGG2100 Pin CABGA**Trays**Pb Free Tin/Silver/Copper-40o C to +85o CZL30120Data SheetApplications•AMCs for AdvancedTCA TM and MicroTCA Systems•Synchronous Ethernet•Multi-Service Edge Switches or Routers•DSLAM Line Cards•WAN Line Cards•RNC/Mobile Switching Center Line Cards•ADM Line CardsZL30120Data SheetTable of Contents1.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.1 DPLL Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.2 DPLL Mode Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121.3 Ref and Sync Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131.4 Ref and Sync Monitoring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141.5 Output Clocks and Frame Pulses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151.6 Configurable Input-to-Output and Output-to-Output Delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172.0 Software Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183.0 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25ZL30120Data SheetList of FiguresFigure 1 - Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Automatic Mode State Machine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 3 - Reference and Sync Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 4 - Output Frame Pulse Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 5 - Behaviour of the Guard Soak Timer during CFM or SCM Failures. . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 6 - Output Clock Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 7 - Phase Delay Adjustments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17ZL30120Data SheetList of TablesTable 1 - DPLL1 and DPLL2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 2 - Set of Pre-Defined Auto-Detect Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 3 - Set of Pre-Defined Auto-Detect Sync Frequencies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 4 - Output Clock and Frame Pulse Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16ZL30120Data Sheet Pin DescriptionPin # Name I/OType DescriptionInput ReferenceC1 B2 A3 C3 B3 B4 C4 A4ref0ref1ref2ref3ref4ref5ref6ref7I d Input References (LVCMOS, Schmitt Trigger). These are input referencesavailable to both DPLL1 and DPLL2 for synchronizing output clocks. All eightinput references can be automatically or manually selected using softwareregisters. These pins are internally pulled down to Vss.B1 A1 A2sync0sync1sync2I d Frame Pulse Synchronization References (LVCMOS, Schmitt Trigger).These are the frame pulse synchronization inputs associated with inputreferences 0, 1 and 2. These inputs accept frame pulses in a clock format (50%duty cycle) or a basic frame pulse format with minimum pulse width of 5ns.These pins are internally pulled down to V ss.Output Clocks and Frame PulsesD10apll_clk0O APLL Output Clock 0 (LVCMOS). This output can be configured to provide anyone of the available SONET/SDH clock outputs up to 77.76MHz, or 25MHz and50MHz. The default frequency for this output is 77.76MHz.G10apll_clk1O APLL Output Clock 1 (LVCMOS). This output can be configured to provide anyone of the available SONET/APLL clock outputs up to 77.76MHz, or 25MHz and50MHz. The default frequency for this output is 19.44MHz.E10apll_fp0O APLL Output Frame Pulse 0 (LVCMOS). This output can be configured toprovide virtually any style of output frame pulse synchronized with an associatedAPLL output clock. The default frequency for this frame pulse output is 8kHz.F10apll_fp1O APLL Output Frame Pulse 1 (LVCMOS). This output can be configured toprovide virtually any style of output frame pulse synchronized with an associatedAPLL output clock. The default frequency for this frame pulse output is 2kHz.K9p0_clk0O Programmable Synthesizer 0 - Output Clock 0 (LVCMOS). This output can beconfigured to provide any frequency with a multiple of 8kHz up to 100MHz inaddition to 2kHz. The default frequency for this output is 2.048MHz.K7p0_clk1O Programmable Synthesizer 0 - Output Clock 1 (LVCMOS). This is aprogrammable clock output configurable as a multiple or division of the p0_clk0frequency within the range of 2kHz to 100MHz. The default frequency for thisoutput is 8.192MHz.K8p0_fp0O Programmable Synthesizer 0 - Output Frame Pulse 0 (LVCMOS). This outputcan be configured to provide virtually any style of output frame pulse associatedwith the p0 clocks. The default frequency for this frame pulse output is 8kHz.J7p0_fp1O Programmable Synthesizer 0 - Output Frame Pulse 1 (LVCMOS). This outputcan be configured to provide virtually any style of output frame pulse associatedwith the p0 clocks. The default frequency for this frame pulse output is 8kHz.ZL30120Data SheetJ10p1_clk0OProgrammable Synthesizer 1 - Output Clock 0 (LVCMOS). This output can be configured to provide any frequency with a multiple of 8kHz up to 100MHz in addition to 2kHz. The default frequency for this output is 1.544MHz (DS1).K10p1_clk1OProgrammable Synthesizer1 - Output Clock 1 (LVCMOS). This is aprogrammable clock output configurable as a multiple or division of the p1_clk0 frequency within the range of 2kHz to 100MHz. The default frequency for this output is 3.088MHz (2x DS1).H10fb_clk OFeedback Clock (LVCMOS). This output is a buffered copy of the feedback clock for DPLL1. The frequency of this output always equals the frequency of the selected reference.E1dpll2_ref ODPLL2 Selected Output Reference (LVCMOS). This is a buffered copy of the output of the reference selector for DPLL2. Switching between input reference clocks at this output is not hitless.Control H5rst_bIReset (LVCMOS, Schmitt Trigger). A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. Reset should be asserted for a minimum of 300ns.J5dpll1_hs_enI uDPLL1 Hitless Switching Enable (LVCMOS, Schmitt Trigger). A logic high at this input enables hitless reference switching. A logic low disables hitless reference switching and re-aligns DPLL1’s output phase to the phase of the selected reference input. This feature can also be controlled through software registers. This pin is internally pulled up to Vdd.C2D2dpll1_mod_sel0dpll1_mod_sel1I uDPLL1 Mode Select 1:0 (LVCMOS, Schmitt Trigger). During reset, the levels on these pins determine the default mode of operation for DPLL1 (Automatic, Normal, Holdover or Freerun). After reset, the mode of operation can becontrolled directly with these pins, or by accessing the dpll1_modesel register through the serial interface. This pin is internally pulled up to Vdd.Status H1dpll1_lockOLock Indicator (LVCMOS). This is the lock indicator pin for DPLL1. This output goes high when DPLL1’s output is frequency and phase locked to the input reference.J1dpll1_holdover OHoldover Indicator (LVCMOS). This pin goes high when DPLL1 enters the holdover mode.Serial Interface E2sck I Clock for Serial Interface (LVCMOS). Serial interface clock.F1si I Serial Interface Input (LVCMOS). Serial interface data input pin.G1so O Serial Interface Output (LVCMOS). Serial interface data output pin.E3cs_bI uChip Select for Serial Interface (LVCMOS). Serial interface chip select. This pin is internally pulled up to Vdd.Pin # Name I/O Type DescriptionZL30120Data Sheet G2int_b O Interrupt Pin (LVCMOS). Indicates a change of device status prompting theprocessor to read the enabled interrupt service registers (ISR). This pin is anopen drain, active low and requires an external pulled up to VDD.APLL Loop FilterA6apll_filter A External Analog PLL Loop Filter terminal.B6filter_ref0A Analog PLL External Loop Filter Reference.C6filter_ref1A Analog PLL External Loop Filter Reference.JTAG and TestJ4tdo O Test Serial Data Out (Output). JTAG serial data is output on this pin on thefalling edge of tck. This pin is held in high impedance state when JTAG scan isnot enabled.K2tdi I u Test Serial Data In (Input). JTAG serial test instructions and data are shifted inon this pin. This pin is internally pulled up to Vdd. If this pin is not used then itshould be left unconnected.H4trst_b I u Test Reset (LVCMOS). Asynchronously initializes the JTAG TAP controller byputting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internallypulled up to Vdd. If this pin is not used then it should be connected to GND.K3tck I Test Clock (LVCMOS): Provides the clock to the JTAG test logic. If this pin is notused then it should be pulled down to GND.J3tms I u Test Mode Select (LVCMOS). JTAG signal that controls the state transitions ofthe TAP controller. This pin is internally pulled up to V DD. If this pin is not usedthen it should be left unconnected.Master ClockK4osci I Oscillator Master Clock Input (LVCMOS). This input accepts a 20MHzreference from a clock oscillator (TCXO, OCXO). The stability and accuracy ofthe clock at this input determines the free-run accuracy and the long termholdover stability of the output clocks.K5osco O Oscillator Master Clock Output (LVCMOS). This pin must be left unconnectedwhen the osci pin is connected to a clock oscillator.MiscellaneousA9 A10 B5 B9 B10 C5 D1 D3 G3NC No Connection. Leave unconnected.Pin # Name I/OType DescriptionZL30120Data Sheet J2J6H7K1IC Internal Connection. Connect to ground.F2F3K6IC Internal Connection. Leave unconnected.Power and GroundD9 E4 G8 G9 J8 J9 H6 H8V DD PPPPPPPPPositive Supply Voltage. +3.3V DC nominal.E8 F4V CORE PPPositive Supply Voltage. +1.8V DC nominal.A5 A8 C10AV DD PPPPositive Analog Supply Voltage. +3.3V DC nominal.B7 B8 H2AV CORE PPPPositive Analog Supply Voltage. +1.8V DC nominal.D4 D5 D6 D7 E5 E6 E7 F5 F6 F7 G4 G5 G6 G7 E9 F8 F9 H9V SS GGGGGGGGGGGGGGGGGGGround. 0 Volts.Pin # Name I/OType DescriptionZL30120Data SheetI - InputI d -Input, Internally pulled down I u -Input, Internally pulled up O -Output A -Analog P -Power G -GroundA7C7C8C9D8H3AV SSG G G G G GAnalog Ground. 0 Volts.Pin # Name I/O Type DescriptionZL30120Data Sheet1.0 Functional DescriptionThe ZL30120 Multi-Rate Line Card Synchronizer is a highly integrated device that provides timing and synchronization for network interface cards. It incorporates two independent DPLLs, each capable of locking to one of eight input references and provides a wide variety of synchronized output clocks and frame pulses.1.1 DPLL FeaturesThe ZL30120 provides two independently controlled Digital Phase-Locked Loops (DPLL1, DPLL2) for clock and/or frame pulse synchronization. DPLL1 is the main DPLL and is always enabled. To save on power, DPLL2 is disabled by default. For applications where DPLL2 is required, it must be enabled using the dpll_en bit of the dpll2_ctrl_0register (0x2A). Table 1 shows a feature summary for both DPLLs.FeatureDPLL1DPLL2Modes of Operation Free-run, Normal (locked), Holdover Free-run, Normal (locked), Holdover Loop Bandwidth User selectable: 14Hz, 28Hz, or wideband 1 (890Hz / 56Hz / 14Hz)1. In the wideband mode, the loop bandwidth depends on the frequency of the reference input. For reference frequencies equal to or greater than 64kHz, the loop bandwidth = 890Hz. For reference frequencies equal to or greater than 8kHz and less than 64 kHz, the loop bandwidth = 56Hz. For reference frequencies equal to 2kHz, the loop bandwidth is equal to 14Hz.Fixed: 14HzPhase Slope Limiting User selectable: 885ns/s, 7.5µs/s, 61µs/s, or unlimited User selectable: 61µs/s, or unlimited Pull-in Range Fixed: 130ppmFixed: 130ppmHoldover ParametersSelectable Update Times: 26ms, 1s, 10s, 60s, and Selectable Holdover Post Filter BW: 18mHz, 2.5Hz, 10Hz. Fixed Update Time: 26ms No Holdover Post FilteringHoldover Frequency AccuracyBetter than 1ppb (Stratum 3E) initial frequency offset. Frequency drift depends on the 20MHz external oscillator.Better than 50ppb (Stratum 3) initial frequency offset. Frequency drift depends on the 20MHz external oscillator.Reference Inputs Ref0 to Ref7Ref0 to Ref7Sync Inputs Sync0, Sync1, Sync2Sync inputs are not supported.Input Reference Selection/Switching Automatic (based on programmable priority and revertiveness), or manual Automatic (based on programmable priority and revertiveness), or manual Hitless Ref Switching Can be enabled or disabledCan be enabled or disabled Output Clocks apll_clk0, apll_clk1, p0_clk0, p0_clk1, p1_clk0, p1_clk1, fb_clk.p0_clk0, p0_clk1, p1_clk0, p1_clk1.Output Frame Pulses apll_fp0, apll_fp1, p0_fp0, p0_fp1 synchronized to active sync reference.p0_fp0, p0_fp1 not synchronized to sync reference.External Pins Status IndicatorsLock, HoldoverNoneTable 1 - DPLL1 and DPLL2 FeaturesZL30120Data Sheet1.2 DPLL Mode ControlBoth DPLL1 and DPLL2 independently support three modes of operation - free-run, normal and holdover. The mode of operation can be manually set or controlled by an automatic state machine as shown in Figure 2.Figure 2 - Automatic Mode State MachineFree-runThe free-run mode occurs immediately after a reset cycle or when the DPLL has never been synchronized to areference input. In this mode, the frequency accuracy of the output clocks is equal to the frequency accuracy of the external master oscillator. Lock AcquisitionThe input references are continuously monitored for frequency accuracy and phase regularity. If at least one of the input references is qualified by the reference monitors, then the DPLL will begin lock acquisition on that input. Given a stable reference input, the ZL30120 will enter in the Normal (locked) mode.Normal (locked)The usual mode of operation for the DPLL is the normal mode where the DPLL phase locks to a selected qualified reference input and generates output clocks and frame pulses with a frequency accuracy equal to the frequency accuracy of the reference input. While in the normal mode, the DPLL’s clock and frame pulse outputs comply with the MTIE and TDEV wander generation specifications as described in Telcordia and ITU-T telecommunication standards.HoldoverWhen the DPLL operating in the normal mode loses its reference input, and no other qualified references are available, it will enter the holdover mode and continue to generate output clocks based on historical frequency data collected while the DPLL was synchronized.ResetAnother reference is qualified and availablefor selectionPhase lock on the selected reference is achievedLock AcquisitionNormal (Locked)No references are qualified and available for selectionFree-RunHoldoverSelected referencefailsAll references are monitored for frequency accuracy and phase regularity, and at least one reference is qualified.Normal (Locked)ZL30120Data Sheet1.3 Ref and Sync InputsThere are eight reference clock inputs (ref0 to ref7) available to both DPLL1 and DPLL2. The selected reference input is used to synchronize the output clocks. Each of the DPLLs have independent reference selectors which can be controlled using a built-in state machine or set in a manual mode.Figure 3 - Reference and Sync InputsIn addition to the reference inputs, DPLL1 has three optional frame pulse synchronization inputs (sync0 to sync2)used to align the output frame pulses. The sync n input is selected with its corresponding ref n input, where n = 0, 1,or 2. Note that the sync input cannot be used to synchronize the DPLL, it only determines the alignment of the frame pulse outputs. An example of output frame pulse alignment is shown in Figure 4.Figure 4 - Output Frame Pulse Alignmentref7:0sync2:0DPLL2DPLL1ref napll/p0/p1_clk xapll/p0_fp xWithout a frame pulse signal at the sync input, the output frame pulses will align to any arbitrary cycle of its associated output clock.sync n - no frame pulse signal presentWhen a frame pulse signal is present at the sync input, the DPLL will align the output frame pulses to the output clock edge that is aligned to the input frame pulse.ref n apll/p0/p1_clk xapll/p0_fp xsync nn = 0, 1, 2x = 0, 1n = 0, 1, 2x = 0, 1ZL30120Data Sheet Each of the ref inputs accept a single-ended LVCMOS clock with a frequency ranging from 2kHz to 77.76MHz. Built-in frequency detection circuitry automatically determines the frequency of the reference if its frequency is within the set of pre-defined frequencies as shown in Table 2. Custom frequencies definable in multiples of 8kHz are also available.2 kHz8 kHz64 kHz1.544 MHz2.048 MHz6.48 MHz8.192 MHz16.384 MHz19.44 MHz38.88 MHz77.76 MHzCustom ACustom BTable 2 - Set of Pre-Defined Auto-Detect Clock FrequenciesEach of the sync inputs accept a single-ended LVCMOS frame pulse. Since alignment is determined from the rising edge of the frame pulse, there is no duty cycle restriction on this input, but there is a minimum pulse width requirement of 5ns. Frequency detection for the sync inputs is automatic for the supported frame pulse frequencies shown in Table 3.166.67 Hz(48x 125 µs frames)400 Hz1 kHz2 kHz8 kHz64 kHzTable 3 - Set of Pre-Defined Auto-Detect Sync Frequencies1.4 Ref and Sync MonitoringAll input references (ref0 to ref7) are monitored for frequency accuracy and phase regularity. New references are qualified before they can be selected as a synchronization source, and qualified references are continuously monitored to ensure that they are suitable for synchronization. The process of qualifying a reference depends on four levels of monitoring.Single Cycle Monitor (SCM)The SCM block measures the period of each reference clock cycle to detect phase irregularities or a missing clock edge. In general, if the measured period deviates by more than 50% from the nominal period, then an SCM failure (scm_fail) is declared.ZL30120Data SheetCoarse Frequency Monitor (CFM)The CFM block monitors the reference frequency over a measurement period of 30µs so that it can quickly detect large changes in frequency. A CFM failure (cfm_fail) is triggered when the frequency has changed by more than 3%or approximately 30000ppm.Precise Frequency Monitor (PFM)The PFM block measures the frequency accuracy of the reference over a 10 second interval. To ensure an accurate frequency measurement, the PFM measurement interval is re-initiated if phase or frequency irregularities are detected by the SCM or CFM. The PFM provides a level of hysteresis between the acceptance range and the rejection range to prevent a failure indication from toggling between valid and invalid for references that are on the edge of the acceptance range.When determining the frequency accuracy of the reference input, the PFM uses the external oscillator’s output frequency (f ocsi ) as its point of reference. Guard Soak Timer (GST)The GST block mimics the operation of an analog integrator by accumulating failure events from the CFM and the SCM blocks and applying a selectable rate of decay when no failures are detected.As shown in Figure 5, a GST failure (gst_fail) is triggered when the accumulated failures have reached the upper threshold during the disqualification observation window. When there are no CFM or SCM failures, the accumulator decrements until it reaches its lower threshold during the qualification window.Figure 5 - Behaviour of the Guard Soak Timer during CFM or SCM FailuresAll sync inputs (sync0 to sync2) are continuously monitored to ensure that there is a correct number of reference clock cycles within the frame pulse period.1.5 Output Clocks and Frame PulsesThe ZL30120 offers a wide variety of outputs including two low jitter LVCMOS (apll_clk0, apll_clk1) output clocks and four programmable LVCMOS (p0_clk0, p0_clk1, p1_clk0, p1_clk1) output clocks. In addition to the clock outputs, two LVCMOS frame pulse outputs (apll_fp0, apll_fp1) and two LVCMOS programmable frame pulses (p0_fp0, p0_fp1) are also available.The feedback clock (fb_clk ) of DPLL1 is available as an output clock. Its output frequency is always equal to DPLL1’s selected input frequency.refCFM or SCM failuresupper thresholdlower thresholdt d - disqualification timet q - qualification time = n * t dt dt qgst_failZL30120Data SheetThe output clocks and frame pulses derived from the low jitter APLL are always synchronous with DPLL1, and the clocks and frame pulses generated from the programmable synthesizers can be synchronized to either DPLL1 or DPLL2. This allows the ZL30120 to have two independent timing paths.Figure 6 - Output Clock ConfigurationThe supported frequencies for the output clocks and frame pulses are shown in Table 4.apll_clk0, apll_clk1(LVCMOS)11. The apll_clk x outputs can generate either SONET/SDH or Ethernet frequencies (25MHz, 50MHz). p0_clk0, p1_clk0(LVCMOS)p0_clk1, p1_clk1(LVCMOS)apll_fp0, apll_fp1, p0_fp0, p0_fp1(LVCMOS)22. apll_fp x frequencies are available only when the low jitter apll is generating SONET/SDH frequencies6.48 MHz 2 kHz p x _clk0 p x _clk1 =2M166.67 Hz (48x 125 µs frames)9.72 MHz N * 8 kHz (up to 100MHz)400 Hz 12.96 MHz 1 kHz 19.44 MHz 2 kHz 25.92 MHz 4 kHz 38.88 MHz 8 kHz 51.84 MHz 32 kHz 77.76 MHz 64 kHz25 MHz 50 MHzTable 4 - Output Clock and Frame Pulse Frequenciesp0_clk0p0_fp0p0_clk1p0_fp1 P0 Synthesizerp1_clk0p1_clk1P1 Synthesizerapll_clk0apll_fp0apll_clk1apll_fp1Low Jitter APLLFeedback Synthesizerfb_clkDPLL2DPLL1ZL30120Data Sheet1.6 Configurable Input-to-Output and Output-to-Output DelaysThe ZL30120 allows programmable static delay compensation for controlling input-to-output and output-to-output delays of its clocks and frame pulses.All of the output synthesizers (APLL, P0, P1, Feedback) locked to DPLL1 can be configured to lead or lag the selected input reference clock using the DPLL1 Fine Delay . The delay is programmed in steps of 119.2ps with a range of -128 to +127 steps giving a total delay adjustment in the range of -15.26ns to +15.14ns. Negative values delay the output clock, positive values advance the output clock. Synthesizers that are locked to DPLL2 are unaffected by this delay adjustment.In addition to the fine delay introduced in the DPLL1 path, the APLL, P0, and P1 synthesizers have the ability to add their own fine delay adjustments using the P0 Fine Delay , P1 Fine Delay , and APLL Fine Delay . These delays are also programmable in steps of 119.2ps with a range of -128 to +127 steps.In addition to these delays, the single-ended output clocks of the APLL, P0, and P1 synthesizers can be independently offset by 90, 180 and 270 degrees using the Coarse Delay . The output frame pulses (APLL, P0) can be independently offset with respect to each other using the FP Delay .Figure 7 - Phase Delay AdjustmentsDPLL1DPLL2P0 Fine Delayp0_clk0p0_clk1p0_fp0p0_fp1 P0 SynthesizerCoarse DelayCoarse Delay FP Delay FP Delay fb_clkp1_clk0p1_clk1P1 Fine DelayLow Jitter APLLapll_clk0apll_clk1apll_fp0apll_fp1APLL Fine DelayFeedback SynthesizerDPLL1 Fine DelayCoarse DelayCoarse Delay FP Delay FP DelayCoarse Delay Coarse DelayP1 SynthesizerZL30120Data Sheet 2.0 Software ConfigurationThe ZL30120 is mainly controlled by accessing software registers through the serial peripheral interface (SPI). The device can be configured to operate in a highly automated manner which minimizes its interaction with the system’s processor, or it can operate in a manual mode where the system processor controls most of the operation of the device.The following table provides a summary of the registers available for status updates and configuration of the device.Addr (Hex)RegisterNameResetValue(Hex)Description TypeMiscellaneous Registers00id_reg A4Chip and version identification and reset readyindication registerR01use_hw_ctrl00Allows some functions of the device to becontrolled by hardware pinsR/WInterrupts02ref_fail_isr FF Reference failure interrupt service register R 03dpll1_isr70DPLL1 interrupt service register StickyR 04dpll2_isr00DPLL2 interrupt service register StickyR 05ref_mon_fail_0FF Ref0 and ref1 failure indications StickyR 06ref_mon_fail_1FF Ref2 and ref3 failure indications.StickyR 07ref_mon_fail_2FF Ref4 and ref5 failure indications StickyR 08ref_mon_fail_3FF Ref6 and ref7 failure indications StickyR 09ref_fail_isr_mask00Reference failure interrupt service registermaskR/W 0A dpll1_isr_mask00DPLL1 interrupt service register mask R/W 0B dpll2_isr_mask00DPLL2 interrupt service register mask R/W 0C ref_mon_fail_mask_0FF Control register to mask each failure indicatorfor ref0 and ref1R/W0D ref_mon_fail_mask_1FF Control register to mask each failure indicatorfor ref2 and ref3R/W0E ref_mon_fail_mask_2FF Control register to mask each failure indicatorfor ref4 and ref5R/W。

3W3中文手册(通用)

U n i n t e r r u p t i b l eP o w e r S u p p l y用户手册U S E R′S M A N U A L10-40KVA三相输出Three-phase Outputpag. 2 / 29安全规范注意事项本手册包含安装与操作本产品的说明.。

请在安装前由经过专业训练的人员详细阅读本手册。

因为本手册包含基本的使用说明。

请妥善保存!安全规范■ 本产品安装时必须接地请确保地线牢固地索附在有右图标示的接地铜条上:■ 所有关于本产品内部的维修保养工作必须由经过专业训练的人员操作■ 在需要更换保险丝的情形时,请更换同样型式与规格的保险丝(请参阅”设置输出入配线”章节). ■ 在必须切断UPS 的输入市电时,请断开前面板内的所有开关,或者经由UPS 的控制面板选择”SYSTEM OFF”电瓶更换必须由专业人员执行.更换之后的废电瓶请交由专业的废电的处置,因为电池内 可能有对环境造成污染的物质!由于本产品不断的改良与研发,对于本手册内容有所修正时将不另行通知.欢迎您随时与我们联系以取得最新信息.电磁干扰要求本产品”不断电式电源供应器”(UPS),符合基本的电磁干扰要求:EMC 指令89/336e 92/31 a 93/68 ECC.使用说明警告:本产品属于A 等级的UPS.在居住的环境中,本产品可能会造成无线电干扰,此情况下,使用者可能必须采取适当的措施.例如:当电视或者收音机受到干扰时,可将本产品搬移到适当的距离以减少干扰情形.索引外观位置图 (5)储存 (5)安装环境 (6)前置作业 (6)安装环境 (6)安装位置 (6)设置输出入配线 (7)保护 (7)UPS内部 (7)UPS输入 (7)UPS 输出,短路与选择性 (7)差异 (8)配线与连接 (8)启动UPS前置作业 (8)市电与负载连接 (9)三相输出(输入:三相) (9)电瓶 (9)外接电瓶箱 (9)内接电瓶箱 (9)连接状况 (9)开机程序 (9)功能检查 (10)关机 (10)配置模式 (10)在线式(ON - LINE) (10)待机经济模式(STANDBY-ON operation) (10)操作模式 (11)电瓶操作模式(不属于稳压器配置模式) (11)旁路操作模式 (12)手动旁路维护模式 (12)维护 (13)UPS 部件 (13)输入 / 输出过滤器 (13)转换器 (13)pag. 3 / 29逆变器 (14)旁路 (14)SWMB (手动维护开关), SWIN, SWOUT (14)电瓶 (14)RS232 n.1 与 n. 2 介面 (14)讯号及指令面板 (14)EPO连接器 (15)规格 (16)系统 (16)转换器输入 (16)转换器输出 (17)电瓶 (17)输出逆变器 (17)旁路 (17)状态讯息显示 (18)概述 (18)警示灯号: LED (18)警告讯息 (19)控制面板 (20)基本选单 (20)Key menu 1, "?", HELP (20)Key menu 2 "测量" (20)Key menu 2, 2 : “输出测量” (21)Key menu 3 "KEY", 指令 (21)Key menu 3, 2: 电瓶测试 (21)Key menu 3, 5: 使用者自订 (22)Key menu 3, 5, 436215, 2: 工作模式和功率设定 (22)Key menu 3, 5, 436215,3:输出电压,旁路电压范围,旁路频率范围的设定 (22)Key menu 3, 5, 436215, 4:电池数量,电池浮充电压,电池容量设定 (22)Key menu 3, 5, 436215,5:电池定时自测试设定 (22)Key menu 3, 6: 逆变器关闭 / 切至旁路模式 (23)Key menu 3, 7: 系统完全关机设定 (23)Key menu 4:事件记录 (23)故障代码表 (25)附录 (27)尺寸 / 重量 (28)pag. 4 / 29pag. 5 / 29外观位置图1. 控制面板2. 上面板3. 前面板4. 滑轮5. 背面通风孔6. 散热孔7. 风扇网格 8. EPO 连接器9. REMOTE 连接器 10. RS232-2 通讯端口 11. RS232-1 通讯端口 12. 侧面板储存本产品的储存条件如下:温 度:0°- 40°C (32°- 104°F) 相对湿度:< 95%UPS 内含电瓶时:UPS 内部的电瓶会因为化学变化而自我放电.假如您并非要立即使用本产品,请注意外装箱上标示的再充电日期(此标示只有在UPS 内含电瓶时才会有),并在期限内再充电!再充电只要提供UPS输入电源并开机限内再充电,保持在”正常模式”下运作至少24小时安装环境三相输出额定容量 [kVA] 10 15 20 30 40 操作温度0 ± 40 °C最大相对湿度95 % (无冷凝)最大操作高度4000m尺寸 (长 x 宽 x 高) [mm] 505 x 720 x 1140 505 x825 x 1215 UPS 重量100 114 120 126 140在标称负载及电瓶充电时的能量损失.[kW / kcal /B.T.U.]0.760024001.0490036001.39120048002.1180071002.824009600允许通过的空气流速(室内装置)[立方公尺/小时] 370 557 742 1100 1400 最大漏电流 (mA) < 100 mA保护等级IP20配线箱体底部前置作业本产品出厂时附有:- 保证书- 使用手册·-Nr. 3输入电瓶保险丝,-Nr. 2 输入电瓶箱保险丝(假如内接电瓶存在时)安装环境· 避免灰尘量太大,或者空气内有其它粉尘类的物质.· 确认安装的地板可以承受UPS以及电瓶箱的重量(请参照”尺寸与重量”章节) · 请检查安装的地点有足够的空间,不会造成日后维修的困扰· UPS操作时的环境必须在0-40℃之间.本产品可以在0-40℃之间正常操作.建议最佳的UPS与电瓶操作温度是20-25℃之间.事实上,电瓶在20℃下的平均寿命是4年,而在30℃之下则寿命会减半.· 避免阳光直接照射及靠近热源.为了保持安装环境的温度如上所述,请装设适当的排热系统(请参照“规格”章节确认kcal/kW/B.T.U.参考值).你可以参考下列的做法:· 自然散热;· 强制散热:当外界温度(例如20℃比UPS的操作环境低(例如25℃);· 空调设备:当外界温度(例如30℃比UPS的操作环境高(例如25℃)安装位置对于安装位置请注意下列事项:• UPS 的前面板请留至少1公尺的空间以便日后维护方便.pag. 6 / 29• UPS后背板与墙壁间至少留下20公分的距离以保持散热风扇的排热效果;至少40公分以便维护.• 请勿放置任何物品于UPS的上方• 交流/直流输出入电源线可以从UPS的底部或者后方进入设置输出入配线保护UPS内部输出入的保护开关与保险丝如下所列(请查询方块图).更换保险丝时请依照下表所示的规格与型号.三相输出UPS开关及内部保护装置UPS型式开关保险丝[kVA] UPS输入UPS 输出 / 维护整流器输入保险丝电瓶保险丝旁路保险丝输入电流.输出电流.[A]SWIN SWOUT/SWMB FBAT FBY 最大值额定值10 32A(4P) 32A(4P) 25AgR(10x38)25A gR(10x38)25A gG(10x38) 18 14 15 32A(4P) 32A(4P) 32AgR(10x38)32A gR(10x38)32A gG(10x38) 26 2620 32A(4P) 32A(4P) 32AgR(10x38)32A gR(10x38)50A gR(14x51)32A gG(10x38) 35 3530 63A(4P) 63A(4P) 50AgR(14x51)50A gR(14x51)50A gG(14x51) 52 4440 80A(4P) 80A(4P) 63AgR(14x51)80A gR(14x51)63A gG(14x51) 70 61 UPS 输入.当安装输入保护装置时,请考量下列两种模式的最大可能电流:• 在"正常操作"模式, 由输入电源至整流器, “最大输入电流” 如上表所列.断路器在整流器输入位置, 如上表中的"SWIN".• 在"旁路操作"模式, 旁路的最大电流值由断路器"SWBY”保护.UPS 输出, 短路与选择性额定的输出入电流如上表所示.短路当 UPS的负载发生异常状况时,也就是短路,UPS将会经由限制供应的输出电流值做自我保护 (短路电流).视短路发生时的操作状况.可以分成两方面:• UPS 在正常模式下:UPS将马上切换到旁路模式,在保险丝动作前,电流值如同“旁路规格” 表所示.• UPS 在电瓶供电模式下:UPS 提供两倍的额定输出电流(0.1秒)选择性在正常操作模式下,选择性参照第二行。

MSO3034示波器使用说明解读

美国泰克(Tektronix)MSO3034混合信号示波器详细说明:主要性能指标•500, 300, 100 MHz 带宽型号• 2 通道和4 通道型号•16 条数字通道(MSO 系列)•所有通道上2.5 GS/s 的采样率•所有通道上5 M 点的记录长度•>50,000 wfm/s 的最大波形捕获速率•成套高级触发简便易用功能•Wave Inspector® 控制功能,轻松导航和自动搜索波形数据•29 种自动测量FFT 分析,简化波形分析•TekVPI® 探头接口支持有源探头、差分探头和电流探头,自动定标和确定单位•9 英寸(229 mm)WVGA 宽屏彩色显示器•体积小,重量轻- 仅厚5.8 英寸(147mm),仅重9 磅(4 公斤)连接能力•前面板和后面板上的USB 2.0主机端口,迅速简便地存储数据、进行打印及连接USB 键盘•后面板上的USB 2.0 设备端口,简便地连接PC 或直接打印兼容PictBridge® 的打印机•集成10/100 以太网端口,用于联网和视频输出端口,把示波器显示画面导出到监视器或投影仪上选配串行触发和分析功能•I2C、SPI、CAN、LIN、RS-232/422/485/UART和I2S/LJ/RJ/TDM 自动串行触发、解码和搜索选项混合信号设计和分析(MSO 系列)•并行自动触发、解码和搜索功能•多通道建立时间和保持时间触发•MagniVuTM高速采集技术,在数字通道上提供了121.2 ps的精细定时分辨率选配应用支持•电源分析•HDTV 和自定义视频分析多功能混合信号设计调试工具通过MSO/DPO3000系列示波器,您可以使用一台仪器查看模拟信号、数字信号和串行信号,迅速找到和诊断复杂的嵌入式系统设计中的问题。

由于高达500 MHz的带宽及所有通道上5倍的过采样率,您可以获得必要的性能,满足当前许多主流应用的需求。

所有通道上标配高达5 M 点的深记录长度,可以捕获长信号活动窗口,同时保持精细的定时分辨率。

W134M资料

Direct Rambus™ Clock GeneratorW134M/W134SFeatures•Differential clock source for Direct Rambus™ memory subsystem for up to 800-MHz data transfer rate •Provide synchronization flexibility: the Rambus ®Channel can optionally be synchronous to an external system or processor clock•Power-managed output allows Rambus Channel clock to be turned off to minimize power consumption for mobile applications•Works with Cypress CY2210, W133, W158, W159, W161, and W167 to support Intel ® architecture platforms •Low-power CMOS design packaged in a 24- pin QSOP (150-mil SSOP) packageDescriptionThe Cypress W134M/W134S provides the differential clock signals for a Direct Rambus memory subsystem. It includes signals to synchronize the Direct Rambus Channel clock to an external system clock but can also be used in systems that do not require synchronization of the Rambus clock.Block DiagramPin ConfigurationPLLPhase PCLKM MULT0:1REFCLK SYNCLKNOutput LogicLogicTest AlignmentSTOPBS0:1CLK CLKBS0S1VDD GND CLK NC CLKB GND VDD MULT0MULT1GND242322212019181716151413VDDIR REFCLKVDD GND GND PCLKM SYNCLKNGND VDD VDDIPD STOPB PWRDNB123456789101112Pin DefinitionsPin Name No. Type DescriptionREFCLK2I Reference Clock Input. Reference clock input, normally supplied by a system frequencysynthesizer (Cypress W133).PCLKM6I Phase Detector Input. The phase difference between this signal and SYNCLKN is usedto synchronize the Rambus Channel Clock with the system clock. Both PCLKM andSYNCLKN are provided by the Gear Ratio Logic in the memory controller. If Gear RatioLogic is not used, this pin would be connected to Ground.SYNCLKN7I Phase Detector Input. The phase difference between this signal and PCLKM is used tosynchronize the Rambus Channel Clock with the system clock. Both PCLKM andSYNCLKN are provided by the Gear Ratio Logic in the memory controller. If Gear RatioLogic is not used, this pin would be connected to Ground.STOPB11I Clock Output Enable. When this input is driven to active LOW, it disables the differentialRambus Channel clocks.PWRDNB12I Active LOW Power-down. When this input is driven to active LOW, it disables the differ-ential Rambus Channel clocks and places the W134M/W134S in power-down mode. MULT 0:115, 14I PLL Multiplier Select. These inputs select the PLL prescaler and feedback dividers todetermine the multiply ratio for the PLL for the input REFCLK.CLK, CLKB20, 18O Complementary Output Clock. Differential Rambus Channel clock outputs.S0, S124, 23I Mode Control Input. These inputs control the operating mode of the W134M/W134S.NC19–No ConnectVDDIR1RefV Reference for REFCLK. Voltage reference for input reference clock.VDDIPD10RefV Reference for Phase Detector. Voltage reference for phase detector inputs and StopB. VDD3, 9, 16, 22P Power Connection. Power supply for core logic and output buffers. Connected to 3.3Vsupply.GND4, 5, 8, 13, 17,21G Ground Connection. Connect all ground pins to the common system ground plane.MULT111MULT011W134MPLL/REFCLK4.5685.333W134SPLL/REFCLK4685.333S111S011MODENormalOutput Enable TestBypassTestW134M/W134SRefclkW133PLL PhaseAlignD4DLLRACRMCM NGearRatioLogicPclkBusclkSynclkPclk/MSynclk/NW158W159W161W167Figure 1. DDLL System ArchitectureCY2210Key SpecificationsSupply Voltage:...................................... V DD = 3.3V±0.165V Operating Temperature: ...................................0°C to +70°C Input Threshold:..................................................1.5V typical Maximum Input Voltage:........................................V DD +0.5V Maximum Input Frequency:.....................................100 MHz Output Duty Cycle:...................................40/60% worst case Output Type:...........................Rambus signaling level (RSL)DDLL System Architecture and Gear Ratio LogicFigure 1 shows the Distributed Delay Lock Loop (DDLL)system architecture, including the main system clock source,the Direct Rambus clock generator (DRCG), and the core logic that contains the Rambus Access Cell (RAC), the Rambus Memory Controller (RMC), and the Gear Ratio Logic. (This diagram abstractly represents the differential clocks as a single Busclk wire.)The purpose of the DDLL is to frequency-lock and phase-align the core logic and Rambus clocks (Pclk and Synclk) at the RMC/RAC boundary in order to allow data transfers without incurring additional latency. In the DDLL architecture, a PLL is used to generate the desired Busclk frequency, while a distributed loop forms a DLL to align the phase of Pclk and Synclk at the RMC/RAC boundary.The main clock source drives the system clock (Pclk) to the core logic, and also drives the reference clock (Refclk) to the DRCG. For typical Intel architecture platforms, Refclk will be half the CPU front side bus frequency. A PLL inside the DRCG multiplies Refclk to generate the desired frequency for Busclk,and Busclk is driven through a terminated transmission line (Rambus Channel). At the mid-point of the channel, the RAC senses Busclk using its own DLL for clock alignment, followed by a fixed divide-by-4 that generates Synclk.Pclk is the clock used in the memory controller (RMC) in the core logic, and Synclk is the clock used at the core logic interface of the RAC. The DDLL together with the Gear Ratio Logic enables users to exchange data directly from the Pclk domain to the Synclk domain without incurring additional latency for synchronization. In general, Pclk and Synclk can be of different frequencies, so the Gear Ratio Logic must select the appropriate M and N dividers such that the frequencies of Pclk/M and Synclk/N are equal. In one inter-esting example, Pclk =133MHz, Synclk =100 MHz, and M =4 while N = 3, giving Pclk/M = Synclk/N = 33 MHz. This example of the clock waveforms with the Gear Ratio Logic is shown in Figure 2.The output clocks from the Gear Ratio Logic, Pclk/M, and Synclk/N, are output from the core logic and routed to the DRCG Phase Detector inputs. The routing of Pclk/M and Synclk/N must be matched in the core logic as well as on the board.After comparing the phase of Pclk/M vs. Synclk/N, the DRCG Phase Detector drives a phase aligner that adjusts the phase of the DRCG output clock, Busclk. Since everything else in the distributed loop is fixed delay, adjusting Busclk adjusts the phase of Synclk and thus the phase of Synclk/N. In this manner the distributed loop adjusts the phase of Synclk/N to match that of Pclk/M, nulling the phase error at the input of the DRCG Phase Detector. When the clocks are aligned, data can be exchanged directly from the Pclk domain to the Synclk domain.Table 1 shows the combinations of Pclk and Busclk frequencies of greatest interest, organized by Gear Ratio.Pclk Synclk Pclk/M =Synclk/NFigure 2. Gear Ratio Timing DiagramTable 1.Supported Pclk and Busclk Frequencies, by Gear RatioPclkGear Ratio and Busclk2.01.51.331.067 MHz 267 MHz 100 MHz 300 MHz 400 MHz133 MHz 267 MHz356 MHz 400 MHz150 MHz 400 MHz200 MHz400 MHzFigure 3 shows more details of the DDLL system architecture,including the DRCG output enable and bypass modes.Phase Detector SignalsThe DRCG Phase Detector receives two inputs from the core logic, PclkM (Pclk/M) and SynclkN (Synclk/N). The M and N dividers in the core logic are chosen so that the frequencies of PclkM and SynclkN are identical. The Phase Detector detects the phase difference between the two input clocks, and drives the DRCG Phase Aligner to null the input phase error through the distributed loop. When the loop is locked, the input phase error between PclkM and SynclkN is within the specification t ERR,PD given in the Device Characteristics table after the lock time given in the State Transition Section.The Phase Detector aligns the rising edge of PclkM to the rising edge of SynclkN. The duty cycle of the phase detector input clocks will be within the specification DC IN,PD given in the Operating Conditions table. Because the duty cycles of the two phase detector input clocks will not necessarily be identical,the falling edges of PclkM and SynclkN may not be aligned when the rising edges are aligned.The voltage levels of the PclkM and SynclkN signals are deter-mined by the controller. The pin VDDIPD is used as the voltage reference for the phase detector inputs and should be connected to the output voltage supply of the controller. In some applications, the DRCG PLL output clock will be used directly, by bypassing the Phase Aligner. If PclkM and SynclkN are not used, those inputs must be grounded.Selection LogicTable 2 shows the logic for selecting the PLL prescaler and feedback dividers to determine the multiply ratio for the PLL from the input Refclk. Divider A sets the feedback and divider B sets the prescaler, so the PLL output clock frequency is set by: PLLclk = Refclk*A/B.Table 3 shows the logic for enabling the clock outputs, using the StopB input signal. When StopB is HIGH, the DRCG is in its normal mode, and Clk and ClkB are complementary outputs following the Phase Aligner output (PAclk). When StopB is LOW, the DRCG is in the Clk Stop mode, the output clock drivers are disabled (set to Hi-Z), and the Clk and ClkB settle to the DC voltage V X,STOP as given in the Device Character-istics table. The level of V X,STOP is set by an external resistor network.Table 4 shows the logic for selecting the Bypass and Test modes. The select bits, S0 and S1, control the selection of these modes. The Bypass mode brings out the full-speed PLL output clock, bypassing the Phase Aligner. The Test mode brings the Refclk input all the way to the output, bypassing both the PLL and the Phase Aligner. In the Output Test mode (OE), both the Clk and ClkB outputs are put into a high-impedance state (Hi-Z). This can be used for component testing and for board-level testing.W134M/W134SRefclkW133PLLPhase Align D4DLLRACRMCM NGear Ratio LogicPclkBusclkSynclkP c l k /MS y n c l k /NS0/S1StopBW158W159W161W167Figure 3. DDLL Including Details of DRCGCY2210Table 2.PLL Divider SelectionMult0Mult1W134MW134SA B A B 0092410161611181811163163Table 3.Clock Stop Mode SelectionMode StopB Clk ClkB Normal 1PAclk PAclkB Clk StopV X,STOPV X,STOPTable 5 shows the logic for selecting the Power-down mode,using the PwrDnB input signal. PwrDnB is active LOW (enabled when 0). When PwrDnB is disabled, the DRCG is in its normal mode. When PwrDnB is enabled, the DRCG is put into a powered-off state, and the Clk and ClkB outputs are three-stated.Table of Frequencies and Gear RatiosTable 6 shows several supported Pclk and Busclk frequencies, the corresponding A and B dividers required in the DRCG PLL, and the corresponding M and N dividers in the gear ratio logic. The column Ratio gives the Gear Ratio as defined Pclk/Synclk (same as M and N). The column F@PD gives the divided down frequency (in MHz) at the Phase Detector, where F@PD =Pclk/M =Synclk/N.State TransitionsThe clock source has three fundamental operating states.Figure 4 shows the state diagram with each transition labelled A through H. Note that the clock source output may NOT be glitch-free during state transitions.Upon powering up the device, the device can enter any state,depending on the settings of the control signals, PwrDnB and StopB.In Power-down mode, the clock source is powered down with the control signal, PwrDnB, equal to 0. The control signals S0and S1 must be stable before power is applied to the device,and can only be changed in Power-down mode (PwrDnB = 0).The reference inputs, V DDR and V DDPD , may remain on or may be grounded during the Power-down mode.The control signals Mult0 and Mult1 can be used in two ways.If they are changed during Power-down mode, then the Power-down transition timings determine the settling time of the DRCG. However, the Mult0 and Mult1 control signals can also be changed during Normal mode. When the Mult control signals are “hot-swapped” in this manner, the Mult transition timings determine the settling time of the DRCG.In Normal mode, the clock source is on, and the output is enabled.Table 7 lists the control signals for each state.Figure 5 shows the timing diagrams for the various transitions between states, and Table 8 specifies the latencies of each state transition. Note that these transition latencies assume the following.Refclk input has settled and meets specification shown in Table .Mult0, Mult1, S0 and S1 control signals are stable.Table 4.Bypass and Test Mode SelectionMode S0S1Bypclk (int.)Clk ClkB Normal00Gnd PAclk PAclkB Output Test (OE)01–Hi-Z Hi-Z Bypass 10PLLclk PLLclk PLLclkB Test11RefclkRefclkRefclkBTable 5.Power-down Mode SelectionMode PwrDnBClk ClkB Normal 1PAclk PAclkB Power-downGNDGNDTable 6.Examples of Frequencies, Dividers, and Gear RatiosPclk Refclk Busclk Synclk A B M N Ratio F@PD 6733267678122 1.03310050300756186 1.3312.5100504001008144 1.02513367267674142 2.0331336740010061861.3316.7TestMN LKNormal Power-DownClk StopD CG AEF HVDD Turn-On VDD Turn-OnVDD Turn-OnVDD Turn-On B J Figure 4. Clock Source State DiagramTable 7.Control Signals for Clock Source States State PwrDnBStopB Clock Source Output Buffer Power-down 0X OFF Ground Clock Stop 10ON Disabled Normal11ONEnabledTiming DiagramsTable 8.State Transition Latency SpecificationsTransitionFrom To Transition LatencyDescriptionParameter Max.A Power-down Normal t POWERUP 3 ms Time from PwrDnB to Clk/ClkB output settled (excluding t DISTLOCK ).C Power-down Clk Stop t POWERUP 3 ms Time from PwrDnB until the internal PLL and clock has turned ON and settled.K Power-down Test t POWERUP 3 ms Time from PwrDnB to Clk/ClkB output settled (excluding t DISTLOCK ).G V DD ON Normal t POWERUP 3 ms Time from V DD is applied and settled until Clk/ClkB output settled (excluding t DISTLOCK ).H V DD ON Clk Stop t POWERUP 3 ms Time from V DD is applied and settled until internal PLL and clock has turned ON and settled.M V DD ONTestt POWERUP3 ms Time from V DD is applied and settled until internal PLL and clock has turned ON and settled.JNormal Normal t MULT1 msTime from when Mult0 or Mult1 changed until Clk/ClkB output resettled (excluding t DISTLOCK ).PwrDnB Clk/ClkBPower-down Exit and EntryOutput Enable ControlStopBClk/ClkBnot specified glitches may and glitch-free 50 ps of the phase before disabledoccurFigure 5. State Transition Timing Diagramst MULTClk/ClkBMult0 and/or Mult1Figure 6. Multiply Transition TimingFigure 5 shows that the Clk Stop to Normal transition goes through three phases. During t CLKON , the clock output is not specified and can have glitches. For t CLKON < t < t CLKSETL , the clock output is enabled and must be glitch-free. For t >t CLKSETL , the clock output phase must be settled to within 50ps of the phase before the clock output was disabled. At this time, the clock output must also meet the voltage and timing specifications of Table . The outputs are in a high-impedance state during the Clk Stop mode.E Clk Stop Normal t CLKON 10 nsTime from StopB until Clk/ClkB provides glitch-free clock edges.E Clk Stop Normal t CLKSETL 20 cycles Time from StopB to Clk/ClkB output settled to within 50ps of the phase before CLK/CLKB was disabled.F Normal Clk Stop t CLKOFF 5 ns Time from StopB to Clk/ClkB output disabled.L Test Normal t CTL 3 ms Time from when S0 or S1 is changed until CLK/CLKB output has resettled (excluding t DISTLOCK ).N NormalTestt CTL3 ms Time from when S0 or S1 is changed until CLK/CLKB output has resettled (excluding t DISTLOCK ).B,DNormal or Clk Stop Power-down t POWERDN1 ms Time from PwrDnB to the device in Power-down.Table 8.State Transition Latency Specifications (continued)TransitionFrom To Transition LatencyDescriptionParameter Max.Table 9.Distributed Loop Lock Time Specification Parameter DescriptionMin.Max.Unit t DISTLOCKTime from when Clk/ClkB output is settled to when the phase error between SynclkN and PclkM falls within the t ERR,PD spec in Table .5msTable 10.Supply and Reference Current SpecificationParameter DescriptionMin.Max.Unit I POWERDOWN “Supply” current in Power-down state (PwrDnB 1 = 0)–250µA I CLKSTOP “Supply” current in Clk Stop state (StopB = 0)–65mA I NORMAL “Supply” current in Normal state (StopB = 1,PwrDnB = 1)–100mA I REF,PWDN Current at VDDIR or VDDIPD reference pin in Power-down state (PwrDnB = 0)–50µA I REF,NORMCurrent at VDDIR or VDDIPD reference pin in Normal or Clk Stop state (PwrDnB = 1)–2mANotes:1.Represents stress ratings only, and functional operation at the maximums is not guaranteed.2.Gives the nominal values of the external components and their maximum acceptable tolerance, assuming Z CH = 28Ω.3.Do not populate C F . Leave pads for future use.4.Multiple Supplies: The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.5.Refclk jitter measured at V DDIR (nom)/2.6.If input modulation is used: input modulation is allowed but not required.7.Capacitance measured at Freq=1 MHz, DC bias = 0.9V and V AC < 100 mV.8.The amount of allowed spreading for any non-triangular modulation is determined by the induced downstream tracking skew, which cannot exceed the skew generated by the specified 0.6% triangular modulation. Typically, the amount of allowed non-triangular modulation is about 0.5%.Absolute Maximum Conditions [1]Parameter DescriptionMin.Max.Unit V DD, ABS Max. voltage on V DD with respect to ground –0.5 4.0V V I, ABSMax. voltage on any pin with respect ground–0.5V DD +0.5VExternal Component Values [2]Parameter DescriptionMin.Max.Unit R S Serial Resistor 39±5%ΩR P Parallel Resistor51±5%ΩC F Edge Rate Filter Capacitor 4 – 15[3]±10%pF C MIDAC Ground Capacitor470 pF0.1 µF±20%Operating Conditions [4]Parameter DescriptionMin.Max.Unit V DD Supply Voltage3.135 3.465V T A Ambient Operating Temperature 070°C t CYCLE,IN Refclk Input Cycle Time 1040ns t J,IN Input Cycle-to-Cycle Jitter [5]–250ps DC IN Input Duty Cycle over 10,000 Cycles 4060%t CYCLE FM IN Input Frequency of Modulation3033kHz PM IN [6]Modulation Index for Triangular Modulation –0.6%Modulation Index for Non-Triangular Modulation –0.5[8]%t CYCLE,PD Phase Detector Input Cycle Time at PclkM & SynclkN 30100ns t ERR,INIT Initial Phase error at Phase Detector Inputs –0.50.5t CYCLE,PD DC IN,PD Phase Detector Input Duty Cycle over 10,000 Cycles2575t CYCLE,PD t I,SR Input Slew Rate (measured at 20%-80% of input voltage) for PclkM, SynclkN, and Refclk14V/ns C IN,PD Input Capacitance at PclkM, SynclkN, and Refclk [7]–7pF DC IN,PD Input Capacitance matching at PclkM and SynclkN [7]–0.5pF C IN,CMOS Input Capacitance at CMOS pins (excluding PclkM, SynclkN, and Refclk)[7]–10pF V IL Input (CMOS) Signal Low Voltage –0.3VDD V IH Input (CMOS) Signal High Voltage 0.7–VDD V IL,R Refclk input Low Voltage –0.3V DDIR V IH,R Refclk input High Voltage0.7–V DDIR V IL,PD Input Signal Low Voltage for PD Inputs and StopB –0.3V DDIPD V IH,PD Input Signal High Voltage for PD Inputs and StopB 0.7–V DDIPDV DDIR Input Supply Reference for Refclk 1.235 3.465V V DDIPDInput Supply Reference for PD Inputs1.2352.625VNotes:9.Output Jitter spec measured at t CYCLE = 2.5 ns.10.Output Jitter Spec measured at t CYCLE = 3.75 ns.11.V COS = V OH –V OL.12.r OUT = DV O / D I O . This is defined at the output pins.Device CharacteristicsParameter DescriptionMin.Max.Unit t CYCLE Clock Cycle Time2.53.75ns t JCycle-to-Cycle Jitter at Clk/ClkB [9]–60ps Total Jitter over 2, 3, or 4 Clock Cycles [9]–100ps 266-MHz Cycle-to-Cycle Jitter [10]–100ps 266-MHz Total Jitter over 2, 3, or 4 Clock Cycles [10]–160ps t STEP Phase Aligner Phase Step Size (at Clk/ClkB)1–ps t ERR,PD Phase Detector Phase Error for Distributed Loop Measured at PclkM-SynclkN (rising edges) (does not include clock jitter)–100100ps t ERR,SSC PLL Output Phase Error when Tracking SSC –100100ps V X,STOP Output Voltage during Clk Stop (StopB=0) 1.1 2.0V V X Differential Output Crossing-Point Voltage 1.3 1.8V V COS Output Voltage Swing (p-p single-ended)[11]0.40.6V V OH Output High Voltage – 2.0V V OL Output Low voltage1.0–V r OUT Output Dynamic Resistance (at pins)[12]1250ΩI OZ Output Current during Hi-Z (S0 = 0, S1 = 1)–50µA I OZ,STOP Output Current during Clk Stop (StopB = 0)–500µA DC Output Duty Cycle over 10,000 Cycles 4060%t CYCLEt DC,ERR Output Cycle-to-Cycle Duty Cycle Error–50ps t R,t F Output Rise and Fall Times (measured at 20%–80% of output voltage)250500ps t CR,CFDifference between Output Rise and Fall Times on the Same Pin of a Single Device (20%–80%)–100psLayout Example2120191817151413671245GVDDIRG VDDIPD242322G389111210GG Internal Power Supply Plane46GG FB+3.3V SupplyC410 µF0.005 µF G GC3GGG GG G GG GGG G = VIA to GND plane layer FB = Dale ILB1206 - 300 (300Ω @ 100 MHz)All Bypass cap = 0.1 Ceramic XR7Ordering InformationOrdering CodePackage TypeW134M/W134SH 24-pin QSOP (150 mils, SSOP)W134M/W134SHT 24-pin QSOP (150 mils, SSOP) – Tape and Reel W134M/W134SSQC 24-pin QSOP (150 mils, SSOP) – (Lead-free)W134M/W134SSQCT 24-pin QSOP (150 mils, SSOP) – Tape and Reel – (Lead-free)W134SH 24-pin QSOP (150 mils, SSOP)W134SHT24-pin QSOP (150 mils, SSOP) – Tape and ReelPackage Diagram24-Lead Quarter Size Outline Q1351-85055-*BDirect Rambus is a trademark and Rambus is a registered trademark of Rambus Inc. Intel is a registered trademark of Intel Corporation. All product and company names mentioned in this document may be the trademarks of their respective holders.Document #: 38-07426 Rev. *B Page 11 of 12© Cypress Semiconductor Corporation, 2003. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.Document #: 38-07426 Rev. *B Page 12 of 12Document History Page Document Title: W134M/W134S Direct Rambus™ Clock Generator Document Number: 38-07426REV.ECN NO.Issue Date Orig. of Change Description of Change **11553105/10/02DSG Change from Spec number: 38-00822 to 38-07246*A12292712/14/02RBI Add power-up requirements to operating information *B 13167112/15/03RGL Added Lead-free to the W134M device in the ordering information table。

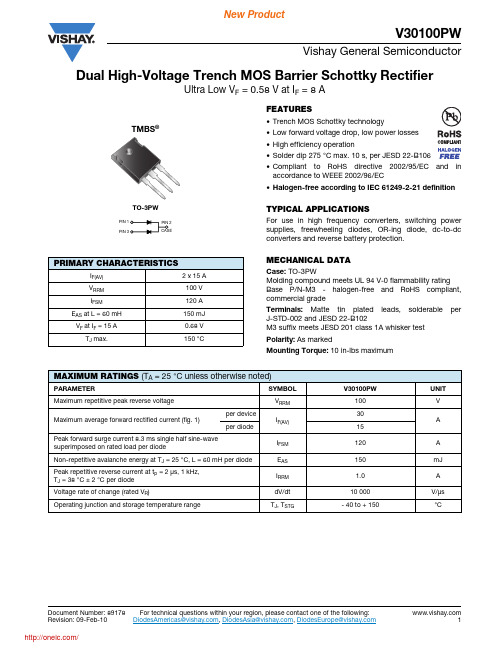

V30100PW-M34W;中文规格书,Datasheet资料

Document Number: 89178For technical questions within your region, please contact one of the following:Dual High-Voltage Trench MOS Barrier Schottky RectifierUltra Low V F = 0.58 V at I F = 8 AV30100PWVishay General SemiconductorFEATURES•Trench MOS Schottky technology•Low forward voltage drop, low power losses •High efficiency operation•Solder dip 275 °C max. 10 s, per JESD 22-B106•Compliant to RoHS directive 2002/95/EC and in accordance to WEEE 2002/96/EC•Halogen-free according to IEC 61249-2-21 definitionTYPICAL APPLICATIONSFor use in high frequency converters, switching power supplies, freewheeling diodes, OR-ing diode, dc-to-dc converters and reverse battery protection.MECHANICAL DATACase: TO-3PWMolding compound meets UL 94 V-0 flammability rating Base P/N-M3 - halogen-free and RoHS compliant,commercial gradeTerminals: Matte tin plated leads, solderable per J-STD-002 and JESD 22-B102M3 suffix meets JESD 201 class 1A whisker test Polarity: As markedMounting Torque: 10 in-lbs maximumPRIMARY CHARACTERISTICSI F(AV) 2 x 15 A V RRM 100 V I FSM120 A E AS at L = 60 mH 150 mJ V F at I F = 15 A 0.68 V T J max.150 °CMAXIMUM RATINGS (T A = 25°C unless otherwise noted)PARAMETERSYMBOL V30100PWUNIT Maximum repetitive peak reverse voltage V RRM 100V Maximum average forward rectified current (fig. 1)per device I F(AV)30A per diode15Peak forward surge current 8.3 ms single half sine-wave superimposed on rated load per diodeI FSM 120A Non-repetitive avalanche energy at T J = 25 °C, L = 60 mH per diode E AS 150mJ Peak repetitive reverse current at t p = 2 μs, 1 kHz,T J = 38 °C ± 2 °C per diode I RRM 1.0A Voltage rate of change (rated V R )dV/dt 10 000V/μs Operating junction and storage temperature rangeT J , T STG- 40 to + 150°C For technical questions within your region, please contact one of the following:Document Number: 89178V30100PWVishay General SemiconductorNotes(1)Pulse test: 300 μs pulse width, 1 % duty cycle (2)Pulse test: Pulse width ≤ 40 msRATINGS AND CHARACTERISTICS CURVES(T A = 25 °C unless otherwise noted)Fig. 1 - Forward Current Derating Curve Fig. 2 - Forward Power Loss Characteristics Per DiodeELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted)PARAMETER TEST CONDITIONS SYMBOL TYP.MAX.UNIT Breakdown voltageI R = 1.0 mA T J = 25 °C V BR100 (minimum)-VInstantaneous forward voltage per diodeI F = 8 AT J = 25 °CV F (1)0.64-V I F = 15 A 0.830.91I F = 8 A T J = 125 °C 0.58-I F = 15 A 0.680.76Reverse current per diodeV R = 70 VT J = 25 °C I R (2) 6.3-μA T J = 125 °C 4.4-mA V R = 100 VT J = 25 °C 22450μA T J = 125 °C1026mATHERMAL CHARACTERISTICS (T A = 25°C unless otherwise noted)PARAMETERSYMBOL V30100PWUNIT Typical thermal resistanceper diode R θJC2.0°C/Wper device1.4ORDERING INFORMATION (Example)PACKAGE PREFERRED P/N UNIT WEIGHT (g)PACKAGE CODEBASE QUANTITYDELIVERY MODETO-3PWV30100PW-M3/4W4.54W30/tubeTubeDocument Number: 89178For technical questions within your region, please contact one of the following:V30100PWVishay General SemiconductorFig. 3 - Typical Instantaneous Forward Characteristics Per Diode Fig. 4 - Typical Reverse Characteristics Per Diode Fig. 5 - Typical Junction Capacitance Per DiodeFig. 6 - Typical Transient Thermal Impedance Per DiodePACKAGE OUTLINE DIMENSIONS in inches (millimeters)Legal Disclaimer Notice VishayDisclaimerALL PRODU CT, PRODU CT SPECIFICATIONS AND DATA ARE SU BJECT TO CHANGE WITHOU T NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.Statements regarding the suitability of products for certain types of applications are based on Vishay’s knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer’s responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer’s technical experts. Product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein.Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Vishay and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attorneys fees, even if such claim alleges that Vishay or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.Material Category PolicyVishay Intertechnology, Inc. hereb y certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.Revision: 12-Mar-121Document Number: 91000分销商库存信息:VISHAY-GENERAL-SEMICONDUCTOR V30100PW-M3/4W。

MIM-5373K4中文资料