High-Level Optimizations for Low-Level Software

Silicon Laboratories 微控制器低功耗选择指南说明书

How to Pick the Right Microcontroller Based on Low-PowerSpecificationsIntroductionChoosing the right ultra-low-power microcontroller (MCU) for your next embedded design can be a confusing task when you compare claimed current consumption specifications in a myriad of data sheets provided by MCU vendors. In many cases, developers initially scan the first page of a data sheet as a reference point to gain basic information about an MCU, including peripherals, operating speed, package information, number of GPIOs and power characteristics. This approach works well to assess an MCU’s overall functionality, but it is not particularly useful when trying to gauge low-power characteristics.To get a broader view of an M CU’s true low-power operation, developers must take into consideration current consumption, state retention, wake-up time, wake-up sources and peripherals that are capable of operating while in low-power mode. Developers must compare a common operating mode to gain a balanced, apples-to-apples comparison among competing low-power MCUs. It is also important to take into consideration any additional functionality or peripherals that can reduce total system power and available evaluation tools that can make an engineer’s job easier.Microcontroller vendors will usually list the lowest power achievable on the first page of the data sheet. Although the device may be capable of achieving the specification in the data sheet, the actual operating mode may not be practical and useful in a real-world application. Some of the non-advertised features of the lowest power mode may include a very slow wake time, no state or RAM retention, or a reduced operating voltage range.To get around the variety of low-power specifications, developers must identify a common operating mode consisting of two sections: electrical specifications and low-power functionality.Comparing Electrical Specifications of MicrocontrollersThe electrical specifications are available in the data sheet, but determining which specifications are relevant may require some digging. Usually the electrical specifications are organized by vendor-specific power mode. This makes assessment slightly more difficult, as it requires knowledge and familiarity with the functionality of each power mode.In general, it is beneficial to define a set of operating conditions and then map them to a power mode. For example, the developer might define the following set of operating conditions:∙Sleep mode current consumption with state and RAM retentiono All other peripherals disabled∙Sleep mode current consumption with RTC running with state and RAM retentiono RTC enabled and running all other peripherals disabled.∙Wake time∙Supply voltage rangeOnce the operating conditions are clearly defined, it should be easy to determine the applicable vendor-specific power mode.Additional Low-Power FunctionalityThe second section, low-power functionality, is not as easy to locate in the vendor’s documentation and may be spread across the data sheet and reference manual. Examples of low-power functionality include: ∙Available wake sources∙How code resumes execution∙Peripherals capable of operating in sleep mode.Once the common operating mode has been clearly defined, developers can begin to examine the documentation in more detail.While going through this exercise of compiling data, keep in mind that there may be some MCU-specific features that can further optimize an application for ultra-low power. Optimizations may reduce bill of material (BOM) costs, provide longer product life or provide greater design flexibility. For example, an on-chip dc-dc converter can efficiently provide power to the system and decrease power consumption. This can enable the use of smaller batteries, which will decrease the overall BOM costs, or provide power budget flexibility. A variety of wake sources can provide design flexibility and allow the microcontroller to stay in the lowest power mode as long as possible, further reducing the average current consumption of the application.Allowing firmware to scale the internal supply voltage is another optimization knob available to the developer. If an MCU is operating at a slow frequency, it may be possible to decrease the supply voltage and save power. Selective clock gating allows hardware blocks to be disconnected from the active circuits, preventing inactive peripherals from consuming power. These types of features are not comprehended by supply current specifications that are commonly used to rank low-power MCUs, but are critical to achieving the lowest overall system power consumption.Reducing Complexity Using ToolsAs MCUs become more and more configurable to achieve the lowest power consumption, they also can become more complex. To cope with this increased complexity, developers should take a close look at the evaluation platforms available for an MCU and the overall ease of implementing a solution. For example, the development board and software tools used to program the MCU should be intuitive and easy-to-use. Hardware that is difficult to understand or use is not likely to lead to an easy firmware development process. From a firmware perspective, MCU vendors should supply firmware examples that can recreate specifications from the data sheet. If advertised current consumption specifications cannot be recreated on an evaluation platform, it is likely that it will be just as difficult (if not impossible) to configure the MCU to achieve these numbers on custom hardware. Giving customers a variety of code examples that can be used as a starting point for their code development can reduce time-to-market and help engineers learn to use a device.Graphical configuration tools can aid in development and help the developer gain a deeper understanding of an MCU. When developing low-power applications, it is helpful to know where the total consumed power is going. This information is useful because it highlights what aspect of a design needs to be further optimized and can also help the developer understand the overall architecture of the device. Ideally, low-power configuration tools could give tips on further reducing power as well as highlight any configuration errors that were detected throughout the configuration process. For example, the Power Estimator utility within Silicon Labs’ AppBuilder graphical configuration tool provides Power Tips that give configuration guidance and a power-budget pie chart showing how much power is consumed and which peripherals are consuming the power. As configuration changes are made, the pie chart automatically updates.Figure 1. Power Estimator Enables Developers to Optimize for Lowest Current Consumption To facilitate the microcontroller comparison process, the following table provides a list of common operating modes, as well as system-level optimizations and development tools available for Silicon Labs’32-bit SiM3L1xx MCUs based on the ARM® Cortex™-M3 core.SummaryEvaluating and selecting a microcontroller for a low-power application requires more than a quick scan of the first page of the data sheet. Determining which MCU provides the lowest overall system power requires developers to know the device’s supply current specifications, as well as any system-level optimizations that can reduce the overall supply current.Unfortunately, each MCU vendor specifies operating conditions differently and in some cases advertises a low-power number that is available in an unusable mode. Using a common operating mode to compare MCUs will prevent developers from being misled by vendor claims of ultra-low-power operation.Once the electrical characteristics of a device are understood and quantified, developers should take a look at the evaluation platform and software tools available. These considerations are crucial in getting an engineering team up and running quickly and should be included in the final microcontroller selection process. Find out more about Silicon Labs’ microcontrollers, including 8-bit and 32-bit MCUs at/mcu.# # #Silicon Labs invests in research and development to help our customers differentiate in the market with innovative low-power, small size, analog intensive, mixed-signal solutions. Silicon Labs' extensive patent portfolio is a testament to our unique approach and world-class engineering team. Patent: /patent-notice© 2013, Silicon Laboratories Inc. ClockBuilder, DSPLL, Ember, EZMac, EZRadio, EZRadioPRO, EZLink, ISOmodem, Precision32, ProSLIC, QuickSense, Silicon Laboratories and the Silicon Labs logo are trademarks or registered trademarks of Silicon Laboratories Inc. ARM and Cortex-M3 are trademarks or registered trademarks of ARM Holdings. ZigBee is a registered trademark of ZigBee Alliance, Inc. All other product or service names are the property of their respective owners.。

德尔·韦玛网络S4048T-ON交换机说明书

The Dell EMC Networking S4048T-ON switch is the industry’s latest data center networking solution, empowering organizations to deploy modern workloads and applications designed for the open networking era. Businesses who have made the transition away from monolithic proprietary mainframe systems to industry standard server platforms can now enjoy even greater benefits from Dell EMC open networking platforms. By using industry-leading hardware and a choice of leading network operating systems to simplify data center fabric orchestration and automation, organizations can tailor their network to their unique requirements and accelerate innovation.These new offerings provide the needed flexibility to transform data centers. High-capacity network fabrics are cost-effective and easy to deploy, providing a clear path to the software-defined data center of the future with no vendor lock-in.The S4048T-ON supports the open source Open Network Install Environment (ONIE) for zero-touch installation of alternate network operating systems, including feature rich Dell Networking OS.High density 1/10G BASE-T switchThe Dell EMC Networking S-Series S4048T-ON is a high-density100M/1G/10G/40GbE top-of-rack (ToR) switch purpose-builtfor applications in high-performance data center and computing environments. Leveraging a non-blocking switching architecture, theS4048T-ON delivers line-rate L2 and L3 forwarding capacity within a conservative power budget. The compact S4048T-ON design provides industry-leading density of 48 dual-speed 1/10G BASE-T (RJ45) ports, as well as six 40GbE QSFP+ up-links to conserve valuable rack space and simplify the migration to 40Gbps in the data center core. Each40GbE QSFP+ up-link can also support four 10GbE (SFP+) ports with a breakout cable. In addition, the S4048T-ON incorporates multiple architectural features that optimize data center network flexibility, efficiency and availability, including I/O panel to PSU airflow or PSU to I/O panel airflow for hot/cold aisle environments, and redundant, hot-swappable power supplies and fans. S4048T-ON supports feature-rich Dell Networking OS, VLT, network virtualization features such as VRF-lite, VXLAN Gateway and support for Dell Embedded Open Automation Framework.• The S4048T-ON is the only switch in the industry that supports traditional network-centric virtualization (VRF) and hypervisorcentric virtualization (VXLAN). The switch fully supports L2 VX-• The S4048T-ON also supports Dell EMC Networking’s Embedded Open Automation Framework, which provides enhanced network automation and virtualization capabilities for virtual data centerenvironments.• The Open Automation Framework comprises a suite of interre-lated network management tools that can be used together orindependently to provide a network that is flexible, available andmanageable while helping to reduce operational expenses.Key applicationsDynamic data centers ready to make the transition to software-defined environments• High-density 10Gbase-T ToR server access in high-performance data center environments• Lossless iSCSI storage deployments that can benefit from innovative iSCSI & DCB optimizations that are unique only to Dell NetworkingswitchesWhen running the Dell Networking OS9, Active Fabric™ implementation for large deployments in conjunction with the Dell EMC Z-Series, creating a flat, two-tier, nonblocking 10/40GbE data center network design:• High-performance SDN/OpenFlow 1.3 enabled with ability to inter-operate with industry standard OpenFlow controllers• As a high speed VXLAN Layer 2 Gateway that connects thehypervisor based ovelray networks with nonvirtualized infrastructure Key features - general• 48 dual-speed 1/10GbE (SFP+) ports and six 40GbE (QSFP+)uplinks (totaling 72 10GbE ports with breakout cables) with OSsupport• 1.44Tbps (full-duplex) non-blocking switching fabric delivers line-rateperformance under full load with sub 600ns latency• I/O panel to PSU airflow or PSU to I/O panel airflow• Supports the open source ONIE for zero-touch• installation of alternate network operating systems• Redundant, hot-swappable power supplies and fansDELL EMC NETWORKING S4048T-ON SWITCHEnergy-efficient 10GBASE-T top-of-rack switch optimized for data center efficiencyKey features with Dell EMC Networking OS9Scalable L2 and L3 Ethernet switching with QoS and a full complement of standards-based IPv4 and IPv6 features, including OSPF, BGP and PBR (Policy Based Routing) support• Scalable L2 and L3 Ethernet switching with QoS and a full complement of standards-based IPv4 and IPv6 features, including OSPF, BGP andPBR (Policy Based Routing) support• VRF-lite enables sharing of networking infrastructure and provides L3traffic isolation across tenants• Increase VM Mobility region by stretching L2 VLAN within or across two DCs with unique VLT capabilities like Routed VL T, VLT Proxy Gateway • VXLAN gateway functionality support for bridging the nonvirtualizedand the virtualized overlay networks with line rate performance.• Embedded Open Automation Framework adding automatedconfiguration and provisioning capabilities to simplify the management of network environments. Supports Puppet agent for DevOps• Modular Dell Networking OS software delivers inherent stability as well as enhanced monitoring and serviceability functions.• Enhanced mirroring capabilities including 1:4 local mirroring,• Remote Port Mirroring (RPM), and Encapsulated Remote PortMirroring (ERPM). Rate shaping combined with flow based mirroringenables the user to analyze fine grained flows• Jumbo frame support for large data transfers• 128 link aggregation groups with up to 16 members per group, usingenhanced hashing• Converged network support for DCB, with priority flow control(802.1Qbb), ETS (802.1Qaz), DCBx and iSCSI TLV• S4048T-ON supports RoCE and Routable RoCE to enable convergence of compute and storage on Active FabricUser port stacking support for up to six units and unique mixed mode stacking that allows stacking of S4048-ON with S4048T-ON to providecombination of 10G SFP+ and RJ45 ports in a stack.Physical48 fixed 10GBase-T ports supporting 100M/1G/10G speeds6 fixed 40 Gigabit Ethernet QSFP+ ports1 RJ45 console/management port with RS232signaling1 USB 2.0 type A to support mass storage device1 Micro-USB 2.0 type B Serial Console Port1 8 GB SSD ModuleSize: 1RU, 1.71 x 17.09 x 18.11”(4.35 x 43.4 x 46 cm (H x W x D)Weight: 23 lbs (10.43kg)ISO 7779 A-weighted sound pressure level: 65 dB at 77°F (25°C)Power supply: 100–240V AC 50/60HzMax. thermal output: 1568 BTU/hMax. current draw per system:4.6 A at 460W/100VAC,2.3 A at 460W/200VACMax. power consumption: 460 WattsT ypical power consumption: 338 WattsMax. operating specifications:Operating temperature: 32°F to 113°F (0°C to45°C)Operating humidity: 5 to 90% (RH), non-condensing Max. non-operating specifications:Storage temperature: –40°F to 158°F (–40°C to70°C)Storage humidity: 5 to 95% (RH), non-condensingRedundancyHot swappable redundant powerHot swappable redundant fansPerformance GeneralSwitch fabric capacity:1.44Tbps (full-duplex)720Gbps (half-duplex)Forwarding Capacity: 1080 MppsLatency: 2.8 usPacket buffer memory: 16MBCPU memory: 4GBOS9 Performance:MAC addresses: 160KARP table 128KIPv4 routes: 128KIPv6 hosts: 64KIPv6 routes: 64KMulticast routes: 8KLink aggregation: 16 links per group, 128 groupsLayer 2 VLANs: 4KMSTP: 64 instancesVRF-Lite: 511 instancesLAG load balancing: Based on layer 2, IPv4 or IPv6headers Latency: Sub 3usQOS data queues: 8QOS control queues: 12Ingress ACL: 16KEgress ACL: 1KQoS: Default 3K entries scalable to 12KIEEE compliance with Dell Networking OS9802.1AB LLDP802.1D Bridging, STP802.1p L2 Prioritization802.1Q VLAN T agging, Double VLAN T agging,GVRP802.1Qbb PFC802.1Qaz ETS802.1s MSTP802.1w RSTP802.1X Network Access Control802.3ab Gigabit Ethernet (1000BASE-T)802.3ac Frame Extensions for VLAN T agging802.3ad Link Aggregation with LACP802.3ae 10 Gigabit Ethernet (10GBase-X) withQSA802.3ba 40 Gigabit Ethernet (40GBase-SR4,40GBase-CR4, 40GBase-LR4) on opticalports802.3u Fast Ethernet (100Base-TX)802.3x Flow Control802.3z Gigabit Ethernet (1000Base-X) with QSA 802.3az Energy Efficient EthernetANSI/TIA-1057 LLDP-MEDForce10 PVST+Max MTU 9216 bytesRFC and I-D compliance with Dell Networking OS9General Internet protocols768 UDP793 TCP854 T elnet959 FTPGeneral IPv4 protocols791 IPv4792 ICMP826 ARP1027 Proxy ARP1035 DNS (client)1042 Ethernet Transmission1305 NTPv31519 CIDR1542 BOOTP (relay)1812 Requirements for IPv4 Routers1918 Address Allocation for Private Internets 2474 Diffserv Field in IPv4 and Ipv6 Headers 2596 Assured Forwarding PHB Group3164 BSD Syslog3195 Reliable Delivery for Syslog3246 Expedited Assured Forwarding4364 VRF-lite (IPv4 VRF with OSPF, BGP,IS-IS and V4 multicast)5798 VRRPGeneral IPv6 protocols1981 Path MTU Discovery Features2460 Internet Protocol, Version 6 (IPv6)Specification2464 Transmission of IPv6 Packets overEthernet Networks2711 IPv6 Router Alert Option4007 IPv6 Scoped Address Architecture4213 Basic Transition Mechanisms for IPv6Hosts and Routers4291 IPv6 Addressing Architecture4443 ICMP for IPv64861 Neighbor Discovery for IPv64862 IPv6 Stateless Address Autoconfiguration 5095 Deprecation of T ype 0 Routing Headers in IPv6IPv6 Management support (telnet, FTP, TACACS, RADIUS, SSH, NTP)VRF-Lite (IPv6 VRF with OSPFv3, BGPv6, IS-IS) RIP1058 RIPv1 2453 RIPv2OSPF (v2/v3)1587 NSSA 4552 Authentication/2154 OSPF Digital Signatures Confidentiality for 2328 OSPFv2 OSPFv32370 Opaque LSA 5340 OSPF for IPv6IS-IS1142 Base IS-IS Protocol1195 IPv4 Routing5301 Dynamic hostname exchangemechanism for IS-IS5302 Domain-wide prefix distribution withtwo-level IS-IS5303 3-way handshake for IS-IS pt-to-ptadjacencies5304 IS-IS MD5 Authentication5306 Restart signaling for IS-IS5308 IS-IS for IPv65309 IS-IS point to point operation over LANdraft-isis-igp-p2p-over-lan-06draft-kaplan-isis-ext-eth-02BGP1997 Communities2385 MD52545 BGP-4 Multiprotocol Extensions for IPv6Inter-Domain Routing2439 Route Flap Damping2796 Route Reflection2842 Capabilities2858 Multiprotocol Extensions2918 Route Refresh3065 Confederations4360 Extended Communities4893 4-byte ASN5396 4-byte ASN representationsdraft-ietf-idr-bgp4-20 BGPv4draft-michaelson-4byte-as-representation-054-byte ASN Representation (partial)draft-ietf-idr-add-paths-04.txt ADD PATHMulticast1112 IGMPv12236 IGMPv23376 IGMPv3MSDP, PIM-SM, PIM-SSMSecurity2404 The Use of HMACSHA- 1-96 within ESPand AH2865 RADIUS3162 Radius and IPv63579 Radius support for EAP3580 802.1X with RADIUS3768 EAP3826 AES Cipher Algorithm in the SNMP UserBase Security Model4250, 4251, 4252, 4253, 4254 SSHv24301 Security Architecture for IPSec4302 IPSec Authentication Header4303 ESP Protocol4807 IPsecv Security Policy DB MIBdraft-ietf-pim-sm-v2-new-05 PIM-SMwData center bridging802.1Qbb Priority-Based Flow Control802.1Qaz Enhanced Transmission Selection (ETS)Data Center Bridging eXchange (DCBx)DCBx Application TLV (iSCSI, FCoE)Network management1155 SMIv11157 SNMPv11212 Concise MIB Definitions1215 SNMP Traps1493 Bridges MIB1850 OSPFv2 MIB1901 Community-Based SNMPv22011 IP MIB2096 IP Forwarding T able MIB2578 SMIv22579 T extual Conventions for SMIv22580 Conformance Statements for SMIv22618 RADIUS Authentication MIB2665 Ethernet-Like Interfaces MIB2674 Extended Bridge MIB2787 VRRP MIB2819 RMON MIB (groups 1, 2, 3, 9)2863 Interfaces MIB3273 RMON High Capacity MIB3410 SNMPv33411 SNMPv3 Management Framework3412 Message Processing and Dispatching forthe Simple Network ManagementProtocol (SNMP)3413 SNMP Applications3414 User-based Security Model (USM) forSNMPv33415 VACM for SNMP3416 SNMPv23417 Transport mappings for SNMP3418 SNMP MIB3434 RMON High Capacity Alarm MIB3584 Coexistance between SNMP v1, v2 andv34022 IP MIB4087 IP Tunnel MIB4113 UDP MIB4133 Entity MIB4292 MIB for IP4293 MIB for IPv6 T extual Conventions4502 RMONv2 (groups 1,2,3,9)5060 PIM MIBANSI/TIA-1057 LLDP-MED MIBDell_ITA.Rev_1_1 MIBdraft-grant-tacacs-02 TACACS+draft-ietf-idr-bgp4-mib-06 BGP MIBv1IEEE 802.1AB LLDP MIBIEEE 802.1AB LLDP DOT1 MIBIEEE 802.1AB LLDP DOT3 MIB sFlowv5 sFlowv5 MIB (version 1.3)DELL-NETWORKING-SMIDELL-NETWORKING-TCDELL-NETWORKING-CHASSIS-MIBDELL-NETWORKING-PRODUCTS-MIBDELL-NETWORKING-SYSTEM-COMPONENT-MIBDELL-NETWORKING-TRAP-EVENT-MIBDELL-NETWORKING-COPY-CONFIG-MIBDELL-NETWORKING-IF-EXTENSION-MIBDELL-NETWORKING-FIB-MIBIT Lifecycle Services for NetworkingExperts, insights and easeOur highly trained experts, withinnovative tools and proven processes, help you transform your IT investments into strategic advantages.Plan & Design Let us analyze yourmultivendor environment and deliver a comprehensive report and action plan to build upon the existing network and improve performance.Deploy & IntegrateGet new wired or wireless network technology installed and configured with ProDeploy. Reduce costs, save time, and get up and running cateEnsure your staff builds the right skills for long-termsuccess. Get certified on Dell EMC Networking technology and learn how to increase performance and optimize infrastructure.Manage & SupportGain access to technical experts and quickly resolve multivendor networking challenges with ProSupport. Spend less time resolving network issues and more time innovating.OptimizeMaximize performance for dynamic IT environments with Dell EMC Optimize. Benefit from in-depth predictive analysis, remote monitoring and a dedicated systems analyst for your network.RetireWe can help you resell or retire excess hardware while meeting local regulatory guidelines and acting in an environmentally responsible way.Learn more at/lifecycleservicesLearn more at /NetworkingDELL-NETWORKING-FPSTATS-MIBDELL-NETWORKING-LINK-AGGREGATION-MIB DELL-NETWORKING-MSTP-MIB DELL-NETWORKING-BGP4-V2-MIB DELL-NETWORKING-ISIS-MIBDELL-NETWORKING-FIPSNOOPING-MIBDELL-NETWORKING-VIRTUAL-LINK-TRUNK-MIB DELL-NETWORKING-DCB-MIBDELL-NETWORKING-OPENFLOW-MIB DELL-NETWORKING-BMP-MIBDELL-NETWORKING-BPSTATS-MIBRegulatory compliance SafetyCUS UL 60950-1, Second Edition CSA 60950-1-03, Second Edition EN 60950-1, Second EditionIEC 60950-1, Second Edition Including All National Deviations and Group Differences EN 60825-1, 1st EditionEN 60825-1 Safety of Laser Products Part 1:Equipment Classification Requirements and User’s GuideEN 60825-2 Safety of Laser Products Part 2: Safety of Optical Fibre Communication Systems FDA Regulation 21 CFR 1040.10 and 1040.11EmissionsInternational: CISPR 22, Class AAustralia/New Zealand: AS/NZS CISPR 22: 2009, Class ACanada: ICES-003:2016 Issue 6, Class AEurope: EN 55022: 2010+AC:2011 / CISPR 22: 2008, Class AJapan: VCCI V-3/2014.04, Class A & V4/2012.04USA: FCC CFR 47 Part 15, Subpart B:2009, Class A RoHSAll S-Series components are EU RoHS compliant.CertificationsJapan: VCCI V3/2009 Class AUSA: FCC CFR 47 Part 15, Subpart B:2009, Class A Available with US Trade Agreements Act (TAA) complianceUSGv6 Host and Router Certified on Dell Networking OS 9.5 and greater IPv6 Ready for both Host and RouterUCR DoD APL (core and distribution ALSAN switch ImmunityEN 300 386 V1.6.1 (2012-09) EMC for Network Equipment\EN 55022, Class AEN 55024: 2010 / CISPR 24: 2010EN 61000-3-2: Harmonic Current Emissions EN 61000-3-3: Voltage Fluctuations and Flicker EN 61000-4-2: ESDEN 61000-4-3: Radiated Immunity EN 61000-4-4: EFT EN 61000-4-5: SurgeEN 61000-4-6: Low Frequency Conducted Immunity。

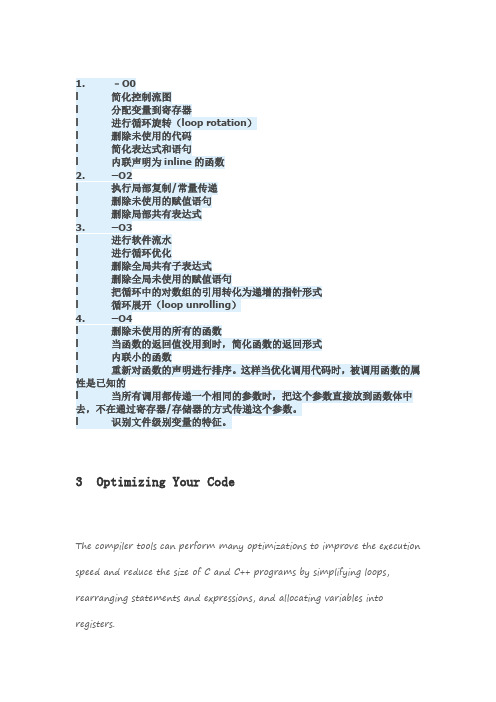

CCS6.2优化选项4级介绍

1. –O0l 简化控制流图l 分配变量到寄存器l 进行循环旋转(loop rotation)l 删除未使用的代码l 简化表达式和语句l 内联声明为inline的函数2. –O2l 执行局部复制/常量传递l 删除未使用的赋值语句l 删除局部共有表达式3. –O3l 进行软件流水l 进行循环优化l 删除全局共有子表达式l 删除全局未使用的赋值语句l 把循环中的对数组的引用转化为递增的指针形式l 循环展开(loop unrolling)4. –O4l 删除未使用的所有的函数l 当函数的返回值没用到时,简化函数的返回形式l 内联小的函数l 重新对函数的声明进行排序。

这样当优化调用代码时,被调用函数的属性是已知的l 当所有调用都传递一个相同的参数时,把这个参数直接放到函数体中去,不在通过寄存器/存储器的方式传递这个参数。

l 识别文件级别变量的特征。

3 Optimizing Your CodeThe compiler tools can perform many optimizations to improve the execution speed and reduce the size of C and C++ programs by simplifying loops, rearranging statements and expressions, and allocating variables into registers.This chapter describes how to invoke different levels of optimization anddescribes which optimizations are performed at each level. This chapter also describes how you can use the Interlist feature when performing optimization and how you can profile or debug optimized code.3.1 Invoking OptimizationThe C/C++ compiler is able to perform various optimizations. High-leveloptimizations are performed in the optimizer and low-level, target-specific optimizations occur in the code generator. Use high-level optimization levels, such as --opt_level=2 and --opt_level=3, to achieve optimal code.The easiest way to invoke optimization is to use the compiler program,specifying the --opt_level=n option on the compiler command line. You can use -O n to alias the --opt_level option. The n denotes the level of optimization (0, 1, 2, 3, and 4), which controls the type and degree of optimization.∙--opt_level=off or -Ooff∙Performs no optimization∙--opt_level=0 or -O0∙Performs control-flow-graph simplification ∙Allocates variables to registers∙Performs loop rotation∙Eliminates unused code∙Simplifies expressions and statements∙Expands calls to functions declared inline ∙--opt_level=1 or -O1Performs all --opt_level=0 (-O0) optimizations, plus:∙Performs local copy/constant propagation ∙Removes unused assignments∙Eliminates local common expressions∙--opt_level=2 or -O2Performs all --opt_level=1 (-O1) optimizations, plus:∙Performs loop optimizations∙Eliminates global common subexpressions∙Eliminates global unused assignments∙Performs loop unrolling∙--opt_level=3 or -O3Performs all --opt_level=2 (-O2) optimizations, plus:∙Removes all functions that are never called∙Simplifies functions with return values that are never used∙Inlines calls to small functions∙Reorders function declarations; the called functions attributes are known when the caller is optimized∙Propagates arguments into function bodies when all calls pass the same value in the same argument position∙Identifies file-level variable characteristicsIf you use --opt_level=3 (-O3), see Section 3.3 and Section 3.4 for more information.∙--opt_level=4 or -O4Performs link-time optimization. See Section 3.6 for details.For information about how the --opt_level option along with the--opt_for_speed option and various pragmas affect inlining, see Section 2.11.By default, debugging is enabled and the default optimization level is unaffected by the generation of debug information. However, the optimization level used is affected by whether or not the command line includes the -g (--symdebug:dwarf) option and the --opt_level option as shown in the following table:Table 3-1 Interaction Between Debugging and Optimization OptionsOptimization no -gno --opt_level--opt_level=off--opt_level--opt_level=2--opt_level=n optimized as specified。

编译原理 技术与工具

作者简介Alfred V.Aho是哥伦比亚大学的Lawrence Gussman计算机科学教授。

Aho教授多次获奖,其中包括哥伦比亚校友会颁发的2003年度Great Teacher奖和电子与电器工程师协会的John von Neumann奖章。

他是美国国家工程院院士,以AACM和IEEE的会员。

编辑推荐经典“龙”书的这一个新版本经过了全面的修订,包含了编译技术中的新进展。

这本书全面地介绍了编译器的设计,并继续强调编译技术在软件和开发中的广泛应用。

本书的前半部分被设计用于本科编译课程,而后半部分可以用于着重于代码优化的研究生课程。

本书简介作为编译器设计的教程,本书重点主要放在解决设计语言翻泽器过程中普遍需要面对的一些问题上,而并不考虑源语言或者目标机器。

本书共 12章。

第一章是一些关于学习动机的资料,同时也给出了一些关于计算机体系结构和程序设计语言原理的背景知识。

第二章开发了一个缩微的编译器,并介绍了很多重要的概念,这些概念将在后面的各个章节中深入介绍。

这个编译器本身在附录中给出。

第三章讨论了词法分析、正则表达式、有穷状态自动机和词法分析器的生成工具,这些内容是各种正文处理的基础。

第四章讨论了主流的语法分析方法,包括自顶向下方法(递归下降法,LL技术)和自底向上方法(LR技术和它的变体)。

第五章介绍了语法制导定义和语法制导翻译的基本思想。

第六章介绍了如何使用第五章中的理论为一个典型的程序设计语言生成中间代码。

第七章讨论了运行时刻环境,主要是运行时刻栈的管理和垃圾收集机制。

第八章介绍了关于目标代码生成的内容,主要讨论了基本块的构造,从表达式和基本块生成代码的方法,以及寄存器分配技术。

第九章介绍了代码优化技术,包括流图、数据流分析框架以及求解这些框架的迭代算法。

第十章讨论了指令级优化。

该章的重点是从小段指令代码中抽取并行性,并在那些可以同时做多件事情的单处理器上调度这些指令。

第十一章讲的是大规模并行的检测和利用。

dashy高级用法

dashy高级用法一、Dashy的基本用法1. Dashy is a really cool tool that I use for organizing my digital stuff. It's like having a super - organized digital drawer where you can put all your important links and apps. For example, I have all my work - related websites in one section of Dashy. It's just so handy! You can easily access your favorite things without having to search through a bunch of bookmarks.2. When I first started using Dashy, I was like, "Wow, this is amazing!" It's so simple to set up. You just add your links and that's it. It's like building your own personal portal to the digital world. I told my friend about it, and he was skeptical at first. "What's so special about it?" he asked. But once he tried it, he was hooked. "This is way better than just using bookmarks," he said with excitement.3. Dashy is great for people who are always on the go. I'm constantly switching between different tasks and apps, and Dashy helps me keep everything in one place. It's like a digitalmand center. For instance, I can quickly open my email, project management tools, and even my social media accounts all from Dashy. It saves me so much time. I feel more in control of my digital life, which is awesome!4. One of the basic things about Dashy is that you can customize it to fit your needs. You can choose the layout, the colors, and even the size of the icons. It's like decorating your own digital workspace. I made mine look really funky with bright colors. My sister saw it and said, "That looks so cool! I want to do mine like that too."5. Using Dashy is not rocket science. It's as easy as pie. All you do is drag and drop your links into the appropriate sections. I showed my mom how to use it, and she was able to set it up in no more than five minutes. She said, "This is really useful. I can now find all my shopping websites easily."6. Dashy can be used on different devices. I have it on my laptop and my phone. It's like having a consistent digital experience everywhere. I was on a bus once and needed to access an important document. I just opened Dashy on my phone and there it was. I thought to myself, "Thank goodness for Dashy!"7. You don't need to be a tech - wizard to use Dashy. Even ifyou're not that good withputers, you can still make it work for you. I have a friend who's not very tech - savvy, but he loves Dashy. He said, "This is the first digital thing that I actually understand how to use."8. The basic functionality of Dashy includes grouping similar links together. It's like sorting your toys into different boxes. For example, I group all my news websites together, all my entertainment sites in another group. It makes it so much easier to find what I'm looking for. My brother asked me, "How do you find things so quickly?" and I showed him how I grouped my links in Dashy.9. Dashy has a search bar too. This is really helpful when you have a lot of links. It's like having a magnifying glass for your digital world. I sometimes forget where I put a particular link, but with the search bar, I can find it in seconds. My colleague was impressed when I showed him this feature. "That's really smart," he said.10. Another basic aspect of Dashy is that it can be password - protected. This gives you an extra layer of security. It's like putting a lock on your digital drawer. I keep some sensitive information in my Dashy, and the password protection makes me feel safe. I told my partner about it, and he said, "That's a great feature. It gives me peace of mind too."二、Dashy的高级用法1. Dashy allows for advanced customization using CSS. This is for those who really want to make their Dashy unique. It's like having a blank canvas and you can paint it however you like. I know a web developer who made his Dashy look like a retro arcade game interface. He said, "With CSS, Dashy can be transformed into something truly extraordinary."2. One advanced use of Dashy is integrating it with other productivity tools. For example, you can connect it with task management apps so that when you click on a project link in Dashy, it automatically shows you the related tasks in the other app. It's like creating a seamless digital ecosystem. My project team was amazed when I set this up. "This is so efficient," they said.3. You can use Dashy's API to automate certain processes. It's like having a digital butler that does things for you. I set up an automation where every time I add a new project link in Dashy, it automatically creates a new folder in my cloud storage with the same name. My boss was really impressed. "This is some next - level stuff," he said.4. Dashy can be used in a multi - user environment. You can share certain sections or the whole Dashy with your colleagues or family members. It's like having a shared digital bulletin board. I shared a section of my Dashy with my workmates where we keep all our team - related resources. One of them said, "This is such a great way to collaborate."5. Advanced users can create custom widgets in Dashy. These can display real - time information like weather updates or stock prices. It's like having a mini - dashboard within Dashy. I made a widget that shows the latest cryptocurrency prices. My friend who's into trading was like, "This is so cool! I can keep an eye on my investments without leaving Dashy."6. Dashy's theming capabilities can be extended further with custom code. It's like taking a basic house and building an entire mansion out of it. I created a dark - mode theme for Dashy with some custom CSS and JavaScript. My sister, who prefers dark - mode on all her apps, said, "This is perfect. I love it!"7. Another advanced feature is the ability to use Dashy for offline access. You can cache certain pages or links so that you can view them even when you don't have an internet connection. It's like having a digital backpack full of useful information. I was on a plane once and was able to read some saved articles from Dashy. I thought, "This is really handy."8. You can use Dashy to manage multiple accounts for the same service. For example, if you have two different email accounts, you can set them up in Dashy and easily switch between them. It's like having a digital keychain for all your accounts. I told my friend who has several social media accounts, and he said, "This will make my life so much easier."9. Dashy can be used to create custom dashboards for different projects or tasks. It's like building a custom control panel for each of your digital adventures. I made a dashboard for my fitness project with links to workout videos, diet plans, and my fitness tracker. My trainer saw it and said, "This is a great way to stay organized and motivated."10. Advanced users can also optimize Dashy's performance. By tweaking some settings and reducing the number of unnecessary elements, you can make it load faster. It's like tuning up a car to make it run smoother. I experimented with some performance optimizations and noticed a significant improvement. I said to myself, "Now that's what I call efficient."三、Dashy的固定搭配1. “Dashy layout” - The layout of Dashy can be customized to suit your preferences. For example, you can choose a grid layout or a list layout. I like the grid layout because it gives a clean and organized look. My friend, on the other hand, prefers the list layout. He said, "It's easier for me to scan through the links."2. “Dashy icon” - You can change the size and style of the Dashy icons. I made my icons really big so that they're easy to click. It's like having big buttons on a control panel. My mom said, "Those big icons are very user - friendly."3. “Dashy section” - Grouping your links into different sections in Dashy makes it more organized. I have a section for work, a section for entertainment, and a section for personal development. It's like having different folders for different types of documents. My sister asked me, "How do you decide which links go in which section?" and I told her it depends on the purpose of the link.4. “Dashy search bar” - The search bar in Dashy is a very useful feature. It helps you find links quickly. It's like having a search engine just for your Dashy. I can't imagine using Dashy without the search bar. My colleague said, "The search bar is a lifesaver when you have a lot of links."5. “Dashy customization” - There are many ways to customize Dashy. You can change the colors, the fonts, and the overall appearance. It's like giving Dashy a makeover. I had so much fun customizing mine. I showed it to my partner and he said, "You've really made it your own."6. “Dashy password protection” - As mentioned before, password protection in Dashy is important for security. It's like a guard at the entrance of your digital space. I always make sure to set a strong password. My dad said, "Good for you for being security - conscious."7. “Dashy API” - For advanced users, the Dashy API opens up a world of possibilities for automation. It's like a key to a hidden treasure chest of functionality. I'm still exploring all the things I can do with the API. I told my tech - geek friend and he said, "The API is where the real power of Dashy lies."8. “Dashy widget” - Creating custom widgets in Dashy can add more functionality. It's like adding extra tools to your digital toolbox. I'm thinking of adding more widgets to my Dashy. My brother said, "Those widgets make Dashy even more interesting."9. “Dashy offline access” - The ability to have offline access in Dashy is really convenient. It's like having a backup plan for when the internet fails. I rely on it when I'm in areas with poor internet connection. My friend who travels a lot said, "This is a must - have feature."10. “Das hy multi - user” - When using Dashy in a multi - user environment, it can enhance collaboration. It's like having a shared workspace for a team. I'm glad that Dashy offers this feature. My workmates and I are using it effectively. One of them said, "This is a great way to work together."。

低功耗 低延时英文

低功耗低延时英文Low Power and Low LatencyIntroduction:In today's highly connected world, there is a growing demand for low power and low latency solutions. The increasing use of smart devices, Internet of Things (IoT) devices, and data centers has driven the need for efficient and fast communication systems. This article will explore the importance of low power and low latency in various industries and discuss the strategies and technologies that can achieve these goals.Low Power:Low power consumption is essential for several reasons. Firstly, it prolongs the battery life of portable devices, such as smartphones and laptops. Users expect their devices to last a whole day without the need for frequent recharging. Secondly, low power consumption reduces energy costs for data centers, which require massive amounts of power to operate. Lastly, it contributes to environmental sustainability by reducing carbon emissions associated with energy production.In order to achieve low power consumption, various techniques can be employed. One common approach is power gating, where unused circuitry is turned off to save power. This is particularly useful in devices with multiple components, such as processors and memory modules. Another technique is voltage scaling, which reduces the power supply voltage to decrease power consumption. Additionally, energy-efficient algorithms and architectures canbe developed to minimize power consumption during data processing and communication.Low Latency:Latency refers to the time delay between the initiation and completion of a task. In the context of communication systems, low latency is crucial for applications that require real-time responsiveness. Industries such as finance, telecommunications, and gaming heavily rely on low latency to ensure smooth and uninterrupted operations.Reducing latency involves optimizing various components of the system. Firstly, reducing the physical distance between devices can significantly decrease latency. By locating servers closer to end-users or deploying edge computing solutions, data transmission time can be greatly reduced. Secondly, efficient protocol design plays a crucial role in reducing latency. For example, the use of lightweight protocols and efficient data compression techniques can reduce the amount of data transmitted, thus decreasing latency. Lastly, hardware and software optimizations, such as parallel processing and efficient algorithms, can further minimize latency in data processing and communication.Applications and Benefits:The importance of low power and low latency spans across multiple industries. In the healthcare sector, for instance, low power consumption is crucial for wearable medical devices that continuously monitor patients' vital signs. These devices need to operate for extended periods without the need for frequent battery replacement. Low latency is equally important intelemedicine applications, where real-time communication between doctors and remote patients is essential for accurate diagnosis and treatment.In the automotive industry, low power and low latency are critical for autonomous vehicles. These vehicles rely on a multitude of sensors and communication systems that must operate with minimal power consumption and ultra-low latency. The ability to quickly process sensor data and make split-second decisions can prevent accidents and ensure passenger safety.Low power and low latency are also fundamental in the field of telecommunications. With the increasing demand for high-speed internet and seamless connectivity, network equipment and infrastructure need to operate with low power consumption and ultra-low latency. This ensures efficient data transmission and improved user experience.Conclusion:Low power and low latency are essential requirements in today's interconnected world. The need for longer battery life, sustainable energy consumption, real-time responsiveness, and efficient communication systems drives the demand for low power and low latency solutions. Through the use of innovative technologies and strategies, such as power gating, voltage scaling, efficient protocol design, and hardware/software optimizations, industries can achieve these goals. By embracing low power and low latency, we can create a more efficient, responsive, and sustainable digital future.。

解决多层级优化问题的方法

解决多层级优化问题的方法Optimizing multi-level problems can be a challenging task that requires strategic thinking and creative solutions. One approach to addressing these complex issues is to break them down into smaller, more manageable components. By systematically analyzing each level of the problem, it becomes possible to identify key areas for improvement and develop targeted strategies for optimization. This method allows for a more focused and structured approach to tackling complex problems, ultimately leading to more effective and sustainable solutions.解决多层次优化问题可能是一项具有挑战性的任务,需要战略思维和创造性解决方案。

应对这些复杂问题的一种方法是将它们拆分为更小、更易管理的组成部分。

通过系统分析问题的每个层次,我们可以确定关键改进领域并制定有针对性的优化策略。

这种方法可以实现更加专注和有条理的方法来应对复杂问题,最终导致更加有效和可持续的解决方案。

In order to effectively optimize multi-level problems, it is important to consider the interconnected nature of the various components. Each level of the problem may impact and be impacted by otherlevels, creating a complex web of relationships that must be carefully navigated. By understanding these interdependencies and interactions, it becomes possible to develop holistic solutions that address the problem from a comprehensive perspective. This holistic approach allows for a more thorough and nuanced understanding of the problem, enabling more effective and sustainable optimization strategies.为了有效地优化多层次问题,重要的是考虑各个组成部分之间的相互关系。

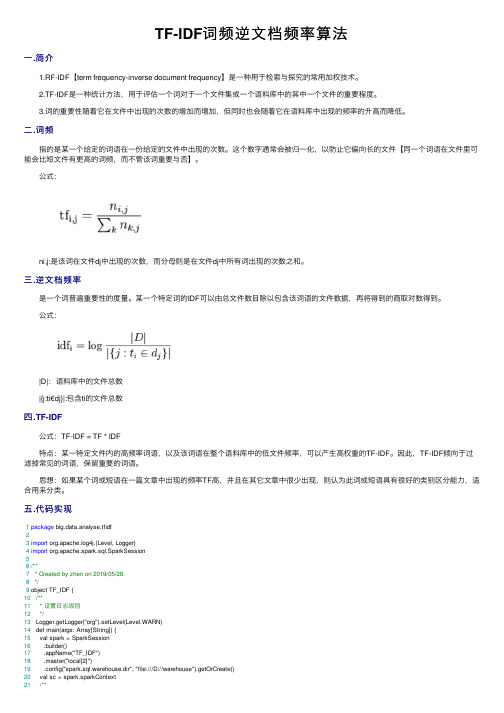

TF-IDF词频逆文档频率算法

TF-IDF词频逆⽂档频率算法⼀.简介 1.RF-IDF【term frequency-inverse document frequency】是⼀种⽤于检索与探究的常⽤加权技术。

2.TF-IDF是⼀种统计⽅法,⽤于评估⼀个词对于⼀个⽂件集或⼀个语料库中的其中⼀个⽂件的重要程度。

3.词的重要性随着它在⽂件中出现的次数的增加⽽增加,但同时也会随着它在语料库中出现的频率的升⾼⽽降低。

⼆.词频 指的是某⼀个给定的词语在⼀份给定的⽂件中出现的次数。

这个数字通常会被归⼀化,以防⽌它偏向长的⽂件【同⼀个词语在⽂件⾥可能会⽐短⽂件有更⾼的词频,⽽不管该词重要与否】。

公式: ni,j:是该词在⽂件dj中出现的次数,⽽分母则是在⽂件dj中所有词出现的次数之和。

三.逆⽂档频率 是⼀个词普遍重要性的度量。

某⼀个特定词的IDF可以由总⽂件数⽬除以包含该词语的⽂件数据,再将得到的商取对数得到。

公式: |D|:语料库中的⽂件总数 |{j:ti€dj}|:包含ti的⽂件总数四.TF-IDF 公式:TF-IDF = TF * IDF 特点:某⼀特定⽂件内的⾼频率词语,以及该词语在整个语料库中的低⽂件频率,可以产⽣⾼权重的TF-IDF。

因此,TF-IDF倾向于过滤掉常见的词语,保留重要的词语。

思想:如果某个词或短语在⼀篇⽂章中出现的频率TF⾼,并且在其它⽂章中很少出现,则认为此词或短语具有很好的类别区分能⼒,适合⽤来分类。

五.代码实现1package big.data.analyse.tfidf23import org.apache.log4j.{Level, Logger}4import org.apache.spark.sql.SparkSession56/**7 * Created by zhen on 2019/05/28.8*/9 object TF_IDF {10/**11 * 设置⽇志级别12*/13 Logger.getLogger("org").setLevel(Level.WARN)14 def main(args: Array[String]) {15 val spark = SparkSession16 .builder()17 .appName("TF_IDF")18 .master("local[2]")19 .config("spark.sql.warehouse.dir", "file:///D://warehouse").getOrCreate()22 * 计算TF23*/24 val tf = sc.textFile("src/big/data/analyse/tfidf/TF.txt")25 .map(row => row.replace(",", " ").replace(".", " ").replace(" ", " ")) // 数据清洗26 .flatMap(row => row.split(" ")) // 拆分27 .map(row => (row, 1.0))28 .reduceByKey(_+_)2930 val tfSize = tf.map(row => row._2).sum() // 计算总词数3132 val tfed = tf.map(row => (row._1, row._2 / tfSize.toDouble)) //求词频33 println("TF:")34 tfed.foreach(println)3536/**37 * 计算IDF38*/39 val idf_0 = tf.map(row => (row._1, 1.0))40 println("加载IDF1⽂件数据。

评价 c开头 -回复

评价c开头-回复C++ Programming Language: A Comprehensive Introduction and Evaluation[Introduction]C++ is a versatile and powerful programming language that has been widely adopted across various industries and domains. This article aims to provide a comprehensive evaluation of C++, exploring its features, applications, strengths, and weaknesses. Whether you are a novice programmer or an experienced developer, this evaluation will help you understand the language's capabilities and determine if it suits your needs.[Background and History]C++ was developed in the early 1980s by Bjarne Stroustrup at Bell Labs. It is an extension of the C programming language and was designed to bring object-oriented programming (OOP) concepts to the existing C language. C++ combines the low-level system access and performance of C with high-level features such as classes, objects, and inheritance, making it a widely used language forsystems programming, game development, and mobile applications.[Features and Syntax]One of the key features of C++ is its support for OOP. The language allows programmers to organize their code into classes, which encapsulate data and methods. This provides modularity and reusability, making it easier to manage large-scale projects. C++ also supports features like inheritance, polymorphism, and templates, allowing for the creation of highly flexible and extensible code.In addition to OOP, C++ supports procedural programming, allowing developers to write efficient and concise code. Its syntax is similar to C, with some added features like namespaces and exception handling. The language supports strong typing and requires explicit declaration of variables and function types, promoting code clarity and reducing the likelihood of errors.[Applications]C++ finds extensive use in a wide range of applications. It is particularly popular in systems programming, where performance and direct hardware access are essential. Operating systems like Windows and Linux are built using C++, as it allows developers to interact with hardware components like memory, input/output devices, and network interfaces.Game development is another domain where C++ excels. Its ability to handle complex algorithms, graphics rendering, and physics simulations makes it a reliable choice for creatinghigh-performance games. Popular game engines like Unreal Engine and Unity rely heavily on C++ for their core functionality.Beyond systems programming and game development, C++ is also widely used in embedded systems, scientific research, and financial analysis. Its speed, memory management, and extensive libraries make it invaluable for applications requiring performance optimization and numerical calculations.[Strengths]One of the significant strengths of C++ is its performance. Thelanguage provides low-level access to memory and hardware, allowing developers to write efficient and close-to-the-metal code. C++ programs can achieve similar performance to those written in languages like C and assembly language, making it a popular choice for resource-intensive applications.C++ is highly portable, with compilers and libraries available for various platforms. This portability enables developers to write code once and run it on multiple operating systems and architectures, saving time and effort in cross-platform development.Another strength of C++ is its extensive library support. The Standard Template Library (STL) provides a collection of data structures and algorithms, making common tasks like sorting, searching, and manipulating collections straightforward and efficient. Additionally, third-party libraries like Boost further enhance the language's capabilities, offering features like networking, GUI programming, and cryptography.C++ fosters code reuse and maintainability through its support for OOP principles. The ability to define classes, encapsulate data and functions, and create hierarchies through inheritance significantlyimproves the readability and maintainability of code. By building on existing classes, developers can save time and effort when creating new projects or modifying existing ones.[Weaknesses]While C++ offers many advantages, it also has its share of weaknesses. The language's complexity can be overwhelming, especially for beginners. C++ requires a deep understanding of memory management, pointers, and other low-level concepts, which can be challenging for programmers without prior experience.C++ code can be verbose and prone to errors. The language's strict typing requires explicit type declarations in many cases, leading to longer code lines and increased chances of typing mistakes. Additionally, C++ lacks built-in garbage collection, making manual memory management a necessity. Improper memory deallocation can lead to memory leaks or segmentation faults, adding complexity and responsibility to the developer.Another weakness of C++ is its steep learning curve. With its manyfeatures and intricate syntax, mastering C++ requires time, dedication, and continuous learning. Beginners may struggle to grasp certain concepts, which can hinder their progress and productivity.[Conclusion]C++ is a powerful and versatile programming language with a rich history and widespread adoption. Its support for OOP, performance optimizations, extensive libraries, and cross-platform capabilities make it an excellent choice for many applications. However, its complexity, lack of built-in garbage collection, and steep learning curve may pose challenges for beginners or those seeking a more straightforward language alternative.Ultimately, the choice to use C++ depends on the specific project's requirements and the developer's familiarity with the language. With dedication and perseverance, mastering C++ can unlock a wide range of opportunities and enable the creation of efficient, high-performance software solutions.。

智慧系统英文缩写建设方案

智慧系统英文缩写建 设方案

汇报人:XX

2024-01-28

REPORTING

• Overview and Background of Smart 目 录

Systems • English abbreviation strategy

development • Technical architecture design and

Promotion strategy planning

• Develop a promotional plan: Develop a detailed promotional plan for the target audience, including promotional channels, timeline, promotional content, etc.

After the project is completed, it will form an efficient, intelligent, and adaptive smart system that can meet the intelligent needs of customers in various fields. At the same time, the implementation of the project will drive the development of related industries and promote sustainable economic and social development.

Evaluation and testing

Evaluate and test the remaining candidate abbreviations, including semantic accuracy, memory difficulty, and fit with the target audience.

raptor

raptorRaptor: An Overview of a Powerful Portable Library for Compiler ConstructionIntroductionThe field of compiler construction has always been crucial in computer science. It involves converting high-level programming languages into machine code that computers can execute. This complex process requires robust tools to facilitate the development of compilers efficiently. One such tool that has gained popularity over the years is Raptor. In this document, we will explore the features, benefits, and usage of Raptor, a powerful portable library for compiler construction.1. Raptor: What Is It?Raptor is an open-source library designed to provide a comprehensive set of tools and utilities for compiler construction. It is written in C++ and utilizes modern programming paradigms to simplify the process of building compilers. Raptor aims to be portable, efficient, and easy to integrate into various development environments.2. Key Features2.1 Lexical AnalysisRaptor provides a robust lexical analysis library that enables efficient tokenization of source code. It supports regular-expression based pattern matching and allows users to define their own token types and associated actions. With Raptor's lexical analysis capabilities, developers can easily implement scanners to extract tokens from source code efficiently.2.2 ParsingRaptor incorporates a powerful parsing mechanism that eases the process of constructing parsers. It supports both top-down and bottom-up parsing techniques, allowing developers to choose the approach that best fits their requirements. Raptor's parsing library also offers extensive error recovery mechanisms and supports the automatic generation of parsers from grammar specifications.2.3 Abstract Syntax Trees (ASTs)Managing Abstract Syntax Trees is a crucial part of compiler construction. Raptor provides utilities for creating and manipulating ASTs effortlessly. It supports the construction, traversal, and transformation of ASTs in a user-friendly manner. With Raptor, developers can focus more on buildingcompiler logic rather than spending excessive time on managing the data structure of ASTs.2.4 Intermediate Representation (IR)Raptor incorporates a flexible intermediate representation library that simplifies the transformation and optimization phases of compilers. It allows developers to design and manipulate IR trees efficiently, facilitating the optimization of generated machine code. Raptor's IR library supports a range of optimizations like dead code elimination, constant propagation, and loop unrolling.2.5 Code GenerationGenerating efficient code is one of the primary goals of any compiler. Raptor offers an intuitive code generation library that enables developers to emit machine code for various target architectures. It supports the generation of assembly code, binary code, or even high-level intermediate representations. Raptor's code generation library provides an abstraction layer that makes the process more straightforward and less error-prone.3. Benefits of Using Raptor3.1 PortabilityRaptor is designed to be highly portable, enabling developers to use it across different operating systems and platforms. Its dependency on widely-supported programming languages like C++ makes it easy to integrate with existing codebases. With Raptor, developers can focus on building compilers without worrying about platform-specific issues.3.2 EfficiencyRaptor is engineered to be highly efficient in terms of both runtime performance and memory usage. It utilizes advanced data structures and algorithms to ensure optimal execution speed while minimizing resource consumption. The efficient design of Raptor enables faster development and enhances the performance of the generated compilers.3.3 ExtensibilityThe modular architecture of Raptor makes it an extensible library. Developers can build upon the existing functionality by integrating their custom modules seamlessly. Raptor's extensibility empowers developers to tailor the library according to their project-specific requirements without breaking the core functionality.4. Getting Started with RaptorTo start utilizing Raptor in your compiler construction projects, you can download the library from the official website (provide link here). The website also provides comprehensive documentation, including tutorials and examples, to help developers understand the library's internals. Additionally, the GitHub repository of Raptor enables developers to contribute to the project and participate in discussions.ConclusionRaptor proves to be a powerful portable library that simplifies the process of compiler construction. Its comprehensive setof features, such as lexical analysis, parsing, AST management, intermediate representation, and code generation, make it a valuable tool for developers. With Raptor's focus on portability, efficiency, and extensibility, it is undoubtedly a reliable choice for building compilers. So, if you are embarking on a compiler construction project, consider leveraging the capabilities of Raptor to enhance your development process.。

英语作文-如何在集成电路设计中实现低功耗与高性能

英语作文-如何在集成电路设计中实现低功耗与高性能In the field of integrated circuit (IC) design, achieving low power consumption and high performance is a critical and challenging task. With the increasing demand for portable and energy-efficient electronic devices, the importance of low-power and high-performance IC design has become more prominent than ever. In this article, we will explore the various techniques and methodologies that can be employed to achieve low power consumption and high performance in IC design.One of the key considerations in low-power IC design is the optimization of power consumption at both the architectural and circuit levels. At the architectural level, power gating, clock gating, and voltage scaling techniques can be utilized to reduce power consumption during idle or low activity periods. Additionally, the use of power-efficient architectures such as asynchronous circuits and near-threshold computing can further contribute to lowering power consumption in IC designs.Furthermore, at the circuit level, the use of advanced power management techniques such as dynamic voltage and frequency scaling (DVFS), power gating, and body-biasing can help to minimize power consumption while maintaining high performance. Additionally, the adoption of advanced low-power design methodologies such as multi-Vt (threshold voltage) and multi-Vdd (supply voltage) design, as well as the use of advanced low-power design libraries and standard cells, can significantly contribute to reducing power consumption in IC designs.In addition to low-power considerations, achieving high performance in IC design involves optimizing circuit speed, area, and power. To achieve high performance, it is essential to carefully consider the trade-offs between power, performance, and area in the design process. This involves the use of advanced optimization techniques such as timing-driven synthesis, clock tree synthesis, and placement and routing optimizations to maximize circuit performance while minimizing power consumption and area.Moreover, the use of advanced circuit design techniques such as pipelining, parallelism, and speculative execution can further enhance the performance of IC designs. Additionally, the incorporation of advanced process technologies such as FinFET and advanced packaging technologies such as 2.5D and 3D integration can also contribute to achieving high performance in IC designs.Furthermore, the adoption of advanced design-for-test (DFT) and design-for-reliability (DFR) techniques can help to ensure the robustness and reliability of IC designs while maintaining high performance. This involves the use of advanced test compression, built-in self-test (BIST), and design-for-aging methodologies to ensure the reliability and longevity of IC designs.In conclusion, achieving low power consumption and high performance in IC design requires a comprehensive and systematic approach that encompasses both architectural and circuit-level optimizations. By leveraging advanced low-power design techniques, power management methodologies, and high-performance design strategies, it is possible to develop IC designs that meet the increasing demand for energy-efficient and high-performance electronic devices. As technology continues to advance, the importance of low-power and high-performance IC design will only continue to grow, making it essential for designers to stay abreast of the latest advancements and methodologies in this field.。

Accelerated Degradation Tests Modeling and Analysis

September 20, 1999

Abstract

High reliability systems generally require individual system components having extremely high reliability over long periods of time. Short product development times require reliability tests to be conducted with severe time constraints. Frequently few or no failures occur during such tests, even with acceleration. Thus, it is di cult to assess reliability with traditional life tests that record only failure times. For some components, degradation measures can be taken over time. A relationship between component failure and amount of degradation makes it possible to use degradation models and data to make inferences and predictions about a failure-time distribution.

1.2 Accelerated degradation data

In some reliability studies, it is possible to measure degradation directly over time, either continuously or at speci c points in time. In most reliability testing applications, degradation data, if available, can have important practical advantages:

high level 含义 概要

在深入探讨“high level”这一主题之前,让我们先来了解一下这个词的含义和概要。

所谓“high level”,通常用来描述一种较为抽象和综合的概念或者视角。

它可以指代高层次的抽象思维,高水平的总体规划,以及广阔的视野和全局性的观察。

在不同的领域和语境下,“high level”都具有着不同的内涵和应用。

从技术领域来看,“high level”通常用来形容一种抽象程度较高的概念或者编程语言。

在软件开发领域,高级编程语言相对于低级编程语言来说更加抽象和易读,能够更快速地实现目标。

在另一个例子中,高级架构设计则是指整体系统设计的规划和构想,而不是具体的技术实现细节。

“high level”在技术领域中往往与抽象、总体规划相关联。

除了技术领域,“high level”在商业、管理、学术、艺术等领域中也有着广泛的应用。

在商业管理中,“high level”决策是指与战略性规划和全局发展方向相关的决策,而非日常运营中的具体细节。

在学术研究中,“high level”思维往往能够帮助研究人员发现问题的本质,并提出更具有整体性和前瞻性的见解。

在艺术创作中,“high level”作品往往能够触及人们内心深处,传达出更高层次的思想和情感。

“high level”不仅仅是一种抽象的概念,更是一种综合性的视角和思维方式。

从“high level”角度出发,我们能够更好地把握事物的本质、规划未来的发展方向,以及洞察事物背后的深层次联系。

学会运用“high level”思维,对于提高我们的综合分析能力、思维深度和全局观念至关重要。

结合以上的探讨,个人认为,“high level”不仅是一种抽象的概念,更是一种对事物的全面观察和思考方式。

通过“high level”思维,我们能够站在更宏观的角度看待问题,理解事物的本质和内在联系。

在日常生活和工作中,我们应该努力培养和运用“high level”思维,提升自己的综合分析能力和解决问题的水平。

high low的技术指标 -回复

high low的技术指标-回复High-low技术指标,也被称为Price Range指标或者High-low带宽指标,是一种用于描绘市场波动性的技术指标。

它通过计算最高价和最低价之间的差异来衡量市场的价格波动幅度。

High-low指标可以帮助交易者识别趋势的强度和市场的波动性,从而在交易决策中提供有价值的信息。

在本文中,我们将逐步解释High-low技术指标以及它的应用方式。

我们将深入探讨High-low指标的计算方法、如何使用High-low指标进行交易决策以及该指标的优缺点。

一、High-low指标的计算High-low指标的计算相对简单,它只需计算最高价和最低价之间的差异即可。

具体计算方法如下:1. 计算每个交易周期(如日、周或月)的最高价和最低价之间的差异。

这将得到每个交易周期的价格范围。

2. 将每个交易周期的价格范围进行加总,得到一段时间(如一段时间内的所有交易周期)的总价格范围。

3. 如果需要,可以将总价格范围进行平滑处理,以减少噪音和波动性。

计算High-low指标的过程中,我们可以选择不同的时间周期进行计算。

较短的时间周期可以提供更敏感的指标,而较长的时间周期则可以提供更平滑的指标。

二、High-low指标的应用High-low指标可以用于以下几个方面:1. 趋势识别:通过观察High-low指标的数值,交易者可以得知市场的趋势强弱。

较高的High-low指标数值意味着市场的波动性较大,可能是处于一个明显的上涨或下跌趋势中。

相反,较低的High-low指标数值表明市场较为平稳,可能是在一个盘整或调整阶段。

交易者可以根据High-low指标的数值来调整其交易策略,如选择更适合高波动性市场的短线交易或者适合低波动性市场的趋势跟踪。

2. 市场波动性预测:High-low指标可以作为预测市场波动性的工具。

较大的High-low指标数值意味着市场当前的波动性较大,可能会继续保持高波动性。

high low的技术指标 -回复

high low的技术指标-回复High-Low 的技术指标,也被称为最高最低指标,是一种用于确定证券价格波动性的技术分析工具。

该指标通过计算一段时间内的最高价和最低价之差,来衡量市场的波动程度。

在这篇文章中,我们将一步一步回答关于High-Low 技术指标的问题,包括它的计算方法、如何使用和解读指标的含义。

第一步:计算High-Low 技术指标High-Low 技术指标的计算非常简单,只需要确定一个特定的时间范围,然后计算这个时间范围内的最高价和最低价之差。

例如,我们选择一个10个交易日的时间范围,那么High-Low 技术指标的计算公式如下:High-Low = 最高价- 最低价这个计算公式将得到一个数值,用于衡量市场在特定时间范围内的波动情况。

第二步:使用High-Low 技术指标High-Low 技术指标可以用于判断市场的波动程度和价格变动的强度。

当市场波动较大时,High-Low 数值较大;当市场波动较小时,High-Low 数值较小。

因此,High-Low 技术指标可以帮助我们判断市场的行情。

以下是一些使用High-Low 指标的方法:1. 波动性策略:当High-Low 数值较大时,市场波动较大,适合使用波动性策略进行交易。

例如,通过购买期权、期货或其他杠杆产品来获得市场波动的利润。

2. 突破策略:当High-Low 数值突破某个特定的阈值时,可以认为市场进入了一个新的趋势阶段,可以采取相应的投资策略。

例如,当High-Low 数值突破历史最高值时,可能意味着市场即将上涨。

3. 高低价差策略:当High-Low 数值较大时,可以认为市场的高低价差较大,适合采取高抛低吸的策略。

例如,当High-Low 数值较大时,可以在市场高点卖出,然后在市场低点买入。

第三步:解读High-Low 技术指标的含义High-Low 技术指标的数值范围可以用来判断市场的价格波动情况。

当High-Low 数值较小时,表示市场波动较小,价格变动趋于平稳;当High-Low 数值较大时,表示市场波动较大,价格变动较为剧烈。

Reliable I/O on the Grid

Research Problems

Virtual Memory • A K-node has one input, one output, and a memory/disk buffer. How should we move data to maximize throughput?

APP BYPASS

Execution Site Storage Site

Reads

FILE SYSTEM

KANGAROO AGENT

K SERVER

SPOOL DIR

K MOVER

Writes

K SERVER

Microbenchmark: File Transfer

Create a large output file at the execution site, and send it to a storage site.

FILE SYSTEM

Existing storage system: NFS, AFS, GASS, etc.

BYPASS

GC AGENT

RPC on TCP

GC

Globus Auth SHADOW

SPOOL DIR

Observations on the Grid Console

Interfaces well with existing systems: • Applied to vanilla Condor(G) jobs. • Works on any dynamically-linked program.

Reliable I/O on the Grid

Douglas Thain and Miron Livny Condor Project

新型一次性生物反应器

The Next-Generation Single-Use BioreactorThe Source of Bioprocess Efficiency™F l e x i b l e , F a s t , E f f e c t i v e ,OverviewThe Nucleo™ single-use bioreactor is the next generation single-use bioreactor developed to provide an efficient complete turnkey solution to the evolving needs of the cell culture industry. Its innovative cube-shaped bag design incorporates a highly efficient mixing pad-dle coupled with a dynamic sparger that enables the Nucleo bioreactor to achieve greater productivity compared to cylindrical bioreactors.The corners of the cube-shaped vessel act as baffles to prevent vortexing and ensure robust mixing with very low shear stress. In addition to superior mixing capabilities, the mixing paddle incorporates a dynamic sparger that provides better gas transfer with high K L .a. and lower gas volumes. These features make the Nucleo bioreactor the best biomanufactur-ing solution for both suspension cells and adherent cells on microcarriers. In addition to routine GMP campaigns, computational fluid dynamics simulations have been performed to characterize and explain the results of this unique design and its impact on cell culture productivity.The reactor vessel, paddle and fittings are single-use components and all contact surfaces are discarded after use. As with all ATMI LifeSciences single-use systems, the Nucleo sys-tem vessels are made from Integrity™ TK8 bioprocess film. The product-contacting layer of TK8 film is blow-extruded in-house by ATMI under cleanroom conditions using medical-grade, ultra-low-density polyethylene resin. It is then laminated to create a gas barrier film of exceptional cleanliness, strength and clarity that is animal-derived component-free (ADCF) and complies fully with USP Class VI requirements. The paddle is enclosed in a medical- grade ULDPE sleeve made from the same contact material as the bag itself, and is coupled on top of the vessel with the external and non-shedding mechanical mixing head.The Nucleo system integrated Software Suite offers a comprehensive set of functionalities dedicated to fermentation and cell cultivation applications, including profile, calculation and strategy modules and complies with Pharmaceutical Regulations, in particular GAMP V5 and 21 CFR PART 11. The aim of the Nucleo Software Suite is to provide the customer with the benefits of standard software while providing the user with the highest flexibility through a wide range of available options.The Nucleo bioreactor platform is the result of the combined expertise of Pierre Guerin– Biolafitte (bioreactors and process control systems) and ATMI LifeSciences (ultra-pure bioprocess films, disposable mixing technology and cell culture process optimizations).• Compatible with batch, fed-batch and perfusion processes• Single-use bag technology- Integrity™ TK8 film with validation package - All contact surfaces of same ATMI medical- grade ULDPE material - No need for CIP/SIP- Avoid all cross contamination risksHighlights & Benefits• Cube-shaped design incorporating a mixing paddle with a dynamic sparger device - Superior mixing capabilities with drastically reduced shear stress - Superior oxygenation and high K L .a. with minimum gas volume • Vessel suitable for low and high working volumes (process flexibility)• Scalable up to 1,000L• Customizable system (modular or fully integrated configuration)• Cultivation of suspended cells and adherent cells on microcarriers at very high densities • User friendly process control system ensuring optimal culture conditions - Control of all process parameters- Fully compliant to GAMP V5 and 21 CFR PART 11- High quality documentation package supporting IQ/OQ - Available with traditional or single-use DO and pH probesATMI-patented mixing paddle coupled with a dynamic sparging device.The fully-integrated 1200 liter Nucleo bioreactor with cube-shaped geometry.E f f i c i e n t S ol u t i o n sBag and Container• Available vessel sizes: 25, 50, 250, 600 and 1200 liters with cube-shaped geometry • Film material: multi-layer film with contact layer in ULDPE, gamma sterilizable, USP - Class VI compliant, fully ADCF (Animal Derived Component Free)• Temperature control via jacketed container and thermostatic bath as an optionMixing System• Mixing system equipped with patented ATMI paddle• Adjustable speed: 20-110 RPMQualification and Validation• FAT/SAT ProtocolsCodeN50–25N50–50N1000–250N1000–600N1000–1200Total/Working Volume25/20L 50/40L 250/200L 600/500L 1200/1000LNucleo Selection GuideThe Nucleo single-use bioreactor offers a complete turn-key solution to cell cuture applications.Aeration• Dual gas inlet including oxygen supply via micro-sparger or optional macro-sparger and air/CO 2 supplies to the head space, both with rotameter and solenoid valve or optional mass flow meters• 0.2μm absolute filters on gas inlet and outlet • Gas outlet line fitted with foam trap set• Optional N 2 supply to the sparger with rotameter and solenoid valve or mass flow meter, additional air supply to the sparger with rotameter and solenoid valve or mass flow meter, CO 2 supply to the sparger instead of the head placeAccessories and Product Lines• Up to four fixed speed peristaltic pumps (two included in the basic configuration) and two external variable speed peristaltic pumps for fed-batch and perfusion applications • Three to six ports for probes and sensors• 14 multi-purpose ports for inoculation, nutrients, reagent additions, sampling, etc.• Easy drain: flush bottom harvest valve• Additive and sampling bags with holders as optionInstrumentation and Control System• Digital Control System with embedded touch screen operator panel (OP), SIEMENS controller and NEPTUNE OP-WinCC software• Up to 16 highly flexible control loops for all process parameters: temperature, speed, pH, pO 2, optional gas flow rates, weight and optical density• Control types include PID, digital on/off and others, cascade mode• Optional PC working station with the NEPTUNE SCADA-iFix or Intouch software for remote control and supervision of up to eight Nucleo bioreactorsNeptune ™ SCADA Software“Standard” Version: OP-WinCC software• Process control via synoptic views • Alarm management • Controller profiles for dynamic set points • Management of user’s access complying with 21 CFR PART 11“Advanced and Expert” Versions (Optional SCADA software)• Calculation module allowing user to define additional calculations and apply control based on these calculations• Strategy module for process strategy optimizationNeptune SCADA Software• Monitoring of controller set points and alarms• Data logging and trends with file export/importSystem DimensionsATMI, 10851 Louisiana Avenue South, Bloomington , MN 55438 USA, 800.966.6698 or 952.942.0855 • ATMI, Reugelstraat 2, 3320 Hoegaarden, Belgium, +32.16.76.80.70 •**************************© 2010, 2011 ATMI, Inc. All rights reserved. ATMI, the ATMI logo and Integrity are trademarks or registered trademarks of Advanced Technology Materials, Inc. in the U.S., other countries, or both. Nucleo is a trademark of Advanced Technology Materials, Inc and of Pierre Guerin in the United States, other countries or both. Neptune is a trademark of Pierre Guerin-Biolafitte.Data Sheet BD003EPG 1107rev1ATMI LifeSciencesThe Source of Bioprocess Efficiency ™Formoreinformation,pleasecontactusat:**************************,***********************。

IAR配置

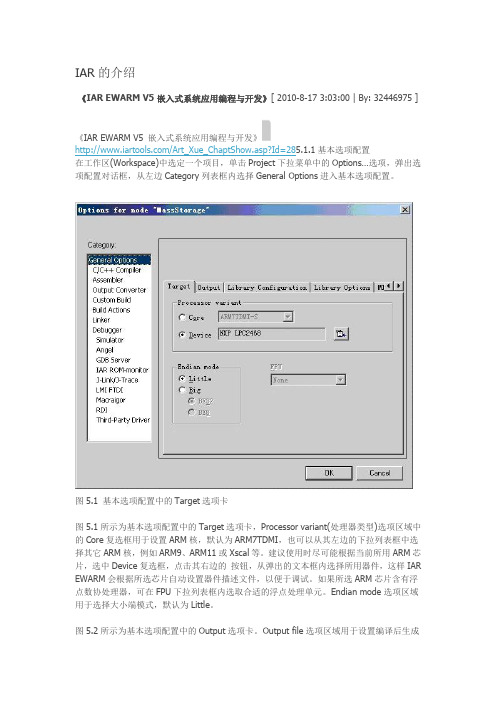

IAR的介绍《IAR EWARM V5 嵌入式系统应用编程与开发》[ 2010-8-17 3:03:00 | By: 32446975 ]《IAR EWARM V5 嵌入式系统应用编程与开发》/Art_Xue_ChaptShow.asp?Id=285.1.1基本选项配置在工作区(Workspace)中选定一个项目,单击Project下拉菜单中的Options…选项,弹出选项配置对话框,从左边Category列表框内选择General Options进入基本选项配置。

图5.1 基本选项配置中的Target选项卡图5.1所示为基本选项配置中的Target选项卡,Processor variant(处理器类型)选项区域中的Core复选框用于设置ARM核,默认为ARM7TDMI,也可以从其左边的下拉列表框中选择其它ARM核,例如ARM9、ARM11或Xscal等。

建议使用时尽可能根据当前所用ARM芯片,选中Device复选框,点击其右边的按钮,从弹出的文本框内选择所用器件,这样IAR EWARM会根据所选芯片自动设置器件描述文件,以便于调试。

如果所选ARM芯片含有浮点数协处理器,可在FPU下拉列表框内选取合适的浮点处理单元。

Endian mode选项区域用于选择大小端模式,默认为Little。

图5.2所示为基本选项配置中的Output选项卡。

Output file选项区域用于设置编译后生成的输出文件类型,可选择Executable(生成执行代码)或Library(生成库文件)。

Output directories选项区域用于设置输出文件目录,默认执行代码文件目录为Debug\Exe,目标文件目录为Debug\Obj,列表文件目录为Debug\List,也可设置其它目录。

图5.2基本选项配置中的Output选项卡图5.3基本选项配置中的Library Configuration选项卡图5.3所示为基本选项配置中的Library Configuration选项卡。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

High-Level Optimizations for Low-Level Software John Regehr—School of Computing,University of UtahEmbedded software needs to meet stringent requirements such as high reliability,minimal use of resources,and short development time.The problem is that these requirements are not only individually difficult,but are also in tension.We are working on VIPA(vertically integrated program analy-sis),a partial solution to this problem.VIPA is a new frame-work that supports high-level optimizations and analyses that are more aggressive and more domain specific than those tra-ditionally performed by compilers.Its distinguishing fea-tures are:Integration of tools operating at multiple levels of ab-straction:the model level,source code level,and binary level.Extraction of as much information as possible from each tool,as opposed to the common practice of using program analyses separately to produce binary results,e.g.,“the network acceptor thread has the potential forstack overflow.”For example,in previous work[1]we not only demon-strated how to show stack safety of embedded software,but also how to use the call chain to the worst-case stack depth as input to a whole-program inliner.The stack tool operates on binaries while the inliner works on source code.This in-tegrated analysis and optimization reduced the overall stack consumption of a number of embedded systems,on average, by32%when compared to a smart inlining policy whose goal was to improve performance without causing code bloat.We are working on more sophisticated feedback loops,such as one that integrates stack depth bounding with an optimiza-tion that maps a number of logically concurrent activities onto a smaller number of OS-supported threads.Eliminating the potential for preemption will make it possible to elim-inate some locks,further reducing computations’memory and CPU requirements.A number of factors motivate VIPA.First,since information is both gained and lost at each level of abstraction in a system,analysis at multiple levels is necessary.For example,accurate estimates of worst-case execution time can only be determined by looking at a bi-nary program;exceptions and concurrency are best analyzed at the source level;and,real-time deadlines and mutually ex-clusive modes are only apparent at the model level.Second,each embedded system has its own set of goals,with different prioritizations among energy usage,develop-ment time,reliability,footprint,etc.By connecting a number of independent tools,and by not forcing developers into any particular design methodology,VIPA will support highly di-verse combinations of goals.Third,thefield of program analysis is rapidly advancing, and tools forfinding race conditions,deadlocks,protocol errors,worst-case execution times,worst-case memory us-age,etc.are becoming ever more useful.There is a large and growing asymmetry between the resources available on a typical workstation and the resources on a typical embed-ded system—this asymmetry can be exploited in order to perform advanced analyses and optimizations.This research faces a number of challenges.First,how will the tools interact with each other?We are developing several exchange formats for program analysis results;one is centered around the callgraphs for a system,another around its concurrency structure:what are the concurrent activities and how do they interact?A number of existing analysis and optimization tools developed at Utah and elsewhere will be adapted to use these exchange formats.Second,what are the most useful feedback loops between analysis and optimiza-tion tools,and in what circumstances is each loop useful? We have already designed and tested a feedback loop that reduces stack memory consumption,and we hope to test a number of other loops in the near future.Third,can users be presented with coherent error messages,at the right level of abstraction,in the presence of a number of interacting analy-sis tools?We believe this to be an important challenge but have not yet made much progress towards solving it.Of course,machines often have trouble answering“why”ques-tions because they usually do not keep track of the reasons that previous decisions were made,and because the correct answer can depend on the frame of mind of a human.We believe that these challenges can be surmounted.If so,VIPA will help developers create systems at higher levels of abstraction,since fewer optimizations and customizations will have to be performed manually.References[1]J.Regehr,A.Reid,and K.Webb.Eliminating stack overflowby abstract interpretation.In Proc.of the3rd InternationalConf.on Embedded Software(EMSOFT),Philadelphia,PA,Oct.2003.。