利用FPGA实现与TS201的LinkPort高速数据互联

FPGA与DSP的高速通信接口设计与实现

FPGA与DSP的高速通信接口设计与实现1 TS101和TS201的链路口分析与比较TS101和TS210都是高性能的浮点处理芯片,目前两者都广泛应用于复杂的信号处理领域。

TS201是继TS101之后推出的新型芯片,核时钟最高可达600MHz,其各类性能也相对优于TS101,而且TS201的链路口采用了低压差分信号LVDS技术,功耗更低、抗噪声性能更好。

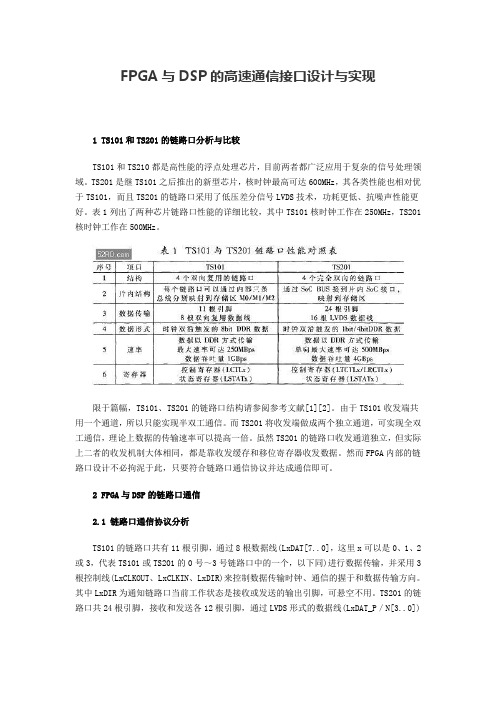

表1列出了两种芯片链路口性能的详细比较,其中TS101核时钟工作在250MHz,TS201核时钟工作在500MHz。

限于篇幅,TS101、TS201的链路口结构请参阅参考文献[1][2]。

由于TS101收发端共用一个通道,所以只能实现半双工通信。

而TS201将收发端做成两个独立通道,可实现全双工通信,理论上数据的传输速率可以提高一倍。

虽然TS201的链路口收发通道独立,但实际上二者的收发机制大体相同,都是靠收发缓存和移位寄存器收发数据。

然而FPGA内部的链路口设计不必拘泥于此,只要符合链路口通信协议并达成通信即可。

2 FPGA与DSP的链路口通信2.1 链路口通信协议分析TS101的链路口共有11根引脚,通过8根数据线(LxDAT[7..0],这里x可以是0、1、2或3,代表TS101或TS201的0号~3号链路口中的一个,以下同)进行数据传输,并采用3根控制线(LxCLKOUT、LxCLKIN、LxDIR)来控制数据传输时钟、通信的握于和数据传输方向。

其中LxDIR为通知链路口当前工作状态是接收或发送的输出引脚,可悬空不用。

TS201的链路口共24根引脚,接收和发送各12根引脚,通过LVDS形式的数据线(LxDAT_P/N[3..0])和时钟线(LxCLK_P/N)进行数据传输,并采用LxACK和LxBCMP#(‘#’代表信号低有效)来通知接收准备好和数据块传输结束。

采用FPGA与DSP通过链路口通信的关键是令双方通信的握手信号达成协议,促使数据传输的进行。

基于TS201图像处理平台的链路口通信方法

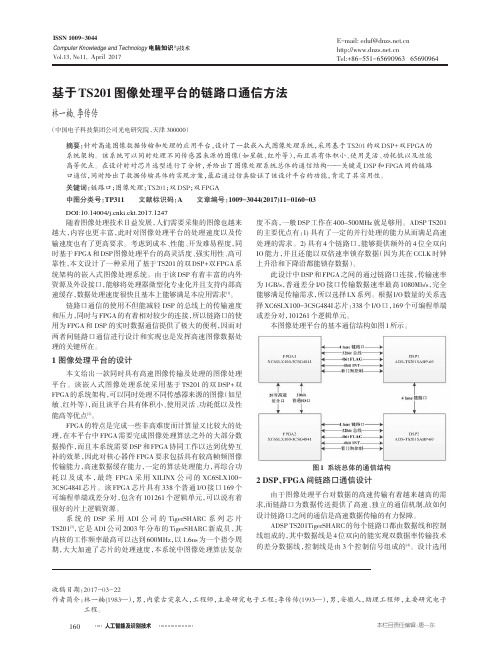

基于TS201图像处理平台的链路口通信方法林一楠,李传传(中国电子科技集团公司光电研究院,天津300000)摘要:针对高速图像数据传输和处理的应用平台,设计了一款嵌入式图像处理系统,采用基于TS201的双DSP+双FPGA 的系统架构。

该系统可以同时处理不同传感器来源的图像(如星敏、红外等),而且具有体积小、使用灵活、功耗低以及性能高等优点。

在设计时对芯片选型进行了分析,并给出了图像处理系统总体的通信结构——关键是DSP 和FPGA 间的链路口通信,同时给出了数据传输具体的实现方案,最后通过仿真验证了该设计平台的功能,肯定了其实用性。

关键词:链路口;图像处理;TS201;双DSP ;双FPGA 中图分类号:TP311文献标识码:A文章编号:1009-3044(2017)11-0160-03随着图像处理技术日益发展,人们需要采集的图像也越来越大,内容也更丰富,此时对图像处理平台的处理速度以及传输速度也有了更高要求。

考虑到成本、性能、开发难易程度,同时基于FPGA 和DSP 图像处理平台的高灵活度、强实用性、高可靠性,本文设计了一种采用了基于TS201的双DSP+双FPGA 系统架构的嵌入式图像处理系统。

由于该DSP 有着丰富的内外资源及外设接口,能够将处理器微型化专业化并且支持内部高速缓存,数据处理速度很快且基本上能够满足本应用需求[1]。

链路口通信的使用不但能减轻DSP 的总线上的传输速度和压力,同时与FPGA 的有着相对较少的连接,所以链路口的使用为FPGA 和DSP 的实时数据通信提供了极大的便利,因而对两者间链路口通信进行设计和实现也是发挥高速图像数据处理的关键所在。

1图像处理平台的设计本文给出一款同时具有高速图像传输及处理的图像处理平台。

该嵌入式图像处理系统采用基于TS201的双DSP+双FPGA 的系统架构,可以同时处理不同传感器来源的图像(如星敏、红外等),而且该平台具有体积小、使用灵活、功耗低以及性能高等优点[2]。

基于TS201与FPGA的数字信号处理系统设计

基于TS201与FPGA的数字信号处理系统设计作者:王韩孙红胜陈昌明来源:《现代电子技术》2016年第05期摘要:研究了一种符合VPX标准的多处理器数字信号处理系统的硬件设计与实现。

该系统基于VPX标准3U板卡,采用2片ADSP TS201作为上层运算单元,1片Kintex 7系列FPGA作为底层处理单元和数据交换中心,提出利用链路口将ADSP TS201与FPGA互连,组成灵活的三点环型架构。

系统指标和实际应用表明,该系统具有很强的运算能力和较高的灵活性。

关键词:数字信号处理; TS201; FPGA; VPX;链路口中图分类号: TN409⁃34 文献标识码: A 文章编号: 1004⁃373X(2016)05⁃0078⁃03实时数字信号处理,数据量大、处理速度要求高,因此需要根据运算需求和应用环境,选择合适的计算芯片进行合理的架构,组成适应于不同需求的数字信号处理系统。

DSP在处理速度上,往往不及FPGA,但在算法的易实现性方面,DSP还有相当的优势。

FPGA的特点是运算能力强和逻辑可配置,使用FPGA能增强系统性能和灵活性。

结合两者优点,采用DSP+FPGA作为核心架构,已经成为目前数字信号处理系统设计的流行方式。

本文设计了一种基于双DSP与FPGA,符合VPX标准的高速数字信号处理系统。

该系统采用VPX 3U板卡标准,使用ADI公司的ADSP TigerSHARC 201系列数字信号处理芯片(TS201)与Xilinx公司的 Kintex 7系列FPGA芯片,提供强大的数据运算能力。

同时配有丰富的数据存储资源,以提高系统的综合性能。

整个系统具有运算能力强、结构灵活、可扩展性好等特点,能广泛应用于宽扩频通信、软件无线电、雷达信号处理等高速数字信号处理领域。

1 系统的设计整个数字信号处理系统可分为DSP,FPGA和VPX总线3个部分。

DSP部分的核心是2片ADSP TS201芯片,同时配有扩展存储能力的SDRAM芯片和用于存储非易失性数据的FLASH芯片。

在Altera的FPGA中实现高速Link口的时序约束方法

Ln ik口的传 输速 率都达 到 40MB s就 变得 相 当 困难 0 / , 了。要在 F G 中实 现多路 高 速 Ln PA ik口的逻辑 , 要 需 设计 高效 的 R L代 码 , T 并能 够对 F G 布局布 线 做严 PA

通信而设计的¨ 。通常 , 为了实现 T 2 1 S0 芯片与其他 不支持 Ln 协议 的芯片进行点对点的通信 , i k 需要使用 FG P A来实 现接 口协议 转换 的功能 。 T2 1Ln S0 ik口是 一 种双 数 据 率 、 同步 接 口。在 源 1 P中可 以通过 编程将 Ln ) S ik口的传 输速率 设置 成 20 0 MB s3 0MB s4 0MB s 6 0MB s / 、0 / 、0 / 或 0 / 。在 F G 内 PA 部布线资源充足的情况下 , 实现单路 L k口40M / i n 0 B s 的传输速率是 比较容易的。但是 , 当需要在 F G P A中

Ab t a t I sd fiu tt e l e mu tp eTS 01 L n o tlg ci e an a e fa sr c : ti ifc l or a i li l 2 i k p r o i n c r i ra o n FPGA n k u et a z t a d ma e s r h t e c i o tl gc c u d o e ae t ea iey ih s e d. c r tl u i DC i n o sri t nd a h L nk p r o i o l p r t a a r ltv l h g p e Ac u aey sng S t mi g c n tan s a

本文首先介绍了timequest时序分析器的基本sdc时序约束方法然后介绍了link口并分析了link口的逻辑代码在altera公司网站可以免费下载到veriloghdl参考代码该代码适用于aherafpga与ts201之间的link口互连经过分析得出需要进行特别约束的几个地方最后给出具体的约束方法

基于FPGA的高速数据传输接口设计与实现

基于FPGA的高速数据传输接口设计与实现摘要:随着信息技术的不断发展,高速数据传输接口的设计和实现变得越来越重要。

本文基于现场可编程门阵列(FPGA)技术,设计并实现了一种高速数据传输接口。

通过对FPGA的编程,我们能够实现灵活、可定制的接口,满足不同应用场景的需求。

本文详细介绍了接口设计的原理、方法和实现过程,并进行了性能测试和评估。

实验结果表明,该高速数据传输接口具有良好的性能和稳定性,能够满足高速数据传输的要求。

关键词:FPGA,高速数据传输接口,灵活性,性能测试1. 引言随着现代科技的快速发展,数据传输速度的需求不断提高。

为了满足这一需求,研究人员提出了各种高速数据传输接口的设计方案。

然而,由于传统硬件的限制,这些接口往往无法满足实际应用的要求。

因此,本文采用了FPGA技术,设计并实现了一种高速数据传输接口,以提升数据传输速度和灵活性。

2. 接口设计原理本文采用了基于FPGA的设计方法,通过对FPGA的编程,实现了高速数据传输接口的设计。

FPGA具有可编程性和并行处理能力,可以根据应用需求进行灵活定制。

通过将数据传输接口的相关功能逻辑实现在FPGA中,可以大大提高传输速度和稳定性。

3. 接口设计方法本文采用了一种基于时钟同步的数据传输方法。

通过将数据传输分为发送端和接收端两个模块,利用时钟信号进行同步,确保数据的准确传输。

发送端将需要传输的数据编码成数字信号,通过FPGA的输出引脚进行传输;接收端通过FPGA的输入引脚接收数字信号,并解码还原成原始数据。

4. 接口实现过程本文采用Verilog HDL语言进行FPGA的编程。

首先,根据接口设计原理和方法,编写发送端和接收端的功能模块;然后,通过逻辑综合、布局布线和时序分析等步骤,生成FPGA的比特流文件;最后,将比特流文件下载到FPGA芯片中,完成接口的实现。

5. 性能测试与评估为了评估所设计的高速数据传输接口的性能,我们进行了一系列的性能测试。

FPGA_ASIC-基于TS201的高速数据记录仪的设计与实现

基于TS201的高速数据记录仪的设计与实现Design and Realization of A High Speed Data Recorder Based On TS201(北京航空航天大学)于鹏飞王俊张文昊张玉玺Yu,Pengfei Wang,Jun Zhang,Wenhao Zhang,Yuxi摘要:本文提出了一种基于TS201的高速数据记录仪,能将雷达模拟信号转换成的数字信号经过处理后实时的按FAT32文件系统存储到固态盘中去。

采用DSP+FPGA的硬件架构,FPGA作为接口处理单元,DSP承担整个系统的协调控制,可以通过RS232和RS422接口与外部实现实时通信。

关键词:TS201,数据记录,高速,实时Abstract: In the paper, a high speed data recorder based on ADSP-TS201 is proposed. The system can store the digital signals, which are transferred from radar analog signals, into hard disk in real time with FAT32 file system. The FPGA+DSP hard architecture is adopted, in which FPGA is used to control the data interface, while DSP is utilized to control the entire system. Also, real time communication with other peripherals is implemented via RS232 and RS422.Key words:TS201;Data Recorder;High Speed;Real time中图分类号:TN957.5 文献标识码:A1引言雷达信号处理是整个雷达系统的核心部分,通过从雷达目标回波信号中提取目标信息,可以使整个系统的性能有很大的提高。

基于FPGA实现的高速串口传输技术与实现

(5)将配置位流文件下载到FPGA芯片中,进行实际运行和测试。

4、结论

本次演示设计和实现了一种基于FPGA的以太网和串口数据传输系统,实现了 高速、高效的数据传输和共享。本系统的优点在于具有高度的灵活性和可扩展性, 可以方便地根据实际需要进行功能扩展和优化。由于采用了FPGA技术,本系统还 具有体积小、功耗低、可靠性高等优点,可以广泛应用于各种嵌入式系统和智能 设备中。

为了更好地实现基于FPGA的高速光纤通信数据传输技术,需要以下几个方面:

1.优化硬件设计:根据具体的应用场景和需求,选择合适的FPGA芯片和硬件 组件,并对其进行优化设计,以实现更高效的数据传输和处理。

2.完善软件算法:利用FPGA的并行处理能力和数字信号处理算法,进一步完 善软件算法,提高数据处理速度和可靠性。

最后,为了提高稳定性和可靠性,可以研究更为高效的错误检测和纠正算法, 以及研究如何提高数据传输的鲁棒性。

总结

本次演示介绍了基于FPGA实现的高速串口传输技术与实现。通过利用FPGA的 灵活性和高效性,我们成功地实现了高速串口传输技术,并在速度测试中验证了 其优势。然而,也需要注意到这种技术存在的不足和挑战。未来,高速串口传输 技术将会朝着更高速度、更低成本、更稳定可靠的方向发展。

参考内容

随着信息时代的到来,数据传输的速度和可靠性成为了关键的要素。光纤通 信作为一种现代化的数据传输方式,具有传输速度快、容量大、抗干扰能力强等 优点,被广泛应用于各个领域。为了进一步提升光纤通信的性能,基于FPGA(现 场可编程门阵列)的高速光纤通信数据传输技术得到了广泛的研究与实现。

FPGA是一种高度灵活的芯片,可以由用户进行编程配置,实现各种不同的逻 辑功能。在光纤通信领域,FPGA可以被用于实现数据编解码、信号调制解调、误 码纠正等功能,从而提升数据传输的速度和可靠性。

ADSP TS201链路口通信的FPGA实现

ADSP TS201链路口通信的FPGA实现魏云斐;张遂南【摘要】AD公司的TS201 DSP系列可通过其特有的链路口实现高速通信,为使不具备此接口的设备也能与TS201进行链路通讯,采用FPGA实现数据在链路口与其他并行接口之间的传输,即128位并行模式和4位通信模式之间的转换.设计选用Xilinx公司的Virtex4系列的FPGA,它具有低功耗差分(LVDS)模式,双倍数据速率(DDR)寄存器以及嵌入式先进先出(FIFO)存储器等功能,更适合于此设计.在ISE和Modelsim等辅助工具的帮助下,使用VHDL语言编程,分析和优化整个设计,最终完成设计.可实现接收链路时钟频率为500 MHz,发送链路时钟频率为400 MHz.【期刊名称】《现代电子技术》【年(卷),期】2009(032)003【总页数】5页(P167-170,174)【关键词】链路口;低功耗差分;双倍数据速率;FPGA;VHDL【作者】魏云斐;张遂南【作者单位】西安微电子技术研究所,陕西,西安,710075;西安微电子技术研究所,陕西,西安,710075【正文语种】中文【中图分类】TN9190 引言随着电子技术的飞速发展,在实际应用中数据高速传输有着越来越高的要求,链路口为数据传送提供了高速、独立的通信机制,得到广泛应用。

AD公司生产的TS201 DSP就具备这种端口。

为了使不具备此接口的器件同样也能通过链路口与TS201进行高速通信,引入FPGA进行设计。

FPGA器件因其集成度高、功能强大、现场可编程等优点被广泛应用于各种场合。

通过在FPGA上参照链路口通信协议编写VHDL程序,完成数据传送方式的转换,实现此接口与其他设备通信,以满足系统的高速通信要求。

本文设计了一种基于Xilinx公司Virtex4系列的FPGA的128位并行数据与ADSP TS201的链路口通信方式。

1 ADSP TS201链路口协议ADSP TS201有4个链路口均采用LVDS(Low Voltage Differential Signaling )电路,每个链路口都是由4位双向差分数据线和另外3个控制信号构成。

利用FPGA实现与TS201的LinkPort高速数据互联

L n P r 发送数 据是以 18 i ik ot 2b t为基本 的单 位 的, 所以一次发

送 数 据 至少 需 要 1 6个 时 钟周 期 来 完 成 。

3 在 F G 中实 L n P r P A ik o t口

基于 L D V S技 术 的 Ln P r , VD ik ot口 L S是 一 种 小 振 幅 差 分 信 号 技 术 , 用 非 常 小 的 幅 度 信 号 (5 mv 通 过 一 对 差 分 P B 使 30 ) C

L BC M PO x

.

\

’

L B CM PI x Lx KI AC Lx K AC O

图 2 Ln r i k Po t通 信 协 议

数 据 桢 的开 始 是 由 Ln P r 时 钟 的上 升 沿 来 指 示 的 , ik ot 在 时 钟 的 上升 沿 和下 降沿 分 别 传 送 数 据 , 钟 结 束 , 时 则数 据传 送

也 停 止 。所 以 Ln P r ik ot口 上 的 时 钟 是 不 连 续 的 。T 2 1的 S0

L B MP 它 们 的连 接关 系如 下 图 1 示 ; xC I 所 其 中 接 收 和 发 送 数 据 的 数 据 线 以 及 时 钟 线 都 是 使 用 L S 这样 有利于 实现高速 的数据传 输 , 应 用 中,S VD , 在 D P之 间 的 Ln P r 传 输 数 据 可 高达 每 对 线 5 0 ik ot 0 MHz 。

的对 接 的 原 理 和 实 际 应 用 , 实 时 系统 和 T 2 1之 间搭 起 了 在 S0

一

Ln P r ik ot口发 送 的 接 收 数 据 的 逻 辑 是 很 直 接 的 , 是 通 但 过 采 用 L S技 术 , 以 运 行 在很 高 的 速度 上 。 2 1处理 器 VD 可 TS 0 所 使 用 的 Ln P r ik ot协议 的一 个 简化 说 明如 下 图 2所 示 :

fpga高速串口原理

fpga高速串口原理FPGA高速串口原理引言在FPGA(可编程逻辑门阵列)的设计过程中,高速串口通信是一项重要的技术。

本文将从浅入深地介绍FPGA高速串口的原理及相关概念。

什么是高速串口高速串口是指在FPGA中实现的,具有高速传输速率的串行通信接口。

它可以通过一根信号线同时传输多个bit的数据,相比传统的串行通信接口,高速串口能够更快地传输数据,提高系统的通信效率。

高速串口的工作原理1.串行通信:高速串口采用串行通信的方式进行数据传输。

串行通信是指逐位逐位地传输数据,相对于并行通信,串行通信能够充分利用有限数量的信号线来传输大量的数据。

2.串行-并行转换:在发送端,高速串口会将并行数据转换为串行数据进行传输。

在接收端,高速串口则将串行数据转换为并行数据供后续处理。

这种串行-并行的转换方式,能够更高效地利用信号线进行数据传输。

3.时钟同步:高速串口的发送端和接收端需要通过共享一个时钟信号来进行数据的传输。

通过时钟同步,可以确保发送端和接收端在相同的时间点进行数据的采样和发送,避免数据丢失或错误。

4.编解码和差分传输:为了提高数据传输的可靠性,高速串口通常会采用编解码技术和差分传输方式。

编解码技术可以将原始数据进行压缩和差错校验,以提高数据传输的速率和可靠性。

差分传输则可以减小传输过程中的干扰和噪声对数据的影响。

高速串口的应用高速串口广泛应用于许多领域,包括但不限于以下几个方面:1.网络通信:高速串口能够实现高速传输和接收网络数据,用于局域网和广域网的通信。

2.存储系统:高速串口可以连接到存储设备,实现高速数据的读写和传输。

3.图像和视频处理:高速串口可以用于实时图像和视频的采集、传输和处理,提高图像和视频处理系统的效率。

4.仪器仪表:高速串口可以连接仪器仪表,实现高速数据的采集和控制。

总结本文从浅入深地讲解了FPGA高速串口的原理及相关概念。

通过了解高速串口的工作原理和应用领域,读者可以更好地理解和应用这一重要技术。

TS201高速通信接口设计及实现

TS201高速通信接口设计及实现作者:龚翠玲吴超龚丽芳宋万杰吴顺君来源:《现代电子技术》2008年第03期摘要:ADI公司TigerSHARC系列DSP芯片TS201性能优越,在高速实时信号处理中得到广泛应用,而其中对TS201的通信接口设计成为保证其高速实时性能的关键。

对TS201与FPGA之间两种主要通信接口进行了分析,并给出了两种接口的设计方法,其中总线传输方式设计简便,但占用较多的资源,而链路口方式采用LVDS技术,传输速率高而且可靠,更适合DSP与FPGA的通信。

该设计方法已成功应用于某高速实时信号处理机中。

关键词:TS201;FPGA;总线传输;链路口传输;LVDS中图分类号:TP36 文献标识码:B文章编号:1004373X(2008)0304003Design and Realization of TS201 High Speed Communication InterfaceGONG Cuiling1,WU Chao1,GONG Lifang2,SONG Wanjie1,WU Shunjun1(1.National Lab of Radar Signal Processing,Xidian University,Xi′an,710071,China;2.Tanbu No.1 Middle School of Huadu,Guangzhou,510820,China)Abstract:As a part of TigerSHARC DSP chip made by ADI Corporation,TS201 has high performance and has been widely used in high speed real—time signal processing.The communication interface design for it has become a key problem of ensuring its high speed real—time performance.This paper makes an analysis of two mainly interfaces of the communication between TS201 and FPGA,which is bus and link port transmission,and presents the design method of those two interface.As the basic transmission method,bus method is simple and has low program complexity.However,link port method requires few sources and has high transmission speed,and is more suitable for communication between DSP and FPGA.The design methods in this paper has been successfully used in some high speed real—time signal processing.Keywords:TS201;FPGA;bus transmission;link port transmission;LVDS1 引言ADSP—TS201是继ADSP—TS101之后美国ADI公司推出的新一代高性能TigerSHARC 处理器ADSP—TS201/202/203系列中的一款,核时钟最高可达600 MHz,其片内集成了更大容量的存储器,性价比高,兼有ASIC和FPGA的信号处理和指令处理器的高度可编程性与灵活性,适用于高性能、大存储量的信号处理和图像应用,例如雷达与声纳应用。

基于ADSP-TS201与FPGA的信号处理系统实现及优化设计

基于ADSP-TS201与FPGA的信号处理系统实现及优化设计现代雷达信号处理已成为雷达功能实现的关键,本文根据某型雷达信号处理机的系统需要,对其硬件结构及软件设计做了系统优化。

设计了1套以4片TS201和1片FPGA为核心信号处理板,该系统仅用l副板卡即实现空时二维信号处理。

实现了自适应副瓣相消,4路脉冲压缩与MTI/MTD,副瓣匿影和差波束测角等算法,可以完成对目标距离,方位偏差量的测算,满足系统需求。

1 系统组成分析回波信号在天线上进行部分微波合成,形成和、差通道信号及两路辅助天线信号,进行IQ正交插值,1/8抽取后,形成4路待测数据,数据率共为128 MB/s。

系统算法结构,如图1所示,主要由旁瓣相消模块,数字脉压模块,MTD处理模块由3部分组成。

和路信号MTD(FFT-CFAR)后经副瓣匿影若判定有目标则再由和、差两路数据计算方位偏差量。

以雷达工作的低重频模式为例,IQ数据为5 388点,重频为140 Hz,考虑到一定的时间余量,4路信号的传输及处理必须在《6.7 ms的时间内完成。

因此系统的数据速率、数据量及运算规模决定了系统设计必须具有以下特点:(1)具有高性能浮点处理芯片,可完成旁瓣相消、脉冲压缩、相参积累、杂波图、恒虚警处理。

(2)内部各处理芯片间可进行高速数据传递且可外部扩展存储芯片,保存大量数据。

(3)具备对外的数据接口和控制接口,并可输出故障检测信号。

(4)软件设计中必须进行大量优化,保证上述所有处理模块在1个脉冲周期内完成。

2 雷达处理机实现2.1 硬件平台设计系统运算量及时间要求,信号处理板需采用多DSP并行处理的结构,为达到高速浮点处理能力、高数据吞吐率及大内存空间的要求,DSP芯片选用ADSP-TS201,它是ADI公司最新型号的TIgerSHARC架构高性能浮点数字信号处理器。

它具有最高达600 MHz的工作时钟,且每周期可完成4条指令;包括双独立运算模块及用于地址计算的双独立整型。

FPGA与ADSP TS201的总线接口设计方案

FPGA 与ADSP TS201 的总线接口设计方案在雷达信号处理、数字图像处理等领域中,信号处理的实时性至关重要。

由于FPGA 芯片在大数据量的底层算法处理上的优势及DSP 芯片在复杂算法处理上的优势,DSP+FPGA 的实时信号处理系统的应用越来越广泛。

ADI 公司的TigerSHARC 系列DSP 芯片浮点处理性能优越,故基于这类DSP 的DSP+FPGA 处理系统正广泛应用于复杂的信号处理领域。

同时在这类实时处理系统中,FPGA 与DSP 芯片之间数据的实时通信至关重要。

TS201 DSP 的外部总线接口有两种协议:慢速协议和高速流水协议。

流水线协议适合与快速同步设备连接,文中采用此协议,实现DSP 与FPGA 之间的通信。

1 DSP 流水线协议流水线协议用来提供流水线方式的数据传输。

在该传输协议下,每个时钟周期可以传输一个数据。

控制流水线协议进行数据传输的主要信号包含以下引脚:RD——数据传输读信号;WRH 和WRL——数据传输写信号;BRST——突发方式数据传输指示;ADDR——地址总线;DATA——数据总线。

流水线协议数据传输有两种方式:普通流水线协议和突发流水线协议。

ADSP TS201 的数据总线位宽可以通过SYSCON 寄存器设置为32 位或者64 位,但是有时候需要传输的数据位宽可能是32 位,64 位或者128 位,这样就有可能出现数据总线位宽和数据位宽不一致的情况,如果总线位宽小于数据位宽,DSP 采用突发流水协议传输,否则采用普通流水线协议。

1.1 普通流水线协议图1 是DSP 使用普通流水协议,写FPGA 内部寄存器时序图,流水深度。

TS201 LINK口光通信传输的接口设计

TS201 LINK口光通信传输的接口设计

李亚捷;唐清善

【期刊名称】《测控技术》

【年(卷),期】2010(029)002

【摘要】针对在应用中高速DSP TS201的LINK 口不能直接通过光纤实现数据远程传输的缺陷,介绍了一种基于FPGA(Xilinx的Virtex-4系列中的XC4VFX60)的LINK口与光纤通信的接口设计.给出了DSPTS201的LINK口与光纤通信转换的硬件和FPGA逻辑设计实例,并对逻辑设计的时序进行了综合和仿真,最后在Virtual DSP开发环境中验证了接口设计的LINK口远程通信互连结果.结果表明通过接口设计电路的转换.TS201 LINK口实现了在物理层按照RockeIO方式通信,数据层按照LINK口协议通信的远程数据传输功能,数据传输速度单向为250 MB/s,双向为500 MB/s,且具有高速、可靠稳定等特点.

【总页数】5页(P28-32)

【作者】李亚捷;唐清善

【作者单位】长沙理工大学,物理与电子科学学院,湖南,长沙,410114;中国科学院声学研究所,北京,100190

【正文语种】中文

【中图分类】TP391.8

【相关文献】

1.基于IP核的TS201和CPCI总线接口设计 [J], 竺红伟

2.ADSP TS201S Link口在多DSP系统中的应用 [J], 赵俊杰;孙大光

3.FPGA与ADSP TS201的总线接口设计 [J], 李丽;曾玲;李思

4.TS201高速通信接口设计及实现 [J], 龚翠玲;吴超;龚丽芳;宋万杰;吴顺君

5.TS201 LINK口通信的关键设计与实现 [J], 唐清善;蔡惠智

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA 的TS201 linkport 数据通信设计与实现

基于FPGA的TS201 linkport数据通信设计与实现王经纬1,杨华军1,黄自力2,高升久21.电子科技大学物理电子学院,成都 (610054)2.西南技术物理研究所,成都 (610041)E-mail:1982wjw602@摘要:DSP+FPGA是一种高端数字信号处理的架构。

TS201的linkport是通过DMA方式控制的,不占用DSP的内核计算时间以及减轻数据总线的负担,并且linkport具有高速传数速率。

本文基于altera公司的Stratixii系列的EP2S60型FPGA与ADI公司的Tigershark系列的TS201型DSP的linkport进行数据通信,该设计已经成功地应用于某图象处理器中。

关键词:DSP+FPGA,TS201,Stratixii,linkport中图分类号:TN1. 引言当今的数字信号处理技术中,DSP+FPGA是比较常用的方式。

与传统的专用集成电路(ASIC)相比,它既避免了惊人的成本,又能满足设计者对高级系统中高性能的要求。

所以在通信、军事、航空、医学等领域都有广泛的应用。

TS201是ADI公司推出的新一代处理器的代表,500/600MHz的时钟速率,24Mbits片内存储器,4个平均吞吐率4Gbits的链路口,确保了它在高端数字信号处理中的地位。

TS201的linkport是通过DMA方式控制的,不占用DSP的内核计算时间以及减轻数据总线的负担,并且linkport具有高速传数速率。

TS201器件含有4条可选的linkport接口,每一个链路口独立地进行接收和发送操作,可与其它链路口连接也可以不连。

它提供一个高速通信渠道,这是一个非常有用的DSP和FPGA之间的连接,linkport接口是一个full-duplex接口,它提供4位接收和4位发送I/0能力,使用LVDS低压差分传送技术,它也可以运行在双数据速率在上跳沿和下跳沿都传输数据,带宽可以达到500MHz,它在噪声/EMI、功耗方面也具有优越性[1]。

TS201 LINK口通信的关键设计与实现

TS201 LINK口通信的关键设计与实现

唐清善;蔡惠智

【期刊名称】《计算机测量与控制》

【年(卷),期】2009(017)008

【摘要】针对DSP芯片TS201的LINK口互连在高速数据通信中存在数据错误、突发数据块传输不稳定等缺点,在分析其通信协议的基础上,并结合实际应用,提出了设计LINK口通信的关键要求,给出设计的要点,设计与实现了TS201的LINK 121互连以及FPGA(Xilinx公司的XC4VFX60)与TS201 LINK口互连,得到了实际测试结果;结果表明,所设计的LINK口互连具备的优点有:1)DSP之间通信可以达到单向600MB/s,双向1.2GB/s;2)DSP与FPGA之间通信可以达到单向450MB/s,双向900MB/s;3)LINK口的通信具备稳定、突发数据块传输无错误等性能.

【总页数】4页(P1594-1597)

【作者】唐清善;蔡惠智

【作者单位】中国科学院声学研究所,北京,100190;中国科学院声学研究所,北京,100190

【正文语种】中文

【中图分类】TP391.8

【相关文献】

1.TS201 LINK口光通信传输的接口设计 [J], 李亚捷;唐清善

2.ADSP TS201S Link口在多DSP系统中的应用 [J], 赵俊杰;孙大光

3.水洗机CANLink网络通信的设计与实现 [J], 黄晓伟;陈东升;陈宇杰

4.基于GUI/Simulink的通信对抗效能仿真平台设计与实现 [J], 邵正途;张路;陈鹏;许登荣

5.一种板间高速通信方式LINK口的设计与实现 [J], 毛海岑;江浩洋;石岩;张天序因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA和TS201链路口的多通道数据采集系统设计

基于FPGA和TS201链路口的多通道数据采集系统设计孙进卿;苏涛【摘要】设计了一个基于TS201高速链路口的多通道数据采集系统.其中FPGA 作为主控器件控制AD的数据采集,并把多通道数据整序通过链路口实时地送到TS201中.有效缓解了在多DSP共享总线平台上多通道数据采集系统引起的总线冲突,提高了信号处理平台的整体性能.【期刊名称】《现代电子技术》【年(卷),期】2007(030)004【总页数】4页(P129-132)【关键词】FPGA;链路口;多通道数据采集;总线冲突【作者】孙进卿;苏涛【作者单位】西安电子科技大学,雷达信号处理国家重点实验室,陕西,西安,710071;西安电子科技大学,雷达信号处理国家重点实验室,陕西,西安,710071【正文语种】中文【中图分类】TP2021 引言一个高速稳定的信号采集系统对于后续的数字信号处理有着重要的意义。

目前随着信号处理系统的计算量越来越大,出现了越来越多的多DSP级连并行信号处理平台。

为了便于各个DSP之间的通信和任务划分,多DSP并行信号处理平台又以共享总线的紧耦合系统结构为主流。

共享的总线不仅要完成DSP之间的通信,还要完成DSP与A/D,DSP与D/A,DSP与串口,DSP与USB器件、DSP与网口等之间的通信。

对于一个实时信号处理系统而言,从AD读数据和向DA写数据都需要连续匀速地进行,这样就会长时间占用共享总线,很容易引起数据采集与其他数据处理之间的总线竞争。

ADI公司TigerSHARC系列DSP具有多个高速链路口。

本设计用FPGA作为数据采集系统的控制器以及数据传输的缓冲器,将采集到的数据按照TS201链路口特殊的传输协议形成数据流,经TS201的链路口送到片内存储器,从而避开了共享总线,大大减少了共享总线的数据传输量,有效缓解了总线的竞争。

此外,链路口传输以DMA方式进行,采样数据的传输不会占用DSP内核的运算时间,可以提高整个系统性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

( 上海 交通大学信息安全工程学 院 ,上海 2O4 ) 需要在不同的系统之间实现 高速通信 ,现介绍 了一种基于 L D VS 的高速数据传输的接 口L ko , 出了在 Xlx FG i Pr 给 n t i 的 P A中实现该接 口的原理以及关键设计 ,并 i n

C SE i te p icp e a d te k y d in i mp e n ig Lik o ti tra e i l x F GA .I e ls ,i U S SOlh rn il e e g n i lme t n P r ne fc n Xii P n h s n n n t a t t h

21 0 上有 4个 L k r 口 , 个 LnP r 口有 ip t 每 no ik o t

2 根 线 , 含 收 发 两 个 模 块 , 个 模 块 中包 含 了 5 4 包 每 对 差分 数据线 和两个 控制线 , 分别 是 LD T 3— P xA 0 0 ,

L DAT03一O x N,L CL x KOUT P,L CL x KOU TN,L AC ̄ , x

成功地将 L kot i Pr口通信 的技 术应 用到 雷达测速 系统 中。 n

关 键词 :L D :L kot C V S i Pr n ;D M;F D D E

Li k o th g p e a a t a s e ewe n F GA n S 0 n P r i h s e d d t r n fr b t e P a dT 2 1

高 速通 道 。

之间 的通 信速 度要 求越 来 越 高 。A I T2 1 目 D 的 S0 是

前 业界性 能最 高 的 D P处 理 器 之一 , 有极 强 的 数 S 具 据处 理 能 力 和 丰 富 的 硬 件 资 源 , 主 频 可 高 达 其

1 Ln P r 介 绍 ik ot

so s p lao nt aa s m ao t pe e ue e t a ue eLnP r f a t eh hw api t ni h r r yt bu se m a r n t sst ik oto r l i i n a ci e d s e d s m t h h r e m g h

s e a rn fr e p d d t ta se . a Ke wo d y r s: L VDS; Lik o t DCM ; F n P r; DDR E RS

O 前 言

随着科技 的进 步 , D P的处 理 速 度 以及 相 互 对 S

和 实 际应用 , 实 时系 统 和 T 21之 间搭 起 了一 条 在 S0

维普资讯

20 0 7年第3 期

中 图分 类号 :N 1 T 91 文 献标 识码 : A 文 章 编 号 :09— 5 220 )3 06— 3 10 25 (07 0 —05 0

利用 F G P A实 现 与 T 2 Ln Pr高速数 据互 联 S0 1的 ik ot

L BCMP , L DATI x O x 3—0P,L DATI x 3一 O , L CLKI N x NP,

60 H , 体性 能 可 以达到 3 F.P 者 1G P , 0M z总 G I S或 D 2 O S 外 部数据 通 信速度 就成 为发挥 其性 能的瓶 颈 。为了

配合 发 挥其 强大 的处 理 能 力 ,S 0 专 门为 高速 通 T2 1

Ab ta t Wi h e eo me t fte tc n lg 。ti e d t mp e n ih s e o sr c : t te d v lp n e h oo y i sn e o i lme thg p e c mmu iain b t e h o h d nc t ewe n o

信 设计 了基于 L D V S技术 的 LnPr i o k t口。 L D V S是 一 种小 振 幅 差 分 信 号 技 术 , 用 非 常 小 的 幅 度 信 号 使 (5n ) 30l 通过一 对 差 分 H] 线 来 传 输 数据 , 两 V B走 在 条 平行 的差 分 信号 上 流经 的 电流 和 电压 幅 度相 反 , 噪声 同时耦合 到 两条线 上 , 于是 噪 声 被抵 消 。L D VS 差分 信 号 技 术 降 低 了 对 噪 声 的 关 注 。T2 1使 用 S0

C N C u .u .HU G u , C N Y - n HE h nh i AN Jn HE aj u

( dol f noma o eui n i eig S a g ̄ J oo gU ies , hn ̄ 204 ,hn ) S l Ifr t nS cryE g er , h a h i t nvri S a g n 0 i t n n an y t 020 C ia

d e n ss m.h a ri r ue V S—bsd h pe a as rief eL k otadds i r tyt T i pp t d csaL D f e e s e no ae i s ddt tnf t a i P r n i h g e a r e n rc n , —

L C KN x L I N,LA K x C O,LB MP。其 中接 收 和发 送 数 xC I 据 的数据 线 以及时钟 线都 是使 用 L D , V S 这样 有利 于 实现 高速 的数 据 传 输 , 应 用 中 , S 在 D P之 间 的 【n — jk